## Testability and Physical Security: The Cell-Level Approach

by

Jan Bělohoubek

A dissertation thesis submitted to

the Faculty of Information Technology, Czech Technical University in Prague, in partial fulfilment of the requirements for the degree of Doctor.

Dissertation degree study programme: Informatics Department of Digital Design

Prague, August 2021

### Supervisor:

Assoc. Prof. Ing. Petr Fišer, Ph.D. Department of Digital Design Faculty of Information Technology Czech Technical University in Prague Thákurova 9 160 00 Prague 6 Czech Republic

### **Co-Supervisor:**

Assoc. Prof. Ing. Jan Schmidt, Ph.D. Department of Digital Design Faculty of Information Technology Czech Technical University in Prague Thákurova 9 160 00 Prague 6 Czech Republic

Copyright © 2021 Jan Bělohoubek

# **Abstract and contributions**

Reliability, testability, and security belong to the most significant digital design challenges. Notable testability and security problems originate at the physical level, while the solutions may be implemented at higher levels.

This dissertation thesis deals with low-level approaches addressing the high-level design problems, namely the problem of the offline test length and fault coverage, and the problem of the physical security. The proposed solutions are based on enhanced CMOS structures. This dissertation thesis includes also a vulnerability analysis of the conventional CMOS circuit static power and established dynamic power countermeasures such as WDDL or SecLib. A particular contribution touches also on the security-reliability interplay.

In particular, the main contributions of the dissertation thesis are as follows:

- 1. Conceptual design of the short-duration offline test. The proposed fast offline test may be incorporated into the normal computation flow and potentially replace the online test in many cases while reducing delay and area penalty at the same time.

- 2. A method for designing a system with increased reliability incorporating the proposed approach is described and its efficiency is shown.

- 3. A novel CMOS design thereat is described, its severity is proved by simulation, and feasible physical attack scenarios are described. The threat arises especially in redundant structures like voters.

- 4. The described threat endangers also the dynamic power balancing countermeasures like SecLib and other conventional dual-rail-based countermeasures in general.

- 5. CMOS circuit-level (standard-cell level) attack countermeasures are proposed and evaluated. The proposed standard cells may be used as a direct replacement of conventional CMOS cells in a standard design process.

### Keywords:

combined attack, data-dependency, domino logic, dynamic logic, error detection, error correction, fault, fault coverage, fault model, invasive attack, offline test, optical beam induced current, online test, power analysis, power imprint, self-checking, side-channel, standard cell

# Acknowledgements

First of all, I would like to express my gratitude to my dissertation thesis supervisors Petr and Jan for their constant help, encouragement, countless discussions, proofreading, excellent collaboration, and friendship.

I would like to express special thanks to my current and former colleagues from the Department of Digital Design at CTU in Prague, ASICentrum spol. s r.o., and the Department of Materials and Technology at UWB in Pilsen, who maintained a pleasant, flexible and stimulating environment, and for their friendly advice, fruitful discussion, and collaboration.

My greatest thanks go to my family, and especially to my wife Klára for her infinite patience, care, and love.

My research has been partially supported by the grant GA16-05179S of the Czech Grant Agency, "Fault-Tolerant and Attack-Resistant Architectures Based on Programmable Devices: Research of Interplay and Common Features" (2016 – 2018), by CTU grants SGS14/105/OHK3/1T/18, SGS15/119/OHK3/1T/18, SGS16/121/OHK3/1T/18, SGS17/213/OHK3/3T/18 and the OP VVV MEYS funded project CZ.02.1.01/0.0/0.0/ 16019/0000765 "Research Center for Informatics". To my wife, Klára

# Contents

| 1        | Intr | oducti  | ion                                                                                                                        |     |  |     |   |   |   | 1        |

|----------|------|---------|----------------------------------------------------------------------------------------------------------------------------|-----|--|-----|---|---|---|----------|

|          | 1.1  | Motiva  | ation                                                                                                                      |     |  |     |   |   |   | 1        |

|          | 1.2  | Proble  | em Statement                                                                                                               |     |  |     |   |   |   | 3        |

|          | 1.3  | Goals   | of the Dissertation Thesis                                                                                                 |     |  |     |   | • |   | 4        |

|          | 1.4  | Struct  | ure of the Dissertation Thesis                                                                                             |     |  | • • |   | • | • | 4        |

| <b>2</b> | Bac  | kgrour  | nd and State-of-the-Art                                                                                                    |     |  |     |   |   |   | <b>5</b> |

|          | 2.1  | VLSI (  | CMOS Technology                                                                                                            |     |  |     |   | • |   | 5        |

|          |      | 2.1.1   | CMOS Technology and Planar Process                                                                                         | , , |  |     |   |   |   | 7        |

|          |      | 2.1.2   | Static and Dynamic CMOS                                                                                                    |     |  |     |   | • |   | 8        |

|          |      | 2.1.3   | Domino Logic                                                                                                               |     |  |     |   | • |   | 9        |

|          |      | 2.1.4   | Static and Dynamic Power                                                                                                   |     |  |     |   | • |   | 10       |

|          | 2.2  | CMOS    | S Photoelectric Laser Stimulation                                                                                          | , , |  |     |   |   |   | 15       |

|          | 2.3  | Digita  | l Circuit Diagnostics                                                                                                      |     |  |     |   | • |   | 18       |

|          |      | 2.3.1   | Physical Defects and Fault Detection                                                                                       | , , |  |     |   |   |   | 18       |

|          |      | 2.3.2   | Fault Models                                                                                                               |     |  |     |   |   |   | 20       |

|          |      | 2.3.3   | Error Detection And Correction                                                                                             | , , |  |     |   |   |   | 21       |

|          |      | 2.3.4   | Area Redundancy Overview                                                                                                   |     |  |     |   |   |   | 22       |

|          |      | 2.3.5   | Time Redundancy Overview                                                                                                   |     |  |     |   |   |   | 23       |

|          |      | 2.3.6   | Time and Area Redundancy Combinations Overview .                                                                           | •   |  |     | • | • |   | 24       |

| 3        | Des  | ign for | · Testability                                                                                                              |     |  |     |   |   |   | 27       |

|          | 3.1  | Motiva  | ation                                                                                                                      |     |  |     |   |   |   | 27       |

|          | 3.2  | Relate  | $ed Art \dots \dots$ |     |  |     |   |   |   | 28       |

|          |      | 3.2.1   | Test-Per-Clock                                                                                                             |     |  |     |   |   |   | 28       |

|          |      | 3.2.2   | Test-Per-Scan                                                                                                              |     |  |     |   |   |   | 29       |

|          |      | 3.2.3   | Fault Current Monitoring                                                                                                   |     |  |     |   |   |   | 29       |

|          | 3.3  | Short-  | Duration Offline Test                                                                                                      |     |  |     |   |   |   | 31       |

|          |      | 3.3.1   | Stuck-At-Fault Symptom Propagation                                                                                         |     |  |     |   |   |   | 31       |

|                                                               |       | 3.3.2 Conventional Monotonic Design                        | 31        |

|---------------------------------------------------------------|-------|------------------------------------------------------------|-----------|

|                                                               |       | 3.3.3 Isolated Monotonic Logic Blocks                      | 32        |

|                                                               |       | 3.3.4 Addressing Testability Limitations at the Cell Level | 35        |

|                                                               | 3.4   | Time-Extended Duplex                                       | 37        |

|                                                               | 3.5   | Discussion                                                 | 40        |

|                                                               | 0.0   |                                                            | 10        |

| 4                                                             | Side  | e-Channel Attacks                                          | <b>43</b> |

|                                                               | 4.1   | Motivation                                                 | 43        |

|                                                               | 4.2   | Related Art                                                | 44        |

|                                                               |       | 4.2.1 Differential Power Analysis                          | 45        |

|                                                               |       | 4.2.2 Correlation Power Analysis                           | 46        |

|                                                               |       | 4.2.3 Dynamic Power Channel                                | 46        |

|                                                               |       | 4.2.4 Static Power Channel                                 | 47        |

|                                                               | 4.3   | Laser-Induced Static Power Channel                         | 50        |

|                                                               |       | 4.3.1 Dual-Rail is Not Safe                                | 53        |

|                                                               | 4.4   | Proposed Attacks                                           | 54        |

|                                                               |       | 4.4.1 Attacker Model                                       | 54        |

|                                                               |       | 4.4.2 Preciselly-Targeted Attack                           | 54        |

|                                                               |       | 4.4.3 Block-Targeted Attack                                | 55        |

|                                                               |       | 4.4.4 Simplified Power Model of Complex Structures         | 56        |

|                                                               |       | 4.4.4 Shippined Tower Model of Complex Structures          | 00        |

| <b>5</b>                                                      | Bala  | anced Standard Cells                                       | <b>59</b> |

|                                                               | 5.1   | Motivation                                                 | 59        |

|                                                               | 5.2   | Related Art                                                | 60        |

|                                                               |       | 5.2.1 Domino Logic Employing Single Precharge PMOS         | 60        |

|                                                               |       | 5.2.2 Symmetric SecLib Gates                               | 60        |

|                                                               | 5.3   | Structures Enabling Static CMOS Current Balancing          | 64        |

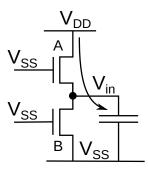

|                                                               |       | 5.3.1 Inverter Balancing                                   | 64        |

|                                                               |       | 5.3.2 Constant Current Source Approximation                | 65        |

|                                                               |       | 5.3.3 Output Voltage Filtering                             | 67        |

|                                                               |       | 5.3.4 Increasing Transistor-Level Symmetry                 | 68        |

|                                                               | 5.4   | Proposed Standard Cells                                    | 69        |

|                                                               | 5.5   | Case Study: SBOX Vulnerability Evaluation                  | 73        |

|                                                               | 5.6   | Discussion                                                 | 78        |

|                                                               |       |                                                            |           |

| 6                                                             |       | aclusions                                                  | 81        |

|                                                               | 6.1   | Summary                                                    | 82        |

|                                                               | 6.2   | Contributions of the Dissertation Thesis                   | 82        |

|                                                               | 6.3   | Future Work                                                | 83        |

| Bi                                                            | bliog | graphy                                                     | 85        |

| Reviewed Publications of the Author Relevant to the Thesis 9' |       |                                                            |           |

|                                                               |       |                                                            |           |

| Granted Patents of the Author Relevant to the Thesis           |                         |                   |

|----------------------------------------------------------------|-------------------------|-------------------|

| Remaining Publications of the Author Relevant to the Thesis 10 |                         |                   |

| Remaining Publications of the Author 10                        |                         |                   |

| A                                                              | Proposed Offline Test   | 105               |

| В                                                              |                         | <b>111</b><br>111 |

|                                                                | B.2 Process Design Kits |                   |

# **List of Figures**

| 2.1  | CMOS inverter cross-section                           | 7 |

|------|-------------------------------------------------------|---|

| 2.2  | Dynamic logic gate                                    | 3 |

| 2.3  | Domino-logic gate                                     | ) |

| 2.4  | Generalized CMOS gate 10                              | ) |

| 2.5  | Circuit Leakage Temperature Dependency Model          | 2 |

| 2.6  | Subthreshold Leakage Model                            | 2 |

| 2.7  | Subthreshold Leakage Temperature Dependency Model     | 3 |

| 2.8  | Gate Leakage Model                                    | 3 |

| 2.9  | Gate Leakage Example                                  | F |

| 2.10 | OBIC in the PN Junction 15                            | j |

| 2.11 | PN Junction SPICE Models                              | ; |

| 2.12 | Parasitic Bipolar Transistor SPICE Model              | 7 |

| 2.13 | OBIC Dependency on Illumination Power                 | 7 |

| 2.14 | Model Abstraction Hierarchy 19                        | ) |

| 2.15 | Conceptual Scheme of TMR                              | 3 |

| 2.16 | Conceptual Scheme of Error-Correcting Duplex          | 3 |

|      | Conceptual Scheme of Duplex Employing Reconfiguration | F |

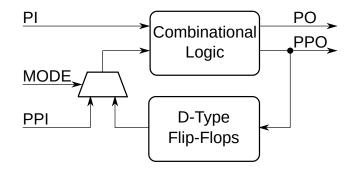

| 3.1  | Test-Per-Clock                                        | 3 |

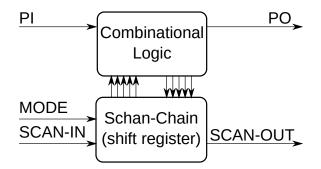

| 3.2  | Test-Per-Scan                                         | ) |

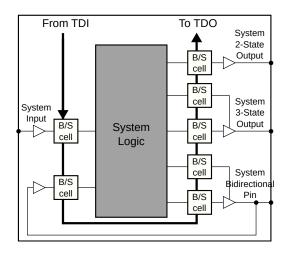

| 3.3  | Boundary-Scan                                         | ) |

| 3.4  | Isolated Monotonic Logic Block                        | 2 |

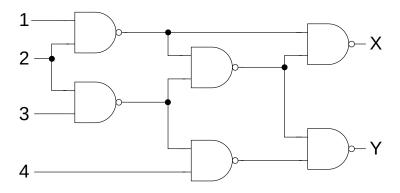

| 3.5  | NAND-based circuit example                            | 2 |

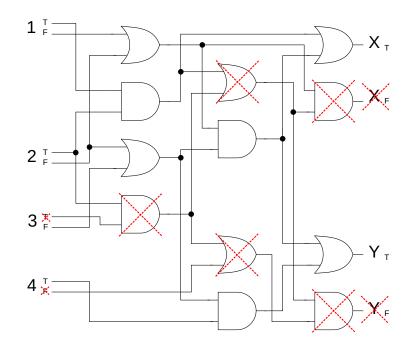

| 3.6  | Dual-rail Logic Circuit Reduction                     | 3 |

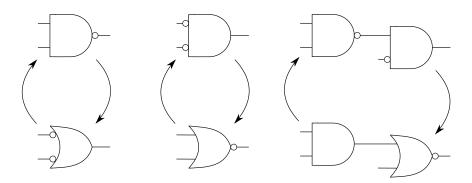

| 3.7  | Gate Transformation: Inverer Moving                   | Ł |

| 3.8  | Proposed Gate Structure                               | j |

| 3.9  | Tripple-Modular Redundancy                            | 7 |

| 3.10 | Time-Extended Duplex                                  | 3 |

| 3.11 | TED and TMR Aread Comparison 40                       | ) |

|      |                                                       |   |

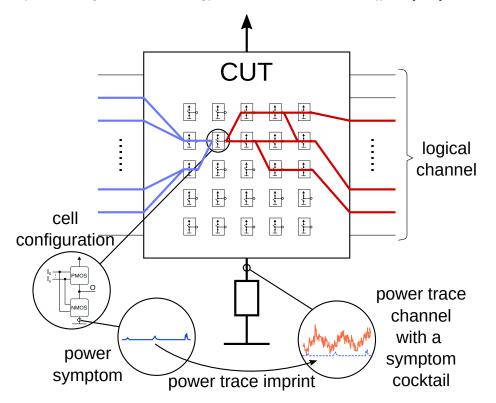

| 4.1  | Symptom Cocktails in Side-Channel                                         | 44  |

|------|---------------------------------------------------------------------------|-----|

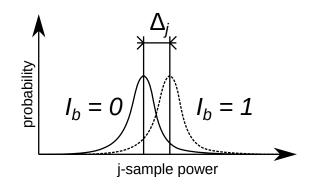

| 4.2  | Difference of Means                                                       | 46  |

| 4.3  | Inverter Leakage Example                                                  | 48  |

| 4.4  | Stack Effect                                                              | 48  |

| 4.5  | Gate Leakage Example                                                      | 48  |

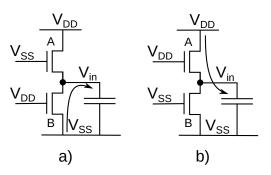

| 4.6  | Illuminated Transistor Stack                                              | 50  |

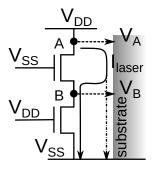

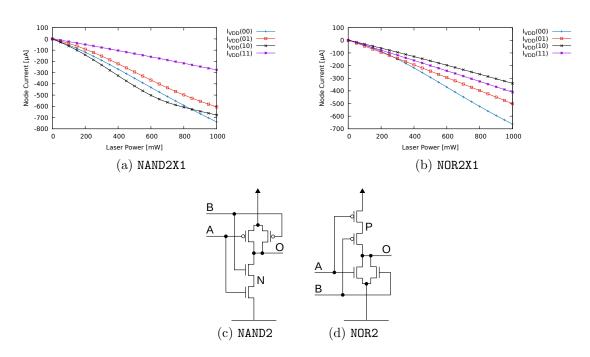

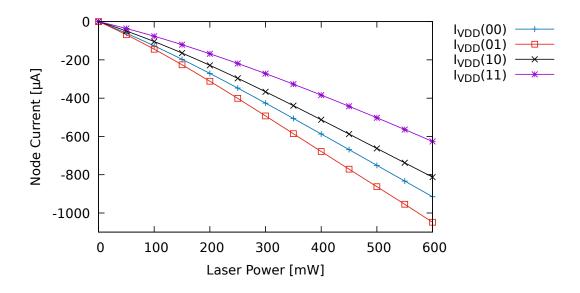

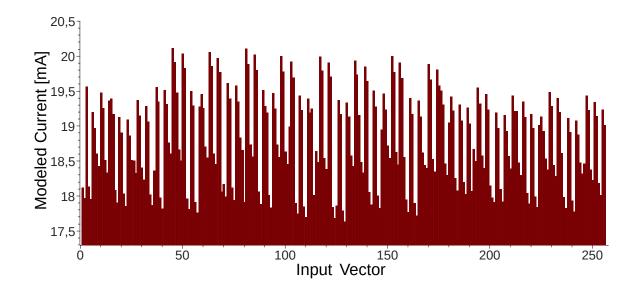

| 4.7  | Power Imprints of Conventional Illuminated CMOS Cells                     | 51  |

| 4.8  | Dual-Rail Power Imprint Depends on Power                                  | 53  |

| 4.9  | Simplified power model of the example circuit                             | 57  |

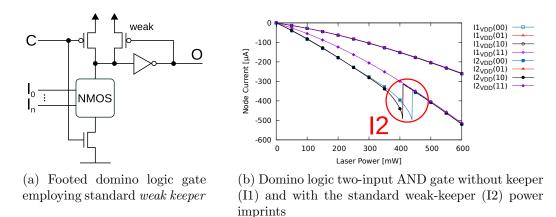

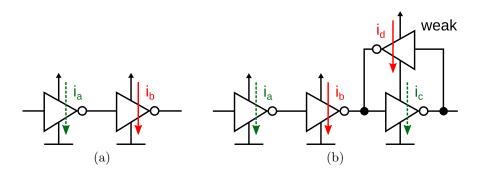

| 5.1  | Domino Logic Gate                                                         | 60  |

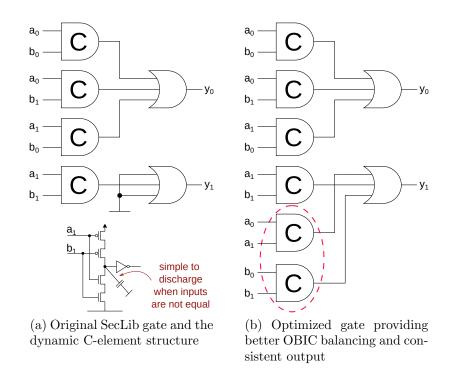

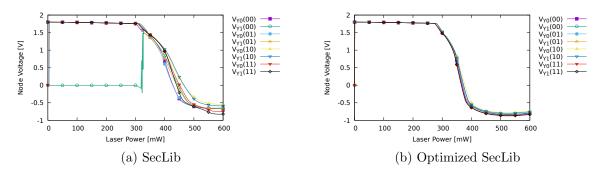

| 5.2  | Conventional and Optimized SecLib Gates                                   | 62  |

| 5.3  | Conventional and Optimized SecLib Outputs                                 | 62  |

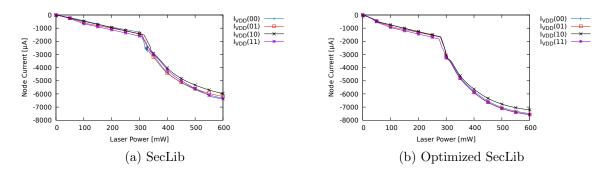

| 5.4  | Conventional and Optimized SecLib OBIC                                    | 63  |

| 5.5  | Inverter Chain Balancing                                                  | 64  |

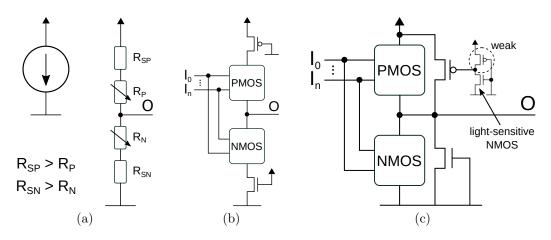

| 5.6  | Constant Current Source Approximation                                     | 66  |

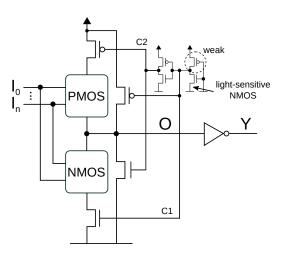

| 5.7  | Proposed Balanced Gate Structure                                          | 67  |

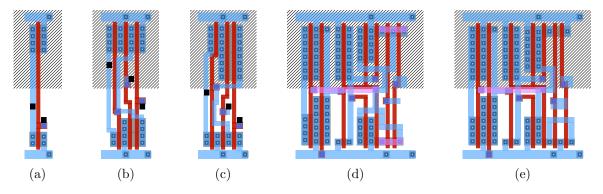

| 5.8  | Standard Cells in TSMC180nm                                               | 69  |

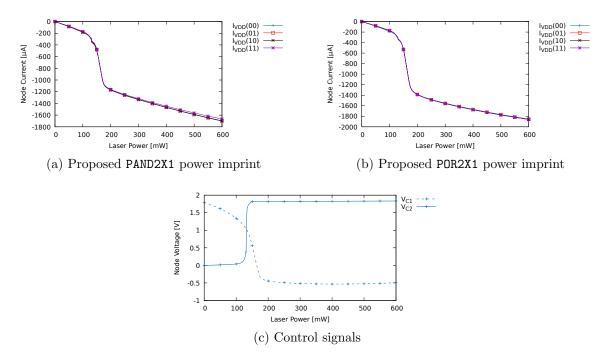

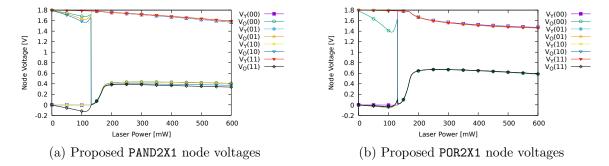

| 5.9  | Proposed Standard Cells Outputs and Power Imprints                        | 70  |

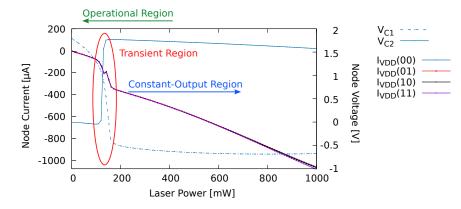

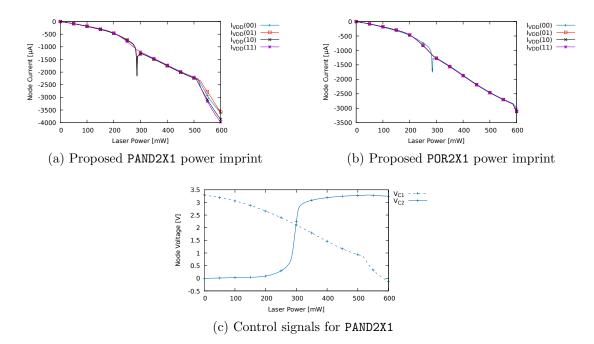

| 5.10 | Proposed Standard Cells Node Voltages                                     | 71  |

| 5.11 | Proposed Cell Operation Regions                                           | 71  |

| 5.12 | Layout size Comparison of Different SBOX Implementations                  | 75  |

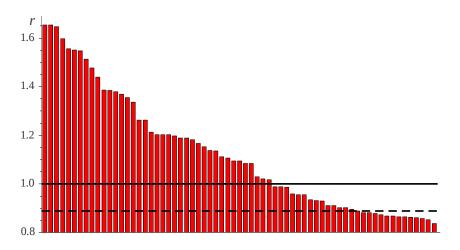

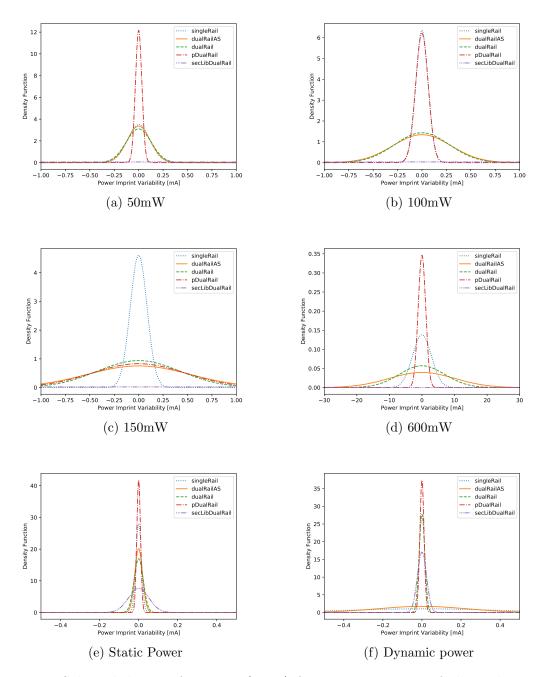

| 5.13 | Power Imprint Density Functions of Different SBOX Implementations         | 77  |

| 5.14 | Proposed Standard Cells Power Imprints and Control under Increased Supply |     |

|      | Voltage                                                                   | 79  |

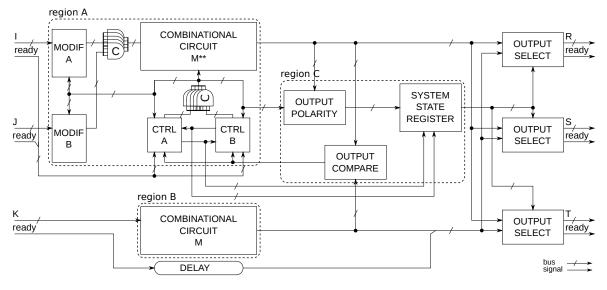

| A.1  | Detailed Scheme of the Time-Extended Duplex                               | 105 |

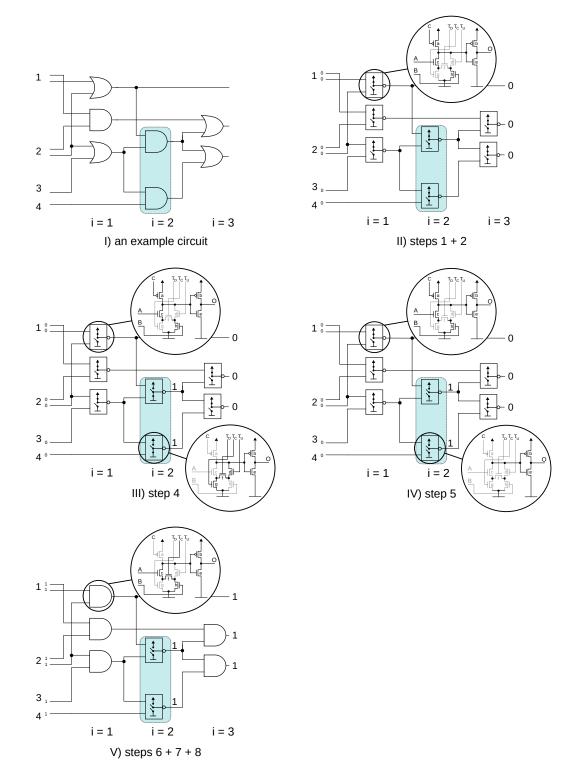

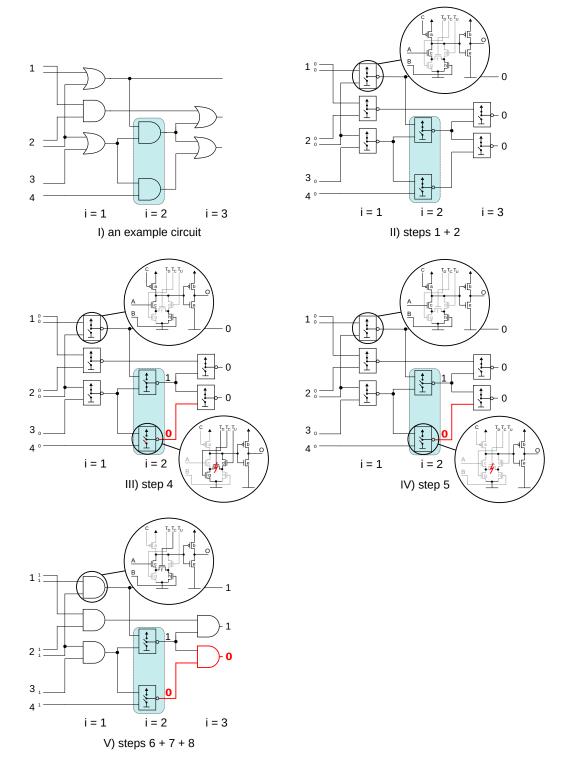

| A.2  | Short-Duration Offline Test Example                                       | 109 |

| A.3  | Short-Duration Offline Test Example – cont                                | 110 |

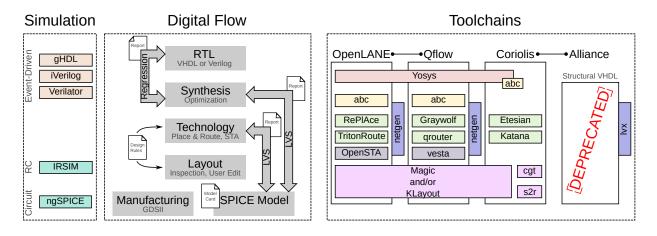

| B.1  | Digital Design Flow                                                       | 112 |

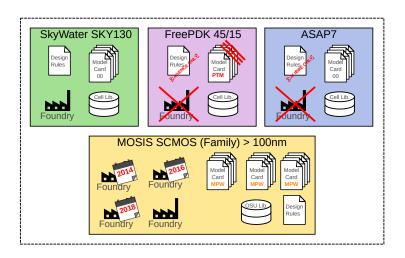

| B.2  | Open PDK Overview                                                         | 114 |

# List of Tables

|     | Control signals for AND gate function                                                                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Control signals for OR gate function                                                                                                                                 |

| 4.1 | Leakage Data-Dependency Example                                                                                                                                      |

| 5.1 | Proposed Cell Comparison                                                                                                                                             |

| 5.2 | Overhead Comparison of Different SBOX Implementations                                                                                                                |

| A.1 | The test sequence of the sub-test 1                                                                                                                                  |

| A.2 | The test sequence of the sub-test $2 \ldots $ |

| A.3 | The test sequence of the sub-test 3                                                                                                                                  |

| A.4 | Sub-tests covering the faults                                                                                                                                        |

# Abbreviations

| ATPG<br>BIST<br>CMOS | Automated Test Pattern Generator<br>Built-In-Self-Test<br>Complementary Metal–Oxide–Semiconductor |

|----------------------|---------------------------------------------------------------------------------------------------|

| CPA                  | Correlation Power Analysis                                                                        |

| DARPA                | Defense Advanced Research Projects Agency                                                         |

| DFT                  | Design For Test                                                                                   |

| DPA                  | Differencial Power Analysis                                                                       |

| DUT                  | Device Under Test                                                                                 |

| EDA                  | Electronic Design Automation                                                                      |

| FPGA                 | Field-Programmable Gate Array                                                                     |

| IDD                  | Supply current                                                                                    |

| IDDQ                 | Quiescent supply current (IDD)                                                                    |

| LPA                  | Leakage Power Analysis                                                                            |

| $\mathbf{LSI}$       | Large-Scale Integration                                                                           |

| MOS                  | Metal Oxide Semiconductor                                                                         |

| MOSFET               | Metal Oxide Semiconductor Field Effect Transistor                                                 |

| $\mathbf{MPW}$       | Multi-Project Wafer                                                                               |

| $\mathbf{MSI}$       | Medium-Scale Integration                                                                          |

| NDA                  | Non-Disclosure Agreement                                                                          |

| NMR                  | N-Modular Redundancy                                                                              |

| OBIC                 | Optical Beam Induced Current                                                                      |

| PDK                  | Process Design Kit                                                                                |

| $\mathbf{PLS}$       | Photoelectric Laser Stimulation                                                                   |

| SCMOS                | Scalable CMOS                                                                                     |

| $\mathbf{SCR}$       | Space Charge Region                                                                               |

| SPICE                | Simulation Program with Integrated Circuit Emphasis                                               |

| $\mathbf{SSI}$       | Small-Scale Integration                                                                           |

| $\operatorname{TED}$ | Time-Extended Duplex                                                                              |

| $\mathbf{TMR}$       | Triple Modular Redundancy                                                                         |

| $\mathbf{TSC}$       | Totally Self-Checking                                                                             |

| TSMC                 | Taiwan Semiconductor Manufacturing Company                                                        |

| VLSI                 | Very Large-Scale Integration                                                                      |

| WDDL                 | Wave Dynamic Differential Logic                                                                   |

# CHAPTER **L**

# Introduction

This dissertation thesis represents a contribution to the testability and security aspects of CMOS circuits design. Several notable testability and security problems originate at the physical level, while the solutions might be addressed on higher levels. Higher-level modeling introduces a certain level of simplification, often enabling an elegant design. On the other hand, the low-level approach allows addressing the root of the problem leading to a precise and compact design. This dissertation thesis addresses the CMOS circuit basic building blocks and continues down to the circuit and technology levels.

## 1.1 Motivation

There are many challenges in digital design today. To the most significant challenges belongs the reliable, safe, and secure design of digital systems supported by threat and reliability analysis [66, 70, 131]. Different approaches may be employed at each level of abstraction separately or combined to enhance security or reliability of the digital device. Similarly, unintended side-effects of high-level design decisions or even algorithm properties may corrupt security or reliability of the digital device [69, 92, 135]. Several levels of abstraction may be addressed starting at the algorithm level, through the architecture level, down to the microarchitecture and circuit levels.

The high-level design of today's digital design is enabled by a careful design of the basic building blocks – CMOS standard cells. CMOS cells are conventionally designed according to functional, power, and delay or area requirements [131]. Less conventionally, system-level reliability, testability, or security requirements are propagated down to the circuit level. It is advantageous to have a compact and universal library of standard cells. Therefore, approaches using standard cells are often preferred [121]. However, some of the security challenges are hard to overcome without the circuit level optimization leading to CMOS cell library extension.

This dissertation thesis represents a contribution to the low-level *design for testability* and *design for security* methods and vulnerability analysis. The method enabling a *short-duration* offline test of a combinational circuit was developed. The method is enabled

#### 1. INTRODUCTION

by a proposed CMOS cell-level design. Secondly, a new static-power-related vulnerability was identified and analyzed. This vulnerability potentially endangers the vast majority of today digital circuits, including the side-channel protected ones. At the same time, new CMOS cell-level approaches were developed to face the threat.

Some of the approaches presented in this dissertation thesis follow the known approaches, which experienced historically several times a great success in the digital design area. Successful examples of a strategy closely connected to the topic of this dissertation thesis are described below.

In the 1980s, the *domino logic* circuit design style was introduced to enhance highperformance CMOS circuits. In domino logic, system performance was increased by significant paradigm change at the lower design level(s). The domino logic optimizes the circuit delay by decreasing the in-circuit parasitic capacitances. In such a circuit, special – twophase – dynamic logic gates with a footprint smaller than conventional CMOS gates are employed in connection with the dual-rail circuit style and the precharge clock in combinational logic. Naturally, the domino logic suffers also from several disadvantages and due to them it was not widely adopted in the *design mainstream*, however, it was a relatively popular design method of high-performance circuits in the 1980s.

Dynamic logic in general and domino-logic in particular, is a design style dedicated to high-performance circuit design [131]. It offers many nice properties and challenges [113]. Since its introduction, domino-logic attracts many improvement efforts [71, 85, 109, 120]. The nature of the domino logic was also one of the inspirations of the first part of this dissertation thesis, as the proposed domino-like structures are used to achieve increased circuit (pseudo-online) testability and therefore reliability.

In the 1990s, Kocher et al. introduced the implementation attacks [92, 93]. Since their introduction, implementation attacks remain a significant threat for digital circuits: many efforts have been made to increase digital circuit attack resistance and novel attacks and attack countermeasures are constantly under development [15, 42, 52, 84, 98, 111, 121]. The implementation attacks use the properties of the implementation technology to break the secret stored in the circuit instead of breaking the (mathematical) principle of the implemented algorithm. The attacks on CMOS dynamic power, including Differential Power Analysis (DPA) or Correlation Power Analysis (CPA), are the most cited and well addressed in the literature. The probably most widely used approach to fight against the dynamic power data dependency is called *hiding*. Hiding mechanisms are incorporated into many real designs [53, 61, 88]. Many hiding approaches are based on dual-rail encoding [52, 111, 121 introducing almost constant (data-independent) dynamic power consumption, at least at the cycle level. As the dynamic power data dependency is closely connected with gate parasitics, delays, or even hazards [52], the CMOS gate, or even cell-level hiding approaches were proposed. In the security area, the low-level design is conventionally used to increase system security [52, 121].

One of the less discovered aspects of implementation attacks are attacks on *static power* consumption [84]. Recently, we described a similar class of attacks on *photoinduced static* current [A.5, A.6, A.7]. As the challenges connected to static power in general, and photoinduced static current in particular, are originated in the nature of CMOS technology,

it is convenient to use the CMOS cell-level optimization to increase the system security.

This dissertation thesis deals with *design for testability* and *design for security*. Novel CMOS structures employed to increase system security and reliability are presented and the CMOS vulnerability is presented and analyzed.

# 1.2 Problem Statement

Two challenges distinct at the system/device level are the subject of this dissertation thesis. Although the challenges are distinct at the system level, both are addressed at the circuit level in general and the CMOS cell-level in particular.

The first addressed problem is the on-line/off-line testability interplay problem. Online testing is employed in systems with an increased level of resilience to achieve a certain level of system reliability. The online test allows to detect system error and take action to mitigate error consequences or even mask the erroneous system output, while offline testing is applied to detect faults and identify faulty parts.

Online testing has two requirements: high error coverage and high test speed. This can be naturally achieved by a design employing area redundancy and checkers. Unfortunately, employing redundancy brings high area and/or delay overhead. Offline testing is conventionally less constrained by test time (compared to online testing) and involves smaller area overhead. On the other hand, it is conventionally not possible to guarantee the functional correctness of the device even when the test fault coverage is high.

The second addressed problem is related to the research of the security threat originating in the CMOS circuits first described by the author in [A.6]: the secret value processed by the CMOS combinational logic may be compromised by a combined attack employing power measurement and *Photoelectric Laser Stimulation* (PLS) of the target device. The severity of this vulnerability is significant, as it may be used to compromise even the trusted circuits with state-of-the-art attack protections. This is caused by the fact that the state-of-the-art physical attacks on CMOS devices are targeted on the circuit dynamic power, but the attack exploiting data-dependency of the PLS allows to overcome many industry-standard dynamic-power attack countermeasures.

# **1.3 Goals of the Dissertation Thesis**

This dissertation thesis deals with reliability and security challenges. The CMOS-based design properties are enhanced by the tunning performed at the CMOS cell-level:

- 1. A fast *short-duration offline test*, enabled by special CMOS cell design, is proposed. The fast offline test may be incorporated into normal computation flow and potentially replace the online test in many cases while reducing delay and area penalty at the same time.

- 2. The method for designing a system with increased reliability incorporating the proposed approach is described and its efficiency is shown.

- 3. A novel CMOS threat is described, its severity is proved by simulation, and feasible physical attack scenarios are described.

- 4. CMOS circuit-level (standard-cell level) attack countermeasures are proposed and evaluated. The proposed standard-cells may be used as a direct replacement of conventional CMOS cells in the common design process.

# 1.4 Structure of the Dissertation Thesis

This dissertation thesis is organized into six chapters as follows:

- 1. Introduction: Describes the motivation and goals of the dissertation thesis.

- 2. *Background and State-of-the-Art*: Introduces the reader to the theoretical background and terminology, and surveys the fundamental state-of-the-art and related work.

- 3. *Design for Testability*: Provides an overview of the state-of-the-art related to the contribution of this dissertation thesis in the DFT area, and continues with its presentation: the principal explanation of the proposed DFT method enabling a really short offline test is provided.

- 4. *Side-Channel Attacks*: Provides an overview of side-channel attacks, summarizes the related work, and continues with the contribution of this dissertation thesis: the chapter describes how the proposed approach discloses processed data in a static power channel in a particular case.

- 5. *Balanced Standard Cells*: Describes the proposed standard cell structure and provides a case study on the AES SBOX block.

- 6. *Conclusions*: Summarizes the results of the dissertation thesis and suggests the possible directions in further work.

# CHAPTER 2

# **Background and State-of-the-Art**

Transistor is not an Ice-Cream-Bar ...

Prof. Pinker, Introduction to Digital Systems

This dissertation thesis deals with CMOS combinational circuits, their structure, and circuit-level structure consequences on testability, side-channel vulnerability, and attack resistance. A bit of distinct language is used by security and testing communities, even though obvious analogies exist: interestingly, both testing and (physical) security have a common playground – the aim is to extract information from within the circuit. The design of the CMOS circuit basic building blocks – standard cells – may be exploited to simplify or complicate the extraction process according to the context and design requirements. This chapter summarizes the current state-of-the-art in both testing and security areas and provides the necessary introduction.

Section 2.1 gives a summary of the theory related to CMOS technology and static and dynamic power channels, Section 2.2 provides a short introduction to the CMOS *Photoelectric Laser Stimulation* (PLS), Section 2.3 summarizes the state-of-the-art in the diagnostics, testing and design for test.

## 2.1 VLSI CMOS Technology

The early integrated circuits in the 1950s were realized exclusively in the *bipolar* transistor technology introduced by Bell Labs. Later, in 1960s, started the success story of the *unipolar Metal Oxide Semiconductor Field Effect Transistors* (MOSFETs) [131]. The predominant advantage of MOSFETs lies in their low power consumption in the idle state compared to bipolar transistors. The MOSFETs require (almost) no current to keep the device in the ON state compared to a bipolar transistor, where the transistor is controlled by its *base* current.

#### 2. Background and State-of-the-Art

The MOSFET transistor comes in two types distinguished by the majority carrier: P-type (PMOS) where the majority of carriers are *holes* and N-type (NMOS) where the majority of carriers are *electrons*. The early commercially available processes utilizing MOSFETs to create integrated circuits manufactured by the *planar* process were *pMOS* and later *nMOS* processes [131].

The pMOS process allows the implementation of pull-up function (transistor structure connected to the supply rail) only<sup>1</sup>, while nMOS allows pull-down function only (transistor structure connected to the ground rail). In the circuit implemented using pMOS or nMOS, the complementary function is implemented by a pull-down or pull-up resistance introducing idle current. Thus the nMOS and the pMOS process still introduce a significant power consumption in the idle state.

The growing size of integrated circuits and unacceptable power consumption and speed limitations of devices manufactured by mainstream processes caused the wide adoption of the more complex and more expensive *Complementary Metal–Oxide–Semiconductor* (CMOS) in the 1980s. The CMOS uses both flavors of MOSFET transistors on a single *substrate*. It allows implementing complementary pull-up and pull-down functions simultaneously, cutting the idle current drastically, while allowing higher circuit performance at the same time [131].

The degree of integration in the semiconductor industry is traditionally indicated by SSI, MSI, LSI, and VLSI acronyms. The small ICs, including first integrated circuits, are denoted as *Small-Scale Integration* (SSI), the term *Medium-Scale Integration* (MSI) denotes later circuits with hundreds of on-chip transistor, while the term *Large-Scale Integration* (LSI) denotes CMOS circuits with tens of thousands transistors. The LSI circuits were first produced during the 1970s. Since hundreds of thousands of transistors are integrated on a chip since the 1980s, the term *Very Large-Scale Integration* (VLSI) is used for advanced circuits up today [119].

Today digital devices are almost exclusively manufactured using a CMOS planar process. Nowadays, however, the importance of the idle consumption of the integrated circuits has araised. As the size of CMOS devices shrinks down, the *channel leakage* rises. When hundreds of thousands or even millions or billions of transistors are integrated on a single chip manufactured in a recent process, its idle or *static power* consumption becomes high.

<sup>&</sup>lt;sup>1</sup>Negative supply voltage was also commonly used in pMOS, in this case, pMOS implements the topological pull-down function

## 2.1.1 CMOS Technology and Planar Process

The *Metal-Oxide Semiconductor* (MOS) devices are built on single crystals of silicon (Si) available as thin circular *wafers* of 15 - 30 cm diameter. As silicon is a group IV element with low conductivity, the group III and V *dopants* are used to increase silicon conductivity. The conductivity of doped silicon is given by missing (P-type) or added (N-type) valence electrons [131].

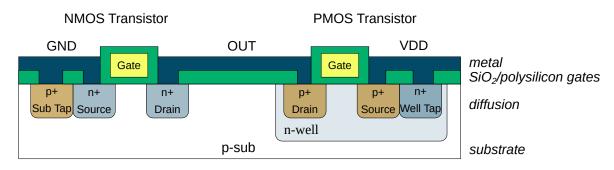

Figure 2.1: Conventional bulk CMOS inverter cross-section

The MOS structure is a sandwich-like *semiconductor* structure formed by conducting and insulating layers. The conventional *planar process* involves several chemical processing steps, including the introduction of dopants, oxidation of the silicon, and deposition and etching of metal layers [131].

The *Complementary MOS* (CMOS) process combines complementary P-type and N-type MOS devices on a single *substrate* (bulk). The complementary arrangement ensures that the idle current is conventionally negligible [131].

Figure 2.1 shows the CMOS device cross-section. The NMOS transistor is built on a Ptype body with N-type source and drain regions, the body is conventionally grounded. The PMOS transistor is conventionally built on a N-type body in a speciall well with P-type source and drain regions, while its body is conventionally connected to the supply voltage. The control gates are insulated by the silicon dioxide (SiO<sub>2</sub>) and are built of polysilicon or metal [131].

The voltage between the control electrode (gate) and transistor body affects the charge concentration in the thin body region under the gate. If the voltage is high enough, the *channel* is formed between the source and drain and the transistor becomes closed (ON) [131].

Materials used to manufacture the conventional CMOS transistors, the manufacturing processes, and the CMOS planar structure incorporating many PN-junctions enabled the great success of this technology in the past 50 years. The technology, however, determines also hidden properties of CMOS, influencing not only further technology scaling, but also typical manufacturing defect nature, or static and dynamic power data dependency, or the environment sensitivity in general and the light sensitivity in particular.

## 2.1.2 Static and Dynamic CMOS

Conventional CMOS circuits are *static*. Static CMOS gates use *complementary* PMOS and NMOS networks to compute output. The advantage of the static CMOS is namely the straightforward design, energy efficiency, and robustness. [131]. Alternative circuit families were developed to address speed, power, or area constraints. The approaches employed in CMOS *dynamic logic* influenced this dissertation thesis.

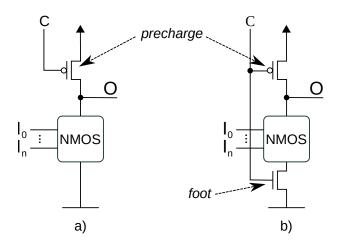

A dynamic gate works in two alternating phases: *precharge* and *evaluation*. In the first phase, the gate is forced to a defined state (by a dedicated control) and in the second phase, the gate inputs are evaluated.

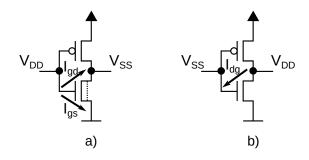

Assume that the control signal, called *clock*, forces the gate output to 1 during precharge. In the evaluation phase, the output remains 1 or switches to 0, depending on the input values, as shown in Figure 2.2a. This design style significantly reduces the load at the gate inputs and also the gate size compared to static CMOS, because the gate inputs drive NMOS transistors only.

Dynamic gates exist in two flavours distinguished by a presence of the NMOS *foot* transistor [131]: an *unfooted* gate is shown in Figure 2.2a, and a *footed* gate in Figure 2.2b.

Figure 2.2: a) dynamic-logic gate and b) footed dynamic-logic gate

The disadvantage of the dynamic logic is that it employs a high fan-out clock signal. This disadvantage is much lower than one would expect, because:

- the clock controls only one (a single PMOS for unfooted) or two (one PMOS and one NMOS for footed gates) transistors per gate,

- clock-controlled transistors may be relatively small because the design tolerates longer rising delays (up to half of the computational cycle for 50% clock duty cycle),

thus the load caused by transistor gates is relatively low. The main issue is that there is the need for additional (balanced) metal wires to distribute the clock signal. The main issue with the dynamic gates described above is that they require *monotonically rising* inputs during evaluation. The outputs of gates described above are *monotonically falling* (during evaluation) – this implies that those gates cannot be simply concatenated to form deeper circuits. Other notable issues connected with dynamic logic in general are *charge leakage* and *charge sharing* [131].

## 2.1.3 Domino Logic

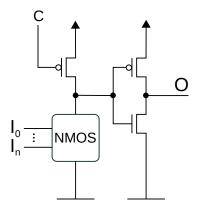

The concatenation of dynamic gates is enabled by inserting a static CMOS inverter at the dynamic gate output – the design style employing static inverters is called *domino logic*. Domino logic gate outputs are *monotonically rising* during evaluation [131] – see Figure 2.3.

Domino logic is a dedicated logic family belonging to dynamic logic [131], recently popular for high-performance chip design [131].

The precharge function can be realized by a single PMOS transistor only. If it is not guaranteed that the gate inputs are always 0 during precharge, it may be necessary to add an additional NMOS *foot* transistor, as shown in Figure 2.2b.

Figure 2.3: Domino-logic gate

The overall advantage of domino logic is the gate size and speed. The *mobility ratio* for holes/electrons is 2 - 3. This causes that PMOS transistors have to be bigger than the NMOS ones to achieve the same conductivity [131]. When the dynamic domino AND and OR gates with precharge to zero are used, the number of PMOS transistors is reduced significantly, compared to the number of NMOS transistors.

Domino logic thus represents a trade-off by providing faster and smaller gates with reduced static power and increased dynamic power.

Note that in domino logic, monotonicity is required, thus the circuit design conventionally employs dual-rail encoding to assure monotonicity.

### 2.1.4 Static and Dynamic Power

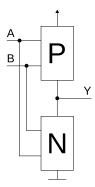

A static CMOS logic gate in general has an NMOS pull-down transistor network (N) and a PMOS pull-up transistor network (P) [131], as illustrated in Figure 2.4. The P/N parts arrangement ensures that only one of both parts is ON and the other is OFF in idle state for any combination of input values.

Figure 2.4: Generalized (2-input) CMOS gate structure

The static CMOS gate requires a significant amount of energy to change its output – it is called *dynamic power*. The dynamic power has a pulsed nature and it is composed mainly of the *load capacitance* charge/discharge and also by the *short current*. The short current is a short-duration part of the dynamic power arising from the simultaneously open PMOS and NMOS networks while switching. The dynamic power is commonly expressed by the following simplified (integral) equation [131]:

$$P_d = \alpha \cdot C \cdot V_{dd}^2 \cdot f, \tag{2.1}$$

where  $V_{dd}$  is the supply voltage, f is the switching frequency, C is the load capacitance being charged/discharged and  $\alpha$  is the activity factor expressing the average frequency of the gate output change. In static CMOS, the activity factor for the datapath is in most cases up to 0.5 (one transition per cycle), while conventionally it is close to 0.1 [131]. The load capacitance of a single gate is only charged/discharged when the output of the gate changes from  $0 \rightarrow 1$  or  $1 \rightarrow 0$ .

The other component of CMOS gate power consumption is called *static power* or *leak-age*. The static power represents the CMOS power in case of no switching activity. Static power is technology-dependent, and ideally, it should be minimized. Static power can be expressed by the following simplified (integral) equation [131]:

$$P_s = I_s \cdot V_{dd},\tag{2.2}$$

where  $V_{dd}$  is the supply voltage and  $I_s$  is the static current. It is not surprising that  $I_s$  for a particular gate depends on many variables including manufacturing process parameters and variability, logic gate geometry (parallel vs. serial connection of transistors), and size. The static curent is composed of several components:

$$I_s = I_{sub} + I_{gate} + I_{junct}, \tag{2.3}$$

where  $I_{sub}$  is the subthreshold leakage, which is the most important source of leakage in technologies with thicker gate oxide layer;  $I_{gate}$  is the gate leakage experienced by transistors with gate oxide thinner than 2nm [131] – in recent technology nodes, this type of leakage may overcome  $I_{sub}$ ; and  $I_{junct}$  is the junction leakage.

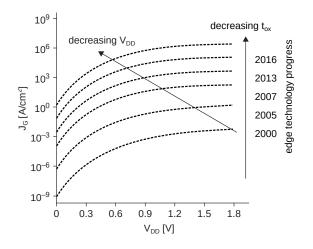

The  $I_{gate}$  is a minority leakage source compared to the subthreshold leakage in technologies above 100nm [58], but it increases significantly faster than the  $I_{sub}$  in recent technology nodes [72]. In a typical low-power CMOS process, care is taken to minimize  $I_{gate}$ , therefore the  $I_{sub}$  is dominant.

The junction leakage depends on the device geometry and junction biasing. The diodes formed on P-N junctions between diffusion and substrate or well might be sources of leakage if forward biased. But commonly, the substate is connected to VSS and well to VDD, ensuring that all junctions are reverse biased. The  $I_{junct}$  is normally below 0.1 fA, which is negligible compared to  $I_{sub}$  and  $I_{gate}$ .

#### Subthreshold Leakage

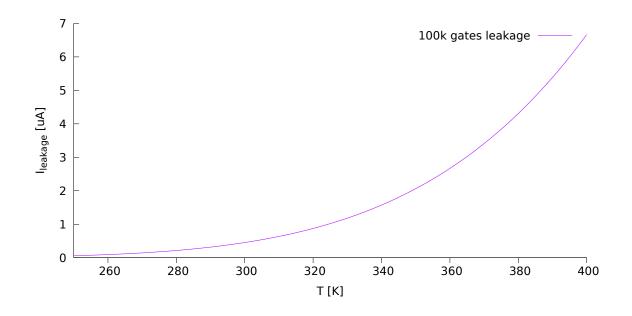

Subthreshold leakage is the dominant source of leakage in the majority of technologies. Subthreshold leakage represents the channel current between drain and source of the MOS-FET when the transistor is in the OFF state (gate-to-source voltage is below the threshold voltage). For conservative technology nodes (above 100nm), subthreshold leakage is the dominant leakage source in CMOS devices. The subthreshold leakage depends on environmental parameters such as temperature and interestingly, it is also input-dependent. Figure 2.5 gives an idea about the impact of the subthreshold leakage to a 100k gate circuit in a conservative 180nm technology node under rising temperature.

The subthreshold leakage model and main parameters are described e.g. in [130, 131]. The following equation expresses the subthreshold leakage:

$$I_{sub} = I_{ds0} \cdot exp(\frac{V_{gs} - V_{t0} + \eta V_{ds} - k_{\gamma} V_{sb}}{nv_T}) \cdot (1 - exp(\frac{-V_{ds}}{v_T})),$$

(2.4)

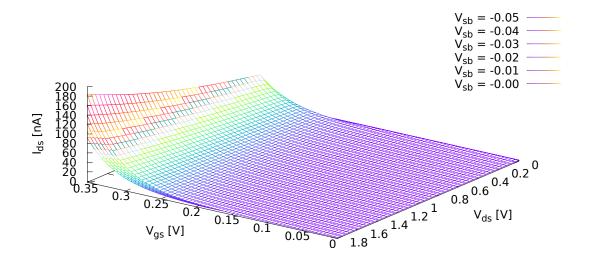

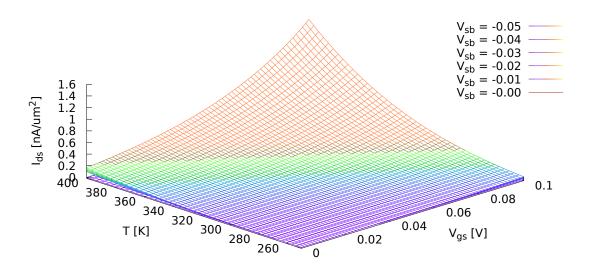

where  $I_{ds0}$  is a process parameter defining the drain current at the threshold voltage  $V_{gs} = V_t$  and the given temperature; the term  $V_{t0} + \eta V_{ds} - k_{\gamma} V_{sb}$  expresses the threshold voltage dependency on  $V_{ds}$  and  $V_{sb}$  – see Figure 2.6;  $\eta$  is the Drain-Induced Barrier Lowering (DIBL) coefficient expressing the threshold voltage dependency on  $V_{ds}$  affecting strongly the short-channel transistors;  $k_{\gamma}$  is the body effect coefficient;  $v_T$  is the thermal voltage expressing the dependency on temperature. The  $v_T$  value is 26mV at room temperature and it is rising with rising temperature – Figure 2.7 illustantes the  $I_{sub}$  temperature dependency.

#### Gate Leakage

The gate leakage is caused by the *direct tunneling* effect experienced by transistors with gate oxide thinner than  $2nm (20\text{\AA})$ . PMOS transistors with the same gate thickness nor-

Figure 2.5: Temperature dependency for circuit composed of 100k gates in TSMC180nm – a simplified model based on a single inverter bahaviour where transistors are perfectly closed (NMOS  $V_{gs} = 0$  and  $V_{ds} = V_{DD}$ )

Figure 2.6: Subthreshold leakage current model for TSMC180nm at the room temperature: falling  $V_{sb}$  causes increase in the leakage as well as rising  $V_{gs}$  and  $V_{ds}$

mally experience a significantly lower gate leakage, as the electrons tunnel from the conduction band but holes in PMOS tunnel from the valence band over a higher barrier [131].

Figure 2.7: Temperature dependency subthreshold leakage current model for TSMC180nm;  $V_{ds} = V_{DD} = 1.8V$ ; Channel area =  $0.2 \times 2.0 \ \mu m$

In a conservative or low-power process, the PMOS gate leakage is typically negligible.

The gate leakage is strongly dependent on the insulator thickness and permittivity and loosely dependent on the supply voltage. The leakage current density depends on the supply voltage and the technology node for the most common insulator, which is the *silicon dioxide*  $(SiO_2)$ , is depicted in Figure 2.8. For processes where the gate dielectric is thin, materials with higher permittivity must be used in place of silicon dioxide [67].

Figure 2.8: Gate leakage as a function of the supply voltage  $(V_{DD})$ , the  $SiO_2$  gate oxide thickness  $(t_{ox})$ , and the technology generation [9, 131]

### 2. BACKGROUND AND STATE-OF-THE-ART

The gate leakage is also strongly connected with the state of the transistor – the area of the open channel region is extremely important – see Figure 2.9.

Figure 2.9: a) the closed NMOS transistor experiences a full gate leakage – tunneling to the channel region is significant; b) the open NMOS transistor experiences negligible reverse gate leakage, as the drain/gate overlap is small [72]

## 2.2 CMOS Photoelectric Laser Stimulation

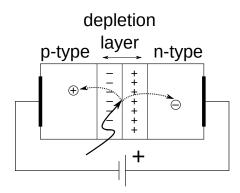

The laser beam passing through silicon creates, as a result of energy absorption, electronhole pairs along its path. In *Space Charge Regions (SCR)* of PN junctions, the generated electron-hole pairs are separated by the internal electric field, generating the *Optical Beam Induced Current* [56, 73, 107]. The principle behind OBIC is called a *photoelectric effect* – see Figure 2.10.

Figure 2.10: In the reverse-biased PN junction, the electron-hole pairs are separated by the electric field in the depletion layer: OBIC is induced

The photoelectric effect is in the context of CMOS often used for diagnostics [54, 56] or fault injection with precise location control [66, 100].

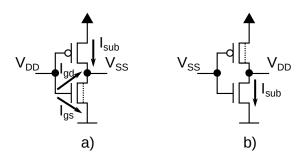

Sarafianos et al. published a series of papers related to *Photoelectric Laser Stimulation* (PLS), incrementally describing the electrical model of the pulsed photoelectric laser stimulation of an NMOS and PMOS respectively, e.g., [104, 105, 107].

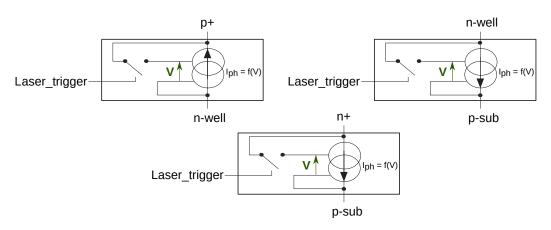

The Sarafianos et al. model includes photocurrents induced at the bulk CMOS PN junctions: p+/n-well, n+/p-sub and p-sub/n-well, as shown in Figure 2.1.

The photocurrent induced by a laser beam in any PN junction is modeled primarily by a voltage controlled current source – see Figure 2.11. The current amplitude is expressed by the following equation:

$$I_{laser} = (a \cdot V + b) \cdot \rho \cdot S, \qquad (2.5)$$

where S is the surface of the sensitive zone  $([\mu m^2])$ , a and b are fitting parameters expressing the laser power and technology parameters, V is the reversed bias voltage of the PN junction under laser illumination. Parameters a and b express the dependency on the laser power ([mW]) by using fitting parameters [107]:

$$a = p \cdot P_{laser}^2 + q \cdot P_{laser} \tag{2.6}$$

$$b = s \cdot P_{laser} \tag{2.7}$$

15

Figure 2.11: Voltage-controlled current sources representing photocurrent induced in certain PN junctions (see Equation 2.5) as used in SPICE models [104, 105, 107]. Laser\_trigger signal is used to turn the laser in the simulation environment ON

The parameter s is specific for PMOS and NMOS. The parameter  $\rho$  is used to take into account the distance between the PN junction and the laser spot, as expressed in the following equation:

$$\rho = \beta \cdot exp(-\frac{d^2}{c_1}) + \gamma \cdot exp(-\frac{d^2}{c_2}), \qquad (2.8)$$

where  $\beta$  and  $\gamma$  are the fitting parameters [107] and  $c_1$  and  $c_2$  express the influence of optical lens – a part of the measurement setup influencing the illuminated area and the energy density per square area.

Note that the equations above contain parameters specific for each PN junction: the *p*sub/n-well junction uses different parameters to express the photocurrent than p+/n-well or p-sub/n+. The parameter values are reported in the referenced papers and are included in our models available online [20].

The equations 2.5, 2.6 and 2.7 disclose that the induced photocurrent is proportional to the PN junction areas – to the transistor size, to the reversed bias voltage, and to the energy density represented by the laser power.

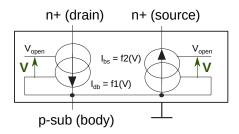

In addition to the OBIC generated in each PN junction, the *parasitic bipolar* transistor might be activated. The NPN parasitic transistor in NMOS is activated when the transistor body voltage is increased enough. The simple bipolar model for NMOS transistor [106, 107] is in Figure 2.12. Similarly, the PNP parasitic bipolar transistor may be activated in PMOS. For lower laser powers, the PNP parasitic bipolar transistor was not observed [106] and thus we do not include it in our models [20].

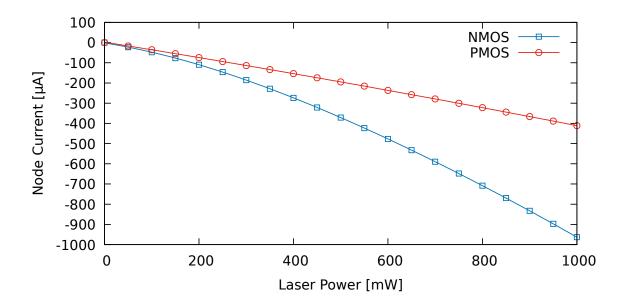

When the described PN-junction models are combined and complemented by the MOS transistor model, the current dependency on the laser power may be obtained for both PMOS and NMOS – see Figure 2.13. The dependency of the laser-induced current on the laser power is analogous to the dependency of the subthreshold leakage on temperature,

Figure 2.12: Parasitic bipolar transistor as modelled in SPICE model [105, 107]. f1 and f2 were fitted according to the measurements by Sarafianos et al. [105, 107]

while the induced current is several orders of magnitude higher – compare Figure 2.13 to Figures 2.7 and 2.5.

Figure 2.13: Optically induced current dependency on the illumination power for a single closed NMOS and PMOS transistors in TSMC180nm (NMOS =  $0.2 \times 2.0 \ \mu m$ , PMOS =  $0.2 \times 4.0 \ \mu m$ )

## 2.3 Digital Circuit Diagnostics

Circuit diagnostics aims at faulty parts detection. A *fault* in a digital circuit is the consequence of a *physical defect* or *environmental effect* causing an unwanted *logic level* behavior possibly leading to *error*: the unintended change of the circuit output or the device state.

We can divide the error-correcting and detecting methods by the impact to the device performance to *online* and *offline* methods. Online methods do not affect the device latency significantly, while offline methods suspend the device.

Tests may deal with faults and/or errors. The offline tests – both manufacturing tests or in-the-field – commonly deal with faults (and output errors). The online tests commonly deal with errors only, as they are conventionally used to identify (and possibly induce a reaction to) errors.

The devices intended for operation in high-risk environments or in critical systems, such as flight control or Anti-lock Brake System (ABS), must be able to deal with errors arising during the device operation. For diagnostics in such systems, different approaches may be used depending on the device's needs. The in-the-field offline test could be performed periodically while the device is not loaded, if it is in the maintenance mode, or temporarily shut down. The other option is to employ the in-the-field *online test*. The online test is performed without the interruption of the device's normal operation, in the background.

The erroneous device output is caused by a fault at the physical level. From this perspective, both offline and online methods can detect fault presence. The main aspects determining the suitability of a given method are *fault coverage*, *error coverage*, *latency*, and area, delay, and power overhead.

In the literature, faults are often categorized according to their duration [70]. The faults, which occur and disappear are denoted as the *transient faults*. When a transient fault disappears, the function of the affected device is fully restored. The faults affecting the device permanently are denoted as *permanent faults*. These are often caused by physical defects [70].

A different fault classification is based on the fault nature. The *stuck-at faults* and *bridging faults* are those caused by a short; *open faults* are caused by a wire interruption and *delay faults* may be caused by transistor ageing, voltage drop, or by process variations (capacity or resistance). A high-energy particle may cause a *single-event-upset* (SEU) or a bit-flip.

## 2.3.1 Physical Defects and Fault Detection

The traditional approach for permanent fault detection in digital circuit diagnostics employs the Automated Test Pattern Generator (ATPG) to generate a huge amount of test vectors used for a complete circuit test [49]. A test vector is used to excite a fault and to propagate the possible fault symptom to the circuit's primary outputs, where it can be observed. If the fault symptom is observed at the circuit's primary output, the fault in the circuit is detected (and partially localized). Such a test is conventionally applied right after device manufacturing before packaging to discover defective parts as soon as possible. The traditional yet widely used digital circuit testing approach is based on *fault simulation* using *fault models*. The fault simulation is a technique employing the fault model to derive the excitation input vector – the *test vector* – and its corresponding output set under the given fault. The test vector job is to excite a fault and propagate the fault symptom to the circuit outputs while ensuring that the fault symptom will be distinguishable.

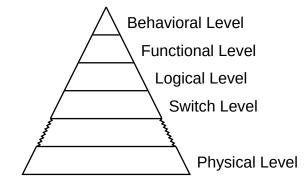

Figure 2.14: Circuit model abstraction level hierarchy

The fault simulation may operate on the several levels of abstraction [13] – see Figure 2.14. The ability to represent a real CMOS *defect* defects differs level-by-level [57, 60].

It has been shown that most defects are – at the *physical level* – caused by bridging faults [45, 76]. It is relatively hard to model bridging faults, thus the time and input invariant *logical level* models are widely used [2]. In both academy [70] and industry [13], the logical level *stuck-at fault* model or the *switch level stuck-open/stuck-on fault* models are widely used.

The mentioned models are preferred due to their simplicity [2, 13]. Both models are conventionally used to model a single fault case. The reason behind considering a single fault only is natural, as if more than a single fault are considered, the simulation, the test time, and mainly the test generation time rise. Here testing becomes impractical and unusable in practice.

Naturally, the test generation process employs methods for making the test set compact. The natural property is that the excitation vector may *cover* multiple modeled (single) faults at the same time. Another method employs fault collapsing: a fault *dominate* over the other fault when the test vectors of the dominating fault are the superset of the test vectors detecting the other fault. The dominant fault is detected by *implication*. These facts lead to the natural reduction of the test length. The test quality metric is the fault coverage expressing the share of modeled faults covered by the test:

$$c_f = \frac{\# \ faults \ detected}{\# \ faults \ modeled} \tag{2.9}$$

A principal problem of the current approaches is that a simplified expectation that only a single fault may occur, may lead to uncovered real circuit defects. The problem is that in reality, more faults might be excited by using a single vector, while their fault symptoms

#### 2. Background and State-of-the-Art

can eliminate each other while propagating to the circuit inputs. Although the single fault models oversimplify the true nature of the faults in today's CMOS processes, it has been shown that if the single stuck-at fault coverage is high, the case where the circuit is marked as fault-free while it is faulty is rare [74] but natural due to model inaccuracy [57].

## 2.3.2 Fault Models

#### Stuck-At-Fault Model

The stuck-at-fault model is a *gate-level* model. It comes from the deep history of digital systems when the main source of faults was the interconnection between logic gates [2]. This model considers two types of permanent faults – permanent logic one (s@1) and permanent logic zero (s@0) at the gate input or output. Today, the stuck-at-fault coverage is still widely used as a metric for the test quality even in industry [13].

It has been shown that the stuck-at-fault model may be used to detect some of the bridging faults [77, 81], and that a high stuck-at-fault coverage implies high bridging fault coverage [74].

### Stuck-Open/Stuck-On Model

A more detailed model is the stuck-open/stuck-on fault model. It is a *transistor-level* model. It considers two types of faults – one corresponds to a permanently open transistor and the second corresponds to a permanently closed transistor. This model may also be defined as an extension of the stuck-at-fault model, where s@1 and s@0 are considered at every transistor gate [2, 18]. Thus, the set of modeled faults includes all faults from the stuck-at-fault, while additional faults are modeled [2].

### **Other Models**

The most commonly used fault model for the bridging faults is the Wired-AND/Wired-OR fault model [2]. A single fault is represented as the AND/OR logic function. As the Wired-AND/Wired-OR fault model [77] does not reflect the behavior of all types of bridging faults, several models reflecting this behavior have been proposed [40, 74].

In [2], the voting model related to the *Byzantine generals problem* for bridging faults has been presented. It is based on the transistor-level comparison of pull-up and pull-down path conductivity.

### **Transient and Intermittent Faults**

For the offline methods, the most problematic faults are those appearing randomly. A fault which occurs and disappears is denoted as the *transient fault* (sometimes called *soft-error*). When a transient fault disappears, the function of the affected device is fully restored. Some authors also distinguish *short-duration transient* and *long-duration transient* faults [99].

An example of a transient fault is a change in a memory cell caused by electromagnetic interference. Sometimes, the transient fault removal may require device reset or re-initialization; correction of a bit-flip in the configuration memory of an FPGA device may require the FPGA reconfiguration [16].

Sometimes, *intermittent faults* are mentioned. The intermittent fault never goes away entirely, but it sometimes affects the system function and sometimes is hidden. The intermittent faults are commonly connected with defects and they often tend to become permanent [70].

#### **Delay Faults**

Some defects do not change the logic function of the circuit but affect its timing. Some of the delay defects are covered by time-invariant models, while many delay faults are not [57, 60].

### 2.3.3 Error Detection And Correction

In applications where *error resilience* is required, some kind of *redundancy* has to be involved to enable in-the-field test. In most cases, the *time* (temporal) or *area* (spatial) redundancy is considered.

The quality metric for error detection and correction method is the error coverage:

$$c_e = \frac{\# \ errors \ detected}{\# \ errors \ occured} \tag{2.10}$$

The full error detection is conditioned by the *self-checking* property. The system is *self-checking* if an occurrence of a fault leads to a faulty output. The important sub-class of the self-checking circuits set are the *Totally Self-Checking* circuits (TSC). The TSC property means that any fault in the circuit may not cause an undetectable faulty output [95]. Thus, any architecture offering full error detection must be TSC to provide full *error coverage*.

The problem with the error coverage is that it is not possible to compute error coverage from the fault coverage (see equation (2.9)), as any fault model is a simplification and it does not reflect all defects and their consequences. It has been shown that if the fault coverage is high and the test passes, the device is most probably not defective [74]. However, using an offline test for error detection or correction is principally limited by the discrepancy between equations (2.9) and (2.10), and thus it cannot be employed in safety-critical systems.

Offline testing can be used to correct errors only if the test has significant and realistic *fault coverage*. If the offline test passes, the output of the device may be correct or not, depending on the test coverage and the fault model accuracy. On the other side, if the test does not pass, it is clear that for the set of input vectors, the device produces an erroneous output (but it can still produce correct outputs for another set of input vectors).

Offline testing can still be employed to detect faults appearing during the device mission. The in-the-field offline test is represented by the *Built-In-Self-Test* (BIST) approach. BIST

#### 2. Background and State-of-the-Art

can be executed during device startup or periodically. BIST is characterized by both spatial and temporal redundancy. The BIST approach is widely used for startup diagnostics.

However, BIST can only be used if the device alternates between operational states and states when it is not loaded: the maintenance mode, or temporarily shut down. If an uninterrupted operation is required, offline testing cannot be used. Additionally, offline testing is proactive; it can be used to identify only long-duration transient or permanent faults before entering the functional mode, not during the computation [70]. Short-duration transient faults are not covered along with hard-to-catch defects [57].

On the other hand, online testing can be used to detect or correct errors reactively during the computation without interruption for a cost of significant area and/or time redundancy.

The redundancy employed by the online test serves to detect or tolerate malfunctions in computational units, storages, or communication channels. Different types of redundancy may be employed, such as information (error detecting and correcting codes), software (N-version programming), *time* (recomputation, offline test), or *area* (concurrent computation in independent units – e.g. N-modular redundancy). Involving any type of redundancy brings additional design, manufacturing, and operating costs [59], thus the balance between costs and benefits has to be targeted. From the hardware point of view, all types of redundancy affect the *time* (latency and throughput) and/or the *area* domain.

From the *physical fault* point of view, the online area redundancy-based methods are well suitable for mitigation of errors caused by both *transient* and *permanent* faults. Computation repetition (i.e., time redundancy) can be efficiently used for mitigating errors caused by *transient* faults.

### 2.3.4 Area Redundancy Overview

A well-adopted approach employing the area redundancy for error detection and correction is the *N*-modular redundancy (NMR). The redundancy of NMR is in the area domain and the error detection (and correction) is performed online, while only a small delay penalty is caused by the voter circuit.

The simplest way to achieve *online error detection* is by duplicating the original module and thus creating the *duplex*. The joint output of two identical modules allows to distinguish a correct (outputs match – both outputs are correct) and an erroneous output (outputs are different – one of the outputs is faulty) in case when at least one of the duplex parts is fault-free, the TSC property holds. Duplex is also the simplest example of a self-checking system.

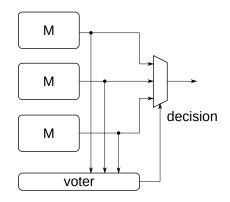

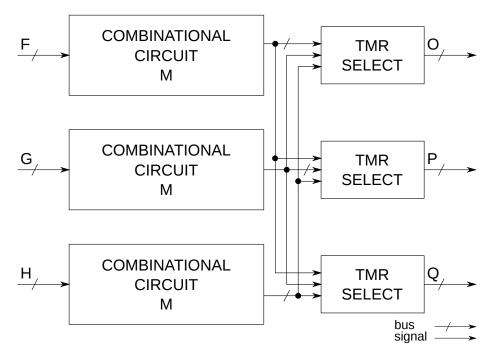

In the NMR family, the online error correction can be achieved by (at least) triplicating the original module. This is called a *Triple modular redundancy* (TMR) – see Figure 2.15. TMR can produce correct output if at least two of three identical modules are fault-free.

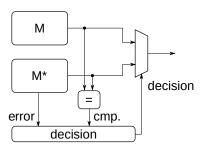

From another point of view, self-checking (error detecting) modules, in general, can be used to construct an error-correcting system – see Figure 2.16. A simple example is the *bi-duplex system*. It is an error-correcting system consisted of two self-checking duplex

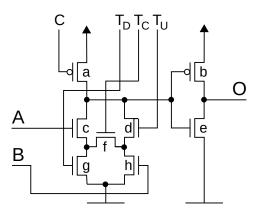

Figure 2.15: Conceptual scheme of an error-correcting TMR

modules [70]. The disadvantage of self-checking circuits is their size. The self-checking circuit size is typically close to the size of the duplex [70, 102].

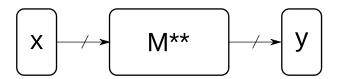

Figure 2.16: Conceptual scheme of an error-correcting duplex system with a self-checking module  $M^*$

The duplex system is not the only example of a self-checking circuit. Self-checking circuits are the subject of deep research in the area of asynchronous circuits [112]. The traditional asynchronous approach is based on *dual-rail* logic [29, 30, 102].

### 2.3.5 Time Redundancy Overview

Time domain methods can be used to eliminate programming errors and transient faults. The *N*-version programming offers immunity to errors caused by developers. Here the code – software or hardware description and test – is developed N-times by different teams. The software can be executed simultaneously in production, while the distinct hardware descriptions and tests are used for verification. It is supposed that the different teams do not make the same mistakes [26]

The straightforward *computation repetition* offers immunity to transient faults (some of them) but it is unable to overcome permanent faults, while specialized techniques employ-

ing coders might also detect permanent faults [86]. If the computation is repeated several times, both error detection and correction may be provided [70].

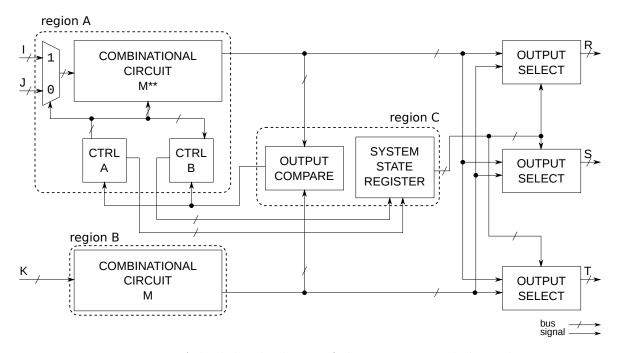

### 2.3.6 Time and Area Redundancy Combinations Overview

The online methods increase the costs (mainly) in the area domain and the offline methods in the time domain. Sometimes, it may be advantageous to combine both approaches. As applying the offline methods disables the system function for some time, it is efficient to use an online method for error detection and when an error is detected, then use an offline method for error correction. Thus, the online error detection is a trigger for the offline error correction.

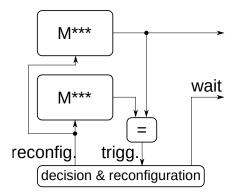

Figure 2.17: Conceptual scheme of an error-correcting duplex employing the reconfigurable modules  $M^{***}$

Works combining time and area redundancy often deal only with transient or *soft faults* like *single-event upsets* (SEU), e.g., [103]. The usability of presented solutions where not only transient faults are considered is problematical due to a delayed fault detection [14, 68]. The following paragraphs contain a list of approaches combining time and area redundancy for error correction.

The approach proposed for handling *bit-flips* in the configuration memory of FPGA devices uses a kind of duplex system to detect errors online and then reconfiguration is performed to repair the faulty parts [16, 43] – see Figure 2.17.

The approach presented in [27] relies on parts, which are not backed up and are considered to be reliable enough, while the unreliable part of the system is reconfigurable and thus allows fault recovery. The system was designed as radiation tolerant, and the approach is efficient for the given application. But this approach deals only with transient faults in the reprogrammable part. Additionally, it is not general and the system contains parts which may be denoted as a single point of failure.

The approach employing backup units may be used for periodical checking of the functional unit. In case of a fault, the functional unit is replaced by a backup unit [14, 68]. The significant disadvantages of this approach are that the fault detection is delayed significantly and that the unit output is not checked in every cycle. Some of the input vectors may disclose present faults but other vectors may produce correct results. Thus, the fault needs not be identified while the incorrect output is produced. This is why the practical usage of this approach is problematic.