# Scalable Vertical GaN FETs (SV- GaN FETs) for Low Voltage Applications

Hongyang Yan and E.M. Sankara Narayanan, Electronic and Electrical Engineering University of Sheffield Sheffield, United Kingdom

#### Abstract

This is the first report on a novel multi-polarization channel applied to realize normally-off and highperformance vertical GaN device devices for low voltage applications. This structure is made with 2DHG introduced to realize the enhancement mode channel instead of p-GaN as in conventional vertical GaN MOSFETs. As the 2DHG depends upon growth conditions, p-type doping activation issues can be overcome. The Mg-doped layer is only used to reduce the short-channel effects, as the 2DHG layer is too thin. Two more 2DEG layers are formed through AlGaN/GaN/AlGaN/GaN polarization structure, which minimizes the on-state resistance. Simulation analysis shows that this proposed structure can provide a large drain current at ~ 500 mA/mm level. The calculation results show this novel vertical GaN MOSFET – termed as SV GaN FET - has the potential of breaking the GaN material limit in the tradeoff between area-specific on-resistance ( $R_{(on,sp)}$ ) and breakdown voltage at low voltages.

Keywords: 2DEG, 2DHG, Low Voltage, Scalable Vertical GaN FETs (SV- GaN FETs)

### **INTRODUCTION**

Due to its capability for higher efficiency, Gallium Nitride (GaN) is widely considered as the next generation pervasive semiconductor that can help address global challenges of climate change, energy security, health, and connectivity. Replacing silicon with GaN has the potential to reduce power loss by 80%, chip size by 90% at 600V and meet the performance/cost parity demanded by Integrated Circuit (IC) industry. Moreover, GaN has great potential to reduce cost because GaN device can be fabricated on epitaxy grown substrate that is larger and less expensive than Silicon Carbide (SiC).

Polarization Super Junction (PSJ) technology has been recently introduced and applied on GaN HEMT devices. It breaks the trade-off between area-specific onresistance  $(R_{(on,sp)})$  and breakdown voltage in lateral formats [1, 2]. However, in most lateral GaN transistors, threshold voltage could not be increased to a high enough level (except through cascode approach) to satisfy the requirement of automotive applications [3]. For highfrequency applications, dynamic on-resistance in lateral GaN devices can degrade device/system efficiency due to increased conduction losses [4]. Besides, most lateral GaN devices are not as area-efficient as vertical GaN transistors since sufficient length between the gate and drain electrodes is necessary to achieve high blocking capability [5]. In vertical GaN MOSFET technology, ptype GaN is usually doped by magnesium (Mg) and the percentage activation of this impurity rarely exceeds 1%. Moreover, the fabrication and performance of high voltage GaN MOSFET structures are dependent on p-GaN doping techniques [6, 7]. To overcome such technical limitations, our innovative idea is to expand the PSJ concept to Scalable Vertical (SV) GaN FETs.

# VERTICAL DEVICE STRUCTURE AND DEVICE SIMULATION

Silvaco TCAD is used for 2D device simulation of SV-GaN FETs. The models adopted for simulating I-V characteristics includes POLAR (spontaneous polarization), CALC.STRAIN (piezoelectric polarization) and FLDMOB (field-dependent mobility).

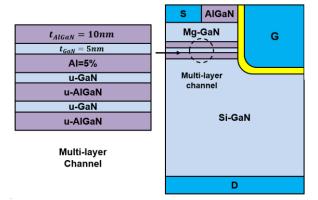

Fig. 1 shows a simplified SV- GaN FET with  $10nm - Al_{0.05}Ga_{0.95}N / 5nm - GaN / 10nm - Al_{0.05}Ga_{0.95}N / 5nm - GaN$  channel. There are two 2DEG layers: the

Fig. 1. Multi polarization channel vertical GaN device cross-section

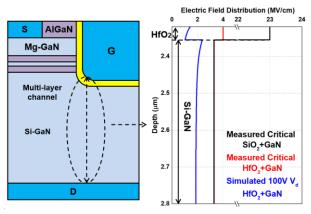

Fig. 2 Gate corner electric field distributions: simulated results vs. measurement material critical electric field [8, 9].

upper layer is connected to the source electrode while bottom 2DEG layer is connected to drain electrode. 2DHG presence in multi-layers is regarded as the channel with the function of realized normally off and controlled threshold voltage. 2DEG and 2DHG sheet carrier density can be controlled by adjusting AlGaN layer thickness and Al mole fraction.

The channel design of multi-layer stacks utilizes a charge compensation concept between the adjacent 2DEG and 2DHG layers to support voltage. The applied voltage is dropped across the stack as well as the Si-doped GaN drift region. BV can be scaled by increasing the number of multi-layer stacks or optimizing the thicknesses of the stacks. In trench gate vertical devices, corner design is an important issue that affects operation reliability. In this work, reported data of measured critical electric field strength of ~ 4MV/cm (23MV/cm) for HfO<sub>2</sub> (SiO<sub>2</sub>) and 3.3MV/cm for Si-GaN is used as the reference values and U-shaped design is considered for the gate geometry to suppress corner effects [8, 9].

Fig. 2 shows that a SV- GaN FET device with  $0.5\mu m$  Si-GaN drift region is simulated at 100V drain voltage, the peak electric field is the only  $2/3^{rd}$  of the reference value. Moreover, other techniques such as p-GaN underneath the gate can further electrically shield the gate corners. As shown in Fig. 3, an Mg-doped GaN region applied

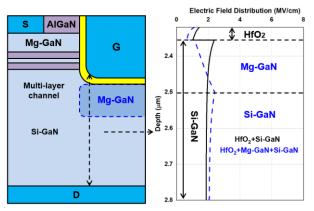

Fig. 3 Gate corner electric field distributions: Si-GaN vs. Mg-GaN+Si-GaN at  $V_d = 100V$ .

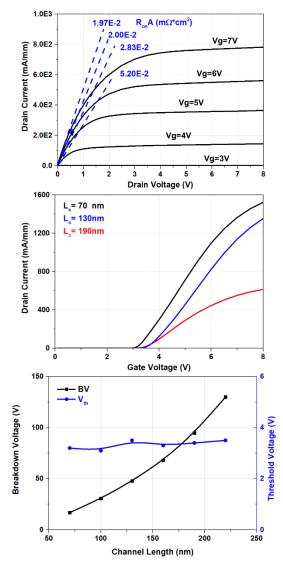

Fig. 4 Simulated (a)  $160\mu m$  channel  $I_d - V_d$  characteristics. (b) Transfer I-V characteristics. (c) Channel length vs BV and  $V_{th}$

beneath the trench gate can further suppress the electric field crowding at the corner of the gate.

Fig. 4(a) shows the  $I_d - V_d$  characteristics as a function of gate voltage. With the increasing number of multipolarization junction stacks, device blocking capability can be improved without any significant increase in  $V_{th}$ , as shown in Fig. 4(c).

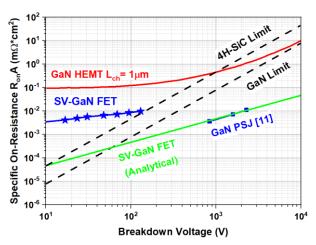

In Fig. 5, for comparison, 4H-SiC and GaN material theoretical limits are demonstrated as well as conventional GaN HEMT with  $1\mu m$  channel length [10]. The calculation results show a performance beyond the material limit by assuming ideal channel mobility of  $1000 \ cm^2/Vs$ . The simulation results for SV-GaN FETs predict significantly superior performance to conventional lateral GaN HEMT, albeit practical carrier mobility is utilized for calibration. Vertical GaN devices based on PSJ concept will be a promising candidate for the next generation of power electronics.

Fig. 5 Area-specific on-resistance vs. Breakdown trend in GaN and SiC; for reference vertical GaN PSJ technology [10] is shown as well as the predicted trend of SV-GaN FET.

### CONCLUSIONS

A novel vertical GaN MOSFET technology, which can be scaled and suitable for low voltage applications, is presented herein. A 100V device can potentially achieve a  $R_{(on,sp)}$  lower than  $10^{-2}m\Omega \cdot cm^2$  as shown in this work. The device can be easily scaled, and the specific on-state resistance can be further optimized with more refined design rules. Based on the results presented, the multi-polarization channel vertical GaN device are predicted to offer immense potential in power electronic systems and high frequency integrated applications.

## REFERENCES

- A. Nakajima, K. Adachi, M. Shimizu, and H. Okumura, "Improvement of unipolar power device performance using a polarization junction," *Applied Physics Letters*, vol. 89, no. 19, 2006, doi: 10.1063/1.2372758.

- [2] A. Nakajima, Y. Sumida, M. H. Dhyani, H. Kawai, and E. M. Narayanan, "GaN-Based Super Heterojunction Field Effect Transistors Using the Polarization Junction Concept," *IEEE Electron Device Letters*, vol. 32, no. 4, pp. 542-544, 2011, doi: 10.1109/led.2011.2105242.

- [3] T. Kachi, "GaN power device for automotive applications," presented at the 2014 Asia-Pacific Microwave Conference.

- [4] K. Matocha and R. J. Gutmann, "High-voltage normally off GaN MOSFETs on sapphire substrates," *IEEE Transactions on Electron Devices*, vol. 52, no. 1, pp. 6-10, 2005, doi: 10.1109/ted.2004.841355.

- [5] T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, "Vertical GaNbased trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV," *Applied Physics Express*, vol. 7, no. 2, 2014, doi: 10.7567/apex.7.021002.

- [6] B. Paszkiewicz et al., "Study of the activation process of Mg dopant in GaN:Mg layers," physica status solidi (c), vol. 3, no. 3, pp. 579-584, 2006, doi: 10.1002/pssc.200564121.

- [7] U. Kaufmann, P. Schlotter, H. Obloh, K. Kohler, and M. Maier, "Hole conductivity and compensation in epitaxial GaN : Mg layers," (in English), *Phys Rev B*, vol. 62, no. 16,

pp. 10867-10872, Oct 15 2000, doi: DOI 10.1103/PhysRevB.62.10867.

- [8] C. Sire, S. Blonkowski, M. J. Gordon, and T. Baron, "Statistics of electrical breakdown field in HfO2 and SiO2 films from millimeter to nanometer length scales," *Applied Physics Letters*, vol. 91, no. 24, 2007, doi: 10.1063/1.2822420.

- [9] I. C. Kizilyalli, A. P. Edwards, H. Nie, D. Disney, and D. Bour, "High Voltage Vertical GaN p-n Diodes With Avalanche Capability," *IEEE Transactions on Electron Devices*, vol. 60, no. 10, pp. 3067-3070, 2013, doi: 10.1109/ted.2013.2266664.

- [10] V. Unni and E. M. S. Narayanan, "Breaking the GaN material limits with nanoscale vertical polarisation super junction structures: A simulation analysis," *Japanese Journal of Applied Physics*, vol. 56, no. 4S, 2017, doi: 10.7567/jjap.56.04cg02.

Addresses of the authors

Hongyang Yan, Broad Lane Street, Sheffield, United Kingdom, hyan8@sheffield.ac.uk

E.M. Sankara Narayanan, Sir Frederick Mappin Building, Sheffield, United Kingdom, s.madathil@sheffield.ac.uk