### Assignment of master's thesis

| Title:                   | Robust flash memory bootloader for a microcontroller over near field |  |

|--------------------------|----------------------------------------------------------------------|--|

|                          | communication                                                        |  |

| Student:                 | Bc. Jitka Seménková                                                  |  |

| Supervisor:              | Ing. Jiří Hušák                                                      |  |

| Study program:           | Informatics                                                          |  |

| Branch / specialization: | Design and Programming of Embedded Systems                           |  |

| Department:              | Department of Digital Design                                         |  |

| Validity:                | until the end of summer semester 2022/2023                           |  |

#### Instructions

Develop a robust flash memory bootloader for a proprietary RISC-V based microcontroller, which will allow the update of the internal flash memory over near field communication (NFC) on the fly.

Implementation:

- Get familiar with all needed technologies.

- Develop nonvolatile flash low-level firmware driver or use an existing one.

- Design and develop all necessary communication layers in the firmware and the bootloader which uses this communication stack.

- Develop an application for one of the mobile platforms (iOS or Android), which can be used to test and benchmark the whole solution.

- Document completely the results in terms of bootloader footprint, transfer time and power consumption.

The final solution must be able to recover from all possible use cases (loss of power, out of range...).

The design choices made in this thesis should support robustness, security, speed of communication and usability in large scale production inside a size constraint of a wearable device design.

Electronically approved by doc. Ing. Hana Kubátová, CSc. on 22 February 2021 in Prague.

Master's thesis

### Robust flash memory bootloader for a microcontroller over near field communication

Bc. Jitka Seménková

Department of Digital Design Supervisor: Ing. Jiří Hušák

June 27, 2021

# Acknowledgements

I would like to thank my supervisor Ing. Jiří Hušák for his valuable advice, comments and help during the whole process of writing this thesis. Also, I would like to thank the team members for introducing me to the project and for their code reviews. Furthermore, I would like to thank my family for their support. Finally, I would like to thank the correctors of this thesis, especially Bc. Martina Klimešová.

## Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. I further declare that I have concluded an agreement with the Czech Technical University in Prague, on the basis of which the Czech Technical University in Prague has waived its right to conclude a license agreement on the utilization of this thesis as a school work under the provisions of Article 60 (1) of the Act. This fact shall not affect the provisions of Article 47b of the Act No. 111/1998 Coll., the Higher Education Act, as amended.

In Prague on June 27, 2021

. . . . . . . . . . . . . . . . . . .

Czech Technical University in Prague Faculty of Information Technology © 2021 Jitka Seménková. All rights reserved. This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the

Copyright Act).

#### Citation of this thesis

Seménková, Jitka. *Robust flash memory bootloader for a microcontroller over near field communication*. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2021.

# Abstrakt

Tato práce obsahuje návrh a implementaci zavaděče flash paměti pro mikrokontroler s architekturou RISC-V. Zavaděč přenáší novou aplikaci přes rozhraní NFC, tvořené deskou NTAG5 link. Součástí práce je i návrh a implementace komunikace přes dané rozhraní. Vytvořený zavaděč je optimalizován na velikost a je navržen tak, aby byl robustní. V rámci práce vznikla i aplikace pro Android pro otestování zavaděče.

Klíčová slova Zavaděč, Flash paměť, NFC, RISC-V

## Abstract

This thesis includes the design and implementation of a flash memory bootloader for a RISC-V microcontroller. Communication is done over the NFC board NTAG5 link. Design and implementation of the communication are also present in this thesis. The created bootloader is robust, and its memory footprint is small. As a part of this thesis, an Android application was created to test the bootloader.

Keywords Bootloader, Flash memory, NFC, RISC-V

# Contents

| In       | trod | uction |                        | 1                                                                                                        |

|----------|------|--------|------------------------|----------------------------------------------------------------------------------------------------------|

| 1        | Ana  | alysis |                        | 3                                                                                                        |

|          | 1.1  | Techn  | ologies and            | d principles                                                                                             |

|          |      | 1.1.1  | Bootload               | ler                                                                                                      |

|          |      |        | 1.1.1.1                | Bootloader stages                                                                                        |

|          |      |        | 1.1.1.2                | Memory layout                                                                                            |

|          |      |        | 1.1.1.3                | Communication interface                                                                                  |

|          |      | 1.1.2  | NFC                    |                                                                                                          |

|          |      |        | 1.1.2.1                | Tag 5 type                                                                                               |

|          |      | 1.1.3  | I <sup>2</sup> C brief | summary                                                                                                  |

|          | 1.2  | Given  | Hardware               |                                                                                                          |

|          |      | 1.2.1  | NTAG5 1                | link                                                                                                     |

|          |      |        | 1.2.1.1                | NFC interface 11                                                                                         |

|          |      |        | 1.2.1.2                | $I^2C$ interface                                                                                         |

|          |      |        | 1.2.1.3                | NTAG5 configuration                                                                                      |

|          |      |        | 1.2.1.4                | Event detection pin                                                                                      |

|          |      |        | 1.2.1.5                | NTAG5 link communication modes 14                                                                        |

|          |      |        | 1.2.1.6                | Example applications                                                                                     |

|          |      | 1.2.2  | Target p               | rocessor $\ldots \ldots 16$ |

|          |      |        | 1.2.2.1                | RISC-V ISA 17                                                                                            |

|          |      |        | 1.2.2.2                | Flash memory 17                                                                                          |

|          |      |        | 1.2.2.3                | Flash driver                                                                                             |

|          |      |        | 1.2.2.4                | $I^2C$ driver                                                                                            |

|          |      |        | 1.2.2.5                | Interrupts                                                                                               |

| <b>2</b> | Des  | sign   |                        | 21                                                                                                       |

| -        | 2.1  | Bootle | oader                  |                                                                                                          |

|          |      | 2.1.1  |                        | nciple                                                                                                   |

|   |            | 2.1.2          | Program flow                                                                                                                             |

|---|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | 2.1.3          | Flash memory layout and interrupt vector tables 22                                                                                       |

|   |            | 2.1.4          | Bootloader operation scheme                                                                                                              |

|   | 2.2        | Comm           | nunication stack $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 24$                                              |

|   |            | 2.2.1          | Communication channel                                                                                                                    |

|   |            |                | 2.2.1.1 NTAG5 mode selection                                                                                                             |

|   |            |                | 2.2.1.2 NTAG5 SRAM usage                                                                                                                 |

|   |            | 2.2.2          | Messaging system                                                                                                                         |

|   | 2.3        |                | $\begin{array}{c} \text{pperation scheme} & \dots & $                    |

|   | 2.3<br>2.4 |                | pader communication                                                                                                                      |

|   | 2.1        | Dootic         |                                                                                                                                          |

| 3 | Imp        | lemen          | tation 37                                                                                                                                |

|   | 3.1        |                | are modules                                                                                                                              |

|   |            | 3.1.1          | NTAG5 controller                                                                                                                         |

|   |            |                | 3.1.1.1 Interface                                                                                                                        |

|   |            |                | 3.1.1.2 Internal functions                                                                                                               |

|   |            |                | 3.1.1.3 Event detection and callbacks                                                                                                    |

|   |            | 3.1.2          | NFC TLV interface                                                                                                                        |

|   |            | 0              | 3.1.2.1 Interface                                                                                                                        |

|   |            | 3.1.3          | Bootloader                                                                                                                               |

|   |            | 0.1.0          | 3.1.3.1 Bootloader manager                                                                                                               |

|   |            |                | 3.1.3.2 Bootloader DFU - controller                                                                                                      |

|   |            | 3.1.4          | Bootloader DFU - flash operations                                                                                                        |

|   |            | 0.1.4          | 3.1.4.1 Interface                                                                                                                        |

|   |            |                | 3.1.4.2 Internal functionality                                                                                                           |

|   | 3.2        | Mobile         |                                                                                                                                          |

|   | 0.2        | 3.2.1          | UI and functionality behind it                                                                                                           |

|   |            | 3.2.1<br>3.2.2 | Logging and testing                                                                                                                      |

|   | 3.3        |                | ple user application $\ldots \ldots 52$                                   |

|   | 3.3        |                | $\frac{1}{2}$                                                                                                                            |

|   | 0.4        | 3.4.1          |                                                                                                                                          |

|   |            | -              | 1                                                                                                                                        |

|   |            | 3.4.2          |                                                                                                                                          |

|   |            | 3.4.3          | Desynchronization of devices during DFU                                                                                                  |

|   | 9 5        | 3.4.4          | Low battery $\ldots \ldots 53$                                     |

|   | 3.5        |                | $e \text{ extensions} \dots \dots$ |

|   |            | 3.5.1          | Adaptation to specific project                                                                                                           |

|   |            | 3.5.2          | Security suggestions                                                                                                                     |

|   |            | 3.5.3          | Transfer from emulator                                                                                                                   |

| 4 | Tog        | ting           | 57                                                                                                                                       |

| Ŧ | 4.1        | 0              | opment and testing environment                                                                                                           |

|   | 4.2        |                | ionality testing                                                                                                                         |

|   | 4.2<br>4.3 |                | analysis $\ldots$ $\ldots$ $58$                                                                                                          |

|   | 4.0        | 4.3.1          |                                                                                                                                          |

|   |            | 7.J.I          |                                                                                                                                          |

|              | 4.3.2 Transition time of one data chunk | 59 |

|--------------|-----------------------------------------|----|

|              | 4.3.3 Others                            | 60 |

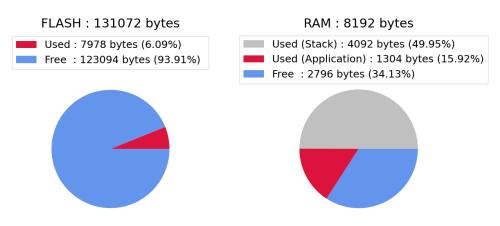

|              | .4 Memory analysis                      | 60 |

| Co           | clusion                                 | 63 |

| Bi           | liography                               | 65 |

| $\mathbf{A}$ | NTAG5 - Pass-through mode               | 69 |

| в            | Acronyms                                | 73 |

| $\mathbf{C}$ | Contents of enclosed CD                 | 75 |

# **List of Figures**

| 1.1               | Scheme of communication                                                           | 3               |

|-------------------|-----------------------------------------------------------------------------------|-----------------|

| 1.2               | Architecture of the flash bootloader                                              | 5               |

| 1.3               | Concept of boot manager                                                           | 5               |

| 1.4               | Concept of boot manager                                                           | 6               |

| 1.5               | NFC tag types                                                                     | 9               |

| 1.6               | $I^2C$ address frame structure                                                    | 10              |

| 1.7               | $I^2C$ example transaction                                                        | 10              |

| 1.8               | NTAG 5 link development board OM2NTP5332                                          | 11              |

| 1.9               | NTAG5 link - $I^2C$ memory commands $\ldots \ldots \ldots \ldots \ldots \ldots$   | 13              |

| 1.10              | NTAG5 link - $I^2C$ register commands $\ldots \ldots \ldots \ldots \ldots \ldots$ | 14              |

| 1.11              | Flash memory scheme of target processor                                           | 18              |

| 2.1               | Flash memory layout                                                               | 23              |

| $\frac{2.1}{2.2}$ | Bootloader operation scheme                                                       | $\frac{23}{25}$ |

| $\frac{2.2}{2.3}$ | User application operation scheme from bootloader point of view .                 | $\frac{25}{25}$ |

| 2.3<br>2.4        | Scheme of communication channel between mobile and target pro-                    | 20              |

| 2.4               | cessor                                                                            | 26              |

| 2.5               | Diagram of usage of NTAG5 link SRAM memory                                        | 20<br>28        |

| $\frac{2.5}{2.6}$ | Structure of TLV messages                                                         | 20<br>29        |

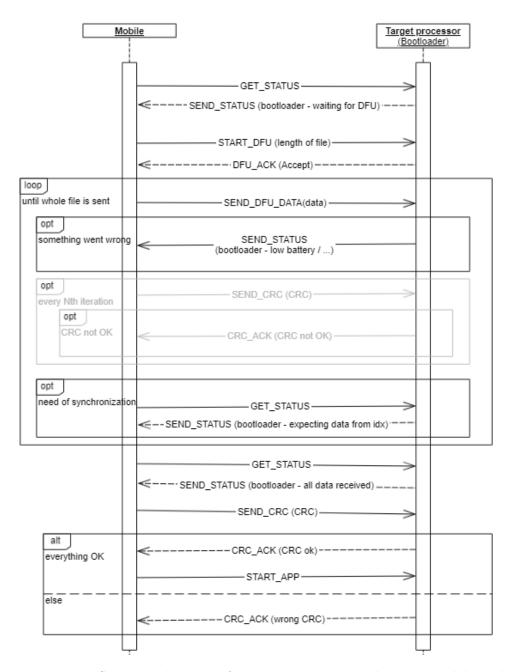

| 2.0<br>2.7        | DFU operation scheme                                                              | $\frac{29}{31}$ |

| 2.1<br>2.8        | Data manipulation for time analysis                                               | 32              |

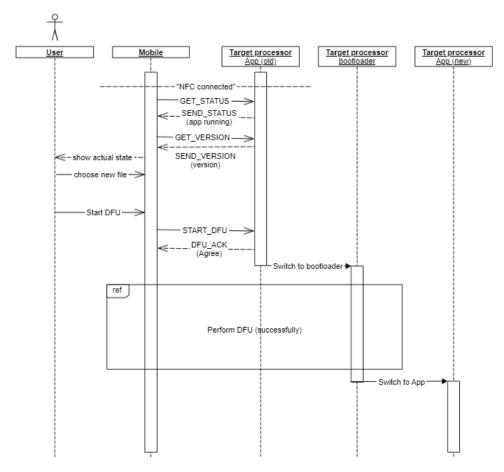

| 2.0<br>2.9        | Sequence diagram of communication between mobile and target                       | 02              |

| 2.0               | processor for bootloader purposes                                                 | 34              |

| 2.10              |                                                                                   | 01              |

| 2.10              | get processor                                                                     | 36              |

|                   | See Proceeder                                                                     | 00              |

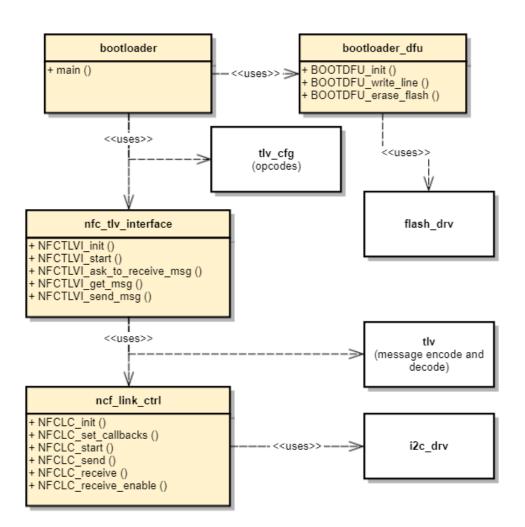

| 3.1               | Bootloader modules architecture                                                   | 38              |

| 3.2               | Class UML of nfc_link_ctrl module                                                 | 39              |

| 3.3               | Class UML of nfc_tlv_interface module                                             | 42              |

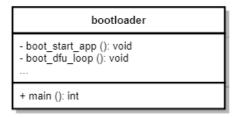

| 3.4               | Class UML of bootloader module                                                    | 42              |

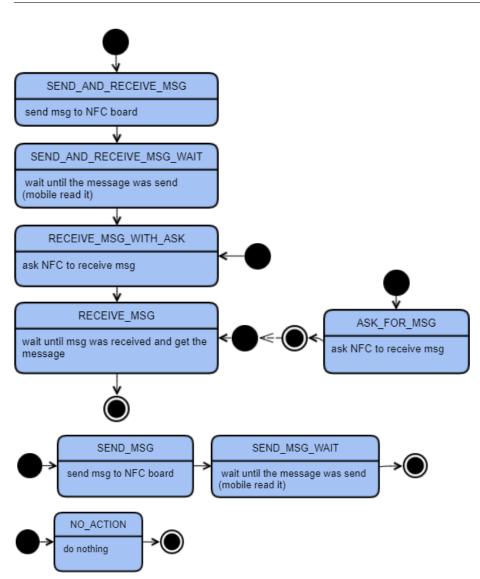

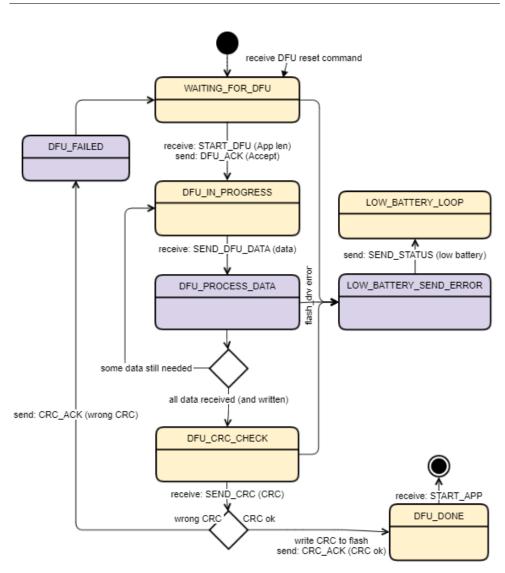

| 3.5 | Communication controller - actions                                                             | 46 |

|-----|------------------------------------------------------------------------------------------------|----|

| 3.6 | DFU controller diagram                                                                         | 47 |

| 3.7 | Class UML of bootloader_dfu module                                                             | 48 |

| 3.8 | Mobile application UI                                                                          | 51 |

| 3.9 | Example of testing output in log                                                               | 51 |

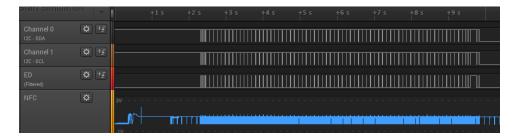

| 4.1 | DFU recording from a Saleae                                                                    | 58 |

| 4.2 | Record of transferring 248 B over NFC with Samsung Galaxy A10                                  | 59 |

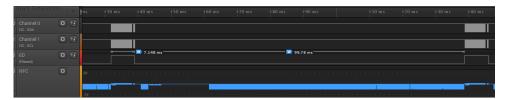

| 4.3 | Record of transferring 248 B over NFC with Samsung Galaxy A10<br>- zoom with time measurements | 59 |

| 4.4 | Record of transferring 248 B over NFC with Samsung A21s - zoom                                 |    |

|     | with time measurements                                                                         | 60 |

| 4.5 | Memory consumption of bootloader                                                               | 61 |

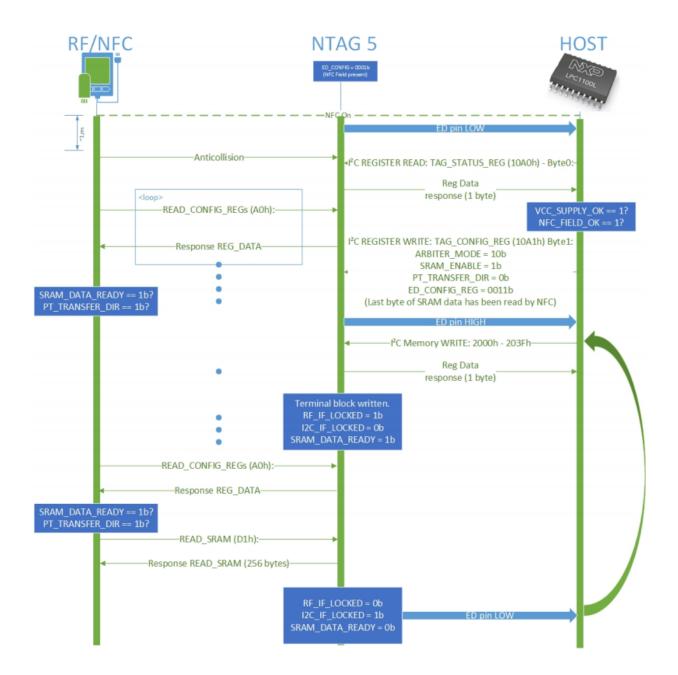

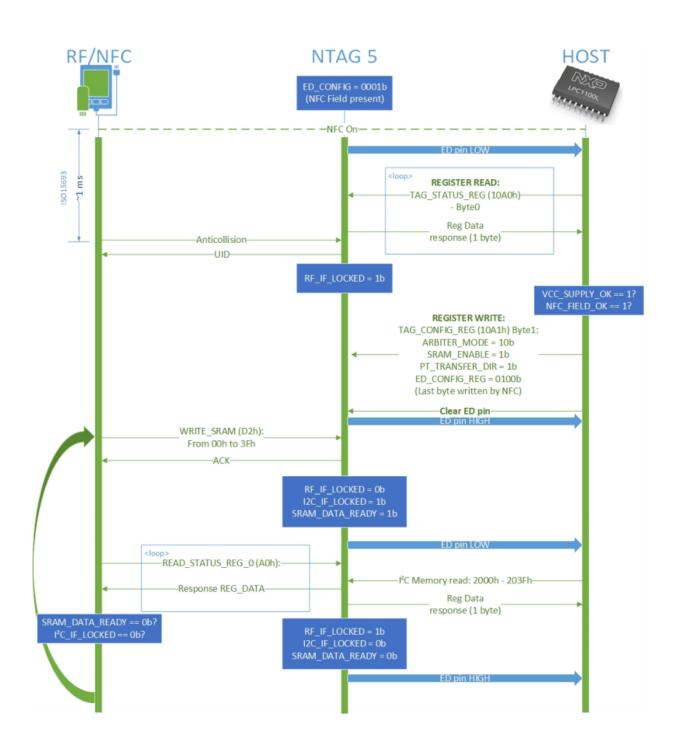

| A.1 | Example usage of NTAG5's Pass-through mode (direction from $I^2C$                              |    |

|     | to NFC)                                                                                        | 70 |

| A.2 | Memory consumption of bootloader                                                               | 71 |

# List of Tables

| 1.1 | NTAG5 link parameters                                                  | 11 |

|-----|------------------------------------------------------------------------|----|

| 1.2 | NTAG5 NFC commands                                                     | 12 |

| 1.3 | NTAG5 event detection pin configurations                               | 15 |

| 1.4 | Target processor parameters                                            | 17 |

| 1.5 | Maximal times of flash memory operations on the target processor       | 18 |

|     |                                                                        |    |

| 2.1 | Initial NFC write SRAM speed testing with Samsung A21S                 | 28 |

| 2.2 | Times of operation needed for time analysis                            | 31 |

| 2.3 | Command set for bootloader communication $\ldots \ldots \ldots \ldots$ | 33 |

|     |                                                                        |    |

| 4.1 | DFU times for a 120kB user application                                 | 59 |

| 4.2 | Times of intervals in NFC communication                                | 60 |

| 4.3 | Times of flash memory operations                                       | 60 |

| 4.4 | Flash memory footprint of modules in bootloader                        | 61 |

## Introduction

In recent years, the popularity of personal electronics, including wearable devices, has been rising. Many people wear a smartwatch as an extension of their smartphone. Smartwatch shows them notifications and can track their daily activities. There are many brands and models to choose from and the manufacturers need to make an effort to engage customers. The customers are considering multiple factors such as features of the device, compatibility with their other devices, and the length of battery life on one charge is also one of the main parameters they focus on because they do not want to charge the device every day.

The devices need to be updated from time to time to add new features or fix bugs. This is where a bootloader comes into play because it is a part of the device's code, enabling it to be updated on the fly. The bootloader needs to be robust so the devices do not get bricked. The bootloader's footprint also needs to be small, so it leaves as much space as possible to the user application, so there can be plenty of features the customers care about.

The assignment of this thesis comes from a real company, which wants to stay anonymous. The result of this thesis is going to be used in a real device in the future.

The applicability in real life and the opportunity to work on something new are the reasons why I chose this assignment.

The goal of this thesis is to create a robust flash memory bootloader for a proprietary RISC-V microcontroller over NFC, with the usage of NTAG5 link board. The aim is to have a robust solution with a small memory footprint and power consumption.

The thesis consists of 4 chapters. The first chapter includes a summary of all used technologies and a description of the target hardware. The second chapter describes the design of the communication stack and the bootloader. The third chapter describes the implementation of the bootloader and the example mobile phone application. The fourth chapter includes the testing results and their analysis.

## CHAPTER \_

# Analysis

This chapter consists of two parts. In the first one, I cover the principle of bootloader and I go through all the technologies that are used in this thesis. In the second part, I describe the hardware for which the implementation will be done.

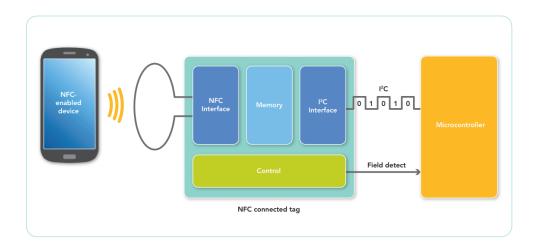

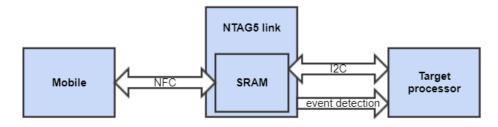

The company specified the assignment and requested for the NFC communication to be done over NTAG5 link board. It is a NFC tag, that can be connected to a microcontroller over  $I^2C$  bus. The mobile phone communicates with the tag over NFC. The microcontroller and mobile phone can exchange data via memory of the NTAG5 link. Figure 1.1 shows the scheme of communication over an NFC tag, like NTAG5 link.

Figure 1.1: Scheme of communication [1]

#### 1.1 Technologies and principles

#### 1.1.1 Bootloader

The term bootloader can have different meanings in different contexts. In this work, bootloader is a part of code that is run on power-up of a microcontroller unit (MCU). It is able to reprogram user application and run it without an external programmer. This is very important in the embedded software, because it enables the user to update the firmware on the fly, which is needed in products, where the application is meant to be updated, fixed or expanded even after the product is in possession of a customer. However, it is also useful for developers because they do not need to use the external programmer at all times and they can test the application in a real environment. Therefore it is usually one of the first things implemented in a project.

#### 1.1.1.1 Bootloader stages

A bootloader is an independent part of code that is run on reset of the controller. Its functionality can be summarized into the following steps:

- 1. Initialize the environment

- 2. Check state of the user application

- 3. Flash new application if needed

- 4. Run the application

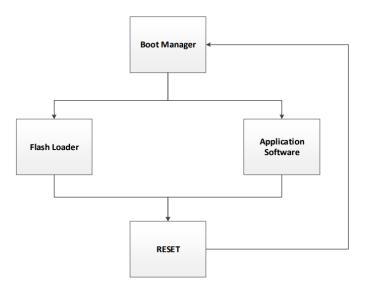

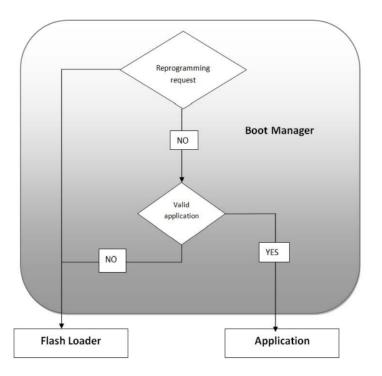

Sometimes the process is theoretically divided into two stages – boot stage (boot manager), which includes steps 1, 2, 4 and load stage (flash loader), which corresponds to step 3. [2, 3, 4]

Possible operation scheme of a bootloader is displayed in figure 1.2 and boot manager internal scheme is in figure 1.3.

The initialization step includes initialization of stack and registers, setup of interrupt vector table, move of selected code section to RAM, setup of watchdogs and clock and initialization of HW drivers. This is partly done in startup code and partly in the actual bootloader code. [5]

After initialization, the bootloader checks if the user application can be run or device firmware update (DFU) needs to be performed. This usually consists of checking if there is a valid application in memory (e.g. CRC check) and if there was a request for an update. [4]

The actual update can be performed in multiple ways based on the options present in a specific circuit. There are two most common options. First consists of preloading a whole new application to external memory or part of internal memory, which is free. The application can be in form of a binary file or a more complex structure that needs to be unpacked or decrypted.

Figure 1.2: Architecture of the flash bootloader[4]

Figure 1.3: Boot manager concept [4] (flowchart starts from the top condition - Reprogramming request)

Finally, the application is copied to the final place at one go, from where it can be run. The second option is to receive the application part by part and store it in the final place continuously. The first option enables to receive and check the new application before the old one is deleted, so if the transfer of the new application fails, the old one can still run. The second option is required if the memory is too small to store both applications at the same time. [2, 6] There are also special techniques like using only an update file instead of downloading the whole application [7].

The steps, before the application is started, depend on the state in which the application expects the processor to be. If the application has a separate start-up code and it initializes everything by itself, the bootloader needs to deinitialize everything it initialized before starting the app. If the application expects everything to be prepared beforehand, the bootloader needs to take care of that. The bootloader will most probably need to take care of the change of the interrupt vector table in both cases, because switch to application is frequently done by jumping to its reset handler [5].

#### 1.1.1.2 Memory layout

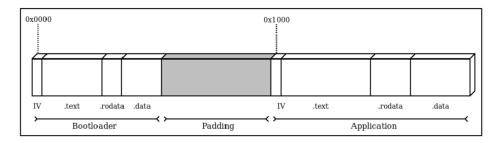

The bootloader is usually located in a different part of memory than the user application, so it can be write protected in the re-programming process. This is important because if the bootloader was overwritten by mistake, the device would get bricked. The bootloader needs to be put to place in memory, so it is automatically run after reset. This location is processor specific and it is mostly defined by the default address of the interrupt vector table (IVT) after reset. Its default address is most frequently at the beginning of the memory. Example, how the memory can look, if the default position is set to the beginning of the memory, is displayed in figure 1.4.

Figure 1.4: Boot manager concept [5] (IV refers to IVT here)

The bootloader, that is stored in flash and also writes the new application to flash, in most cases needs to be at least partly relocated from flash to RAM, because processors mostly do not allow to read flash while erase or write operations are ongoing. Behavior, what happens if a user tries it, depends on a specific processor.

Next important thing is the management of interrupt vector tables. If it is possible for the specific processor to set the location of the IVT on run-time, it is convenient to have separate vector tables for the bootloader and for the application. If it is not possible, special arrangements need to be implemented. Solution for this single vector table design is presented in article [8]. Also if there is a need to use interrupts in the part of bootloader, that needs to be relocated to RAM, the vector table and handlers also need to be put there. Otherwise the interrupts need to be disabled in this part of code.

#### 1.1.1.3 Communication interface

During the load stage, there is no standard way, how to transfer the code of the new application. Bootloader can use any interface present in the device. The firmware update is divided into two types based on the type of the used interface [9]:

- OTW (over-the-wire)

- OTA (over-the-air)

Even though both options are widely used, the OTA is more discussed recently as the fields that use it are expanding. One of its main advantages is the possibility of an easy reprogramming of boards that are difficult to access. This can be the case for lots of sensors and other parts of smart homes or IoT in general or systems supporting agriculture or in automotive. Another advantage is the lack of need for any connector, which may be needed for some water-resistant designs or it is just used to reduce costs. The OTA option can also be used to update multiple nodes at once. Lately, it is frequently connected to the automotive industry. [10]

#### 1.1.2 NFC

Near-field communication (NFC) technology enables wireless half-duplex data exchange between two NFC-enabled devices in close proximity (around 4 cm and less). The communication uses radio waves and it operates on 13.56 MHz. It was developed by Philips (from which NXP Semiconductors spun-off) and Sony in 2002 and it was built on RFID and smart card technology. The companies together with Nokia founded NFC Forum in 2004. Since then, the NFC Forum promotes usage and covers the standardization of the NFC to ensure compatibility of the devices. Its standards are built on ISO standards. [11, 12]

In NFC communication there are two types of devices based on their actions with the RF field:

- active device can generate RF field (NFC readers, smartphones)

- passive device only modulates RF field that it is in (NFC tags)

Active devices always have their own power supply. Passive devices can be powered from the RF field of the active device if the device is small and the field is strong and stable enough (this action is called energy harvesting). [11, 13]

There are two positions in which a device can be in the NFC communication based on who starts the communication. The device that initiates and directs the NFC communication is called initiator. The second device, that answers to this communication, is called target. Initiator always has to be an active device. The target device can be either passive or active. [11]

There are 3 defined NFC communication operating modes [11, 12]:

- reader/writer used for reading and writing data to NFC tags by mobile phones or NFC readers

- peer to peer used for data exchange between two mobile phones

- card emulation mobile phone emulates a smart card while communicating with a NFC reader

NFC tags can be either standalone devices, where they can store a small amount of data in the form of an NFC data exchange format (NDEF) messages, which is transmitted to the active device on tapping mobile on the tag. Or the tag can be connected to an IC and be used as an NFC interface, for communication with active devices. [13]

To this day, there are 5 different types of tag specifications released by NFC Forum. The names are "Type X Tag", where X goes from 1 to 5. Where the 5th one is the youngest, released in 2015. Basic info about each type is in table showed in figure 1.5. The values for memory size and data rates are only informative, and real values depend on a specific device.

Further in this thesis I will pursue only type 5, because it is the type of my target device.

#### 1.1.2.1 Tag 5 type

The tag 5 type is based on ISO/IEC 15693, which was originally developed for vicinity cards. Both specifications (ISO/IEC 15693 and tag 5 type) are available only after purchase.

The standards, among other things, specify commands, that the device must and can support. For example, it includes commands for controlling and manipulation with tag's memory. More information about the commands is included in section 1.2.1.1, which also discusses specific commands supported by the tag, which is used in this thesis.

Communication based on these standards have an integrated CRC. It uses CRC16 to secure every single command.

Mobile phone operating systems have an included support for NFC to be used in the applications. In Android, it is possible to use the Android Java

| Property       | Type 1                        | Туре 2                        | Type 3                                  | Туре 4                                                  | Type 5                        |

|----------------|-------------------------------|-------------------------------|-----------------------------------------|---------------------------------------------------------|-------------------------------|

| Standard       | ISO/IEC 14443A                | ISO/IEC 14443A                | ISO/IEC 18092<br>JIS X 6319-4<br>FELICA | ISO/IEC 14443A<br>ISO/IEC 14443B                        | ISO/IEC 15693                 |

| Memory         | 96 bytes to<br>2 Kbytes       | 48 bytes to<br>2 Kbytes       | 2 Kbytes                                | 32 Kbytes                                               | 64 Kbytes                     |

| Data rate      | 106 kbit/s                    | 106 kbit/s                    | 212 kbit/s,<br>424 kbit/s               | 106 kbit/s,<br>212 kbit/s,<br>424 kbit/s                | 26.48 kbit/s                  |

| Capability     | Read<br>Re-write<br>Read-only | Read<br>Re-write<br>Read-only | Read<br>Re-write<br>Read-only           | Read<br>Re-write<br>Read-only<br>Factory-<br>configured | Read<br>Re-write<br>Read-only |

| Anti-collision | No                            | Yes                           | Yes                                     | Yes                                                     | Yes                           |

| Notes          | Simple, cost<br>effective     | -                             | Higher cost,<br>complex<br>applications | -                                                       | Vicinity area                 |

Figure 1.5: NFC tag types [13]

package android.nfc. It includes NfcV class, which provides functionality for communication with type 5 tags. Android activity can be notified when a tag is detected, so it can start the communication with it. NfcV automatically adds CRC to every message, so no action from the user is needed. Also if a message is received and the CRC is not correct, it raises an exception. [14]

#### 1.1.3 I<sup>2</sup>C brief summary

$I^2C$  is a 2-wire bus. It operates on master-slave principle. By default, it can always be multi-slave and if extra logic is added to masters, it can also be multi-master. Neither option requires adding additional wires like it is for SPI. Both wires are usually connected to pull-ups and nodes operate them by pulling them down via an open-drain output. One wire is used for clock transfer and is operated by the master. The second wire is used for transferring data in both directions. Synchronization is done by using start and stop conditions, which mark the start and the end of one transaction and they are generated by the master. The bus can operate at data rates up to 100 kbit/s (Standard-mode), 400 kbit/s (Fast-mode), 1 Mbit/s (Fast-mode Plus), or 3.4 Mbit/s (High-speed mode). [5, 15]

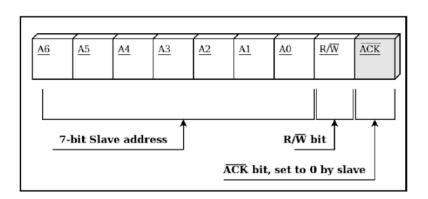

Each transaction starts with an address frame, which most frequently consists of 7 bit slave address (there is also a 10 bit version) and 1 bit mode select (1 for read, 0 for write mode). Slave with given address acknowledges the frame by pulling the data wire down. [5] Structure of the address frame is displayed in figure 1.6.

Figure 1.6:  $I^2C$  address frame structure [5]

The rest of the transaction consists of data frames. The direction of the transfer depends on the mode selected in the address frame. In read mode, the data is sent from slave to master – slave puts data on the bus and master acknowledges them. In write mode, the data is sent from master to slave – master puts data on the bus and slave acknowledges them. [5]

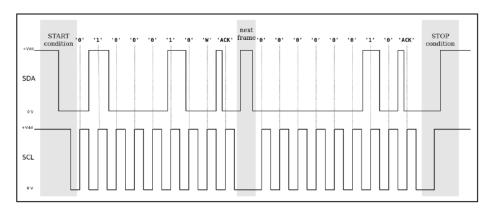

Figure 1.7 includes example of one bus transaction, that sends 1 byte of data from master to slave.

Figure 1.7: Example of  $I^2C$  transaction [5]

#### 1.2 Given Hardware

In this section, I will describe hardware (HW) for which the program will be developed. First, I will write about NTAG5 link board, which is a NFC tag and then I will describe the target processor, including already implemented modules I will use.

#### 1.2.1 NTAG5 link

Board NTAG5 link OM2NTP5332 is a development kit made by NXP Semiconductors, for designing systems with NFC interface. Image of the board can be seen in figure 1.8. The NFC included is of tag type 5 and is based on ISO/IEC 15693 specification. The board offers multiple wired connection possibilities:  $I^2C$ , PWM, GPIO. I will only discuss  $I^2C$  interface further in this thesis. [16, 17]

Figure 1.8: NTAG 5 link development board OM2NTP5332 [17]

Table 1.1 includes basic parameters of NTAG5 link.

| Parameter               | Value               |

|-------------------------|---------------------|

| NFC Tag Type            | 5                   |

| SRAM memory size        | 256 B               |

| EEPROM memory size      | 2 KB                |

| Maximal interface speed | $53 \mathrm{~kbps}$ |

| Supply voltage          | 1.8-5.5 V           |

Table 1.1: NTAG5 link parameters [16]

#### 1.2.1.1 NFC interface

The NFC interface of NTAG5 link is based on ISO/IEC 15693 and Type 5 Tag norms. It can communicate in close proximity with common NFC-enabled active devices and powerful industrial readers can reach it from a range up to 60 cm. [18]

The base of command set of NTAG5 link is built on mandatory and optional commands defined in ISO/IEC 15693 and Type 5 Tag specifications. On top of that NXP added custom commands to provide better and faster options for specific NTAG5 use cases. [18] The board can operate either in selected or addressed mode. In selected mode, the initiator sends select command with tag's address mostly only at the beginning of the communication session and then the following commands do not include address of the tag in the header. In addressed mode, the mobile phone needs to include the address in every command.

Memory is writable and readable only by blocks (4 B) from NFC interface. Table 1.2 includes a list of NFC commands that will be used in the example mobile application. Detailed documentation of each command can be found in [18].

| Command             | Description                                                          |  |

|---------------------|----------------------------------------------------------------------|--|

| SELECT              | Transfer to selected mode                                            |  |

| READ SINGLE BLOCK   | Read a block from memory                                             |  |

| WRITE SINGLE BLOCK  | Write a block to memory                                              |  |

| READ SRAM           | Read blocks of data from SRAM                                        |  |

|                     | (only in Pass-through mode)                                          |  |

| WRITE SRAM          | Write blocks of data to SRAM                                         |  |

|                     | (only in Pass-through mode)                                          |  |

| READ CONFIGURATION  | Read blocks of data from configuration<br>memory or session register |  |

| WRITE CONFIGURATION | Write a block to configuration memory                                |  |

|                     | or session register                                                  |  |

Table 1.2: NTAG5 NFC commands [18]

The maximal length of one command from a phone is 253 B. For the command that writes SRAM, which has 5 B header (selected mode), it only leaves 248 B for data to be written. Therefore if we wanted to use the whole SRAM (256 B) for transferring data, we would need to use at least two separate commands to send the data.

#### 1.2.1.2 I<sup>2</sup>C interface

The  $I^2C$  interface of NTAG5 board supports both master and slave mode. The master mode can be used for collecting data from sensors without using MCU. In this work there is an external processor, which will be used as a bus master, so slave mode will be used for NTAG5.

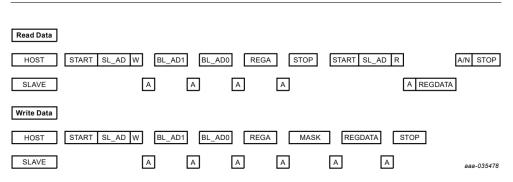

NTAG5 link I<sup>2</sup>C interface uses standard 7-bit addressing. It can operate on 100 kHz or 400 kHz speed in slave mode. Board's default address is 0b1010100 (0x54). The interface is used to read and write memory or registers. Start and stop conditions and address frame are omitted in the communication description below for better readability, as they are mandatory. Brief summary of I<sup>2</sup>C bus communication was done in 1.1.3 section.

The communication scheme for working with EEPROM memory can be seen in figure 1.9. For SRAM, there are only different constraints, but the principle is the same. Reading from memory requires two  $I^2C$  transactions. The first one is a write of higher and lower byte of address from where the data will be read. The second one is the actual read of N bytes from memory. The number of bytes to be read is not limited on the side of NTAG5.

Writing memory is handled by one  $I^2C$  transaction. The first two transmitted bytes are the higher and lower byte of the memory address, where the data will be written. After that N bytes of data is sent. It is only possible to write exactly 4 bytes to EEPROM. Writing to SRAM is limited to a maximum of 256 bytes at once and the number should be a multiple of 4.

| Read Data                               |                      |                    |

|-----------------------------------------|----------------------|--------------------|

| HOST START SL_AD W BL_AD1 BL_AD0 STOP   | START SL_AD R        | A A AN STOP        |

| SLAVE A A                               | A DATA 0 DA          | TA 1 DATA 2 DATA N |

| Write Data                              |                      |                    |

| HOST START SL_AD W BL_AD1 BL_AD0 DATA 0 | DATA 1 DATA 2 DATA 3 | STOP               |

| SLAVE A A A                             | A A A                | asa-035477         |

Figure 1.9: NTAG5 link - I<sup>2</sup>C read and write memory commands [18]

The communication scheme for working with session registers can be seen in figure 1.10. The interface allows to manipulate only one byte of the register block at a time (one block has 4 bytes). For most operations, this is sufficient and when there is a need to modify more bytes at one time, the time overhead is not that high. Register value reading communication consists of two  $I^2C$ transactions. The first one writes higher and lower byte of register block address followed by index of wanted byte in the block. The second transaction is used to actually read the one byte of the register's value.

Writing a value to a register is done by one  $I^2C$  transaction. The transaction consists of writing higher and lower byte of register block address, index of the specific byte in the block, mask of bits that will be written from the value and it ends with the actual value to be written.

#### 1.2.1.3 NTAG5 configuration

There are two ways how the NTAG5 can be configured:

- Configuration (memory) setting

- Session registers

The data from the configuration setting is always copied to session registers on power on reset (POR). While the NTAG5 is operating, the configuration

Figure 1.10: NTAG5 link - I<sup>2</sup>C read and write register commands [18]

is taken from session registers. This means that using configuration setting enables the user to set long-term config that will persist after reset, but will not take effect immediately. On the other hand, setting session registers affects current communication, but will be overwritten on the next reset. So configuration that should be used permanently or at the very beginning of communication, when NFC field is entered, should be set in configuration setting and any other configuration should be set in session registers. A good example of what needs to be set in the configuration setting is the use case config - operation mode of the NTAG5 board (in this work, it is I<sup>2</sup>C slave option). Also the security information should be set there. [18]

The configuration memory can be set by READ CONFIG and WRITE CONFIG from NFC interface and by memory manipulations from  $I^2C$  interface. The session registers can be also set by READ CONFIG and WRITE CONFIG from NFC interface, but from  $I^2C$  interface the register manipulations are needed instead of the memory ones. Note that  $I^2C$  interface addresses memory (starting from 0x1000), where NFC interface addresses only blocks in the commands (0x00 is the first block). [18]

#### 1.2.1.4 Event detection pin

NTAG5 link board includes an event detection (ED) pin, that is used for signaling external devices that an event has occurred. The tracked event can be chosen by modifying bits 0-3 in ED\_CONFIG (configuration memory) or ED\_CONFIG\_REG (session register). The ED pin has active low implementation (ON = 0, OFF = 1). [18]

Table 1.3 contains possible configurations of ED pin, that are important for this thesis.

#### 1.2.1.5 NTAG5 link communication modes

This section describes different communication modes that are available on NTAG5 link for bidirectional communication between the NFC interface and

| Name                                 | Value | State | Description                                                                    |

|--------------------------------------|-------|-------|--------------------------------------------------------------------------------|

| Disable ED                           | 0000b | OFF   | Event detection pin disabled                                                   |

| NFC Field detect                     | 0001b | ON    | NFC field present                                                              |

|                                      | 00010 | OFF   | NFC field absent                                                               |

| I <sup>2</sup> C to NFC pass-through | 0011b | ON    | Last byte of SRAM data has<br>been read via NFC; host can<br>access SRAM again |

|                                      |       | OFF   | Last byte written by I2C, or<br>NFC off, or VCC is off                         |

| NFC to I <sup>2</sup> C pass-through | 0100b | ON    | Last byte written by NFC;<br>host can read data from<br>SRAM                   |

|                                      |       | OFF   | Last byte has been read from<br>I2C, or NFC off, or VCC off                    |

| Arbiter lock                         | 0101b | ON    | Arbiter locked access to NFC interface                                         |

|                                      |       | OFF   | Lock to NFC interface re-<br>leased                                            |

Table 1.3: NTAG5 event detection pin configurations [18]

the slave  $I^2C$  interface. The modes differ in the memory they use and the style of arbitration, which interface can access the memory. Some of the modes support extra commands.

NTAG5 link can operate in 4 communication modes for exchanging data between NFC and slave  $I^2C$  interface [19]:

- Normal Mode EEPROM is used for main data storage, but the SRAM can also be accessed if requirements are matched. The memory access arbitration is based on first come first serve principle.

- SRAM Mirror Mode the same as normal mode, but SRAM is mirrored on EEPROM (EEPROM underneath is inaccessible), and it can be used for functionalities restricted for that area (NDEF messages)

- SRAM Pass-Though Mode SRAM is used as the only data storage. There are two parts of arbitration - the direction setting (changed manually by writing to session registers) and the interface lock (changed automatically based on reads and writes to the last data block). It also includes additional commands for reading and writing multiple blocks of data at once from NFC interface, which dramatically affects the time needed to transfer bigger data.

• **PHDC Mode** - special mode for Personal Health Device Communication - similar to normal mode, but special commands are supported

Pass-Through mode allows the smoothest data transfer for an application, where a large amount of data is sent in one or both directions. This is the case for the bootloader, where new application needs to be loaded. This is mostly caused by the ability to write multiple blocks of memory at once from the NFC interface, because this has a big effect on the transaction time.

As mentioned above, the Pass-through mode synchronizes the devices behind the NFC interface and  $I^2C$  interface by default. For the Normal and SRAM mirrored mode, it is possible to synchronize the devices by using signalization on SYNCH\_BLOCK. NTAG5 detects and remembers when the synchronization block has been read or written. This is somewhat similar to Pass-Through mode detection on the last memory block, but the address of the block can be specified on runtime by modifying SYNCH\_DATA\_BLOCK register and the devices need to implement the arbitration mechanism themselves.

To be able to use Pass-Through mode or SRAM Mirror Mode, it is required to have the NTAG5 VCC supplied. This is required so that SRAM memory can be used. The same goes for using SRAM in Normal mode. [19]

Example, how the manufacturer suggests to use the Pass-through mode in document [19], is present in appendix A.

#### 1.2.1.6 Example applications

NXP Seminductors developed example applications for NTAG5 usage. There is a set of an embedded project and an android app. Together they can demonstrate different use cases for the NTAG5, like Pass-Through mode, GPIO, PWM and I<sup>2</sup>C master mode. The applications in the embedded project are designed for NXP's FRDM-KW41Z board. [17]

Authors in [20] describe the different features mainly from the view of the android app.

There is also an iOS version of the example application. There are two Windows applications. One enables the user to configure NTAG5 from NFC interface with an NFC reader connected via USB to the PC. The second one enables the user to configure NTAG5 from  $I^2C$  interface via USB-I2C bridge. [17]

Only the first set is interesting for this thesis, and especially the android app, which I will use as a base for the testing application.

All the applications are available from [17].

#### **1.2.2** Target processor

The bootloader will be implemented for a proprietary processor with RISC-V architecture. The company, which gave me the assignment, wishes for the

name of the processor to remain hidden, so I will refer to the processor as "the target processor".

The target processor is still in development. I am using the processor emulated on an FPGA and once in a while, I receive an updated bitstream. This means that some things are still changing, while I am working on this thesis, and there are some things that do not work correctly. This makes the work harder than it would be if the processor was done and its specification was complete and not changing.

Basic information about the target processor is included in table 1.4.

| Parameter         | Value      |

|-------------------|------------|

| Architecture      | 32b RISC-V |

| Clock frequency   | 8 MHz max  |

| Supply voltage    | 1-3.6 V    |

| SRAM memory size  | 8 kB       |

| Flash memory size | 128 kB     |

Table 1.4: Target processor parameters [21]

The processor is designed for usage in ultra low-power IoT projects.

#### 1.2.2.1 RISC-V ISA

RISC-V is an instruction set architecture (ISA) with an integer base of 32b or 64b. There are multiple prepared extensions and the ISA is opened for customization and specialization. [22]

The RISC-V ISA base includes instructions for fundamental operations with integers (load, store and computation) and code flow-control instructions. Standard extensions add integer multiplication and division operations, single and double precision floating-point operations and atomic operations. [22]

Names of RISC-V implementations are based on the base and extensions that are included. The name starts with ether "RV32" or "RV64" depending on the integer register width and followed by "I" standing for the base. Then the one-letter identifications of included extensions are added. [22]

The target processor is of type RV32IMC. It is built on a 32b base with addition of standard extension of compressed instructions and partial support of integer multiplication and division. [21]

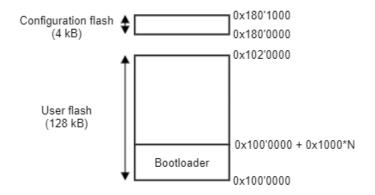

#### 1.2.2.2 Flash memory

Flash memory of the processor includes two sections. There are 128 kB of user memory and 4 kB of flash is dedicated for configuration data. The flash's sector size is 4 kB and row (line) size is 128 B. This means that one sector consists of 32 rows and the whole memory has 32 sectors (1024 rows). Lines are

the minimal unit for erase operations and the only unit for write operations. [21]

The memory can be programmed either from JTAG interface or by inapplication programming, where the data is received from any other present interface. [23]

The architecture expects that the bootloader will be located in the first N sectors at the beginning of the flash memory (N goes from 0 to 32) [21]. There is no particular functionality based on this except for the mass erase function (viz. 1.2.2.3).

Figure 1.11 shows the flash memory scheme of the target processor.

Figure 1.11: Flash memory scheme of target processor

Table 1.5 includes times of flash operations. These times are just an estimate to be corrected once the real version in silicon is characterized. Measured times for current configuration will be included in section 4.3.

Table 1.5: Maximal times of flash memory operations on the target processor [21]

| Operation              | Time              |

|------------------------|-------------------|

| Memory erase           | 4-10 ms           |

| (mass, sector or line) |                   |

| Line write             | $3.5 \mathrm{ms}$ |

#### 1.2.2.3 Flash driver

The driver is required for erasing and writing the memory. It is not needed for reading operations. The flash memory is not accessible for reading while erase or write operation is being executed, so it is mandatory to move the flash driver and any other code that should be executed in the meantime from flash to SRAM. Any attempt to access the flash will stall the processor until the operation is done. [23]

The flash driver has been implemented by the MCU manufacturer before this thesis. That is why the implementation is not included in it. However, I was actively involved in testing and debugging the driver and I have made some minor changes in it, so it could be included in the project.

The driver implements following operations for the flash memory [24]:

- Locking and unlocking the memory Locking the memory prevents an unwanted modification or corruption of the memory. It is essential to unlock the memory only for the time necessary to perform erase and write operations.

- Mass erase This function is meant to be used for erasing the whole memory except for sectors where the bootloader is located. It accepts an address of the first block, from where the erase will be performed.

- Sector erase This function is used to erase a single sector (4 kB) of the memory.

- Line erase This function is used to erase a single line (128 B) of the memory.

- Line write This function writes data to one line (128 B) of the memory. It is required to write only previously erased memory.

- Waiting for an operation to end The erase and write functions mentioned above only order the HW layer below to perform the specified operation. This function is used to wait until that operation is done. The user can specify a timeout for this function.

A rewrite of a part of memory is meant to be performed by executing following steps:

- 1. Unlock the memory

- 2. Erase a part of memory

- 3. Write all needed lines

- 4. Lock the memory

It is possible to split the erase and the write operations or not to perform all the write operations at the same time, but in that case, it is needed to lock the memory in between them.

It is necessary to avoid reset while the erase or write operation is ongoing (watchdog should be kicked, software reset should not be called, etc.). The state of the battery should be checked before performing erase or write operation and voltage monitoring should be enabled. If one of the operations fails due to a voltage drop, it is necessary to erase the part of memory to which the operation was connected. [23]

### 1.2.2.4 $I^2C$ driver

The I<sup>2</sup>C driver provides API for operating I<sup>2</sup>C. The processor can act only as a master. It can be either used with busy waiting on every operation or with interrupts. DMA support has not been added yet. [21]

$I^2C$  interface in the target processor supports 7b addressing and data rates up to 100 kbps, 400 kbps, or 1 Mbps (requires an external pull-up resistor). The  $I^2C$  controller includes a 2 B FIFO for storing received bytes or data to be sent. The direction of the communication is automatically assumed from the address byte. [21]

The I<sup>2</sup>C driver API includes [24]:

- Initialization of the bus setting up the environment, including the pins

- Enabling and disabling of the bus

- Starting an operation start condition and sending address frame + setting data counter (number of data that will be sent/receive in this operation)

- Receiving a byte get byte from FIFO or try to wait until timeout if it is empty

- Send a byte put byte to FIFO or try to wait until timeout if it is full

- Wait for a stop condition

#### 1.2.2.5 Interrupts

The mtvec register in RISC-V stores the base address of the interrupt vector table. The possibility of changing its value depends on implementation. [25]

The target processor enables to change the address contained in mtvec and it can even point to SRAM. This means that the whole interrupt handling can be moved to SRAM. This can be needed if the processor needs to be able to continue working while a flash memory erase or write operation is performed. [21]

# CHAPTER 2

# Design

In this chapter, I go through the design choices that I needed to make.

Section 2.1 describes the design of the bootloader. First, I describe how the bootloader will work in general. Then I show and describe the memory layout. Finally, I introduce the operation workflow of the bootloader, except for the DFU part that I will describe in section 2.3.

Section 2.2 includes design of the communication stack. In there, I describe which mode will be used for NTAG5 link board and how the communication will work over this channel.

Section 2.3 introduces the design of the DFU operation scheme. It also describes how the communication parameters affect this design.

Section 2.4 introduces the messaging system that will be used between the bootloader and the mobile phone. It includes a list of commands and sequence diagrams of the communication.

# 2.1 Bootloader

The design of the bootloader in this thesis is strictly dependent on the target processor and its properties. The most limiting factor is small memory size. The processor has only 128 kB of flash memory and 8 kB of SRAM. This affects the functionalities that the bootloader can have (the goal is to have a small bootloader to leave space for user application) and also the process of how the bootloader needs to operate. The second crucial thing is the request for the bootloader to be robust. This means the bootloader (or the user application) must not include operations that could potentially corrupt the bootloader (for example, if the operations failed or were interrupted).

#### 2.1.1 DFU principle

The bootloader created in this thesis will be able to update the user application only. It will not be possible to update the bootloader on-the-fly, because it is not possible to do it safely without using a multilayer bootloader (the first code that is executed after reset needs to be always fixed).

The new application cannot be pre-downloaded as a whole due to lack of memory space (external flash is not available at all). Because of this, the update of the software is done only in the bootloader. If the pre-downloaded could be done, it could be done while the old app was running. Because it is not possible, the DFU in bootloader will be done in two steps:

- 1. Clear the memory (delete the old application)

- 2. Receive new application part by part and write it to flash on the fly

#### 2.1.2 Program flow

The bootloader could theoretically be built on a scheduler. This may seem like a good idea at first, that it would be easier to communicate and operate the flash at the same time, but it is really not necessary. It is even counterproductive because the bootloader should be as simple as possible to minimize its memory footprint and to reduce the space for error (as said, the bootloader will not be updatable on the fly). So the bootloader will work sequentially, just with the use of interrupts.

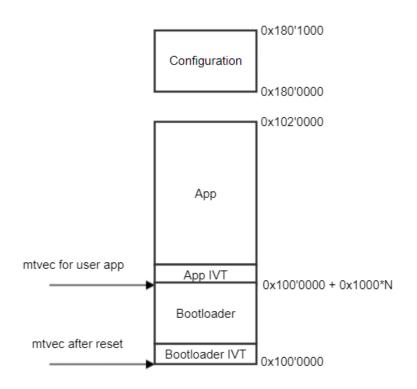

#### 2.1.3 Flash memory layout and interrupt vector tables

The flash memory layout that will be used in this thesis is displayed in figure 2.1. The bootloader will be placed at the beginning of the user flash memory. It is already defined like this in the specification of the processor. There are two reasons why this was already specified there.

The first one is that the flash controller has a mass erase function with "protection" of the first N memory sectors (4 kB). This also means that the bootloader needs to be aligned to sector size and the user application cannot be placed closer than in the next sector.

The second reason is connected to interrupt vector tables. The bootloader and the user application will each have their own IVT. This enables the user to compile the codes separately. It is possible to have multiple IVTs, because the processor enables the user to specify the address of IVT in mtvec register at run time. Upon reset of the processor, the value of mtvec is always set to the beginning of flash memory (0x1000000), so the bootloader IVT has to be placed there. Once the bootloader is in the stage when the user application should be started, it sets the mtvec to address of the application IVT and it jumps to the application's reset handler. Only these two operations with mtvec (using value after reset and set upon app start) are sufficient for the bootloader to work. Analysis, why it not necessary to also have an IVT in SRAM, is done in section 2.3.

Figure 2.1: Flash memory layout

#### 2.1.4 Bootloader operation scheme

In this section, I will go through bootloader operation design. The first two paragraphs include a brief overview and the following text includes detailed description.

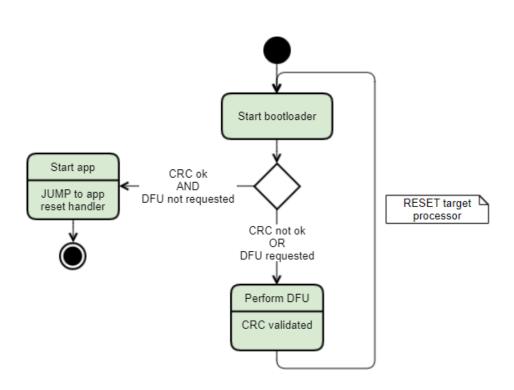

The bootloader is always run on reset of the processor. It checks if the DFU needs to be performed (there was an external request for DFU, or the CRC of application in memory does not match the control CRC stored in configuration memory) and if so, the bootloader performs it. After a successful DFU, the memory includes a valid app and its CRC is stored for future checking to the configuration memory. Once the memory includes a valid app, the bootloader can run it.

A standard request for a DFU is made through the user application. If the user application knows the DFU needs to be performed (e.g. it received a command to do so), it forwards the information to the bootloader by invalidating the CRC in configuration memory, and it resets the processor. After the reset, the bootloader is started and it thinks the application in memory is not valid, so it performs the DFU.

Figure 2.2 displays scheme how bootloader is operating. The bootloader is

started after each reset of the processor. First, it initializes the environment ("Start bootloader"). Then it checks if there is a valid application in memory. This will be done by computing its CRC32 and comparing it to value that has been stored after the last DFU to the configuration flash.

If the CRCs do not match, the bootloader knows that the DFU has to be performed and it switches to it ("Perform DFU"). The second option how to trigger the DFU is a DFU request from outside. This is definitely needed in case when there is a valid app in memory, but it is not able to invalidate the CRC for any reason (e.g. a bug causing reset before it can do it). However, this option is project specific and it will need to be implemented based on the needs of the particular project. It can be, for example, done by sniffing on a pin or pins for a given amount of time or by checking the NFC interface, if there is not a message requesting DFU.

If the CRCs match and there was not a request for DFU, the bootloader starts the application ("Start app"). It is necessary to deinitialize everything before the application is started because the application performs its own initialization. Then the bootloader changes the value in mtvec so that it points to the application interrupt vector table (interrupts should be disabled at the time). And finally, the bootloader jumps to the reset handler of the application.

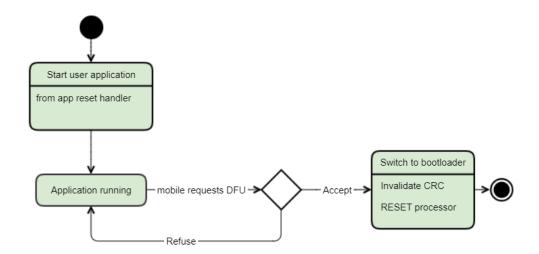

Operation of user application from bootloader point of view is displayed in figure 2.3. It starts when the bootloader jumps to the application's reset handler ("Start user application"). With this, the application becomes autonomous. Its startup code initializes everything just as if there was no bootloader. Apart from normal functionality, the app is expecting that in future, it will receive a request for DFU. This can be, for example, a request from mobile via the NFC interface. Once the request is received, the application assesses if there are no obstacles, why the DFU cannot be performed at this moment. If everything is ok, the application can prepare for shutdown by saving data and such. Once it is ready, it invalidates the CRC value stored in configuration flash to let the bootloader know DFU needs to be performed, and it restarts the processor to start the bootloader ("Switch to bootloader").

## 2.2 Communication stack

In this section, I will describe the design choices I made while creating the communication stack between mobile and target processor over NFC, with the usage of NTAG5 link NFC tag. The communication stack will be used by the bootloader but also by the user application to unify the communication. In the bootloader, the main goal of the communication is to transfer data of the new application (up to 128 kB) to the processor. This will require a large number of long messages, but also some short control messages. On the other hand, the application will probably mostly use shorter commands to get status

Figure 2.2: Bootloader operation scheme

Figure 2.3: User application operation scheme from bootloader point of view

or set some value, but sometimes it may also need to transfer a larger amount of data sometimes (e.g. log data). Therefore the communication stack will need to be flexible to support sending short and long messages both ways.

#### 2.2.1 Communication channel

The communication channel between mobile and target processor consists of two parts.

- NFC part between mobile and NTAG5 link

- I<sup>2</sup>C part between NTAG5 link and target processor

In between these parts, the data will be stored in SRAM of NTAG5 link. NTAG5 link also supports EEPROM for this job, but it is not suitable for the purpose of sending a large amount of data. The scheme of the data paths is displayed in figure 2.4.

Figure 2.4: Scheme of communication channel between mobile and target processor

#### 2.2.1.1 NTAG5 mode selection

NTAG5 link offers two modes that could possibly be used with SRAM in the middle: the SRAM mirrored mode and pass-through mode (description of both of them was done in 1.2.1.5 section). If we only needed to send short messages, ideally with a fixed length, the mirrored mode would be fine. For a larger amount of data, it is not ideal because it does not support command for writing multiple blocks of SRAM memory at once, which greatly reduces transfer time for this use case.

This command is only supported in Pass-through mode, which is the main reason why this mode will be used. Another specification of this mode is that developer needs to control the direction of communication. This setting needs to be done from  $I^2C$  side. Once the direction is set, the board automatically switches interface locks, so only one interface can manipulate the data in memory. The lock is switched on every interaction with the last block of SRAM (write or read of this block). This strict arbitration can be used as an advantage here. Both sides can check the state of the communication anytime, and they do not need to do any special synchronization.

#### 2.2.1.2 NTAG5 SRAM usage

NTAG5 link has 256 B of SRAM memory divided into 64 blocks (one block has 4 bytes).

From the NFC side, it is only readable and writable by blocks. Write SRAM (respectively Read SRAM) command contains a specification of how many blocks should be read. It is defined by one byte, so it could theoretically write (respectively read) the whole SRAM. However, the NFC interface of each device limits the maximal length of a message. For the NTAG5 link, it is 253 B. The Write SRAM command in selected mode has a 5 B header, so it leaves 248 B (62 blocks) for data transfer. The Read SRAM command can return up to 252 B (63 blocks) of data at once.

From the  $I^2C$  side, it is limited by  $I^2C$  driver in the target processor, which can handle only 256 frames per operation. With taking command structure into account, 255 B can be read and 252 B written at one operation.

It was necessary to choose an address where the mobile and target processor should expect the beginning of the message. There were two options after putting together length limits of read and write commands from both interfaces:

- start from block 0x02

- 248 B available

- big data writable (readable) with one command (suitable for long messages)

- messages will not start at the beginning of memory

- start from block 0x00

- 256 B available

- even long messages need 2 commands to be written (read)

- messages will start at the beginning of memory

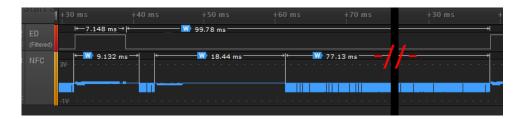

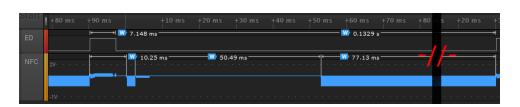

If we wanted to use the whole SRAM, we would need to always use two read and write commands from each interface. Unfortunately, the NFC interface has a quite large overhead for each command. Times measured in initial NFC speed testing I have done are in table 2.1. The times were measured on the event detection pin of NTAG5 link. <sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Because in the final implementation, the exchange between using only 248 B or the whole 256 B can be done very easily, I was able to measure the difference this choice made in the end. Results of the measurement are included in chapter "Testing".

| Data length     | Transfer time         | Transfer speed        |

|-----------------|-----------------------|-----------------------|

| 4 B             | 23.6 ms               | $0.17 \mathrm{~B/ms}$ |

| 248 B           | $137.2 \mathrm{\ ms}$ | 1.81 B/ms             |

| 256 B (2*128 B) | $155.1 \mathrm{ms}$   | $1.65 \mathrm{~B/ms}$ |

Table 2.1: Initial NFC write SRAM speed testing with Samsung A21S

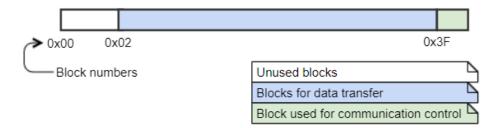

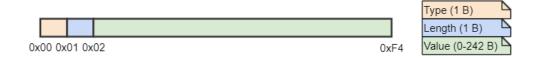

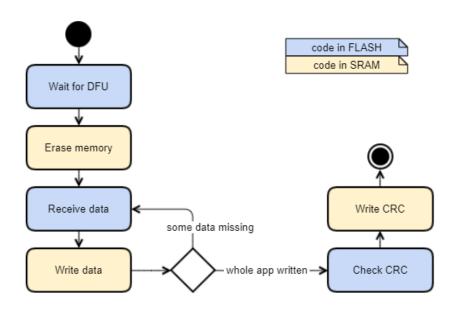

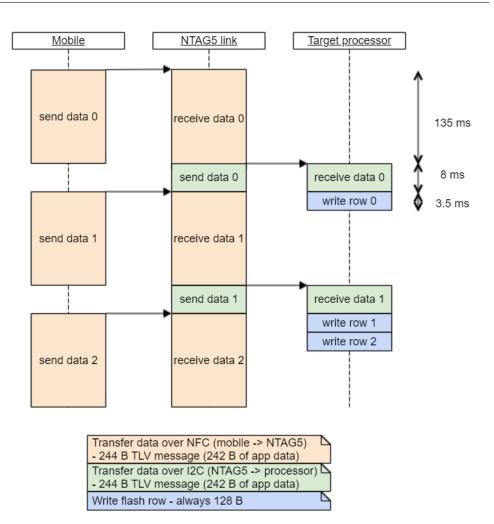

In the implementation, I will use the option with using only 248 B of NTAG5 link's SRAM. It enables faster transfer of data and the fact that the data does not start at the beginning of the memory is not crucial even for debugging because the memory is not readable directly.