### Assignment of bachelor's thesis

| Title:                   | Development of parallel sorting algorithms for GPU |

|--------------------------|----------------------------------------------------|

| Student:                 | Xuan Thang Nguyen                                  |

| Supervisor:              | Ing. Tomáš Oberhuber, Ph.D.                        |

| Study program:           | Informatics                                        |

| Branch / specialization: | Computer Science                                   |

| Department:              | Department of Theoretical Computer Science         |

| Validity:                | until the end of summer semester 2021/2022         |

#### Instructions

1. Study the basics of programming GPU using CUDA.

2. Learn the fundamentals of the development of parallel algorithms with TNL library (www.tnl-project.org).

3. Learn and understand parallel sorting algorithms, namely bitonic sort and quick sort.

4. Implement both algorithms into TNL library to run on CPU and GPU.

5. Implement unit tests for testing correctness of the implemented algorithms.

6. Perform measurement of speed-up compared to sorting algorithms in the STL library and GPU implementation [1].

[1] https://github.com/davors/gpu-sorting

Electronically approved by doc. Ing. Jan Janoušek, Ph.D. on 30 November 2020 in Prague.

Bachelor's thesis

# Development of parallel sorting algorithms for GPU

Nguyen Xuan Thang

Department of Theoretical Computer Science Supervisor: Ing. Tomáš Oberhuber, Ph.D.

May 13, 2021

## Acknowledgements

I would like to thank my supervisor Ing. Tomáš Oberhuber, Ph.D. for his support, guidance and advices throughout the whole time of creating this thesis. My gratitude also goes to my family that helped me during these hard times.

## Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular that the Czech Technical University in Prague has the right to conclude a license agreement on the utilization of this thesis as a school work under the provisions of Article 60 (1) of the Act.

In Prague on May 13, 2021

. . . . . . . . . . . . . . . . . . .

Czech Technical University in Prague Faculty of Information Technology © 2021 Xuan Thang Nguyen. All rights reserved. This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the

#### Copyright Act).

#### Citation of this thesis

Nguyen, Xuan Thang. Development of parallel sorting algorithms for GPU. Bachelor's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2021.

## Abstrakt

Tato práce se zabývá vybranými paralelními řadícími algoritmy vhodnými pro implementaci na GPU. Jedná se konkrétně o Bitonic sort a Quicksort. Bitonic sort, i když má vyšší časovou složitost, je vhodným kandidátem na řazení malých posloupností. Paralelní Quicksort je rychlejší pro větší vstupy, ale potřebuje  $\Theta(n)$  paměti na pomocné pole pro přeskládání. Oba algoritmy jsou popsány a implementovány pro GPU od NVIDIA s pomocí CUDA API a TNL knihovny. Jako jazyk byl zvolen C++. U Bitonic sortu je navíc představena varianta, která využívá jen lambda funkce a odprošťuje se tak od kontejneru dat. Všechny implementace jsou řádně otestovány, změřeny a porovnány s jinými implementacemi, které jsou dostupné pro CPU a GPU.

**Klíčová slova** paralelní řazení, GPU, CUDA, C++, TNL, Bitonic sort, Quicksort

### Abstract

This thesis is about selected sorting algorithms suitable for GPU implementation. The chosen algorithms are Bitonic sort and Quicksort. Although Bitonic sort has a worse theoretical time complexity, it is a suitable candidate for sorting smaller inputs. Quicksort is faster for bigger inputs, but for parallel implementation,  $\Theta(n)$  auxiliary memory is needed because it is an out-of-place algorithm. Both algorithms were studied and then implemented in C++ extended with CUDA API with the help of TNL library. For Bitonic sort, a version that only uses lambda functions is introduced. The resulting work was then tested, measured, and compared with other CPU and GPU implementations.

Keywords parallel sort, GPU, CUDA, C++, TNL, Bitonic sort, Quicksort

### Summary

#### Motivation

Sorting is an important operation used in many algorithms, but a singlethreaded implementation can take a long time to process big inputs. For this reason, GPUs can be used to sort a sequence in parallel and gain speed-up.

#### Goals

The goal of this thesis is to implement a parallel version of selected sorting algorithms, namely Bitonic sort and Quicksort. These two functions will be running on GPU using CUDA with the help of TNL library [1]. The implementations are to be tested, measured, and compared against other known CPU and GPU implementations.

#### Method

To explain the algorithms, GPU architecture, TNL library, and CUDA are first explained. Then, the theory around sorting is introduced and afterward, the algorithms themselves.

The first part of the implementation describes parts of Bitonic sort and shows where speed-up was gained with the use of faster shared memory. In the next part, Quicksort kernels are explained in detail and all steps necessary to partition a task are described. The use of shared memory and its methods of gaining speed-up is also explained.

#### Results

The resulting work contains an efficient version of Bitonic sort that can be called both from CPU and GPU. Measurements show that this version's Bitonic sort can rival the implementation provided by CUDA SDK [2]. For big inputs, Bitonic quickly loses against other algorithms with better time complexity. Our parallel Quicksort runs faster than the original solution implemented by Cederman et al. [3] but loses against Manca et al.'s [4] optimized implementation of Quicksort. TNL Quicksort was also compared against thrust::sort[5] available in the CUDA toolkit. The results show worse performance than the highly optimized thrust::sort, but this stems from the fact that the function from thrust implements Radix sort internally.

#### Conclusion

Both Bitonic sort and Quicksort were properly tested and measured and are ready to be added into the TNL library. Although the results do not show the best performance, the speed-up compared to CPU sort is still noticable.

## Contents

| 1               | Intr | oducti  | on                                            | 1 |

|-----------------|------|---------|-----------------------------------------------|---|

| 2 Preliminaries |      |         | ries                                          | 3 |

|                 | 2.1  | GPU a   | architecture                                  | 3 |

|                 | 2.2  | CUDA    |                                               | 3 |

|                 |      | 2.2.1   | Thread grouping                               | 4 |

|                 |      | 2.2.2   | Memory hierarchy                              | 4 |

|                 |      | 2.2.3   | Thread Synchronization                        | 5 |

|                 |      | 2.2.4   |                                               | 7 |

|                 | 2.3  | TNL     |                                               | 7 |

|                 |      | 2.3.1   | TNL data structures                           | 7 |

|                 |      | 2.3.2   | TNL View structures                           | 8 |

|                 |      | 2.3.3   | Lambdas                                       | 8 |

|                 | 2.4  | Notati  | on                                            | 8 |

|                 | 2.5  | Sortin  | g problem                                     | 9 |

|                 |      | 2.5.1   | Single thread limitation                      | 9 |

|                 |      | 2.5.2   | Overview of existing algorithms               | C |

| 3               | Bite | onic So | ort 12                                        | L |

|                 | 3.1  | The B   | itonic sort algorithm 1                       | 1 |

|                 |      | 3.1.1   | Bitonic merge                                 | 2 |

|                 |      | 3.1.2   | Sorting in-place                              | 4 |

|                 |      | 3.1.3   | The recursive algorithm                       | 5 |

|                 |      | 3.1.4   | Time complexity                               | 5 |

|                 |      | 3.1.5   | Sorting not aligned sequences                 | 6 |

|                 | 3.2  | Paralle | el algorithm                                  | 6 |

|                 |      | 3.2.1   | Sorting network                               | 7 |

|                 |      | 3.2.2   | Time complexity of parallel implementation 19 | 9 |

|                 | 3.3  | Existin | ng implementations 19                         | 9 |

|          | 3.4 | Implementation of Bitonic sort with CUDA 20                                                                 |

|----------|-----|-------------------------------------------------------------------------------------------------------------|

|          |     | 3.4.1 Host side                                                                                             |

|          |     | 3.4.2 Device side                                                                                           |

|          |     | 3.4.3 Calculating the direction of swap                                                                     |

|          |     | 3.4.4 Optimizations                                                                                         |

|          |     | 3.4.5 Shared memory in Bitonic Sort                                                                         |

|          | 3.5 | Bitonic sort from GPU                                                                                       |

| <b>4</b> | Qui | cksort 27                                                                                                   |

|          | 4.1 | The Quicksort algorithm                                                                                     |

|          |     | 4.1.1 Partitioning algorithms                                                                               |

|          |     | 4.1.2 Pivot Choice                                                                                          |

|          | 4.2 | Parallel algorithm                                                                                          |

|          |     | 4.2.1 Prefix sum                                                                                            |

|          |     | 4.2.2 Parallel Quicksort algorithm                                                                          |

|          |     | 4.2.3 Stopping in time                                                                                      |

|          | 4.3 | Implementation of Parallel Quicksort with CUDA                                                              |

|          |     | 4.3.1 Host Side                                                                                             |

|          |     | 4.3.2 Pivot choice                                                                                          |

|          |     | 4.3.3 First phase                                                                                           |

|          |     | 4.3.4 Multi block partitioning                                                                              |

|          |     | 4.3.5 Moving elements                                                                                       |

|          |     | 4.3.6 Writing pivot                                                                                         |

|          |     | 4.3.7 Creating new tasks                                                                                    |

|          |     | 4.3.8 Second phase                                                                                          |

|          |     | 4.3.9 Single block Quicksort                                                                                |

|          |     | 4.3.10 Explicit stack                                                                                       |

|          | 4.4 | Optimizations                                                                                               |

|          | 1.1 | 4.4.1 Parallel prefix sum                                                                                   |

|          |     | 4.4.2 Optimization with array rotation                                                                      |

|          |     | 4.4.3 Elements per CUDA block                                                                               |

|          | 4.5 | Using CUDA dynamic parallelism                                                                              |

|          | 1.0 | 4.5.1 Version 1                                                                                             |

|          |     | 4.5.2 Version 2                                                                                             |

| 5        | Tes | ting and measuring 47                                                                                       |

| Č        | 5.1 | Environment                                                                                                 |

|          | 5.2 | Testing                                                                                                     |

|          | 5.2 | Methods of measuring                                                                                        |

|          | 0.0 | 5.3.1 Testing data sets                                                                                     |

|          |     | 5.3.2 Comparison with other implementations                                                                 |

|          |     | 5.3.3 Results                                                                                               |

|          | 5.4 | Profiling                                                                                                   |

|          | 0.4 |                                                                                                             |

|          |     | 5.4.1 Bitonic sort $\ldots \ldots 53$ |

| 5.4.2 Quicksort $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | <br>54                |

|--------------------------------------------------------------------------------------------------|-----------------------|

| Conclusion Goals and results                                                                     | <b>57</b><br>57<br>58 |

| Bibliography                                                                                     | 59                    |

| A Acronyms                                                                                       | 63                    |

| B Contents of enclosed medium                                                                    | 65                    |

## **List of Figures**

| 3.1 | One step of Bitonic merge where $a_n > a_{2n}$       | 14 |

|-----|------------------------------------------------------|----|

| 3.2 | Sorting network comparator for two elements          | 17 |

| 3.3 | Bitonic sorting network for 8 elements               | 18 |

| 3.4 | Sorting 7 elements with a Bitonic sorting network    | 19 |

| 3.5 | Shared memory usage for Bitonic sort with 8 elements | 24 |

| 4.1 | Recursive tree of Quicksort                          | 28 |

| 4.2 | Using prefix sum to divide memory between threads    | 31 |

| 4.3 | Distribution of auxiliary array during Quicksort     | 37 |

## List of Tables

| 5.1 | Environments used to perform measuring and testing               | 47 |

|-----|------------------------------------------------------------------|----|

| 5.2 | Speed-up of algorithms compared to std::sort for random distri-  |    |

|     | bution                                                           | 51 |

| 5.3 | Speed-up of algorithms compared to std::sort for staggered dis-  |    |

|     | tribution                                                        | 52 |

| 5.4 | Comparison of kernels of CUDA Bitonic sort against TNL Bitonic   |    |

|     | sort for integer types                                           | 54 |

| 5.5 | Comparison of kernels of CUDA Bitonic sort that sorts (int, int) |    |

|     | against TNL Bitonic sort doubles.                                | 54 |

| 5.6 | Profilation of first phase and second phase of Quicksort         | 55 |

## List of Algorithms

| 3.1.1 Recursive Bitonic sort                                |

|-------------------------------------------------------------|

| 3.1.2 Recursive Bitonic Merge 15                            |

| 3.4.1 Bitonic sort kernel launch                            |

| 3.4.2 Bitonic sort kernel launch with shared memory 23      |

| 4.1.1 Quicksort algorithm                                   |

| 4.1.2 Hoare partition scheme                                |

| 4.1.3 Lomuto partition scheme                               |

| 4.2.1 Parallel Quicksort                                    |

| 4.3.1 Quicksort kernel launch                               |

| 4.3.2 Parallel partitioning in the first phase of Quicksort |

| 4.3.3 Second phase of parallel Quicksort                    |

| 4.4.1 CUDA parallel inclusive prefix sum 42                 |

| 4.5.1 Quicksort with CDP version 1                          |

| 4.5.2 Quicksort with CDP version 2                          |

## CHAPTER

### Introduction

Sorting problem is one of the most studied fields in computer science with a wide variety of applications. All libraries that deal with computation and numbers usually contain a sorting function to be used. Sorting also can be applied to many problems, either to simplify the problem or when the sorted property is required. If a search operation is used often, it might be better to give order to the input and use binary search to find elements faster.

As shown, sorting is very useful, and it is meaningful to study this problem. In some cases, fast sorting can have real-time impact. For this reason, this thesis will present implementations of sorting functions that can run faster than single threaded sorts.

A sorting algorithm that only uses comparisons has to make  $\Omega(n \log n)$  compares and as such will run in  $\Omega(n \log n)$  time. However, this limitation only applies to single-threaded implementations. With the help of more compute units, it is possible to occupy the hardware and spread out the load to gain speed-up. A CPU, usually labeled as a multi-core device, has only tens of cores to use at the same time and can only handle tens to low hundreds of threads at best. GPUs on the other hand can handle thousands of threads and are generally more suitable for mass parallelization.

The thesis' main goal is to implement selected sorting algorithms suitable for GPU and create a solution ready to be incorporated into the TNL library [1]. The implementation, as part of a templated library, has to be able to sort data of arbitrary type and not only numeric values. The code has to be implemented in C++ with the help of CUDA as this platform is used in the library.

In the first part of the theoretical section, the necessary hardware and software will be introduced. Then the sorting problem itself is explained and improvements are proposed. A general overview of existing GPU sorting implementations will also be present. Not all algorithms are suitable to be parallelized, for this reason, the advantages and disadvantages of the chosen algorithms are explained.

#### 1. INTRODUCTION

For the algorithms themselves (Bitonic sort and Quicksort), a whole chapter is dedicated to their theory and how the algorithm will run. Bitonic sort, albeit being intensively studied by specialists, is not very known by the outside community. Because of this, the algorithm is described in great detail and a proof is given. Quicksort, while being well-known, has a different implementation compared to its CPU version and the parallelization part is not as straightforward compared to Bitonic sort. For this reason, this thesis will also describe in detail the steps necessary to partition an input and how to use the available resources efficiently.

In the implementation part, the code itself will be studied and the main choices made explained. The algorithms are then further enhanced to utilize faster shared memory available to threads during run-time and then problematic spots will be analyzed.

Finally, this thesis will present experimental results measured on a professional grade GPU and then, comparison between the implementation and other CPU and GPU sorts will be shown.

$_{\text{CHAPTER}} 2$

## **Preliminaries**

#### 2.1 GPU architecture

A GPU (Graphics processing unit) is a specialized device that works with CPU (Central processing unit) to compute tasks. The main difference between them is how each device is designed. CPUs are highly optimized to run at high frequency using only one or a few threads on one processing unit. A thread is a sequence of instructions that need to be carried out and a processing unit is the hardware that can perform the operations. A CPU, to achieve high throughput, uses many tricks and optimizations such as data and instruction caching, out-of-order execution or branch predicting. A GPU on the other hand relies on simpler hardware but contains more computing units. A CPU by design devotes most of the surface to data cache and other transistors to optimize flow control and minimize data access latency while a GPU occupies the space available with hardware necessary to do calculations. This allows GPU devices to start thousands of threads to use the high number of computing units to process data in parallel and mask data latency this way [6].

#### 2.2 CUDA

CUDA is a computing platform and programming model that allows the programmer to utilize NVIDIA GPUs [6]. The CUDA toolkit not only contains a software environment extending C++ but also other tools to help the programmer develop efficient programs on GPUs, such as debugging and profiling applications. With CUDA, it is also necessary to install the correct driver to enable communication with the GPU. The CUDA API is extensive and is in detail described in the CUDA guide documentation [6]. In this thesis, only the important parts of the CUDA API will be described to give a brief overview.

#### 2.2.1 Thread grouping

The fundamental building blocks of a CUDA program are kernels. Kernels are CUDA C++ extended functions that are executed in parallel by n different CUDA threads [6]. Threads that execute a kernel are grouped into a *block* and the size of the block is set by the programmer during kernel launch. The size of the block is usually set as a multiplier of 32 because of warp execution. A warp is a group of 32 threads within a block that have consecutive thread *id* (e.g. thread 0...31 create a warp).

Each thread in a kernel has access to multiple hidden variables available from anywhere in the device code to identify themselves. The variable **blockDim** holds information about how many threads there are in a block and **threadIdx** is used to identify the thread in a block. To check how many blocks were launched, all threads have access to gridDim. It should be noted however, that all three previously mentioned constants are 3 dimensional structures with three fields — x, y, z. For simplicity, the implementation will only use the x field to identify a thread inside a CUDA block.

There are also limitations on how many threads can be launched. Each CUDA block has a limited amount of shared memory and registers given by the hardware and the resources need to be divided between threads. For this reason, on the current GPUs, the number of threads per block is limited to 1024 [6].

#### 2.2.2 Memory hierarchy

When accessing memory while programming with CUDA, it is necessary to differentiate between GPU memory and CPU memory. CPU memory can be allocated using malloc or new, but to allocate memory on GPU, CUDA API has to be used. An allocating operation returns a pointer to the first available memory address. A problem arises when pointers to GPU and CPU memory are mixed and not differentiated. Memory in GPU lies in a different address space than CPU memory, as such, accessing a GPU memory from CPU can lead to segmentation fault. The same thing happens when a CUDA thread tries to access CPU memory. To access a GPU variable from CPU, first, the block of memory needs to be copied from GPU to CPU. Similarly, to pass a CPU variable to a GPU kernel, the variable has to be copied into GPU.

Each thread in a kernel has access to many kinds of memory, each with different access speed and size, and it is the programmer's responsibility to structure the program in a way that maximal throughput is achieved. At the top level, all running threads have access to global memory. Access to global memory is very slow and read/write operations should be minimized for best performance. Still, the use of global memory is inevitable because the input data has to be stored somewhere during kernel launch. Because of this, CUDA devices enable some optimization for the developer. One of the fundamental access patterns is coalesced read and write. When a warp accesses memory, the device groups up the operations into one or more transactions depending on the distribution of the memory addresses accessed [6]. Failing to group addresses can lead to serialization of this transaction and can degrade the performance of the program.

Every block has a faster local memory labeled as shared. This on-chip memory is visible to every thread in the same block and can be used as usermanaged data cache [7]. There are two ways to allocate shared memory. The first type is statically allocated shared variables. All these variables are declared using static \_\_shared\_\_ keywords. The size of each static shared variable has to be known at compile time. The second way is with the use of extern \_\_shared\_\_ keywords. With the keyword extern, the programmer declares that the memory will be dynamically allocated during kernel creation. Dynamically allocated shared memory can be declared only once as an array. To declare multiple variables, the initial array has to be split using type casting and pointer arithmetic. To prevent data race, block synchronization should be performed after writing into shared memory to ensure changes are visible to other threads.

Every thread also disposes with a set of very fast registers visible only to the thread. Data from registers can be shared with other threads in the same warp using shuffle functions without the use of shared memory. The number of registers available to the thread is limited by the architecture of the GPU and the compiler tries to minimize the amount of registers used by the block.

#### 2.2.3 Thread Synchronization

The CUDA API enables multiple means to synchronize CUDA threads. The first and most important synchronization is between kernel launches. A kernel launch starts from the CPU and until all threads are done, no other kernel is executed at the same time. This call is nonblocking for the host device, meaning the control is returned right back to CPU, but the work does not have to be executed on the GPU yet. This allows the CPU to push tasks to GPU rapidly and the GPU will perform the tasks in the correct order whenever the hardware is not occupied and ready to be used. To explicitly block the host until all GPU works are done, the programmer has multiple options. One solution is to call cudaDeviceSynchronize(). This function waits until all tasks on GPU are done and returns an error code if anything failed, otherwise cudaSuccess. Another way to synchronize host and device is to copy memory between these two platforms.

On the lowest level, some CUDA threads are implicitly synchronized on the hardware level due to the execution model. CUDA threads are executed in groups of 32, also known as warp. Warp size is important because during any instance, all threads within warp execute the same instruction (if warps do not diverge because of branching). This approach of execution is labeled as SIMT (single instruction multiple threads) architecture. When warps diverge, it is necessary to stop the warps that take a different branch path and only allow a subset of threads to execute the instruction. This divergence leads to a performance penalty and diverging threads should be kept to minimum.

To implicitly synchronize threads, the CUDA programming model provides a simple barrier function implemented as \_\_synchthreads(). It is important to note that this function can only synchronize threads within the same CUDA block. Upon calling this function, the thread is blocked and has to wait for all the other threads in the same CUDA block to call \_\_synchthreads() as well. Once all threads have called the function, all blocked threads are released.

The use of synchronization in a block is to ensure that all critical sections are handled properly and shared memory is properly updated and can be used by other threads, i.e. the data that a thread holds need to be given to another thread. The CUDA API also supports warp **shuffle** operations. These sets of functions allow active threads in a warp to exchange data with the use of registers and are available to devices with compute capability 3.x or higher [6]. With this, data can be moved between threads in a warp without having to stop other threads with synchronization and this approach is generally much faster than writing into shared memory and then calling **\_\_synchthreads()**.

If multiple CUDA blocks need to be synchronized, the best option is to store the data on hand into global memory, end the kernel and synchronize through CPU. Lastly, start a new kernel to continue where the last kernel stopped. This solution works on all CUDA enabled GPUs but on newer devices, the CUDA API introduced the concept of cooperative groups [6]. This feature allows the programmer to synchronize threads across blocks without having to end the kernel and inside a CUDA block, it provides a mean to synchronize threads with finer granularity than \_\_synchthreads(). The only drawback is that this feature is only available on GPUs supporting CUDA 9 and higher. As such, this feature was not used in the implementation and only the basic synchronization means were used.

To ensure that operations on global memory are executed deterministically, atomic operations were used. To demonstrate how they work, only atomicAdd will be described. There are also other atomic operations, but they all work similarly. The function atomicAdd takes a memory address and a value as parameter. It atomically adds the value to the address and returns the old value that lied in memory. When two threads add to the same address at the same time, the operation is performed in sequence, meaning one of the threads will have to wait until the first thread finishes the operation before atomicAdd can be executed again. The use of atomic operations should be minimized to gain the best possible performance.

#### 2.2.4 CUDA dynamic parallelism

CDP or CUDA dynamic parallelism is an extension of the CUDA API that allows the programmer to launch new kernels within the kernels themselves. This approach is only available to devices with compute capability of 3.5 and higher [6]. By default, only two levels of kernel launch recursion are allowed and to enable deeper recursion, max depth has to be explicitly set on host before kernel launch. With each recursive kernel launch, more memory has to be set aside for parent-child synchronization. Because of this limitation, most algorithms using CDP are memory bound.

#### 2.3 TNL

TNL is an open-source library that helps with the development of efficient numerical solvers. The library is mainly written in C++ and uses templates and other tricks to give the programmer a user-friendly interface. TNL also provides support for modern hardware, such as multicore CPUs, GPUs, and distributed systems. One of the core concepts of TNL is unifying the interface of data structures and algorithms for different memory spaces [1].

#### 2.3.1 TNL data structures

TNL contains some very useful structures to store data, one of which is TNL::Containers::Array. The class allows the user to create array-like structures to store information without having to implement memory allocation and deallocation. To create data in GPUs, the memory has to be allocated using CUDA API. This can lead to a lot of coding just to allocate memory, initialize and then deallocate at an appropriate time. Furthermore, every GPU operation has to be checked as failed function calls from CUDA API are not caught explicitly. All allocations and deallocations are handled in the constructor and destructor of the object using RAII [1] and only a high level interface is accessible to the user.

The Array class exposes some public methods allowing data reading and modification. To access memory, Array::getElement can be used. This method guarantees that the element is returned even if called from the wrong address space (i.e. Array holds data in GPU and the CPU fetches the data). Similarly, Array::setElement can be used to modify an element and the method guarantees correctness, no matter which device called the method.

Array also implements operator[], allowing the developer to access to the elements as if it were a regular array of elements. The operator returns a reference to the element, as such, calling the method from host for data allocated on device (or vice versa) leads to segmentation fault (on the host system) or broken state of the device [1].

```

1 ArrayView<int, Device> view = ...;

2 auto addLambda = [=]_cuda_callable__(int i, int j)

3 {return view[i] + view[j];}

```

Listing 1: Example of a lambda capturing a View. The lambda adds two values from Array.

#### 2.3.2 TNL View structures

To create efficient algorithms, memory operations — such as copying — should be kept to minimum. To move Array around, there are two efficient solutions. One is to capture the object by reference. This approach works well when the object is needed in the same device, but when launching a kernel, all parameters need to be captured by value. Another problem arises when lambdas are used. To create a lambda callable in kernel, all variables need to be captured by value. This leads to a lot of unnecessary copying of data and the performance is greatly degraded. All these problems stem from the fact that CPU memory and GPU memory are separate and referencing data from the wrong memory space can lead to failure of the program.

The other solution, and the one used in TNL, relies on binding the internal pointer and wrapping it in another class. This shallow copy of Array is labeled as ArrayView and implements the same methods as the original class. Creation and copying of ArrayView is very fast because only the pointer and the size of the array are passed around.

#### 2.3.3 Lambdas

CUDA kernels support the use of C++ lambdas and these user defined functions can be used in many general templated functions. CUDA lambdas, to be callable from GPU, need to have \_\_device\_\_ specifier. The TNL library unifies both \_\_host\_\_ and \_\_device\_\_ specifiers under the \_\_cuda\_callable\_\_ macro. To give an example, in Listing 1, the piece of code creates a lambda that adds two elements from a view. Lambdas created in CPU and called in GPU also can not capture variables by reference because of difference in memory address space, as such all variables need to be captured by value.

#### 2.4 Notation

In this work, the goal of the algorithms is to sort a sequence. A sequence a containing  $(a_1, a_2, a_3 \dots a_n)$  will be used as  $a[1 \dots n]$ . Element at position i is denoted as  $a_i$ . To concatenate sequences  $a[i \dots j]$  and  $a[k \dots l]$ ,  $a[i \dots j, k \dots l]$  will be used.

For algorithms, this thesis will also provide information about how long the implementation will run. The standard notation for time and space complexity is the asymptotic notation [8] and this notation will also be used in this thesis. An algorithm that needs at most n operations that take constant time is denoted as O(n). If exactly  $n \log n$  operations are needed —  $\Theta(n \log n)$ .  $\Omega(n^2)$  will be used when the algorithm needs at least  $n^2$  operations.

#### 2.5 Sorting problem

In this thesis, the goal is to sort data of arbitrary type. As such, only algorithms using a binary operator < will be considered. The comparison operator is a function that answers for every two elements  $a_i$ ,  $a_j$  whether <, > or = is true [8].

The sorting problem is about reordering the input in such a way that  $a_i < a_{i+1}$  or  $a_i = a_{i+1}$  for  $1 \le i < n-1$ . There are many types of sorting algorithms and each has a different property. As stated in [8], the most notable property that a sorting procedure can have is:

**Definition 2.1.** Let  $a_i$ ,  $a_j$  are equal. Also, let  $a_{i'}$  is the new position of  $a_i$  and  $a_{j'}$  is the new position of  $a_j$  after sorting. A sorting algorithm is stable if  $i \leq j$  then  $i' \leq j'$ .

**Definition 2.2.** A sort algorithm is in-place if the amount of memory needed to move the elements is constant. An auxiliary array to store the elements temporarily is allowed, but only a constant number of elements can be outside the input array.

#### 2.5.1 Single thread limitation

For comparison-based sorting algorithms, the best deterministic implementation will work in time  $\Omega(n \log n)$  [8] for the worst input. To gain any real speed-up, there are a few options that come to mind. One solution is to implement an algorithm that works in time  $\Theta(n \log n)$  but has a small multiplicative constant. Another solution is to use a faster CPU that can execute instructions faster. Both of these solutions are still limited by the theoretical time complexity.

To gain theoretical speed-up, at least one of the constraints needs to be broken. One of which is using a non-comparison based sorting algorithm. A representative of such algorithm is Radix sort or Counting sort [8]. These solutions are not ideal because they cannot sort non-numeric values.

The solution introduced by this thesis breaks the deterministic constraint and parallelization of the algorithm will be done to sort faster than  $O(n \log n)$ .

#### 2.5.2 Overview of existing algorithms

For CPU, many efficient sorting algorithms have been implemented and almost any numerical or standard library contains a sort function. For C++, the standard is std::sort from the libstdc++ library. The sorting algorithm selected in the library comprises of two algorithms — Introsort is used on a big input and then the algorithm switches to Insertion sort once the input is small enough. To give an example for other languages, Java 7, Python, Swift, and Rust, to name a few, implement Timsort [9]. This algorithm uses Merge sort and Insert Sort. As shown, these highly optimized sorts in the libraries all have one thing in common, in the first phase, a more complex method is used to preprocess a big input and then a simpler procedure is used to finish the sorting on smaller subsequences.

For parallel implementation, the goal of the algorithm is not only to have a good time complexity but a big bottle neck comes from how memory is accessed. A major factor that influences overall time needed to sort comes from the limited bandwidth of the GPU [10]. The main optimizations that can be done to improve run-time usually are based on memory access patterns and efficient use of faster memory. This is also recommended by the CUDA Programming Guide [6] as the most important aspect to gain speed-up.

The CUDA toolkit comes with a library supporting various operations on GPU called thrust [5]. This templated library contains a sorting function that can be run on either CPU or GPU. Internally the function implements Radix sort, one of the most popular sorting algorithm for GPU [10]. Another popular parallel sorting algorithm is Bitonic sort [11]. Bitonic sort belongs to the family of so called *sorting network* algorithms. Algorithms from this group are easy to implement as it is possible to map the network directly to a GPU kernel [10]. A very natural approach to parallelizing sorting involves reducing a big problem to smaller problems and recursively (and in parallel) process newly created buckets. This solution was presented by Cederman et al. in their GPU-Sort paper [3] that uses Quicksort to partition a sequence in parallel on GPU. Later on, Manca et al. [4] published their optimization of GPU-Sort for CUDA devices.

In this thesis, Quicksort and Bitonic sort will be implemented. Both of them are comparison based algorithms that only need a comparator defined. This allows for the data type to be of arbitrary type.

# Chapter 3

### **Bitonic Sort**

#### 3.1 The Bitonic sort algorithm

Bitonic sort was first introduced by K. E. Batcher in 1968 [11]. It is a comparison-based sorting algorithm that uses multiple layers of sorting networks to sort the whole input sequence. To understand the algorithm, it is necessary to define the following terms.

**Definition 3.1.** A sequence is bitonic if it is a concatenation of two monotonic sequences, one ascending and the other descending. Furthermore, the sequence is still bitonic, even if we split the sequence anywhere and interchange the sequences.

**Definition 3.2.** Bitonic merge is an operation that transforms a bitonic sequence into a monotonic sequence.

With these definitions, the sorting process is simple: split the input array in two parts, sort one part recursively in one direction and the other part in a different direction. Because the two parts are next to each other, a concatenation operation is not needed and by definition, the input is now bitonic. Then Bitonic merge is used to transform the bitonic sequence into a monotonic one and the input is sorted. The operation is called Bitonic merge because it merges two monotonic sequences and creates a bigger monotonic sequence.

*Example* 3.1. Any sequence of length 1 is bitonic, additionally any sequence of length 2 is also bitonic. The first element creates an ascending monotonic sequence of length 1 and the second element creates a descending monotonic sequence.

Furthermore, any sequence of length 3 is also bitonic. Any two neighbouring elements create a monotonic sequence and the leftover third element can be either ascending or descending depending on the need. *Example* 3.2. a = (1, 2, 4, 5) is a bitonic sequence. The subsequence (1, 2, 4, 5) is ascending and the descending part is of length 0. Another way to split the input can be (1, 2, 4) and (5) where the first part is ascending and the second part is descending.

*Example* 3.3. a = (3, 4, 6, 5, 0, 2) is a bitonic sequence. First, split the sequence a into (3, 4, 6, 5) and (0, 2) and interchange them, creating a' = (0, 2, 3, 4, 6, 5). The sequence a' is bitonic which means the original a was also bitonic.

Example 3.4. a = (3, 4, 6, 5, 0, 5) does not create a bitonic sequence.

#### 3.1.1 Bitonic merge

**Theorem 3.1.** Let a[1...2n] be bitonic sequence. Let  $d_i = \min(a_i, a_{i+n})$ and  $e_i = \max(a_i, a_{i+n})$  for  $1 \le i \le n$ . Then both d[1...n] and e[1...n] are bitonic. Also,  $\max(d[1...n]) \le \min(e[1...n])$ . We call this operation Bitonic split.

The merging operation is described in [11]. To transform a bitonic sequence into monotonic, Bitonic split is repeatedly performed on the input. This operation splits the input into two bitonic sequences, one holding n smaller elements while the other holds n bigger elements. This operation is then recursively applied to each of the newly created bitonic sequences until the input is of size 1. The original input is now monotonic.

To prove Theorem 3.1, some definitions and lemmas will be needed first.

**Definition 3.3.** A left cyclic shift is an operation that reorders the input sequence a[1...n] into a[2...n, 1]. Similarly, a right cyclic shift moves all elements by 1 to the right, creating a[n, 1...n - 1].

Formally, left cyclic shift can be written as

$$a_i' = \begin{cases} a_{i+1} & i < n \\ a_1 & i = n \end{cases}$$

and right cyclic shift as

$$a_i' = \begin{cases} a_n & i = 1\\ a_{i-1} & i > 1 \end{cases}$$

Remark 3.1. Splitting a sequence of length 2n into 2 sequences of length |k| and |l|, such that 2n = |k| + |l|, and interchanging them can be seen as performing left cyclic shift |k|-times or right cyclic shift |l|-times.

**Lemma 3.1.1.** Performing a right cyclic shift on a[1...2n] also cyclically shifts d[1...n] and e[1...n]. The sequences undergo the same change when left cyclic shift is applied.

*Proof.* For every element  $a_i$ , there exists exactly one other element that is n positions away (meaning the paired element is  $a_{i+n}$  or  $a_{i-n}$ ). The pair is not broken up even after cyclically shifting  $a[1 \dots 2n]$ .

Therefore, it is possible to cyclically shift the input until

$a_1 \leq a_2 \leq \ldots \leq a_j \geq a_{j+1} \geq \ldots \geq a_{2n}$

$a_j$  is the global maximum of the input and  $a[1 \dots j]$  is increasing and  $a[j \dots 2n]$  is decreasing. This satisfies the bitonic property and does not change the maximum value of  $d[1 \dots n]$  nor minimum of  $e[1 \dots n]$ .

**Lemma 3.1.2.** Flipping the input  $a[1 \dots 2n]$  into  $a[2n \dots 1]$  does not affect the bitonic property. After flipping,  $d[1 \dots n]$  becomes  $d[n \dots 1]$  and  $e[1 \dots n]$  is also flipped.

Using Lemma 3.1.2, it is sufficient to prove Theorem 3.1 for case  $a_1 \le a_2 \le \ldots \le a_j \ge a_{j+1} \ge \ldots \ge a_{2n}$ , where  $n < j \le 2n$ .

Now with all the necessary conditions set, Theorem 3.1 can be proven.

*Proof.* Let a[1...2n] be the bitonic sequence that needs to be merged by Bitonic merge. There are 2 cases that can happen.

Let  $a_n \leq a_{2n}$ , then for  $1 \leq i \leq n$ ,  $a_i \leq a_{i+n}$  so  $d_i = \min(a_i, a_{i+n}) = a_i$  and  $e_i = \min(a_i, a_{i+n}) = a_{i+n}$ .  $d[1 \dots n] = a[1 \dots n]$  and it has been proposed that the sequence is ascending in this part, therefore  $\max(d[1 \dots n]) = d_n = a_n$ .  $e[1 \dots n] = a[n+1 \dots 2n]$ , furthermore,  $\min(e[1 \dots j-n]) = e_1 = a_{n+1}$  because this part is increasing and  $\min(e[j - n \dots n]) = e_n = a_{2n}$  as this part is decreasing. In total,  $\min(e[1 \dots n]) = \min(e_1, e_n) = \min(a_{n+1}, a_{2n})$ .

Together  $\max(d[1 \dots n]) = a_n \leq \min(a_{n+1}, a_{2n}) = \min(e[1 \dots n])$ . If  $a_{n+1}$  is minimum then the inequality is still true because  $a[1 \dots j]$  is increasing, otherwise  $a_{2n}$  is minimum and the inequality is also true because of the initial proposition.

Let  $a_n > a_{2n}$ , then there exists such a  $k : j \le k \le 2n$ , that  $a_{k-n} \le a_k$  and  $a_{k-n+1} > a_{k+1}$ . This stems from the fact that  $a[j - n \dots j]$  is increasing while  $a[j \dots 2n]$  is decreasing.  $d_i$  and  $e_i$  are created as follows:

and

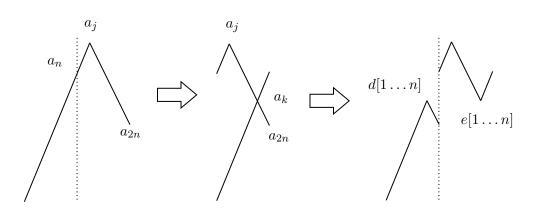

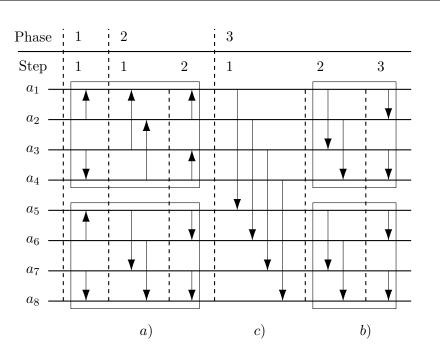

Figure 3.1: One step of Bitonic merge where  $a_n > a_{2n}$ .

The first part  $d[1 \dots k - n] = a[1 \dots k - n]$  is ascending and the second part  $d[k - n + 1 \dots n] = a[k + 1 \dots 2n]$  is descending, this satisfies the bitonic property.  $e[1 \dots j - n] = a[n + 1 \dots j]$  is ascending,  $e[j - n + 1 \dots k - n] =$  $a[j + 1 \dots k]$  is descending and  $e[k - n + 1 \dots n] = a[k - n + 1 \dots n]$  is ascending. Let us also notice that it is possible to perform right cyclic shifts on  $e[1 \dots n]$ to create  $e[k - n + 1 \dots n, n + 1 \dots k - n] = a[k - n + 1 \dots k]$  which is in part ascending until  $e_{j-n} = a_j$  and then descending till the end. Sequence  $e[1 \dots n]$ therefore also satisfies the bitonic property.

After analyzing,  $\max(d[1...n]) = \max(d_{k-n}, d_{k-n+1}) = \max(a_{k-n}, a_{k+1})$ and  $\min(e[1...n]) = \min(a[k-n+1...k]) = \min(a_{k-n+1}, a_k)$ . If  $d_{k-n} = a_{k-n}$ is the maximum, then  $a_{k-n} \leq a_{k-n+1}$  because this part is ascending and  $a_{k-n} \leq a_k$  due to initial proposition. Else  $d_{k-n+1} = a_{k+1}$  is maximum, then  $a_{k+1} \leq a_{k-n+1}$  due to initial proposition and  $a_{k+1} \leq a_k$  because the sequence is descending in this part. In all 4 cases, the inequality holds.  $\Box$

#### 3.1.2 Sorting in-place

To split the input, the sequences d[1...n] and e[1...n] do not need to be allocated. It is sufficient for d[1...n] = a[1...n] and e[1...n] = a[n+1...2n]. With this, it is only necessary to compare  $a_i$  and  $a_{i+n}$  and swap the elements if needed.

Formally  $d_i = a_i = \min(a_i, a_{i+n})$ ,  $e_i = a_{i+n} = \max(a_i, a_{i+n})$  for  $1 \le i \le n$ . Here the min function uses the < comparator to determine which element is smaller, similarly max returns the bigger element of the two. These 2 operations can furthermore be optimized to compare  $a_{i+n} < a_i$  first and only swap them if they are in the wrong order.

#### 3.1.3 The recursive algorithm

The resulting algorithm can be seen in Algorithm 3.1.1 and Algorithm 3.1.2. To sort the input, BitonicSort is recursively called twice, once on  $a[1 \dots n]$  and the second time on  $a[n + 1 \dots 2n]$ . It should be noted that one of the sequences needs to be sorted in the opposite direction in order for them to create a bitonic sequence at the end.

The last operation that needs to be done is **BitonicMerge**. The function implements Bitonic split — moves n smaller elements into the first half and n bigger elements into the second half. The two resulting subsequences are also bitonic. Then **BitonicMerge** is called on both the subsequences.

| Algorithm 3.1.1: Recursive Bitonic sort                    |

|------------------------------------------------------------|

| <b>Input:</b> array $a[12n]$ , sort ordering ordering      |

| 1 if $2n = 1$ then                                         |

| 2 return                                                   |

| <b>3</b> BitonicSort $(a[1n], \text{ opposite } ordering)$ |

| 4 BitonicSort $(a[n+12n], ordering)$                       |

| <b>5</b> BitonicMerge $(a[12n], ordering)$                 |

Algorithm 3.1.2: Recursive Bitonic Merge

**Input:** array  $a[1 \dots 2n]$ , sort ordering ordering

```

1 if 2n = 1 then

\mathbf{2}

return

3 for i from 1 to n do

if ordering is ascending then

\mathbf{4}

if a_{i+n} < a_i then

\mathbf{5}

swap(a_i, a_{i+n})

6

else if ordering is descending then

\mathbf{7}

if a_i < a_{i+n} then

8

| \operatorname{swap}(a_i, a_{i+n}) |

9

10 BitonicMerge(a[1...n], ordering)

11 BitonicMerge(a[n+1...2n], ordering)

```

#### 3.1.4 Time complexity

Bitonic split creates the sequences  $d[1 \dots n]$  and  $e[1 \dots n]$ . For each comparison, two elements from  $a[1 \dots 2n]$  are processed so a Bitonic split is of time  $\frac{n}{2} = \Theta(n)$ . Bitonic merge performs one Bitonic split and then recursively calls itself twice (once on d[1...n] and once on e[1...n]). From this, we get  $T(n) = \frac{n}{2} + 2T(\frac{n}{2})$ , using Master theorem, the result is  $T(n) = \Theta(n \log n)$ .

To sort the whole sequence, first the input is split in half and Bitonic sort is called on each half, then merge operation is called. The complexity is  $T(n) = 2T(\frac{n}{2}) + n \log n = \Theta(n \log^2 n)$  [12].

#### 3.1.5 Sorting not aligned sequences

So far, the Bitonic sort that has been introduced could sort only sequences of length  $n = 2^m$ . To sort sequences of any length, the algorithm has to be modified. There is the trivial solution [13] of extending the sequence to the length of the next closest power of 2 and fill the missing elements with maxvalue (min-value when sorting in descending order). However, such a solution is not very efficient for big inputs. First, a new temporary array of length  $2^k \ge n$  has to be allocated, the whole input has to be copied into auxiliary memory, sorted there and then copied back without padding elements. With temporary memory, the option to sort in place is lost and the space complexity becomes  $\Theta(n)$ . However, for smaller elements this approach might be more efficient due to low overhead compared to the next introduced solution.

The Bitonic merge operation only requires the input to be bitonic and it does not matter whether the sequence is a concatenation of an ascending and then descending sequence or descending and then ascending sequence. Using this, the change is as follows [13]: let  $n \ge 1$  be the length of input and k is the biggest power of 2 that still smaller than n (formally  $k < n \le 2k$ ), then split the original sequence into  $a[1 \dots k]$  as left part and  $a[k+1 \dots n]$  as right part. Sort the left part in descending order and the right part in ascending order. Lastly, call Bitonic merge on the newly created bitonic sequence.

Let us notice that the left part is of size k which is a power of 2. Sorting this part can proceed as normal. For the right part, whenever  $a_i$  — where i > n — is needed, a max-value (if sorting in descending order, then minvalue is used) can be substituted in. In this situation, no swap is needed and the max-value does not have to exist physically in memory. This approach is called virtual padding. With virtual padding, only the direction of sorting has to be minded during calculation and the algorithm does not lose the property of being in-place nor is the time complexity degraded.

# 3.2 Parallel algorithm

To implement an efficient parallel version of Bitonic sort, the algorithm has to be modified a little. Instead of using recursion, it is better to build the monotonic sequences in iterations [11]. The algorithm first creates monotonic sequences of length 1, this is trivial. Now the input a[1...n] consists of nmonotonic sequences. In the next step, Bitonic merge is used on two neighbouring monotonic sequences, each with length k. This creates new monotonic

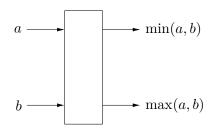

Figure 3.2: Sorting network comparator for two elements, adopted from [11]. The comparator sorts in ascending order.

sequences of length 2k. To be able to use Bitonic merge, the two monotonic sequences had to be sorted each in different directions (so they create a bitonic sequence). It is also necessary to merge the correct way (ascending or descending) so that the next step will have two oppositely sorted sequences to merge again.

#### 3.2.1 Sorting network

Bitonic sort, when used iteratively, can be represented as a sorting network. A sorting network, as defined in [14], is a hardware sorter circuit. The basic element of a sorting network is a comparator. A comparator has two input lines and two output lines. It receives two numbers on its input lines, compares them, and outputs the maximum on its higher output line and the minimum on its lower output line. By interchanging the output lines, a comparator that sorts in descending order can be gained. A simple scheme of a comparator is shown in Figure 3.2.

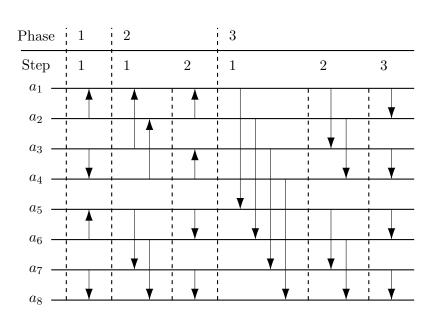

To sort the input, the comparators need to be connected in such a way that they permutate the input correctly and send the elements in the correct order to the output. The sorting network in Figure 3.3 shows a way to connect comparators to simulate Bitonic sort. The network consists of multiple layers which are called steps and multiple steps are grouped into phases. The strength of sorting networks lies in the fact that it can be implemented on the hardware level to run parallel. Bitonic sort due to its recursive property is very convenient for mass production of the hardware. A large bitonic sorter can be created by connecting smaller Bitonic sorters.

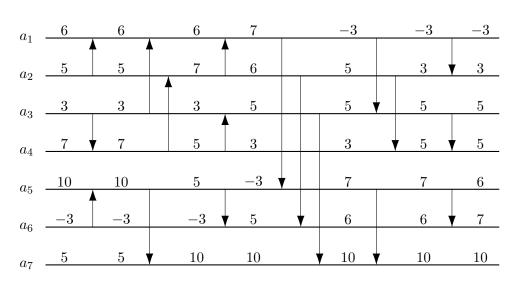

*Example* 3.5. In this example, only phase 2, step 1 and 2 of Bitonic merge will be demonstrated. The steps will be described in text and a general scheme with a bitonic sorter will be shown in Figure 3.4.

Let input  $a[1 \dots n] = ((6,5), (3,7), (10,-3), (5))$  be a concatenation of 4 monotonic sequences.

**Setup:** The current monotonic length is 2 (the last part (5) is an exception as the input is not aligned into power of 2). In the beginning, concatenate two neighbouring monotonic sequences to create a bitonic sequence twice as

Figure 3.3: Bitonic sorting network for 8 elements, adopted from [13].

big. ((6,5), (3,7)) is bitonic and Bitonic split can be applied. The same thing happens to ((10, -3), (5)). The sequence ((10, -3), (5)) is not aligned and needs to sorted in ascending order, this forces the left part ((6,5), (3,7)) to be sorted in descending order.

**Phase 2, step 1:** The elements 6 and 3 are compared first, maximum is sent through the top line and minimum though bottom line, same with 5 and 7. This creates the sequence (6,7,3,5). Here d[1...k] = (6,7) and e[1...k] = (3,5). At the same time, 10 and 5 are compared and swapped as they are in the wrong order. -3 does not have a partner and is not swapped. After Bitonic split, the input becomes (6,7,3,5,5,-3,10). It should be noted that all comparisons and swaps done in this step were independent and can be performed in parallel.

**Phase 2, step 2:** Each bitonic sequence is now of length 2. To demonstrate, the input can be split as ((6,7), (3,5), (5,-3), (10)). Elements 6 and 7 are still part of a sequence that needs to be sorted in descending order and therefore are in wrong order and need to be swapped. Same with (3,5). (5,-3) needs to be sorted in ascending order and are also swapped. (10) does not have a partner and is not swapped.

The result then turns into ((7, 6, 5, 3), (-3, 5, 10)) and the sequence is ready for another application of Bitonic merge which will turn the input into 1 monotonic sequence.

As demonstrated in Example 3.5, a Bitonic merge phase consists of multiple Bitonic splits. All swaps in one Bitonic merge step are independent and can be performed in parallel.

Figure 3.4: Sorting example 3.5 with a Bitonic sorting network.

#### 3.2.2 Time complexity of parallel implementation

If there are O(n) threads available to work during each step, it is possible to perform all  $\left\lceil \frac{n}{2} \right\rceil$  swaps of a Bitonic split in O(1) as all comparisons are independent. The time complexity then collapses to the number of phases and steps. After the first phase, each part is a sorted sequence of length 2. After second phase, the length is 4. After k phases, each part is a monotonic sequence of length  $2^k$ . Thus, the number of phases is  $O(\log_2 n)$ . The first step of phase i will split a bitonic sequence of length  $2^i$  into 2 bitonic sequences, each with length  $2^{i-1}$ . Bitonic split is then applied on each of the newly created bitonic sequences until they are of length 1. Therefore, each phase needs  $\log_2 2^i = i$  steps.

Together, the complexity of bitonic sort is

$$\sum_{i=1}^{\log_2 n} i = \log_2 n \frac{1 + \log_2 n}{2} = O(\log^2 n)$$

# 3.3 Existing implementations

Bitonic sort for GPU has been studied intensively due to its simplicity [10] and has been implemented by many researchers. Despite this, most of them are implemented to sort only integer types and can only handle aligned sequences. A very good and optimized implementation of Bitonic sort is available in the CUDA SDK [2], but this implementation can only sort unsigned integer types and the interface forces the user to sort key-value which greatly reduces the performance when keys are also values. The goal is to implement a Bitonic

```

ArrayView<double, Device::Cuda> view = ...;

1

auto Fetch = [=]__cuda_callable__(int i){return view[i];};

2

auto Cmp = [=]__cuda_callable__(const double & a,

3

const double & b)

4

\{return a < b;\};

5

auto Swap = [=]__cuda_callable__(int i, int j) mutable

\mathbf{6}

{TNL::swap(view[i], view[j]);};

7

bitonicSort(0, view.getSize(), Fetch, Cmp, Swap);

8

```

Listing 2: Example of fetch and swap version of Bitonic sort with lambdas.

sort that can be called both from CPU and GPU. The function will not be restricting, meaning the data type will be templated and there will be no restriction on the size of the input.

# 3.4 Implementation of Bitonic sort with CUDA

On the highest abstract level, there are two available interfaces of Bitonic sort. The main one is BitonicSort(ArrayView<Value, Device>). This function takes an ArrayView as input and will sort the input using Bitonic sort on GPU. As default, the comparator for two elements from the input is operator< and as such will sort in ascending order. Same as with std::sort, an overloaded version of this function with custom comparator is available. It should be noted that the comparator has to be callable from device, because of this, the function or lambda has to have \_\_device\_\_ specifier. With a different comparator, it is possible to sort any data type ascending or descending.

To sort key and value types of data, the programmer has two options: to zip the key and value into one structure and then use a custom comparator, or to use the BitonicSort interface with fetch and swap. The second approach allows the user to sort any type of indexed container (arrays, vectors, lists etc.) in-place without having to create additional structure to zip key-value. The function needs five values — first and last index of the structure that needs to be sorted, a fetch function that returns the element on i-th position, a compare function that compares two elements and a swap function that swaps elements on i-th and j-th position. The swap function allows the user not only to swap the fetched elements but also perform other operations (such as swap values in another structure or do other calculations). Because swap takes non const values as argument and changes memory, if used as lambda, the keyword mutable has to be used, on top of \_\_device\_\_ specifier. This approach is universal for almost any data container, but the performance is greatly reduced because all operations have to be carried out in global memory. An example on how to call the function is provided in Listing 2.

#### 3.4.1 Host side

To sort the input, Bitonic merge has to be repeatedly called, each time with different parameters. In section 3.2, the algorithm was described and pointed out how many times Bitonic merge needs to be called during *i*-th phase. The Algorithm 3.4.1 shows that the iterative approach can be easily implemented with two nested for loops.

Algorithm 3.4.1: Bitonic sort kernel launchInput: array  $arr[1 \dots n]$ 1  $gridSize, blockSize \leftarrow$  calculate optimal configuration2 for  $i \leftarrow 1$  to  $\lceil \log n \rceil$  do3  $\left[ \begin{array}{c} \text{for } j \leftarrow i \text{ to } 1 \text{ do} \\ 4 \end{array} \right] \left[ \begin{array}{c} \text{BitonicMerge}_{i,j} < gridSize, blockSize > (arr[1 \dots n]) \end{array} \right]$

The host side is mainly used to synchronize kernels inbetween kernel launches. Each kernel launch will start the swapping of a layer of a Bitonic sorting network. It is assumed that the number of threads available in GPU is at least half the size of the input sequence. Each block will be started with 512 or 256 threads and the theoretical maximum number of blocks that can be launched is  $2^{31} - 1$  [6]. To use up all threads, the input would have to have more than  $2^{40}$  elements and it is not assumed that such a big input will fit in the memory of a GPU.

In host, blockSize and gridSize is calculated and these two numbers are used for every kernel launch until the input sorted. Each CUDA thread is implemented to compare two elements and simulate a comparator in a step of a sorting network, as such, to sort a sequence with n elements,  $\lceil \frac{n}{2} \rceil$  threads will be needed in total.

To maximize shared memory usage, the number of threads per CUDA block is selected as 512 or 256. By default, 512 is used and 1024 elements are processed in every CUDA block, but if the data type is too large (some complicated structure), 256 can be used to reduce the memory consumption per block. If even  $256 \times 2$  elements cannot be copied into shared memory, then all operations will be executed in global memory with 512 threads per block.

#### 3.4.2 Device side

Each CUDA thread in Bitonic sort is implemented to simulate a comparator from Bitonic sorting network. The kernel consists of calculating which two elements need to be fetched, calculating whether the two elements need to be sorted in ascending or descending order and the last operation that needs to be done is comparing them and then execute swap on the elements if needed.

```

int i = blockIdx.x * blockDim.x + threadIdx.x;

int offset = bitonicLen / 2;

int s = (i / offset) * bitonicLen + (i % offset);

int e = s + offset;

```

Listing 3: Implementation of how the two compared elements by thread  $i - a_s$  and  $a_e$  — are calculated.

To calculate which two elements need to be accessed by a thread, the *global* thread id needs to be known and the current step and phase of the Bitonic merge. In the implementation, one of the parameters passed to the kernel is **bitonicLen**, this value indicates how long each bitonic sequence is in the input and directly corresponds to the phase and step of the Bitonic sort. Global id of the thread can be calculated (as shown in Listing 3) with just CUDA available thread variables (blockDim, blockIdx, threadIdx) and is labaled as i. These two values are then used to calculate the first element that will be used. The first element is on position **s** and the second element is on **e** = **s** + **bitonicLen/2**. These two values correspond to  $a_s = a_i$  and  $a_e = a_{i+n}$  introduced in the theoretical part.

#### 3.4.3 Calculating the direction of swap

A common operation that every thread calculates is whether the two compared elements should be in ascending or descending order. After *completing a phase*, the order of every two neighbouring monotonic subsequences should be alternating so they can create a bitonic sequence. In the implementation, it has been decided that every even subsequence will be sorted in descending order and every odd subsequence sorted in ascending order. The only exception is for the last two subsequences. As discussed in subsection 3.1.5, the implementation will use the version with virtual padding and it is important to sort the last subsequence — which can potentially be not aligned — in ascending order.

#### 3.4.4 Optimizations

To optimize Bitonic sort, shared memory will be used. Nevertheless, the use of shared memory is not the only optimization that can be done to gain speed-up. One of the tricks used in the implementation is based on bitwise operations. The modulo operator is very slow in GPUs and can be replaced with faster bitwise & under some circumstances. Whenever (i mod m) is calculated and m is a power of 2, the whole operation can be replaced with i&(m-1) [6].

Instruction change is not the only optimization that can be used in GPU. Another big improvement can be gained by reducing divergent threads in a warp. For this, a faster version of compare and swapped is used (Listing 4).

```

template <typename Value, typename CMP>

1

__cuda_callable__

2

void cmpSwap(Value &a, Value &b,

3

bool ascending, const CMP &Cmp)

4

{

\mathbf{5}

if (ascending == Cmp(b, a))

6

TNL::swap(a, b);

7

}

8

```

Listing 4: Implementation of fast compare and swap with templated parameters.

The comparison consists of checking the direction of swapping that is required and calling the Cmp function on two elements. Here, Cmp is just a lambda that replaces operator<. With this implementation, the check for ascending does not create a fork and only 1 call of Cmp is needed. It should also be noted that Cmp is called as b < a. This lambda call checks if the two elements are sorted in *descending* order.

#### 3.4.5 Shared memory in Bitonic Sort

Algorithm 3.4.2: Bitonic sort kernel launch with shared memory **Input:** array  $arr[1 \dots n]$ 1  $gridSize, blockSize \leftarrow$  calculate optimal configuration **2** bitoniSort1stPhase<gridSize, blockSize>(arr[1...n])**3** for  $i \leftarrow \log_2 blockSize + 1$  to  $\lceil \log n \rceil$  do for  $j \leftarrow i \ to \ 1 \ do$ 4 if  $2^{j} > 2 * blockSize$  then 5 bitonicMerge<sub>*i*,*j*</sub> < gridSize, blockSize > (arr[1...n])6 7 else bitonicMergeShared<sub>*i*,*j*</sub> < *gridSize*, *blockSize*> (*arr*[1...n]) 8 break 9

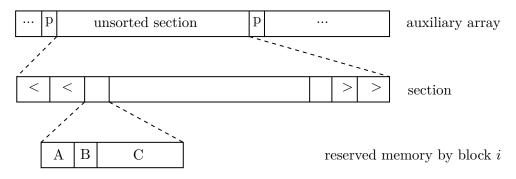

To maximize the usage of shared memory available to a CUDA block, Bitonic sort is implemented in three parts (Algorithm 3.4.2). The first optimization is used when a whole bitonic sequence can be copied into shared memory. In this case, the only synchronization that will be needed is blockwide synchronization. The function is labeled as **bitonicMergeShared** in the implementation. As seen (Figure 3.5, part b), a CUDA block accesses the same elements multiple times and thus can be processed in shared memory.

Figure 3.5: Display of shared memory usage for Bitonic sort with 8 elements and 2 CUDA blocks, each block having 2 threads:

- a) usage of shared memory in bitoniSort1stStepSharedMemory,

- b) usage of shared memory in bitonicMergeShared,

- c) comparison and swapping is done in global memory through **bitonicMerge**.

First, the elements are cached in shared memory, then the elements in shared memory are sorted using repeated application of Bitonic Merge. It is necessary to synchronize threads in the CUDA block after every merge to update the shared memory correctly. Once the elements in shared memory are sorted, they are copied back into global memory.

The second optimization is used right in the beginning. Instead of building the monotonic sequences iteratively, it is possible to create monotonic sequences of length blockDim.x\*2 directly in a CUDA block. Each CUDA block copies a part of the sequence into memory and sorts it completely in shared memory (Figure 3.5, part a). It is necessary for neighbouring CUDA blocks (their blockIdx differs by 1) to sort the subsequences in opposite directions so once block sort is done, the neighbouring monotonic sequences can be concatenated into a bitonic sequence. The whole procedure is done in bitoniSort1stPhase.

The last function is a regular Bitonic merge that accesses elements in global memory and only simulates one step of Bitonic sort (Figure 3.5, part c).

```

1 template <typename Value, typename CMP>

2 __device__

3 void bitonicSort_Block(ArrayView<Value, Devices::Cuda> src,

4 ArrayView<Value, Devices::Cuda> dst,

5 Value *sharedMem, const CMP &Cmp);

```

Listing 5: Interface of block Bitonic sort that uses shared memory. The function is callable directly from a CUDA kernel.

# 3.5 Bitonic sort from GPU

Bitonic sort was also implemented to be able to sort *from* GPU. These sets of functions were implemented so that the sort procedure could be called directly from a GPU kernel. The device function requires every thread in a block to call the **bitonicSort\_Block** function. The function has two overloaded versions. The first one uses shared memory to sort, as such, pointer to shared memory address has to be passed as parameter. It is also necessary for shared memory to be at least as big as the input array because the whole data will first be copied in shared memory back into global memory. We used this to our advantage and allowed in the implementation to copy the result into another array than the source array. This allow the function interface to be more flexible. The full signature of the function is shown in Listing 5.

The other overloaded version of the function with the same name also allows a CUDA block to use Bitonic sort directly from GPU but will not use shared memory. The Bitonic sort used in this version is in-place and executes all compares and swap in global memory.

CHAPTER 4

# Quicksort

# 4.1 The Quicksort algorithm

Quicksort is one of the fastest sequential comparison based algorithm in practice with optimal theoretical time complexity on average —  $O(n \log n)[8]$ . The pseudo code of the algorithm is shown in 4.1.1.

| Algorithm 4.1.1: Quicksort algorithm                                 |

|----------------------------------------------------------------------|

| <b>Input</b> : array $A[1 \dots n]$                                  |

| 1 if $n \leq 1$ then                                                 |

| 2 return                                                             |

| <b>3</b> $pivot \leftarrow$ select an element from $A[1 \dots n]$    |

| 4 $i \leftarrow \text{partition } A[1 \dots n] \text{ using } pivot$ |

| 5 quicksort $(A[1i])$                                                |

| 6 quicksort( $A[i+1n]$ )                                             |

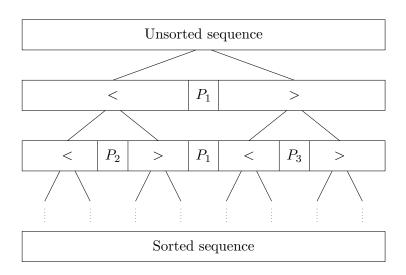

This basic idea of Quicksort was initially introduced in [15]. First, a partition procedure is applied on the input sequence. This operation moves all elements smaller than the pivot to A[1...i], all elements greater or equal to pivot into A[i+1...n]. There also exist versions of partitioning that split the array A[1...n] into three parts, the left part will hold elements smaller than pivot, the middle part will have elements equal to the pivot, and the right part will contain elements greater than the pivot Then Quicksort is recursively called on the left and then right part. This approach of problem solving where a big input is split into smaller problems is categorized as *divide and conquer* algorithm [8]. The amount of work needed afterwards depends on pivot selection. A general idea of how the memory is partitioned is shown in Figure 4.1.

#### 4. Quicksort

Figure 4.1: Recursive tree of Quicksort

#### 4.1.1 Partitioning algorithms

In Hoare's paper [16], the author suggested using two pointers that go against each other, whenever both elements are in wrong order, they are swapped. The process stops when i and j cross.

Algorithm 4.1.2: Hoare partition scheme

```

Input : array A, index p, index r

1 pivot \leftarrow A[p]

\mathbf{2} \ i \leftarrow p-1

3 j = r + 1

4 while True do

do

\mathbf{5}

j \leftarrow j-1

6

while A[j] \leq pivot;

7

8

do

i \leftarrow i+1

9

while A[i] \ge pivot;

\mathbf{10}

if i < j then

11

swap(A[i], A[j])

\mathbf{12}

else

13

return j

\mathbf{14}

```

Another partition scheme was introduced by Lomuto [17], this method of partitioning also uses two pointers, but this time they start from the beginning of the sequence. At any given iteration,  $A[p \dots i]$  will hold elements smaller

Algorithm 4.1.3: Lomuto partition scheme

Input : array A, index p, index r  $pivot \leftarrow A[r]$  $i \leftarrow p - 1$ 3 for j = p to r - 1 do  $\qquad if A[j] \le pivot$  then  $\qquad lif A[i] \le pivot$  then  $\qquad lif A[i] \le pivot$  then  $\operatorname{swap}(A[i+1], A[j])$ 8 return i + 1

than or equal to the pivot, A[i+1...j] will have elements greater than the pivot. The rest of the array still has not been processed.

The two previously shown implementations of partitioning work in-place and have a time complexity of  $\Theta(n)$ , this is also the best possible algorithm asymptotically. Every element needs to be compared with the pivot at least once to check if the relative order in memory is correct.

#### 4.1.2 Pivot Choice

With an inappropriate pivot, the load balance between the two newly created sections after partitioning can greatly degrade the performance. In the worst case, only one element gets processed — the pivot — and one of the sections holds the rest of the sequence. After each partitioning, the section that still needs to be sorted gets smaller by 1. This degrades the time complexity of the algorithm to  $\Theta(n^2)$ .

Ideally, the true median of the input is chosen as the pivot. Then the two sections are of equal size and the recursive tree will have  $\log_2 n$  depth. This best case gives the algorithm a  $\Theta(n \log n)$  time complexity [8].