## ASSIGNMENT OF MASTER'S THESIS

| Efficient concurrent memoization system    |

|--------------------------------------------|

| Bc. Viacheslav Kroilov                     |

| Ing. Daniel Langr, Ph.D.                   |

| Informatics                                |

| System Programming                         |

| Department of Theoretical Computer Science |

| Until the end of summer semester 2020/21   |

|                                            |

#### Instructions

Get familiar with the problem of concurrent hash tables intended for efficient use in multi-threaded applications.

Get familiar with the problem of memoization systems, i.e., software cache databases with limited capacity and support for automatic data removal.

Design and implement an efficient concurrent memoization system with a focus on scalability for higher thread numbers.

Conduct an extensive experimental study of the proposed solution by its comparison with existing solutions.

Include the proposed solution into an existing HPC application and evaluate its efficiency. For implementation, use C++.

#### References

Will be provided by the supervisor.

anousel.

doc. Ing. Jan Janoušek, Ph.D. Head of Department

doc. RNDr. Ing. Marcel Jiřina, Ph.D. Dear

Prague October 8, 2019

Master's thesis

## Efficient Concurrent Memoization System

Bc. Viacheslav Kroilov

Department of theoretical computer science Supervisor: Ing. Daniel Langr, Ph.D.

February 12, 2020

## Acknowledgements

I would like to thank my parents, Mikhail and Elena, for the constant support and love they give to me.

I gratefully recognize the assistance of Daniel Langr, Ph.D. and doc. Ivan Šimeček with my academic research.

Also I would like to thank Dr. Adnan Aziz, Tsung-Hsien Lee, Daria Doronina, Elizaveta Ulyanova, and Anna Vasilenko for the invaluable feedback they gave on early versions of this thesis.

## Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. In accordance with Article 46(6) of the Act, I hereby grant a nonexclusive authorization (license) to utilize this thesis, including any and all computer programs incorporated therein or attached thereto and all corresponding documentation (hereinafter collectively referred to as the "Work"), to any and all persons that wish to utilize the Work. Such persons are entitled to use the Work in any way (including for-profit purposes) that does not detract from its value. This authorization is not limited in terms of time, location and quantity.

In Prague on February 12, 2020

Czech Technical University in Prague Faculty of Information Technology © 2020 Viacheslav Kroilov. All rights reserved. This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its

Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

## Citation of this thesis

Kroilov, Viacheslav. *Efficient Concurrent Memoization System*. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2020. Also available from: (https://metopa.github.io/deferred\_lru/).

## Abstrakt

Automaticky memoizační systém - také softwarová cache - ukládá omezený počet prvků v paměti, které byly nedávno zpřístupněny a zrychluje tak následný přístup k nim. Least-Recently-Used (LRU) je populární strategie nahrazování prvků pro hardwarovou a softwarovou cache. Nicméně, její paralelní implementace má nízkou škálovatelnost v důsledku přeskupování seznamu, které je prováděno jak při vyhledávání tak při vkládání.

V této práci je představena nová paralelní softwarová cache DeferredLRU, která vychází z LRU strategie. Hlavním cílem návrhu byla škálovatelnost a efektivní využití na mnoha-jádrových sýstémech. Toho bylo dosaženo použitím jiného řešení ke sledování pořadí přístupu k prvkům. Toto řešení podstatně snižuje počet opětovných vložení prvků do seznamu, což je hlavním faktorem zpomalení u běžné LRU cache.

Výkonnost a hit-rate DeferredLRU jsou citlivé na nastavení konfiguračních parametrů. Díky vyladělnému nastavení parametrů pro specifické vstupy byl dosažen vyšší hit-rate než u běžné LRU cache ve všech testovaných případech. Relativní rozdíl byl až 7,8%.

Výkon DererredLRU byl porovnán s existujícími alternativami, včetně souvisejícíh implementací cache z projektů Intel TBB a Facebook HHVM. Testované implementace cache byly hodnoceny až do 32 vláken (na 16 HW CPU jádrech). Při 32 vláknech, DeferredLRU bylo rychlejší ve všech 16 testech. Pokud byly přístupy distribuovány mezi více malých cache z důvodu lepšího paralelizmu (tzv. binning), DeferredLRU bylo rychlejší v 11 z 16 případů a ve zbylých 5 byl výkon blízko nejlepšímu pozorovanému výsledku. DeferredLRU s binning přístupem bylo až 28,8 krát rychlejší na 32 vláknech ve srovnání s jedno-vláknovým výkonem.

**Klíčová slova** LRU cache, memoizace, paralelní datové struktury, paralelní výpočet, softwarová cache, souběžný výpočet, strategie nahrazování prvků, techniky lock-free programování, víceprocesové systémy

## Abstract

An automatic memoization system — also known as a software cache — stores a limited number of recently accessed elements and speeds up consequent accesses to them. Least-Recently-Used (LRU) is a popular replacement policy for hardware and software caches. However, its concurrent implementation suffers from high contention due to the list reordering performed both on lookup and insertion.

A novel LRU-inspired concurrent software cache, called DeferredLRU, is presented in this thesis. The main goal of the design was to make it scalable and suitable for many-core systems. These properties were achieved by using a different approach to tracking item access order. This approach substantially decreases the number of list reinsertions — the main factor of the contention in a regular LRU cache.

DeferredLRU throughput and hit-rate are sensitive to the meta-parameter setting. By fine-tuning meta parameters for specific inputs, it was possible to achieve higher hit-rate than of a regular LRU cache for every tested input. The relative difference was up to 7.8%.

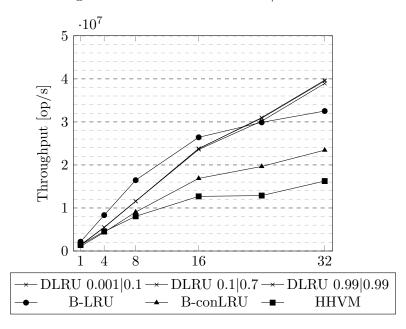

DeferredLRU performance was compared to existing alternatives, including corresponding caches from Intel TBB and Facebook HHVM projects. Tested caches were evaluated with up to 32 threads (on a 16 HW cores CPU). In 32 threads evaluation, DeferredLRU was faster in all 16 tests. When accesses were distributed among multiple smaller caches for better parallelism (this approach is called binning), DeferredLRU was faster in 11 of 16 tests and was close to best-performing caches in 5 other tests. DeferredLRU with binning was up to 28.8 times faster on 32 threads compared to single-threaded performance.

**Keywords** Cache eviction strategy, concurrent computing, concurrent data structure, lock-free programming techniques, LRU cache, memoization, multi-processing systems, parallel computing, software cache

## Contents

| In       | trod         | uction                                                 | 1              |

|----------|--------------|--------------------------------------------------------|----------------|

|          |              |                                                        | 1              |

|          |              |                                                        | $\overline{2}$ |

|          | Out          |                                                        | 3              |

| 1        | ٦            | ated Work                                              | 5              |

| Ŧ        | 1.1          |                                                        | 5              |

|          | $1.1 \\ 1.2$ | 1 0                                                    | 7              |

| <b>2</b> | Bac          | kground                                                | 9              |

|          | 2.1          | Sequential data structures and algorithms              | 9              |

|          | 2.2          | Approaches to synchronization in concurrent programs 1 | 3              |

|          | 2.3          | Concurrent data structures and algorithms              | 0              |

| 3        | Cor          | current LRU Caches 2                                   | 3              |

|          | 3.1          | LRU with mutex                                         | 3              |

|          | 3.2          | ConcurrentLRU                                          | 3              |

|          | 3.3          | Intel TBB LRU                                          | 4              |

|          | 3.4          | Facebook HHVM LRU                                      | 5              |

| 4        | Def          | erredLRU Design 2                                      | 7              |

|          | 4.1          | Data structures                                        | 8              |

|          | 4.2          |                                                        | 0              |

|          | 4.3          | Auxiliary operations                                   | 2              |

| <b>5</b> | Per          | formance Evaluation 3                                  | 9              |

|          | 5.1          | Test setup                                             | 9              |

|          | 5.2          | Meta-parameter choice                                  | 2              |

|          | 5.3          |                                                        | 6              |

|          | 5.4          | Performance                                            | 7              |

|              | 5.5                                    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49                         |

|--------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|              | 5.6                                    | LSU3shell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                         |

| 6            | Rec                                    | ommendations for Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                         |

|              | 6.1                                    | Write-free cache lookup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55                         |

|              | 6.2                                    | Improved eviction strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56                         |

|              | 6.3                                    | Improved hash table design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56                         |

|              | 6.4                                    | Additional evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56                         |

| Co           | onclu                                  | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57                         |

| Bi           | bliog                                  | graphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59                         |

|              |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| $\mathbf{A}$ | Def                                    | erredLRU Meta-parameter Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>65</b>                  |

| Α            |                                        | erredLRU Meta-parameter Measurements<br>Wikipedia 1/10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>65</b><br>66            |

| Α            | A.1                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

| Α            | A.1<br>A.2                             | Wikipedia $1/10$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                         |

| Α            | A.1<br>A.2<br>A.3                      | Wikipedia 1/10       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 66<br>68                   |

| Α            | A.1<br>A.2<br>A.3<br>A.4               | Wikipedia 1/10          Wikipedia 1/1000          P4 1/10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66<br>68<br>70             |

| Α            | A.1<br>A.2<br>A.3<br>A.4<br>A.5        | Wikipedia 1/10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>68<br>70<br>72       |

| в            | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6 | Wikipedia 1/10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>68<br>70<br>72<br>74 |

# **List of Figures**

| 1.1                 | 42 years of microprocessor trend data                                                                           | 7  |

|---------------------|-----------------------------------------------------------------------------------------------------------------|----|

|                     | LRU cache structure                                                                                             |    |

| 4.2                 | DeferredLRU structure                                                                                           | 34 |

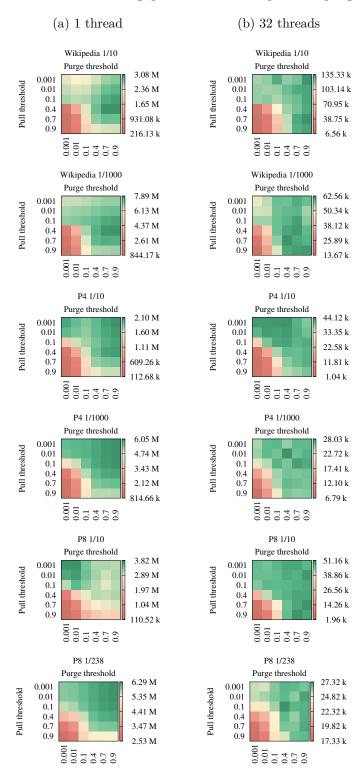

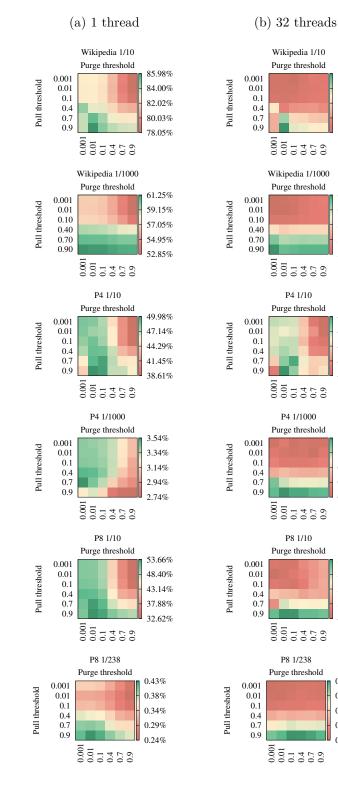

| $5.1 \\ 5.2 \\ 5.3$ | Meta-parameter throughput measurementsMeta-parameter hit-rate measurementsPerformance on Wikipedia 1/1000 trace | 45 |

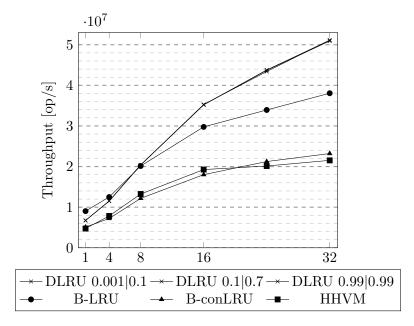

| 5.4                 | Performance on P4 1/1000 trace                                                                                  | 52 |

## List of Tables

| 2.1  | Integer increment race condition                                        | 14  |

|------|-------------------------------------------------------------------------|-----|

| 2.2  | ABA problem in a lock-free stack                                        | 19  |

| 5.1  | Data traces for performance evaluation                                  | 41  |

| 5.2  | Hit-rate comparison                                                     | 46  |

| 5.3  | Singular cache performance                                              | 50  |

| 5.4  | Binned cache performance                                                | 51  |

| 5.5  | LSU3shell running time with different caches                            | 53  |

| A.1  | Meta-parameter throughput measurements, Wikipedia $1/10,1$ thread       | 66  |

| A.2  | Meta-parameter hit-rate measurements, Wikipedia $1/10$ , 1 thread       | 66  |

| A.3  | Meta-parameter measurements baseline, Wikipedia $1/10$ , 1 thread       | 66  |

| A.4  | Meta-parameter throughput measurements, Wikipedia $1/10, 32$            | ~ - |

|      | threads                                                                 | 67  |

| A.5  | Meta-parameter hit-rate measurements, Wikipedia $1/10$ , 32 threads     | 67  |

| A.6  | Meta-parameter measurements baseline, Wikipedia $1/10$ , 32 threads     | 67  |

| A.7  | Meta-parameter throughput measurements, Wikipedia $1/1000, 1$           |     |

|      | thread                                                                  | 68  |

| A.8  | Meta-parameter hit-rate measurements, Wikipedia $1/1000$ , 1 thread     | 68  |

| A.9  | 1 / 1 / /                                                               | 68  |

| A.10 | Meta-parameter throughput measurements, Wikipedia $1/1000, 32$          |     |

|      | threads                                                                 | 69  |

| A.11 | Meta-parameter hit-rate measurements, Wikipedia $1/1000$ , $32$ threads | 69  |

|      | Meta-parameter measurements baseline, Wikipedia $1/1000$ , $32$ threads | 69  |

| A.13 | Meta-parameter throughput measurements, P4 1/10, 1 thread               | 70  |

| A.14 | Meta-parameter hit-rate measurements, P4 1/10, 1 thread $\ldots$        | 70  |

| A.15 | Meta-parameter measurements baseline, P4 1/10, 1 thread $\ldots$        | 70  |

| A.16 | Meta-parameter throughput measurements, P4 1/10, 32 threads $~$ .       | 71  |

|      | Meta-parameter hit-rate measurements, P4 1/10, 32 threads               | 71  |

| A.18 | Meta-parameter measurements baseline, P4 $1/10$ , 32 threads $\ldots$   | 71  |

| A.19 | Meta-parameter throughput measurements, P4 $1/1000$ , 1 thread .     | 72 |

|------|----------------------------------------------------------------------|----|

|      | Meta-parameter hit-rate measurements, P4 1/1000, 1 thread            | 72 |

| A.21 | Meta-parameter measurements baseline, P4 1/1000, 1 thread            | 72 |

|      | Meta-parameter throughput measurements, P4 1/1000, 32 threads        | 73 |

|      | Meta-parameter hit-rate measurements, P4 1/1000, 32 threads          | 73 |

| A.24 | Meta-parameter measurements baseline, P4 1/1000, 32 threads          | 73 |

| A.25 | Meta-parameter throughput measurements, P8 1/10, 1 thread            | 74 |

|      | Meta-parameter hit-rate measurements, P8 $1/10$ , 1 thread           | 74 |

| A.27 | Meta-parameter measurements baseline, P8 $1/10$ , 1 thread           | 74 |

| A.28 | Meta-parameter throughput measurements, P8 $1/10$ , 32 threads .     | 75 |

| A.29 | Meta-parameter hit-rate measurements, P8 $1/10$ , 32 threads         | 75 |

| A.30 | Meta-parameter measurements baseline, P8 $1/10$ , 32 threads         | 75 |

| A.31 | Meta-parameter throughput measurements, P8 $1/238$ , 1 thread        | 76 |

| A.32 | Meta-parameter hit-rate measurements, P8 $1/238$ , 1 thread $\ldots$ | 76 |

| A.33 | Meta-parameter measurements baseline, P8 1/238, 1 thread             | 76 |

| A.34 | Meta-parameter throughput measurements, P8 $1/238,32$ threads .      | 77 |

| A.35 | Meta-parameter hit-rate measurements, P8 1/238, 32 threads           | 77 |

| A.36 | Meta-parameter measurements baseline, P8 1/238, 32 threads           | 77 |

| B.1  | Singular cache performance I                                         | 80 |

| B.2  | Singular cache performance II                                        | 81 |

| B.3  | Singular cache performance III                                       | 82 |

| B.4  | Binned cache performance I                                           | 83 |

| B.5  | Binned cache performance II                                          | 84 |

| B.6  | Binned cache performance III                                         | 85 |

## Introduction

## Motivation

Modern computations and data processing rely heavily on caching systems. Software cache [1] (SW cache) is a key-value storage used to speed up access to commonly used or recently used elements in some domain.

Without caching, required values are recomputed or fetched from network each time they are requested. With a SW cache, the values are stored in memory once obtained. Later, the requested value is searched in memory before being retrieved again. If it is found, the costly recomputation of this value is omitted.

SW cache supports at least the following two operations: LOOKUP that looks up a value by its key in memory and INSERT that stores a new keyvalue pair (while possibly evicting some existing element). Usually, they are combined into one procedure that searches for the requested item, and in case it is not found the item is recomputed and inserted into the SW cache.

Among numerous SW cache applications, there are systems for optimizing server-side IO throughput [2,3] and distributed file systems [4,5]. Caching is an integral part of the database systems in many ways: it is used for managing disk buffering [6], server-side request caching, client-side ORMDB caches [7], and many more. Memcached [8] and Redis [9] are popular general-purpose caching solutions for modern network systems [10, 11].

An automatic memoization approach is a form of caching that is primarily used in algorithmization. This process is also denoted as tabling [12]. It was first described in [13], and it is widely used in term rewriting [14], artificial intelligence [15], and other scientific computations [16–18].

The SW cache is used when it is impractical or impossible to store all the values in local memory. Its goal then is to store the most valuable elements. Some stored elements must be evicted from the cache in order to free up space for the insertion of a new one. SW caches differ by the replacement strategy they use to choose such an element.

#### INTRODUCTION

The Least-Recently-Used (LRU) [19] is a simple replacement strategy. When a replacement is required, the element that has not been accessed for the longest time is chosen. It is achieved by keeping all elements in a linked list ordered by the last access time. When an element in a cache is accessed, it is moved to the head of the list. The element at the tail of the list is considered least recently used, and it is chosen for eviction. The list is combined with a dictionary data structure (usually, a hash table) for fast item lookup by key.

This implementation performs well in a sequential program, but adapting this data structure for a concurrent environment raises multiple issues. One of the main flaws is the high contention on the list head since both LOOKUP and INSERT operations imply an insertion into the LRU list head. When each thread attempts to access the same memory address, these accesses are serialized. This limits the scalability of the whole cache.

What is more, it is hard to combine concurrent hash table and concurrent linked list in a single system while preserving the correctness and scalability of these data structures. There are known implementations for a doubly linked list and concurrent hash table (see Section 2.3.1). However, special care should be taken to avoid race conditions when combining them. For instance, an element can be evicted from the list while it is searched in the hash table. The routine that moves accessed elements to the list head must foresee this.

## Contribution

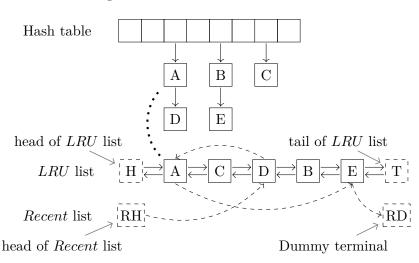

An LRU-inspired concurrent SW cache, called DeferredLRU, is presented in this thesis. It attempts to preserve LRU caching efficiency while making it more suitable for a concurrent environment.

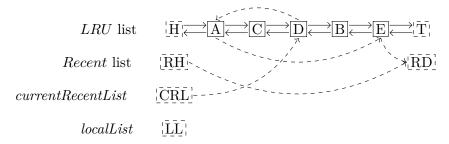

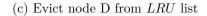

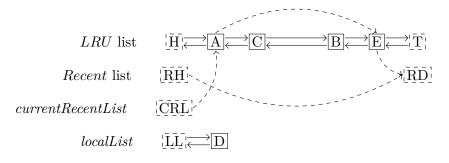

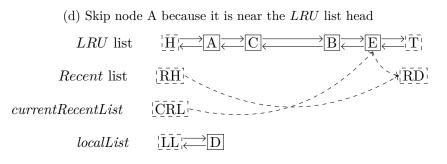

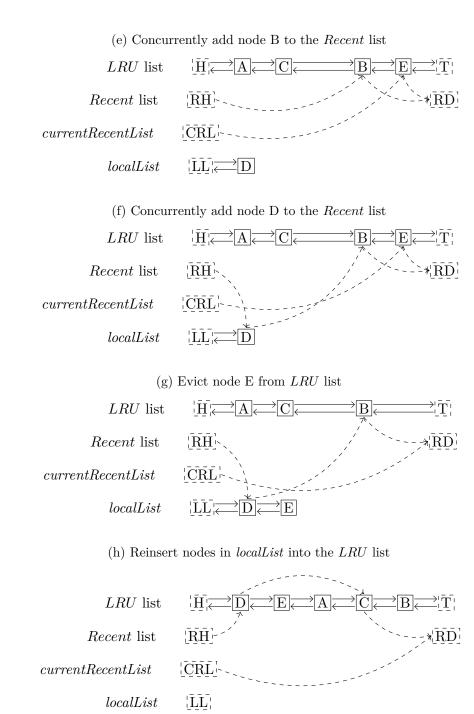

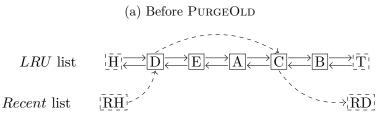

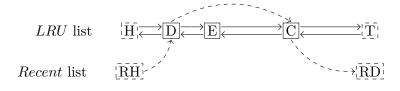

It uses a different approach to moving accessed elements to the head. Instead of being moved immediately after each element lookup, they are added to another linked list, called *Recent* list (in contrast to *LRU* list). When the number of elements in the *Recent* list hits some threshold, a single thread performs the PULLRECENT operation while other threads are still able to perform lookups and insertions concurrently. PULLRECENT evicts all the elements in the *Recent* list from the *LRU* list and reinserts them into the head. The whole sublist is inserted in a single step. This trick vastly decreases the total number of head insertions (making one insertion per PULLRECENT, not per lookup), and therefore, it improves scalability.

PULLRECENT is done as a part of cache consolidation. In case the cache is full, the consolidation stage also performs PURGEOLD operation. PURGEOLD evicts some tail nodes to reuse them for storing new items. It is guaranteed that only one thread performs consolidation at a time, and it is the only time when nodes are removed from the LRU list. The only other operation that is performed on the LRU list is the head insertion. These two facts allowed the list synchronization to be greatly simplified and reduced (see Section 2.3.2). In addition to that, the thesis contains a comprehensive performance evaluation of DeferredLRU and compares it to existing concurrent LRU SW caches under different workloads.

DeferredLRU puts the main focus on improving cache scalability with a novel approach to updating the LRU list. The ideas presented in this thesis can be used for implementing other scalable concurrent SW caches that are based on more sophisticated replacement strategies (see Section 1.1) similarly to how LRU is used as a building block in many of these strategies.

## Outline

The thesis proceeds as follows. In Chapter 1, an overview of selected SW caches and replacement strategies is presented. In Chapter 2, data structures and algorithms necessary for understanding the DeferredLRU implementation are introduced. In Chapter 3, several concurrent LRU SW caches are studied. These caches are later used in the performance evaluation for comparison with DeferredLRU cache. In Chapter 4, the DeferredLRU implementation is introduced. In Chapter 5, an extensive performance evaluation of DeferredLRU and other LRU containers is presented. It studies the effect of the DeferredLRU meta parameters choice and compares cache throughput and hit-rate under different workloads and with a varying number of threads. In Chapter 6, the future improvements to DeferredLRU are discussed.

## CHAPTER **I**

## **Related Work**

In recent years, the progress on SW caches has been made in two primary directions: improving replacement strategy to make smarter evictions and improve performance, especially for parallel applications.

## **1.1** Replacement strategies

Least-Recently-Used (LRU) [19] is a simple replacement strategy. It always chooses to evict an element that has not been accessed for the longest time. Least-Frequently-Used (LFU) is another base approach to node eviction. It tracks the number of accesses to each element in the cache and evicts the one that has the least number of accesses.

Bélády's algorithm [20] is the most efficient replacement strategy. It discards entries that are not required for the longest time. However, to do so, the algorithm would have to see the input ahead, which is not possible with non-static inputs. Therefore, Bélády's algorithm cannot be implemented in reality. It is useful for evaluating other cache replacement strategies, as it sets the best possible hit-rate that can be achieved with a given input.

LRU-K [19] attempts to find a balance between both LRU and LFU approaches. It makes eviction decision based on last K accesses.

2Q [6] attempts to overcome an issue with inserted items that were not referenced afterward. Such items unnecessary take up valuable caches capacity. 2Q maintains two queues (hence the name 2Q). On first access, items are placed to the first FIFO queue. If an item is reaccessed before it is evicted, it is promoted to the second LRU queue. By changing the ratio between the queue capacities, it is possible to adjust eviction behavior.

Low Inter-reference Recency Set (LIRS) [21] uses the reuse distance metric number of other elements accessed between two consecutive references to the given element. LIRS ranks entries in the cache based on the maximum of reuse distances between last and second-to-last reference and distance between the last access and current point in time.

### 1. Related Work

Adaptive replacement cache (ARC) [22] attempts to exploit both recency and frequency of access locality. It maintains LRU and LFU caches and a set of ghost-entries (meta-data of recently evicted items) for each of them. The total cache capacity is dynamically divided between the two caches based on the number of hits each cache receives. That is, if a particular workload caches better with a frequency-based replacement strategy, the LFU cache capacity is gradually increased and vice versa. The adaptation process is continuous; therefore, ARC is able to capture changes in workload.

TinyLFU [23] is a cache admission policy. For a new element and a given eviction candidate, it decides whether it worths performing the replacement. It does so by considering access frequency that is tracked in a very economic way based on Bloom filter theory [24]. W-TinyLFU [23] is a cache replacement strategy that uses a combination of a small LRU cache and a much larger SLRU cache with an embedded TinyLFU admission policy. Initially, elements are written into the LRU cache and may be propagated to the SLRU cache on subsequent accesses.

Hawkeye [25] cache replacement algorithm is based on a completely different idea than the previous caches. It approaches the replacement decision as a binary classification problem. It executes Bélády's algorithm on a history of recent accesses to study the workload distribution and make predictions.

## 1.2 Concurrent caches

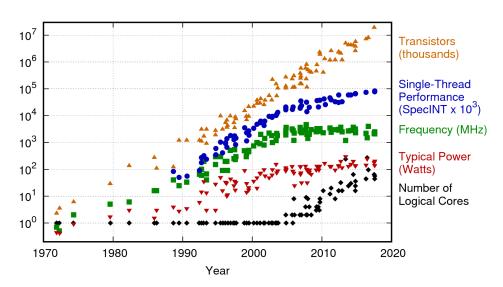

The demand for concurrent caching arises from the shift in CPU development trends. Gordon E. Moore has predicted that the number of transistors doubles every 2 years [27]. Figure 1.1 demonstrates that this statement remains correct for the last 5 decades.

However, single-threaded performance trend is not keeping up with this trend for the last 10 years. The overall performance is catching up by the number of logical cores, that has increased drastically even in consumer-grade processors. Server processors have been having tens of cores for a long time, and the counts approach hundreds rapidly.

There are several SW caches that are suitable for a concurrent program. C++ implementations of concurrent LRU cache can be found in the Intel Threading Building Blocks library [28] and the Facebook HHVM project [29]. These implementations are studied in Chapter 3.

Agnes [30] presents another concurrent cache, called BagLRU. Inserted items are accumulated in an "AgeBag" collection. When the AgeBag is full, another one is allocated, and new items are written to it. When the cache is full, the oldest AgeBag is emptied. Items that have been accessed since the corresponding was full are added to a newer AgeBag. The other items are evicted. Other concurrent cache implementations can be found in [31–33]. These implementations were written in Java. Therefore, they can not be directly compared with existing DeferredLRU implementation.

Figure 1.1: 42 years of microprocessor trend data [26]

CHAPTER 2

## Background

In this chapter, the algorithms, data structures, and concepts that DeferredLRU implementation is built upon are presented. At first, common data structures like linked list or hash table are introduced. It is followed by an overview of some approaches used in concurrent programming for ensuring thread synchronization. Then, a survey of existing concurrent hash tables is presented. Finally, a DeferredLRU-specific implementation of concurrent doubly linked list is introduced.

## 2.1 Sequential data structures and algorithms

### 2.1.1 Singly linked list

Singly linked list is a basic data structure for maintaining a sorted sequence of elements. It is built of nodes that consist of user data and a link to the next node. In most implementations, the last node link points to a distinctive value that is often denoted as NULL. List traversal stops when this value is reached. Another common option is to set the last link node pointing to the very first node. In this case, the list is called cyclic. The first linked list node is called the list head. Respectively, the last node is called the list tail. All other nodes can be reached from a head node. Usually, a linked list is handled by a link to its head. Sedgewick [34] provides a detailed explanation of the linked list data structure.

In comparison to other data structures, specifically arrays, linked list has the following advantages:

• Nodes in a linked list can be reordered by merely reassigning their next links. This allows  $\mathcal{O}(1)$  element insertion and removal in the beginning and middle of a linked list in contrast to  $\mathcal{O}(N)$  for array (when inserting into an array, all elements after the position of the insertion must be shifted and there is N/2 such elements on average).

- Consequently, this allows *fast list slicing and joining* operations. For instance, appending one list at the end of another is just a matter of setting the next link of the last node in one of the lists.

- Singly linked list has an *overhead of one link per element*, which is more than the overhead of an array, but still less than many other data structures.

- Linked list is a *stable container*, meaning that changing the order of list elements would not invalidate any existing link to a node inside the list.

- Linked list *can be intrusive*, meaning that it can be embedded into another structure. It is even possible to embed multiple linked lists in a single structure. Then instances of this structure may be linked independently through different lists while using the same memory placement.

- Linked lists can use a node pool for *efficient memory reclamation*. When a node is removed from a list, it is added to a dedicated linked list, called node pool, instead of deallocating the memory. The list is formed by reusing an existing next link in the nodes. Later, when required, the node is obtained from the node pool instead of allocating it in runtime.

Adding and removing nodes from a node pool is expected to be much faster than using general memory management facilities. Some nodes may be preallocated and added to a memory pool beforehand to avoid initial allocations. Multiple lists of the same type may use a shared node pool.

However, these advantages come at a cost. One of the main downsides of a linked list is the absence of random access support. Accessing N-th node generally requires to iterate all the way down from the corresponding list head node. Moreover, traversing a linked list makes CPU cache futile. Since the next node can be anywhere in memory, each access may result in a CPU cache miss, pessimizing traversal performance. Finally, singly linked list does not allow backward traversal as nodes have no information about their predecessors. For the same reason, it is not possible to remove a node without knowing its predecessor. The last two problems can be solved with a doubly linked list.

### 2.1.2 Doubly linked list

Doubly linked list is a data structure that is in many ways similar to a singly linked list. However, instead of one link, each node in a doubly linked list contains links to both its preceding and following nodes (usually referred to as **prev** and **next** links). This modification allows doubly linked list to be traversed in both directions (but direct access by index is still not possible). Other than that, doubly linked list has the same advantages and disadvantages as singly linked list (see Section 2.1.1). See [34] for additional information.

### 2.1.3 Hash table

Hash table implements Dictionary abstract data type. It is capable of storing key-value pairs and looking up a value by the corresponding key. Also, it supports operations to add, update, and remove key-value pairs.

Internally hash table maintains an array of entries. It maps each key to an index in this array. To map a possibly infinite space of keys to a finite space of array indices, it uses a hash function [35]. A notable property of hash table is that its lookup time complexity does not depend on the number of items in it.

### 2.1.3.1 Hash collisions

In general case, the mapping cannot be injective, thus many keys are mapped to the same array index. This is called a *hash collision*. The number of collisions is controlled with a *load factor*. It is calculated as a maximum ratio of the number of items to the capacity.

There are two main approaches to dealing with collisions. With *closed* addressing, each entity in the hash table array is a linked list that contains all collided keys. With open addressing hash table array directly stores key-value pairs. A separate function for hash collision resolution is used. It generates a sequence of indices that are probed until an empty element in the array is found. If the sequence is (N, N + 1, N + 2, ...), such probing is called linear probing. Sedgewick [34] explains these concepts in greater detail.

### 2.1.3.2 Cuckoo hash table

When using open addressing, it is unclear how may addresses are probed before the searched key is found. Cuckoo hashing is a variant of the open addressing hash table that guarantees the constant number of probes for lookup [36].

The insertion is performed as follows. For each key in the Cuckoo hash table, two positions in the array are calculated using different hash functions. These positions may be either in the same array or in two different arrays. During the insertion, both positions are checked. If at least one of them is empty, then it is chosen for insertion.

Otherwise, the collision is resolved by replacing one of the old elements with the new one and pushing the replaced elements to its second position. In case it is occupied as well, the element evicted in the previous step is written to the slot and the replacement is repeated for the newly evicted key.

If no empty slot was found after performing a predefined number of such replacements, the hash table is considered full, and it is rehashed.

Although insertion may result in a long chain of replacements, each key is always placed into one of its two positions. Therefore, the Cuckoo hash table allows a fast lookup, that has to check at most two memory locations.

#### 2.1.3.3 Hopscotch hash table

The Cuckoo hash table requires a few memory accesses on lookup. These accesses can be anywhere in memory and each access likely results in a CPU cache miss. Hopscotch hash table [37] combines advantages of the Cuckoo hashing and linear probing to minimize CPU cache misses.

Items are kept in an array of buckets. H consequent buckets form a group of neighbors. Each bucket consists of a single slot for a key and the *hop information*. When a collision occurs, the key is attempted to be placed in one of the neighbor buckets. If the bucket is full, the hash table is rehashed.

The hop information is a bit array that has bits set for those positions in the group, that are occupied by the collided items. E.g., with H = 6, elements X, Y, and Z belong to the bucket 1. However, during collision resolution, they have been written to buckets 1, 2, 4. In this case, hop information equals to 110100. Hop information is used to speed up lookups.

### 2.1.3.4 Cache-line hash table

Another attempt to improve memory access patterns concerning the CPU caching is made in CLHT [38]. It is based on a closed addressing. However, each bucket contains a chain of arrays of keys instead of separate nodes. Each array is of the same size as a CPU cache line. Therefore, each CPU cache transaction allows us to load and traverse multiple keys.

## 2.1.4 LRU cache

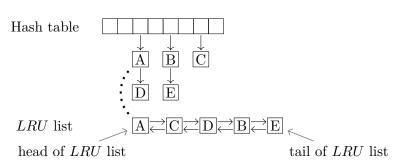

A typical LRU implementation is based on a combination of a hash table (for a fast element lookup) and a doubly linked list that keeps elements ordered by their access order, i.e., recently accessed and just added elements are inserted into the head and the least recently accessed elements are in the tail. Each successful element lookup results in the corresponding node being moved to the list head.

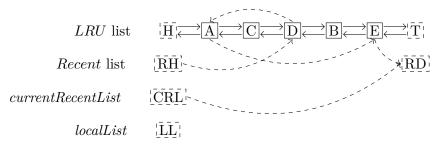

Figure 2.1 shows an example of LRU cache that contains 5 items (A, B, C, D, E). This implementation uses a closed addressing hash table, although other variants can be used as well. Item A has been accessed most recently. In case item B is accessed, LRU list will contain items in the following order: B, A, C, D, E. In case an eviction is performed, item E is removed from LRU list and hash table as it is the last entry in the LRU list.

The important property of this approach is that lookup and insert operations have  $\mathcal{O}(1)$  space and time complexity. The lookup consists of the hash table lookup and optionally a linked list node removal and insertion. Insert operation consists of insertion into the hash table and into the linked list head. In the case of insertion into a full cache, another element also has to be evicted. This adds a hash table removal and a linked list removal. Indeed, all operations are  $\mathcal{O}(1)$ .

Figure 2.1: LRU cache structure

# 2.2 Approaches to synchronization in concurrent programs

This section describes some general approaches to thread synchronization, primitives that are used by these approaches, and common pitfalls that may occur in concurrent programs.

## 2.2.1 Race conditions

As described in Section 1.2, the main advance in modern chip development is made towards increased parallelism. Hence nowadays, many programs are required to support multi-core execution, and so do their building blocks, namely data structures and algorithms.

For most sequential codes that actively interact with memory, it stands that executing them in parallel results in undefined behavior and often a program crash too. When multiple threads access shared memory, they must appropriately synchronize reads and writes to the memory. Therefore, the corresponding codes must be rewritten with concurrency in mind. In other words, with the idea that other threads may execute any other viable code at the same time.

It is easy to demonstrate the issues coming up with multi-threaded execution even with a simple function that increments an integer X. On a machine instruction level, its implementation may look like in Algorithm 1. The important part is that the increment is performed in 3 steps: load current value from memory, increment it, write it back to memory.

In case two threads make progress on the function simultaneously, it is expected that X is incremented twice. However, due to the nature of concurrent programming, the instructions of different threads may be executed in any relative order. It may happen that on a global timeline, the instructions are ordered the way it is shown in Table 2.1. One can see that both threads concurrently read and increment the initial value of X. Therefore, after execution, X is only incremented by 1. Such a circumstance is called a *race condition*.

### Algorithm 1 Integer increment

```

function INCREMENT(X)

Load X to register

register \leftarrow register + 1

Write register to X

end function

```

Table 2.1: Integer increment race condition

| Thread A                         | Thread B               | X | $R\theta$ | <i>R1</i> |

|----------------------------------|------------------------|---|-----------|-----------|

|                                  |                        | 0 | ?         | ?         |

| Load X to $R\theta$              |                        | 0 | 0         | ?         |

|                                  | Load $X$ to $R1$       | 0 | 0         | 0         |

|                                  | $R1 \leftarrow R1 + 1$ | 0 | 0         | 1         |

|                                  | Write $R1$ to $X$      | 1 | 0         | 1         |

| $R\theta \leftarrow R\theta + 1$ |                        | 1 | 1         | 1         |

| Write $R\theta$ to $X$           |                        | 1 | 1         | 1         |

The ordering presented in Table 2.1 may appear unlikely to happen. However, in a similar test, where two threads incremented a shared variable 100000 times, the final value of the variable is 120937 instead of 200000. About 40% of increments had been discarded due to the race condition in the code. In practice, it turns out that Murphy's law [39] applies to concurrent programming particularly well.

For eliminating the race condition discussed above, threads must be prevented from incrementing the same value and overwriting each other changes. Several approaches to such synchronization are presented in this section.

## 2.2.2 Mutual exclusion lock

Many concurrent data structures often rely on a mutual exclusion lock (mutex) for ensuring thread synchronization. Mutex prevents a part of the algorithm from being executed by multiple threads at the same time. Such a part is usually called a *critical section*.

Mutex is supposed to be locked when entering the corresponding critical section and unlocked upon exit. When some thread attempts to lock an already locked mutex, it is suspended until the mutex is unlocked. Additionally, mutex provides non-blocking TRYLOCK operation that attempts to lock the mutex, but the thread is not suspended if the mutex is locked already.

The 3-step number increment in Algorithm 1 is an example of a critical section. It may be implemented with a proper mutex-based synchronization as shown in Algorithm 2. In case of the ordering denoted in Table 2.1, thread B would be suspended until A unlocks the mutex.

Algorithm 2 Integer increment with mutex synchronization

| function INCREMENT $(X, mutex)$    |  |

|------------------------------------|--|

| LOCK(mutex)                        |  |

| Load $X$ to register               |  |

| $register \leftarrow register + 1$ |  |

| Write register to $X$              |  |

| UNLOCK(mutex)                      |  |

| end function                       |  |

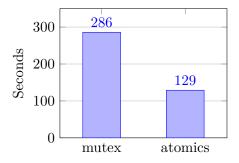

Figure 2.2: Concurrent integer increment from 0 to 320000000 with 32 threads using different synchronization approaches

### 2.2.3 Atomic operations

Many modern processors support atomic instructions [40,41]. These operations are different from regular ones because they are executed in a single memory transaction even though they consist of multiple memory loads and stores. This means that other threads will either see the memory before the operation starts or after it finishes, but never in some intermediate state.

One of the basic atomic operations is ATOMICCAS(A, C, value) (atomic Compare-And-Swap). If the current value of variable A equals to the value of variable C, A is set to value. Otherwise, the current value of A is written to C, but A itself remains unchanged. The operation returns a true/false result that tells whether value was written to A. The atomicity ensures that the value of Acannot be changed concurrently after it was observed by a thread performing ATOMICCAS until this operation finishes. Full ATOMICCAS semantic is denoted in Algorithm 3.

Other common atomic operations are ATOMICEXCH and FETCHANDADD. ATOMICEXCH(A, value) operation returns the current value of A, while atomically setting A to value. FETCHANDADD(A, value) fetches the current value of A while incrementing A by value.

Many atomic operations can be expressed with ATOMICCAS. For example, ATOMICEXCH implementation based on Compare-And-Swap is presented in Algorithm 4.

### Algorithm 3 Atomic Compare-And-Swap

```

function ATOMICCAS(A, C, value)

Output: returns TRUE if value has been written to A, FALSE otherwise

atomically

if A = C then

A \leftarrow value

return TRUE

else

C \leftarrow A

return FALSE

end if

end atomically

end function

```

| Algorithm 4 | ŀ | Atomic | Exchange |

|-------------|---|--------|----------|

|-------------|---|--------|----------|

```

function ATOMICEXCH(A, value)

Output: returns the last value of A before assignment

tmp \leftarrow A

repeat

until ATOMICCAS(A, tmp, value)

return tmp

end function

```

Atomic operations are often used instead of critical sections with mutexes because they may yield better performance. In a small test of incrementing an integer 3200000000 times with 32 threads version with atomic operations is 2.2x times faster than the one with a mutex (see Figure 2.2). For details on the test machine, see Chapter 5.

## 2.2.4 Coarse-grained synchronization

The simplest way to make any data structure thread-safe is to add a single mutex that guards all its operations. This approach is a so-called coarsegrained synchronization. The main advantage of it is its simplicity. Indeed, all algorithms are the same with slight modification for mutex locking.

However, only one thread may operate on a data structure at a time. Hence, the scalability is limited. If the data structure is the central component of some computations, then running these computations on multiple cores would show almost no speedup compared to a single-threaded run. The performance often even degrades with the number of threads rising.

### 2.2.5 Fine-grained synchronization

The scalability can be improved if the data structure operations are divided into multiple independent critical sections. Then different threads can execute the operations in parallel if they are in different critical sections. They still may happen to enter the same critical section at the same time, in which case one of them is suspended. However, this is not expected to happen too often. This approach is called fine-grained synchronization.

In the case of LRU cache, each operation requires the accessed element to be moved to the head of the LRU list. Therefore each thread enters the same critical section (associated with the LRU list head) on every LOOKUP and INSERT operation. This limits the applicability of fine-grained synchronization to LRU cache.

### 2.2.6 Binning

For some data structures, scalability can be improved by *binning*. The trick is to allocate multiple smaller instances of a data structure — bins — and to distribute concurrent accesses among them. The number of bins is to be derived from the expected number of threads.

In application to SW cache, a binning adapter distributes keys uniformly across all bins using a hash function. Since most SW caches internally use a hash table, the binning adapter and the internal hash table must use different hash functions.

Binning significantly improves scalability even with coarse-grained synchronization (see Chapter 5). On the other side, it unpredictably affects cache hit-rate, improving it in some cases and worsening in others (see Appendix B). Also, it may have some side-effects like worse CPU caching (since multiple SW caches combined have a larger memory footprint).

### 2.2.7 Lock-free programming

Lock-based design is prone to system-wide stalls in case a thread that is holding a mutex is suspended (e.g., by the operating system scheduler). If a thread never releases the lock, other threads may stall indefinitely long. For instance, this may happen with priority inversion when the process scheduler keeps granting time to high-priority threads that are impeded by a mutex locked by a low-priority thread. Therefore, the system as a whole does not make progress at all.

In contrast to this, a lock-free programming model guarantees system-wide progress. That is, there is always at least one thread that can make progress even if all other threads are suspended. In practice, this usually means avoiding using mutexes and using atomic memory operations for thread synchronization instead. Fraser [42] provides a more in-depth explanation of lock-freedom and related concepts.

## 2.2.8 ABA problem

ABA problem is a type of a race condition, that mostly happens in atomicsbased synchronization. It occurs when a thread relies on the assumption that two consecutive reads from a specified memory location being equivalent implies that the dependent data structure has not changed.

In reality, another thread may overwrite the checked variable multiple times, make some other changes to the dependent data structure, and by coincidence, write the initial value to the checked variable in the end. The first thread then would not detect the occurred changes since the checked variable is effectively the same. Consecutive operations performed by the thread results in undefined behavior and likely in the data structure corruption.

ABA problem can be easily demonstrated with a naive linked list-based lock-free stack implementation. Stack is a data structure with two basic operations: PUSH adds objects to a stack, and POP extracts them in reverse (last in, first out) order.

The simple implementation presented in Algorithm 5 is prone to the ABA problem, as shown in Table 2.2. One can see that after the execution finishes *stackHead* points to invalid memory location.

Dechev et al. [43] introduce a technique for systematic ABA problem avoidance and compare it with other existing approaches. DeferredLRU avoids the ABA problem by putting specific constraints on the used lock-free data structures that make it impossible to happen.

For example, a constraints that could prevent ABA problem in Algorithm 5 is to avoid using POP operation at all. The ABA problem cannot emerge from PUSH as this operation does not rely on the stack not being changed apart from the *stackHead* variable itself. By using some other operation for resetting the stack (see Section 4.1.6), the ABA problem can be avoided without using any explicit ABA avoidance technique.

| Algorithm 5 Lock-free stack PUSH and POP (prone to Al                            | BA problem)                     |

|----------------------------------------------------------------------------------|---------------------------------|

| 1: global $stackHead \leftarrow NULL$                                            |                                 |

| 2: function PUSH(node)                                                           |                                 |

| 3: repeat                                                                        |                                 |

| 4: $currentHead \leftarrow stackHead$                                            | $\triangleright$ Atomic load    |

| 5: $node.next \leftarrow currentHead$                                            |                                 |

| 6: <b>until</b> ATOMICCAS( <i>stackHead</i> , <i>currentHead</i> , <i>node</i> ) |                                 |

| 7: end function                                                                  |                                 |

| 8: function Pop                                                                  |                                 |

| 9: repeat                                                                        |                                 |

| 10: $node \leftarrow stackHead$                                                  | $\triangleright$ Atomic load    |

| 11: <b>if</b> $node = $ NULL <b>then</b>                                         |                                 |

| 12: return NULL                                                                  | $\triangleright$ Stack is empty |

| 13: <b>end if</b>                                                                |                                 |

| 14: $nextNode \leftarrow node.next$                                              |                                 |

| 15: <b>until</b> ATOMICCAS( <i>stackHead</i> , <i>node</i> , <i>nextNode</i> )   |                                 |

| 16: return node                                                                  |                                 |

| 17: end function                                                                 |                                 |

Table 2.2: ABA problem in a lock-free stack

|                                                                                 | Thread          | l A variables |

|---------------------------------------------------------------------------------|-----------------|---------------|

| Stack                                                                           | node            | nextNode      |

| Initial state                                                                   |                 |               |

| $stackHead \rightarrow X \rightarrow Y \rightarrow Z \rightarrow \texttt{NULL}$ | ?               | ?             |

| Thread A executes Pop until being                                               |                 |               |

| suspended between lines 14 and 15                                               |                 |               |

| $stackHead \rightarrow X \rightarrow Y \rightarrow Z \rightarrow \texttt{NULL}$ | X               | Y             |

| Thread B executes Pop; reference to $X$ b                                       | pecomes invalio | d             |

| $stackHead \rightarrow Y \rightarrow Z \rightarrow \texttt{NULL}$               | X               | Y             |

| Thread B executes Pop; reference to $Y$ b                                       | oecomes invalio | ł             |

| $stackHead \rightarrow Z \rightarrow \texttt{NULL}$                             | X               | Y             |

| Thread B executes Push and inserts $X'$                                         |                 |               |

| New node $X'$ happens to have the same a                                        | address as X    |               |

| $stackHead \rightarrow X' \rightarrow Z \rightarrow \texttt{NULL}$              | X'              | Y             |

| Thread A finishes Pop                                                           |                 |               |

| AtomicCAS on line 18 succeeds as the pe                                         | ointer value is | the same      |

| $stackHead \rightarrow Y \rightarrow ?$                                         | ?               | ?             |

# 2.3 Concurrent data structures and algorithms

#### 2.3.1 Concurrent hash table

Hash table is a key data structure in numerous applications. There is a substantial progress made towards fast concurrent implementations. Chen et al. [44] and Maier et al. [45] present the most recent studies on concurrent hash tables.

Specifically, Chen et al. [44] conclude that there is no silver bullet: a concrete hash table must be chosen depending both on the typical use case and the target hardware (as the implementations often rely on specific hardware properties).

#### 2.3.1.1 Fine-grained synchronization

As with other data structure, any hash table can be made concurrent using a coarse-grained synchronization approach. However, due to the nature of hash tables, accesses are usually distributed uniformly across all used memory. It makes the hash table a good fit for a fine-grained synchronization.

Indeed, the fine-grained hash table implementation is straightforward. Each bucket is associated with its mutex. Each thread locks the corresponding mutex before accessing nodes. This way, different buckets can be accessed concurrently. Considering the fact that hash tables usually contain many buckets, the contention on each of them is expected to be low.

This design results in large memory overhead, since each mutex may take up a considerable amount of memory (for instance, on Linux platform each mutex takes up 40 bytes). It can be optimized by associating one mutex with a group of buckets. With many groups, there is still enough independent critical sections. At the same time, the memory overhead is divided across all buckets in a group.

Locking mutex is an expensive operation. Therefore, such design usually yields low per-thread performance. What is more, if many threads attempt to access the same value at the same time, all the accesses are serialized. Never the less, many concurrent implementations rely on this kind of lock-based design. Other implementations are based on the lock-free design.

#### 2.3.1.2 Concurrent Cuckoo hash table

Scouarnec [46] presents a scalable concurrent version of the Cuckoo hash table, called Cuckoo++. It uses lock-based design with one lock per bucket. Cuckoo++ attempts to omit a costly fetching of the secondary location by using the following heuristics.

Firstly, it relies on an "optimistic approach" — it expects the element to be found in its primary location and therefore it avoids memory prefetching for the secondary one. Secondly, each primary location bucket has a Bloom filter [24], that is able to detect, that the key is definitely not in the secondary location without actually accessing it.

#### 2.3.1.3 Concurrent Hopscotch hash table

Herlihy et al. [37] describe both sequential and concurrent versions of the Hopscotch hash table. Concurrent Hopscotch also employs an optimistic partially lock-free synchronization. Each bucket maintains its lock and a version number, that is associated with all the keys mapped to the bucket (even if they are placed into different buckets due to collisions). Insertions and evictions use the lock for mutual synchronization and updates the version counter after each change.

However, LOOKUP optimistically expects that the bucket is not changed while it is accessed. It records the version number in the beginning and compares it with a current value after the lookup. If the values are equal, then the bucket has not been changed concurrently and the data is valid. Otherwise, the operation is repeated on its slow path that considers concurrent modifications.

#### 2.3.1.4 Concurrent Cache-line hash table

There are two concurrent versions of CLHT [47]. The first one, called CLHT-LB, uses lock-based synchronization. Each array of buckets contains an additional lock, that is held when accessing the data.

The second version — CLHT-LF — is a lock-free hash table. It relies on atomic version-data pairs for detecting concurrent changes. When the data is modified, the version is increased. Then the updated pair is attempted to be posted to the shared memory using ATOMICCAS.

#### 2.3.1.5 Implementations

These are existing high-performance hash table implementations [28, 47–52].