Czech Technical University in Prague Faculty of Information Technology Department of Computer Systems

# Properties and Implementation Aspects of Residue Arithmetic for a Hardware Solver of Systems of Linear Equations

by

Jiří Buček

A dissertation thesis submitted to the Faculty of Information Technology, Czech Technical University in Prague, in partial fulfilment of the requirements for the degree of Doctor.

Dissertation degree study programme: Informatics

Prague, August 2017

#### Supervisor:

prof. Ing. Róbert Lórencz, CSc. Department of Computer Systems Faculty of Information Technology Czech Technical University in Prague Thákurova 9 160 00 Prague 6 Czech Republic

Copyright © 2017 Jiří Buček

#### **Abstract**

This dissertation thesis focuses on implementation aspect of hardware-based error-free solving of systems of linear equations. Error-free solution of linear systems is often needed in case of large, dense and ill-conditioned systems, where rounding errors can lead to long run times due to stability problems, or even hinder the solution completely. We explored the modular arithmetic approach using the Residue Number System (RNS).

We have analyzed and implemented several architectures for modular multiplication and modular inverse, which are needed to implement the elimination algorithm for solving the linear systems. We have redesigned the architecture of a residual processor for solving systems of linear congruences. This is a part of a modular system for solving systems of linear equations using the residue number system.

We have analyzed the implementation results in FPGA and ASIC platforms for different parameters such as word length or matrix dimension. The quality of hardware implemented algorithms was measured using the metrics of time and area and also the time-area product.

Our analysis is will serve as a base for improvement of the modular system for solving systems of linear equations. The resulting system architecture permits error-free solution of dense systems of linear equations of sizes of more than 1000 equations in reasonable configuration in a few seconds using contemporary technology.

#### **Keywords:**

modular arithmetic, error-free computation, linear algebra, system of linear equations, modular inverse, Montgomery inverse, Montgomery multiplication, FPGA, ASIC.

## Acknowledgements

First of all, I would like to express my gratitude to my dissertation thesis supervisor, Dr. Róbert Lórencz. He has been a constant source of encouragement and insight during my research and helped me with numerous problems and professional advancements.

I would also like to thank to my collaborators for valuable contribution to my work. This research has also been partially supported by the Czech Technical University SGS grant No. SGS13/101/OHK3/1T/18 and by the Czech Science Foundation project no. P103/12/2377.

Finally, my greatest thanks go to my family members, for their infinite patience and care.

## Contents

| A | bbre                 | viation | $\mathbf{s}$                                        | xiii |

|---|----------------------|---------|-----------------------------------------------------|------|

| 1 | Intr                 | oducti  | on                                                  | 1    |

|   | 1.1                  | Structi | ure of the Dissertation thesis                      | 2    |

| 2 | The                  | oretica | al Background and State-of-the-Art                  | 3    |

|   | 2.1                  | System  | ns of linear equations                              | 3    |

|   | 2.2                  | Montg   | omery multiplication                                | 7    |

|   |                      | 2.2.1   | The original algorithm                              |      |

|   |                      | 2.2.2   | Choice of radix                                     |      |

|   |                      | 2.2.3   | Binary radix Montgomery multiplication              | 8    |

|   |                      | 2.2.4   | Final subtraction                                   | 9    |

|   |                      | 2.2.5   | Choice of encoding                                  | 9    |

|   | 2.3                  | Modul   | ar Inverse                                          | 10   |

|   |                      | 2.3.1   | Montgomery Inverse                                  | 13   |

|   |                      | 2.3.2   | Left-Shift Inverse                                  | 14   |

| 3 | $\operatorname{Pre}$ | vious F | Results and Related Work                            | 15   |

|   | 3.1                  | Modul   | ar system for solving systems of linear equations   | 15   |

|   | 3.2                  | Montg   | omery multiplication                                | 16   |

|   |                      | 3.2.1   | Software approaches                                 | 16   |

|   |                      | 3.2.2   | Hardware approaches                                 |      |

|   | 3.3                  | Modul   | ar Inverse                                          | 20   |

|   |                      | 3.3.1   | Subtraction-Free Montgomery Inverse                 | 20   |

|   |                      | 3.3.2   | Left-Shift Inverse                                  | 20   |

| 4 | Ove                  | rview   | of Our Approach                                     | 25   |

|   | 4.1                  | FPGA    | implementation of a pipelined Montgomery multiplier | 28   |

|   | 4.2                  | Montg   | omery multiplier with modified Carry-Save encoding  | 28   |

|    | 4.3        | HW optimization of Left-Shift Inverse                                          | 30             |

|----|------------|--------------------------------------------------------------------------------|----------------|

|    | 4.4<br>4.5 | 4.3.2 Controller                                                               | 32<br>34<br>35 |

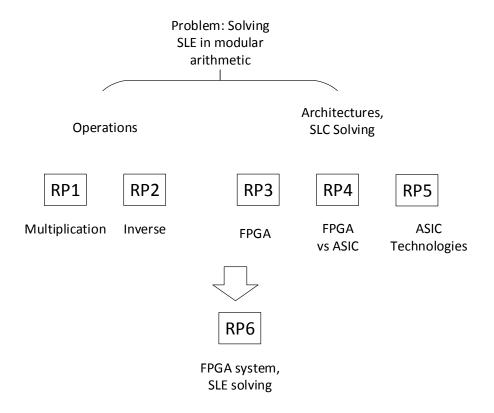

| 5  | Aut        | hor's Relevant Papers                                                          | 39             |

|    | 5.1        | RP1 – Montgomery Multiplication on FPGA with Modified Carry-Save Encoding      | 41             |

|    | 5.2        | RP2 – Comparing Subtraction-Free and Traditional AMI                           | 45             |

|    | 5.3        | RP3 – Dedicated Hardware Implementation of a Linear Congruence Solver in FPGA  | 49             |

|    | 5.4        | RP4 – Comparison of FPGA and ASIC Implementation of a Linear Congruence Solver | 54             |

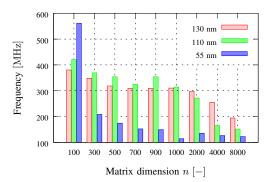

|    | 5.5        | RP5 – An ASIC Linear Congruence Solver Synthesized with Three Cell Libraries   | 59             |

|    | 5.6        | RP6 – Design of a Residue Number System Based Linear System Solver in Hardware | 64             |

| 6  | Cor        | aclusions                                                                      | 79             |

| Ū  | 6.1        | Summary                                                                        | 79             |

|    | 6.2        | Contributions of the Dissertation Thesis                                       | 81             |

|    | 6.3        | Future Work                                                                    | 81             |

| Bi | bliog      | graphy                                                                         | 83             |

| R  | eviev      | ved Publications of the Author Relevant to the Thesis                          | 87             |

| R  | emai       | ning Publications of the Author Relevant to the Thesis                         | 89             |

| R  | emai       | ning Publications of the Author                                                | 91             |

# List of Figures

| 3.1 | Modular system for solving systems of linear equations exactly $[1, 2]$     | 16 |

|-----|-----------------------------------------------------------------------------|----|

| 3.2 | Scalable pipelined implementation of the Montgomery multiplier              | 18 |

| 3.3 | Pipeline processing element                                                 | 19 |

| 4.1 | Internal structure of adders: a) conventional carry-save adder, b) modified |    |

|     | carry-save adder                                                            | 29 |

| 4.2 | Adder tree using a) carry-save encoding, b) modified carry-save encoding    | 29 |

| 4.3 | Multiplier architecture with modified CSA adder tree                        | 30 |

| 4.4 | LSI datapath schematic                                                      | 33 |

| 4.5 | Master part of AMI: a) Two subtractors, b) one subtractor with swappable    |    |

|     | inputs, c) subtraction-free                                                 | 34 |

| 4.6 | Arhitecture of the residual processor                                       | 36 |

| 5.1 | Relationships among author's relevant papers                                | 40 |

# List of Tables

| 2.1 | Computational complexity of individual steps of solving a system of linear equations using RNS                                                    | 6  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Left-Shift Inverse operation summary                                                                                                              | 21 |

| 4.1 | Left-Shift Inverse HW optimized operation summary                                                                                                 | 32 |

| 6.1 | Load, elimination, and read times for the MS architecture with multiple RPs.  The Total architecture is the sum of each row for the case of 1 RP  | 80 |

| 6.2 | FPGA (Xilinx xc6vlx240t) area occupation of MS architecture with multiple RPs. The last column is only the RP without the rest of the MS. BRAM is |    |

|     | the number of block RAM primitives computed as the number of RAMB18E1                                                                             |    |

|     | plus $2 \times RAMB36E1$                                                                                                                          | 80 |

# List of Algorithms

| 2.1 | Gauss-Jordan elimination algorithm modulo $m$ without row swapping | 5  |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Montgomery reduction                                               | 8  |

| 2.3 | High-radix Montgomery multiplication                               | 9  |

| 2.4 | Binary-radix Montgomery multiplication                             | 9  |

| 2.5 | Extended Euclidean algorithm for modular inverse                   | 11 |

| 2.6 | Extended Binary GCD Euclidean Algorithm                            | 12 |

| 2.7 | Montgomery modular inverse                                         | 13 |

| 3.1 | Rutishauser modification of Gauss-Jordan elimination modulo $m$    | 16 |

| 3.2 | Multi-word Montgomery multiplication                               | 18 |

| 3.3 | Binary Montgomery multiplication with carry-save encoding          | 19 |

| 3.4 | Subtraction-Free AMI                                               | 21 |

| 3.5 | Left-Shift Inverse algorithm                                       | 22 |

| 4.1 | Left-shifting inversion algorithm, HW optimized variant            | 31 |

## **Abbreviations**

#### **Number Sets**

- Natural numbers set

- $\mathbb{N}_0$  Natural numbers set  $\cup \{0\}$

- $\mathbb{Z}$  Integer numbers set

- $\mathbb{Z}_m$  Least nonzero residue number set with a module of m

- $\mathbb{S}_m$  Symmetric residue number set with a module of m

- Q Rational numbers set

- $\mathbb{R}$  Real numbers set

#### Common Mathematical Functions and Operators

|x| Absolute value of x

$|x|_m$  Least nonnegative residue of x modulo m, i.e. x mod m

$\boldsymbol{b}$  Vector  $\boldsymbol{b}$

$b_i$  the  $i^{\,\mathrm{th}}$  element of vector **b**

A Matrix A

$a_{i,j}$  Element of matrix **A** at the  $i^{\text{th}}$  row, and the  $j^{\text{th}}$  column

$a_{i,j}$  Element of matrix  $\mathbf{A}$  at the  $i^{\text{th}}$   $\mathbf{A}^{-1}$  Inverse matrix to matrix  $\mathbf{A}$  Transposed matrix to matrix  $\mathbf{A}$

$\max \{a, b\}$  Maximum of a and b, a when  $a \ge b$ , b when a < b  $\min \{a, b\}$  Minimum of a and b, a when  $a \le b$ , b when a > b

O(x) The big O notation  $\Theta(x)$  The big  $\Theta$  notation

#### **Mathematical Terminology**

$$M$$

A product of individual moduli  $M = \prod_{i=1}^{Q} m_i$

#### Miscellaneous Abbreviations

**AMI** Almost Montgomery Inverse

ASIC Application-Specific Integrated Circuit

AU Arithmetic Unit

CCU Central Control Unit

CU Communication Unit

CSA Carry Save Adder

**DSP** Digital Signal Processor

**EEA** Extended Euclidean Algorithm

**FP** Floating Point

FPGA Field-Programmable Gate Array

FPU Floating Point Unit

FSM Finite State Machine

GCD Greatest Common Divisor

GF Galois Field, a finite field

GJ Gauss-Jordan

**HDL** Hardware Description Language

HS Host SystemHW Hardware

LSI Left-Shift Inverse MI Modular Inverse

MM Montgomery MultiplicationMMI Montgomery Modular InverseMRC Mixed Radix Conversion

MRS Mixed Radix System

MS Modular System

NTL Number Theoretic LibraryRNS Residue Number System

**RAM** Random Access Memory, a read-write memory

**RP** Residal Processor

RSA Rivest-Shamir-Adleman cryptosystem

RTL Register Transfer Level

SLC System of Linear CongruencesSLE System of Linear Equations

TSMC Taiwan Semiconductor Manufacturing Company

VHDL Very High Speed Integrated Circuits Hardware Description Language

XST Xilinx Synthesis Technology, a HDL synthesis toolDDR Double Data Rate, a type of memory interface

## Introduction

In the field of scientific computation, it is always needed to consider the influence of roundoff errors on the solved problems. Solving systems of linear equations is one of the most frequent problems in scientific computation. Traditionally, solving of such systems is done in floating point arithmetic which brings its associated rounding errors.

The input data for solving can arise from measurements, model simulation parameters, or other sources. It is encountered in many different fields such as mechanical and electrical modeling and simulation, modeling of plasma behavior in astrophysics [3].

Although there are algorithms that minimize the impact of rounding errors on the error of the solution, in some cases this is not enough. Error-free solution of linear systems is often needed in case of large, dense and ill-conditioned systems, where rounding errors can lead to long run times due to stability problems, or even hinder the solution completely. One of the methods to perform error-free computation is using the Residue Number System (RNS).

When designing hardware architectures for computing in RNS, we have to implement basic operations in modular arithmetic. In this work, we focus on modular multiplication and modular inverse. Subsequently, these operations are used to implement an architecture for solving systems of linear congruences with prime modulus, which serves as the basis for solving systems of linear equations using RNS.

For modular multiplication, the Montgomery multiplication algorithm [4] is often used. As opposed to the conventional modular multiplication, the Montgomery's algorithm does not use division by the modulus N, rather it uses division by  $2^i$ , which is faster, since it is done merely by shifting (i is an integer). The reduction step is performed depending on the least significant digit of the intermediate result, rather than on the most significant one, as in the case of a conventional multiply. This causes another speedup, since the critical path does not necessarily go through the full carry chain of the adder.

Calculation of the modular inverse is needed for solving systems of linear congruences as well as conversion from RNS to integer numbers. It is also used in cryptography especially in computing point operations on elliptic curves [5], or in accelerating the modular exponentiation operation using the so-called addition-subtraction chains [6].

#### 1. Introduction

The quality of hardware implemented algorithms is measured using the metrics of time, area and power consumption. The underlying technology is often an Application Specific Integrated Circuit (ASIC) or a reconfigurable architecture such as a Field Programmable Gate Array (FPGA). Other technology includes general purpose processors, DSPs or embedded microcontrollers.

#### 1.1 Structure of the Dissertation thesis

The thesis is organized as follows. Chapter 2 introduces basic definitions and terminology regarding Montgomery multiplication, modular inverse and systems of linear equations. Chapter 3 summarizes the previous work in this field. Chapter 4 presents our architecture modifications. Chapter 5 presents our results in the form of a collection of published papers, and Chapter 6 concludes with outlines for future work.

# Theoretical Background and State-of-the-Art

In this chapter, we summarize the basics covering the problem of solving systems of linear equations in residue (modular) arithmetic. We also visit some of the individual operations needed, namely modular multiplication and modular inverse.

#### 2.1 Systems of linear equations

Let us assume the following linear system with a square matrix of coefficients **A** and a vector of right-hand sides  $b \neq 0$ . The task is to compute the solution vector x.

$$\mathbf{A}\boldsymbol{x} = \boldsymbol{b} \tag{2.1}$$

Most often the input values, i.e. the coefficients and right-hand sides of individual linear equations, are floating point numbers, sometimes integers. (We are not considering complex or irrational numbers.) Traditionally, solving of such systems is also done in floating point arithmetic, which brings its associated rounding errors.

There are many methods to solve such systems – direct methods like the Cramer's rule or Gaussian elimination, matrix decomposition methods like the LU decomposition (essentially equivalent to Gaussian elimination), QR decomposition or singular value decomposition, and also iterative methods like Jacobi method, Gauss-Seidel method, or conjugate gradient method.

Although there are algorithms that minimize the impact of rounding errors on the error of the solution, in some cases this is not enough. Error-free solution of linear systems is often needed in case of large, dense and ill-conditioned systems, where rounding errors can lead to long run times due to stability problems, or even hinder the solution completely. One of the methods to perform error-free computation is using the residue number system (RNS), and thus using modular arithmetic.

When considering which methods and algorithms are suitable for RNS, we must know what operations are required, and how easily can they be implemented in RNS. The operations needed for iterative methods include minimization of a vector of residuals that must fullfill a termination criterion, usually a small absolute value. Magnitude comparison operations are quite expensive in RNS, and the result is inherently imprecise, which is against the effort to get error-free solution. The QR and SVD decomposition methods need the square root operation, which cannot be implemented easily in RNS.

Matrix  $\mathbf{A}$  and vector  $\mathbf{b}$  can be given as rational or floating point numbers. In any case, the system (2.1) it can be transformed to an equivalent linear system with integer numbers by scaling individual rows of  $\mathbf{A}$  together with corresponding elements of  $\mathbf{b}$ . Therefore we can safely assume that all numbers are integers. Nevertheless, the elements of solution vector  $\mathbf{x}$  will be rational in general.

First, we will convert the input system into RNS, then we will use modular arithmetic, to compute the solution in RNS, and finally we will convert the solution from RNS to rational numbers. In order to get correct result in full precision, we need a sufficiently large modulus M, whose value can be derived from the Hadamard's inequality for the determinant D of matrix A:

$$D^2 \le \prod_{i=1}^n \sum_{k=1}^n a_{ik}^2 \tag{2.2}$$

The largest value M, that can be encountered in the computation of the linear system, is bound [7, 1] by

$$M > 2 \max \left\{ \begin{array}{ll} n^{\frac{n}{2}} \max(a_{ij})^n, & i, j = 1, 2, ..., n, \\ n(n-1)^{\frac{n-1}{2}} \max(a_{ij})^{n-1} \max(b_i), & i, j = 1, 2, ..., n \end{array} \right\}$$

(2.3)

and

$$\gcd(M, D) = 1. \tag{2.4}$$

The computation will be done using multiple-modulus residue arithmetic with the moduli forming a vector  $\boldsymbol{\beta} = (m_1, m_2, ..., m_r)$ , where  $m_i$  are distinct primes and  $\prod_i m_i = M$ . In practice, it would be unnecessary to enforce that the determinant D be coprime to M rigorously. If  $\gcd(M, D) \neq 1$ , it means that for some  $m_s$ ,  $\gcd(m_s, D) \neq 1$ . We can then exclude this  $m_s$  form our moduli vector  $\boldsymbol{\beta}$  and continue with the remaining moduli.

In this work, we will use a variant of Gaussian elimination – the Gauss-Jordan elimination algorithm. Gaussian elimination converts a matrix to its row echelon form, whereas Gauss-Jordan elimination converts it to a unity matrix (provided the matrix was square and full rank, i.e. invertible). If applied to the augmented matrix  $A = (\mathbf{A}|\mathbf{b})$  of the linear system (2.1), it produces the solution vector  $\mathbf{x}$  of the system.

The process of solving (2.1) using multi-modulus residue arithmetic can be done using the following method.

**Algorithm 2.1** Gauss-Jordan elimination algorithm modulo m without row swapping.

Inputs: A is the augmented matrix, n is matrix dimension. Output: Solution vector  $\boldsymbol{x}$  is the last column in A. 1. assuming pivot row *j* is found during loading of matrix 2. for k = 1..n begin  $A(j) = |A_{j,k}^{-1} A(j)|_m$ 3. for i = 1..n except j begin 4.  $A(i) = |A(i) - A_{i,k} A(j)|_m$ 5. 6. test new pivot, set pivot row  $j_{\text{new}}$ 7. end 8.  $j = j_{\text{new}}$ 9. end 10. return x as  $x_i = A_{i,n+1}$  for i = 1..n

- 1. Input scaling conversion of the input linear system from floating point (rational) numbers to integers.

- 2. Input conversion conversion of the system  $\mathbf{A}x = \mathbf{b}$  to systems of congruences  $\mathbf{A}x_k \equiv \mathbf{b} \pmod{m_k}$

- 3. Solving SLC solving r systems of linear congruences, computing  $\boldsymbol{x}_k$  and  $D_k = |\det A|_{m_k}$ , and also the product  $\boldsymbol{z}_k = |D_k \boldsymbol{x}_k|_{m_k}$ .

- 4. Output conversion conversion of  $|D_k|_{m_k}$  and  $z_k = |D_k x_k|_{m_k}$  into integers D and z

- 5. Solution finalization conversion of D and z into the final solution vector x

Input scaling is done by multiplying the coefficients the right hand side of each equation with their common denominator (or a multiple thereof) in order to get integers. This can be done for any rational coefficients and, provided floating point inputs, can be done just by binary shifting. A sequential implementation requires  $O(n^2)$  multiplications.

Input conversion means computing the residui of all elements of **A** and **b** modulo individual moduli  $m_k$ . This involves computing the remainder from the division of each coefficient by  $m_i$  and requires  $O(rn^2)$  operations.

Solving systems of linear congruences mod  $m_k$  by Gauss-Jordan elimination requires  $O(rn^3)$  operations. During the computation in each modulus, the operations needed are modular multiplicative inverse for each of the n pivots, and modular multiplication, addition, and subtraction (or additive inverse). Additionally, either row swapping or result reordering is needed for the cases when a pivot is not found directly at the diagonal.

Output conversion involves reconstruction of the rational solution vector  $\boldsymbol{x}$  from the individual solution vectors in each modulus. The values  $|D|_{m_k}$  and  $\boldsymbol{z}_k = |D\boldsymbol{x}|_{m_k}$  are converted into integers. A sequential Garner algorithm for Multi-Radix Conversion takes  $O(r^2n)$  operations.

Solution finalization results in the solution vector  $\mathbf{x} = \frac{\mathbf{z}}{D}$ . It is computed either as a precise rational number, or as a floating point number.

The computational complexity of the individual steps are summarized in table 2.1.

| Step                                       | 1        | 2         | 3         | 4         | 5    |

|--------------------------------------------|----------|-----------|-----------|-----------|------|

| Sequential computation                     | $O(n^2)$ | $O(rn^2)$ | $O(rn^3)$ | $O(r^2n)$ | O(n) |

| Row-parallel, modulo parallel architecture | $O(n^2)$ | O(n)      | $O(n^2)$  | O(rn)     | O(n) |

Table 2.1: Computational complexity of individual steps of solving a system of linear equations using RNS

The operations needed are modular addition, subtraction, multiplication and multiplicative inverse. The time complexity of individual operations depends of the hardware architecture of each functional unit. We will consider only arithmetic of the Galois field GF(p), where p is a prime number. Assume the bit length of p being e bits, i.e.  $e = \lceil \log_2 p \rceil$ . Modular addition (and subtraction) is a combination of binary addition and a modulo reduction. The time and area complexity of the operation depends on the architecture. Many different architectures exist for binary adders (ripple-carry, carry look-ahead, carry-select and many others). Depending on the word size and other constraints, number of concurrent additions and other parameters, bit-serial adders can be appropriate.

Modular multiplication can be performed by a variety of methods, most of which are based on a combination of integer multiplication and modulo reduction. The choice of multiplication method depends of the operand length and performance requirements. Apart from schoolbook (long) multiplication, other methods exist mainly for large numbers, such as Karatsuba [8], Toom-Cook [9], and Schönhage-Strassen [10].

Modulo reduction means computing a remainder after division. This can be computed after multiplication, or interleaved during the product computation. For relatively small operands that fit in the machine word (tens of bits), a variant of the schoolbook multiplication is suitable, as it is easily interleaved with reduction steps to maintain the intermediate result within the machine word. Multiplication takes e additions, shifts and modular reductions in the computation.

The most complex elementary operation is the modular inverse. Several different algorithms exist for the inverse. In GF(p), algorithms based on the Extended Euclidean Algorithm are prevalent. Their operational complexity is derived from the binary GCD computation, whose average number of cycles is 1.4e.

In the following sections, we will present a brief overview of the mathematical background of arithmetic operations that are suitable for a solver of linear equations in modular arithmetic. In section 2.2, we deal with Montgomery multiplication, a special type of modular multiplication that is often used due to its efficient hardware implementation. In section 2.3, we will present a summary of the basic principles of modular inverse.

#### 2.2 Montgomery multiplication

Montgomery multiplication is a method for computing modular multiplication. It operates on a special representation of residue classes, often called the Montgomery domain. The Montgomery domain is a set of images, also called N-residues.

**Definition 2.2.1.** Let N, a be integers, N > 1,  $0 \le a < N$ . Let R be an integer coprime to N and R > N. The N-residue (Montgomery image)  $\overline{a}$  of a is defined as  $\overline{a} = |aR|_N$ .

Let  $R^{-1}$  and N' be integers satisfying

$$0 < R^{-1} < N, 0 < N' < R, RR^{-1} - NN' = 1$$

(2.5)

The Montgomery multiplication computes:

$$\overline{c} = \mathrm{MM}(\overline{a}, \overline{b}) = |\overline{a}\overline{b}R^{-1}|_N$$

It can be shown that  $\bar{c}$  is the Montgomery image of c = ab, since

$$\overline{c} = |\overline{a}\overline{b}R^{-1}|_{N}$$

$$\overline{c} = |aRbRR^{-1}|_{N}$$

$$\overline{c} = |abR|_{N}$$

$$\overline{c} = |cR|_{N}$$

Further we can see that the addition algorithm is unmodified, as  $\bar{s} = |\bar{a} + \bar{b}|_N = |aR + bR|_N = |(a+b)R|_N = |sR|_N$  and thus we get the image of the sum by adding the images together. The same holds for subtraction.

In order to process integer numbers modulo N, we have to convert them to N-residues. After finishing computation in the Montgomery domain, we have to convert them back to the integer domain. We can perform forward as well as backward conversions using the same algorithm that we use for Montgomery multiplication. Observe that  $\overline{a} = |aR|_N = \text{MM}(a, R^2)$  and  $a = |\overline{a}R^{-1}|_N = \text{MM}(\overline{a}, 1)$ . The constant  $|R^2|_N$  can be precomputed and stored in the system as long as the modulus does not change too often.

Note: In this paper, we will no further distinguish between an integer a and its N-residue by its notation, since they are both integers of the same range. Their meaning is generally obvious, possible exceptions will be denoted explicitly.

#### 2.2.1 The original algorithm

Montgomery proposed the algorithm for modular multiplication without trial division in his paper [4]. We choose R in such a way that operations modulo R are inexpensive;

possibly the machine word size or a power thereof. Again,  $R^{-1}$  and N' are determined by  $0 < R^{-1} < N, 0 < N' < R, RR^{-1} - NN' = 1$ . Montgomery has shown that if  $0 \le T < RN$ , we can quickly compute  $|TR^{-1}|_N$  using the following algorithm.

#### Algorithm 2.2 Montgomery reduction

```

function REDC(T)

```

- 1.  $m := ||T|_R N'|_R$

- 2. t := (T + mN)/R

- 3. if  $t \ge N$  then return t N else return t

In order to get the Montgomery product  $\bar{c} = \text{MM}(\bar{a}, \bar{b})$ , we first perform an integer multiplication T = ab. Then we use Algorithm 2.2, c = REDC(T), to reduce T to  $|TR^{-1}|_N$ . Since  $0 \le a < N, 0 \le b < N$ , it holds that  $0 \le T < RN$  and thus the input condition is satisfied.

Notice that the reduction phase is presented independently of the multiplication phase. However, in this case we need sufficient space to store the result of the multiplication before the reduction is done. In order to save resources, we often interleave the two phases. The interleaving can be performed in a variety of means, some of them are presented below.

#### 2.2.2 Choice of radix

As we stated above, we choose R to be such a value that operations modulo R are inexpensive to process. This usually means that R is  $2^k$ , where k is the number of bits in the binary representation of the operands and the result. We perform operations modulo R in the step (1) of Algorithm 2.2. If we interleave the multiplication and reduction phases, we have a wide variety of options how to organize the computation.

Let r, e, w be positive integers, r > 1. If we choose R = re, then r is the radix of our arithmetic operations. Usually we set  $r = 2^w$ ,  $R = r^e = 2^{ew}$ . We express the operands and product as  $A = \sum_{i=0}^{e-1} a_i r^i$ ,  $B = \sum_{i=0}^{e-1} b_i r^i$  and  $S = \sum_{i=0}^{e-1} s_i r^i$ . We can also express the modulus N as  $N = \sum_{i=0}^{e-1} n_i r^i$  and take advantage of the digit representation by using only the least significant digit of N' for the reduction:  $n'_0 = |-n_0^{-1}|_r$ . The computation can be then expressed as follows: (Note that we do not perform the final subtraction, see below.)

#### 2.2.3 Binary radix Montgomery multiplication

Binary Montgomery multiplication is a special case where r=2. Assuming that  $A=\sum_{i=0}^{e-1}a_i2^i$ ,  $B=\sum_{i=0}^{e-1}b_i2^i$  and  $S=\sum_{i=0}^{e-1}s_i2^i$ , we may describe the basic binary Montgomery multiplication algorithm as presented in Algorithm 2.4. The binary version has the advantage that we need not compute N', since the reduction is performed such that the quotient q is a single bit. Given r=2 the multiplication factor  $n'_0$  in step 3 is always  $n'_0=|-N^{-1}|_2=1$ .

#### Algorithm 2.3 High-radix Montgomery multiplication

```

Inputs: A, B, N, e

Output: S = MM'(A, B)

1. S := 0

2. for i = 0 to e - 1

3. q := |(s_0 + a_i b_0) n'_0|_r

4. S := S + a_i B + qN

5. S := S/r

6. end for

7. return S

```

#### Algorithm 2.4 Binary-radix Montgomery multiplication

```

Inputs: A, B, N, k

Output: S = \text{MM}'(A, B)

1. S := 0

2. for i = 0 to k - 1

3. q := s_0 + a_i b_0

4. S := S + a_i B + q N

5. S := S/2

6. end for

7. return S

```

#### 2.2.4 Final subtraction

Step (3) of Algorithm 2.2 guarantees that the result is always less than N. However, the comparison made here implies a subtraction with a consequent sign check of possibly very long operands. This is unfortunate, since this operation is very slow. There have been efforts to avoid the final subtraction step at all. The paper in [11] shows that for Algorithm 2.3, the result of the Montgomery multiplication is bound, S = MM'(A, B) < 2N, as long as A < 2N, B < 2N and  $2N < r^{e-1}$ . Another paper [12] improves this bound to  $N < 2^{(e-1)w}$  at the cost that  $w \ge 2$ . This means that we have to relax the constraints on the operands A, B, while at the same time increasing the number of digits we compute. In both cases, we have to compute at least one more digit as opposed to the algorithm with final subtraction. It is important to know that we get properly reduced output once we convert the result S using MM'(S,1). This is proved in [11].

#### 2.2.5 Choice of encoding

We have multiple choices how to encode the operands and the (partial) product of the multiplication.

• Binary encoding

- Carry-save encoding

- Signed-digit encoding

We can also specify different encoding for individual variables in the algorithm. We decide how to encode each of the following:

- Multiplication operands

- Partial product

Binary encoding is non-redundant, having the advantage that we do not need additional conversions of the operands and/or the product. The drawback is that long binary addition can be slow because of the carry path in the adders. This can be mitigated by using faster adders such as carry look-ahead or carry completion adders. The area overhead and limited scalability of such adders however makes them unsuitable in most cases.

There are platforms, such as Field Programmable Gate Arrays (FPGAs), which have fast dedicated resources for carry chains and thus are (to a certain limit) less sensible to word length when performing binary addition.

Carry-save and signed-digit encodings are redundant, making conversions necessary when the result is to be used outside of the algorithm. Redundant representations are used to achieve higher working frequency of the resulting hardware since they avoid direct carry propagation through very long adders.

In order to implement more complex computation, such as a modular exponentiation, it is necessary to reuse the result of one multiplication in subsequent multiplications. Hence, it is desirable to avoid unnecessary conversions between redundant and non redundant forms of any of the operands. This can be solved by leaving both operands A, B as well as the result S in carry-save form. This approach ensures high throughput of modular exponentiation because the intermediate results can be directly used as operands of the next multiplication.

#### 2.3 Modular Inverse

Modular (multiplicative) inverse  $MI(a) = |a^{-1}|_m$  of an integer a modulo m is defined as a number satisfying  $aa^{-1} \equiv 1 \pmod{m}$ , or  $|aa^{-1}|_m = 1$ . There are several algorithms for computing the modular inverse, mainly using Fermat's little theorem, or a variant of the Euclidean algorithm. In this work, we consider several different variants of the Euclidean algorithm. The most straightforward algorithm is the extended Euclidean algorithm (EEA), which uses repeated integer division to compute the greatest common divisor  $\gcd(a, m)$  and two coefficients x, y of Bézout's identity

$$\gcd(a, m) = ax + my. \tag{2.6}$$

If gcd(a, m) = 1, then it x is the multiplicative inverse of a modulo m. The coefficient y is usually not needed, therefore it is not computed at all. A reduced form of EEA, which computes only the inverse, is given in Algorithm 2.5.

#### Algorithm 2.5 Extended Euclidean algorithm for modular inverse

```

Input: Integers a \in [1, m-1] and m > 2

Output: r = |a^{-1}|_m or error

u := m, v := a, r := 0, s := 1, k := 0

1.

2.

while (v \neq 0)

3.

q := |u/v|

4.

v_{\text{new}} := u - qv, u := v, v := v_{\text{new}}

5.

s_{\text{new}} := r - qs, r := s, s := s_{\text{new}}

6.

if (u \neq 1) return "Not relatively prime"

7.

if (r < 0) r := r + m

8.

return r

```

Notice the algorithm can be split in two parts – the master part computes the greatest common divisor, represented by the variables u and v in Algorithm 2.5. The slave part computes the modular inverse (variables r, s) and is controlled by the master part by the quotient q computed in step 3.

In hardware implementations, the division operation used in step 3 of Algorithm 2.5 would be unnecessary expensive. However, division by two is very cheap and is done by shifting. A binary variant of EEA can be formulated in Algorithm 2.6. This algorithm, attributed to M. Penk, is mentioned (in a slightly different form) in [13] (answer to exercise 39 of section 4.5.2). This algorithm performs halving in both the master part (variables a, b) and the slave part  $(f_1, f_2, g_1, g_2)$ . In order to enable division by two, the algorithm tests if the variable is even. If not, a suitable odd value is added or subtracted to ensure the value can be halved. This can be simplified using the Montgomery inverse described in the next section.

#### Algorithm 2.6 Extended Binary GCD Euclidean Algorithm

```

Input: a, b \in \mathbb{Z} and a > b > 0

Output: gcd(a, b) = xa + yb and x, y \in \mathbb{Z}

k := 0, f_1 := 1, f_2 := 0, g_1 := 0, g_2 := 1

2.

while (a \text{ even } \land b \text{ even})

3.

a := a/2, b := b/2, k := k + 1

4.

while (a > 0)

5.

if (a \text{ even}) then

6.

a := a/2

7.

if (f_1 \text{ even } \land g_1 \text{ even}) then

8.

f_1 := f_1/2, g_1 := g_1/2

9.

else

f_1 := (f_1 + b)/2, g_1 := (g_1 - a)/2

10.

else if (b \text{ even}) then

11.

12.

b := b/2

if (f_2 \text{ even } \land g_2 \text{ even}) then

13.

f_2 := f_2/2, g_2 := g_2/2

14.

15.

else

f_2 := (f_2 + b)/2, g_2 := (g_2 - a)/2

16.

17.

else

18.

c := (a - b), d := f_1 - f_2, e := g_1 - g_2

19.

if (c \ge 0) then

20.

a := c, f_1 := d, g_1 := e

21.

else

b := -c, f_2 := -d, g_2 := -e

22.

23. return gcd(a,b) := 2^k b and x := f_2, y := g_2

```

#### 2.3.1 Montgomery Inverse

Montgomery modular inverse was introduced in 1995 by Kaliski [14] in the form  $|a^{-1}2^n|_p$ . The algorithm consists of two phases. The first phase computes  $|a^{-1}2^k|_p$ , where  $k \geq n$ . The second phase then divides this intermediate result by  $2^{k-n}$  modulo p, yielding  $|a^{-1}2^n|_p$ . This algorithm can be used to compute modular inverse of an argument in the Montgomery domain while obtaining the resulting inverse in the integer domain:  $|(x2^n)^{-1}2^n|_p = |x^{-1}|_p$ . This is not always useful when we want to stay with the operands in the Montgomery domain.

Savaş and Koç presented a modified algorithm [15] (Algorithm 2.7) that maintains the Montgomery domain. This means that the modified Montgomery inverse takes the argument in the Montgomery domain and provides the result also in Montgomery domain. The first phase remains the same computing  $|a^{-1}2^k|_p$ , but the second phase is modified to multiply the intermediate result by  $2^{2n-k}$  modulo p, yielding  $MMI(a) = |a^{-1}2^{2n}|_p$ . When computing the inverse of an argument in the Montgomery domain, we get  $|(x2^n)^{-1}2^{2n}|_p =$  $|x^{-1}2^n|_p$ .

The first phase of Motgomery inverse is referred to as Almost montgomery inverse  $AMI(a) = |a^{-1}2^k|_p$ . Therefore  $MMI(a) = |AMI(a)2^{2n-k}|_p = |MI(a)2^{2n}|_p$ .

#### Algorithm 2.7 Montgomery modular inverse

```

Input: a \in [1, p-1] and p > 2 is prime, n number of bits in p

Output: r \in [1, p-1], where r = |a^{-1}2^{2n}|_p

Phase I (Almost montgomery inverse)

u := p, v := a, r := 0, s := 1, k := 0

1.

2.

while (v > 0)

if (u \text{ even}) then

u := u/2, s := 2s

3.

v := v/2, r := 2r

4.

else if (v \text{ even}) then

u := (u - v)/2, r := r + s, s := 2s

else if (u > v) then

5.

v := (v - u)/2, s := r + s, r := 2r

6.

else

7.

k := k + 1

if (u \neq 1) then return "Not relatively prime"

8.

if (r \ge p) then r := r - p

9.

Phase II (Savaş, Koç)

10. while (k \neq 2n)

r := 2r

11.

12.

if (r \geq p) then r := r - p

14.

k := k + 1

15. return r

```

#### 2.3.2 Left-Shift Inverse

In the previous algorithms, the master part, computing the greatest common divisor, was shifted to the right. On the contrary, the algorithm by Lórencz [16] shifts the master variables u and v to the left. The algorithm is referred to as Left-Shift Inverse (LSI) and will be described in section 3.3.2 in the next chapter.

## Previous Results and Related Work

Solving systems of linear equations, being one of the most often performed tasks in scientific computation, enjoys constant devotion of the scientific community. The majority of implementations today use floating point arithmetic on (clusters of) general purpose CPUs, or, more recently, GPUs.

Recent hardware based solvers almost exclusively use floating point arithmetic. Zhang et al. use FPGAs to implement LU decomposition in FP arithmetic without pivoting with the focus on portability among different FPGA platforms [17]. The problem of rounding errors can be addressed by special FP arithmetic and iterative refinement as in [18, 19], or increasign FP precision to Double-Double (128 bits) and Quad-Double (256 bits) [20].

In this chapter we present the summary of previous results on solving systems of linear equations in modular arithmetic, the state-of-the-art of Montgomery multiplication and modular inverse.

# 3.1 Modular system for solving systems of linear equations

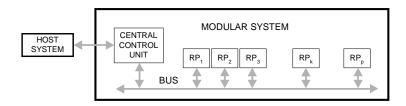

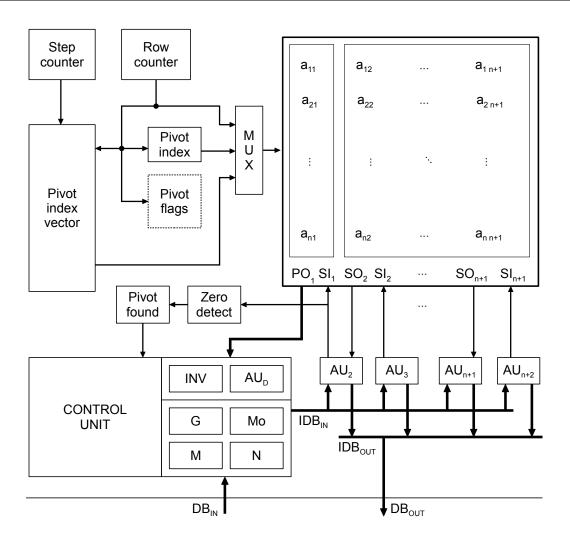

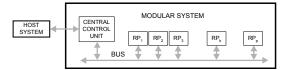

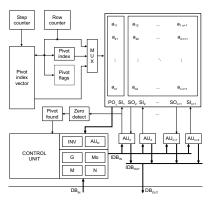

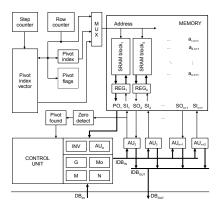

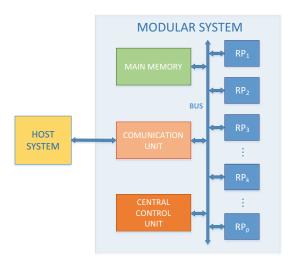

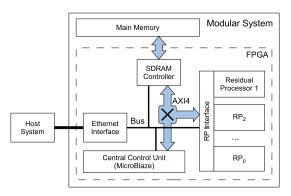

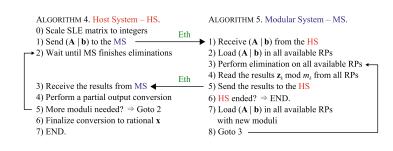

Lórencz and Morháč [1, 2] presented a design of a parallel hardware system for solving dense sets of linear equations precisely. The architecture is presented at fig. 3.1. The modular system uses an array of processing units interconnected together and with a master control unit via buses.

The residual processor uses Gauss-Jordan (GJ) elimination with Rutishauser modification to solve the system of linear congruences. GJ elimination has the advantage of regular memory access pattern and associated regular arithmetic operations. A normal GJ algorithm would produce a reduced row echelon form matrix with a solution of the associated system of linear equations in the last column. We can simplify the GJ algorithm by omitting any row swapping at the expense of having to reorder the solution vector. This GJ algorithm was described in Algorithm 2.1.

Figure 3.1: Modular system for solving systems of linear equations exactly [1, 2].

Rutishauser modification of Gauss-Jordan elimination discards the unity submatrix produced in the GJ algorithm by shifting the matrix one column to the left as each row is processed. This affects two important operands in Algorithm 3.1, namely the pivot  $A_{j,k}$  (step 3) and the element  $A_{i,k}$  controling the row reduction in step 5. Both these values will always appear in the first column of the matrix, which simplifies the search for pivot and effectively simplifies the design of the memory interface.

#### **Algorithm 3.1** Rutishauser modification of Gauss-Jordan elimination modulo m.

```

Input: A is the augmented matrix, n is matrix dimension.

Output: Solution vector \boldsymbol{x} is the first column in A.

assuming pivot row j is found during loading of matrix

1.

2.

for k = 1..n begin

A(j, 1..n - k) = |A_{j,1}^{-1} A(j, 2..n - k + 1)|_m

3.

4.

for i = 1..n except j begin

5.

A(i, 1..n - k) = |A(i, 2..n - k + 1) - A_{i,1} A(j)|_{m}

6.

test new pivot, set pivot row j_{\text{new}}

7.

end

8.

j = j_{\text{new}}

9.

return \boldsymbol{x} as x_i = A_{i,1} for i = 1..n

```

#### 3.2 Montgomery multiplication

There are many published papers regarding analysis and implementation of Montgomery multiplication. Most of them concern applications in cryptography, especially RSA. Others deal with Diffie-Hellman key exchange, elliptic curves or focus on the multiplication algorithm itself. We present a summary of some of the published work.

#### 3.2.1 Software approaches

Although we focus on hardware implementation, there are some publications concerning software implementation that are worth mentioning.

Software implementations are designated to run on general-purpose or other processors (vector processors, DSPs). As such, they are specific in that they are limited to fixed word size operations of the particular processor. In order to be able to process long operands, they use multiprecision arithmetic. They often use high-radix algorithms to utilize the word-size granularity of the processors.

A basic adaptation to multiprecision arithmetic is presented in Montgomery's original paper [4]. However, this algorithm is not optimal since it always uses the full length of N' (2.5), which involves more multiplications than necessary. The paper [21] presents a faster way to determine the quotient for modular reduction when we take advantage of the fact that we compute one digit at a time. This is used in Algorithm 2.3, where it suffices to use a single precision arithmetic to compute q using  $n'_0$  (which is also a single digit).

The paper [22] brings an overview of five selected software methods and analyzes their time and memory requirements.

#### 3.2.2 Hardware approaches

There are many hardware implementations of Montgomery multiplication ranging from simple sequential architectures implementing the binary variant of the algorithm to complex unified GF(p) and  $GF(2^n)$  pipelined and high-radix architectures.

A basic sequential hardware implementation is sketched in Montgomery's original paper [4] using binary version of the algorithm. Although the paper does not present any hardware architecture, it creates a base on which other authors can build. Several options regarding hardware implementation of modular multiplication are presented in [23].

High-radix implementation on FPGA was presented in [24]. The authors used the Xilinx XC4000 FPGA family. They used a radix of 16 and adopted a technique for simplified quotient determination from [25]. The paper presents also an exponentiation unit and contains a comparison of different configurations used for RSA encryption and decryption. Other high-radix implementations include [26] and [27].

The paper [28] deals with a systolic binary implementation on the Xilinx Virtex V1000-FG680-6 FPGA. The authors present three modifications of the binary Montgomery multiplication algorithm.

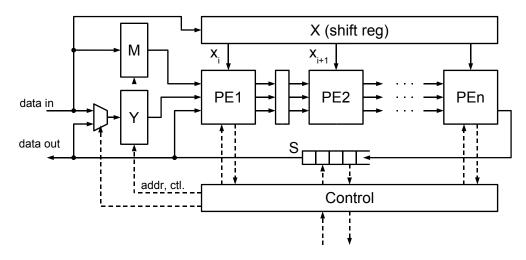

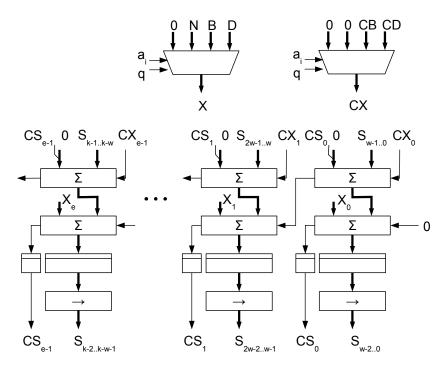

Pipelined semi-systolic implementations presented in [29], [30], [31] are targeted at ASIC hardware. The operands are divided into words, resulting in a modified algorithm (Algorithm 3.2). The operand Y, the modulus M and the result S are composed of e words of size w. We add one more word that will be always zero in order to simplify the right-shift operation, since the least significant bit is shifted towards the lower word.

We need the trailing zero word in order to get the last valid word  $S^{(e-1)}$  at the end of the inner loop of Algorithm 3.1. Thus  $Y = (0, Y^{(e-1)}, ..., Y^{(0)}), M = (0, M^{(e-1)}, ..., M^{(0)}), S = (0, S^{(e-1)}, ..., S^{(0)})$  and  $X = (x_{n-1}, ..., x_0)$ , where the words are marked with superscripts and the bits are marked with subscripts.

The architectures presented are unified, i.e. able to compute in both GF(p) and  $GF(2^n)$ . The architectures are also scalable, providing a means of working with arbitrary-length keys and are configurable in word size and pipeline depth. These architectures were the base

#### Algorithm 3.2 Multi-word Montgomery multiplication

```

Inputs: X, Y: operands, M: modulus, n: bit width, w: word size, e: number of words

Output: S: MM(X,Y)

1. S := 0

2. for i = 0 to n - 1

for j = 0 to e

3.

(c_0, S^{(j)}) := S(j) + x_i Y^{(j)} + c_0

4.

if j = 0 then q := S_0

5.

(c_1, S^{(j)}) := S^{(j)} + qM^{(j)} + c_1

6.

if j > 0 then S^{(j-1)} := (S_0^{(j)}, S_{w-1..1}^{(j-1)})

7.

8.

end for

9. end for

10. return S

```

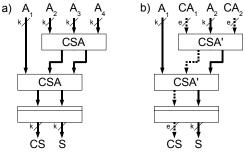

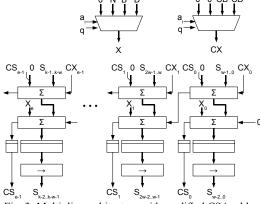

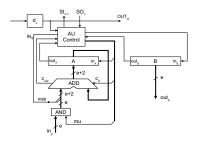

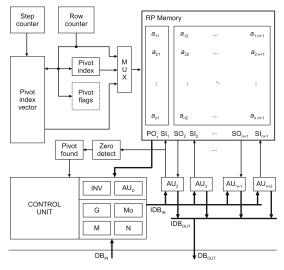

of one of our experiments. Figure 3.2 shows the pipelined architecture and Figure 3.3 depicts the processing element. The architectures make use of carry-save encoding of the partial product S in order to achieve shorter critical path. The result must be converted to non-redundant binary representation before it can be reused in subsequent multiplications (not shown in the picture).

Figure 3.2: Scalable pipelined implementation of the Montgomery multiplier.

Another approach is presented in [32], where both operands and the product are in carry-save form. The architecture is sequential, utilizing full-length adder trees, i.e. the adders are as long as the operands. Two different architectures are presented. They differ in the number of operands in the adder tree. The former one, five-to-two Carry Save Adder (CSA), uses carry-save adder tree to sum all the components. The latter one, four-to-two

Figure 3.3: Pipeline processing element.

CSA, involves smaller adder tree and uses multiplexers and precomputed constants. The variables D and CD are computed at the start of the multiplication and stored in registers.

#### Algorithm 3.3 Binary Montgomery multiplication with carry-save encoding

```

Inputs: A, CA, B, CB, N, k

Output: (CS, S) = MM(CA, A, CB, B)

1. (CD, D) := CB + B + N

2. (CS, S) := 0

3. for i = 0 to k - 1

q := |CS + S + a_i(CB + B)|_2

5.

if ai = 0 and q = 0 then (CX, X) = (0, 0)

elsif a_i = 0 and q = 1 then (CX, X) = (0, N)

6.

7.

elsif a_i = 1 and q = 0 then (CX, X) = (CB, B)

8.

else (CX, X) = (CD, D)

9.

end if

(CS, S) := (CS + S + CX + X)/2

10.

11. end for

12. return (CS, S)

```

#### 3.3 Modular Inverse

There are several papers that describe a hardware implementation of modular multiplicative inverse. The papers [33, 34] present a scalable architecture that deals with inversion of very long numbers that are frequently encountered in cryptography. These operands may be thousands of bits long and are typically stored and processed in a multi-word format. The architecture [34] is designed as unified, i.e. it can perform inversion in GF(p) as well as  $GF(2^n)$ . A different approach is taken in [35] which uses carry-free arithmetic using a redundant binary encoding using signed digit number representation.

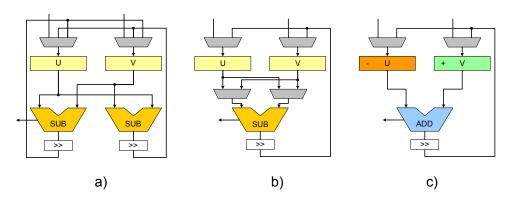

Our efforts focus on shorter numbers (tens to hundreds of bits), which are suitable for error-free computation (and may also be used in elliptic curves cryptography), and therefore we focus mainly on small and fast data paths and controllers. The paper [36] presents a hardware implementation of an ordinary modular inverse using AMI (Almost montgomery inverse, Phase I of MMI) with a modified second phase to obtain MI(a).

#### 3.3.1 Subtraction-Free Montgomery Inverse

The Montgomery modular inverse can be further improved when we focus on the comparison and subtraction operations. Lórencz and Hlaváč in 2005 [37] shown that a negative result of subtraction that would normally have to be discarded can be used without further correction when we exploit the two's complement encoding of the result. This is taken to the extreme so that the u register is always negative and the v always positive, thus the effect of subtraction in the previous inversion algorithms is attained usign addition.

The algorithm thus does not involve any subtractions at all, thus its name — subtraction-free Montgomery modular inverse. The paper [37] focuses only on the first phase of MMI – the Almost Montgomery inverse, see Algorithm 3.4.

#### 3.3.2 Left-Shift Inverse

Modular multiplicative inversion algorithms in GF(p) are often based on the binary extended euclidean algorithm with the operands being compared, subtracted and shifted to the right. However, the modular inversion can also be computed by shifting the operands left, thus aligning them to the most significant bit. The left shifting inversion algorithm was first published in [16]. Recently, this algorithm was used in [38] to design an arithmetic unit for computations in GF(p) with implementation in FPGA.

The algorithm can be split to three parts – the initialization, the main loop which takes a variable number of cycles to complete, and the postprocessing which takes a fixed number of steps.

The algorithm holds five operands in its registers u, v, r, s, p. The u and v registers are used to compute the greatest common divisor of the argument a and the modulus p. Upon initialization u is set to p and v is set to a. The GCD is expected to be 1 for the inverse to exist, but as the values are shifted to the left, the resulting GCD is also shifted and therefore the computed value becomes a power of two. The number of shifts of u is stored

#### **Algorithm 3.4** Subtraction-Free AMI

```

Input: a \in [1, p-1] and p > 2 is prime

Output: o \in [1, p-1] and k, where

o = a^{-1}2^k \bmod p \text{ and } n - 1 \le k < 2n

u \leftarrow (-p), v \leftarrow a, r \leftarrow 0, s \leftarrow 1, k \leftarrow 0

1.

2.

3.

if (u_{LSB} == 0) then

4.

u \leftarrow u/2, s \leftarrow 2s

else if (v_{LSB} == 0)

5.

v \leftarrow v/2, r \leftarrow 2r

6.

7.

else

8.

x = u + v, y = r + s

9.

if (CARRY(x) == 0) then

10.

u \leftarrow x/2, r \leftarrow y, s \leftarrow 2s

11.

else

v \leftarrow x/2, s \leftarrow y, r \leftarrow 2r

12.

13.

k \leftarrow k + 1

14

while (x \neq 0)

15.

return o \leftarrow s and k

```

in the counter  $c_u$ , the number of shifts of v is stored in  $c_v$ . Moreover both positive and negative subresults are allowed, so the algorithm will stop as soon as  $u = \pm 2^{c_u}$  or  $v = \pm 2^{c_v}$ . The operations performed on u and v are selected according to the the most significant bits – generally they are shifted to the left whenever possible, otherwise their sign is compared and they are subtracted when their sign is equal or added when their sign is different.

The r and s registers are used to compute the multiplicative inverse. Initialized to r := 0 and s := 1, the operations with r and s are governed by the values of u and v.

The arithmetic operations involved in the algorithm are u+v, u-v, v-u, r+s, r-s, s-r in table 3.1.

| Destination    | Initial | Main cycle |     |       |     | Postprocessing |    |     |     |

|----------------|---------|------------|-----|-------|-----|----------------|----|-----|-----|

| $\overline{u}$ | p       | 2u         |     | u + v | u-v |                |    |     |     |

| v              | a       | 2v         |     | u+v   | v-u |                |    |     |     |

| r              | 0       | 2r         | r/2 | r+s   | r-s | s              | -r | p-r | r+p |

| s              | 1       | 2r         | s/2 | r+s   | s-r |                |    |     |     |

Table 3.1: Left-Shift Inverse operation summary

The main loop of the algorithm can be split to the "master" part – computation with u, v, c u, c v, and the "slave" part computing with r, s. The "master" part completely

#### Algorithm 3.5 Left-Shift Inverse algorithm

```

Input: a \in [1, p-1] and p

Output: r \in [1, p-1], where r = a^{-1} \mod p, c_u, c_v

and 0 < c_v + c_u \le 2n

1. u := p, v := a, r := 0, s := 1

2. c u = 0, c_v = 0

3. while (u \neq \pm 2^{c} - u \& v \neq \pm 2^{c} - v)

if (u_n, u_{n-1} = 0) or (u_n, u_{n-1} = 1 \& OR(u_{n-2}, ..., u_0) = 1) then

5.

if (c \ u \ge c \ v) then

6.

u := 2u, r := 2r, c \quad u = c \quad u + 1

7.

else

8.

u := 2u, s := s/2, c_u = c_u + 1

9.

else if (v_n, v_{n-1} = 0) or (v_n, v_{n-1} = 1 \& OR(v_{n-2}, ..., v_0) = 1) then

10.

if (c \ v \ge c \ u) then

11.

v := 2v, s := 2s, c_v = c_v + 1

12.

else

v := 2v, r := r/2, c \quad v = c \quad v + 1

13.

14. else

15.

if (v_n = u_n) then

oper = " - "

16.

17.

else

oper = " + "

18.

19.

if (c \ u \leq c \ v) then

20.

u = u oper v, r = r oper s

21.

else

22.

v = v oper u, s = s oper r

23. if (v = \pm 2^c - v) then

24. r := s, u_n := v_n

25. if (u_n = 1) then

26. if (r < 0) then

27.

r := -r

28. else

29.

r := p - r

30. if (r < 0) then

31. r := r + p

32. return r, c u, and c v.

```

determines the computation of the "slave" part.

The main cycle ends when  $u=\pm 2^{c_{-}u}$  or  $v=\pm 2^{c_{-}v}$ . This can happen either at the beginning when a=1 and thus v=1, or during the computation after addition or subtraction.

## Overview of Our Approach

Optimal implementation is such an implementation that realizes the algorithm and has an optimum metric in time, area, power consumption or some combination of those. Our optimization goals are time and area, we also analyze the time-area product (sometimes called the quality factor).

The optimization process can done at several levels – from the most general system level downto the physical implementation on silicon. We consider a subset of these levels for our optimization namely the algorithmic level, register transfer level, and gate level. We will follow these basic steps:

- Algorithm selection

- Structure design

- Technology selection

- RTL to gate level synthesis

Algorithm selection. At the algorithmic level, we select the algorithms according to their suitability for hardware implementation. This criterion is the reason for selection of binary variants of the algorithms. We further analyze the selected algorithms with regard to the operations involved in them. We examine the operation count and the data flow in the course of computation. We also analyze the conditions used in branches and loops and the corresponding control flow. We describe the algorithm using a programming language and simulate its behavior in order to gather statistical data about the data and control flows. For high level analysis we use the C/C++ programming language with the NTL [39] library to simulate operations with numbers that do not fit into the machine word size. This analysis serves as a foundation for the first synthesis step which transforms the algorithm to the register transfer level. We use Wolfram Mathematica for verification of correct solution of more complex tasks like solving systems of linear congruences.

**Structure design.** The next step is to design and analyse the structure of the hardware unit on the register transfer level. The hardware unit at this level consists of blocks

that implement registers, multiplexers, adders, subtractors etc. The types of operations and their occurence in the data flow influence the types and counts of the blocks and their interconnection. Planning together with resource alocation result in the structure of data path and the behavior of the controller that will control the computation. Operand encoding must be considered when implementing arithmetic operations. If specific encoding follows directly from the implementation of an operation, such as the two's complement code after subtraction with negative result, this knowledge can be applied to the original algorithm.

We can describe the hardware unit using a variety of formal methods, including schematics, graphs, tables and hardware description languages (HDLs). We chose a HDL to describe the hardware unit because of the flexibility it can offer when describing parametrized hardware. We have chosen VHDL — other HDLs, such as Verilog, would be equally useful. We use VHDL generics to specify operand length, word length, number of words and other parameters. We describe the hardware units manually at the register transfer level in order to have full control over the architecture while still utilizing the low level optimization and technology mapping capabilities of synthesis tools.

At the RTL level we also perform simulation in order to verify correct function of the described architecture. We write a behavioral VHDL testbench that reads a set of stimuli from a file and exercises the VHDL model of the unit while comparing the outputs with the correct values generated from our C++ and Mathematica programs. We use Mentor Graphics' ModelSim simulator to simulate the model.

Technology selection and RTL to gate level synthesis. The RTL specification is then synthesized to the gate level of the particular hardware platform (FPGA or ASIC). The synthesis tools used for this task are configured using technology libraries.

Each implementation platform has its specific properties that influence the implementation. FPGAs have a more coarse granularity and offer dedicated structures mainly for arithmetic operations such as adders and subtractors, multipliers etc. These dedicated structures can hide some complexity because the cost (area, delay) is lower than when the same function is implemented using general logic. ASICs feature a finer granularity depending on the level of customization. We use a standard cell technology library that provides the functional and quantitative description of elementary logic cells. The synthesis of complex cells such as adders is then controlled by the synthesis library which provides one or more ways to compose a complex cell from elementary cells, e.g. ripple-carry adders or carry look-adead adders.

Another important feature of ASIC synthesis is gate sizing. This is enabled by the technology library containing several cells with same function differing in the size of their internal transistors, thus with different delay and area values. The synthesis tool can then trade delay for area by selecting the appropriate cell variation.

Memory arrays require special attention because ASIC synthesis tools cannot infer memory elements other than registers form the standard cell library. In order to use onchip memories, we need technology libraries that come with memory compilers. We use the memory compiler to create memory blocks of appropriate size and then we can use (instantiate) them in our VHDL design. The synthesis process results in a gate level netlist of the designed circuit. This model is more detailed than the source RTL VHDL model because it is described using technology cells from the library. Design area and delays are estimated from the netlist and can be annotated to the individual gates and signals in the circuit. Because the operations are performed on individual bits of the operands, each bit can have a different delay. This information can be utilized on the RTL or even algorithmic level to further modify and optimize the algorithm and its architecture.

We synthesize the hardware unit to two different technologies. First target technology is the Xilinx FPGA, for example Virtex2 (xc2v4000) or Virtex6 (xc6vsx475t). We use Xilinx ISE toolchain with XST for synthesis. We synthesize the unit and perform placement and routing. The time and area data is extracted from the placed and routed result. Second target technology is  $0.13\mu$  ASIC (TSMC or GlobalFoundries) with Synopsys Design Compiler 2005.09 SP2 (RTL synthesis). The time and area data is a post-synthesis estimate extracted from the synthesized netlist using time and area reporting in Design Compiler.

We perform synthesis of several variants of the architecture parametrized to several different operand lengths and word lengths, where applicable. For a selected subset of models we also perform post-place and route and post-synthesis simulation in order to verify the correct function of the resulting detailed model. For the FPGA technology we perform post-place and route simulation using Simprim simulation libraries and ModelSim. For the ASIC technology we perform post-synthesis simulation using a simulation library converted form the synthesis library using Synopsys Library Compiler and ModelSim.

We present two modifications of existing architectures for mongomery multiplication, both implemented in FPGA. The former one is a pipelined multiplier, where we study the effect of the underlying FPGA architecture on variable word size and pipeline depth. The latter one is based on a sequential carry-save architecture where both the operands and the partial product are encoded in carry-save form. We modify the carry-save encoding in that we reduce the redundancy and take advantage of the fast dedicated carry chains in the FPGA.

Among various algorithms for computing the multiplicative modular inverse we have selected two, montgomery modular inverse and left-shift inverse. We focus on optimizing these two algorithms and their variants and comparing their relative implementation metrics in FPGA and ASIC. The algorithms were selected because of their suitability for use in GF(p) and our previous experience. Montgomery inverse is frequently used and its variants and associated architectures are under constant development. The Subtraction-Free algorithm for the Almost Montgomery Inverse [37] was recently published at the time of our research. The Left-Shift Inverse algorithm [16] for the classical modular inverse was promising because of the low number of subtractions needed to compute the inverse. Both variants were originally studied for the purpose of implementing cryptographic algorithms, they are however also suitable for solving systems of linear congruences.

Finally we implement a dedicated hardware processor for solving systems of linear congruences in FPGA and ASIC. We use internal on-chip memory in the form of BLOCKRAM in FPGA and synchronous static memory block compiled using special memory compiler in ASIC.

# 4.1 FPGA implementation of a pipelined Montgomery multiplier

The multi-word Montgomery multiplication algorithm can be implemented on various architectures in software and in hardware. The architecture consists of a computing pipeline of p processing elements. Each processing element (PE) consists of 2 partial product generators, 2 adders and a shift and alignment layer, which includes registers. The latency of a single PE is 1 clock cycle. The PEs are separated by registers, therefore the latency of one pipeline stage is 2 clock cycles.

The Y operand and the modulus M are stored in memory. The X operand is stored in a shift register, since after  $x_i$  was used in the computation, it is no longer needed and can be discarded. The partial results coming out of the pipeline are stored in a queue until they can be used again in the computation.

Our architecture [A.13] differs from [29] in that we do not use redundant carry-save form of the intermediate result, because the underlying FPGA architecture includes dedicated carry logic and interconnect. Therefore a binary adder that uses FPGA-specific carry chain is faster than a carry-save adder, as long as the carry chain is not split into pieces, which would involve additional delay since the general-purpose routing is much slower than the dedicated carry interconnection.

# 4.2 Montgomery multiplier with modified Carry-Save encoding

We consider implementation on a Field Programmable Gate Array (FPGA) reconfigurable hardware.

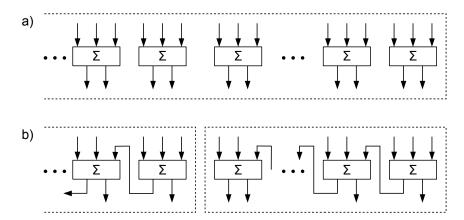

Our improvement of the architecture [32] is based on the fact, that in an FPGA, there is hardware dedicated for implementing fast ripple-carry adders. We can make use of it when considering the possible encoding of the operands.

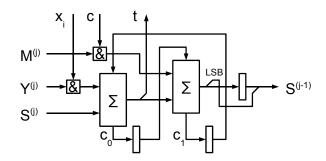

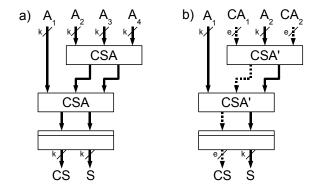

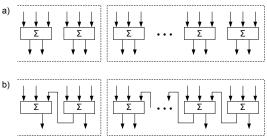

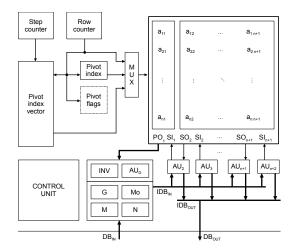

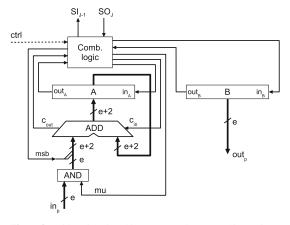

Instead of using normal carry save encoding, we modify the encoding such that a carry bit is "saved" only for each w-th bit. We break the operands into e words of length w, e = k/w. If w = 1, we get the conventional carry-save encoding. If w > 1, we get a modified (relaxed) carry-save encoding (Figure 4.1). Our approach was published in [A.1].

We can use both the conventional and the modified carry-save representation to construct adder trees. Examples of four-to-two carry-save adder trees are presented in Figure 4.2.

When using conventional carry-save encoding, we get  $(CS, S) = CSA(A_1, A_2, A_3, A_4)$ , where S is the sum, CS is the carry and operands  $A_i$  as well as S and CS have the same width.

Using modified carry-save encoding we have  $(CS, S) = CSA'(A_1, CA_1, A_2, CA_2)$ , where the sum parts  $A_1$ ,  $A_2$  and S are k-bit numbers, whereas the carry parts  $CA_1$ ,  $CA_2$  and CS are CS and CS are CS are CS are CS and CS are CS are CS are CS and CS are CS are CS are CS are CS are CS are CS and CS are CS are CS are CS and CS are CS are CS are CS and CS are CS are CS are CS are CS are CS are CS and CS are CS are CS are CS and CS are CS are CS and CS are CS are CS and CS are CS are CS and CS are CS are CS and CS are CS and CS are CS and CS are CS and CS are CS and CS are CS are CS and CS

Figure 4.1: Internal structure of adders: a) conventional carry-save adder, b) modified carry-save adder.

Figure 4.2: Adder tree using a) carry-save encoding, b) modified carry-save encoding.

The architecture is derived from [32], we consider four-to-two CSA. It consists of two layers of carry-save adders with k-bit operands. We substitute w-bit sections of the carry-save adder with sections of ripple-carry adders. Consequently, in each word, w-1 bits of the carry part (CS) are zeros, thus do not need to be stored in registers (Figure 4.3).

For w > 1, we extend the carry chain fragments, thus extending also the critical path. However, due to the fast dedicated adders in FPGA, this needs not necessarily to introduce significant delay to the critical path.

In the implementation phase the automatic synthesis, placement and routing tools make use of the dedicated adder hardware present in FPGA and construct several carry chains of length 2w. The carry chains consist of one adder from the first layer and one adder from the second layer (Figure 4.3).

When increasing the word size w, we expect the occupied area to decrease, because the number of carry bits decreases and we save more registers and logic cells. We expect that the additional delay introduced by the ripple-carry adder segments is compensated by the savings in routing resources associated with the carry bits.

Figure 4.3: Multiplier architecture with modified CSA adder tree.

## 4.3 HW optimization of Left-Shift Inverse

The left-shift inversion algorithm (Algorithm 3.5) can be modified to better utilize hardware components, as is shown in Algorithm 4.1. The main area of changes is in the way the test conditions are computed. For example, step 3 of Algorithm 3.5,  $u \neq \pm 2^{c_{-}u}$  &  $v \neq \pm 2^{c_{-}v}$  can be implemented by masking using an auxiliary register m.

Consider an example using 5 bits, where  $c_u = 2$ , and we are testing whether  $u = \pm 2^{c_u}$ . The binary image of  $2^{c_u} = 2^2$  is 00100, whereas for  $-2^2$  it is 11100. Two least significant bits must be zero. In this case only one mask value is sufficient to test both  $\pm 2^2$ : Let m = 11100. Then  $u = -2^2$  can be tested with a simple equality comparator. The other case of  $u = 2^2$  can be tested by masking with shifted value of m. If  $u \& (m \ll 1) = 000000$  then  $u = 2^2$ . This follows from the fact that u was shifted 2 bits left and so the 2 least significant bits must be zero.

Similarly, the counter comparison tests in steps 10 and 19 of Algorithm 3.5 can be optimized using flags d and  $u/\bar{v}$ . This way we can replace the expensive " $\leq$ " and " $\geq$ " test with a simpler equality test and sequential tracking of counter values. This approach is reflected in the HW optimized Algorithm 4.1.

#### Algorithm 4.1 Left-shifting inversion algorithm, HW optimized variant

```

Input: a \in [1, p-1] and p

Output: r \in [1, p-1], where r = a^{-1} \mod p, c \mid u, c \mid v

and 0 < c_v + c_u \le 2n

u := p, v := a, r := 0, s := 1, c u = 0, c v = 0, u/\bar{v} := 1, m := 1, t pos := 1, t neg := 1

1.

2.

while (t \ neg = 1 \& t \ pos = 1)

3.

if (u_n, u_{n-1} = 0) or (u_n, u_{n-1} = 1 \& OR(u_{n-2}, ..., u_0) = 1) then

4.

if (d=0 \text{ or } u/\bar{v}=0) then

5.

u := 2u, r := 2r, c \quad u := c \quad u + 1, u/\bar{v} := 0

6.

else

7.

u := 2u, s := s/2, c \quad u := c \quad u+1

8.

else if (v_n, v_{n-1} = 0) or (v_n, v_{n-1} = 1 \& OR(v_{n-2}, ..., v_0) = 1) then

9.

if (d=0 \text{ or } u/\bar{v}=1) then

10.

v := 2v, s := 2s, c \quad v := c \quad v + 1, u/\bar{v} := 1

11.

else

v := 2v, r := r/2, c \quad v = c \quad v + 1

12.

13.

else

if (v_n = u_n) then

14.

if (d=0) then

15.

x := u - v, u := 2x, r := 2(r - s), c \quad u := c \quad u + 1, u/\bar{v} := 0, wu := 1

16.

17.

else if (u/\bar{v}=1) then

18.

x := u - v, u := 2x, r := r - s, s = s/2, c \quad u := c \quad u + 1, m := 2m, wu := 1

19.

else

20.

x := v - u, v := 2x, s := s - r, r = r/2, c \quad v := c \quad v + 1, m := 2m, wu := 0

21.

else

22.

if (d=0) then

23.

x := u + v, \ u := 2x, \ r := 2(r + s), \ c \ u := c \ u + 1, \ u/\bar{v} := 0, \ wu := 1

24.

else if (u/\bar{v}=1) then

25.

x := u + v, u := 2x, r := r + s, s = s/2, c \quad u := c \quad u + 1, m := 2m, wu := 1

26.

else

27.

x := v + u, v := 2x, s := s + r, r = r/2, c \quad v := c \quad v + 1, m := 2m, wu := 0

28.

t \ pos := OR(x \& 2m), t \ neg := OR(x \oplus m)

29.

d := OR(c \ u \oplus c \ v)

30. if (wu = 1) then

31.

if (u/\bar{v}=1) then

32.

s := r

33.

else

34.

s := r/2

35. if (t neg = 0 \& s_m = 1 \text{ or } t pos = 0 \& s_m = 0) then

36.

r := 0

37.

else

38.

r := p

39. if (t \ neg = 1) then

r := r - s

40.

41. else

42.

r := r + s

43. return r

```

| Destination | Initial |    | Main cycle |        |        |     |     | Postprocessing |     |     |     |

|-------------|---------|----|------------|--------|--------|-----|-----|----------------|-----|-----|-----|

| u           | p       | 2u |            | 2(u+v) | 2(u-v) |     |     |                |     |     |     |

| v           | a       | 2v |            | 2(u+v) | 2(v-u) |     |     |                |     |     |     |

| r           | 0       | 2r | r/2        | 2(r+s) | 2(r-s) | r+s | r-s | 0              | p   | r-s | r+s |

| s           | 1       | 2r | s/2        | 2(r+s) | 2(s-r) | r+s | s-r | r              | r/2 |     |     |

The original table of operations (Table 3.1) is thus modified resulting in Table 4.1.

Table 4.1: Left-Shift Inverse HW optimized operation summary

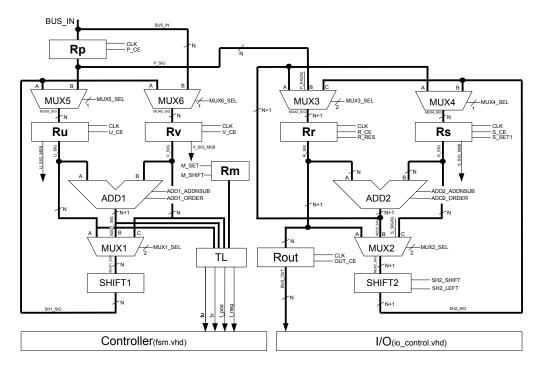

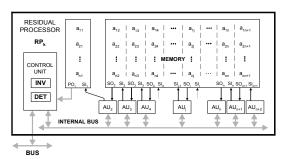

The computation unit consists of three major parts – datapath, controller and I/O block. The datapath contains data memory elements (registers) to store the operands and intermediate values (u, v, r, s, p, m), two adders/subtracters to compute the arithmetic operations, and multiplexers that switch the cata flow according to the particular operation to be performed. The controller contains a finite state machine, two counters and some logic, whose role is to control the progress of computation using control and status signals to the datapath. The I/O block connect the internal input and output buses to the external bidirectional bus and contains associated control and status signals of the whole unit.

#### 4.3.1 Datapath

The datapath is depicted in Figure 4.4. It contains two adders/subtractors. ADD1 is a reversible adder/subtracter, i.e. it performs u+v, u-v or v-u. Subtraction is performed using bitwise negation of one of the operands and presenting a "hot one" carry-in. Each of the inputs of the adder can be negated separately, thus determining order of subtraction (u-v or v-u).

#### 4.3.2 Controller