Czech Technical University in Prague Faculty of Electrical Engineering Department of Circuit Theory

# Analysis and modeling of the modern charge pump circuits

Disertation thesis

Ing. Jan Marek

Ph.D. programme: P 2612 Electrical Engineering and Information Technology Branch of study: 2602V013 Theoretical Electrical Engineering Supervisor: Doc. Dr. Ing. Jiří Hospodka Supervisor–specialist: Ing. Ondřej Šubrt, Ph.D.

Prague, September 2018

#### Thesis Supervisor:

Doc. Dr. Ing. Jiří Hospodka Department of Circuit Theory Faculty of Electrical Engineering Czech Technical University in Prague Technická 2 160 00 Prague 6 Czech Republic

Copyright © September 2018 Ing. Jan Marek

### Thesis Supervisor–Specialist:

Ing. Ondřej Šubrt, Ph.D.<sup>1,2</sup> <sup>1</sup>Department of Circuit Theory Faculty of Electrical Engineering Czech Technical University in Prague Technická 2 160 00 Prague 6 Czech Republic

<sup>2</sup>ASICentrum, a company of the Swatch group Novodvorská 994 142 21 Prague Czech Republic

Copyright © September 2018 Ing. Jan Marek

# Declaration

I hereby declare I have written this doctoral thesis independently and quoted all the sources of information used in accordance with methodological instructions on ethical principles for writing an academic thesis. Moreover, I state that this thesis has neither been submitted nor accepted for any other degree.

In Prague, September 2018

..... Ing. Jan Marek

# Abstract

The thesis presents the design process of the cross-coupled charge pump on the circuit-level hardware realization, which is used for supplying low current consumption peripherals on the chip. The unconventional approach to the discrete-time analogue circuit description arising from non-linear systems theory is offered. Design aspects of the SC circuits are firstly explained, including the analysis of the basic topologies of two-phase charge pumps. The main part deals with the steps of the cross-coupled charge pump design algorithm. Synthesis procedure includes the design of the pump functional blocks based on BSIM equations of MOSFET for long channel technology process and application of the pump stage complex model for estimation of the number of pump stages via state-space model description and using of the interpolation polynomial functions in the algorithm. Two available solutions are introduced satisfying particularly two criteria in terms of the circuit and economic optimization – high efficient, i.e. pump maximal voltage gain and an areaefficient charge pump. The whole procedure is summarized in the practical example, including the comparison between calculated and simulation results. Added functions of the design environment are explained, inclusive of the designed pump netlist generating for professional design environment Mentor Graphics including the real models of components that are available in library MGC Design Kit. In addition, the complex model allows the inclusion effects of higher-levels and is also applicable to other MOSFET technology process, as PSP or EKV. The main benefit is the charge pump synthesis precedure without long time-consuming optimization process.

**Keywords:** Cross-coupled charge pump, synthesis, BSIM model, state-space model, simulations, programme procedure.

viii

# Abstrakt

Dizertační práce se zabývá návrhem křížově vázané nábojové pumpy, jež se používá pro napájení nízkopříkonových obvodů na čipu. Používá netradiční přístup k popisu diskrétně pracujících analogových soustav vycházející z teorie nelineárních systémů. V úvodní části jsou shrnuty základní poznatky v oblasti SC obvodů včetně vlastností základních struktur dvoufázových nábojových pump. Hlavní část práce se zabývá řešením jednotlivých kroků návrhového algoritmu křížově vázané nábojové pumpy od analytického popisu a návrhu funkčních bloků až k sestavení komplexního modelu, jenž je využit k odhadu počtu stupňů reálné struktury prostřednictvím Lagrangeova interpolačního polynomu. Každá buňka v obvodu pumpy je popsána zjednodušenými rovnicemi BSIM modelu MOSFET tranzistoru s dlouhým kanálem. Jsou uvedena dvě možná řešení výsledné struktury, a to jednak na základě kritéria maximálního napěťového zisku (statická napěťová účinnost) a jednak dosažení minimální celkové plochy obvodu na čipu. Návrhový algoritmus je ukázán na praktickém příkladu, včetně srovnání dosažených parametrů se simulačními výsledky. Návrhové prostředí umožňuje mj. vygenerovat tzv. netlist výsledné struktury pro simulátor ELDO se zahrnutím modelů reálných prvků dostupných v knihovně MGC Design Kit. Popis struktury je univerzální jak z hlediska použitých modelů (PSP, EKV a další), tak i z hlediska implementace parazitních prvků vyšších stupňů. Hlavním přínosem práce je postup návrhu uvedeného typu nábojových pump bez časově náročného iteračního procesu, tedy bez nutnosti aplikace optimalizačních metod.

**Klíčová slova:** Křížově vázaná nábojová pumpa, návrh, BSIM model, stavový model, simulace, programová procedura.

# Acknowledgements

I would like to express many thanks to my supervisor Doc. Dr. Ing. Jiří Hospodka and my supervisor-specialist Ing. Ondřej Šubrt, Ph.D. for their helpful support of my Ph.D. Thesis.

This work has been supported by the grant No.  $\rm SGS17/183/OHK3/3T/13$  of the CTU in Prague.

# List of symbols and acronyms

| ~ [ ]                                | nomogius nonomaton                                  |

|--------------------------------------|-----------------------------------------------------|

|                                      | regressive parameter                                |

| $A_{bulk}$ [-]                       | bulk charge effect bulk charge effect $(V - V) = 0$ |

| $A_{bulk0}[-]$                       | bulk charge effect at $(V_{GS} - V_{TH})_{eff} = 0$ |

| $A_{inv} [\mathrm{m}^2]$             | inverter area                                       |

| $C_L^{,}$ [F]                        | total load capacitance                              |

| $C_{ij}$ [F]                         | capacitance value between electrods $i, j$          |

| $C_{min}$ [F]                        | minimal MOSFET capacitance                          |

| $C_{mont}$ [F]                       | added strange capacitance                           |

| $c_{oxe}$ [F]                        | electrical oxide capacitance                        |

| $C_{pump}$ [F]                       | equivalent pump capacitance                         |

| $C_{s_i}[\mathbf{F}]_{(k+1)}$        | strange capacitance in $i$ -node                    |

| $C_{si}^{,(k+1)}$ [V]                | voltage on the strange capacitor in the next cycle  |

| $C_{si}^{,}$ [F]                     | total strange capacitance                           |

| $C_i$ [F]                            | main capacitance in $i$ -node                       |

| $C_L$ [F]                            | load capacitance                                    |

| $C_L^{,}$ [F]                        | total load capacitance                              |

| $E_{crit}  [\mathrm{Vm}^{-1}]$       | crititical electrical field                         |

| $f_c \; [\mathrm{Hz}]$               | driving frequency                                   |

| $f_s$ [Hz]                           | signal frequency                                    |

| $G_{v_i}$ [V]                        | voltage gain in i-node                              |

| $I_{D_{sat0R}}$ [A]                  | reverse drain switch current in saturation region   |

| $I_{DS0_F}$ [A]                      | forward switch drain current in triode region       |

| $I_{DS0_R}$ [A]                      | reverse switch drain current in triode region       |

| $I_{S_R}$ [A]                        | reverse switch current                              |

| $\tilde{I}_{SR}  [\mathrm{Am}^{-1}]$ | drain current for unity width                       |

| $I_{0N(P)}$ [A]                      | drain current at $V_{GS} = 0$                       |

| $I_{1N(P)}$ [A]                      | linearized inverter cross current                   |

| $I_{av}$ [A]                         | average curret value                                |

| $i_{c_F}$ [A]                        | forward charge current                              |

| $I_{cross}$ [A]                      | inverter cross current                              |

| $I_D$ [A]                            | static drain current                                |

| $I_{DD}$ [A]                         | current consumption                                 |

| $I_{DS0}$ [A]                        | drain current in the triode region                  |

| $I_{DS0N(P)}$ [A]                    | drain current in subtreshold region                 |

| $I_{Dsat0}$ [A]                      | drain current at $V_{DS} = V_{DSsat}$               |

| $i_{inls}$ [A]                       | input current of the pump stage                     |

| $I_{Lmax}$ [A]                       | maximal load current                                |

| $I_{max}$ [A]                        | maximal current                                     |

| $i_{out1ls}, i_{out2ls}$ [A]         | output current of the pump stage                    |

| $I_L$ [A]                            | load current                                        |

| $I_r$ [A]                            | reverse current                                     |

| $I_s$ [A]                            | switch drain current                                |

| $I_{S0N(P)}$                         | drain current in subtreshold region at $V_{DS} = 0$ |

|                                      |                                                     |

#### xiv

| k $[-]$                                                                                                            | multiply constant                                              |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| $K_1, K_{1ox}, K_2, K_{2ox}$ [-]                                                                                   | body effect coeficients (BSIM)                                 |

| L [m]                                                                                                              | channel length                                                 |

| $L_{eff}$ [m]                                                                                                      | effective channel length                                       |

| $L_c$ [m]                                                                                                          | MOS capacitor length                                           |

| $L_d$ [m]                                                                                                          | diode transistor length                                        |

| $L_p$ [m]                                                                                                          | PMOS inverter transistor length                                |

| $L_s$ [m]                                                                                                          | switch transistor length                                       |

| n [-]                                                                                                              | emission coeffecient                                           |

| N [-]                                                                                                              | number of the pump stages                                      |

| $\hat{N}$ [-]                                                                                                      | estimation of the number of the pump stages                    |

| $\hat{N}_{i_0}$ [-]                                                                                                | estimation of the initial number of the pump stages            |

| $\tilde{P}_{DC}$ [W]                                                                                               | static power estimation                                        |

| $P_{\bar{\phi}}$ [W]                                                                                               | power consumption of the second-phase clock signal             |

| $P_{\phi}$ [W]                                                                                                     | power consumption of the second-phase clock signal             |

| $\begin{array}{c} P_{DC} \left[ \mathbf{W} \right] \end{array}$                                                    | static power                                                   |

|                                                                                                                    | -                                                              |

| $P_{out}$ [W]<br>O [C]                                                                                             | output power<br>total charge                                   |

| $Q_{cc}$ [C]                                                                                                       | total charge                                                   |

| $q_{inj}$ [C]<br>$Q_i$ [C]                                                                                         | injected charge<br>charge in i-node                            |

| R [-]                                                                                                              | inverter MOSFETs sizes ratio                                   |

| $R_{ekv} \left[\Omega\right]$                                                                                      | equivalent resistor                                            |

| $\frac{R_{ekv}}{R_{opt}} \left[ V^{-1} \right]$                                                                    | optimal inverter MOSFETs sizes ratio factor                    |

| $\begin{array}{c} R_{opt} \left[ \mathbf{v} \right] \\ R_{pump} \left[ \Omega \right] \end{array}$                 | equivalent pump resistance                                     |

| $R_{Smax}$ [-]                                                                                                     | inverter MOSFETs sizes ratio factor at the maximal sensitivity |

| $R_l \left[\Omega\right]$                                                                                          | leakage resistance                                             |

| $R_L \left[\Omega\right]$                                                                                          | load resistance                                                |

| $S[V^{-1}]$                                                                                                        | sensitivity                                                    |

| $S_{max} [V^{-1}]$                                                                                                 | maximal sensitivity                                            |

| $S_{pump} [\mathrm{m}^2]$                                                                                          | total pump area                                                |

| $t_{0_F}$ [s]                                                                                                      | charge time in forward configuration                           |

| $t_{0_R}$ [s]                                                                                                      | charge time in reverse configuration                           |

| $T_{clk}$ [s]                                                                                                      | clock signal period                                            |

| $t_{HL}$ [s]                                                                                                       | fall time                                                      |

| $t_{LH}$ [s]                                                                                                       | rise time                                                      |

| $T_c$ [s]                                                                                                          | period of the driving signal                                   |

| $T_r$ [s]                                                                                                          | rise time                                                      |

| $V_{\bar{\phi}}$ [V]                                                                                               | the second-phase clock signal amplidue                         |

| $V_{\phi}$ [V]                                                                                                     | the first-phase clock signal amplidue                          |

| $V_{BS_{eff}}$ [V]                                                                                                 | effective bulk-source voltage                                  |

| $V_{TH0_N(P)}$ [V]                                                                                                 | threshold voltage of the N(P)MOS at zero bias voltages         |

| $V_{0_F}$ [V]                                                                                                      | voltage value at the charge time                               |

| $V_{ADIBL}$ [V]                                                                                                    | dibl voltage                                                   |

| $V_{bc}$ [V]                                                                                                       | bulk-source voltage at $dV_{TH}/dV_{bs} = 0$                   |

| $v_{bn}$ [V]                                                                                                       | pump stage bulk NMOS voltage                                   |

| $V_{bound}$ [V]-                                                                                                   | boundary of the bulk-source voltage                            |

| $v_{bp}$ [V]                                                                                                       | pump stage bulk PMOS voltage                                   |

| $ \begin{array}{c} v_{bp} \left[ \mathbf{V} \right] \\ v_{C_{i_0}}^{(k+1)} \left[ \mathbf{V} \right] \end{array} $ | voltage on the main capacitor in the next cycle                |

| $v_{c_R}$ [V]                                                                                                      | voltage on the capacitor in reverse configuration              |

| $v_{cF}$ [V]                                                                                                       | voltage on the capacitor in forward configuration              |

| $V_{DD}$ [V]                                                                                                       | power supply voltage                                           |

| $V_{DSeff}$ [V]                                                                                                    | effective drain-source voltage                                 |

| $V_{DSsat}$ [V]                                                                                                    | saturation drain-source voltage                                |

| 1                                                                                                              |                                                                      |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| $v_{fb}$ [V]                                                                                                   | pump stage feedback voltage                                          |

| $V_{fin}$ [V]                                                                                                  | final voltage valued                                                 |

| $V_{gs_{eff}}$ [V]                                                                                             | effective gate-source voltage                                        |

| $v_{i_{\infty}}$ [V]                                                                                           | voltage in the steady state                                          |

| $v_{i_0}$ [V]                                                                                                  | initial voltage value                                                |

| $V_{IH}$ [V]                                                                                                   | input inverter voltage defines the output low logic level            |

| $V_{ij}$ [V]                                                                                                   | volatage between electrods $i, j$                                    |

| $V_{IL}$ [V]                                                                                                   | input inverter voltage defines the output high logic level           |

| $V_{in}$ [V]                                                                                                   | input pump stage voltage                                             |

| $v_{inv} [V]$                                                                                                  | inverter output voltage                                              |

| · · · ·                                                                                                        | cut-off voltage                                                      |

| $V_{off}$ [V]                                                                                                  | 0                                                                    |

| $V_{out,av}$ [V]                                                                                               | average value of the pump output voltage                             |

| $V_{out,max}$ [V]                                                                                              | maximal pump output voltage                                          |

| $V_{out}$ [V]                                                                                                  | output voltage                                                       |

| $v_{out}$ [V]                                                                                                  | pump stage output voltage                                            |

| $V_{r_{max}}$ [V]                                                                                              | maximal ripple voltage                                               |

| $v_{sat}  [\mathrm{ms}^{-1}]$                                                                                  | drift velocity saturation                                            |

| $V_{SP}$ [V]                                                                                                   | inverter switching point                                             |

| $V_{TH_{Mxi}}$ [V]                                                                                             | threshold voltage of the $M_{si}$ MOSFET                             |

| $V_{TH}$ [V]                                                                                                   | threshold voltage                                                    |

| $V_{TH0}$ [V]                                                                                                  | threshold voltage at zero bias voltages                              |

| $v_i$ [V]                                                                                                      | node voltage                                                         |

| $v_i^k$                                                                                                        | node voltage for $k - cycle$                                         |

| $V_r$ [V]                                                                                                      | ripple voltage                                                       |

| $V_t$ [V]                                                                                                      | temperature voltage                                                  |

| $v_z$ [V]                                                                                                      | load voltage                                                         |

| $W_{M_{S_{opt}}}$ [m]                                                                                          | optimal switch transistor width                                      |

| $W_c [m]$                                                                                                      | MOS capacitor width                                                  |

| $W_d$ [m]                                                                                                      | diode transistor width                                               |

| $W_p$ [m]                                                                                                      | PMOS inverter transistor width                                       |

| $W_s$ [m]                                                                                                      | switch transistor width                                              |

| ,, , [111]                                                                                                     |                                                                      |

| $\alpha$ [V]                                                                                                   | linearized body effect coefficient                                   |

| $\alpha_D$ [-]                                                                                                 | proportional voltage increment                                       |

| $\beta [-]$                                                                                                    | couple ratio                                                         |

| $\beta_c [AV^{-2}]$                                                                                            | current factor                                                       |

| $\beta_c \left[ \text{AV}^{-2} \text{m}^{-1} \right]$<br>$\beta_D \left[ \text{AV}^{-2} \text{m}^{-1} \right]$ | diode transistor current coefficient                                 |

| $\delta [-]$                                                                                                   | sensitivity ratio factor                                             |

|                                                                                                                |                                                                      |

| $\epsilon$ [V]                                                                                                 | maximal voltage gain for the steady state detection                  |

| $\eta_{\varepsilon}$ [-]                                                                                       | power efficiency                                                     |

| $\eta_v [-]$                                                                                                   | static voltage efficiency                                            |

| $\gamma \begin{bmatrix} - \end{bmatrix}$                                                                       | body effect coeficient                                               |

| $\hat{\eta}_v$ [-]                                                                                             | estimation of the static voltage efficiency                          |

| $\hat{T}_r$ [s]                                                                                                | estimation of the pump rise time                                     |

| $\lambda$ [-]                                                                                                  | capacitance ratio factor                                             |

| $\mu_{eff}  [\mathrm{m^2 V^{-1} s^{-1}}]$                                                                      | effective mobility                                                   |

| $\mu_{eff_{i0}} [\text{m}^2 \text{V}^{-1} \text{s}^{-1}]$                                                      | effective mobility of the $M_i$ MOSFET at the initial voltage values |

| $\phi_s  [V]$                                                                                                  | surface voltage                                                      |

| $\psi$ [-]                                                                                                     | modulation factor                                                    |

| au [s]                                                                                                         | time constant                                                        |

| $\tau(v)$ [s]                                                                                                  | Taylor approximation of the voltage function at time                 |

| $\varepsilon_{r_{Vout}}$ [-]                                                                                   | relative error of the output voltage                                 |

| $\varepsilon_{Si}$ [-]                                                                                         | relative permittivity of silicon                                     |

|                                                                                                                |                                                                      |

$\varepsilon_{Tr}$  [-] Dynamic efficiency during rise time  $\varphi, \chi, \rho \ [\mathrm{C}]$ coefficients number of stages calculations  $\vartheta \ [^{\circ}C]$ temperature  $\zeta$  [V] voltage factor ARC Active filter Colony Collapse Disorder CCD CLK Clock frequency CLM Channel length modulation CTSCharge-transfer-switch DIBL Drain-induced barrier lowering effect DtAC Discrete-time analog circuit EEPROM Electrically Erasable Programmable Read-Only Memory Hhigh voltage level L low voltage level HVT high-voltage transistor  $IC_i [V]$ voltage initial condition NDEP  $m^{-3}$ substrate doping concentration PDIBLC2, PDIBLCB [-DIBL effect coeficients  $\mathbf{SC}$ Switched capacitor SCBE Substrate Current Induced Body effect Switched current SIVFBCV [V] flat band voltage VTC Voltage transfer characteristics  $\mathbf{X}_i$ subcircuit of the i-pump stage  $X_{LS}$ subcircuit of the last pump stage ٦*٢* 1. 1

| $M_{D_i}$            | diode transistor                     |

|----------------------|--------------------------------------|

| $M_{si}$             | switch transistor                    |

| $M_{pi}$             | inverter PMOS transistor             |

| $M_{ni}$             | inverter NMOS transistor             |

| $\phi$               | the first-phase of the clock signal  |

| $\phi \over ar \phi$ | the second-phase of the clock signal |

xvi

# List of Tables

| 1.1          | Some properties of the DtAC                                                                                                                                                                     | 3        |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| $3.1 \\ 3.2$ |                                                                                                                                                                                                 | 14<br>14 |

| 5.1          | $M_{Si}$ transistor control voltages configuration for the setting of $I_S$                                                                                                                     | 30       |

| 5.2          | Simulation parameters                                                                                                                                                                           | 35       |

| 6.1          | Simulation circuit parameters                                                                                                                                                                   | 39       |

| 6.2          | Simulation results                                                                                                                                                                              | 40       |

| 6.3          | Bias voltages of the nested functions (NF) $V_{TH}$ , $A_{bulk}$ and $u_{eff}$                                                                                                                  | 42       |

| 6.4          | Relationship between parameters k and $\alpha$ calculated from Eq. (6.14)                                                                                                                       | 45       |

| 6.5          | Relationship between parameters k and $\alpha_D$ calculated from Eq. (6.30)                                                                                                                     | 47       |

| 6.6          | Width of the $M_{D_i}$ transistor vs. $\alpha$ parameter $\ldots \ldots \ldots$ | 48       |

| 6.7          | Simulation parameters                                                                                                                                                                           | 48       |

| 6.8          |                                                                                                                                                                                                 | 49       |

| 6.9          | Pump output voltage vs. main capacitance value                                                                                                                                                  | 55       |

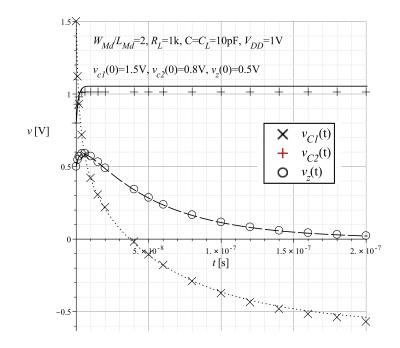

| 7.1          | Simulation parameters                                                                                                                                                                           | 64       |

| 7.2          | Simulation results                                                                                                                                                                              | 65       |

| 8.1          | List of the input pump requirements                                                                                                                                                             | 71       |

| 8.2          | List of the charge pump parameters                                                                                                                                                              | 73       |

# List of Figures

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | Equivalent circuit of the switched-capacitor                                                                                                                                                                                                                              | $\frac{2}{3}$                          |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5$         |                                                                                                                                                                                                                                                                           | 5<br>6<br>9<br>10<br>11                |

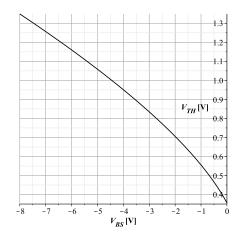

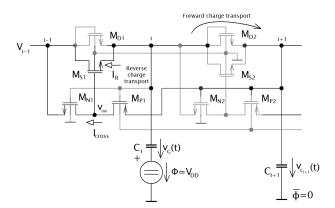

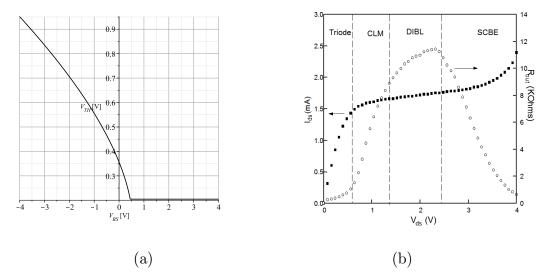

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6    | Threshold voltage vs bulk-source bias voltage $\ldots$ $\ldots$ $\ldots$ $\ldots$ Reverse charge transport $\ldots$                                                                      | $13 \\ 15 \\ 16 \\ 16 \\ 16 \\ 17 $    |

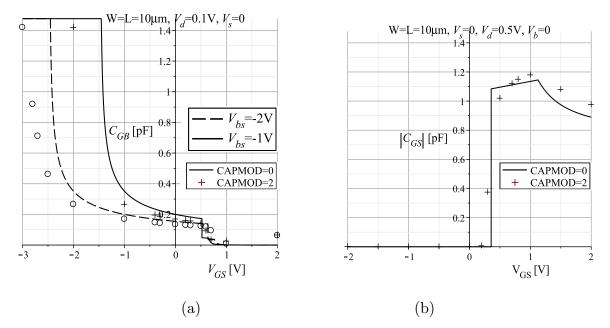

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5           | MOS gate capacitances: gate-bulk (a) and gate-source capacitance (b)<br>Diagram of the CMOS inverter                                                                                                                                                                      | 22<br>24<br>24<br>25                   |

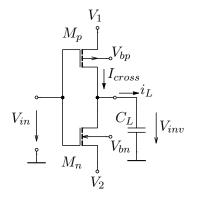

| 5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11  | region: $V_1 > V_2$ (a) and $V_1 < V_2$ (b)                                                                                                                                                                                                                               | 29<br>30<br>31<br>32<br>32<br>34<br>35 |

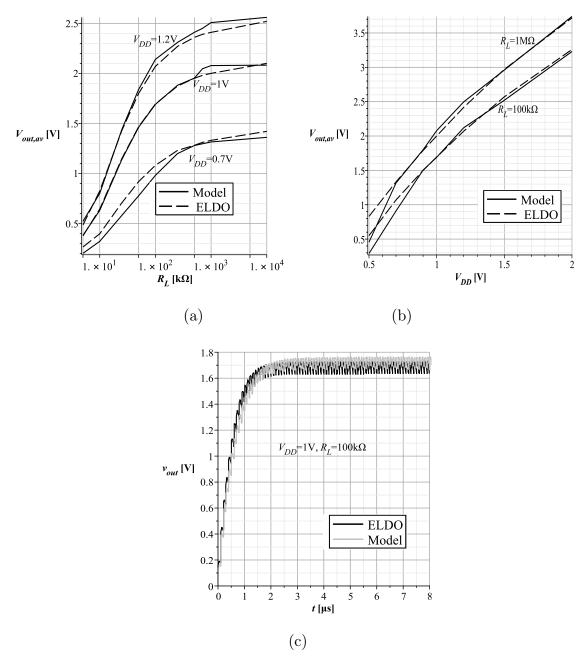

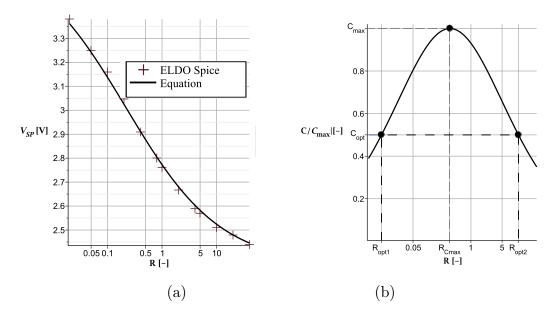

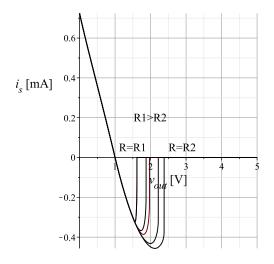

| 6.1                                       | voltage vs. load resistance (a) and supply voltage (b), dynamic char. (c) $\ldots$ .<br>Switching point analysis – dependence on the ratio $R$ and normalized sensitivity curve $\ldots$ | 36<br>37                               |

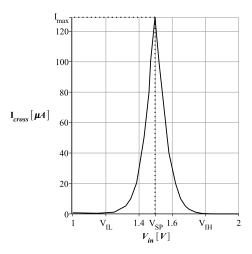

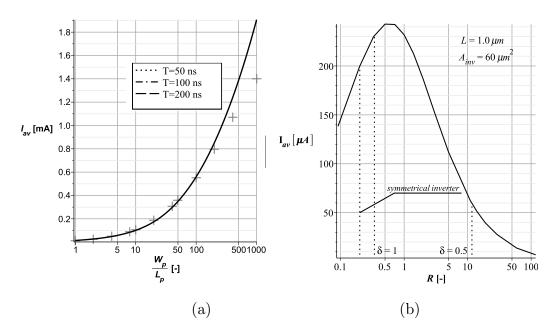

| 6.2<br>6.3                                | Average value of the cross current vs. the $W_p/L_p$ ratio for $W_n = 40 \mu\text{m}(a)$ and $I_{av}$ vs. $R$ ratio for $A_{inv} = \text{konst.}(b) \ldots \ldots$                                  | 40<br>40                               |

| $6.4 \\ 6.5 \\ 6.6$                       | Time response characteristics of the circuit from Fig. 6.4                                                                                                                                                                                                                | 41<br>42<br>43                         |

| 6.7                                                                                      | Time response characteristics of the circuit from Fig. 6.6                                      | 44                                                                   |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 6.8                                                                                      | Time response characteristics for the pumping losses minimization                               | 45                                                                   |

| 6.9                                                                                      | Linearization of the time response characteristics                                              | 45                                                                   |

| 6.10                                                                                     | The last stage of the charge pump and waveform of the output voltage in the                     |                                                                      |

|                                                                                          | steady state                                                                                    | 46                                                                   |

| 6.11                                                                                     | Time response characteristics of the diode transistor                                           | 46                                                                   |

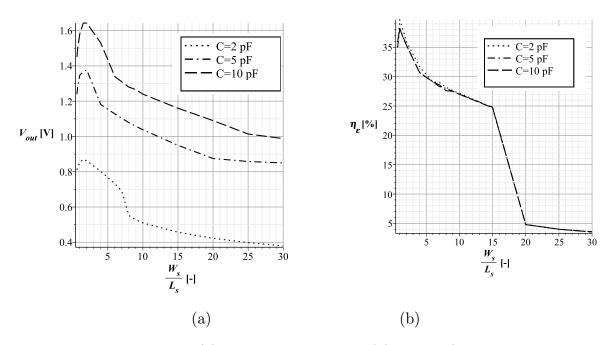

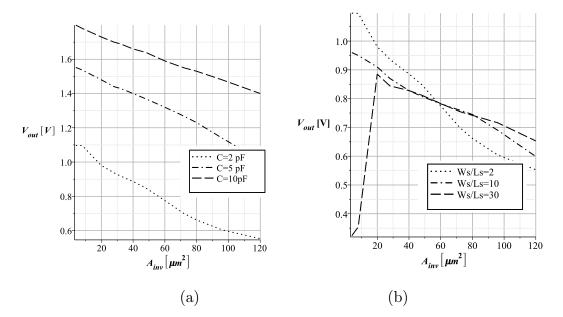

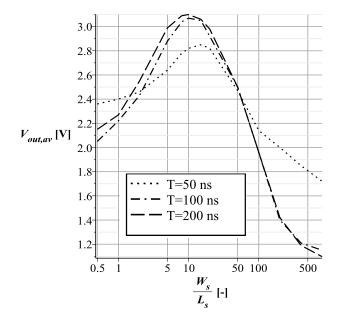

| 6.12                                                                                     | Pump output voltage vs. the ratio $W_s/L_s$                                                     | 48                                                                   |

| 6.13                                                                                     | Pump output voltage vs. the ratio $W_D/L_D$                                                     | 50                                                                   |

| 6.14                                                                                     | Charge of the main capacitor in the first pump stage: diagram (a) and time                      |                                                                      |

|                                                                                          | response characteristics (b)                                                                    | 51                                                                   |

| 6.15                                                                                     | Energy transport in the last pump stage: block diagram (a) and time response                    |                                                                      |

|                                                                                          | characteristics (b)                                                                             | 51                                                                   |

| 6.16                                                                                     | Time response characteristic of the last pump stage-calculated waveform and                     |                                                                      |

|                                                                                          | simulation results                                                                              | 52                                                                   |

| 6.17                                                                                     | Time response characteristics of Example                                                        | 55                                                                   |

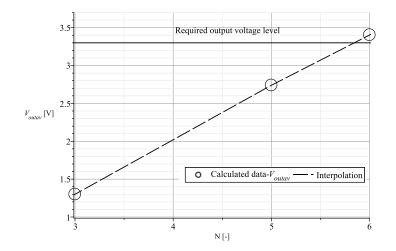

| 6.18                                                                                     | Pump output voltage vs number of stages                                                         | 55                                                                   |

| 6.19                                                                                     | MOS gate capacitance                                                                            | 56                                                                   |

|                                                                                          |                                                                                                 |                                                                      |

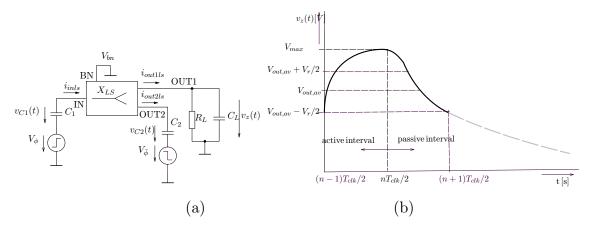

| 71                                                                                       | Cross coupled charge nume diagram implemented with MOS conscitors and par                       |                                                                      |

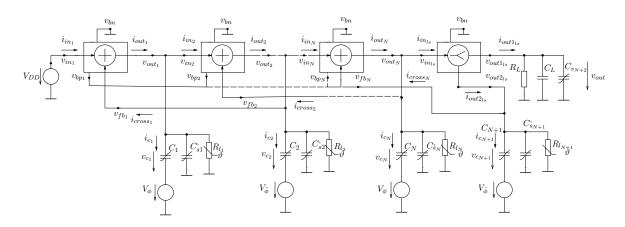

| 7.1                                                                                      | Cross-coupled charge pump diagram implemented with MOS capacitors and par-<br>asitic impedances | 50                                                                   |

|                                                                                          | asitic impedances                                                                               | 59<br>60                                                             |

| 7.2                                                                                      | asitic impedances                                                                               | 60                                                                   |

| $7.2 \\ 7.3$                                                                             | asitic impedances                                                                               | $\begin{array}{c} 60 \\ 62 \end{array}$                              |

| $7.2 \\ 7.3 \\ 7.4$                                                                      | asitic impedances                                                                               | 60<br>62<br>63                                                       |

| 7.2<br>7.3<br>7.4<br>7.5                                                                 | asitic impedances                                                                               | 60<br>62<br>63<br>65                                                 |

| $7.2 \\ 7.3 \\ 7.4$                                                                      | asitic impedances                                                                               | 60<br>62<br>63                                                       |

| 7.2<br>7.3<br>7.4<br>7.5                                                                 | asitic impedances                                                                               | 60<br>62<br>63<br>65                                                 |

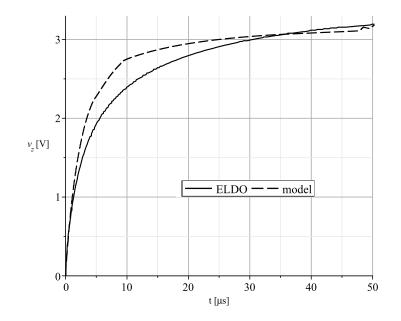

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6                                                          | asitic impedances                                                                               | 60<br>62<br>63<br>65<br>66                                           |

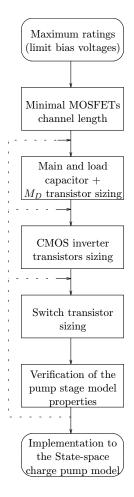

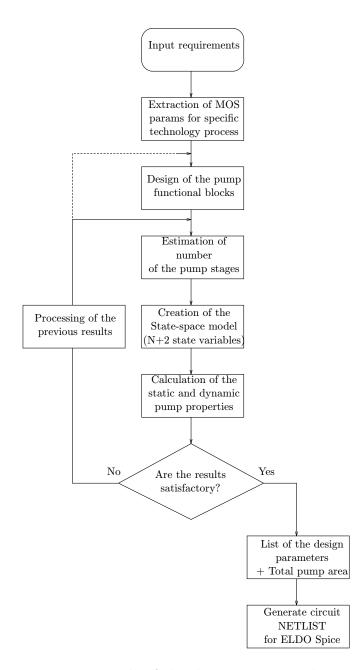

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>8.1</li> </ol> | asitic impedances                                                                               | 60<br>62<br>63<br>65<br>66<br>68                                     |

| $7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 8.1 \\ 8.2$                                          | asitic impedances                                                                               | 60<br>62<br>63<br>65<br>66<br>68<br>69                               |

| $7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 8.1 \\ 8.2 \\ 8.3$                                   | asitic impedances                                                                               | 60<br>62<br>63<br>65<br>66<br>68<br>69<br>72                         |

| $7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 8.1 \\ 8.2 \\ 8.3 \\ 8.4$                            | asitic impedances                                                                               | 60<br>62<br>63<br>65<br>66<br>68<br>69<br>72<br>72                   |

| $7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 8.1 \\ 8.2 \\ 8.3 \\ 8.4 \\ 8.5 \\ 8.6 \\$           | asitic impedances                                                                               | 60<br>62<br>63<br>65<br>66<br>68<br>69<br>72<br>72<br>72<br>72<br>74 |

| $7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 8.1 \\ 8.2 \\ 8.3 \\ 8.4 \\ 8.5 $                    | asitic impedances                                                                               | 60<br>62<br>63<br>65<br>66<br>68<br>69<br>72<br>72<br>72<br>72       |

# Contents

| Al            | bstract                                                                                                                                                                                                                                                                                                                                                                                                                                                     | vii                                                                                                                    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Al            | bstrakt                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ix                                                                                                                     |

| A             | cknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                             | xi                                                                                                                     |

| $\mathbf{Li}$ | st of symbols and acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                  | xiii                                                                                                                   |

| Li            | st of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                | xvii                                                                                                                   |

| $\mathbf{Li}$ | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                               | xix                                                                                                                    |

| 1             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                      |

| 2             | Two-phase charge pumps in overview         2.1       Dickson charge pump         2.1.1       Dynamic properties         2.2       Static pump CTS-1                                                                                                                                                                                                                                                                                                         | <b>5</b><br>5<br>6<br>9                                                                                                |

| 3             | Cross-coupled charge pump                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                                                                                     |

| 4             | Disertation thesis targets                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                                                                                                                     |

| 5             | Description of the pump functional blocks         5.1       BSIM model equations         5.2       CMOS inverter         5.2.1       Strong inversion         5.2.2       Subtreshold region and other cases         5.3       Model of the pump stage         5.3.1       Static part of the model         5.3.2       Dynamic part of the model         5.4       Testing of the behavioral model in the simulator                                        | <ul> <li>21</li> <li>24</li> <li>25</li> <li>29</li> <li>30</li> <li>30</li> <li>32</li> <li>35</li> <li>35</li> </ul> |

| 6             | Design of the pump functional blocks         6.1       CMOS inverter draft         6.1.1       Static power minimization         6.1.2       Switching characteristics         6.1.3       Experimental part         6.2       Switch transistor sizing         6.2.1       Time response characteristics         6.2.2       Minimization of the pumping losses         6.2.3       Sizing of the "diode" transistor         6.2.4       Experimental part | 37<br>37<br>38<br>39<br>41<br>41<br>44<br>46<br>48<br>50                                                               |

|              | 6.3.1 Experimental part                                | 54 |

|--------------|--------------------------------------------------------|----|

|              | 6.4 The MOSFET capacitor sizing                        | 55 |

|              | 6.5 Summary                                            | 57 |

| 7            | Estimation of the pump properties                      | 59 |

|              | 7.1 State model of the system                          | 59 |

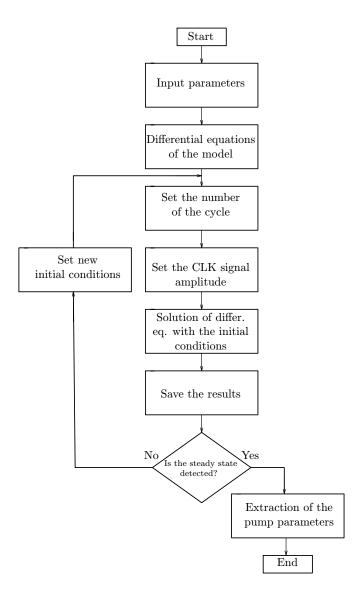

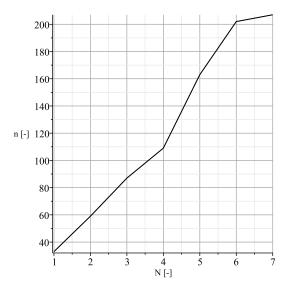

|              | 7.2 The basic principle of the algorithm               | 61 |

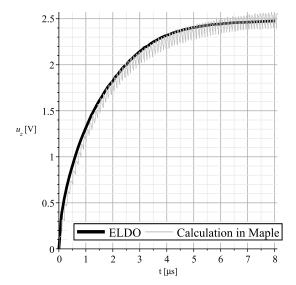

|              | 7.3 Experimental part                                  | 64 |

|              | 7.4 Summary                                            | 66 |

| 8            | Charge pump design on the circuit-level HW realization | 67 |

|              | 8.1 Synthesis process                                  | 67 |

|              | 8.2 Other properties of the design environment         | 70 |

|              | 8.3 Experimental part                                  | 71 |

|              | 8.4 Summary                                            | 74 |

| 9            | Conclusion                                             | 77 |

|              | 9.1 Summary of thesis                                  | 77 |

|              | 9.2 Fulfilments of targets                             | 78 |

|              | 9.3 Further extensibility and recommendations          | 79 |

| $\mathbf{A}$ | Design utility-illustration                            | 81 |

| в            | Netlist for ELDO                                       | 83 |

| С            | Charge pump–logo                                       | 87 |

| D            | Design maplet for 4-phase charge pump                  | 89 |

| Bi           | ibliography                                            | 91 |

|              | List of candidate's work related to the thesis         | 95 |

|              | List of other candidate's publications                 | 96 |

# Chapter 1

# Introduction

Discrete-time analog circuits (DtAC) have been developed since the second half of the 20th century. N-routes systems were originally used for the realization of the narrow bandpass filters (measurements purposes) and CCD sensors (system with the charge transition). Now, N-routes systems are on the decline. Subsequently, DtAC have been divided into two main groups according to the principle of the function as a result of the microelectronic technology development. Switched–capacitors circuits (SC) were firstly implemented in the early 80's and switched–current circuits (SI) [9] up in the 80's of the 20th century. The second mentioned group is still in the growth. These systems are characterized by analog switches operating in the dynamic mode, two variants are possibble from the view of its driving:

- Systems without driving–using mainly in the power applications.

- Systems with controlled switches. The circuits may include either internal or external clock signal circuit. Its using is in both power (high-voltage sources, controlled voltage rectifiers) and signal applications (integrated filters, A/D and D/A converters, modulators, charge pumps, special applications). A switch is nonlinear component that samples input analog signal. The sampling theorema must be respected: the digital clock signal frequency f<sub>c</sub> must be at least an order greater then maximum value of the input signal frequency f<sub>s</sub>, f<sub>c</sub> ≫ f<sub>s</sub> [7] (Charge pumps are an exceptional case of DtAC, where the input "signal" is represented by the DC source voltage).

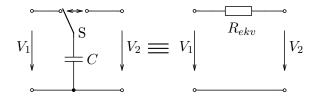

Attention will be focused on SC circuits with the external clock signal designed for signal applications. Currently, SC circuits represent very perspective sector of quasi-analog systems. Options of the unipolar monolitic technology solve the basic problem associated with the integration of precise and stable resistor networks. The basic principle is based on the resistor simulated by the switched-capacitor [6], as it is shown in Figure 1.1. In case that the period of clock signal is sufficiently short compared to time change of the voltage  $v_1(t)$  and the settling time of the switch is neglibly small, then the average current flowing through the capacitor is given by

$$i = \frac{\mathrm{d}Q}{\mathrm{d}t} \doteq \frac{\Delta Q}{T_c} = \frac{C(V_1 - V_2)}{T_c} = \frac{C}{T_c} \Delta V \tag{1.1}$$

Figure 1.1: Equivalent circuit of the switched-capacitor

and the equivalent resistance value from (1.1) is equal to

$$R_{ekv} = \frac{T_c}{C} = \frac{1}{f_c C},\tag{1.2}$$

where C is switched-capacitor value and  $f_c = 1/T_c$  is clock frequency.

SC circuits are mainly used for the implementation of active filters–ARC structures. There are also special applications in an analog domain including integrated voltage converters–*charge pumps*. These circuits allow to convert (decrease, increase or invert) the input voltage. Charge pumps were originally constructed for high-voltage applications (particle accelerators that use electromagnetic field, high-voltage generators). Nowadays, charge pumps are important part of low-power integrated circuits [38], for example FLASH memories.

DtAC design represents the fundamental problem, which relates to the solution of the part steps of the design algorithm. The following three key steps are necessary for a successful design:

- circuit model,

- simulation,

- evaluation of the simulation results.

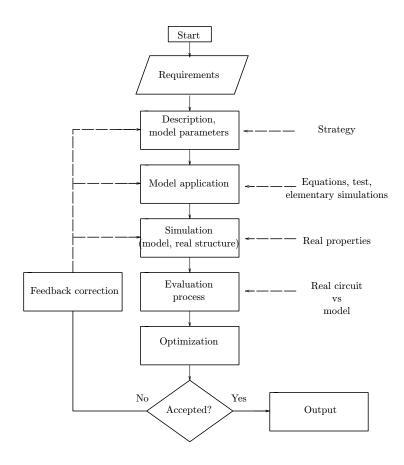

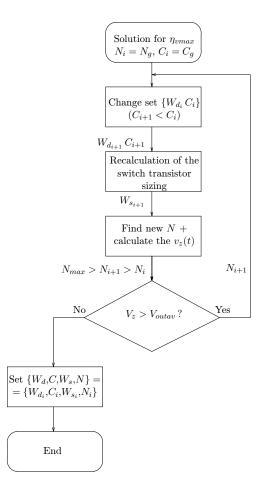

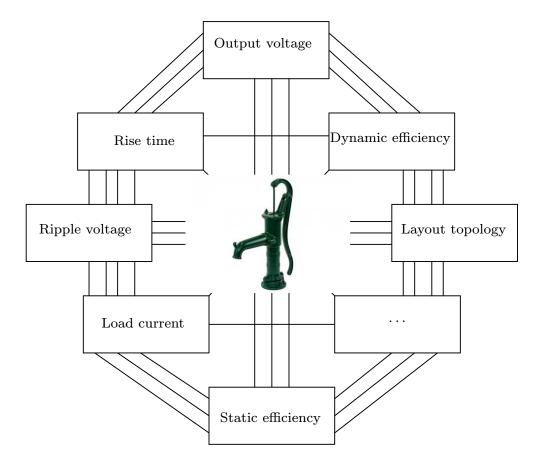

These are closed associated with the general description, as will be discussed bellow. Simulation must be exclusively done in *transient analysis*. Another type of analysis does not make sense in the absence of the operating point. It is a fundamental difference of approach compared to analog circuits. Optimization is usually long-time process due to many iterations to achieve of the required parameters (static, dynamic). However, the optimal solution is not given *unambiguously.* Feedback correction of the design procedure is very useful for this purposes (Fig. 1.2). Characterization system has been published in many books and research papers ([6,7]). However, universal design process has not been known. Quasi-analog systems take over some characteristics of the analog circuits and others from the digital circuits. Some important characteristics are summarized in the Table 1.1. DtACs (including SC circuits) behave as the digital circuit from the "system view" but during the period of the CLK signal are "seen" as an analog circuit. Respecting of this, two methods exist for the circuit description. First method takes into account the continuous nature of the processed signal. The system is described by the differential equations for each phase of the clock signal supplemented by the initial conditions. This method is complex but the computational algorithms are very difficult. Moreover, the transition into the frequecy domain often requires special form of the circuit functions. The second method neglects continuous signal in time and system is only described in the steady state

Figure 1.2: Simplified design algorithm of the DtAC

| Analog systems                        | Digital systems                        |  |  |

|---------------------------------------|----------------------------------------|--|--|

| form of processed signal              | signal processing in the discrete time |  |  |

| frequency limitation                  | clock signal                           |  |  |

| dynamic properties                    | ambiguous properties                   |  |  |

| environmental influence (temperature) | easy tunnable (filters)                |  |  |

| reproducibility                       | easy integration                       |  |  |

Table 1.1: Some properties of the DtAC

(digital circuit). Equations can be directly assembled in the frequency domain (Z-transform) [7]. It is very simple compared with the first method but the process leads to the *ideal case*. The following three methods are preffered for SC circuits in discrete-time domain [8]:

- The equivalent resistors method. Equivalent structure may be resolved by procedures that are specific for analog circuits. The most properties are not be considered (switch resistance, frequency properties, etc.), thus the output function is only an approximation of the real result.

- The charge equation method. The description is based on the SC circuit conversion to the frequency domain using the equivalent circuits. These circuits are derived from the charge matrix  $\mathbf{Q} = \mathbf{C} \cdot \mathbf{U}$  that is equivalent of the admittance matrix  $\mathbf{I} = \mathbf{Y} \cdot \mathbf{U}$ .

• State description. The method is based on the principle that SC circuit is described by the state equations at the end of each phase. State equation from the last phase is also initial condition for the next phase (recurrent equations).

Notice that the inclusion of the real parameters into the calculation in discrete time is *limited* to the mathematical tools to express transfer function in the Z-transform. For example, it can be included: parasitic capacitances, finite gain of the active components.

Because DtAC is multiphase, it is also necessary to define the time interval in which the output of the circuit is active. Then DtAC is modeled by an N-branch circuit for each of the phase [8]. Control signal CLK is two-phase in the simplest case.

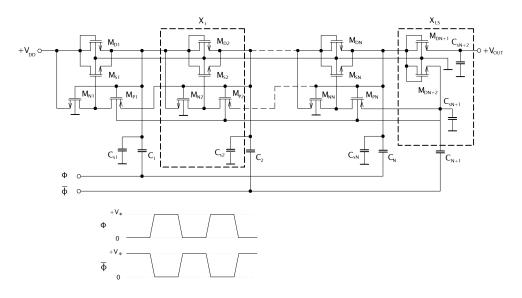

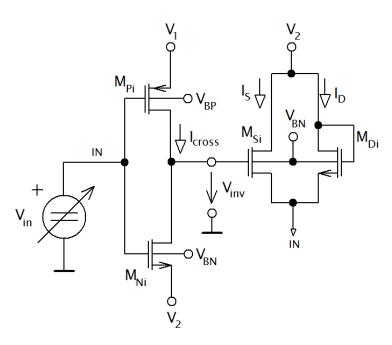

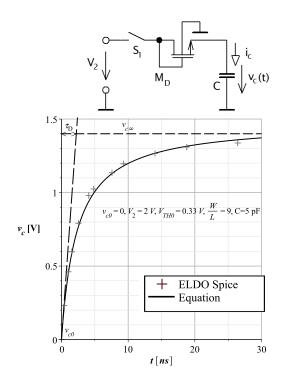

The thesis deals with specific type of the charge pump–**CROSS-COUPLED CHARGE PUMP** patented in 1998 [32], which rapidly solves the problem of the reverse current of the static pump. Nowaday this type of charge pump is still perspective block of the integrated structure; the main advantage is the simple topology, which is receiving the two-phase clock signal. Circuit may be commercially used (ASIC) without claims for patent right, thus **the pump is the subject of thorough research.** The analyzes were made in overview [33–39] but a detailed analysis and description has not been known yet. Published relationships [42–44] come from digital representation of the circuit whose consequences have been pronounced. Their application may not be automatically disapproved, but the model (described by the analytical equations) is usually accurate for a limited set of the parameters [41]. A slightly different path represents the addition of the digital model by the semi-emipric equations obtained by the simulation/measurement of the complex circuit. A number of blocks are modeled in this way, for example BSIM or EKV MOSFET models. Approximation of the measured curves is usually difficult process requiring special mathematical functions. Coefficients contained in the equations are, inter alia, dependent on the specific technological process.

The thesis offers an unconventional view on the charge pump, specifically one type of twophase charge pump. Firstly, the basic conceptions of two-phase charge pumps are introduced, preceding the architecture of the cross-coupled charge pump. The main deals with the *description and design of the pump functional blocks as an analogue circuit* based on the *BSIM model equations*, i.e. operating modes of the active and nonlinear components are captured. Nonlinear system theory is applicable for both the estimation of the real N-stage pump properties (analysis part) and the pump design (synthesis part) via the *state-space model*.

The main benefit of Thesis is the design utility for analogue designers, which allows step by step synthesis on the circuit-level HW realization without the long-time numerical optimization process. High-voltage application asumes the long channel MOSFETs and strong inversion region, so that utility is compatible with other technology process, as PSP or EKV [29].

The program procedure for analysis and synthesis process was created in Maple SW [40] and all the formulae/procedures were verified in the professional design environment Mentor Graphics Design Architect-IC v2008.2\_16.4 including the real models of the components, which are availabled in library MGC Design Kit [31].

### Chapter 2

# Two-phase charge pumps in overview

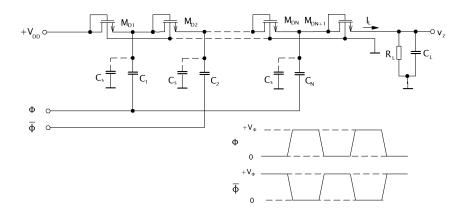

### 2.1 Dickson charge pump

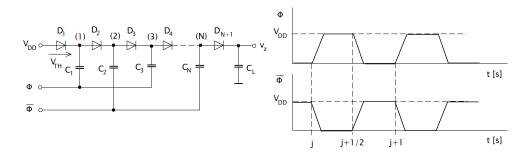

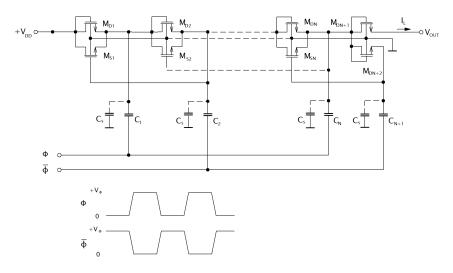

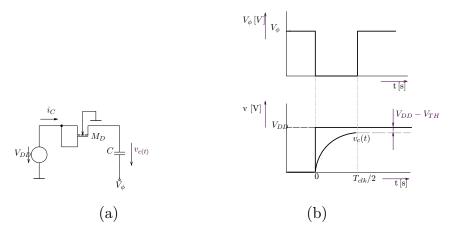

The circuit topology in Fig. 2.1 consists of the chain of the diodes realized by the MOSFETs. Power supply voltage is connected to anode of  $M_{D_1}$  and load impedance  $R_L$ ,  $C_L$  is connected to catode of  $M_{Dn+1}$ . Both the clock signals, labeled  $\phi$ ,  $\bar{\phi}$ , with amplitudes  $V_{\phi}$  and  $V_{\bar{\phi}}$ , which are operating mutually in antiphase, are connected trough the main capacitors to node between catode of the  $M_{Di}$  and anode of the  $M_{Di+1}$ . Diodes ensure the transport charge and "isolates" the pump stages. In the first phase of the clock signal, when  $V_{\phi} = "L"$ , the main capacitors, which are connected to the odd stages, are charged (passive interval) and in the second phase, when  $V_{\bar{\phi}} = "H"$ , the potential in these nodes is increased and the charge is transported to the next stage (active interval). Voltage potential in the next node is reduced by the treshold voltage of the diode transistor  $V_{TH}$ ,

$$v_{i+1} - v_i \doteq V_{TH}$$

and voltage in the node i is reduced by the parasitic capacitor  $C_{si}$ ,

$$v_i' = \frac{C}{C+C_{si}} v_i = \frac{1}{1+\beta} v_i,$$

where  $\beta$  is couple ratio.

Figure 2.1: Dickson charge pump [38]

Figure 2.2: Timing in Dickson charge pump [4]

Repeating of the both cycles, output voltage  $v_{out}$  increases to the end voltage, whose maximal value is theoretically equal to

$$V_{out,max} = V_{DD} + N\left(\frac{\max\{V_{\phi}, V_{\bar{\phi}}\}}{1+\beta} - V_{TH}\right) - V_{TH}, \text{ for } I_L = 0.$$

(2.1)

When the pump output supplies load current  $I_L$ , then average value of the output voltage is given by

$$V_{out,av} = V_{out,max} = R_{pump}I_L = \frac{N}{f_c C(1+\beta)},$$

(2.2)

where f is the cloc signal frequency and  $R_{pump}$  is an equivalent internal pump resistance calculated from SC technique (1.2).

Diode  $D_{n+1}$  is OFF in the low logic level of the  $V_{\phi}$ , in this case, load capacitor  $C_L$  is discharged through the load resistance  $R_L$ . It causes the voltage drop, peak value is defined as [1,2,38],

$$V_r = \frac{I_L}{fC_L} = \frac{V_{out,av}}{fR_LC_L}.$$

(2.3)

#### 2.1.1 Dynamic properties

In this section will be presented main dynamic pump properties: rise time and internal pump equivalent capacitance. Description of the circuit has character of the recurrent expression. Derivation is shown for only the pump with even number of stages, principle is the same for the second case. Accompanying scheme with timing diagram is in Fig. 2.2. Mathematical tool assumes the idealized structure. The following facts must be respected [1, 2, 4]:

- all the switches (MOSFETs) has the same and constant threshold voltage and zero leakage current,

- all the capacitors are ideal,

- parasitic capacitances are negligibly small,

- pulse width of the phase of the CLK is long enough for all the time RC constants in the circuit, amplitude of the CLK is  $V_{DD}$ ,

- rise time of the pump output voltage is very long in comparision with the clock cycle. Then, steady state in each of the pump nodes is assumed.

The capacitor  $C_1$  is fully charged in the time j, in the node 1 is acumulated charge value,

$$Q_1 = C(V_{DD} - V_{TH}). (2.4)$$

During the high logic level of  $V_{\phi} = V_{DD}$ , the charge is injected in node (1). Diode  $D_2$  is ON and charge is transported to node (2). The transport is ended in the time j + 1/2 and potential in node (2) is increased,

$$V_2 = \frac{Q_2 + q_{inj}}{C},$$

(2.5)

where  $Q_2$  is the current charge in node (2) and  $q_{inj}$  is the part of the charge that is trasported after that the potential in node (1) was increased, i.e.  $V_{\phi} = V_{DD}$  and  $V_1 = V_2 + V_{TH}$ . New potential value in node (1) at the time j + 1/2 is equal to:

$$V_1 = V_{DD} + \frac{Q_1 - q_{inj}}{C}.$$

(2.6)

Combining (2.4) and (2.5),

$$V_{TH} = V_{DD} + \frac{Q_1 - q_{inj}}{C} - \frac{Q_2 + q_{inj}}{C}.$$

(2.7)

In the first phase, i.e. at the time j diode  $D_3$  will be OFF and

$$V_{TH} = V_{DD} + \frac{Q_2}{C} - \frac{Q_3}{C}.$$

(2.8)

Combining (2.7) and (2.8),

$$Q_3 = 3C(V_{DD} - V_{TH}) - 2q_{inj}.$$

(2.9)

The following procedure is based on the same principle, as it was shown. In general form, the charge value in each of the nodes is defined as [41],

$$Q(2n-1) = C(2n-1)(V_{DD} - V_{TH}) - 2q_{inj}(n-1)$$

(2.10)

$$Q(2n) = 2nC(V_{DD} - V_{TH}) - 2q_{inj},$$

(2.11)

where 1 < n < N/2. Charge in the N<sup>th</sup> pump stage, when diode  $D_{N+1}$  is OFF, is given by

$$Q_N = C(V_{out,av} - V_{DD} + V_{TH}), (2.12)$$

By comparing of both equations (2.11) and (2.12), relationship for injected charge was derived by Dickson [38]:

$$q_{inj}\frac{C}{N}\left[(V_{DD} - V_{TH})(N+1) - V_{out,av}\right].$$

(2.13)

Combining (2.10), (2.11) and (2.13), the charge accumulated in each the main capacitor is calculated from:

$$Q(2n-1) = \frac{2C(n-1)}{N} \left( V_{out,av} - V_{DD} + V_{TH} \right) + C(V_{DD} - V_{TH})$$

(2.14)

$$Q(2n) = \frac{2nC}{N} (V_{out,av} - V_{DD} + V_{TH}).$$

(2.15)

Total pump charge can be determined in 2 ways: based on the charges that are stored in each of the capacitor or from the sum of the injected charges during the period of the CLK. The sum of all the charges in the circuit, labeled  $Q_{cc}(n,j)$ , for  $0 \le n \le N$  is given by [1,2,4,38]:

$$Q_{cc}^{d}(j) = \sum_{n=1}^{N} Q_{cc}(k,j) = \sum_{n=1}^{N} n[Q(n,j) - Q(n,0)] + (N+1)[Q_{inj} - Q_{inj}(0)].$$

(2.16)

Using the following initial conditions,

$$Q(2n,0) = 0, (2.17)$$

$$Q(2n-1,0) = C(V_{DD} - V_{TH}), (2.18)$$

$$Q_{inj}(0) = C_L (V_{DD} - V_{TH}), (2.19)$$

which follow from (2.14) and (2.15). Using (2.12) (2.14) and (2.15), total charge in circuit is given by,

$$Q_{cc}^{d}(j) = (N+1)C_{L}^{\prime}(V_{out}(j) - V_{DD} + V_{TH})$$

(2.20)

Load capacitance consists two parts: load capacitance  $C_L$  and pump capacitance  $C_{pump}$ ,

$$C_{pump} = \begin{cases} \frac{4N^2 + 3N + 2}{12(N+1)}C, & \text{for even } N\\ \frac{4N^2 - N - 3}{12N}C, & \text{for odd } N. \end{cases}$$

(2.21)

Total charge, which is acumulated at time j is given by

$$Q_{cc}(j) = (N+1) \sum_{n=0}^{j} \frac{C}{N} \left[ (N+1) \left( V_{DD} - V_{TH} \right) - V_{out}(m) \right].$$

(2.22)

Combining (2.16) and (2.22), the follow charge equation is valid:

$$C_{L}^{\prime} = (V_{out}(j) - V_{DD} + V_{TH}) = \sum_{m=0}^{j} \frac{C}{N} \left[ (N+1)(V_{DD} - V_{TH}) - V_{out}(m) \right]$$

(2.23)

and substituting of the the recursive expression to (2.23), then

$$C_{L}^{,}(V_{out}(j+1) - V_{out}(j)) = \frac{C}{N} \left[ (N+1)(V_{DD} - V_{TH}) - V_{out}(j+1) \right].$$

(2.24)

Substituting the initial condition  $V_{out}(0) = V_{DD} - V_{TH}$  from (2.19) into (2.24), the output voltage at the time j becomes to

$$V_{out}(j) = (N+1)(V_{DD} - V_{TH}) + [V_{out}(0) - (N+1)(V_{DD} - V_{TH})]\lambda^{j}, \qquad (2.25)$$

where  $\lambda = \frac{1}{1 + \frac{C}{NC_L^{,}}}$ .

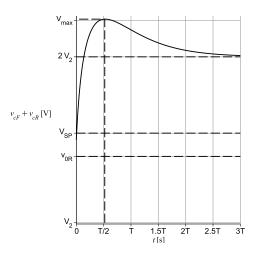

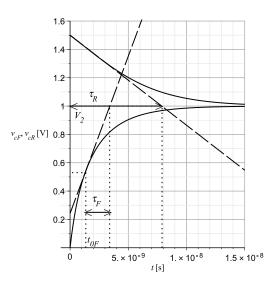

Rise time, during of it the pump output voltage increases from initial value  $V_{out}(0)$  to end voltage value  $V_{fin}$  was derived by Tanzawa and Tanaka [1]:

$$T_{r} = \frac{\ln\left[1 - \frac{V_{fin} - V_{out}(0)}{N(V_{DD} - V_{TH})}\right]}{\ln(\lambda)} \frac{1}{f}$$

(2.26)

Average value of the power supply current during the time  $T_r$  is calculated from:

$$I_{DD} \approx \frac{Q_{cc}(T_r)}{T_r} = \frac{(N+1)(V_{fin} - V_{out}(0))C_L^{,}}{T_r},$$

(2.27)

similarly, average value of the load current is given by:

$$I_L = \frac{C_L^{,}(V_{fin} - V_{out}(0))}{T_r}.$$

(2.28)

Now, power dissispation and output power are defined as,

$$P_{in} = \sum_{j=0}^{T_r} \frac{q_{cc}(j)V_{DD}}{T_r} = \frac{(N+1)(V_{fin} - V_{out}(0)V_{DD}C_L^{,}}{T_r},$$

(2.29)

$$P_{out} = \sum_{j=0}^{T_r} \frac{q_{inj}(j)V_{out}(j)}{T_r} = \frac{1}{2}C_L^{,} \frac{V_{fin}^2 - V_{out}^2(0)}{T_r}$$

(2.30)

and dynamic efficiency during  $T_r$  is given by

$$\varepsilon_{T_r} = \frac{P_{out}}{P_{in}} = \frac{V_{fin} + V_{out}(0)}{2(N+1)V_{DD}}$$

(2.31)

Dynamic efficiency is approximately equal to half of the efficiency in the steady state [38]:

$$\varepsilon_s = \frac{V_{DD} + N \left[ \frac{\max\{V_{\phi}, V_{\bar{\phi}}\}}{1+\beta} - V_{TH} - \frac{I_L}{fC(1+\beta)} \right]}{(N+1)V_{DD}}$$

(2.32)

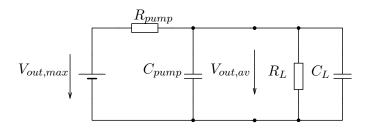

The charge pump is modeled by the analogue prototype [38], see Fig. 2.3. However, it does not mean that circuit reflects the dominant effects of the real structure, as it was explained in introduction. The dominant parts of the pump losses are primarly threshold voltage and body effect and parasitic capacitances, which can be also included into the previous equations. Derivation was done, for example, in [4,5,41]. Mentioned description is usually used for practical design, despite its shortcomings. Simplicity of the implementation is main advantage of the description. Experiments and verification of all the pump characteristics are listed in [3,5,41].

Figure 2.3: Equivalent circuit of the charge pump [38]

Problems of the circuit description exist in case of more advanced topologies. Although these increase efficiency, show the other effects, whose mathematical expression is difficult.

### 2.2 Static pump CTS-1

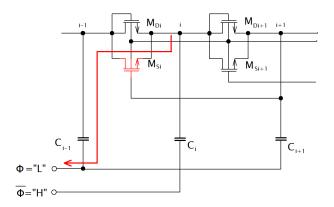

Static pump CTS-1 (Charge-Transfer-Switch) to some extent eliminates threshold voltage transfer elements so that the switch transistor is connected in parallel to the diode in each of the pump stages. Diagram is shown in Fig. 2.4 Each of the switch transistor, whose Drain and

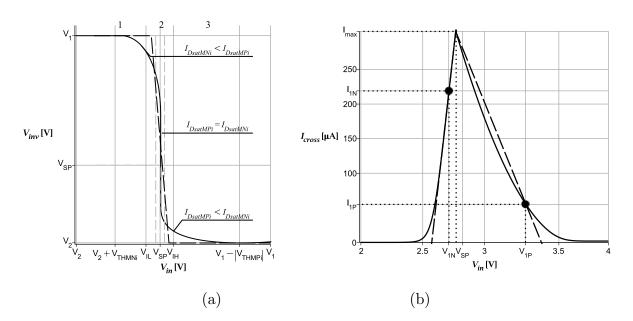

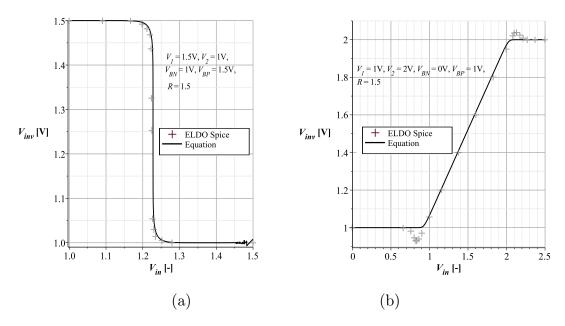

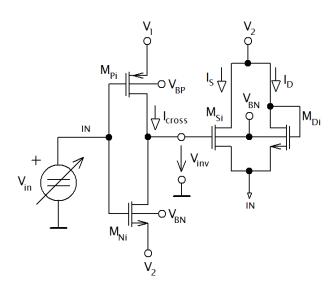

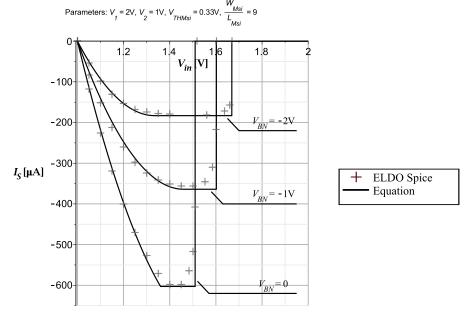

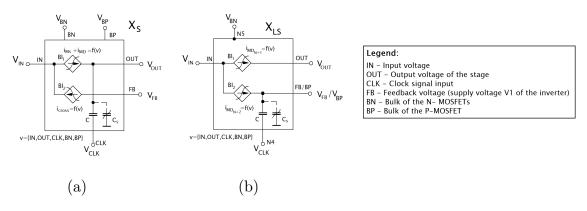

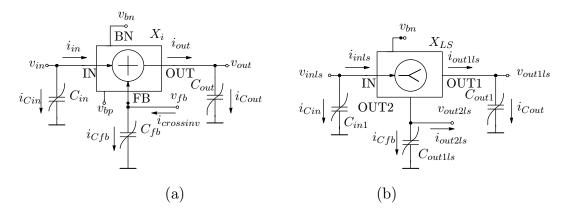

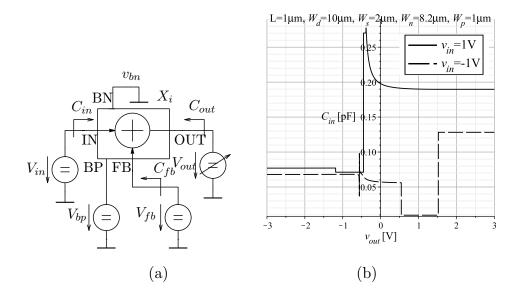

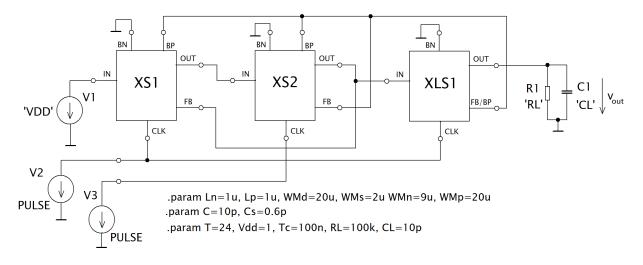

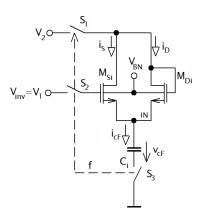

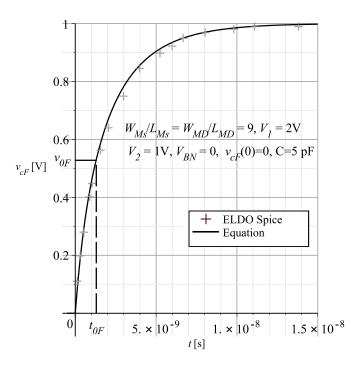

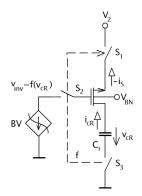

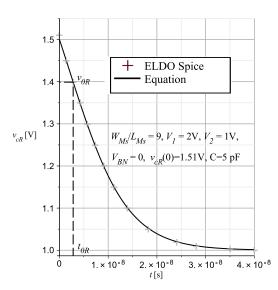

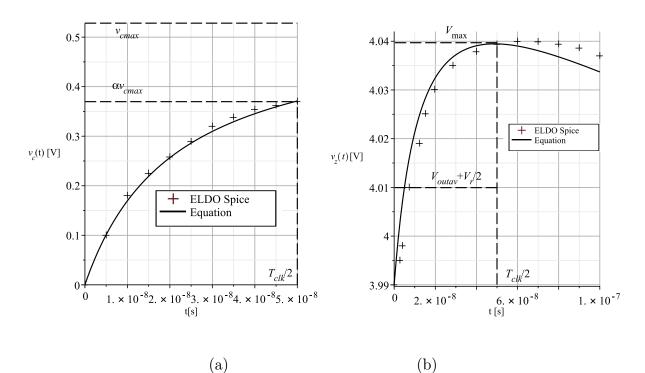

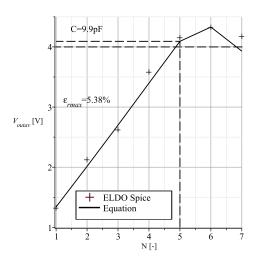

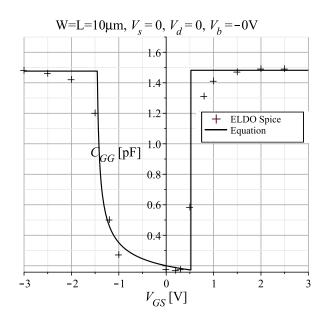

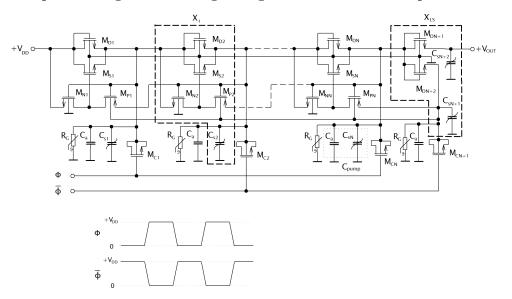

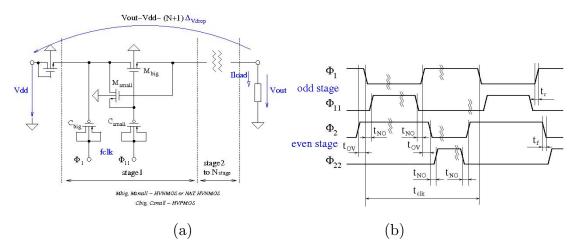

Figure 2.4: CTS-1 charge pump [32]