#### ASSIGNMENT OF BACHELOR'S THESIS

| Title:           | Power side channel information leakage of a microcontroller |

|------------------|-------------------------------------------------------------|

| Student:         | Marina Shchavleva                                           |

| Supervisor:      | Ing. Jiří Buček                                             |

| Study Programme: | Informatics                                                 |

| Study Branch:    | Computer engineering                                        |

| Department:      | Department of Digital Design                                |

| Validity:        | Until the end of summer semester 2018/19                    |

#### Instructions

Study the methods of power analysis attacks on microcontrollers. Design and implement an experiment with the aim to analyze the dependencies of power consumption on individual instructions of an AVR microcontroller. Dependency on instruction type, operand value, and instruction address will be analyzed. Create an experimental measurement setup, execute necessary measurements, and analyze the results.

#### References

Will be provided by the supervisor.

doc. Ing. Hana Kubátová, CSc. Head of Department doc. RNDr. Ing. Marcel Jiřina, Ph.D. Dean

Prague February 2, 2018

# Acknowledgements

I would like to thank my supervisor Ing. Jiří Buček for introduction to power analysis, for his help and valuable advices. Also I want to thank my partner, Ladislav, for his support and, of course, my parents, who sent me to study abroad in the first place, for their endless love and support throughout my study here and their patience.

## Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular that the Czech Technical University in Prague has the right to conclude a license agreement on the utilization of this thesis as school work under the provisions of Article 60(1) of the Act.

In Prague on May 15, 2018

Czech Technical University in Prague Faculty of Information Technology © 2018 Marina Shchavleva. All rights reserved. This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the

#### Copyright Act).

#### Citation of this thesis

Shchavleva, Marina. Power side channel information leakage of a microcontroller. Bachelor's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2018.

## Abstrakt

Spotřeba zařízení může prozradit mnoho informací ohledně jeho vnitřní struktury a toku dat který toto zařízení zpracovává. Jednoduchá a Diferenciální odběrové analýzy jsou v odborné literatuře široce probrané techniky pro útoky postranními kanály. Tato práce uvádí čtenáře do problematiky analýzy spotřeby a dává krátký přehled metod, které jsou k tomu používány.

Hlavním cílem této bakalářské práce je analýza spotřeby mikrořadiče při vykonávání různých operací z jeho instrukční sady, konkrétně se jedná o mikrořadič ATMega163, vestavěný do smartkarty. Jsou probrány důležité aspekty toho, jak mikrořadič funguje a jak zpracovává instrukce: instrukční cyklus, adresy v paměti programu, hodnoty operandů a tok dat. Kromě toho práce popisuje jak typ instrukce ovlivňuje spotřebu, jinak řečeno, jaké procesy se odehrávají uvnitř mikrořadiče při zpracování dat a kontrole toku programu.

**Klíčová slova** útoky postranními kanály, analýza spotřeby, SPA, DPA, spotřeba mikrořadičů, ATMega163, instrukční sada

### Abstract

Through power consumption of a device a lot of information about it internal structure and data it processes can be leaked. Simple and Differential power analysis are well described techniques for such side channel attacks. This work gives brief introduction to the idea of power side channel analysis and methods it uses.

The main objective of this Bachelor's thesis is power side channel analysis of a microcontroller's instruction set specifically ATMega163 which is embedded in a smartcard. Important aspects of microcontroller's operation and it's instructions are discussed: instruction execution cycle, address in a Program Memory, operand values and data flow. Also how instruction type affects power consumption, in other words, what does microcontroller internally do to process data or manage program flow.

**Keywords** side channel attacks, power analysis, SPA, DPA, microcontroller's power consumption, ATMega163, instruction set

# Contents

|          |      | Citation of this thesis                                                       | vi |

|----------|------|-------------------------------------------------------------------------------|----|

| In       | trod | uction                                                                        | 1  |

| 1        | Pow  | ver side channel analysis attacks                                             | 3  |

|          | 1.1  | Power analysis attacks                                                        | 3  |

|          |      | 1.1.1 Simple Power Analysis                                                   | 3  |

|          |      | 1.1.2 Differential power Analysis                                             | 5  |

|          |      | 1.1.3 High-Order Differential Power Analysis                                  | 6  |

|          | 1.2  | Summary                                                                       | 6  |

| <b>2</b> | Test | design and measurement setup                                                  | 7  |

|          | 2.1  | Measurement setup                                                             | 7  |

|          |      | 2.1.1 Obtaining power traces: SC Power Measurement                            | 7  |

|          |      | 2.1.2 Post-processing $\ldots$                                                | 8  |

|          | 2.2  | Test design                                                                   | 10 |

|          |      | 2.2.1 Design properties                                                       | 10 |

|          |      | 2.2.2 Test generation and communication with measurement                      |    |

|          |      | setup $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 12 |

|          | 2.3  | Software                                                                      | 12 |

| 3        | Pow  | ver consumption analysis of a microcontroller ATMega163                       | 13 |

|          | 3.1  | Architecture and instruction execution of $ATMega163$                         | 13 |

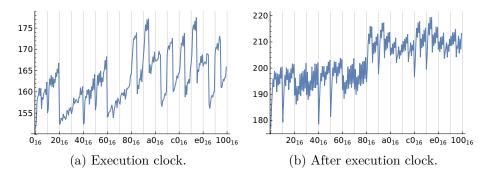

|          | 3.2  | Instruction address dependency                                                | 15 |

|          | 3.3  | Operand value dependency                                                      | 17 |

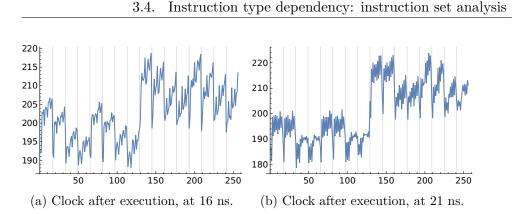

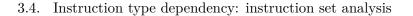

|          | 3.4  | Instruction type dependency: instruction set analysis                         | 20 |

|          |      | 3.4.1 Arithmetic and logic instructions                                       | 20 |

|          |      | 3.4.2 Bit and bit-test instructions                                           | 34 |

|          |      | 3.4.3 Data transfer instructions                                              | 38 |

|          |      | 3.4.4 Branch instructions                                                     | 54 |

|          | 3.5  | Analysis summary                                                              | 61 |

|    | 3.5.1       | Instruction comparison | 61        |

|----|-------------|------------------------|-----------|

|    | 3.5.2       | Results                | 62        |

| Co | onclusion   |                        | 65        |

| Bi | bliography  |                        | 67        |

| A  | Acronyms    |                        | 69        |

| в  | Contents of | of enclosed CD         | <b>71</b> |

# **List of Figures**

| 1.1        | SPA trace of basic square-and-multiply algorithm [5]                                                                                                                      | 4        |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2        | SPA trace showing an entire DES operation [7]                                                                                                                             | 5        |

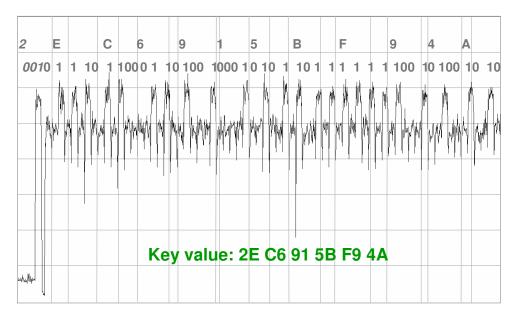

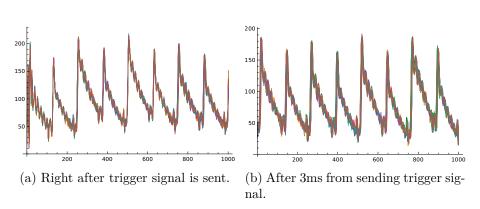

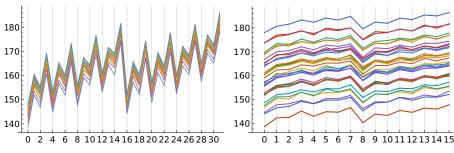

| 2.1        | One hundred of raw power traces of 1 $\mu$ s                                                                                                                              | 9        |

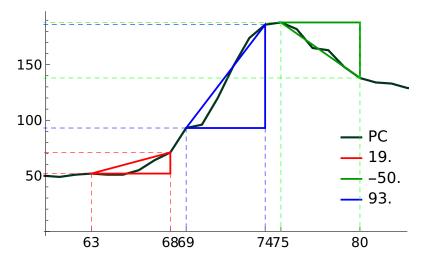

| 2.2        | Analysis of a three sample pairs in a window for $n = 5$ with position<br>to analysis 63, 69, 75. Legend shows difference value by which the<br>starting point is chosen. | 9        |

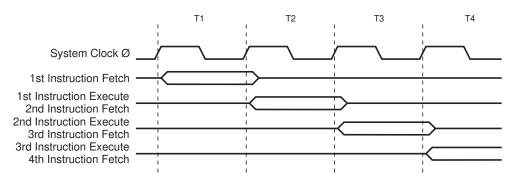

| 3.1        | The Parallel Instruction Fetches and Instruction Executions                                                                                                               | 14       |

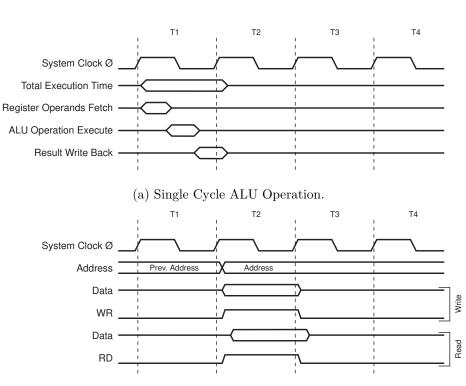

| 3.2        | Operations during execution stage of ATMega163                                                                                                                            | 15       |

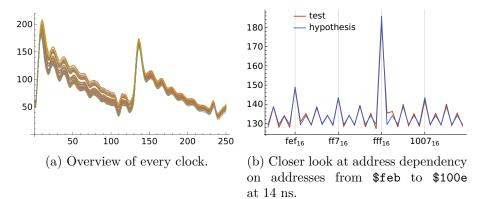

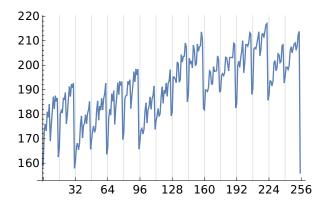

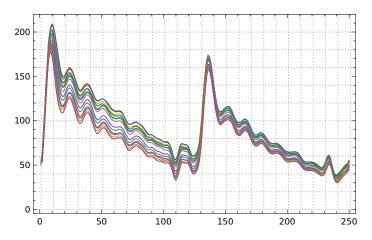

| 3.3        | NOP executed at 6000 different addresses, starting from $2b5.$                                                                                                            | 16       |

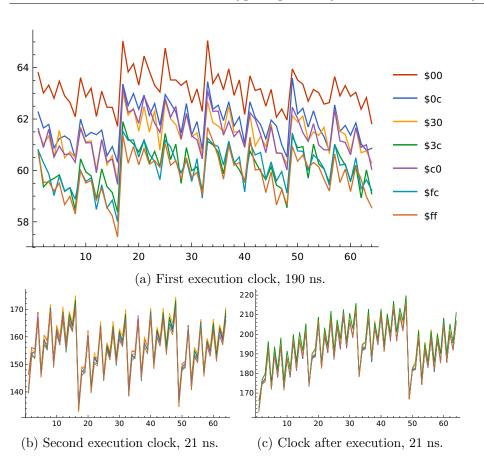

| 3.4        | Power traces at 18 ns for constant number of destination register<br>and different data stored in it                                                                      | 18       |

| 3.5        | Power traces of ADD, where destination register is constant in data<br>and it's number and changing number of source register and their<br>data                           | 18       |

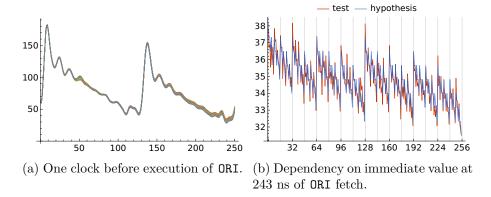

| 3.6        | Fetch of ORI with different immediate values.                                                                                                                             | 18<br>19 |

| 3.0<br>3.7 | Power traces of ADD r16, r17, where r17 is ranging from 0 to 255                                                                                                          | 19       |

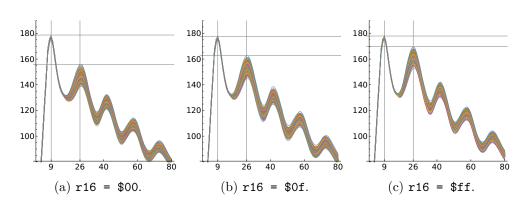

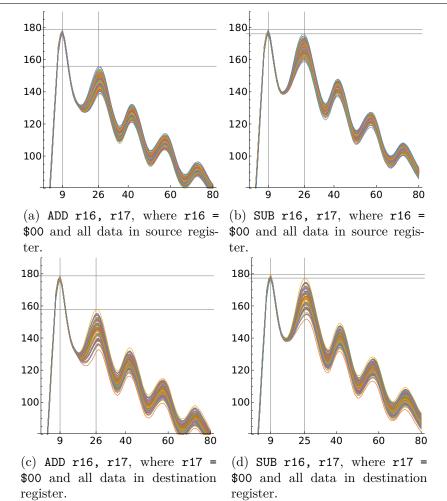

| 0.1        | and with different values stored in r16                                                                                                                                   | 21       |

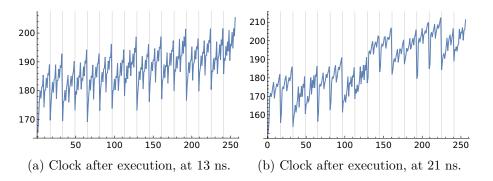

| 3.8        | Power traces of clock after ADD r16, r17, where r16 contains \$0f                                                                                                         |          |

|            | and $\texttt{r17}$ is ranging from 0 to 255 at different points of execution                                                                                              | 22       |

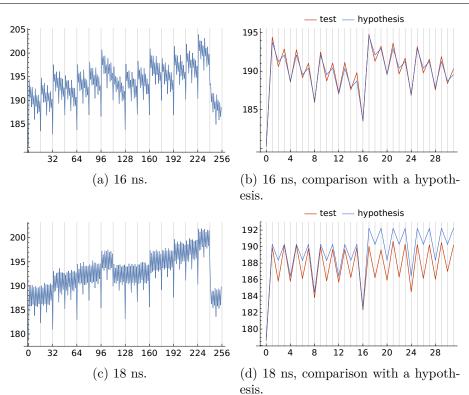

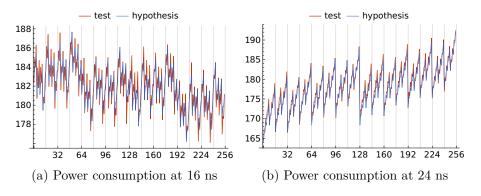

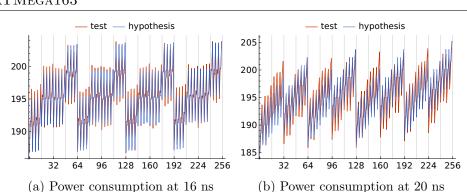

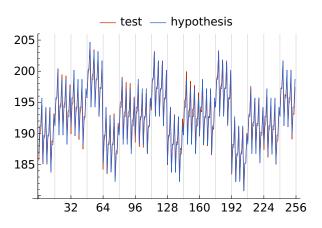

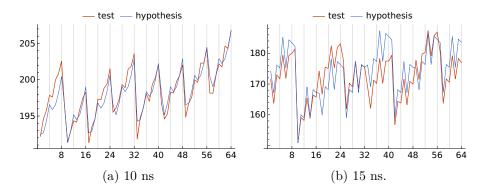

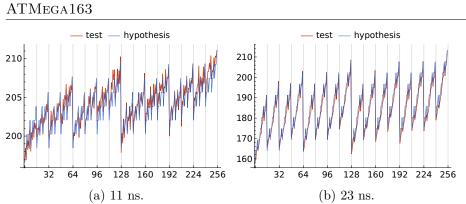

| 3.9        | Power consumption in the clock after ${\tt SUB}$ execution at 16 ns, with                                                                                                 |          |

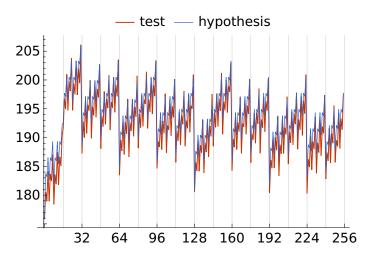

|            | hypothesis.                                                                                                                                                               | 23       |

| 3.10       | Comparison between power consumption of ADD r16, r17 and SUB with different data being processed.                                                                         | 24       |

| 3.11       | Power consumption of SUBI at 21 ns with constant value in desti-                                                                                                          |          |

|            | nation register and different immediate values                                                                                                                            | 25       |

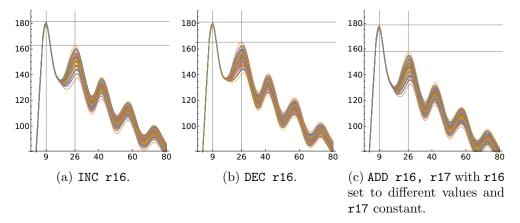

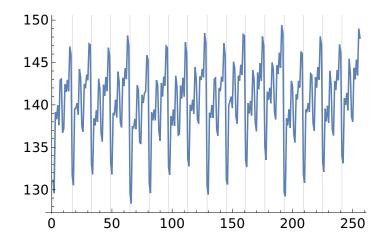

| 3.12       | Comparison between ADD and INC                                                                                                                                            | 27       |

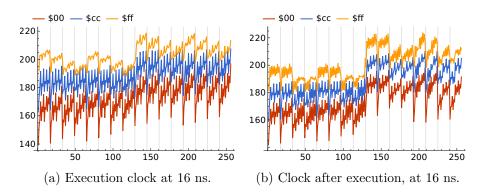

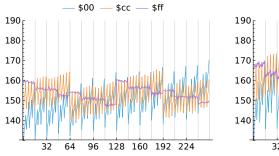

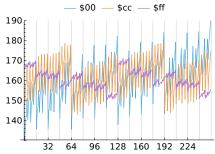

| <ul> <li>3.14 Power consumption of ANDI with different immediate values and constant value stored at destination register at the clock of execution at 16 ns.</li> <li>3.15 Power consumption of ANDI with different immediate values and constant value stored at destination register at and the clock after 3.16 Power consumption of a clock after execution of ANDI with different immediate values and with different constants stored at destination register.</li> <li>3.17 Power consumption of clock after OR r16, K, with r16 = \$cc and all possible K at different points of execution with respective hypotheses.</li> <li>3.18 Power consumption of ORII with different immediate values and constant value stored at destination register at and the clock after 3.19 Clock after execution of ASR in comparison with my hypothesis, that power consumption is dependent on original data and a resul 3.20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution .</li> <li>3.21 Power consumption of MOV with different values stored in source register and constant value stored at destination register at the clock after execution at 16 ns.</li> <li>3.22 Power consumption of LDI with different immediate values and zero stored in destination register at the clock after execution at 24 ns.</li> <li>3.23 Power consumption of second execution clock of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 13 ns.</li> <li>3.24 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different .</li> <li>3.26 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.25 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.26 Power consumption of LD with constant addresses are set to \$00, with respective hypothesis, at 17 ns.</li> <li>3.27 Power cons</li></ul>   | 3.13 | Power consumption of clock after AND r16, K, with r16 = \$cc<br>and all possible K at different points of execution with respective     | 20       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

| <ul> <li>tion at 16 ns.</li> <li>3.15 Power consumption of ANDI with different immediate values and constant value stored at destination register at and the clock after</li> <li>3.16 Power consumption of a clock after execution of ANDI with different immediate values and with different constants stored at destination register.</li> <li>3.17 Power consumption of clock after OR r16, K, with r16 = \$cc and all possible K at different points of execution with respective hypotheses.</li> <li>3.18 Power consumption of ORII with different immediate values and constant value stored at destination register at and the clock after</li> <li>3.18 Power consumption of ORII with different immediate values and constant value stored at destination register at and the clock after</li> <li>3.19 Clock after execution of ASR in comparison with my hypothesis, that power consumption is dependent on original data and a resul</li> <li>3.20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution .</li> <li>3.21 Power consumption of MOV with different values stored in source register and constant value stored at destination register at the clock after execution at 16 ns.</li> <li>3.22 Power consumption of LDI with different immediate values and zero stored in destination register at the clock after execution at 26 and reses as operand value, loading 256 data entries from addresses starting with \$0070 at 22 ns.</li> <li>3.24 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different .</li> <li>3.25 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different values at different .</li> <li>3.26 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different values at different .</li> <li>3.26 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different values at different .</li> <li>3.27 Power consumption at the second clock of LD with increm</li></ul>   | 3.14 | hypotheses                                                                                                                              | 29       |

| <ul> <li>constant value stored at destination register at and the clock after</li> <li>3.16 Power consumption of a clock after execution of ANDI with different immediate values and with different constants stored at destination register.</li> <li>3.17 Power consumption of clock after OR r16, K, with r16 = \$cc and all possible K at different points of execution with respective hypotheses.</li> <li>3.18 Power consumption of ORII with different immediate values and constant value stored at destination register at and the clock after</li> <li>3.19 Clock after execution of ASR in comparison with my hypothesis, that power consumption is dependent on original data and a resul</li> <li>3.20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution .</li> <li>3.21 Power consumption of MOV with different values stored in source register and constant value stored at destination register at the clock after execution at 16 ns.</li> <li>3.22 Power consumption of LDI with different immediate values and zero stored in destination register at the clock after execution at 16 ns.</li> <li>3.23 Power consumption of second execution clock of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 13 ns.</li> <li>3.24 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different .</li> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different .</li> <li>3.26 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.25 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different values at different .</li> <li>3.26 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different values at different .</li> <li>3.27 Power consumption at the second clock of LD with increment/decret b</li></ul> |      | 0                                                                                                                                       | 30       |

| <ul> <li>immediate values and with different constants stored at destination register.</li> <li>3.17 Power consumption of clock after OR r16, K, with r16 = \$cc and all possible K at different points of execution with respective hypotheses.</li> <li>3.18 Power consumption of ORII with different immediate values and constant value stored at destination register at and the clock after</li> <li>3.19 Clock after execution of ASR in comparison with my hypothesis, that power consumption is dependent on original data and a resul</li> <li>3.20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution .</li> <li>3.21 Power consumption of MOV with different values stored in source register and constant value stored at destination register at the clock after execution at 16 ns.</li> <li>3.22 Power consumption of LDI with different immediate values and zero stored in destination register at the clock after execution at 24 ns.</li> <li>3.23 Power consumption of second execution clock of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 13 ns.</li> <li>3.24 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different .</li> <li>3.25 Power consumption of LD with constant addresses \$70 to \$b0, with first six bits prepended with different values at different .</li> <li>3.26 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.24 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are loaded into register that is set to \$cc.</li> <li>3.27 Power consumption at the second clock of LD with increment/decrement both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns.</li> </ul>                                                                                                                               | 3.15 | Power consumption of ANDI with different immediate values and constant value stored at destination register at and the clock after.     | 31       |

| <ul> <li>3.17 Power consumption of clock after OR r16, K, with r16 = \$cc and all possible K at different points of execution with respective hypotheses.</li> <li>3.18 Power consumption of ORII with different immediate values and constant value stored at destination register at and the clock after</li> <li>3.19 Clock after execution of ASR in comparison with my hypothesis, that power consumption is dependent on original data and a resul</li> <li>3.20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.16 | Power consumption of a clock after execution of ANDI with different immediate values and with different constants stored at destination |          |

| <ul> <li>all possible K at different points of execution with respective hypotheses.</li> <li>3.18 Power consumption of ORII with different immediate values and constant value stored at destination register at and the clock after</li> <li>3.19 Clock after execution of ASR in comparison with my hypothesis, that power consumption is dependent on original data and a resul</li> <li>3.20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution</li> <li>3.21 Power consumption of MOV with different values stored in source register and constant value stored at destination register at the clock after execution at 16 ns.</li> <li>3.22 Power consumption of LDI with different immediate values and zero stored in destination register at the clock after execution at 24 ns.</li> <li>3.23 Power consumption of second execution clock of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 13 ns.</li> <li>3.24 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different.</li> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different.</li> <li>3.26 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different values at different data are loaded into register that is set to \$cc.</li> <li>3.27 Power consumption of LD with constant address, at loaded memory entry \$00, with respective hypothesis, at 17 ns.</li> <li>3.28 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns.</li> </ul>                                                                                                                                                                                                                                                                                                                     | 3.17 |                                                                                                                                         | 31       |

| <ul> <li>3.18 Power consumption of ORII with different immediate values and constant value stored at destination register at and the clock after</li> <li>3.19 Clock after execution of ASR in comparison with my hypothesis, that power consumption is dependent on original data and a resul</li> <li>3.20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.11 | all possible K at different points of execution with respective hy-                                                                     | 32       |

| <ul> <li>3.19 Clock after execution of ASR in comparison with my hypothesis, that power consumption is dependent on original data and a result and 20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.18 | Power consumption of $\tt ORII$ with different immediate values and                                                                     |          |

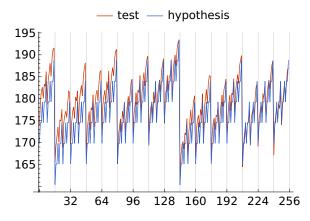

| <ul> <li>3.20 Dependency on a Hamming Distance between result and data processed at the clock after SWAP execution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.19 |                                                                                                                                         | 32       |

| <ul> <li>cessed at the clock after SWAP execution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 20 | that power consumption is dependent on original data and a result.                                                                      | 35       |

| <ul> <li>register and constant value stored at destination register at the clock after execution at 16 ns.</li> <li>3.22 Power consumption of LDI with different immediate values and zero stored in destination register at the clock after execution at 24 ns.</li> <li>3.23 Power consumption of second execution clock of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 13 ns.</li> <li>3.24 Power consumption of clock after execution of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 22 ns.</li> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different.</li> <li>3.26 Power consumption of LD with constant address, different data are loaded into register that is set to \$cc.</li> <li>3.27 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.28 Power consumption at the second clock of LD with increment/decrement both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns.</li> <li>3.29 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | cessed at the clock after SWAP execution $\ldots \ldots \ldots \ldots \ldots$                                                           | 36       |

| <ul> <li>3.22 Power consumption of LDI with different immediate values and zero stored in destination register at the clock after execution at 24 ns.</li> <li>3.23 Power consumption of second execution clock of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 13 ns.</li> <li>3.24 Power consumption of clock after execution of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 22 ns.</li> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different.</li> <li>3.26 Power consumption of LD with constant address, different data are loaded into register that is set to \$cc.</li> <li>3.27 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.28 Power consumption at the second clock of LD with increment/decrer both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns.</li> <li>3.29 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.21 | Power consumption of MOV with different values stored in source register and constant value stored at destination register at the       |          |

| <ul> <li>stored in destination register at the clock after execution at 24 ns.</li> <li>3.23 Power consumption of second execution clock of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 13 ns.</li> <li>3.24 Power consumption of clock after execution of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 22 ns.</li> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different.</li> <li>3.26 Power consumption of LD with constant address, different data are loaded into register that is set to \$cc.</li> <li>3.27 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.28 Power consumption at the second clock of LD with increment/decrement both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns.</li> <li>3.29 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | clock after execution at 16 ns                                                                                                          | 39       |

| <ul> <li>addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 13 ns.</li> <li>3.24 Power consumption of clock after execution of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 22 ns.</li> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different.</li> <li>3.26 Power consumption of LD with constant address, different data are loaded into register that is set to \$cc.</li> <li>3.27 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.28 Power consumption at the second clock of LD with increment/decrer both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns.</li> <li>3.29 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.22 | Power consumption of LDI with different immediate values and zero stored in destination register at the clock after execution at 24 ns. | 40       |

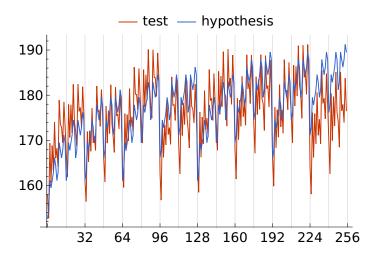

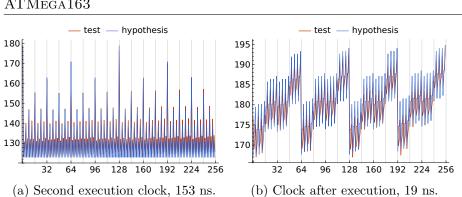

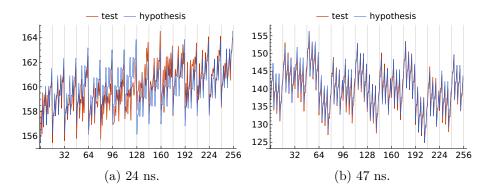

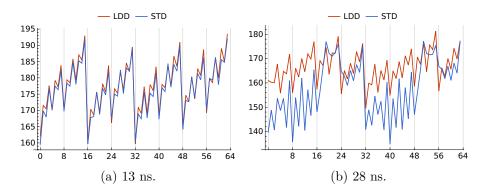

| <ul> <li>3.24 Power consumption of clock after execution of LDS with different addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 22 ns.</li> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different.</li> <li>3.26 Power consumption of LD with constant address, different data are loaded into register that is set to \$cc.</li> <li>3.27 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.28 Power consumption at the second clock of LD with increment/decrementry \$00, with respective hypothesis, at 17 ns.</li> <li>3.29 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.23 | addresses as operand value, loading 256 data entries from addresses                                                                     |          |

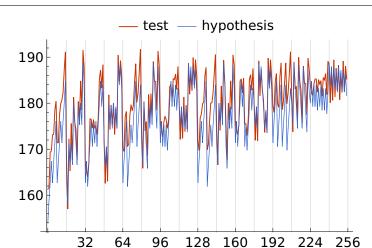

| <ul> <li>starting with \$0070 at 22 ns.</li> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different.</li> <li>3.26 Power consumption of LD with constant address, different data are loaded into register that is set to \$cc.</li> <li>3.27 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.28 Power consumption at the second clock of LD with increment/decrer both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns.</li> <li>3.29 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.24 |                                                                                                                                         | 41       |

| <ul> <li>3.25 Power consumption of LDS with addresses \$70 to \$b0, with first six bits prepended with different values at different</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | addresses as operand value, loading 256 data entries from addresses starting with \$0070 at 22 ns                                       | 42       |

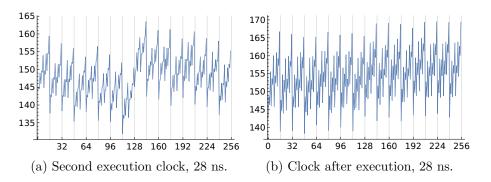

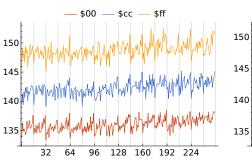

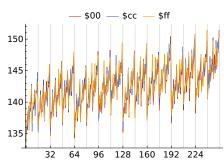

| <ul> <li>3.26 Power consumption of LD with constant address, different data are loaded into register that is set to \$cc</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.25 | Power consumption of LDS with addresses \$70 to \$b0, with first                                                                        | 43       |

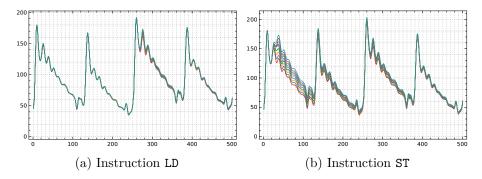

| <ul> <li>3.27 Power consumption of LD with constant address, at loaded memory entry \$00 is stored, different data are stored in register.</li> <li>3.28 Power consumption at the second clock of LD with increment/decrement both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns.</li> <li>3.29 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis are set to \$00, with respective hypothesis at 17 ns.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.26 | Power consumption of LD with constant address, different data are                                                                       |          |

| <ul> <li>3.28 Power consumption at the second clock of LD with increment/decrement both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.27 | -                                                                                                                                       | 44       |

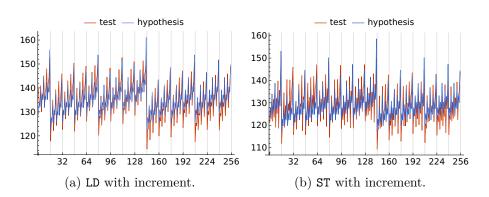

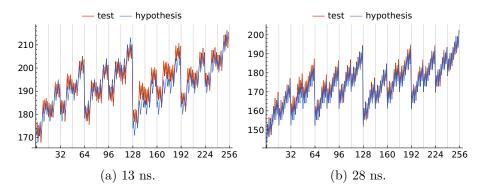

| <ul><li>both destination register and memory entry at tested addresses are set to \$00, with respective hypothesis, at 17 ns</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.28 | entry \$00 is stored, different data are stored in register Power consumption at the second clock of LD with increment/decrement        | 44<br>nt |

| 3.29 Power consumption at the second clock of LDD, both destination register and memory entry at tested addresses are set to \$00, with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.20 | both destination register and memory entry at tested addresses are                                                                      |          |

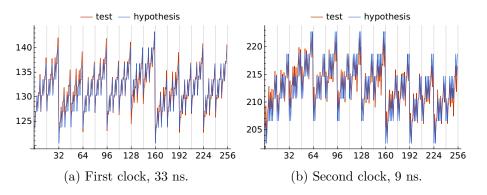

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.29 | Power consumption at the second clock of LDD, both destination                                                                          | 45       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | register and memory entry at tested addresses are set to \$00, with respective hypothesis, address is set to \$77                       | 46       |

| 3.30 | Power consumption of ST with constant address, different data are     |    |

|------|-----------------------------------------------------------------------|----|

|      | stored from register, with memory entry set to <b>\$cc.</b>           | 47 |

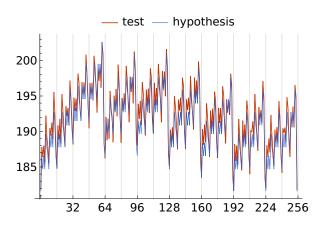

| 3.31 | Power consumption of ST tested at 21 ns                               | 48 |

| 3.32 | Power consumption of ST in dependency on data in source register      |    |

|      | and those stored in memory.                                           | 48 |

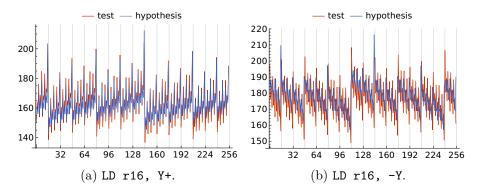

| 3.33 | Power consumption of $ST$ and $LD$ at 50 ns with increment and        |    |

|      | respective hypotheses                                                 | 49 |

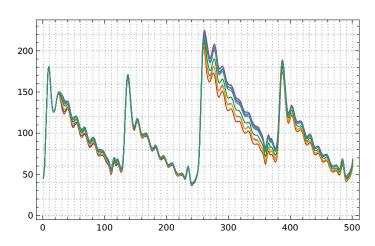

| 3.34 | Comparison between power consumption of a second clock of in-         |    |

|      | structions LDD and STD.                                               | 50 |

| 3.35 | Power consumption of first clock of LPM execution from address \$582, |    |

|      | accessing 256 different addresses                                     | 53 |

| 3.36 | Power consumption of IJMP with respective hypothesis                  | 54 |

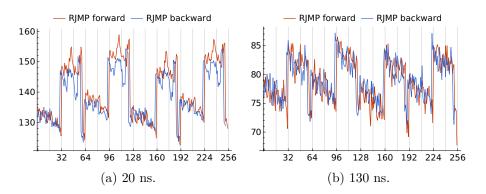

| 3.37 | Power consumption of RJMP, third clock of execution at 10 ns          | 55 |

| 3.38 | Power consumption of RJMP, first clock of execution, both executed    |    |

|      | from same addresses, with different relative address value            | 56 |

| 3.39 | Power consumption of SBRS r16, 4, second clock of execution,          |    |

|      | different data are set into register, so skip does or does not occur  |    |

|      | in dependency on bit 4                                                | 60 |

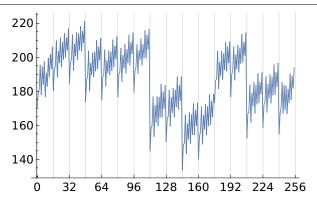

| 3.40 | NOP with different Hamming distance between current and next          |    |

|      | address                                                               | 61 |

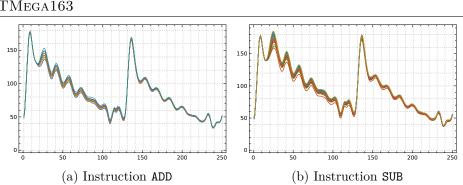

| 3.41 | Power consumption of two arithmetic instructions.                     | 62 |

|      | Power consumption of two data transfer instructions                   | 62 |

| 3.43 | IJMP with different Hamming distance between current and next         |    |

|      | address                                                               | 63 |

### Introduction

Often, when designing cryptographic algorithm, developer is concerned mainly with it's mathematical properties: if not mathematically unbreakable, algorithm needs to be practically unbreakable. This is the first Kerckhoffs's principle[6], set by Auguste Kerckhoffs among others in nineteenth century that is still relevant. On the flip side, algorithm needs implementation, and programs do not exist in vacuum.

Secure implementation is as important as secure algorithm. Without well thought implementation security of a whole system might be compromised. Device might produce some side-effects, like different time of computation given different data, noise produced by hardware device itself, or power consumption that is dependent on processed data. Side-channel attacks based on such properties of a device may pose threat to security of a system. Power side channel analysis attacks target power consumption of a device.

Main objective of this work is to analyze power consumption of a microcontroller, how it's internal architecture can affect power traces during execution of various instructions. To perform this analysis the preparation stages should be taken, such as picking up a microcontroller to test, creating measurement setup and design a number of tests.

#### Work structure

Chapter 1 introduces reader to the idea behind power analysis attacks and describe main methods of it's implementation.

In chapter 2 I describe test prerequisites for practical part of the work to be done: what measurement setup I had, which tools I used to acquire and process power traces, what problems I encountered and how I dealt with them.

Chapter 3 present the practical output of my work. Here I describe internal architecture of ATMega163 — microcontroller used for analysis — and how it affects power consumption. I continue with describing instruction set and

#### INTRODUCTION

types of instructions. I analyze power consumption of individual instructions with dependency on the type of instruction, operands and data they process.

# CHAPTER **]**

# Power side channel analysis attacks

This chapter will provide introduction to power side channel analysis attacks, and what methods of power analysis exist. I will briefly mention historical development and significant concepts in this topic and how it influenced my work.

#### **1.1** Power analysis attacks

First to introduce cryptographic community to power analysis attacks were Paul Kocher, Joshua Jaffe and Benjamin Jun, in their report "Differential power analysis" in the year 1998[7]. Despite the name, they've brought up two methods of power analysis: Simple Power Analysis and Differential Power Analysis. Simple power analysis targets implementation details, such as conditional pieces of code, which are or are not executed in dependency on data that are being processed and structures such as loops or any repetitive pieces of computation. Differential power analysis exploits statistical properties of data and respective power consumption trace.

#### 1.1.1 Simple Power Analysis

To successfully implement Simple power analysis attack only a few power traces are sufficient, even one power trace may expose all information that attacker needs. Power consumption is analyzed along time axis, because important part of it is algorithm itself. Great example of Simple power analysis attack is provided by Marc Joye[5]. In this example Simple Power Analysis attack was performed against basic square-and-multiply implementation, see algorithm 1.

The problematic part here is that at the moment of checking conditional statement, when condition is not met (bit i of d is 0) execution of this iteration

Algorithm 1 Basic square-and-multiply algorithm.

$\begin{array}{l} k \leftarrow bitsize(d) \\ y \leftarrow x \\ \textbf{for } i = k - 2 \ \textbf{downto} \ 0 \ \textbf{do} \\ y \leftarrow y^2(\text{mod}n) \\ \text{if bit } i \ \text{of } d \ \text{is } 1 \ \textbf{then } y \leftarrow y * x(\text{mod}n) \\ \textbf{end if} \\ \textbf{end for} \end{array}$

of a loop is shorter in comparison to iterations where condition is met. Which is afterwards can be seen at the power trace of a device, that used straightforward implementation of this algorithm, as seen on figure 1.1.

Figure 1.1: SPA trace of basic square-and-multiply algorithm [5].

Another typical example is observation of repeated structures, for example, rounds in block ciphers. Although just from a power consumption of a block or groups of blocks, Simple Power Analysis is used as supplement to Differential power analysis to "remove irrelevant regions" [8].

Rita Mayer-Sommer in [9] pointed out, that SPA can be applied to individual instructions, not only to conditional branching instructions. She objected the statement from [7], that SPA is easily prevented "by avoiding conditional branching and jumps" and presented results of power consumption measurement of MOV instruction in PIC16C84 chip. Those measurements show that by a mere SPA attacker can figure out Hamming weight of data processed, which creates a threat no one before anticipated.

Figure 1.2: SPA trace showing an entire DES operation [7].

#### 1.1.2 Differential power Analysis

In contrast to Simple Power Analysis, Differential Power Analysis requires a large amount of power traces to perform it, therefore it is usually necessary to physically possess one attacked device[12]. On the upside, attacker doesn't need to know implementation details about cryptographic device, all that he needs is "being merely informed about general code structure"[9].

Generally, to perform Differential power analysis attack few steps need to be taken according to Mangard[12]:

- 1. Choose intermediate value of executed algorithm: it needs to be a result of a function f(d, k), where d is a non-constant data value (either plain text or cipher text) and k is constant key;

- 2. Measure power consumption: attacker needs to obtain power traces of ciphering/deciphering data, known to the attacker. It is important for resulting power traces matrix to be aligned, i.e. at every point in time (column in matrix) needs to be performed same operation;

- 3. Calculate hypothesis: attacker has to have some model (more on models later in text), by which he can create hypothesis about intermediate value in dependency on key;

- 4. Mapping hypothesis to power traces and compare them.

There are two basic models for calculating hypothesis, based on Hamming Weight<sup>1</sup> and on Hamming Distance between two intermediate values<sup>2</sup>.

Technique, that is widely used to calculate liner correlation between power traces and hypothesis is sample Pearson correlation coefficient[3]. Formula for it reads as follows

$$r = \frac{n \sum x_i y_i - (\sum x_i \sum y_i)}{\sqrt{[n \sum x_i^2 - (\sum x_i)^2][n \sum y_i^2 - (\sum y_i)^2]}}$$

where n is the sample size,  $x_i$  and  $y_i$  are samples at i position in the set.

#### 1.1.3 High-Order Differential Power Analysis

Number of countermeasures to DPA attacks exist, such as masking, insertion of random operations, that do not affect the computation, shuffling and so on, discussed at great detail by Mangard[12]. But for every countermeasure there is better yet attack scheme.

Higher-order (second or more) DPA attacks deal with not one, but with a number of points in measurement. This attack requires even more power traces for it to success, but is able to deal with various standard countermeasures against first-order DPA attack[4].

#### 1.2 Summary

Thematically, my work is close to that of Rita Mayer-Sommer I mentioned above while describing Simple Power Analysis. Before discovering her work, I came up with idea of testing instructions against known values in order to see, how instructions behave with regard of their power consumption.

As she stated in [9], SPA attack can be performed against individual instructions. With that in mind, I would like to say that objective of this work is to perform Differential Power Analysis, so future works could rely on it to perform Simple Power Analysis. Difference between her work and mine is that here I provide more comprehensive exploration of almost every instruction, with more detailed overview of timings<sup>3</sup>.

<sup>&</sup>lt;sup>1</sup>Hamming weight of a value is number of ones in it's binary representation.

$<sup>^2\</sup>mathrm{Hamming}$  distance between two values is Hamming weigh of a result of operation "exclusive or" between the two.

<sup>&</sup>lt;sup>3</sup>Not to mention that we analyze different microcontrollers

# CHAPTER 2

# Test design and measurement setup