### CZECH TECHNICAL UNIVERSITY IN PRAGUE FACULTY OF INFORMATION TECHNOLOGY

### ASSIGNMENT OF BACHELOR'S THESIS

| Title:           | Side channel analysis of cryptographic algorithms implementations |

|------------------|-------------------------------------------------------------------|

| Student:         | Bc. Lukáš Mazur                                                   |

| Supervisor:      | DrIng. Martin Novotný                                             |

| Study Programme: | Informatics                                                       |

| Study Branch:    | Computer engineering                                              |

| Department:      | Department of Digital Design                                      |

| Validity:        | Until the end of summer semester 2016/17                          |

### Instructions

1. Get familiar with methods of side-channel analysis of cryptographic algorithms implementations. Focus mainly on Differential Power Analysis (DPA).

2. Learn how to use DPA for implementations in SmartCards.

3. Consequently, explore viability of DPA to FPGA implementations of cryptographic algorithms.

4. Based on the consultation with a supervisor, select suitable variants of implementations.

5. Explore resistance of these variants against DPA.

### References

Will be provided by the supervisor.

L.S.

doc. Ing. Hana Kubátová, CSc. Head of Department prof. Ing. Pavel Tvrdík, CSc. Dean

Prague December 6, 2015

CZECH TECHNICAL UNIVERSITY IN PRAGUE FACULTY OF INFORMATION TECHNOLOGY DEPARTMENT OF DIGITAL DESIGN

Bachelor's thesis

# Side channel analysis of cryptographic algorithms implementations

Bc. Lukáš Mazur

Supervisor: Dr.-Ing. Martin Novotný

8th January 2017

## Acknowledgements

At this point I want to thank to my supervisor Dr.-Ing. Martin Novotný for all his comments and remarks during writing the thesis, and for the help with measurement. I want to thank to Ing. Jiří Buček for the help with measurement. I also want to thank to Priv.-Doz. Amir Moradi for consultations on proper oscilloscope setup. I want to thank to Jan Severyn for valuable collaboration while working on this thesis.

### Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular that the Czech Technical University in Prague has the right to conclude a license agreement on the utilization of this thesis as school work under the provisions of Article 60(1) of the Act.

In Prague on 8th January 2017

Czech Technical University in Prague Faculty of Information Technology © 2017 Lukáš Mazur. All rights reserved.

This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

### Citation of this thesis

Mazur, Lukáš. Side channel analysis of cryptographic algorithms implementations. Bachelor's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2017.

## Abstrakt

V bakalářské práci byly prozkoumány možnosti rozdílové odběrové analýzy (DPA) na programovatelná hradlová pole (FPGA). V rámci práce byl modifikován program pro měření proudové spotřeby, vytvořeny skripty pro provádění DPA a vytvořeny různé implementace algoritmu AES na FPGA. Vyvinuté skripty a programy pro DPA byly ověřeny proti implementaci AES na čipové kartě. Poté, co tyto programy úspěšně prolomily implementaci na čipové kartě, přistoupili jsme k aplikaci DPA proti implementaci AES na desce s FPGA. DPA proti FPGA byla provedena v šesti různých konfiguracích. Tyto konfigurace se lišily v implementaci AES na FPGA, v konfiguraci desky, v nastavení osciloskopu a v metodě útoku. Byly nalezeny konfigurace, které byly úspěšně prolomeny. Bylo zjištěno, že nastavení osciloskopu a měřícího prostředí má významný dopad na proveditelnost DPA na FPGA. Implementace je méně důležitá pro úspěch útoku. Nejdůležitejší aspekt implementace je hodinová frekvence. Také bylo zjištěno, že použití různých zdrojů proudu a odebrání kondenzátorů na FPGA desce má významný dopad na proveditelnost DPA.

**Klíčová slova** Rozdílová odběrová analýza, útoky postranními kanály, Advanced Encryption Standard, FPGA, čipová karta, korelační analýza

## Abstract

We explored the possibilities of the Differential Power Analysis (DPA) on the Field Programmable Gate Array (FPGA). We have modified the application for measuring a power consumption, created scripts for performing DPA, and created different implementations of AES algorithm for FPGA. Developed scripts and applications for DPA were verified against AES implementation for smart cards. Once those applications successfully broke the implementation for smart cards, we continued with the application of DPA against AES implementation for an FPGA board. DPA against FPGA was performed in six different configurations. Those configurations differed in AES implementation for FPGA, in board configuration, in oscilloscope setup, and in method of the attack. We found variants that could be successfully broken. We found out that an oscilloscope and measuring environment setups has major impact on the feasibility of the DPA on FPGA. The implementation is less important for the success of the attack. The most important aspect of the implementation was the clock frequency. We have also found out that using different power sources and removing capacitors on the FPGA board have significant impact on the feasibility of the DPA.

**Keywords** Differential Power Analysis, Side Channel Attacks, Advanced Encryption Standard, FPGA, Smart Card, Correlation Analysis

## Contents

| In       | trod | uction 1                                        |

|----------|------|-------------------------------------------------|

| 1        | Bac  | kground 3                                       |

|          | 1.1  | Advanced Encryption Standard                    |

|          | 1.2  | Side Channel Attacks                            |

| <b>2</b> | Ana  | alysis 7                                        |

|          | 2.1  | Encryption Algorithm                            |

|          | 2.2  | Methods of the Attack                           |

|          | 2.3  | FPGA Board 10                                   |

| 3        | Imp  | blementation 13                                 |

|          | 3.1  | SC Power Measurement                            |

|          | 3.2  | Key Recovery                                    |

|          | 3.3  | AES for Smart Card                              |

|          | 3.4  | AES for FPGA                                    |

|          | 3.5  | AES_CLK                                         |

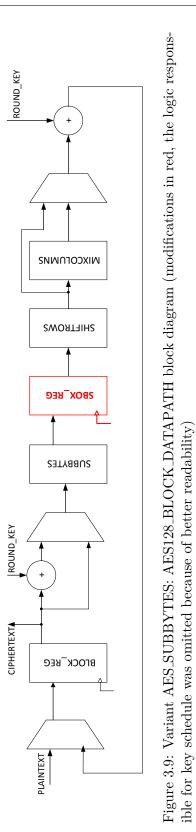

|          | 3.6  | AES_SUBBYTES                                    |

|          | 3.7  | AES_BYTES 32                                    |

|          | 3.8  | AES_KEY                                         |

| 4        | Tes  | ting 37                                         |

|          | 4.1  | Testing Tools                                   |

|          | 4.2  | Verification                                    |

|          | 4.3  | Validation                                      |

| <b>5</b> | Mo   | unting the DPA Attack on AES Implementations 41 |

|          | 5.1  | Smart Card                                      |

|          | 5.2  | FPGA                                            |

|          | 5.3  | Summary                                         |

| 6 Future Work               | 61 |

|-----------------------------|----|

| Conclusion                  | 63 |

| Bibliography                | 65 |

| A Acronyms                  | 69 |

| B Contents of Enclosed DVDs | 71 |

## **List of Figures**

| 1.1  | Possible methods of DPA against AES128                                   | 6  |

|------|--------------------------------------------------------------------------|----|

| 2.1  | Different implementation variants of AES128                              | 8  |

| 2.2  | Digilent Basys 2                                                         | 11 |

| 2.3  | Spartan 3E Starter Board                                                 | 12 |

| 3.1  | AES128 block diagram                                                     | 20 |

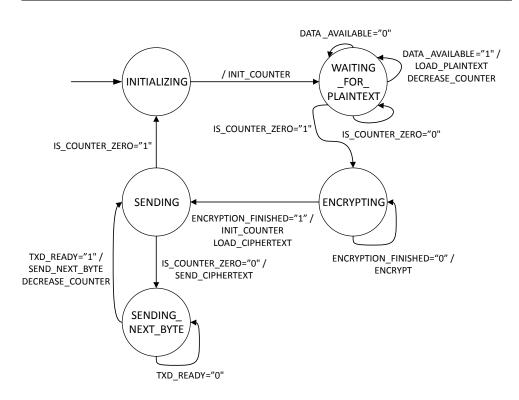

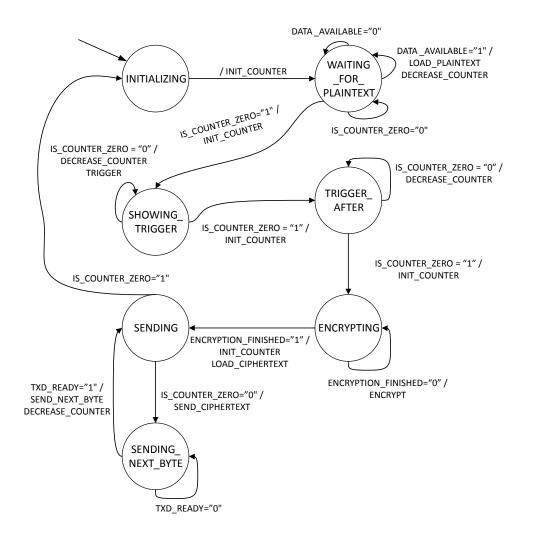

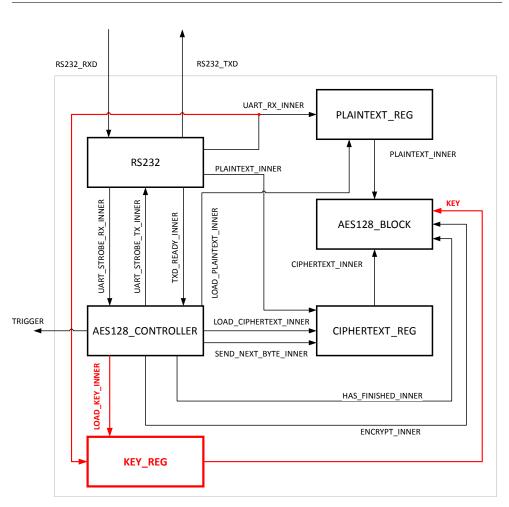

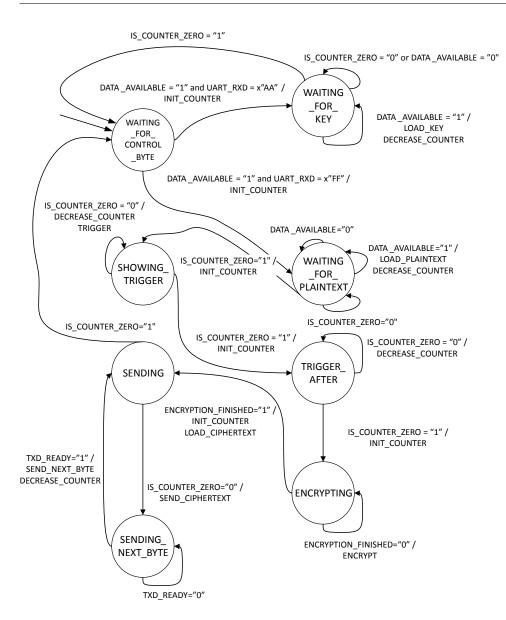

| 3.2  | AES128_CONTROLLER state diagram                                          | 21 |

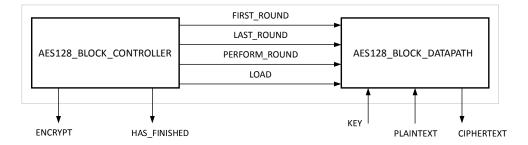

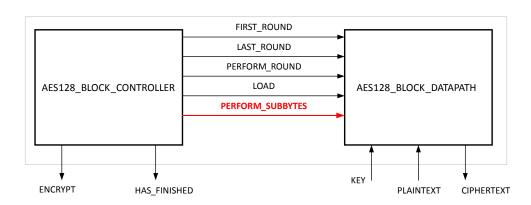

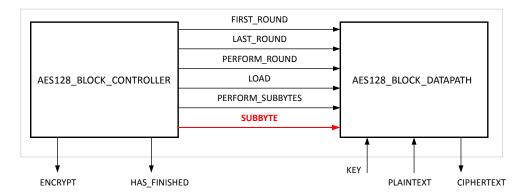

| 3.3  | AES128_BLOCK block diagram                                               | 23 |

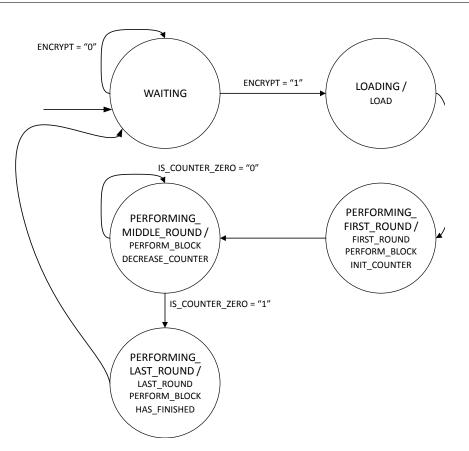

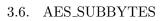

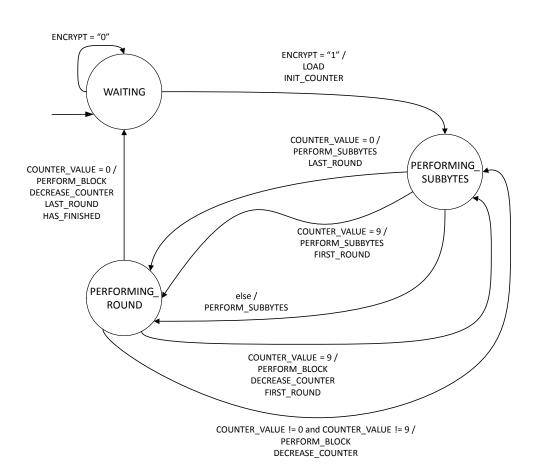

| 3.4  | AES128_BLOCK_CONTROLLER state diagram                                    | 24 |

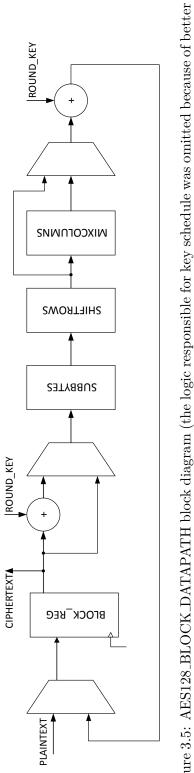

| 3.5  | AES128_BLOCK_DATAPATH block diagram                                      | 27 |

| 3.6  | Variant AES_CLK: AES128_CONTROLLER state diagram                         | 29 |

| 3.7  | Variant AES_CLK: AES128 block diagram change                             | 29 |

| 3.8  | Variant AES_SUBBYTES: AES128_BLOCK block diagram                         | 30 |

| 3.9  | Variant AES_SUBBYTES: AES128_BLOCK_DATAPATH block dia-                   |    |

|      | gram                                                                     | 31 |

| 3.10 | Variant AES_SUBBYTES: AES128_BLOCK_CONTROLLER state                      |    |

|      | diagram                                                                  | 33 |

|      | Variant AES_BYTES: AES128_BLOCK block diagram                            | 33 |

|      | Variant AES_KEY: AES128 block diagram                                    | 34 |

| 3.13 | Variant AES_KEY: AES128_CONTROLLER state diagram                         | 35 |

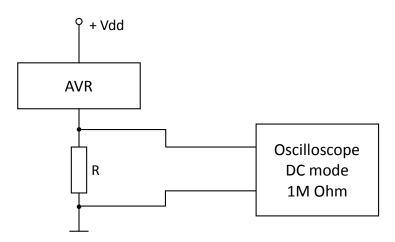

| 5.1  | Measurement setup for smart card                                         | 42 |

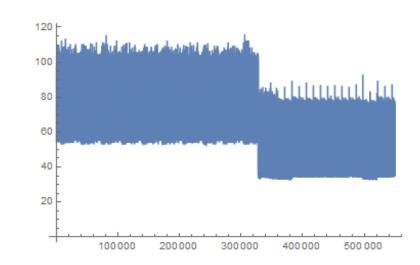

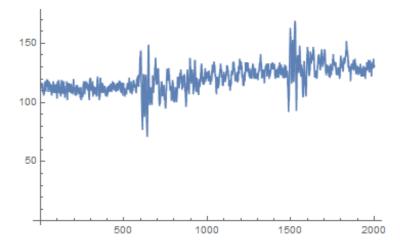

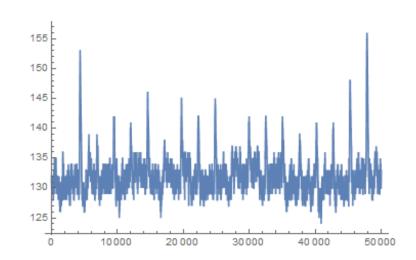

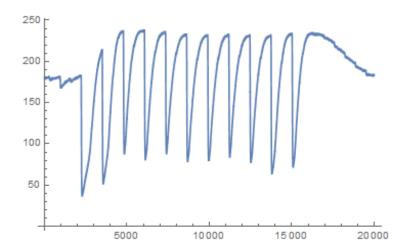

| 5.2  | Power trace. Configuration section 5.1 (smart card)                      | 43 |

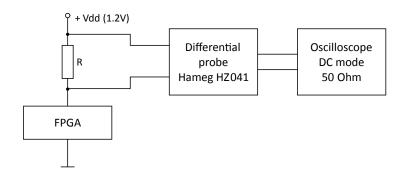

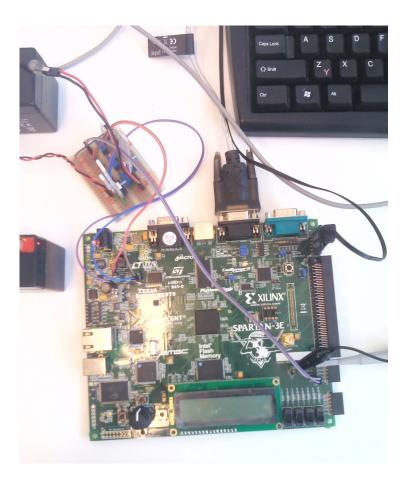

| 5.3  | Measurement setup for FPGA with differential probe                       | 44 |

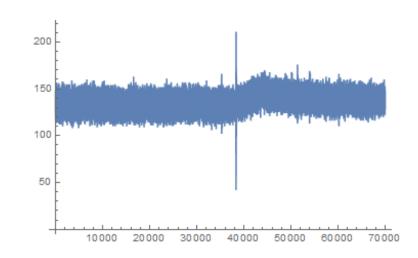

| 5.4  | Power trace. Configuration: subsection 5.2.1 (AES_CLK, capacit-          |    |

|      | ors present, switched-mode power supply, differential probe)             | 45 |

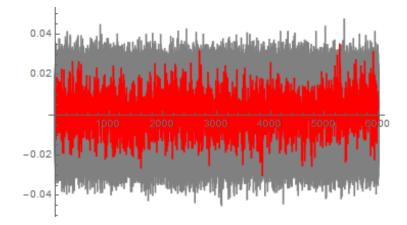

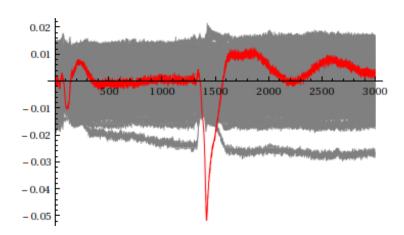

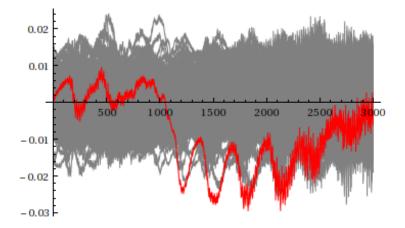

| 5.5  | Traces of correlation coefficients (correct key in red), samples 38,000– |    |

|      | 44,000. Configuration: subsection $5.2.1$ (AES_CLK, capacitors           |    |

|      | present, switched-mode power supply, differential probe)                 | 46 |

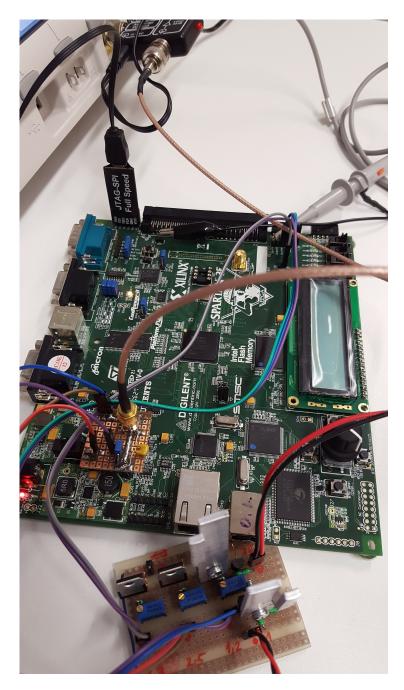

| 5.6  | FPGA board powered by accumulators, which are connected through stabilizers                                                                                                                                                                                                    | 47 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

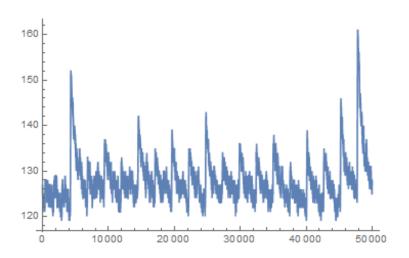

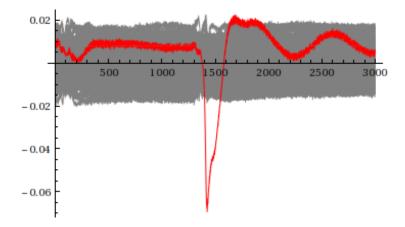

| 5.7  | Power trace. Configuration: subsection 5.2.2 (AES_SUBBYTES, capacitors present, accumulators, differential probe)                                                                                                                                                              | 47 |

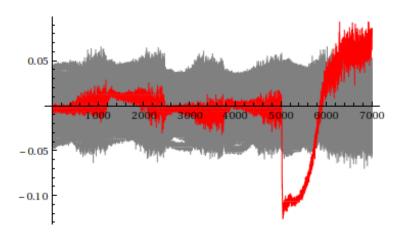

| 5.8  | Traces of correlation coefficients (correct key in red). Configura-<br>tion: subsection 5.2.2 (AES_SUBBYTES, capacitors present, ac-<br>cumulators, differential probe)                                                                                                        | 48 |

| 5.9  | Power trace, samples 50,000–100,000. Configuration: subsection 5.2.3 (AES_KEY, capacitors removed, accumulators, differential probe, 1 Ohm resistor)                                                                                                                           | 49 |

| 5.10 | Power trace, samples 50,000–100,000. Configuration: subsection 5.2.3 (AES_KEY, capacitors removed, accumulators, differential probe, 10 Ohm resistor)                                                                                                                          | 49 |

| 5.11 | FPGA board powered by accumulators, which are connected through stabilizers. The board is connected to the oscilloscope through                                                                                                                                                |    |

|      | preamplifier.                                                                                                                                                                                                                                                                  | 51 |

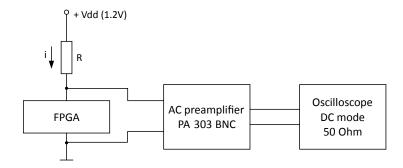

|      | Measurement setup for FPGA with AC preamplifier                                                                                                                                                                                                                                | 52 |

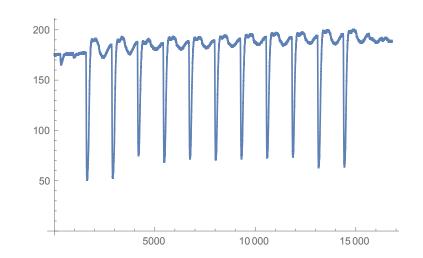

| 5.13 | Power trace. Configuration: subsection 5.2.4 (AES_CLK, capacit-<br>ors removed, accumulators, AC preamplifier)                                                                                                                                                                 | 53 |

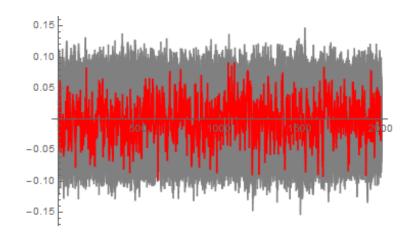

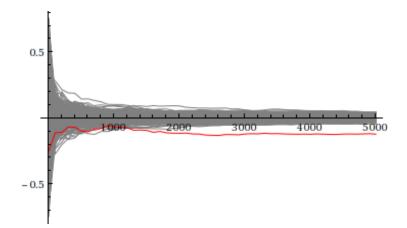

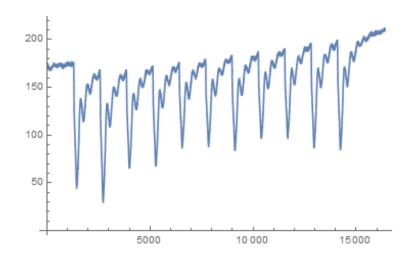

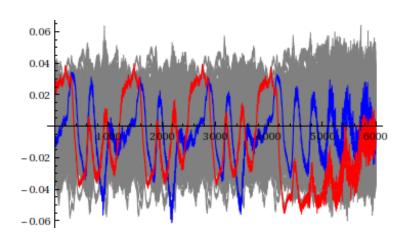

| 5.14 | Traces of correlation coefficients (correct key in red), samples 10,000–<br>17,000, 5,000 traces. Configuration: subsection 5.2.4 (AES_CLK,<br>capacitors removed, accumulators, AC preamplifier)                                                                              | 54 |

| 5.15 | Traces of correlation coefficients for different number of power traces (correct key in red), sample 15,045. Configuration: subsection 5.2.4 (AES_CLK, capacitors removed, accumulators, AC                                                                                    |    |

| 5.16 | preamplifier)                                                                                                                                                                                                                                                                  | 54 |

| 5.17 | ors removed, switched-mode power supply, AC preamplifier)<br>Traces of correlation coefficients (correct key in red), samples 13,000–<br>16,000, 30,000 traces, $1^{st}$ byte. Configuration: subsection 5.2.5<br>(AES_CLK, capacitors removed, switched-mode power supply, AC | 55 |

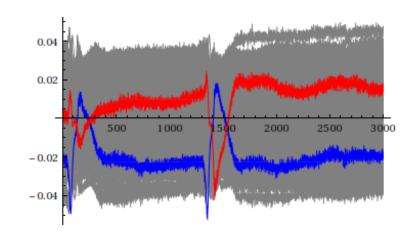

|      | preamplifier)                                                                                                                                                                                                                                                                  | 56 |

| 5.18 | Traces of correlation coefficients (correct key in red), samples 13,000 - 16,000, 30,000 traces, 7 <sup>th</sup> byte. Configuration: subsection 5.2.5 (AES_CLK, capacitors removed, switched-mode power supply, AC preamplifier)                                              | 56 |

| 5.19 | Traces of correlation coefficients (correct key in red, key hypothesis with lowest correlation coefficient in blue), samples 13,000–16,000, 5,000 traces. Configuration: subsection 5.2.5 (AES_CLK, capacit-                                                                   |    |

| F 90 | ors removed, switched-mode power supply, AC preamplifier)                                                                                                                                                                                                                      | 57 |

| ə.20 | Power trace. Configuration: subsection 5.2.6 (AES_CLK, capacit-<br>ors present, accumulators, AC preamplifier)                                                                                                                                                                 | 58 |

| 5.21 | Traces of correlation coefficients (correct key in red), samples 13,000– |    |

|------|--------------------------------------------------------------------------|----|

|      | 16,000, 30,000 traces. Configuration: subsection 5.2.6 (AES_CLK,         |    |

|      | capacitors present, accumulators, AC preamplifier)                       | 58 |

| 5.22 | Traces of correlation coefficients (correct key in red, key hypothesis   |    |

|      | with lowest correlation coefficient in blue), samples 10,000–16,000,     |    |

|      | 5,000 traces. Configuration: subsection 5.2.6 (AES_CLK, capacit-         |    |

|      | ors present, accumulators, AC preamplifier)                              | 59 |

|      |                                                                          |    |

## List of Tables

| Comparison of different implementation variants                        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview of intended attacks                                           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Overview of AES FPGA implementations                                   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Overview of clock cycles needed for encryption in each variant $\ .$ . | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Overview of performed tests                                            | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measurement on smart card                                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Summary of performed measurements                                      | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measurement AES_CLK, differential probe                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measurement AES_SUBYTES, accumulators, differential probe              | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measurement AES_SUBYTES, accumulators, differential probe              | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measurement AES_CLK, no capacitors, accumulators, AC preamp-           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| lifier                                                                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measurement AES_CLK, no capacitors, AC preamplifier                    | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measurement AES_CLK, accumulators, AC preamplifier                     | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DPA summary                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                        | Overview of intended attacksOverview of AES FPGA implementationsOverview of AES FPGA implementationsOverview of clock cycles needed for encryption in each variantOverview of performed testsOverview of performed testsMeasurement on smart cardSummary of performed measurementsMeasurement AES_CLK, differential probeMeasurement AES_SUBYTES, accumulators, differential probeMeasurement AES_SUBYTES, accumulators, differential probeMeasurement AES_CLK, no capacitors, accumulators, AC preamplifierMeasurement AES_CLK, no capacitors, AC preamplifierMeasurement AES_CLK, accumulators, AC preamplifier |

## Introduction

Cryptography is a major part of computer security and data security in general. Substantial effort is being put into developing more secure and faster cipher algorithms, and into breaking them. Many governments have their own standards and requirements for cryptographic algorithms usually based on mathematical findings and theories that make them secure. But even the most mathematically secure algorithms can be broken in a matter of hours or minutes by side channel attacks. Side channel attacks do not exploit weaknesses in the mathematical model behind the cryptographic algorithm, but the implementation of the algorithm is targeted instead. Even a very secure cipher algorithm implementation can be broken if implemented incorrectly.

The volume of digital data in the world is growing rapidly and the demand for its encryption is growing as well. Cryptography has its use not only in protecting government secrets but also in protecting people's lives. Cryptography makes it impossible<sup>1</sup> for an intruder to intercept a remote communication in mission-critical systems such as planes or automated urban metro subway systems. By researching possible attacks, the researches can find weak spots in encryption systems and find effective ways of securing them.

Traditionally, research was mostly done in the ciphers themselves, and not theirs implementations. This has changed since Paul Kocher et al. presented their article in 1999 [18]. They showed that it is possible to get the secret key from cryptographic device by looking at its power consumption. An intensive research in the field of Differential Power Analysis (DPA) has begun and it is sill ongoing. Different attacks and countermeasures against those attacks have been introduced.

The aim of this thesis is to get familiar with side channel attacks and especially with the DPA. The DPA will be applied to the smart card to properly learn the method of performing it. After that the viability and resistance of different implementations of cryptographic system in Field Programmable

<sup>&</sup>lt;sup>1</sup>At least we hope it is impossible

Gate Array (FPGA) will be explored.

The structure of this thesis is as follows: In the first chapter we offer a brief introduction into the topic. In the second chapter we analyse several variants of the implementation of the cryptographic system, we discuss the ways of implementation of the side channel attack, and we make a selection of suitable FPGA board with respect to the feasibility of the attack. In the third chapter we describe the design of different implementations of cryptographic systems for smart card and FPGA, the implementation of scripts used for the attack, and modification of the application for measurement. We performed both the verification and validation testing. The tests and their results are described in the fourth chapter. We present results of different attacks on different configurations of the cryptographic system in the fifth chapter. In the sixth chapter we propose a few topics that could be researched in the future. In last chapter we make conclusions from our findings.

CHAPTER **]**

## Background

This chapter briefly introduces the reader into the topic. After the consultation with thesis supervisor we have selected Advanced Encryption Standard (AES) as a cryptographic system that will be used in this thesis. The chapter begins by a discussion of the AES selection process and short description of the AES algorithm in section 1.1. The side channel attacks are explained in section 1.2.

### 1.1 Advanced Encryption Standard

The AES predecessor, Data Encryption Standard (DES), was often criticized because of its short key being only 56 bits long. DES was broken by brute-force attack for the first time in 1997 by a cluster of thousands personal computers [16]. It became apparent that a new encryption standard was needed. In the same year, National Institute of Standards and Technology (NIST) announced that DES successor would be called AES [24]. There was a call for submissions of new algorithms a few months later [25]. The algorithm was required to have a block size of 128 bits, and to support 128, 192 and 256 bit keys. The cipher Rijndael won the competition and has been standardized as Federal Information Processing Standards (FIPS) 197 [26] in 2001.

The AES processes the block in rounds. The number of rounds is 10, 12, or 14 for 128, 192, or 256 bit key respectively. The algorithm performs 4 transformations in each round:

- SubBytes—non-linear byte substitution according to a predefined table

- ShiftRows—exchange of positions of some bytes

- MixColumns—combination of multiple bytes, this transformation is skipped in the last round

- AddRoundKey—xoring of round key and cipher state

A different round key is used for each round. Round keys are derived from the original key by the mechanism called Key Schedule or Key Expansion. A detailed explanation of the cipher is provided in [28] or [17].

A dedicated hardware for breaking DES by a brute force attack, COPA-COBANA, can break the cipher in 9 days on average [20]. Later, a new device, RIVYERA, was created. It can break DES in 1 day on average [31]. Breaking AES with 128 bit key by a brute-force attack on a device with the same computational power as computational power of RIVYERA would take approximately  $13 * 10^{18}$  years. The brute force attack against AES is not feasible with state-of-the-art hardware.

Related key attacks against AES algorithm are known. The complexity of breaking AES192 and AES256 can be reduced to  $2^{176}$  and  $2^{99.5}$  respectively [12]. The 9 round version of AES256 can be broken in time  $2^{39}$ , and 10 round version in time  $2^{45}$  [11].

### 1.2 Side Channel Attacks

According to [28], the cryptanalysis can be divided into 3 types:

- Classical cryptanalysis—it involves attacks that exploit the internal structure of the cipher or brute force attacks. It tries to find some weak spot in mathematical model behind the cipher, in its properties, or in its design.

- Social engineering attacks—they usually involve humans, and the aim of those techniques is to get the secret key directly from humans. Members of this group are techniques such as bribing, blackmailing, phishing, or tricking.

- Implementation attacks—side channel attacks can be used to reveal the key from information leaks caused by the implementation. In this thesis we focus on one type of such attack.

Attacks which belong to implementation attacks include power analysis, magnetic field analysis, timing analysis, or temperature analysis.

In this thesis we focus on side channel attacks, namely the method called Differential Power Analysis (DPA). As has been said in [30] "The efficiency of DPA attacks is much greater than the efficiency of differential or linear cryptanalysis". Below we bring brief introduction into this method.

### **1.2.1** Differential Power Analysis

The detailed explanation of DPA can be seen in [21] or [19]. We present a brief description here. The power consumption depends on the data being processed

[15]. The key can be obtained by analysis of the power traces captured during the encryption.

During the attack we are using the device and capturing the power traces. We are sending different plaintexts and storing the traces of the power consumption.

The key recovery process starts by creating a key hypothesis. We estimate the consumption for different values of each byte of the key (0-255). Those estimates are then correlated with obtained traces and the key hypothesis with highest correlation coefficient is considered to be a correct key.

Different models can be used during the creation of the key hypothesis. There are two orthogonal parts of the model which can be combined, the consumption model, and the round (just in case of block ciphers). The combination produces four different possible attack variants.

#### Consumption model

During the creation of a key hypothesis we try to estimate changes in the power consumption. Two models are commonly used: Hamming weight and Hamming distance.

- Hamming weight By Hamming weight we can measure a current state of the system (register). It gives us the number of ones in a register. Hamming weight is a static model in its nature. It measures only the current state and not the changes that preceded the current state.

- Hamming distance Hamming distance gives the difference between two values. If those two values represent different time points, the distance can actually measure the change in time of one value. Hamming distance is useful in cases when a small change in register (for instance the change of just one bit) can cause a chain of changes in the following combinational logic. Each of these changes has an impact on the overall consumption. By using distance we can more closely approximate the changes and their power consumption in the model.

### Round (in a block cipher)

Block ciphers are typically composed of multiple rounds. There is usually a sequence of different types of operations in each round. Typically those types of operations include permutation, substitution, diffusion, and key addition. When applying DPA on a block cipher, we focus on the inner state of cipher in suitable moment either in first round or last round. If we are attacking the first round, we estimate the cipher state according to the plaintext and we guess first round key. If we are attacking the last round we estimate the cipher state according to the cipher s

#### 1. BACKGROUND

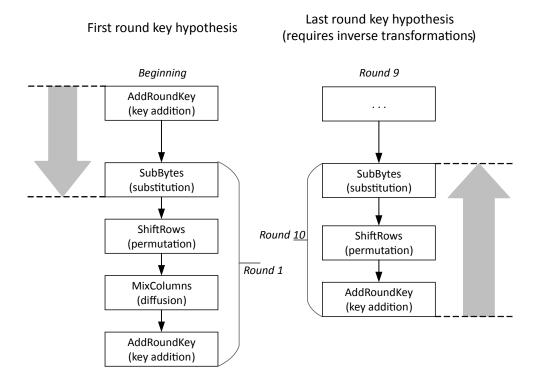

Substitution, which is a non-linear operation, is required to be present between the inner state and plaintext/ciphertext. The addition of round key needs to be performed before the non-linear operation, and between the inner state and the plaintext/the ciphertext. Permutation and other linear operations can be present between the key addition and substitution. The diagram of both methods (for AES) is shown in Figure 1.1.

Figure 1.1: Possible methods of DPA against AES128

Combination of different consumption models and rounds leads to 4 possible attacks:

- Hamming weight and first round

- Hamming weight and last round

- Hamming distance and first round

- Hamming distance and last round

## CHAPTER 2

### Analysis

This chapter contains the analysis of the structure of the implementation in section 2.1. Then it discusses different methods of the attack and summarizes the methods which will be used (see section 2.2). The chapter ends by section 2.3 which contains the analysis and selection of the FPGA board used for the implementation.

### 2.1 Encryption Algorithm

The DPA can be used against various encryption algorithms because it does not target the underlying mathematical model of the cipher but it targets its implementation instead. With regard to the previous statement we were free to choose whatever cipher we wanted. As has been state above, after consultation with thesis supervisor, we decided to use the AES encryption algorithm with 128 bit key, as it is widely used and secure algorithm. Many resources on AES are available. Because of that it was fairly easy to get familiar with inner function of AES.

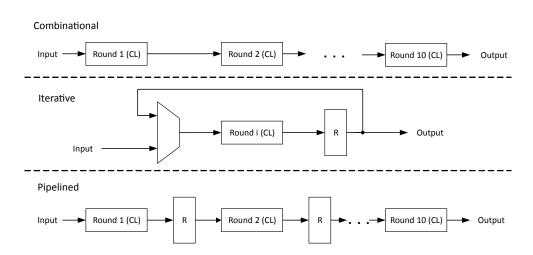

Different approaches to the structure of the implementation exist. We were considering three options. Expected impact of these options on the feasibility of DPA is described below. The scheme of all three variants can be seen in Figure 2.1. Detailed description of different designs is in [29]. Below we introduce three design approaches we considered for designing AES. Possible options are summarized in Table 2.1.

- **Combinational logic** All the rounds would be performed in one clock cycle in this design. DPA usually targets just one round, but this design would perform all the rounds and transformations in one clock cycle. We suppose that it could introduce a lot of noise to the captured traces.

- **Iterative design** Just one round of one block would be encrypted per clock cycle. Encryption of one block of plaintext takes 10 clock cycles plus

Figure 2.1: Different implementation variants of AES128 (CL—combinatorial logic, R—register)

overhead. It gives us the opportunity to measure the consumption more precisely without the noise caused by other rounds.

**Pipelined architecture** The encryption is separated into multi-stage pipeline. One round of multiple blocks<sup>2</sup> is being processed in one clock cycle. We expect this option to be more noisy than previous one because data from different blocks are influencing the consumption.

|               | Per clock cycle      |        |  |  |

|---------------|----------------------|--------|--|--|

| Structure     | Rounds of each block | Blocks |  |  |

| Combinational | 10                   | 1      |  |  |

| Iterative     | 1                    | 1      |  |  |

| Pipelined     | 1                    | 10     |  |  |

Table 2.1: Comparison of different implementation variants

We have decided to use the iterative implementation because we expect it to be easier to break than the others. Only one round and one encryption are performed at a time. Other versions process more data at one time and thus we expect them to be harder to break because there is more information involved in the encryption in one clock cycle. Moreover we have decided to use iterative variant because it consumes less chip area than other variants.<sup>3</sup>

<sup>&</sup>lt;sup>2</sup>Number of processed blocks depends on number of stages of pipeline

$<sup>^{3}</sup>$ Lately, we found out that using iterative variant was clever decision because iterative variant uses around 30% of chip area. Other variants would be too large to fit in the selected chip.

### 2.2 Methods of the Attack

We discuss the suitability of different methods of the attacks in this section. A summary of attacks which will be performed is placed at the end of the section.

### 2.2.1 Consumption Model

Two consumption models are commonly used (see section 1.2.1). We expect each model to be effective against different kind of cryptographic devices.

We assume the Hamming weight to be more effective for smart cards (which is actually a single chip computer). Our assumption is based on following hypothesis. Changes in power consumption occurs when the data on the internal bus inside the processor changes. At this time the bus needs to charge or discharge depending on the data. Thus the consumption is linked to the current state of the bus. Hamming weight should be relevant model in this case because we are guessing the content of data on the internal bus. The fact that Hamming weight gives better results than Hamming distance on smart cards was confirmed by Tillich and Herbst [33].

We will use both Hamming weight and Hamming distance for FPGA, but we expect that Hamming distance will be more efficient because the number of zeroes and ones in register is not relevant to the overall consumption. Changes of values are more relevant in the case of FPGA. By Hamming distance we can estimate the number of changes that happened in one clock cycle.

### 2.2.2 Round

Possible rounds that can be a subject of the attack are described in section 1.2.1. We decided to mount the attack both against the first round, and against the last round. The description of the creation of the key hypothesis is below.

- **First round** Creation of key hypothesis is simpler for the first round. It requires just 2 steps.

- 1. AddRoundKey

- 2. SubBytes

The key hypothesis is finished at this point.

Last round In the case of the last round the transformations are applied in the reverse order. The process of creating key hypothesis begins with the ciphertext (the final value of the state register) and goes backwards through the last round. This attack requires using the inverses of all the transformations (except the AddRoundKey).

- 1. AddRoundKey<sup>4</sup>

- 2. Inverse ShiftRows

- 3. Inverse SubBytes

The order of SubBytes and ShiftRows is not important. ShiftRows just changes position of a byte. I could perform the SubBytes before ShiftRows in a DPA if it would lead to easier implementation.

### 2.2.3 Intended Attacks

We have decided to use Hamming weight against the first round in case of smart card. This is a proven method and our primary aim was to use smart cards to get familiar with the DPA. We have made a decision to test both Hamming weight against the first round, and Hamming distance against the last round on FPGA. We want to start with Hamming weight and first round because this method will be already developed for the smart card. If unsuccessful, we will switch to the Hamming distance and last round because we expect better result for this DPA parameters. The summary of intended attacks is provided in Table 2.2.

|                  | First round      | Last round |

|------------------|------------------|------------|

| Hamming weight   | Smart card, FPGA |            |

| Hamming distance |                  | FPGA       |

Table 2.2: Overview of intended attacks

### 2.3 FPGA Board

This section describes the analysis of possible FPGA boards. At first we identified a set of requirements that the board has to satisfy:

- Availability of some communication channel (we prefer the serial line as a communication mean)

- Ability to measure the change of the current

- Availability in the university hardware lab

- Possibility to connect to our own power supply

$<sup>^4\</sup>mathrm{The}$  inverse transformation for AddRoundKey is not needed because it is same as non-inversed one

### 2.3.1 Suitable boards

We were considering two boards, Digilent Basys 2 and Digilent Spartan 3E Starter Board. We found out that the Spartan 3E Starter Board satisfies all the feature requirements. There was no need to evaluate other boards because it was a very good match.

### Digilent Basys 2

Figure 2.2: Digilent Basys 2, source: Digilent Inc.<sup>5</sup>

This is an entry level board by Digilent. It has a Spartan 3E-100 core and a wide range of peripherals such as VGA port or PS/2 connector. Unfortunately it is missing the serial port. Moreover the FPGA core is not large enough for the design. We verified this fact later during the development. If we targeted the core in Basys 2 in the development environment, the synthesis failed because the core was not big enough. But, we didn't know this fact at the time when we were selecting the board. The technical specification can be found in the reference manual [8].

#### Spartan 3E Starter Board

This is a Spartan 3E development board by Digilent. It features the Spartan 3E-500 core. It has 5 times more logic gates in comparison to the core placed on Basys 2. According to the data sheet [6] it has all the required features.

$<sup>^5</sup>$  Available online at https://reference.digilentinc.com/\_media/reference/programmable-logic/basys-2/basys2-0.png [cit. 2016-11-21]

$<sup>^{6}</sup>$  Available online at http://cdn6.bigcommerce.com/s-7gavg/products/110/images/3604/S3E\_top\_600\_14188.1449786819.1280.1280.png [cit. 2016-11-21]

Figure 2.3: Spartan 3E Starter Board, source: Digilent Inc.<sup>6</sup>

We identified a spot on the board suitable for placing the oscilloscope probe. It is the jumper JP7 located on the 1.2V power line between voltage regulator and the core. We have also identified spots for connecting our own power supply bypassing the original one. We could use the JP7 jumper (the same as for measurement) for connecting 1.2V source and JP6 jumper for connecting the 2.5V supply (see Schematic Sheet 5 and Schematic Sheet 9 in User Guide [6]). The 3.3V source could be connected to any peripheral VCC pin and GND pin.

## CHAPTER **3**

### Implementation

This chapter describes all the designs and other applications that we made or modified as a part of this thesis.

We have modified the existing application SC Power Measurement which is the application used for communication with the oscilloscope and automatic measurement. It was originally created by Ing. Jiri Bucek and Ing. Petr Vyleta for teaching DPA in the course MI-BHW [4] that is taught at Faculty of Information Technology (FIT) of Czech Technical University (CTU) (section 3.1).

We have created following applications and designs:

- The application used for the key recovery. It is used for computing the correct key and obtaining correlation matrices (section 3.2).

- The AES algorithm. We have developed 6 different AES128 implementations. These implementations differ in programming language they are written in and in their inner structure. The resistance against DPA of these implementations was tested. Following implementations were made:

- AES for smart card (section 3.3)

- AES for FPGA (section 3.4), with following modifications:

- \* Lower clock rate (section 3.5)

- \* Register placed after the subbytes operation (section 3.6)

- \* Each byte substitution is written into register in different clock cycle (section 3.7)

- \* The key is not harcoded but there is a register for key and it is transmitted over serial line (section 3.8)

### 3.1 SC Power Measurement

We used the SC Power Measurement from the course MI-BHW [4] for performing the measurements. It is written in C++ programming language. It communicates with Agilent oscilloscope via VISA drivers. It generates random plaintexts, sends them to the device under attack, and waits for the response. It downloads power traces that were captured during the encryption by the oscilloscope. It is also capable of sending the same data repeatedly which is useful for initial setting of measurement setup and environment.

It outputs 4 files containing data used for encryption and power traces.

- traces.bin Binary file containing power traces. Each sample has size 1 byte.

- **plaintext.txt** Text file that contains the plaintexts. Each line has one block of plaintext. The bytes of plaintext are written hexadecimally and separated by space.

- **ciphertext.txt** File containing the ciphertexts. It has the same format as *plaintext.txt*.

traceLength.txt Text file containing the number of samples per trace.

There is no information about the number of traces but it can be computed from the size of the file *traces.bin* and the number of samples per trace, or by counting the number of plaintexts/ciphertexts.

The application was originally developed to be used with smart cards. Together with Jan Severyn who is also performing a DPA in his bachelor thesis we added a support for FPGAs. Moreover there is a bug in VISA drivers causing the SC Power Measurement to crash randomly. We performed a few changes in the application to make it more resistant against the failure. This is a list of all changes that we made:

- We added support for serial communication. The parameters of the communication such as baud rate, number of parity bits or port are hard-coded in file *sources/main.cpp*. It uses 115,200 bauds, 1 start bit, 1 stop bit and no parity bits. It uses following Windows application programming interface (API) functions:

- CreateFile(...)

- WriteFile(...)

- ReadFile(...)

- In the original application, all the power traces were saved at the end of measurement. If the application crashed during measurement, no traces were kept at all. We changed the way of storing traces. Each trace is saved after each single measurement and not at the end. This preserves the obtained traces even in case of crash.

- The random generator that generates the plaintexts was originally seeded by zero. We changed the seed to the current timestamp. This change allowed us to see different plaintexts in each run of the application.

- We added various logs to the standard output. This is useful for tracking the progress during measurement.

- We added the possibility to prepend each plaintext by value 0xFF. This value at the beginning is required by the implementation with the register for key which can be found in section 3.8. The SC Power Measurement exists in two versions. One version prepends the byte at the beginning and the other does not.

### 3.2 Key Recovery

We have created a script for obtaining the correct key in Wolfram Mathematica. It uses files output from SC Power Measurement. Loading traces was optimized to use as low memory as possible. The loading procedure was taken from the webpage of the course MI-BHW [4]. But even with this optimization it run out of memory on machine with 8GB of RAM if I attempted to perform the analysis with 100,000 traces and thousands of samples per trace. As it can handle 1,000–2,000 samples per trace for 100,000 traces at most, the visual inspection of captured data is necessary. Then we can use a subset of samples that is located around the clock cycle which the operation was performed in. There are ways of optimizing the computation (see section 6).

We have created two versions of the key recovery script. They differ in the round that is being attacked and in the consumption model that is used. They use methods proposed in subsection 2.2.3. It works on a byte basis and the computation needs to be repeated for each byte of the key.

The script at first creates a key hypothesis. Key hypothesis is a matrix with dimensions (number of traces, 256). Number 256 represents all possible values that can be held by one byte of key<sup>7</sup>. First version attacks the first round and uses Hamming weight. Pseudocode of first version can be seen in Listing 3.1. Second version attacks the last round and uses Hamming distance. Pseudocode of second version can be seen in Listing 3.2.

The script then loads traces into the matrix with dimensions (number of traces, number of samples). Those two matrices are correlated producing a resulting matrix with dimensions (number of samples, 256). The plot of correct key hypothesis correlation coefficient is different from others. Thus, visual inspection is necessary to find the key. The number of column subtracted by one (indexes in Mathematica start from 1) is the value of correct key. The number of row with highest value corresponds to the sample which the

<sup>&</sup>lt;sup>7</sup>Provided one byte has 8 bits

Listing 3.1: First round Hamming weight key hypothesis pseducode

```

Listing 3.2: Last round Hamming distance key hypothesis pseducode

```

operation took place in. Depending on the settings of the oscilloscope there are usually more samples per one clock cycle of AES design.

### 3.3 AES for Smart Card

This is the first AES implementation that we made. It is written in C programming language and it is intended for smart card. The primary aim of this implementation was to get familiar with AES and DPA. The DPA against smart cards was heavily researched and there are many available resources on it.

The smart card we were using is controlled by Atmel AVR microcontroller unit (MCU). It is an 8 bit MCU, all operations in the implementation are byte oriented. It runs the AES in a for loop where each iteration is one round. All the transformations are performed per byte. The S-Box is implemented as a look-up table in program memory. Whole implementation is located in one source file with one exported function. Its signature can be seen in listing 3.3. For better readability the implementation is separated into multiple functions but those functions are not exported. The arguments of function in Listing 3.3 are:

|      | ¥                                            |

|------|----------------------------------------------|

| void | aes128_block_encrypt(                        |

|      | <b>const unsigned char</b> * plaintext,      |

|      | unsigned char * ciphertext,                  |

|      | $ {\bf const \ unsigned \ char \ * \ key}) $ |

plaintext The address of a buffer with plaintext. Its expected size is 16 bytes.

Listing 3.3: AES C implementation interface

- **ciphertext** The address of a buffer which is used for storing ciphertext. Its expected size is 16 bytes.

- **key** The address of a key. Because the function encrypts by 128 bit AES, the size of a key is 16 bytes.

The source file is a part of simple operating system for smart cards called BHW SOSSE. This system is used in the course MI-BHW [4] for teaching DPA against smart cards.<sup>8</sup> The communication with this system is via application protocol data unit (APDU).<sup>9</sup> The system supports 5 commands. Four of them invoke example encryption and decryption algorithms in C and assembler. The fifth actually does nothing. It is up to the students of MI-BHW course to add a genuine implementation of AES here. We added our AES implementation here and we used this system for performing a DPA on a smart card.

### 3.4 AES for FPGA

This is the first VHSIC Hardware Description Language (VHDL) implementation of AES that we made. The other VHDL implementations are modifications of this one. We subsequently modified this implementation to make it easier to break. Summary of all FPGA implementations is provided in Table 3.1.

The encryption in each of AES designs takes a different number of clock cycles. The operation was subsequently divided among more and more clock cycles. There is also a preparation before the encryption which takes one clock cycle. The summary of clock cycles needed for the encryption is shown in Table 3.2.

The top level entity is called AES128 and its interface is shown in listing 3.4. The following list presents a brief description of the AES128 ports.

**RS232\_RXD** A serial line receive signal connected to RXD pin (R7) of serial line connector on the board.

<sup>&</sup>lt;sup>8</sup>It was originally created by Matthias Bruestle at Ruhr-University Bochum

<sup>&</sup>lt;sup>9</sup>A protocol for communication between a smart card and a reader

#### 3. Implementation

| Variant      | Frequency<br>(kHz) | Trigger<br>before<br>start | S-Box<br>register | S-Box<br>per clock<br>cycle | Key<br>register |

|--------------|--------------------|----------------------------|-------------------|-----------------------------|-----------------|

| AES          | 50,000             | X                          | X                 | ×                           | X               |

| AES_CLK      | 1,562.5            | 1                          | X                 | ×                           | X               |

| AES_SUBBYTES | 1,562.5            | 1                          | 1                 | ×                           | X               |

| AES_BYTES    | 1,562.5            | 1                          | 1                 | 1                           | X               |

| AES_KEY      | 1,562.5            | 1                          | 1                 | 1                           | 1               |

Table 3.1: Overview of AES FPGA implementations

| Variant      | Initial preparation | One round | Total |

|--------------|---------------------|-----------|-------|

| AES          | 1                   | 1         | 11    |

| AES_CLK      | 1                   | 1         | 11    |

| AES_SUBBYTES | 1                   | 2         | 21    |

| AES_BYTES    | 1                   | 17        | 171   |

| AES_KEY      | 1                   | 17        | 171   |

Table 3.2: Overview of clock cycles needed for encryption in each variant (Total equals Initial preparation plus 10 times One round)

Listing 3.4: FPGA implementation top level entity interface

```

entity AES128 is

port (

RS232_RXD : in std_logic;

RST : in std_logic;

CLK : in std_logic;

RS232_TXD : out std_logic;

ENCRYPTING : out std_logic

);

end entity;

```

- **RST** A reset connected to the South Button (FPGA pin K17). During testing I have found out that the reset button needs to be pushed down after loading the bitstream to the FPGA chip for the design to correctly work. If the reset button is not pushed down the board returns incorrect results.

- **CLK** A clock signal connected to the oscillator with frequency 50 MHz (pin C9).

- **RS232\_TXD** A serial line transmit signal connected to TXD pin (M14) of serial line connector on the board.

**ENCRYPTING** A trigger signal connected to the pin IO9 (FPGA pin D7). In the initial design the trigger is in the state of logic one during the encryption. The logic driving the trigger was changed in subsequent designs. Trigger was put high for 16 cycles and then low for another 16 cycle before the actual encryption begun. Trigger signal helps to properly locate the encryption on the oscilloscope during measurement. We have found out that without trigger it is nearly impossible to locate the time frame of the encryption.

All the functionality is encapsulated by this entity. It basically listens to serial interface and waits till enough bytes, which is 16 in this case, were received. After that, it starts the encryption and waits until the encryption is done. Any data received over serial line during the encryption are discarded. Once the encryption is completed, the encrypted block is sent back. Then it waits for another block.

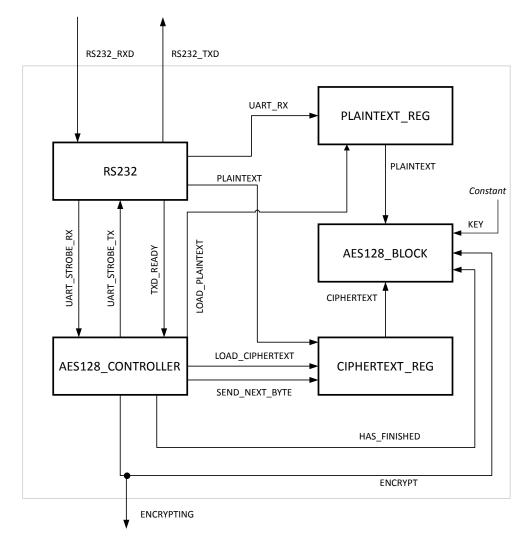

The block diagram of top level entity AES128 can be seen in Figure 3.1. It consists of 5 entities:

AES128\_CONTROLLER The finite state machine (FSM) that controls receiving, encrypting and sending data.

**AES128\_BLOCK** This entity performs the encryption.

**RS232** A module that sends and receives data over serial line.

CIPHERTEXT\_REG Register for storing ciphertext.

**PLAINTEXT\_REG** Register for storing plaintext.

The  $AES128\_BLOCK$  entity expects a 128 bit wide vector containing the key. The constant key 0x00~0x11~0x22~0x33~0x44~0x55~0x66~0x77~0x88~0x990xAA~0xBB~0xCC~0xDD~0xEE~0xFF is being put to this vector. It is hard-coded in the design and cannot be changed in runtime.

Below we bring description of all 5 blocks composing the top level entity AES128.

### 3.4.1 AES128\_CONTROLLER

The controller is realized as a Mealy FSM. It follows a typical structure with 3 processes. The first process is a combinatorial logic of transitions, second process is a combinatorial logic of outputs and third process is a sequential logic storing current state. The FSM state diagram can be seen in Figure 3.2

There is another auxiliary process. It serves as a counter of received bytes from the serial line before the actual encryption takes place, and transmitted bytes over serial line when the encryption is done. If the signal  $INIT\_COUNTER$  is put high the counter value is set to 16. The counter

Figure 3.1: AES128 block diagram (each name of signal inside the entity ends by JNNER, this string was removed from the diagram because of simplicity)

Figure 3.2: AES128\_CONTROLLER state diagram

decrements by one if signal *DECREASE\_COUNTER* is in the state of logic one. If the counter value is zero the signal *IS\_COUNTER\_ZERO* is pulled up.

The input of the controller are state signals from data paths. State transitions in the finite state machine are driven by those state signals. State signals are as follows:

- DATA\_AVAILABLE Active if new byte was received over serial line.

- **TXD\_READY** Active if RS232 entity (see 3.4.2) is able to sent another byte.

- **ENCRYPTION\_FINISHED** High if the encryption has finished.

The output of the controller are following control signals:

- **LOAD\_PLAINTEXT** Stores next byte of plaintext in *PLAINTEXT\_REG* (see 3.4.3).

- **LOAD\_CIPHERTEXT** Stores the output of *AES128\_BLOCK* (see 3.4.4) in *CIPHERTEXT\_REG* (see 3.4.3).

- **SEND\_CIPHERTEXT** Emits a signal to the RS232 converter (see 3.4.2) to transmit another byte.

**SEND\_NEXT\_BYTE** Performs a shift by one byte to the left in *CIPHER*-*TEXT\_REG* (see 3.4.3).

**ENCRYPT** Starts the encryption.

### 3.4.2 RS232

This is the entity used for communication over serial line. At first we used an implementation that we had created together with Jan Severyn as a part of an assignment in the course BI-PNO [1]. However due to issues with correct communication in our own implementation we switched to the implementation provided by the supervisor. It can be downloaded from webpage of course MI-BHW [4].

In comparison with original implementation we changed the baud rate from 9,600 bauds to 115,200 bauds. The entity is capable of sending and receiving data over serial line. The RS232 unit takes the data from  $TXD_DATA$  if  $TXD_STROBE$  is active and transmits them to the counter party. Once the transmission is done, and RS232 converter is able to transfer another byte, it pulls the signal  $TXD_READY$  high. The entity waits for data received by serial connection. When it receives complete byte it makes the signal  $RXD_STROBE$  active and the received data are present in vector  $RXD_DATA$ . The data are valid as long as  $RXD_STROBE$  is in the state of logic one.

### 3.4.3 CIPHERTEXT\_REG and PLAINTEXT\_REG

Shift registers for storing ciphertext or plaintext respectively. Both are simple and similar to each other. Because of their simplicity they were not realized as standalone entities but just as processes in the top level entity.

- **CIPHERTEXT\_REG** It stores the ciphertext from *AES128\_BLOCK* (see 3.4.4) if the signal *LOAD\_CIPHERTEXT\_INNER* is active. The left shift is performed if the signal *SEND\_NEXT\_BYTE\_INNER* is "1". The most left byte is discarded and the register is padded by one byte with value 0 on the right. The highest 8 bits of the output are connected to the input of *RS232* (see 3.4.2)

- **PLAINTEXT\_REG** The only purpose of this register is to store received bytes until enough bytes were received. The encryption starts once 16 bytes were received.

#### 3.4.4 AES128\_BLOCK

This is the entity that performs the encryption by AES128 cipher. It encrypts one block at a time. The interface of this entity is shown in Listing 3.5. If the signal ENCRYPT is put high the entity stores the PLAINTEXT and KEY into internal registers and the encryption begins. Once the encryption finishes

|                   | 0                                                    |

|-------------------|------------------------------------------------------|

| entity AES128_BLO | CK is                                                |

| $\mathbf{port}$ ( |                                                      |

| PLAINTEXT         | : in std_logic_vector (127 downto 0);                |

| KEY               | : in std_logic_vector (127 downto 0);                |

| ENCRYPT           | : in std_logic;                                      |

| RESET             | : in std_logic;                                      |

| CLK               | : in std_logic;                                      |

| CIPHERTEXT        | : <b>out</b> std_logic_vector (127 <b>downto</b> 0); |

| HAS_FINISHED      | : out std_logic                                      |

| );                |                                                      |

| end entity AES128 | BLOCK                                                |

Listing 3.5: AES128\_BLOCK interface

Figure 3.3: AES128\_BLOCK block diagram (each name of signal inside the entity ends by \_INNER, this string was removed from the diagram because of simplicity)

the signal  $HAS\_FINISHED$  is active. If it is active the data in the vector CIPHERTEXT are valid. It is active only for one clock cycle. Encryption of new block can start when the encryption of previous block is done.

We have decided to use the implementation with iterative design. Our original idea was to test different implementations but eventually we sticked just with this one and we have not tested the pipelined one for instance. We have found out during measurement that the determinant for success is mostly the oscilloscope setup and not the implementation itself.

The entity performs one round per one clock cycle. At the end of the round the data are stored to the register. Next round starts in next clock cycle. The encryption takes 11 clock cycles in total. Ten round accounts for 10 cycles and one more cycle is used at the beginning of the encryption to store original key and plaintext. This sums up to 11 clock cycles in total.

AES128\_BLOCK is separated to two entities: data paths and the controller (see Figure 3.3 for overall structure).

Figure 3.4: AES128\_BLOCK\_CONTROLLER state diagram

### AES128\_BLOCK\_CONTROLLER

The controller of the  $AES128\_BLOCK$  entity is realized as a Moore FSM. As in the case of the top level entity (see subsection 3.4.1), the controller consists of 3 processes. It waits till the signal ENCRYPT has a value of "1" and then it starts the encryption. It makes active signals  $FIRST\_ROUND$ and  $LAST\_ROUND$  according to the round that is being processed. It holds the  $PERFORM\_ROUND$  high for the duration of the encryption. When the encryption is over it sets the  $HAS\_FINISHED$  to "1". The ciphertext is valid as long as the signal  $HAS\_FINISHED$  has value "1". The controller also contains an internal counter for counting rounds. The diagram of the FSM can be seen in Figure 3.4.

### AES128\_BLOCK\_DATAPATH

This is the entity which the actual encryption takes place in. The block diagram is shown in Figure 3.5. The entity has a register which is used for storing the current cipher state. The current cipher state is written to the register when the  $PERFORM_ROUND$  signal is active. If the signal LOAD is active the plaintext is loaded to the register instead of the cipher state.

Round keys are not precomputed at the beginning but each successive round key is computed in applicable round. There are two registers used for the round key computation. The registers are  $ROUND\_KEY\_REG$  and  $RCON\_REG$ . The  $ROUND\_KEY\_REG$  register stores the current round key. If the signal  $PERFORM\_ROUND$  is high a new round key is stored. If the signal LOAD is active the original key is loaded to the register. The  $RCON\_REG$  is used for storing the round constant. It computes and stores new round constant if the signal  $PERFORM\_ROUND$  is active. If the signal LOAD is active the original key is loaded to the register.

All the registers do not write anything if both *PERFORM\_ROUND* and *LOAD* are not active. If the signal *FIRST\_ROUND* is active, the plaintext is xored with the key. If the signal *LAST\_ROUND* is high, the operation MixColumns is omitted.

The transformations in AES are defined in terms of operations in  $GF(2^8)$ . In the design we created functions used for computations in  $GF(2^8)$ . Those functions are located in file  $AES\_COMMON.vhd$ . The summary of the functions is below:

**Addition** Addition of two values in  $GF(2^8)$  is a bit xor of those values.

- Multiplication by 2 When multiplying by 2 the value is shifted to the left by one. If there is an overflow the result of shifting is xored with the value 0x1B.

- Multiplication by 3 The value is multiplied by 2 at first and then the original value is added to the result of the multiplication. It is based on the identity 3a = 2a + a.

The AES consists of 4 transformations as described in section 1.1. The list below describes realization of each of the blocks in the design.

- **AddRoundKey** This is simply realized as a *xor* in VHDL language. The vector with the key and the vector with the current cipher state are xored.

- **SubBytes** Subbytes are realized as a *case* statement. The substitution of values is performed on a byte basis. We have found out during synthesis that this operation takes the most FPGA chip area. We were experimenting with different realizations but all ended up with similar or worse results.

- **ShiftRows** We change the order of bits. It is implemented as a vector assignment with different indexes.

**MixColumns** This operation is based on matrix multiplication in  $GF(2^8)$ . For the multiplication we use functions described earlier in this section.

Figure 3.5: AES128\_BLOCK\_DATAPATH block diagram (the logic responsible for key schedule was omitted because of better readability)

Listing 3.6: Variant AES\_CLK: top level entity interface

```

entity AES128 is

port (

RS232_RXD : in std_logic;

RST : in std_logic;

CLK : in std_logic;

RS232_TXD : out std_logic;

TRIGGER : out std_logic

);

end entity;

```

### 3.5 AES\_CLK

We decided that a few modifications are needed. This section and following ones contain the description of the modifications. Each modification has all the features that the previous one plus the features described in particular section. Based on suggestions of thesis supervisor we decided to lower the clock rate and change the logic behind the trigger.

The previous implementation (section 3.4) was clocked on 50 MHz. In modification  $AES\_CLK$ , we divided the clock rate by a factor of 32 which resulted to 1,562.5 MHz. It was the lowest clock rate the universal asynchronous receiver/transmitter (UART) module was able to operate on (with 115,200 baud). We achieved the required behavior by adding a prescaler to the top level entity. Prescaler is a 5 bit counter that increases by one with every rising edge of the clock signal. The highest bit of prescaler is connected to the clock inputs of other entities.

The second change that we made regards the trigger. The trigger was originally active during whole encryption. Because of possible interferences that could lower the quality of signal we changed the trigger so as the trigger is set active for 16 cycles then there is a delay 16 cycles long and then the encryption begins. The trigger reuses the counter used for counting bytes. This change involved change of the *AES128\_CONTROLLER* (see subsection 3.4.1), and change of one signal in the top level entity. Changes are shown in Figure 3.6, and Figure 3.7 respectively. The output port *ENCRYPTING* of the top level entity was renamed to *TRIGGER* because it has more accurate meaning (see Listing 3.6).

### 3.6 AES\_SUBBYTES

We were not able to get power traces without the noise and break the implementation at this point. As was revealed later (see chapter 5), it was mostly

Figure 3.6: Variant AES\_CLK: AES128\_CONTROLLER state diagram

Figure 3.7: Variant AES\_CLK: AES128 block diagram change

#### 3. Implementation

Figure 3.8: Variant AES\_SUBBYTES: AES128\_BLOCK block diagram (modifications in red, each name of signal inside the entity ends by \_INNER, this string was removed from the diagram because of simplicity)

caused by improper measurement setup. However, we were not originally familiar with this fact, and so we made further modifications to the design to make the implementation easier to break.

The first idea was to separate the S-box from the rest of the computation. We added the register after the S-box operation. This modification divided one round into two clock cycles. The S-box result is written into S-box register in first clock cycle and the result of all other operations is written in the second clock cycle into cipher state register. A new signal *PERFORM\_SUBBYTES* was added between the data paths and the controller (see Figure 3.8). The result of S-box is written to the S-box register if signal *PERFORM\_SUBBYTES* is high (see Figure 3.9).

#### 3. Implementation

Beside adding a register we also modified the controller. The modification reflects the change in data path and emits a signal that writes the data to the S-box register. At this point we decided to rewrite the controller from Moore FSM to Mealy FSM. By rewriting we lowered the number of states and the FSM has became more maintainable. The FSM is shown in Figure 3.10. The controller contains signal *COUNTER\_VALUE* with type *natural* which is used as a counter of rounds. Value 9 is loaded to the *COUNTER\_VALUE* if signal *INIT\_COUNTER* is active. If signal *DECREASE\_COUNTER* is active value of the counter is decremented by 1.

In this variant, one round takes 2 clock cycles. The data are written to  $BLOCK\_REG$  register in first clock cycle, and to  $SBOX\_REG$  in second clock cycle.

# 3.7 AES\_BYTES

Writing to the S-box register was divided into multiple clock cycles in this variant. Each byte of the SubBytes operation is written into the S-box register in a different clock cycle. One round takes 16 + 1 = 17 clock cycles (Writing to *BLOCK\_REG* takes 1 clock cycles, subsequent writing of bytes to *SBOX\_REG* takes 16 clock cycles.). Out motivation was to divide the operation we are targeting into particular cycles (DPA reveals just one byte of a key at one moment).

A new control signal *SUBBYTE* was added between controller and data paths (see Figure 3.11). The signal has type *natural* with range from 0 to 15. It contains the number of byte that should be written to the S-box register.

The controller was modified to support this behavior. There is a new signal  $BYTE\_COUNTER\_VALUE$  which has the same type as a signal SUBBYTE. The value is loaded to the byte counter if signal  $INIT\_BYTE\_COUNTER$  is "1". If signal  $DECREASE\_BYTE\_COUNTER$  is active the value of byte counter is decreased by one. The signal  $BYTE\_COUNTER\_VALUE$  is connected to the signal SUBBYTE in  $AES128\_BLOCK$ . The state diagram is nearly the same as the one in previous variant except two modifications:

- Signal *INIT\_BYTE\_COUNTER* is active in states:

- PERFORMING\_ROUND