# **CZECH TECHNICAL UNIVERSITY IN PRAGUE**FACULTY OF TRANSPORTATION SCIENCES

# Jakub Řada IMPLENTATION OF THE MSC COMPRESSION ALGORITHM IN FIELD PROGRAMMABLE GATE ARRAY Master's thesis

#### CZECH TECHNICAL UNIVERSITY IN PRAGUE

Faculty of Transportation Sciences

Dean's office

Konviktská 20, 110 00 Prague 1, Czech Republic

**K614.....** Department of Applied Informatics in Transportation

# MASTER'S THESIS ASSIGNMENT

(PROJECT, WORK OF ART)

Student's name and surname (including degrees):

Bc. Jakub Řada

Code of study programme code and study field of the student:

N 3710 - IS - Intelligent Transport Systems

Theme title (in Czech): Implementace kompresního algoritmu MSC v

programovatelném hradlovém poli

Theme title (in English): Implementation of the MSC Compress Algorithm in Field

Programmable Gate Arrays

#### **Guides for elaboration**

During the elaboration of the master's thesis follow the outline below:

- Get acquainted with principles of logical circuits design in the field programmable gate array architecture

- Read up working principle of the Multistream Compression algorithm

- Design the block architecture of the compression module with regard to the implementation on a hardware platform

- Specify the requirements for selection of the field programmable gate array needed for the implementation

- Implement selected blocks

Graphical work range:

according to supervisor's recommendations

Accompanying report length: min. 55 pages including figures, graphs and tables

Bibliography:

· IEEE Standard VHDL Language Reference Manual, IEEE

Std 1076<sup>™</sup>-2008, New York, 2009

Kochanek J., et.all: Multistream Compression, Data Compression Conference, Snowbird, Utah, USA, 2008

Kilts S.: Advanced FPGA Design: Architecture,

Implementation, and Optimization, John Wiley & Sons,

2007, ISBN 978-0470054376

Master's thesis supervisor:

doc. Ing. Vít Fábera, Ph.D.

Ing. Tomáš Musil, Ph.D.

Date of master's thesis assignment:

May 29, 2015

(date of the first assignment of this work, that has be minimum of 10 months before the deadline of the theses submission based on the standard duration of the study)

Date of master's thesis submission:

November 30, 2016

a) date of first anticipated submission of the thesis based on the standard study duration and the recommended study time schedule

b) in case of postponing the submission of the thesis, next submission date results from the recommended time schedule

doc. Dr. Ing. Tomáš Brandejský head of the Department of Applied Informatics in Transportation prof. Dr. Ing. Miroslav Svítek, dr. h. c. dean of the faculty

I confirm assumption of master's thesis assignment.

Bc. Jakub Řada Student's name and signature

Prague ......June 6, 2016

#### ACKNOWLEDGEMENT

I would like to thank both supervisors of the thesis – doc. Ing. Vít Fábera Ph.D. and Ing. Tomáš Musil Ph.D. for their constructive advices and suggestions and especially their willingness to spend so much of their valuable time on the project. Furthermore, I would like to thank all the people that supported me during my studies in any way.

#### **DECLARATION**

I declare that I have accomplished my final thesis by myself and I have named all the sources I had used in accordance with the guideline about the ethical rules during preparation of university final theses.

I have no relevant reason against using this schoolwork in the sense of §60 of Act No. 121/2000 concerning the authorial law.

Prague 27/11/2016

signature

**Title**: Implementation of the MSC compression algorithm in Field Programmable Gate Array

Author: Bc. Jakub Řada

**Department**: Department of Applied Informatics in Transportation

**Supervisors**: doc. Ing. Vít Fábera, Ph.D., Ing. Tomáš Musil, Ph.D.

Supervisors' email addresses: fabera@fd.cvut.cz, musil@asix.cz

#### **ABSTRACT**

The thesis describes the first attempt of hardware implementation of Multistream Compression (MSC) algorithm. The algorithm is transformed to series of Finite State Machines with Data path using Register-Transfer methodology. Those state machines are then implemented in VHDL to selected FPGA platform. The algorithm utilizes a special tree data structure, called MSC tree. The thesis presents new way to store nodes of the tree using the Left Tree Representation. To encode data, the described implementation of the algorithm chooses between two methods – Elias Alpha and ZEBC.

#### **KEYWORDS:**

Multistream compression, Field Programmable Gate Array, MSC, FPGA, Compression, Parallel compression, Left Tree Representation

# **Contents**

| Contents                              | 5  |

|---------------------------------------|----|

| List of Figures                       | 8  |

| List of Tables                        | 9  |

| List of abbreviations                 | 10 |

| 1 Introduction                        | 11 |

| 1.1 Goals of the thesis               | 12 |

| 1.2 Organization of the thesis        | 12 |

| 1.3 Initial remarks                   | 12 |

| 2 MSC Algorithm                       | 14 |

| 2.1 The Steps of the Algorithm        | 14 |

| 2.1.1 Input Data Statistics           | 14 |

| 2.1.2 Creation of Binary Tree         | 15 |

| 2.1.3 Creation of Counter Streams     | 15 |

| 2.1.4 Statistical Analysis of Streams | 16 |

| 2.1.5 Compression                     | 16 |

| 2.2 The Coding Methods                | 16 |

| 2.2.1 Elias α                         | 17 |

| 2.2.2 ZEBC                            | 17 |

| 2.2.3 Huffman Coding                  | 18 |

| 2.3 MSC Properties                    | 18 |

| 3 RTL Design                          | 19 |

| 3.1 Method Overview                   | 19 |

| 3.2 RTL Design Steps                  | 21 |

| 4 FPGA Architecture                   | 22 |

| 5 Design Overview                     | 27 |

| 5.1 Choice of the Platform            | 29 |

| 5.2 Implementation                    | 32 |

| 5.3 Memory structure                  | 33 |

| 5.4 SDRAM Interface                   | 35 |

| 5.4.1 Signals                                             | 36 |

|-----------------------------------------------------------|----|

| 5.4.2 Pseudocode of SDRAM Controller                      | 37 |

| 5.4.3 Block Diagram                                       | 38 |

| 5.5 Memory Arbiter                                        | 39 |

| 5.6 UART                                                  | 40 |

| 6 Design details                                          | 41 |

| 6.1 Input of Data to FPGA Board                           | 41 |

| 6.2 Creation of Statistics                                | 42 |

| 6.3 Building the Tree                                     | 44 |

| 6.3.1 Representation of Binary Tree                       | 44 |

| 6.3.2 Process of Tree Building                            | 48 |

| 6.3.3 Memory Structure Used for Nodes                     | 50 |

| 6.4 Determination of Subtrees                             | 51 |

| 6.5 Creation of Streams                                   | 54 |

| 6.5.1 Specification of Counter Position in Thread Streams | 55 |

| 6.5.2 Counter Statistics                                  | 57 |

| 6.6 Calculation of ZEBC Table                             | 59 |

| 6.7 Parallel Analysis                                     | 59 |

| 6.7.1 Statistics processing                               | 60 |

| 6.7.2 Coding analysis                                     | 61 |

| 6.7.3 Advance to next node                                | 63 |

| 6.8 Buffer scheme                                         | 63 |

| 6.9 Compression                                           | 65 |

| 6.10 Output of Compressed Data                            | 67 |

| 7 Results                                                 | 68 |

| 8 Future Considerations                                   | 71 |

| 8.1 Sorting Algorithm                                     | 71 |

| 8.2 Decomposition of Tree to Layers                       | 71 |

| 8.3 Huffman Coding                                        | 72 |

| 0 Can alwaise                                             | 72 |

| 10 References | 74 |

|---------------|----|

| Appendix      | 78 |

# **List of Figures**

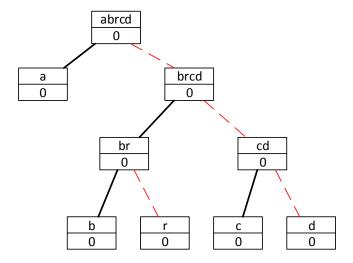

- Figure 1 Example of MSC tree in default setting

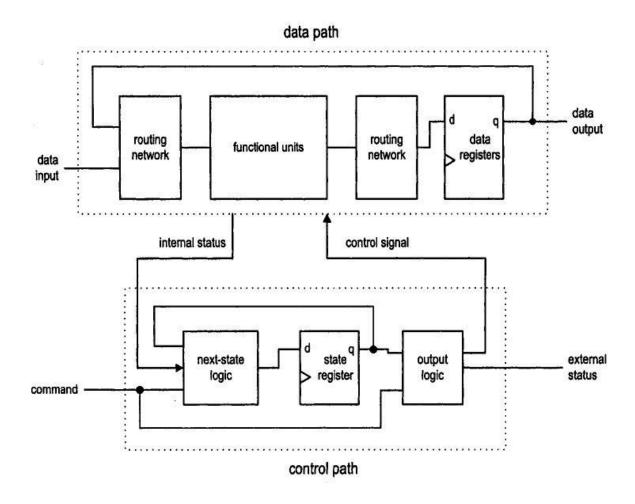

- Figure 2 Block diagram of a general system designed by RT methodology

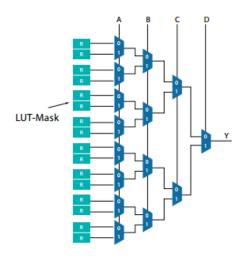

- Figure 3 Architecture of a LUT

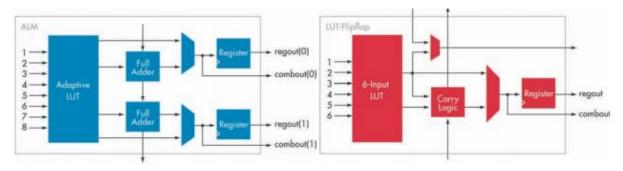

- Figure 4 Comparison of Xilinx's and Altera's architecture

- Figure 5 CLB Array and Interconnect channels of Xilinx

- Figure 6 General overview of Xilinx FPGA architecture

- Figure 7 The structure of MSC algorithm hardware implementation

- Figure 8 Xilinx ISE® WebPACK<sup>TM</sup> development environment

- Figure 9 Xilinx ISim simulation environment

- Figure 10 Architecture of the MSC design

- Figure 11 The SDRAM interface

- Figure 12 Memory arbiter

- Figure 13 Structure of data sent over UART

- Figure 14 Dataflow diagram of SDRAM interface during input data writing

- Figure 15 Dataflow on SDRAM interface during creation of statistics

- Figure 16 Example of MSC tree for "abracadabra"

- Figure 17 Left tree of "brcd" node

- Figure 18 Traversing of tree during transformation from LR to LTR

- Figure 19 Chosen thread root if no\_of\_threads >= 1

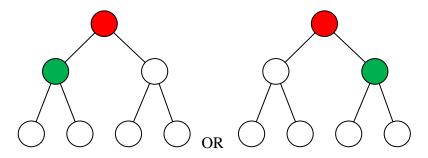

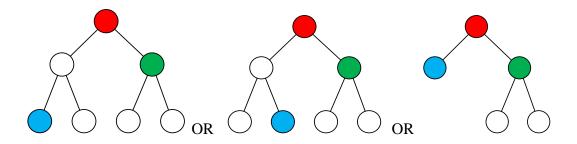

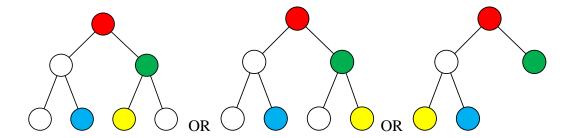

- Figure 20 Alternative choices for thread root 1

- Figure 21 Alternative choices for thread root 2

- Figure 22 Alternative choices for thread root 3

- Figure 23 Selection of subtrees for a random tree

- Figure 24 Dataflow of SDRAM interface during creation of streams

- Figure 25 Example of MSC tree

- Figure 26 STATISTICS manipulation during analysis phase

- Figure 27 Dataflow on SDRAM interface during coding phase

- Figure 28 Workplace

# **List of Tables**

- Table 1 Constructs used in pseudo language

- Table 2 Comparison of FPGA models

- Table 3 Resource estimation

- Table 4 CMD signal

- Table 5 SIZE signal

- Table 6 Attributes of used TYPES of data

- Table 7 Sequence of bytes sent from PC to FPGA

- Table 8 Structure of INPUT DATA STATISTICS in BRAM

- Table 9 a), b) Squeezing statistics

- Table 10 Sequential representation of nodes in memory

- Table 11 Linked representation of nodes in memory

- Table 12 Left tree representation of nodes in memory

- Table 13 First block of memory containing node attributes (NODE1)

- Table 14 Second block of memory containing node attributes (NODE2)

- Table 15 Third block of memory containing node attributes (NODE3)

- Table 16 Fourth block of memory containing node attributes (NODE4)

- Table 17 Types of threads

- Table 18 ZEBC TABLE memory structure

- Table 19 Examples of values coded by ZEBC with different bases

- Table 20 MSC Overhead

- Table 21 Header format of node's first coded counter

- Table 22 Identifier of different thread

- Table 23 FPGA resource utilization

- Table 24 IOB utilization

# List of abbreviations

ALM Adaptive Logic Module

ALUT Adaptive Look-Up Table

ASIC Application-Specific Integrated Circuit

ASMD Algorithmic State Machine with Data path

BC Binary Complement

BRAM Block Random-Access Memory

BWT Burrows-Wheeler transform

CLB Configurable Logic Block

CPLD Complex Programmable Logic Device

DCM Digital Clock Manager

DLL Delay Locked Loop

DSP Digital Signal Processing

DSRC/WAVE Dedicated Short Range Communications/Wireless Access in Vehicular Environments

FPGA Field Programmable Gate Array

FSM Finite State Machine

FSMD Finite State Machine with Data path

IO Input/Output

IOB, IOE Input/Output Block, Element

JPEG Joint Photographic Experts Group

JTAG Joint Test Action Group

LAB Logic Array Block

LC/LE Logic Cell/Logic Element

LR Linked Representation

LSB Least Significant Bit

LTR Left Tree Representation

LUT Look-Up Table

MSB Most Significant Bit

MSC Multi Stream Compression

PC Personal Computer

PLD Programmable Logic Device

PLL Phase Locked Loop RAM Random-Access Memory

RT Register Transfer

RTL Register Transfer Level

SDRAM Synchronous Dynamic Random-Access Memory

SRAM Static Random-Access Memory

SRL16 16-bit shift register SRL32 32-bit shift register

UART Universal Asynchronous Receiver/Transmitter

VHDL VHSIC Hardware Description Language

XML Extensible Markup Language

ZE Zero Ending

ZEBC Zero Ending & Binary Complement

# 1 Introduction

Information science has affected nearly all levels of modern society. Nowadays, the world is approaching the stage in which every device is going to be connected to a global network. Indispensable amount of research concerning the so-called Internet of Things conducted so far provides an opportunity for customized manufacturing, safer transport and more comfortable living with ever-increasing automation. These put above a big demand on communication infrastructure to cope with an enormous volume of data.

Compression is a way to lower this volume. During the last few decades, numerous compression algorithms were invented, ranging from the universal ones (such as Huffman Coding or Arithmetic coding) to those designed for specific data (for example, JPEG, MP3). In pursuit of maximum compression ratio and speed, new compression methods are still being developed.

One of the recently developed compression methods is Multistream Compression (MSC) algorithm [1]. In contrast to other methods, MSC encodes a special stream of counters to achieve decent compression ratio. Its design allows for parallel processing to reduce the processing time. In some applications, this method can be used as a replacement of some existing methods (Huffman or Arithmetic coding) as it often gives better outcome. Besides, this method gives favorable results if applied in conjunction with various transformations (such as Burrows-Wheeler Transform) used for input data preprocessing. Main application areas of the MSC algorithm are text and image compression. One of its utilizations could thus be found in compression of document databases. Analysis of text compression using the MSC algorithm is shown in [2]. The experiment using the MSC algorithm for compression of JPEG images can be found in [3].

Due to its wide area of application, MSC is concern of transportation sciences as well. Nowadays, transport is already extensively computerized – there are information networks in vehicles, communication links between the infrastructure and control centers, and many others. The implementation of cooperative systems is inevitably causing a huge increase of transferred data on the infrastructure. Despite the fact that MSC algorithm does not find use in compressing XML or fixed-length binary encoded messages used by DSRC/WAVE standard [4], there are other possibilities of its utilization such as formerly mentioned database or image compression.

#### 1.1 Goals of the thesis

The goal of this thesis is to design and implement MSC algorithm on FPGA platform. Main features of the algorithm are complex tree structure, high memory demand and parallel processing.

One of the main tasks is to find representation of the used tree structure in memory that would possess advantageous properties for latter stages of the algorithm. Further task is to specify the hardware requirements for implementation of the algorithm with given input parameters. The final objective is to implement the design to highest possible extent into selected platform and verify its functionality.

This thesis should serve as a stepping-stone for further development of the hardware implementation of the algorithm and as an inspiration for building the decompression module which is not subject of this thesis. Obtained results of this implementation shall thus be presented in order to provide objective measure for monitoring future improvements.

#### 1.2 Organization of the thesis

The content of the thesis is conceptually divided into two parts. In first half, the presented information is exclusively theoretical and goes from the ideas to be implemented (chapter 2), through the design methodology that describes how the ideas to be implemented have to be transformed to fit the used platform (chapter 3), to the description of actual hardware platform that physically realizes the ideas (chapter 4). The other half puts emphasis on the practical work although short sections of theory ale also contained. The chapter 5 describes mainly the hardware aspects of the overall design and chapter 6 discusses the details of the individual parts with emphasis on the ideas. Chapter 7 analyzes the results of the implementation and chapter 8 gives incentives for further work.

#### 1.3 Initial remarks

Before reading, some features of the thesis should be mentioned. The reader should beware of similar names for different entities. The MSC algorithm for example creates statistics more than once, so terms like 'statistics' or 'number of occurrences' are used in different contexts.

For an easy orientation, different fonts and capital letters are used in the chapters concerning the algorithm design. CAPITAL LETTERS are used to denote Finite State Machines and memories. *Arial Narrow in italics* is used for attributes in memory.

Throughout the work, snippets of code using pseudo language are used. The occurring constructs are explained in Table 1 below:

Table 1 Constructs used in pseudo language

| Construct                 | Example                                 | Meaning                                                                                                                        |  |

|---------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| == / !=                   | while (end == 0)                        | equal to / not equal to in conditions                                                                                          |  |

| =                         | last = 1 assignment to var              |                                                                                                                                |  |

| (x) / (x downto y)        |                                         | index / range of indexes                                                                                                       |  |

| (others => '1')           | data(FREE-1 downto 0) = (others => '1') | assignment of specified value to range of indexes                                                                              |  |

| $\Rightarrow$             |                                         | do specified operation                                                                                                         |  |

| var(x, y,)                | ⇒ read DATA_OUT(TYPE, INDEX, POSITION)  | do specified operation with parameters in brackets (for example: read DATA_OUT from memory address specified by the parameters |  |

| . CURRENT_NODE.left_child |                                         | attributes of memory item (for example: attribute left_child of item CURRENT_NODE                                              |  |

# 2 MSC Algorithm

The MSC algorithm is a new lossless compression method invented by Czech scientist Jiří Kochánek [1]. The method is based on the idea that data can be split into different parts. Each of these parts contains own data for compression arranged in streams. For each part of the data, coding method that gives the best compression result is chosen. The MSC algorithm differs from other models based on splitting data into streams by the fact that in this case the streams do not contain symbols but counters. The process of compression is rather complex and requires multiple passes of input data. However, the algorithm presents the possibility of parallel processing.

# 2.1 The Steps of the Algorithm

The algorithm consists of these five steps [3]:

☐ Input data statistics

☐ Creation of binary tree based on statistics

☐ Transformation of input data into logical streams belonging to single binary node

☐ Statistical analysis of each stream ending with selection of the best performance compression method

☐ Compression execution

For simplicity, the description will be given only for sequential processing. The details about the parallel processing will be given in further chapters discussing the implementation.

# 2.1.1 Input Data Statistics

The algorithm starts with reading characters<sup>1</sup> from the input data, one at a time. The input data of the algorithm could be a text or a picture in which case the symbol would be a letter or pixel color, respectively. For each symbol occurring in the input data, its first occurrence as well as number of occurrences is determined. After all input data are read, the statistics is sorted according to the number of occurrences.

<sup>&</sup>lt;sup>1</sup> Character is one item in the input data. Symbol is a value of the character. Alphabet is a set of all symbols.

#### 2.1.2 Creation of Binary Tree

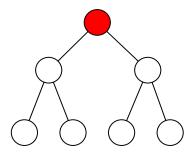

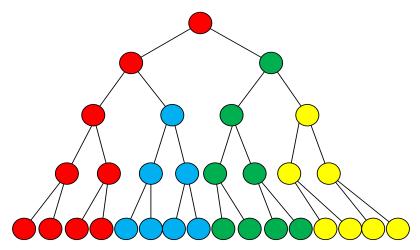

When the statistics is in the desired form it serves as a basis for building MSC tree. The items of the statistics become the leaves of the binary tree. In this stage, parents of two nodes with the lowest number of occurrences are created iteratively until there is only one unconnected node remaining – the root of the tree. The tree might resemble Huffman tree, however, the MSC tree is governed by additional rule which states that every left child has earlier occurrence in the data than the right one, even if it has lower number of occurrences. Moreover, the nodes are equipped with counters and direction switches.

#### 2.1.3 Creation of Counter Streams

Initially, before the traversing of the tree starts, the counter of each node is set to zero and each switch position set to left as shown on Figure 1. The switch determines the active child of a node and thus one active path is built in a tree from root to leaf. During creation of streams the input data are read for the second time. Knowing the investigated symbol, the tree is traversed from the root node all the way to the leaf node representing this symbol. Each time a node is passed its counter is incremented. If two consecutive symbols are different, the direction switches need to be switched to other direction in those nodes where the current path differs from the previous path. The rule is that when the position of a switch is swapped, the counter value is written into stream of the particular node.

When the reading of input data is finished, there are still nonzero values in node counters which need to be written to streams as well. Therefore, each node is entered once again. The values in streams are actually the data that will be compressed.

Figure 1 Example of MSC tree in default setting

#### 2.1.4 Statistical Analysis of Streams

After obtaining the streams, the length of the compressed data is calculated for different coding methods and the method giving the best result is selected. The coding methods are specified in advance. The analysis is executed for each node of the tree separately and the best method is selected for every single one. If ZEBC coding (section 2.2.2) is among the investigated methods, the analysis is performed for whole range of bases. In case of Huffman coding, Huffman tree needs to be built for every node of the MSC tree.

#### 2.1.5 Compression

At this stage, the streams of counters are known as well as the method of coding. First, the overhead of the final stream of coded values is written to the output. It carries information required for correct decompression. Some of the items in the overhead are input parameters, others are obtained at the compression module.

For creation of the final compressed stream, traversing of the MSC tree is executed once again. At the beginning, the counter of root node is set to number of characters in input data, counters of other nodes are reset and switches are set to left. The tree is traversed from the root to leaf nodes using the active path until the counter of root node is equal to zero. In case the counter at the entrance of a node has value 0, next value from the stream of counters is read, coded and written to the final stream of coded values. If a node is accessed for the first time, additional information (consisting of leaf node flag, symbol in case of leaf, the chosen coding method and its parameters) is written to the output before the coded counter value. Each time a node is accessed, its counter is decremented. When it reaches zero, the switch position of the parent node is changed.

#### 2.2 The Coding Methods

The previous paragraphs imply that the MSC algorithm chooses among different coding methods. Basically, they can be arbitrary methods. However, the criteria for the convenience of the method can differ. Sometimes, the speed of the decompression is crucial, in other cases the achievement of the maximal compression ratio is desired. Depending on criteria set of methods is adequately adjusted. In the first software application a set of 3 methods that appear to be complementary was tested.

#### **2.2.1** Elias α

Elias Alpha coding is usually used for short or badly compressible streams. If all streams are coded by Elias  $\alpha$ , the output data has equal length to the same data compressed by Huffman coding. In the MSC algorithm, the inverted version of this unary method is used. If a number n is coded by this method, it will be of the following form [5]:

$$\alpha(n) = 1_1 1_2 \dots 1_{n-1} 0_n$$

#### 2.2.2 **ZEBC**

Zero Ending & Binary Complement (ZEBC) is a simple way of coding similar to Elias  $\gamma$ . It was developed specifically for MSC method by the authors of the algorithm [1]. It is parameterized by a selected number, the base – ZEBC(b), which further optimizes the coding of stream. Selection of this number is based on analysis of counters. This method is mostly used for compression of streams of middle length.

The ZEBC coding is a type of variable-length coding that is used for coding natural numbers. The coded number comprises of Zero Ending (ZE) prefix coded by inverted Elias  $\alpha$  coding and of a value expressed by the binary complement (BC) but only if the number to be coded is greater than the base value. If the number is lower than the base, it is expressed only in ZE code. The base can be viewed as a number that determines the boundary, from which the coded value is expressed by ZEBC code.

The coding is performed according to ZEBC table of intervals (Appendix A). Construction of the table is governed by a set of elementary rules. Each interval has beginning and end. The values of the first table interval are known – the beginning is 0 and the end is 1. The index i denoting the intervals goes from zero onwards. The calculation of the i-th interval is governed by these rules:

When number n is coded by ZEBC(b), these rules are followed: if the number n is lower than base b, the number n is expressed only in ZE code. If it is larger or equal to b, then the difference D is calculated as D = n - b and the table interval i into which D belongs is found. The ZEBC(b) code of the number is then expressed by sequence (b + i) in ZE code, followed by number (D - beginning(i)) in BC code of length (i+1) bits.

# 2.2.3 Huffman Coding

This method is intended for coding of largest streams. It is because the first counter of each tree node coded by this method contains a large header containing all the necessary information for reconstruction of the Huffman tree. Therefore, if a large stream is coded, the percentage of the header in the final compressed stream is low.

The method uses the static Huffman coding for coding of counters, meaning the number of occurrences of each symbol is known in advance.

# 2.3 MSC Properties

Since the invention of the first compression methods, many new methods were discovered. It is because none of the methods is the best one for all types of data and for various requirements and every single one has its benefits and drawbacks. MSC is not an exception. The list of the advantages and disadvantages is below [6].

#### **ADVANTAGES**

|       | Higher compression efficiency than pure entropy methods for many types of data. Particularly suitable as replacement of Huffman and arithmetic coding in codecs, endecs (MPEG and JPEG types) and after BWT |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Decompression is markedly fast with minimum requirements for memory size                                                                                                                                    |

|       | Method allows both sequential and parallel processing                                                                                                                                                       |

|       | Parallel processing can fully exploit the nowadays progress in component base (multi-core processors, FPGA, CPLD,)                                                                                          |

|       | The data is processed without multiplication and division (unlike arithmetic method), which is particularly advantageous for small devices lacking mathematic coprocessors (e.g. mobile phones)             |

|       | The development of this method is only in its early stage with still huge potential for improvement                                                                                                         |

| DISAD | VANTAGES                                                                                                                                                                                                    |

|       | Multiple passing - compression consist of 2 passes through input data and one pass through transformed data                                                                                                 |

|       | High requirements on system components (memory size) during compression phase                                                                                                                               |

|       | Slower compression phase than current entropy methods                                                                                                                                                       |

# 3 RTL Design

As hardware systems nowadays are very complex, it is impossible to create a design considering the connection among transistors. In the modern era, logic gates as blocks of higher abstraction level are used to realize logic functions. For large designs, however, those are too detailed as there is a possibility in hardware to realize commonly used higher level operations that can be created from the logic gates. The example of such high abstraction blocks are adders, comparators, multiplexers or registers. This level of abstraction is called Register-Transfer Level (RTL).

#### 3.1 Method Overview

In the area of informatics, complex processes are usually described by algorithms, as sequences of steps or actions. Nowadays, algorithms are generally implemented by software and executed in a general purpose computer. However, to obtain better performance and efficiency, it is sometimes beneficial or even necessary to realize them in hardware. The Register-Transfer (RT) methodology is a design methodology that describes the system operation by a sequence of data transfers and manipulations among the registers.

To realize an algorithm in hardware, general hardware constructs that resemble the variable and sequential execution model are needed. The RT methodology is aimed for this purpose. The key characteristics of this methodology are:

|   | Registers are used to store the intermediate data and are equivalent to variables |

|---|-----------------------------------------------------------------------------------|

|   | used in an algorithm                                                              |

| П | Data noth is used to realize all the required register operations                 |

- ☐ Data path is used to realize all the required register operations

- ☐ Control path is used to specify the order of the register operations

When an algorithm is realized by RT methodology, the necessary data manipulation and data routing are performed by dedicated hardware blocks. The data manipulation circuit, routing network and the registers together are known as the data path. Since an algorithm is described as a sequence of actions, a circuit to control the RT operations flow is needed, and it is known as the control path. Both blocks with connections between them are shown on Figure 2.

Figure 2 Block diagram of a general system designed by RT methodology (source: [7])

A control path is usually realized by a Finite State Machine (FSM), which uses states to enforce the order of the desired steps and branches, which are equivalent to conditions and loops in an algorithm. A FSM consists of two elements: combinatorial logic and registers. The registers are used to store the state of the machine. The combinatorial logic can be viewed as two distinct functional blocks: the next state logic and the output logic. There are two widely known types of state machines: Mealy and Moore. The output function which specifies the value of the output signals is where the two types differ. If it is a function of the state only, the output is known as a Moore output. On the other hand, if it is a function of the state and input signals, the output is known as a Mealy output. A complex FSM normally has both types of outputs.

Since an RT operation is performed in a state of the FSM, the FSM is extended to Finite State Machine with Data path (FSMD) to indicate the desired RT operation in each state. The state representation and state transition of an FSMD are similar to those of an FSM. An Algorithmic state machine with data path (ASMD) chart is a usual way of descripting FSMD [7].

Most architectures require both control and some data. Only very few of them are either all control (for example, simple communications protocols) or all data (digital filters). Separating the design into a controller and a data path helps to think about the operation of the system [8].

# 3.2 RTL Design Steps

Frank Vahid [9] recognizes 4 steps in the RTL design.

- 1. The desired behavior of the system shall be described as high-level state machine. The state machine is high-level as the transition conditions and the state actions are more than just Boolean operations on bit inputs and outputs.

- 2. A data path to carry out the data operations of the high-level state machine is created.

- 3. Data path, specifically the external Boolean inputs and outputs are connected to a controller block.

- 4. High-level state machine is converted to FSM for the controller, by replacing data operations with setting and reading of control signals to and from data path.

In case of FPGAs (and other Programmable Logic Devices) the hardware description of the circuit is the first step in the implementation, the description is coded and after that synthesized, technology mapped and packed usually by using software tools. At the end, the circuit is placed and routed to the hardware platform to complete the design flow.

# 4 FPGA Architecture

Field Programmable Gate Arrays (FPGAs) are pre-fabricated silicon devices that can be electrically programmed. FPGAs consist of an array of different blocks, including general purpose logic blocks and specific purpose hard blocks, such as memory or DSP blocks. General purpose logic blocks are programmable and along with specific purpose hard blocks they are surrounded by a programmable routing fabric that allows these blocks to be programmably interconnected. The array of blocks and the routing fabric are then surrounded by programmable input/output blocks that connect the chip to the outside world. In the following text, architectures of two biggest FPGA vendors Xilinx and Altera will be described. The other manufacturers use similar architecture.

A configurable logic block (CLB) used by Xilinx is a basic component of their FPGAs that further divides into slices. The slices contain blocks performing combinatorial logic, register resources and multiplexors [10]. The elementary building block of Altera's devices is called Logic Array Block (LAB) and it consists of ten Adaptive Logic Modules (ALM) or 16 logic elements.

Commercial vendors use Look-up Tables (LUTs) to provide basic logic and storage functionality. LUT-based blocks provide a good trade-off between too fine-grained and too coarse-grained logic blocks, ensuring that the wasting of resources is minimal while maintaining high performance. The capacity of a LUT is limited by the number of inputs, not by the complexity of a function. Unlike the logic realized by gates, the delay through the LUT is constant, regardless of what logic function is being performed inside.

A LUT is typically built out of SRAM bits to hold the configuration memory LUT-mask and a set of multiplexers to select the bit of the SRAM that matches the inputs. To implement a k-input LUT (k-LUT),  $2^k$  SRAM bits and a  $(2^k - 1)$  multiplexers are needed. Figure 3 shows a 4-LUT, which consists of 16 bits of SRAM and a 16:1 multiplexer implemented as a tree of 2:1 multiplexers [11].

Figure 3 Architecture of a LUT (source [11])

The parameters of various FPGAs differ beyond the names of different vendor components. The Xilinx devices encompass 6-input LUTs and two or three types of slices depending on platform. The LUTs of the most basic slice type can be configured as either a 6-input LUT with one output, or as dual 5-input LUTs with identical 5-bit addresses (shared inputs) and two independent outputs. In contrast, the LUTs in the most complex slice type can also be used as distributed 64-bit RAM with 64 bits or two times 32 bits per LUT, as a single 32-bit shift register (SRL32), or as two 16-bit shift registers (SRL16s) with addressable length [10].

Unlike Xilinx, Altera uses two types of architecture in their model series. The architecture used in majority of their devices utilizes a component called Adaptive LUT (ALUT) with 8 inputs that provides resources for realizing either 6-input LUT or two LUTs that can work independently in case the total number of inputs is less or equal to 8, otherwise the inputs need to be shared. The number of shared inputs depends on widths of the realized LUTs. Two extra adders are included to enhance the arithmetic capability of the ALM, allowing for two 2-bit addition or two 3-bit addition per ALM. The comparison of the two architectures is shown on simplified schemes on Figure 4.

Figure 4 Comparison of Xilinx's and Altera's architecture (source [11])

The other Altera's architecture utilizes a 4-input LUT, however, a gradual shift to the formerly mentioned architecture is visible [11].

Besides LUTs and registers, basic building blocks of devices from both vendors also have carry logic resources which are designed to implement arithmetic logic functions with high speed performance due to their dedicated carry chain which runs vertically in columns.

The input/output blocks or elements (IOBs/IOEs), depending on a vendor, make an interface between the FPGA and the outside world. In Xilinx devices, IOBs are grouped into IO banks located on each edge of the device. The IOBs contain registers and some specialized resources. One of the purposes of the IOBs is to clock data in and out of the FPGA.

Besides registers, the IOBs contain interface logic that is designed to translate the internal voltage domain of the FPGA to any used I/O standard.

Spartan 6 has 4-6 IO banks, depending on the device density and each IO bank has between 30 and 83 IO pins [12].

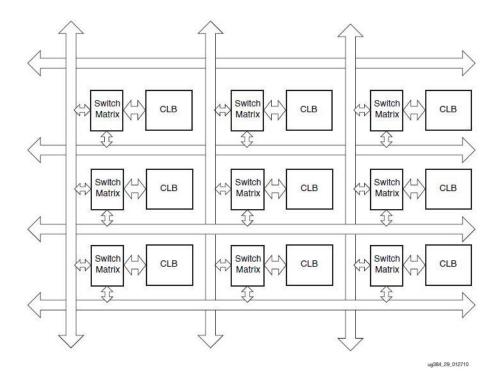

Interconnect is a programmable network of signal pathways between the inputs and outputs of functional elements within the FPGA, such as IOBs, CLBs, DSP slices, and block RAMs. Interconnect, also called routing, is segmented for optimal connectivity. The interconnect (besides the carry logic resources) is routed through the switch matrices. The switch matrices are in between each function block and they are designed to connect to other switch matrices as well as neighboring blocks as shown on Figure 5 [10].

The implementation tools select an appropriate routing that may include different kinds of routing resources. The result of the routing is designed to try and meet the timing needs of design. It is important that timing constraints are specified so that the timing objectives can be communicated to the implementation tools, allowing the software to choose the smartest routing solution to meet the needs.

Figure 5 CLB Array and Interconnect channels of Xilinx (source: [10])

Besides the LUTs, which can be configured as small memory blocks for coefficient storage and low capacity buffering, FPGAs contain also dedicated blocks of RAM memory. These memories can operate in true dual-port mode, meaning they have two ports A and B and either of these ports can be a WRITE or READ port, independent of the function on the other port, sharing only the stored data. In the dedicated memories, WRITE and READ are synchronous operations. Data bus of each port can be configured in one of the available widths, independent of the other port.

The Xilinx block RAM (BRAM) is an 18 or 36 Kb block of memory, depending on the device, which can also be configured as two independent 9/18 Kb blocks. The maximum width of the memory data bus is 36/72 bits containing a parity bit for each byte [13]. Each Altera device uses one of the memories labeled as M20K and M10K with maximum data bus width of 40/20 bits (20-bit width applies for true dual port mode) same for both types and capacities of 20 Kb and 10 Kb, respectively. Unlike the Xilinx block, the M20K and M10K blocks cannot be split [14], [15]. High-end platforms from Xilinx also contain dedicated logic for cascading BRAMs thus creating Ultra RAM blocks of maximum capacity 288 Kb.

Today's FPGAs contain more types of clock networks that include at least global and regional networks. The networks are designed to minimize clock skew by optimized integrated circuit layout using buffers and multiplexors, and also some further techniques are employed such as Phase Locked Loop (PLL).

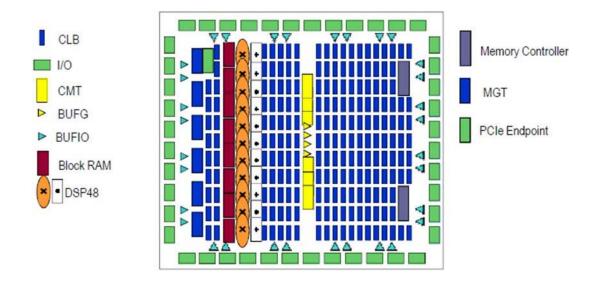

Figure 6 General overview of Xilinx FPGA architecture (source: <a href="https://www.pantechsolutions.net">https://www.pantechsolutions.net</a>)

# 5 Design Overview

Chapter 3 showed the difference between the way an algorithm is implemented in software and hardware. Before the hardware implementation, described in this thesis, was performed, there had already been software implementation of the MSC compression algorithm in C language. Analysis of its source code was performed as a first step of the hardware implementation. It was necessary to familiarize with the algorithm very closely and to understand it to smallest details.

The analysis served as a basis for rewriting the code into pseudocode that removed all the features that are used in software but cannot be used in hardware, such as pointers. The pseudocode was written in a form that would allow direct inference of a Finite State Machines and that considered division of data to memory structures. Besides, new features had to be introduced, such as new representation of tree, for convenient mapping to hardware. Example of such pseudocode is shown at the end of this page. Pseudocodes for all parts of the algorithm are attached in Appendix B.

At this point, memory demand of the design was already known so it was required to map these memory requirements into the resources, as described in section 5.1.

At the end, Finite State Machines (with data path) were inferred for logically divided parts of the algorithm, according to the pseudocode. The FSMs aimed at minimizing number of states and using the minimum number of clock cycles so that each part of the algorithm took as little time as possible. They were then translated into VHDL code, continuously simulated to verify functionality and synthesized. The results of the synthesis served as a basis for choosing a suitable FPGA. At the end, the algorithm was programmed into the chosen FPGA.

```

i = 0

while (i < SID)

symbol = INPUT_DATA(i)

no_of_occ = STAT(symbol).no_of_occ

no_of_occ = no_of_occ + 1

if (no_of_occ == 1)

STAT(symbol).symbol = symbol

STAT(symbol).first_occ = i

STAT(symbol).sum = 1

STAT(symbol).no_of_occ = no_of_occ

i = i + 1</pre>

```

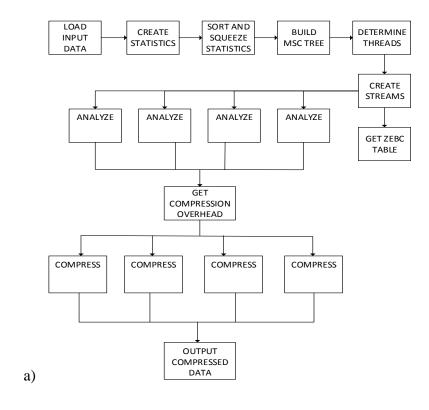

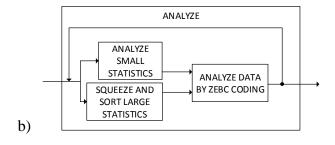

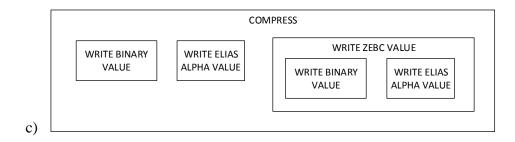

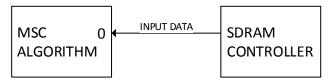

The figure 7a) shows the structure and flow of the hardware implementation of MSC algorithm. Rectangles symbolize FSMs, which are instantiated as components in VHDL language. The arrows symbolize the transition among the FSMs implemented by control signals. The FSMs that follow after parallel processing are launched as soon as processing in the slowest parallel block is finished.

The parallel blocks run concurrently, however, all of them need not be utilized. The number of used blocks is fed into the algorithm as one of the input parameters.

Some of the FSMs are further divided into subcomponents as figures 7b) and 7c) suggest. The ANALYZE block utilizes the subcomponents as steps, whereas the COMPRESS block uses its subcomponents when they are required.

The algorithm is implemented completely in parallel, which means that no resources besides memory are explicitly shared.

Figure 7 The structure of MSC algorithm hardware implementation

#### 5.1 Choice of the Platform

There is a variety of FPGA manufacturers that offer a broad range of products with different number of resources suitable for diverse applications. The number of logic cells in contemporary FPGAs lies in the range from few thousand to several million [16], [17], therefore the designer needs to make a selection of appropriate density as an integral part of a design. Even the features (such as LUT width) of similar sized platforms are different.

Generally, the choice of the FPGA platform is constrained by cost and physical requirements. There is not one specific method that is used for selection of the right-sized FPGA, however, in the design process, as [18] suggests, one shall estimate the number of:

- ☐ Look-up Tables, Flip-flops, RAM bits, DSP Blocks

- $\square$  IOs for each voltage level (3.3, 2.5, 1.8V...)

- ☐ Clock pins, PLL/DLL/DCM, Clock buffers required (regional or global)

In case an FPGA board is used, the electrical wiring is already provided. The pins of the FPGA dedicated for power supply and configuration are on the board wired to connectors that form the interface with outside world. The same applies for communication interfaces.

With utilization of two clock domains, FPGAs provides enough clock resources for the implemented design of the algorithm, which leaves us with only need for specification of memory size, number of registers and logic elements, when there are no further requirements.

In this section, numbers of these resources that are needed for implementation of MSC algorithm are estimated. The estimate will be very rough due to different physical implementations on different platforms, various optimizations, signal trimming, using dedicated components (e.g. DSP blocks) or using synthesis tools<sup>2</sup> from different vendors.

<sup>&</sup>lt;sup>2</sup> Synthesis tool is a computer program that executes logic synthesis. Logic synthesis is process of converting a high-level design description into an optimized gate level representation.

In the first step of estimation process, the architectures of currently used FPGAs from two major manufacturers Xilinx and Altera were analyzed. It was assumed that the algorithm implementation should not require using high-end platforms that are used for the largest designs. This premise already significantly reduced the number of possible choices. To substantiate this assertion, Table 2 shows comparison of 6 FPGA models from Xilinx and Altera that cover the entire range that today's market can offer. Choosing an oversized platform results in unnecessary expenses, which can eventually make the implementation of design unfeasible.

Table 2 Comparison of FPGA models (source: <a href="http://www.digikey.com/">http://www.digikey.com/</a>, prices from 08/16/2016)

| Vendor | Device family, model    | Price in USD | # of LCs/LEs | RAM bits   | # of IOs |

|--------|-------------------------|--------------|--------------|------------|----------|

| Xilinx | Kintex Ultrascale KU115 | 5,635.00     | 1,451,100    | 77,721,600 | 338      |

| Xilinx | Kintex 7 XC7K410T       | 1,301.25     | 406,720      | 29,306,880 | 400      |

| Xilinx | Spartan 6 XC6SLX45      | 54.74        | 43,661       | 2,138,112  | 218      |

| Altera | Stratix V 5SEEB         | 7,309.97     | 952,000      | 65,561,600 | 696      |

| Altera | Arria V 5AGXB5          | 1,256.63     | 420,000      | 23,625,728 | 544      |

| Altera | Cyclone V 5CEA4         | 49.40        | 49,000       | 3,464,192  | 224      |

Xilinx offers three and Altera two lower-end FPGA families, from which the final platform suitable for this application will be picked. As the official materials say, the selected families of FPGAs put the main emphasis on low price [19] [20].

In the next step, after the description of all the state machines in HDL language, the code, which was written independently of any platform, was synthetized to different Xilinx platforms in WebPack ISE. From the synthesis report, it was found that the synthesizer infers the same RTL components for all tested FPGAs (with the same architecture) even for those that could not fit the design. Initially, the calculation of quantity of LUTs required for implementation of RTL components inferred by the synthesizer was performed. However, the estimated number of used LUTs, which is also provided at the end of synthesis, was very far from the calculated number, due to various optimizations and signal trimmings. It equaled approximately one third of the obtained result. Similar outcomes were obtained for only parts of the whole design. The calculation could be performed for the Altera architecture in the same manner, but it seems that the estimation would become more of a guess.

Xilinx and Altera as two main rivals like to compare the performance of their products. They came up with a metrics that allows comparison of logic capacity of their FPGAs [21] [22]. This metric, however, mainly seems as a way to advertise their products. Not only there is a big dispersion of values for various designs, but the average value of 1.2 that expresses the logic capacity ratio of 6-input LUT/ALM claimed by the Xilinx is rather different from value 1.8 claimed by the Altera.

These considerations leave the impression that the best way to find appropriate size of FPGA from the perspective of LUTs is to synthesize the design, which needs to be built anyway, for particular architecture and use the result of estimated resources for decision. The same way can be used with advantage in case of register count determination.

Unlike the previous case, the memory requirements are already precisely determined during the design phase. After the memory bits are known, they need to be fitted to a particular platform.

The MSC compression algorithm is memory demanding. The algorithm needs to store diverse types of data throughout the process. For some data, this demand increases exponentially with symbol size in input data.

There are 3 structures that consume the majority of memory. In case of implemented 8-bit input symbols those structures take up approximately 6.5 Mb. There are FPGAs on the market that could fit this amount of data to internal memory. However, generally FPGAs with bigger memory are greater in all respects. So, it needs to be investigated, whether other resources would not stay unused, which is the case here. An alternative option is to use an external RAM memory.

Besides the large data structures, the rest of data can fit into approximately 25 blocks of M20K memories or 18 Kb BRAMs. The Xilinx BRAM comes out better from the comparison to Altera memories as they offer wider data bus and thus possibility to retrieve more data in one clock cycle.

The estimation of the component utilization by the synthesis tool is in Table 3.

**Table 3 Resource estimation**

| NUMBER OF LUTS          | ~17 000 |

|-------------------------|---------|

| NUMBER OF REGISTERS     | ~8 500  |

| NUMBER OF MEMORY BLOCKS | ~25     |

The numbers consider the algorithm without the mentioned large data structures, FSM for external memory controller and UART receiver and transmitter. Also it is advised to utilize an FPGA not more than of 80% of its full capacity [18]. Based on the gathered information, a development board with the XC6SLX45 FPGA type from Spartan 6 family connected to external SDRAM memory was selected.

# 5.2 Implementation

The description of the hardware (FSMs) was performed in one of the two most used Hardware description Languages – VHSIC Hardware Description Language (VHDL), defined in standard IEEE 1076 [23]. The language is platform-independent, meaning it can be used for not only FPGAs but also other programmable logic devices (PLD) and Application-specific integrated circuits (ASIC).

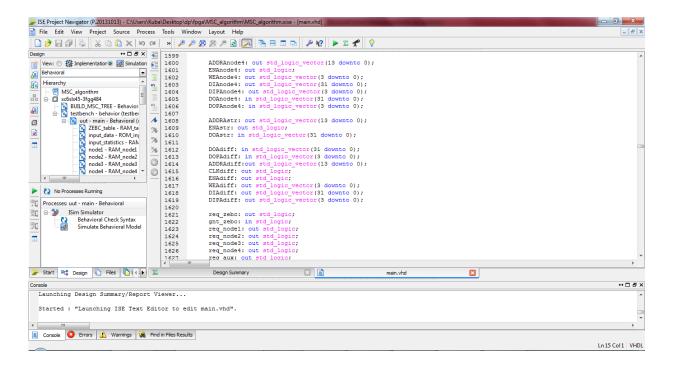

Because Xilinx platform was chosen, the design was implemented in the development environment of the same company – Xilinx ISE Design Suite 14.7, more specifically the free version ISE® WebPACK<sup>TM</sup> [24]. WebPACK provides FPGA and CPLD logic design solution offering HDL synthesis and simulation, implementation, device fitting, and JTAG programming. Therefore, it delivers a complete, front-to-back design flow providing instant access to the ISE features and functionality. Screenshot of the environment can be seen on Figure 8.

Figure 8 Xilinx ISE® WebPACK<sup>TM</sup> development environment

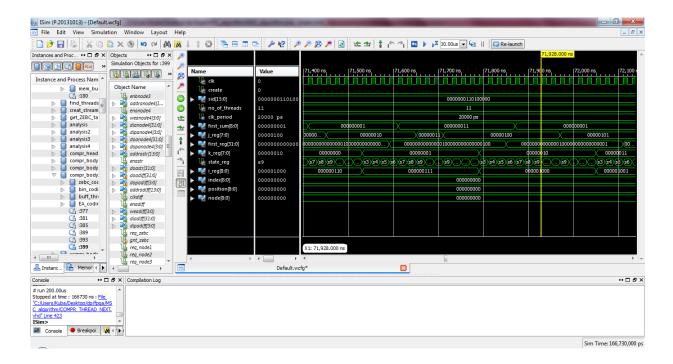

During the design, the ISim [25] simulation environment, included in the WebPACK, was used. The ISim is capable of performing behavioral and timing simulations for designs described in Hardware Description Languages – VHDL, Verilog, and mixed VHDL/Verilog language designs. Its user interface is shown on Figure 9.

Figure 9 Xilinx ISim simulation environment

# **5.3** Memory structure

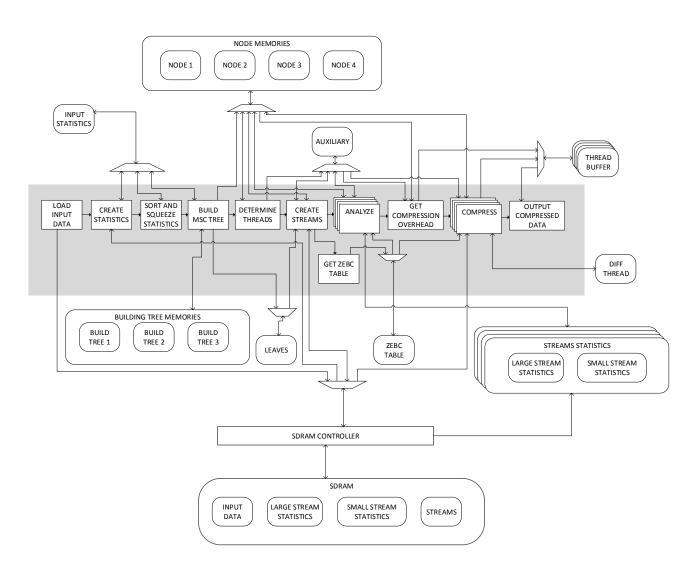

It is obvious from previous sections that the implementation of the MSC algorithm uses internal (BRAMs) as well as external (SDRAM) memories to chosen platform. The Figure 10 shows simplified structure of the MSC algorithm implementation, including memories. The memories are pictured as rectangles with rounded edges. FSMs are represented by rectangles with sharp edges and for easier orientation they are highlighted by grey background. For simplification, some of the memories in the scheme are grouped, thus scaling down the accuracy of the scheme.

As different FSMs share the memories, memory inputs need to be multiplexed, otherwise they would be driven by more sources. The scheme also shows direction of data flow between memory and FSMs (whether data are read, written or both). For illustration purposes, sacrificing the accuracy, both of these phenomena are drawn in the same scheme.

The parallel segments of the algorithm are also illustrated in the scheme. Some of the memories are parallelized as well. Besides, there are nonparallel memories that are accessed from parallel blocks. To prevent collisions caused by simultaneous access of memory, an arbiter needs to be present in the design, which decides which parallel blocks are prioritized in the access over others (section 5.4).

Due to the presence of external SDRAM in the architecture, a memory controller has to be part of the design serving as an interlink between the memory and the compression algorithm. This thesis tackles only the design of the interface between the controller and algorithm (section 5.3). The interaction with the SDRAM memory is elaborated by Ing. Tomáš Musil, Ph.D. who is one of the supervisors of the thesis.

Figure 10 Architecture of the MSC design

At closer inspection of the scheme, it can be seen that the STREAM STATISTICS are in the scheme more than once – in SDRAM and in BRAMs. That is not a mistake, it is an intention, because in the ANALYZE stage of the algorithm, part of the entire statistics, which is stored in SDRAM, is needed. Therefore, it is copied to BRAMs when needed for easier manipulation with the data. For more information see sections 5.4 and 6.7.

#### **5.4 SDRAM Interface**

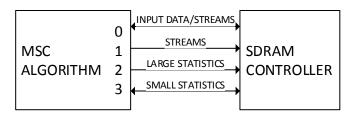

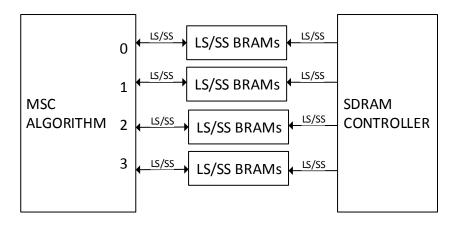

The SDRAM memory is high capacity memory that is needed for the capacity-demanding data structures in the MSC algorithm. Namely, those demanding structures are INPUT DATA, STREAMS, SMALL STATISTICS AND LARGE STATISTICS.

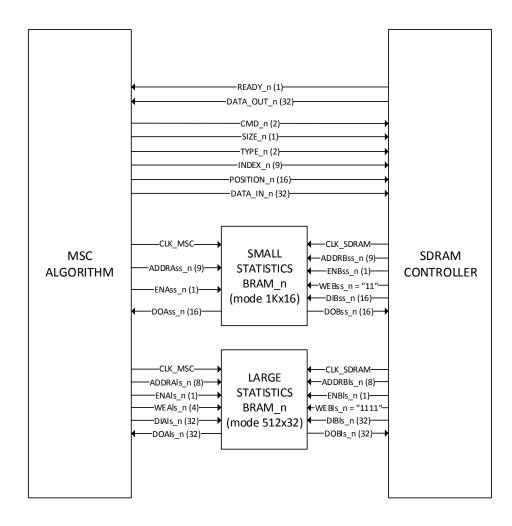

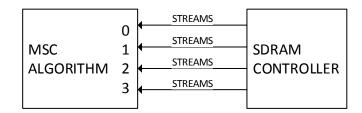

The interface between the algorithm Finite State Machines and the SDRAM controller contains 4 equivalent ports. Each port is formed by 3 buses. The first bus is used for control of the interface as well as for manipulation of a single item of data. The two remaining buses control one memory port of two BRAMs contained in one port. It is because both blocks that form the SDRAM interface (MSC algorithm and SDRAM controller) possess one memory port of LARGE STATISTICS BRAM and one memory port of SMALL STATISTICS BRAM, which is shown in scheme on Figure 11.

The complexity of the interface is given by the variety of data that are transferred via this interface and also due to parallel processing. Up to four blocks can run concurrently doing the same thing for different data – different nodes in the MSC tree, so each block owns one port and thus speed of the algorithm is not reduced by constant waiting for data retrieval due to queues on the port.

The high count of signals can also be taken as an advantage in times when there is only one sequential block running, during the stage when the counter STREAMS are created. In this stage, INPUT DATA are read and one value of counter is written into STREAMS and, depending on the value of the counter, to SMALL STATISTICS or LARGE STATISTICS. With this interface, each structure can have its own port for transfer.

Parallel processing is used for analysis and compression. During analysis, both SMALL and LARGE STATISTICS are needed. In this case, it is not only one value but the whole block for one particular node. For this purpose, both statistics are copied into dedicated BRAMs. The LARGE STATISTICS is modified in the process but need not be copied back to SDRAM. When the compression is being carried out, values from STREAMS are read one by one.

The external memory should not present a bottleneck when single values are read. In case of reading the whole STATISTICS block into BRAMs a delay has to be expected. This delay can be lowered by clocking the SDRAM and the ports of the BRAMs, controlled by the SDRAM controller, to the highest clock frequency allowed by the design.

### 5.4.1 Signals

The interface is designed with respect to the above mentioned parameters. The description of signals and data buses of one port follows.

☐ CMD launches the interaction with the SDRAM. As the Table 4 shows, if CMD = "00", the memory waits for data transfer. If CMD = "01", specified data are read and if CMD = "11", specified data are written into SDRAM.

**Table 4 CMD signal**

| CMD   | bit representation |

|-------|--------------------|

| IDLE  | 00                 |

| READ  | 01                 |

| WRITE | 11                 |

□ SIZE specifies the amount of transferred data as shown in Table 5. If SIZE = '0', only one item is read from/written to an address specified by INDEX and POSITION. The size of an item depends on the TYPE as can be seen in Table 6. Else if SIZE = '1', items on all POSITIONs from particular INDEX are transferred between SDRAM and particular BRAM. This option applies only for SMALL STATISTICS and LARGE STATISTICS.

Table 5 SIZE signal

| SIZE | bit representation |

|------|--------------------|

| ONE  | 0                  |

| ALL  | 1                  |

- ☐ TYPE determines which data are manipulated. The list of used four types is in Table 6.

- ☐ INDEX specifies exact position for block of data and rough position for specific item.

Table 6 Attributes of used TYPES of data

| TYPE             | bit representation | INDEX | POSITION | data_size |

|------------------|--------------------|-------|----------|-----------|

| INPUT DATA       | 00                 | 0     | 0-65534  | 8         |

| STREAM           | 01                 | 0-3   | 0-65535  | 16        |

| SMALL STATISTICS | 10                 | 0-510 | 0-360    | 16        |

| LARGE STATISTICS | 11                 | 0-510 | 0-180    | 32        |

□ POSITION specifies exact position of specific item

□ DATA\_IN bus specifies data to be written into SDRAM in case of writing one specific item.

□ READY is output signal to announce that DATA\_OUT is ready or that writing is finished in case SIZE = '0'. If SIZE = '1' then the BRAM that is paired with SDRAM is not accessed by the MSC algorithm side, until READY is equal to 1.

□ DATA\_OUT outputs the read data in case of reading one specific item.

□ ADDRx is address for accessing BRAM

□ ENx is enable signal of BRAM that permits to read/write data

□ WEx is write enable of BRAM that allows writing into memory. Its functionality is determined by active ENx signal.

□ DIx is input data bus of BRAM

□ DOx is output data bus of BRAM

□ CLK\_MSC/CLK\_SDRAM are two different clock domains used by the two

#### 5.4.2 Pseudocode of SDRAM Controller

interface sides

- lower index determines to/from which BRAM the data are copied. There are 2 paired BRAMs for each interface port: BRAM<sub>LARGE\_STATISTICS</sub> with 32 bit wide data bus and BRAM<sub>SMALL STATISTICS</sub> with 16 bit data bus.

- READY is in both READ and WRITE branch to determine if the SDRAM is occupied

```

⇒ go to beginning

elseif (SIZE == ALL)

⇒ copy to BRAM<sub>TYPE_n</sub> (TYPE, INDEX)

READY = 1

⇒ go to beginning

elseif (CMD == WRITE)

if (SIZE == ONE)

⇒ write DATA_IN(TYPE, INDEX, POSITION)

READY = 1

⇒ go to beginning

elseif (SIZE == ALL)

⇒ copy from BRAM<sub>TYPE_n</sub> (TYPE, INDEX)

READY = 1

⇒ go to beginning

```

### **5.4.3** Block Diagram

The block diagram of SDRAM interface captures only 1 of 4 ports. The n in the names of the data buses ranges from 0 to 3 and so the interface is 4 times larger than Figure 11 shows. The FSMs of the MSC algorithm decide when and how many ports are needed.

Figure 11 The SDRAM interface

# 5.5 Memory Arbiter

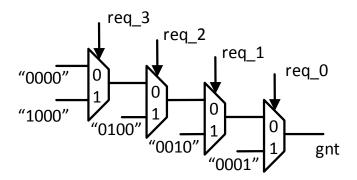

An arbiter is generally an element that governs the access to shared resources according to a set priority [26]. In case of the described implementation, memories are shared among different parallel blocks. All of the parallel blocks have equal priority, so the access is decided according to the index of parallel blocks. The memory requesting FSMs generally need to use the memory resources quite a low percentage of time so the priority of the blocks is set constant. Otherwise, a token would have to be passed among parallel blocks prioritizing the ones that did not use the memory for a longer time than the other ones.

In this setting, the memory arbiter is realized in hardware by a set of two input multiplexers. When a FSM requests a memory, it sets request signal *req* of particular memory to 1 and if no other parallel block with lower index requests the same memory, the appropriate grant signal *gnt* is set to 1.

Figure 12 Memory arbiter

Sharing of the memory increases complexity of FSMs. New states are introduced causing slightly longer duration of FSM execution. Further delay might be introduced by the fact that blocks sometimes wait few clock cycles for the grant signal. However, this hold up is minor in comparison with the time saved due to parallel processing.

As the parallel blocks access memories in random times, the memory output needs to be stored to registers as soon as it appears. It ensures that the FSM can operate this data many clocks after they were read.

### **5.6 UART**

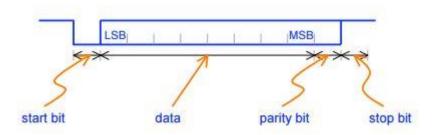

The objective of FPGA board in this implementation is to perform the compression of input data. This data need to be loaded from computer (section 6.1). Similarly, the compressed data are transferred back to the computer after the compression is finished (section 6.10). For this purpose, the Universal Asynchronous Receiver/Transmitter (UART) is used as a transfer protocol between the computer and the FPGA.

The UART is a protocol that sends bytes of data through a serial line one by one. The transmission of a single byte is shown in Figure 13. The serial line is in the '1' state when no data are transferred. The transmission is started with a start bit that has value '0', followed by five to eight data bits and ended with a stop bit of value '1'. It is also possible to append an optional parity bit to the end of the data bits. The transmission is defined by a set of parameters in advance, which include the baud rate (i.e., number of bits per second), the number of data bits, and use of the parity bit. The bits for each transmitted byte are sent from least significant bit (LSB) to most significant bit (MSB) [27].

Figure 13 Structure of data sent over UART (source: <a href="http://lslwww.epfl.ch/">http://lslwww.epfl.ch/</a>)

# 6 Design details

The steps performed in MSC algorithm were already described in chapter 2. In this section, detailed explanation of the algorithm implementation is provided.

Unlike the software implementation, the algorithm presented in this thesis makes selection only between two coding methods – Elias Alpha and ZEBC. Besides those two methods and Huffman coding, no other methods were considered. The Huffman coding was eliminated during design phase for two reasons. The first reason is that it brought quite a significant simplification of the algorithm and rise in speed of its execution. And the second has to do with the size of the compressed files. In this implementation the number of characters in input file is limited to 65 535. The Huffman coding introduces large header for each node coded by this method, meaning that the header itself could form considerable part of the final compressed stream. The large size is a significant handicap for coding of short input files, so the Huffman method may possibly not get used. The header contains all the information needed for reconstruction of Huffman tree, in contrast with no parameters in case of Elias Alpha coding and one single parameter – the base in ZEBC coding.

Besides, the Huffman coding is very demanding as far as the resources are concerned. Its implementation would occupy large amount of memory and it would require some change in the memory structure as well.

# 6.1 Input of Data to FPGA Board

The input data need to be loaded from computer to the SDRAM memory of the FPGA board. The data flow diagram of the SDRAM interface is shown on Figure 14.

Figure 14 Dataflow diagram of SDRAM interface during input data writing

Besides those data, the compression algorithm also needs to receive compression parameters. The described implementation requires two parameters – a) number of used parallel blocks in range 1 to 4 and b) size of input data or in other words the number of input data characters.

The first parameter is sent as a first byte and two subsequent bytes in Big endian format are occupied by the second parameter. In order to lower memory requirements, the size of symbols in input data is limited to 8 bits, therefore one character is transferred in one byte. The transferred sequence is shown in Table 7. The N denotes number of input characters. The transfer follows the UART protocol described in section 5.6. The communication uses 8 data bits without parity and the transfer rate is fixed to 115200 Bd.

| Byte  | Type of data                       |

|-------|------------------------------------|

| 0     | Number of parallel blocks          |

| 1     | Size N of input data (15 downto 8) |

| 2     | Size N of input data (7 downto 0)  |

| 3     | Input data                         |

| :     |                                    |

| N + 2 | Input data                         |

Table 7 Sequence of bytes sent from PC to FPGA

### **6.2** Creation of Statistics

To obtain statistics, the entire input data need to be read one by one from SDRAM as shown in dataflow diagram on Figure 15. For each read symbol, if it has not occurred in the input data yet (in other words if number of occurrences obtained from memory is zero) it is written into the memory along with its attributes. If it is not first occurrence of symbol, number of occurrences is incremented and the new value is written into the memory. It is obvious, that each symbol has a specified place in memory, which is determined by the value of symbol.

Figure 15 Dataflow on SDRAM interface during creation of statistics

The INPUT DATA STATISTICS is stored in one 18Kbit BRAM. The size of alphabet (maximum variety of symbols) is  $2^8 = 256$ , due to the restriction to only 8bit symbols. Each item of statistics has five attributes and is represented by 58 bits in total. Because the width of the structure is higher than the memory data bus of width 32 bits, bit representation of symbol, sum of left subtree's nodes and index (more on meaning of the values in paragraph 6.3) are stored on different address than number of occurrences and first occurrence of symbol.

The position in memory of the first group of attributes is [2\*symbol] and it is [2\*symbol + 1] for the other group. So in reality, one item takes up 64 bits of memory for their easy addressing in memory. The structure of the stored data can be seen in Table 8.

**Table 8 Structure of INPUT DATA STATISTICS in BRAM**

| address/data | 32                       | 24                 | 16                  | 8     |  |

|--------------|--------------------------|--------------------|---------------------|-------|--|

| 0            | symbol (31 downto 24)    | sum (23 downto 15) | index (14 downs     | to 6) |  |

| 1            | no_of_occ (31 downto 16) |                    | first_occ (15 downt | o 0)  |  |

| :            |                          |                    |                     |       |  |

| 510          | symbol (31 downto 24)    | sum (23 downto 15) | index (14 downs     | to 6) |  |

| 511          | no_of_occ (31 downto 16) |                    | first_occ (15 downt | o 0)  |  |

Generally, not all symbols from alphabet are present in the input data, which means there will be unused addresses in the memory block. The statistics in this format is not convenient for next stages. So, when reading of the input file is finished, it is needed to prepare the STATISTICS for building the MSC tree. The items of STATISTICS are copied to the lowest addresses one after another so that they make one block, omitting the unused symbols. In this process, the STATISTICS array is traversed from the end to the beginning and if a *symbol* used in the input data is encountered, it is copied along with other attributes to the first unoccupied position (from the beginning) in the same array as shown in Tables 9. The number of used symbols (*no\_of\_symbols*), important for next processing, is obtained. At the end, the items are sorted in increasing order according to the *number of occurrences*.

Table 9 a), b) Squeezing statistics

| index  | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|--------|---|---|---|---|---|---|---|---|---|---|----|----|----|

| symbol | X |   | Z |   | f |   | a | b |   |   |    |    | c  |

| index  | 0 | 1 | 2 | 3 | 4 | 5 |

|--------|---|---|---|---|---|---|

| symbol | X | c | Z | b | f | a |

Although, a variety of sophisticated sorting methods have been elaborated in hardware, one of the simplest algorithms – the modified Bubble sort [28] was converted into FSM. The Bubble sort was selected due to its simplicity and its low resource demand. This method compares each two subsequent items in an array and if they are in wrong order (depending on type of sorting), they are swapped. Each iteration ends when the last swapped item in previous iteration is reached. Sorting ends, when no items are swapped in one iteration.

# **6.3** Building the Tree

In this stage the STATISTICS becomes the array of unconnected nodes, which will be step by step overwritten by currently unconnected nodes. It is obvious that the initially unconnected nodes form leaves of MSC tree.

Before the process of tree building is described, it is necessary to make introduction into representation of binary tree in memory.

# **6.3.1** Representation of Binary Tree

When it comes to representing a tree in the standard programming language, it can be done so quite easily by using pointers or objects, telling the program, which nodes are connected to a particular node. In case of hardware implementation, however, when the designer works directly with memory, there is not such an option. Moreover, the MSC tree is not ordinary binary tree, but it has some special properties, which play a big role in choosing the right representation.

The important feature for selection of suitable tree representation is that the MSC algorithm requests traversing of the tree from root to a particular leaf, which is known in advance. The properties of the representation required by the algorithm are:

| each parent knows the position of left and right child                      |

|-----------------------------------------------------------------------------|

| each node is capable of determining the direction to a particular leaf      |

| the option to traverse only specified subtree of the MSC tree (for parallel |

| processing)                                                                 |

There are two widely used models of binary tree representation in memory [29]. The two following sections will present some theory on how they work and why they are not suitable for MSC tree representation.

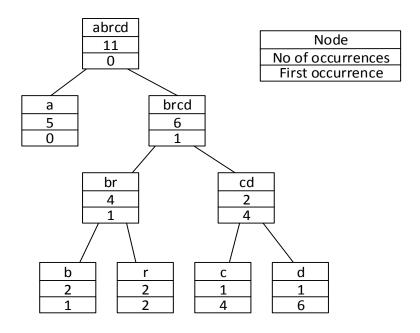

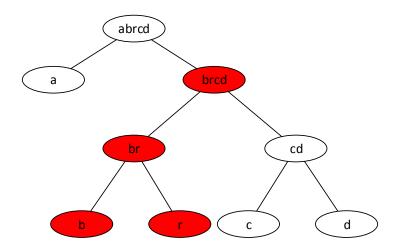

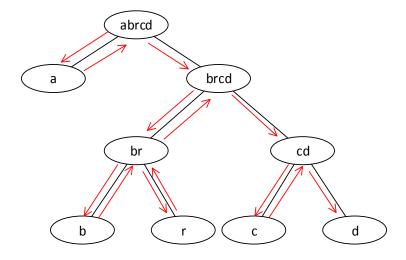

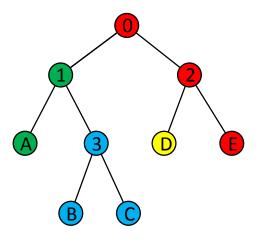

All of the tree representations will be demonstrated on the example of coding a word "abracadabra". This tree can be seen on the Figure 16.

Figure 16 Example of MSC tree for "abracadabra"

### 6.3.1.1 Sequential Representation

In this representation, the position of all nodes in memory, which can be seen as an array, is fixed and is the same for all binary trees. The root is always stored at index 0, the left child of any node with index n is stored on position 2n + 1 and the index of right child of the same node is calculated as 2n + 2. At first glance, it seems like a perfect representation – no additional data required for finding both children. On closer inspection, it is apparent that in case of uneven tree (tree where the depth of the leaves varies considerably), a lot of memory is needed for the representation and also big percentage ends up unused. Another problem is that when the tree is to be traversed from the root to a particular leaf, additional information is required in order to determine the correct path.

For the example shown on Figure 16, fifteen cells are needed for storage of nine nodes, leaving 40% of memory wasted.

Table 10 Sequential representation of nodes in memory

| index | 0     | 1 | 2    | 3 | 4 | 5  | 6  | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

|-------|-------|---|------|---|---|----|----|---|---|---|----|----|----|----|----|

| node  | abred | a | brcd | - | - | br | cd | - | - | - | -  | b  | r  | c  | d  |

#### 6.3.1.2 Linked Representation

In linked representation, all nodes can be stored in cells one after another, but it does not come for free - some additional information is needed. Each node must store the index of left and right child in the array, which is not so memory consuming considering each node in the MSC algorithm possesses plenty of other information. In case of 8-bit input symbols, the indexes take up 9 + 9 bits. The obstacle with this representation is that only with this information, the path from root to particular node cannot be found due to the random position of each node. Each leaf of the tree would require some string of bits that would hold the information about which way to go from every node on the path. As depths in MSC trees can become quite high, these strings can be rather long, taking up plenty of memory and possibly requiring multiple reads from the memory.

The Table 11 shows one of the possible layouts of tree nodes in memory. The path is expressed by directions from root to leaf which are represented by bits, where 0 means – go left and 1 means – go right. It can also be seen that there is a lot of unused memory space as leaves do not have children and the path is needed for leaves only.

| index    | 0   | 1   | 2   | 3   | 4 | 5  | 6  | 7    | 8     |

|----------|-----|-----|-----|-----|---|----|----|------|-------|

| node     | d   | С   | r   | b   | a | cd | br | brcd | abrcd |

| left_ch  | -   | -   | -   | -   | - | 1  | 3  | 6    | 4     |