## CZECH TECHNICAL UNIVERSITY IN PRAGUE FACULTY OF ELECTRICAL ENGINEERING DEPARTMENT OF MICROELECTRONICS

# DIPLOMA THESIS Low voltage low power bandgap reference

Author: Jan Škoda 11.května 2015 České vysoké učení technické v Praze Fakulta elektrotechnická

katedra mikroelektroniky

# ZADÁNÍ DIPLOMOVÉ PRÁCE

Student: Bc. ŠKODA Jan

Studijní program: Komunikace, multimédia a elektronika Obor: Elektronika

Název tématu: Návrh nízkopříkonové napěťové reference v technologii CMOS

#### Pokyny pro vypracování:

- 1. Make a general research on voltage references structures and its functionality. Focus on low-power CMOS designs.

- 2. Design selected solution in CMOS 0.18 technology with given parameters:

- Supply voltage 0.9 V 2 V

- Temperature range -50 °C 100 °C

- Use inherent bipolar devices in CMOS technology

- Reference shall be started by enable signal

- Capacitive load 0.1 pF 5 pF

- Focus on power minimization

#### Seznam odborné literatury:

[1] Gray, Hurst, Lewis, Meyer: Analysis and design of analog integrated circuits.[2] Johns, Martin: Analog integrated circuit design.

Vedoucí:

doc.Ing. Jiří Jakovenko, Ph.D.

Platnost zadání:

31. 8. 2015

prof. Ing. Miroslav Husák, CSc. vedoucí katedry prof. Ing. Pavel Ripka, CSc. děkan

V Praze dne 30. 3. 2015

# Declaration

I completed my diploma thesis on my own with the contribution of my supervisor and consultants. I used only materials (literature, projects, articles) specified in the attached list.

I agree with the utilisation of the information presented in my thesis, in compliance with copyright  $\S$  60 Zákona 121/2000 Sb., (autorský zákon).

Prague, .....

Signature

# Acknowledgement

I would like to thank my supervisor Jiří Jakovenko and external consultants Oskar Křenek and Michal Münzberger. This thesis could not be written without their help and consultation.

## Abstrakt

Tato práce se zabývá návrhem nízko napěťové, nízko příkonové napěťové reference. Úvodem jsou zde probraný MOS tranzistory a pasivní prvky dostupné v technologii CMOS. Tyto kapitoly tvoří s kapitolou popisující technologické odchylky výroby základ pro lepší pochopení návrhářské problematiky. Dále následuje souhrn několika jednoduchých i složitějších napěťových referencí, včetně reference na principu bandgap.

Hlavním úkolem práce je pak samotný návrh napěťové reference s nízkým napájecím napětím a nízkou spotřebou. V kapitole VI je čtenář postupně seznámen se základními prvky technologie CMOS a je provázen návrhem těchto hlavních částí: jádro napěťové reference, operační zesilovač, startovací obvod a trimovací obvod. Návrh a simulace je provedena v programu Cadence ver. 6.1.3. Během práce bylo třeba se alespoň okrajově seznámit s programovacím jazykem Skill a Verilog pro vytvoření simulačního skriptu a ideálního ADC převodníku.

### Abstract

This diploma thesis describes design of a LWLP (low voltage and low power) voltage reference. At the beginning, transistors and passive elements available in CMOS technology are discussed. These two chapters and presented technology variations chapter form good base for a better understanding of IC design issues. This is followed by a summary of a few simple and complex types of voltage references, including the principle of bandgap references.

The main goal of this thesis is designing a low supply voltage and low power consumption voltage reference. In chapter VI, the reader is gradually familiarized with the CMOS basic elements and designing these main parts: voltage reference core, operational amplifier, start-up circuit and trimming circuit. Design and simulation is performed in the program Cadence ver. 6.1.3. During this work it was necessary to set familiar with the programming language Skill and Verilog for making an advanced corner simulation script and for creating the ideal ADC.

# Contents

| 1        | Intr                                  | oducti                 | ion                                                                                                                                     | 1                                 |

|----------|---------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 2        | MO<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Large<br>MOS<br>Thresl | Parameters, Operating Region                                                                                                            | <b>2</b><br>2<br>4<br>7<br>8<br>0 |

| 3        | Pas                                   | sive D                 | evices 14                                                                                                                               | 4                                 |

|          | 3.1                                   | Resist                 | or                                                                                                                                      | 4                                 |

|          |                                       | 3.1.1                  | Sheet Resistance                                                                                                                        | 4                                 |

|          |                                       | 3.1.2                  | Poly-Silicon Resistor                                                                                                                   |                                   |

|          |                                       | 3.1.3                  | N-Well Resistor                                                                                                                         |                                   |

|          |                                       | 3.1.4                  | MOS Resistor                                                                                                                            | -                                 |

|          | 3.2                                   |                        | itors                                                                                                                                   |                                   |

|          | 0.2                                   | 3.2.1                  | Metal-Metal Capacitor                                                                                                                   |                                   |

|          |                                       | 3.2.2                  | Pn Junction Capacitor                                                                                                                   |                                   |

|          |                                       | 3.2.3                  | MOS Capacitor                                                                                                                           |                                   |

| 4        | Val                                   | taga D                 | eferences 22                                                                                                                            | ი                                 |

| 4        | VOI                                   | 4.0.4                  | CTAT                                                                                                                                    |                                   |

|          |                                       | -                      |                                                                                                                                         |                                   |

|          |                                       | 4.0.5                  |                                                                                                                                         | -                                 |

|          |                                       | 4.0.6                  | Simple Type Reference                                                                                                                   |                                   |

|          | 4 1                                   | 4.0.7                  | Advanced Reference Topology                                                                                                             |                                   |

|          | 4.1                                   |                        | $ ap Reference (BGR) \dots \dots$ |                                   |

|          | 4.0                                   | 4.1.1                  | Bandgap Basic Principle                                                                                                                 |                                   |

|          | 4.2                                   | -                      | ap Basic Topology                                                                                                                       |                                   |

|          |                                       | 4.2.1                  | Voltage Adding Topology                                                                                                                 |                                   |

|          |                                       | 4.2.2                  | Current Summing Topology                                                                                                                | 4                                 |

| <b>5</b> | Offs                                  | sets an                | d Technology Variations 30                                                                                                              | 6                                 |

|          | 5.1                                   | Offset                 | Definition                                                                                                                              | 6                                 |

|          | 5.2                                   | Techn                  | ology Variations                                                                                                                        | 7                                 |

|          |                                       | 5.2.1                  | Process Variations                                                                                                                      | 7                                 |

|          |                                       | 5.2.2                  | Mismatch Variation                                                                                                                      | 8                                 |

| 6 | Circ | uit De  | sign                                           | <b>40</b> |

|---|------|---------|------------------------------------------------|-----------|

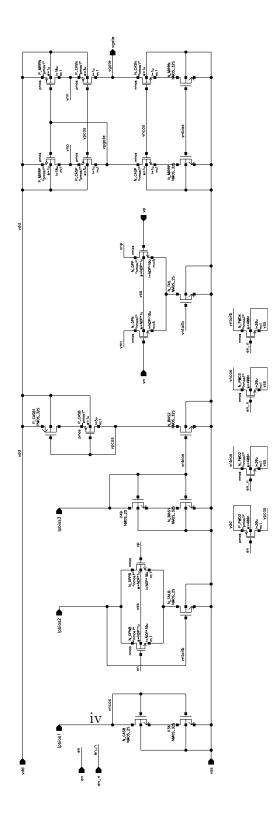

|   | 6.1  | Design  | of the Bandgap Core                            | 40        |

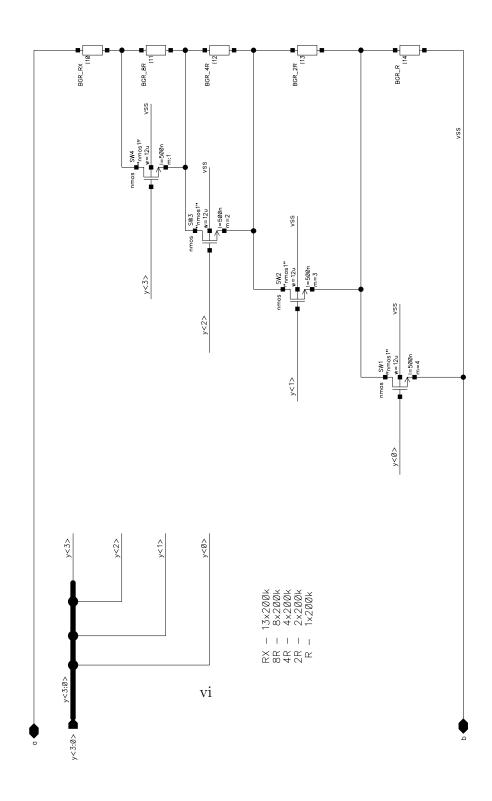

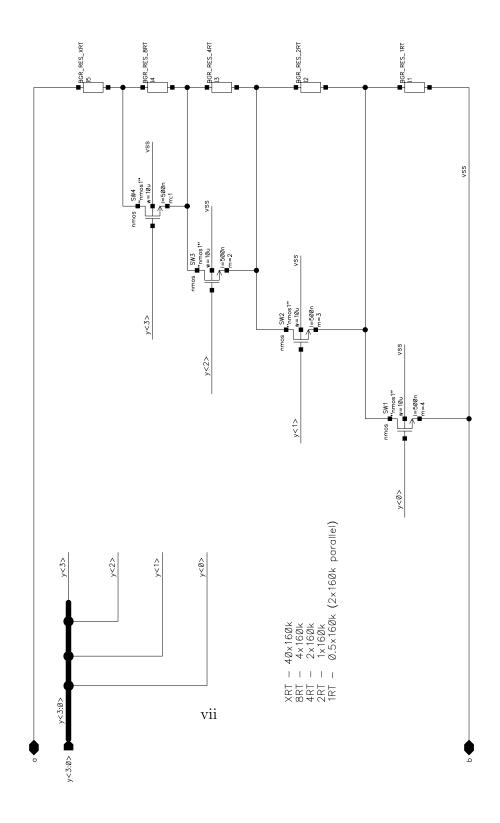

|   | 6.2  | Design  | of the Trimming Circuit                        | 44        |

|   |      | 6.2.1   | Trimming of the $R_{out}$                      | 46        |

|   |      | 6.2.2   | Trimming of the $R_s$                          | 47        |

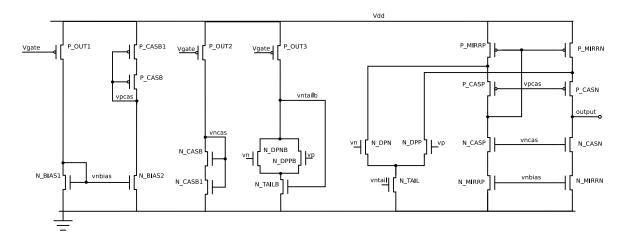

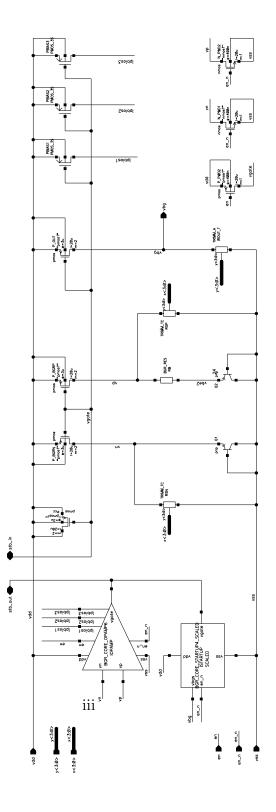

|   | 6.3  | Design  | of the Opamp                                   | 48        |

|   |      | 6.3.1   | Folded Cascode OTA with NMOS Differential Pair | 49        |

|   |      | 6.3.2   | Rail-to-Rail Folded Cascode OTA                | 57        |

|   |      | 6.3.3   | Final OTA Design                               | 60        |

|   |      | 6.3.4   | Stability Compensation                         | 66        |

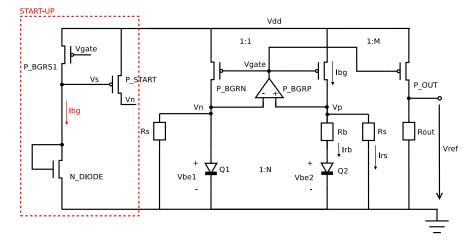

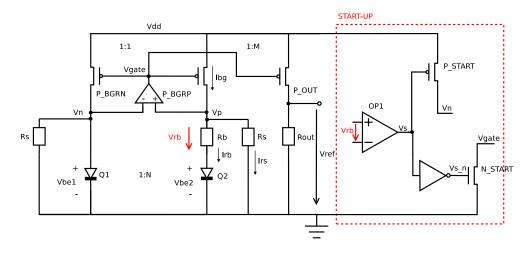

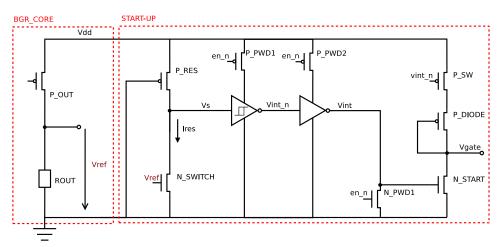

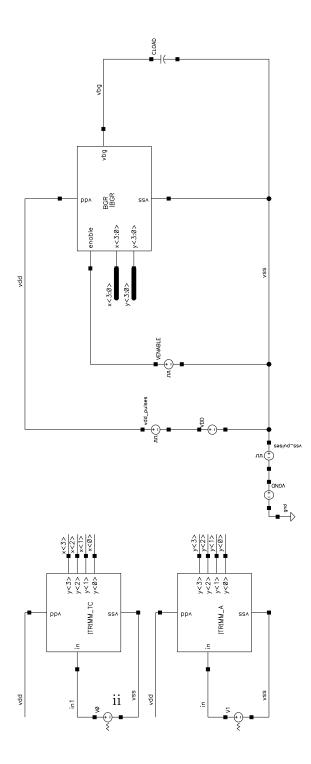

|   | 6.4  | Design  | of the Start-up Circuit                        | 67        |

|   |      | 6.4.1   | Inroduction, Start-up Examples                 | 67        |

|   |      | 6.4.2   | Final start-up design                          | 71        |

| 7 | Sim  | ulation | and Results                                    | 74        |

| 8 | Con  | clusior | 1                                              | 86        |

# List of Figures

| 1  | Simplified cross-sectional view of NMOS transistor                              | 2  |

|----|---------------------------------------------------------------------------------|----|

| 2  | MOS transistor schematic symbols used in the thesis (a) NMOS                    |    |

|    | (b) PMOS                                                                        | 3  |

| 3  | NMOS transistor, output characteristic                                          | 4  |

| 4  | Large signal model, [All02]                                                     | 5  |

| 5  | Small signal model explanation                                                  | 5  |

| 6  | Small signal models (a) Full (b) Simplified, [All02]                            | 6  |

| 7  | The $V_{th}$ extraction, ELR method $\ldots \ldots \ldots \ldots \ldots \ldots$ | 8  |

| 8  | $I_D$ - $V_{GS}$ relation with marked threshold voltage                         | 9  |

| 9  | $V_{DSat}$ and $g_m/I_D$ parameters as a function of IF, [Ste08]                | 11 |

| 10 | Design tradeoffs as a function of IF, $[BFJ^+07]$                               | 13 |

| 11 | A simple resistor layout                                                        | 15 |

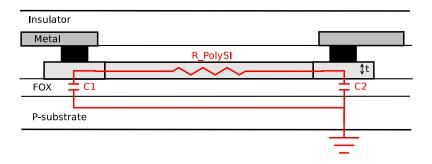

| 12 | A first order Poly-Si resistor model (Cross section)                            | 15 |

| 13 | N-well resistor without depletion layer (Cross section)                         | 16 |

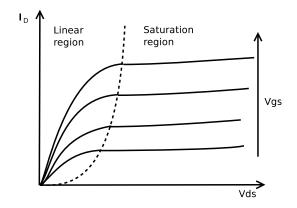

| 14 | NMOS transistor, output characteristic                                          | 17 |

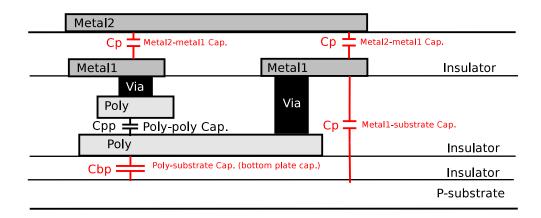

| 15 | Poly-poly capacitor with parasitic capacitances (Cross section)                 | 19 |

| 16 | (a) NMOS capacitor (Cross section), (b) NMOS cap. symbol                        | 20 |

| 17 | The variation of the gate capacitance with $V_{GS}$ voltage $\ldots$            | 21 |

| 18 | (a) PTAT and (b) CTAT voltage references                                        | 23 |

| 19 | CTAT voltage realization                                                        | 24 |

| 20 | Temperature behaviour of the diode                                              | 25 |

| 21 | PTAT voltage realization                                                        | 26 |

| 22 | (a) resistor only divider, (b) MOS only divider                                 | 27 |

| 23 | MOS-resistor voltage reference                                                  | 28 |

| 24 | Voltage reference exploiting $V_{be}$                                           | 29 |

| 25 | Voltage reference exploiting $U_T$                                              | 30 |

| 26 | A simplified energy band diagram                                                | 31 |

| 27 | Zero TC due to PTAT and CTAT                                                    | 32 |

| 28 | Principle of bandgap                                                            | 33 |

| 29 | Voltage summing topology                                                        | 34 |

| 30 | Principle of current Bandgap                                                    | 35 |

| 31 | Definition of offset                                                            | 37 |

| 32 | Principle of the current BGR                                                    | 40 |

| 33 | The common centroid geometry of diodes Q1,Q2 (N=24) $\ldots$                    | 43 |

| 34 | Trimming of the $R_{out}$ , trimming resistor network                           | 46 |

| 35 | Opamp and OTA symbols                                                           | 48 |

| 36 | Folded cascode OTA with NMOS differential pair                                                      | 49 |

|----|-----------------------------------------------------------------------------------------------------|----|

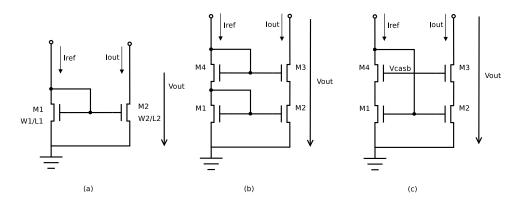

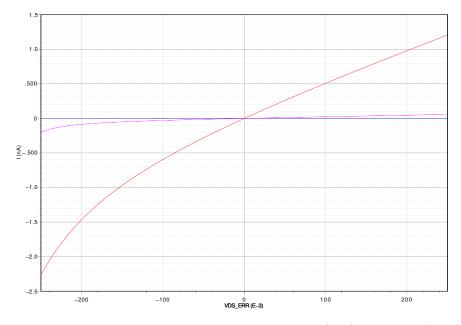

| 37 | Current mirrors (a) basic (b) stacked (c) low voltage cascode .                                     | 50 |

| 38 | Current mirror error vs. $V_{DS}$ for basic (red), stacked (blue)                                   |    |

|    | and cascoded (violet)                                                                               | 52 |

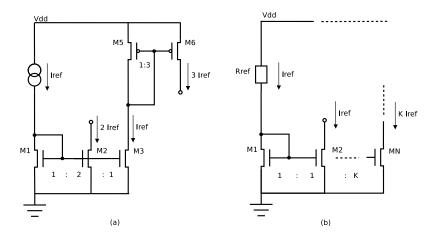

| 39 | Bias network with ideal source (a) and with $R_{REF}$ resistor (b)                                  | 53 |

| 40 | Current sources biasing                                                                             | 53 |

| 41 | Tail current biasing                                                                                | 54 |

| 42 | Cascode biasing                                                                                     | 55 |

| 43 | Self-biased network                                                                                 | 56 |

| 44 | Upgraded self-biased network                                                                        | 56 |

| 45 | Rail to rail input stage                                                                            | 57 |

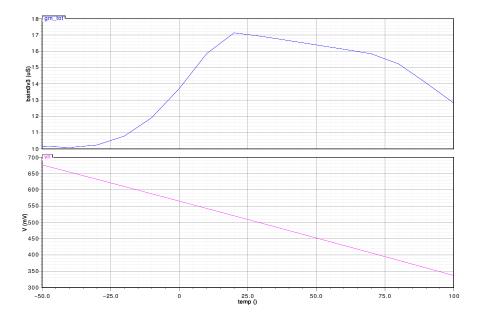

| 46 | $g_{mtot}$ and $V_{in,cm}$ temperature dependence                                                   | 58 |

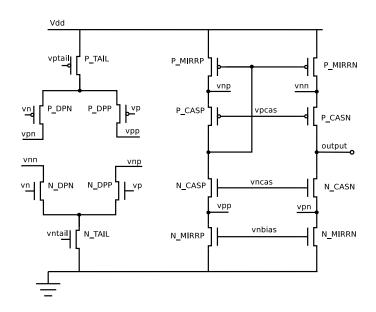

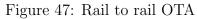

| 47 | Rail to rail OTA                                                                                    | 59 |

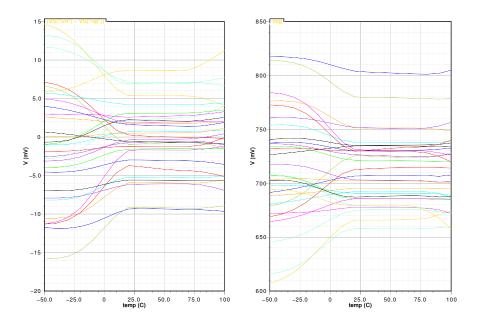

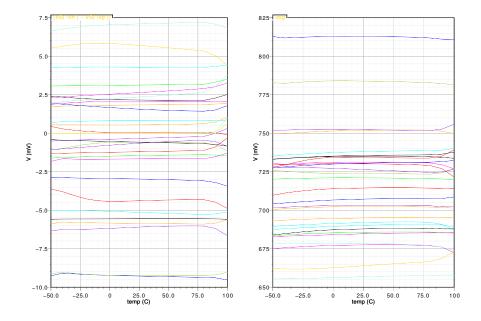

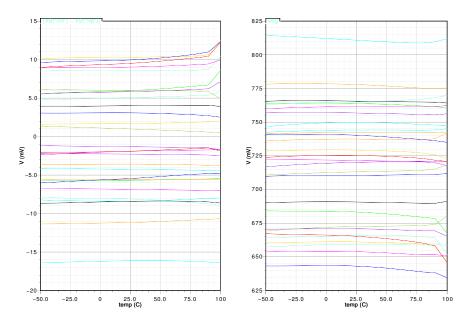

| 48 | Offset issue Vdd=1V, (Input referred offset and reference volt-                                     |    |

|    | age as a function of temperature, Monte Carlo 20 runs)                                              | 59 |

| 49 | Offset issue Vdd=1.2V, (Input referred offset and reference                                         |    |

|    | voltage as a function of temperature, Monte Carlo 20 runs)                                          | 60 |

| 50 | Offset Vdd=1V, (Input referred offset and reference voltage                                         |    |

|    | as a function of temperature, Monte Carlo 20 runs), upgraded                                        |    |

|    | N-TAIL                                                                                              | 62 |

| 51 | Complete OTA schematic with the bias part                                                           | 64 |

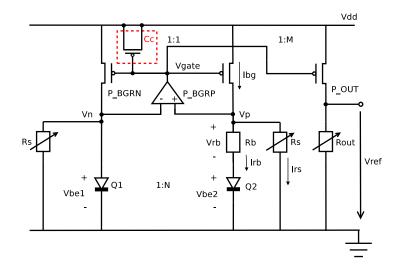

| 52 | BGR schematic with a stability compensation (MOS capacitor                                          |    |

|    | Cc)                                                                                                 | 67 |

| 53 | Start-up sensing options                                                                            | 68 |

| 54 | Start-up example based on $V_{gate}$ sensing                                                        | 69 |

| 55 | Start-up example based on $V_{rb}$ sensing $\ldots \ldots \ldots \ldots \ldots$                     | 70 |

| 56 | Final Start-up Circuit                                                                              | 71 |

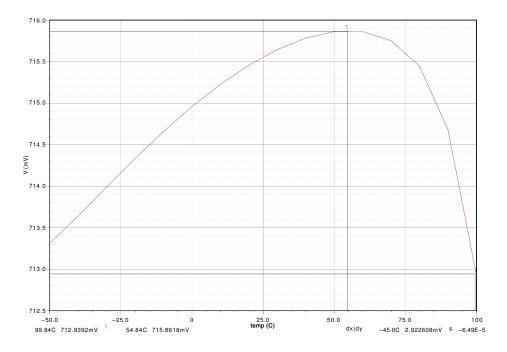

| 57 | Reference voltage $V_{ref}$ vs. temperature (-50-100°C), NN corner                                  | 75 |

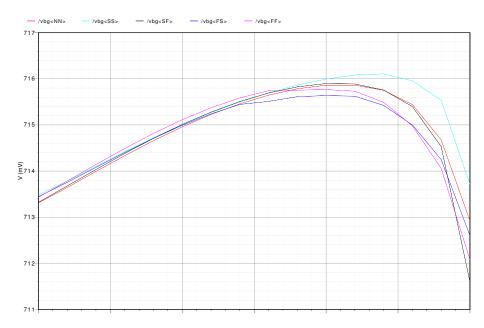

| 58 | Reference voltage $V_{ref}$ vs. temperature (-50-100°C), for vari-                                  |    |

|    | ous technological corners (NN,SS,SF,FS,FF)                                                          | 75 |

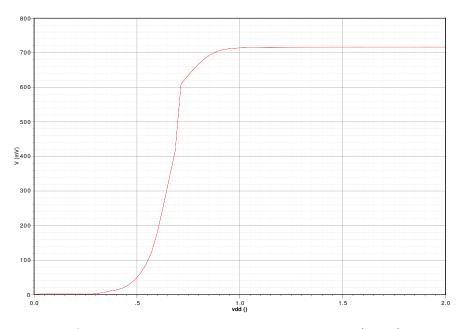

| 59 | Reference voltage $V_{ref}$ vs. supply voltage (0-2V), NN corner,                                   |    |

|    | -50°C                                                                                               | 76 |

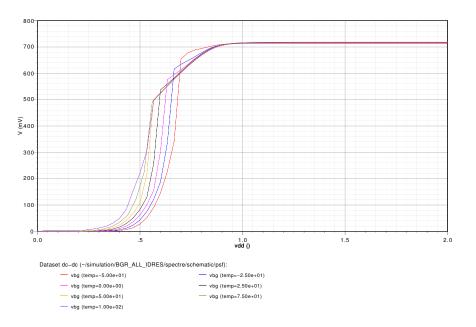

| 60 | Reference voltage $V_{ref}$ vs. supply voltage (0-2V), for various                                  |    |

|    | temperatures $(-50, -25, 0, 25, 50, 75, 100 ^{\circ}\text{C})$                                      | 76 |

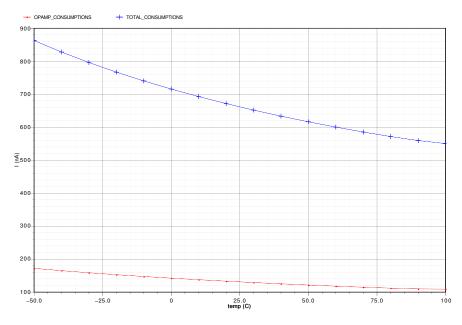

| 61 | BGR current consumption and OTA consumption vs. tem-                                                |    |

|    | perature (-50-100°C) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 77 |

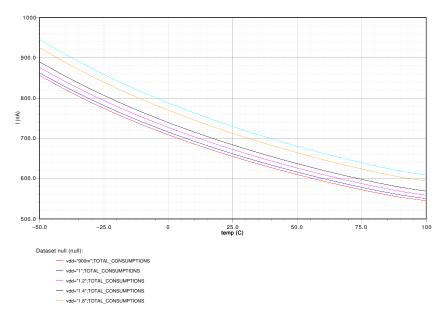

| 62 | BGR current consumption vs. temperature (-50-100°C), for                                            |    |

|    | various power supply $(0.9, 1.0, 1.2, 1.4, 1.8, 2.0V)$                                              | 77 |

|    |                                                                                                     |    |

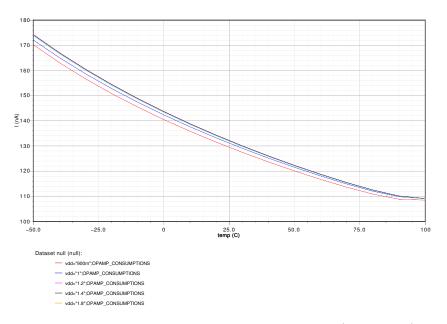

| 63 | OTA current consumption vs. temperature (-50-100 $^{\circ}$ C), for                                    |    |

|----|--------------------------------------------------------------------------------------------------------|----|

|    | various power supply $(0.9, 1.0, 1.2, 1.4, 1.8, 2.0V)$                                                 | 78 |

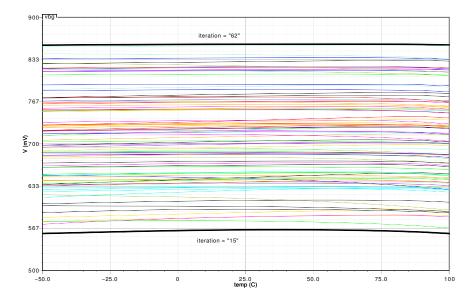

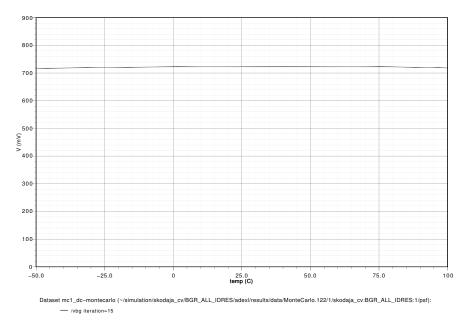

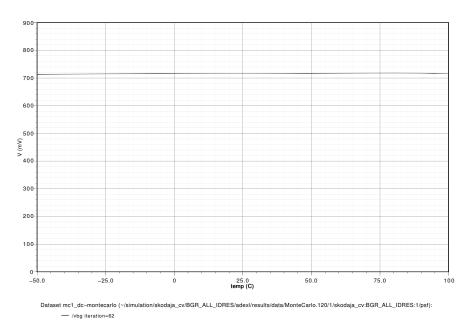

| 64 | Reference voltage $V_{ref}$ vs. temperature (-50-100°C), Monte                                         |    |

|    | Carlo 100 runs process and mismatch, worst cases $= 62$ and                                            |    |

|    | 15 iteration $\ldots$ | 79 |

| 65 | Reference voltage $V_{ref}$ vs. temperature (-50-100°C) - trimmed                                      |    |

|    | worst case 15 iteration                                                                                | 79 |

| 66 | Reference voltage $V_{ref}$ vs. temperature (-50-100°C) - trimmed                                      |    |

|    | worst case 62 iteration                                                                                | 80 |

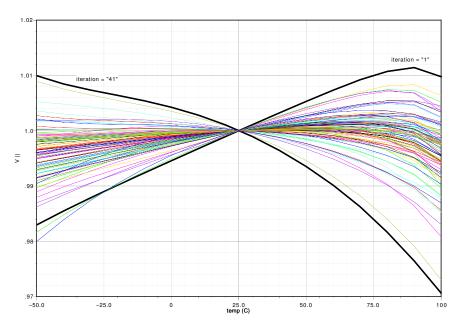

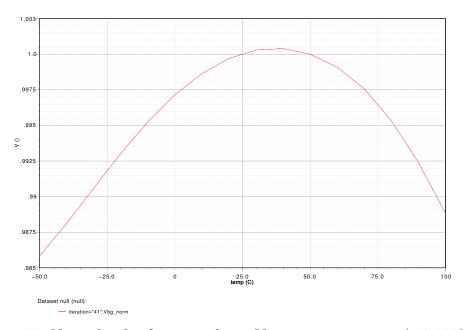

| 67 | Normalized reference voltage $V_{ref}$ vs. temperature (-50-100°C),                                    |    |

|    | Monte Carlo 100 runs process and mismatch, worst cases $=$                                             |    |

|    | 41 and 1 iteration $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 80 |

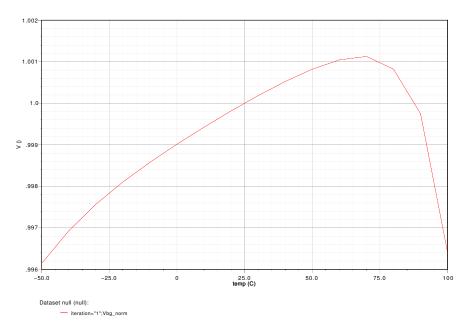

| 68 | Normalized reference voltage $V_{ref}$ vs. temperature (-50-100°C)                                     |    |

|    | - trimmed worst case 1 iteration                                                                       | 81 |

| 69 | Normalized reference voltage $V_{ref}$ vs. temperature (-50-100°C)                                     |    |

|    | - trimmed worst case 41 iteration                                                                      | 81 |

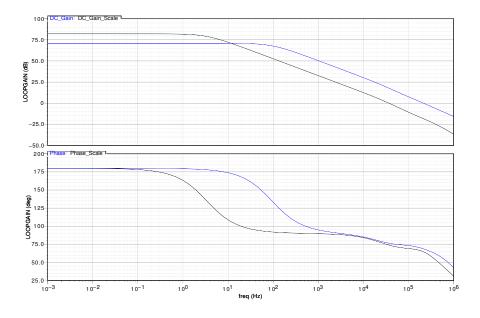

| 70 | BGR AC. simulation, DC gain and phase                                                                  | 82 |

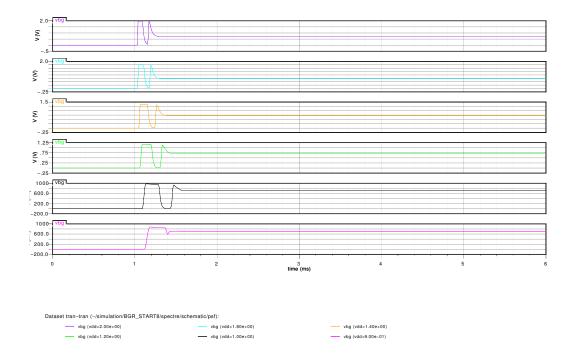

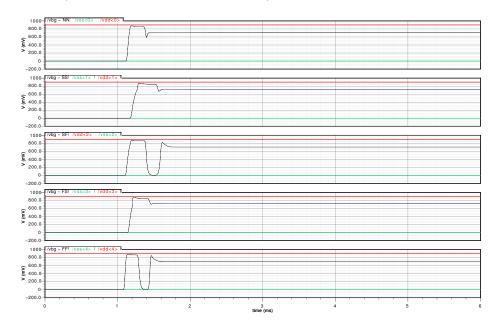

| 71 | Start-up test results, different supply voltage $(0.9V, 1V, 1.2V)$                                     |    |

|    | , 1.4V, 1.8V, 2V), temperature $-50^{\circ}$ C                                                         | 84 |

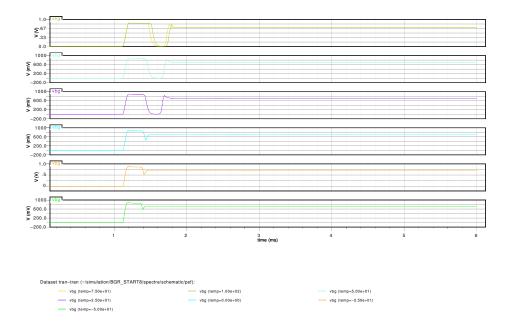

| 72 | Start-up test, worst case (0.9V supply voltage) for various tem-                                       |    |

|    | peratures $(-50, -25, 0, 25, 50, 75, 100 ^{\circ}\text{C})$                                            | 85 |

| 73 | Start-up test, worst case (0.9V supply voltage, -50 °C) for                                            |    |

|    | various technological corners (NN, SS, SF, FS, FF)                                                     | 85 |

|    |                                                                                                        |    |

# List of Tables

| 1 | MOS transistor capacitances                                          | 7  |

|---|----------------------------------------------------------------------|----|

| 2 | Operating regions definition with respect to the IF, [Ste08]         | 11 |

| 3 | BGR core design choice                                               | 44 |

| 4 | OTA Device sizing, scaling factors are 32 (for amplifier) and        |    |

|   | 40 (for bias part) $\ldots$                                          | 65 |

| 5 | OTA Scaling results                                                  | 66 |

| 6 | Start-up device sizing                                               | 73 |

| 7 | AC results of the scaled and unscaled BGR, (NN corner, tem-          |    |

|   | perature $-50^{\circ}$ C, supply voltage 1V)                         | 83 |

| 8 | Scaled BGR AC parameters, tested for various supply voltages         |    |

|   | (0.9, 1.0, 1.2, 1.4, 1.8, 2.0), temperatures $(-50, -25, 0, 25, 50)$ |    |

|   | ,75, 100), technological corners (NN, SS, SF, FS, FF)                | 83 |

| 9 | Performance comparison of low-power BGR                              | 86 |

# Notations

| $A_V$    | Voltage gain                            |

|----------|-----------------------------------------|

| BGR      | Bandgap reference                       |

| BJT      | Bipolar transistor                      |

| Cc       | Compensation capacitance                |

| CMOS     | Complementary metal oxide semiconductor |

| $C_{OX}$ | Silicon oxide capacitance               |

| CTAT     | Complementary to absolute temperature   |

| Ec       | Energy of conduction band               |

| Eg       | Energy bandgap                          |

| Ev       | Energy of valence band                  |

| $I_D$    | Drain current                           |

| IC       | Integrated circuit                      |

| Ic       | Collector current                       |

| IF       | Inversion factor                        |

| Is       | Saturation current                      |

| k        | Boltzmann constant                      |

| L        | Channel length                          |

| MOS      | Metal oxide semiconductor               |

| NMOS     | Negative metal oxide semiconductor      |

| OTA      | Operational transconductance amplifier  |

| PM       | Phase margin                            |

| PMOS     | Positive metal oxide semiconductor      |

|          |                                         |

| PTAT       | Proportional to absolute temperature |

|------------|--------------------------------------|

| T          | Absolute temperature                 |

| TC         | Temperature coefficient              |

| $U_T$      | Thermal voltage                      |

| $V_{be}$   | Base-emitter voltage                 |

| $V_{dd}$   | Positive supply voltage              |

| $V_{DS}$   | Drain-source voltage                 |

| $V_{DSat}$ | Saturation voltage                   |

| $V_{GS}$   | Gate-source voltage                  |

| $V_{OS}$   | Offset voltage                       |

| $V_{ss}$   | Negative supply voltage              |

| $V_{th}$   | Threshold voltage                    |

| $V_{ref}$  | Reference voltage                    |

| W          | Channel width                        |

|            |                                      |

## 1 Introduction

Voltage references are important not only for ADC and DAC or memories. They are the essential part of every chip because circuit needs some biasing that sets proper working conditions.

Requirements of voltage reference are: accurate and constant voltage (independent on temperature and supply voltage) without noise transfer into the system (noiseless), low voltage and low power, preferably independent of the process and mismatch.

It is clear that it is impossible to design circuit with ideal parameters and in the most cases temperature and supply voltage independence are preferred.

Some simple circuits that provide poor voltage reference are later introduced. Despite poor voltage reference accuracy, these circuits can be useful for some applications due to their simplicity. Advanced topology usually exploits thermal voltage or base-emitter voltage etc. They usually contain parasitic diode on that account.

At the beginning the MOS transistor and passive device in CMOS technology are discussed for better insight of complex IC design.

## 2 MOS Transistor

## 2.1 Basic Parameters, Operating Region

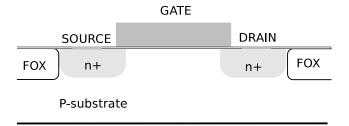

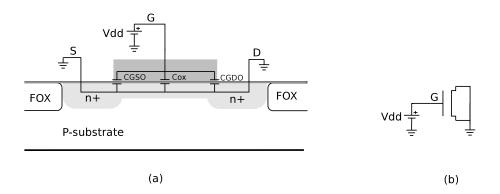

MOS transistor is the four terminal (Gate, Source, Bulk, Drain) non-linear basic device in electronic design. The origin of short-cut MOS is from Metal-Oxide-Semiconductor structure in the transistor where metal creates a gate terminal, oxide forms insulator ( $SiO_2$ ) under the gate terminal and semiconductor is P or N-type substrate. Fig.[1] shows simplified cross-section view of NMOS transistor without the Bulk terminal.

Figure 1: Simplified cross-sectional view of NMOS transistor

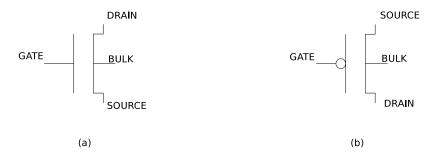

NMOS and PMOS transistors are two basic types of MOS transistor. NMOS transistor has an N-type source and drain area and P-type substrate, while PMOS has P-type source/drain and N-type substrate. Fig.[2] shows basic symbols of NMOS and PMOS transistors. The bulk terminal is connected to the negative supply voltage (often Gnd) in the case of the NMOS, while PMOS transistor has bulk terminal connected to the positive supply voltage (often Vdd).

In the next schematics the bulk terminals are not shown for better readability.

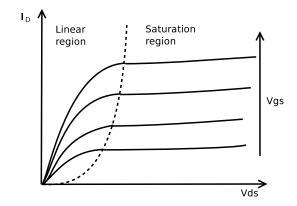

MOS transistor has two operating regions depending on  $V_{DS}$  and  $V_{GS}$  voltage. Linear region and saturation region. Eq.[1] shows condition for each saturation region and Eq.[2] for the linear region. Note that, these equations are valid only for strong inversion.

$$V_{DS} \ge V_{GS} - V_{th} \tag{1}$$

Figure 2: MOS transistor schematic symbols used in the thesis (a) NMOS (b) PMOS

$$V_{DS} \le V_{GS} - V_{th} \tag{2}$$

The behaviour and equation for drain current are different for each region, see Fig.[3]. MOS transistor in the linear region behaves as a resistor, while in the saturation region its behaviour is rather near to a current source. Eq.[3] defines drain current in the saturation region and Eg.[4] in the linear region.

$$I_D = \frac{\beta}{2} (V_{GS} - V_{th})^2 = \frac{1}{2} K' \frac{W_{ef}}{L_{ef}} (V_{GS} - V_{th})^2$$

(3)

$$I_{D} = \beta \left[ (V_{GS} - V_{th}) - \frac{V_{DS}}{2} \right] V_{DS} = K' \frac{W_{ef}}{L_{ef}} \left[ (V_{GS} - V_{th}) - \frac{V_{DS}}{2} \right] V_{DS} \quad (4)$$

where

$$\begin{split} I_D &= \text{drain current} \\ \beta &= K' \frac{W_{ef}}{L_{ef}} \text{ - transconductance parameter} \\ W_{ef}, L_{ef} &= \text{effective channel width and length} \\ K' &= \mu_0 C_{ox} \text{ - technological constant} \\ V_{th} &= \text{threshold voltage} \\ V_{DS}, V_{GS} &= \text{drain-source and gate-source voltage} \end{split}$$

Figure 3: NMOS transistor, output characteristic

### 2.2 Large and Small Signal Model

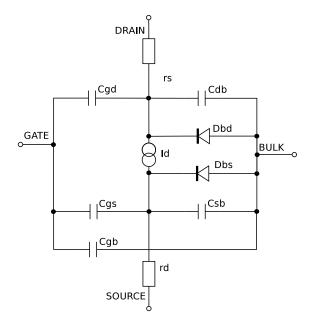

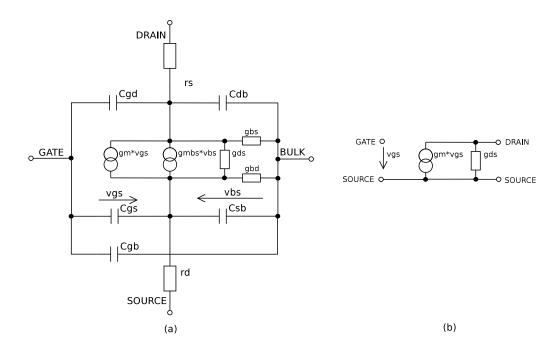

The large signal model is important for determination of operation region. Drain current and saturation voltage can be calculated from it. This model is shown on Fig.[4]. It contains four terminals (Gate, Source, Drain and Bulk) and current source  $I_D$ . There are other devices in the large signal model. For instance, capacitances (Cgs, Cgd, Cgb, Cdb, Csb), substrate diodes (Dbd, Dbs) and serial resistances rs,rd. All these devices are parasitic. Ideally, only voltage control current source is present.

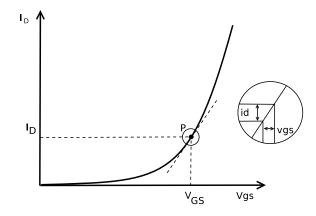

As mentioned before, MOS transistor is the non-linear device. Therefore, the large signal model is also non-linear. Small-signal model is needed for obtaining the linear characteristic/function. Simply, it is linearisation of the large-signal model in the specific operating point. Due to the linear function all parameters calculations are easier. Fig.[5] shows the principle of smallsignal model. MOS transistor is biased by the DC gate-source voltage  $V_{GS}$ to the proper value of DC drain current  $I_D$ . In this operating point, an AC gate-source signal voltage  $v_{gs}$  is applied. The small-signal  $v_{gs}$  voltage causes change in the small-signal drain current  $i_d$ . As Fig.[5] shows, the small-signal variations are linear if the following conditions are valid (i.e  $|v_{gs}| \ll V_{GS}$  and  $|i_d| \ll I_D$ ).

Fig.[6(a)] shows the small-signal model. The most important parameter is transconductance  $g_m$ . This parameter relates to the small-signal gate voltage  $v_{gs}$  and to the small-signal drain current  $i_d$  as Eq.[5] shows. Other

Figure 4: Large signal model, [All02]

Figure 5: Small signal model explanation

transconductance is a  $g_{mbs}$ .

$$i_d = g_m \cdot v_{gs} \tag{5}$$

Model also contains capacitances from the large-signal model and three conductances  $g_{DS}$ ,  $g_{BD}$ ,  $g_{BS}$ . The conductance  $g_{DS}$  is a conduction of the channel and it is also an important small-signal parameter. The last two conductances represent conduction of parasitic substrate diodes. These diodes are usually off and therefore these conductivities  $(g_{BD}, g_{BS})$  are often neglected. Fig.[6(b)] shows simplified small-signal model.

Figure 6: Small signal models (a) Full (b) Simplified, [All02]

The previous mentioned small-signal parameters can be calculated by Eq.[6,7,8]

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \tag{6}$$

$$g_{DS} = \frac{\partial I_D}{\partial V_{DS}} \tag{7}$$

$$g_{mbs} = \frac{\partial I_D}{\partial V_{BS}} \tag{8}$$

These parameters are valid only at given operating point and at its close vicinity. The following equations show the basic relations for the small-signal parameters in the linear (9,11) and in the saturation region (10,12). Note that strong inversion is assumed.

$$g_m = \beta V_{DS} \tag{9}$$

$$g_m = \frac{2I_D}{(V_{GS} - V_{th})}\tag{10}$$

$$g_{DS} = \beta ((V_{GS} - V_{th}) - V_{DS})$$

(11)

$$g_{DS} = \lambda I_D \tag{12}$$

## 2.3 MOS Capacitances Summary

Capacitances Csb and Cdb are the reversed biased junction capacitances. More about behaviour of junction capacitance can be found in the chapter 3.2.3.

The main three capacitances are Cgs, Cdb and Cgd. These capacitances are given by the overlap capacitance ( $C_{GDO}$ ,  $C_{GBO}$  or  $C_{GSO}$ ) and by the part of gate capacitance  $C'_{ox}$  (it is a capacitance between the gate and the channel). Note that a shape of the channel is not constant, it depends on  $V_{DS}$  and  $V_{GS}$ . Thus the value of capacitances Cgs, Cdb and Cgd are determined by the operating region. Table [1] lists the values of mentioned capacitances.

| Name | Off                          | Triode                 | Saturation                               |

|------|------------------------------|------------------------|------------------------------------------|

| Cgd  | $C_{GDO} \cdot W$            | $\frac{1}{2}WLC'_{ox}$ | $C_{GDO}$ · W                            |

| Cgb  | $C_{ox}WL + C_{GBO} \cdot L$ | $C_{GBO}$ ·L           | $C_{GBO}$ · L                            |

| Cgs  | $C_{GSO}$ ·W                 | $\frac{1}{2}WLC'_{ox}$ | $\frac{2}{3}WLC'_{ox} + C_{GSO} \cdot W$ |

Table 1: MOS transistor capacitances

### 2.4 Threshold Voltage and Body Effect

In the previous chapters it is assumed that MOS transistor is turned on. The threshold voltage  $V_{th}$  is applied to the gate terminal for keeping MOS transistor turned on.

The definition of threshold voltage is complex and the concrete value depends on many factors (thickness of gate oxide  $t_{ox}$ , substrate doping level, temperature etc.). Moreover the threshold voltage value depends on the bulk-source voltage  $V_{BS}$ .

The threshold voltage extraction can be described by several methods: Constant current method, Second derivative method, Extrapolation in the linear region method (ELR) etc...

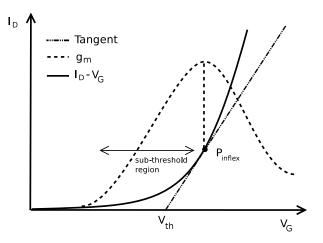

According to the ELR method, the threshold voltage is found at the intercept of the tangent in the inflexion point with the  $V_G$  axis, [DPDR00]. The inflexion point  $P_{inflex}$  is the point where the transconductance  $g_m$  reaches its maximum. This method assumes NMOS with the source and bulk connected to the ground (therefore the  $I_D$ - $V_G$  plot is used instead of the  $I_D$ - $V_{GS}$ ). Moreover this method neglects the parasitic series resistances and mobility degradation.

Figure 7: The  $V_{th}$  extraction, ELR method

From Fig.[7] is clear that some drain current flows under the threshold voltage. This operating area is called sub-threshold or weak-inversion region, see next sub-chapter for more information. Applying a gate-source voltage

$V_{GS} \leq V_{th}$  to the gate terminal, the sub-threshold region can be achieved. Thus only a small number of electrons is attracted under the gate oxide.

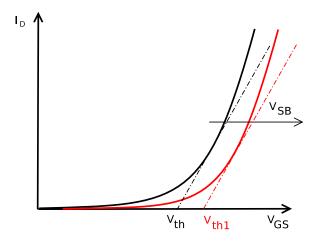

As mentioned before, the threshold voltage  $V_{th}$  depends on the voltage  $V_{BS}$ . If the source and bulk are not at the same potential then a Body effect occurs. The Body effect is usually unwanted phenomenon that simply steals some electrons from the channel. Thus the threshold voltage rises and the drain current  $I_D$  decreases (for constant  $V_{GS}$ ), see Fig.[8].

Figure 8:  $I_D$ - $V_{GS}$  relation with marked threshold voltage

Eq.[13] describes influence of  $V_{BS}$  on the threshold  $V_{th}$ , [Bak10].

$$V_{th} = V_{th0} + \gamma \left( \sqrt{|2\phi_f| + V_{SB}} - \sqrt{|2\phi_f|} \right)$$

(13)

where,

$V_{th0}$  = zero-bias threshold voltage  $2\phi_f$  = flatband voltage - constant  $V_{SB}$  = source-bulk voltage  $\gamma$  = body factor

The body factor  $\gamma$  and the flatband voltage  $2\phi_f$  are (for simplicity) considered as a constants.

## 2.5 MOS Transistor Inversion Level

As mentioned before MOS transistor has basically two operating regions (linear, saturation region) depending on voltages  $V_{GS}$  and  $V_{DS}$ . This approximation is sufficient for some design approaches. But for micro-power design it is not.

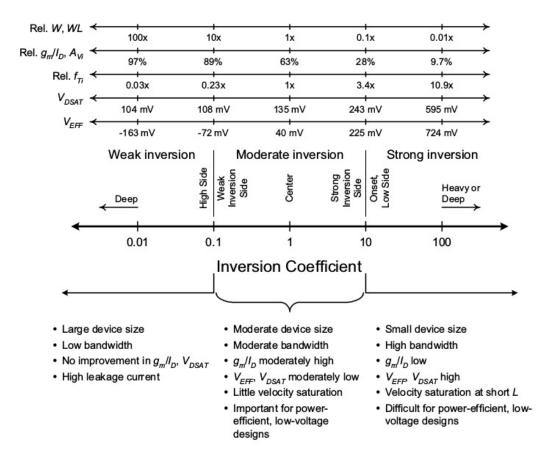

Therefore the saturation region is divided into next three operating levels, [Ste08]: Weak inversion, Moderate inversion and Strong inversion. This three operating levels depend on the  $V_{GS}$  voltage and they are significant for modern low-power integrated circuit design.

The exact definitions of these region are based on: surface potential  $\psi_s$ , pinch-off voltage  $V_p$ , Inversion charge  $Q_{inv}$  and depletion charge  $Q_{dep}$ . It is clear that the definition is very complex and unfortunately the exact explanation of this matter is beyond the scope of this work.

The inversion level can be estimated by the  $V_{GS} - V_{th}$  value, [SW94].

Weak inversion:  $V_{GS} - V_{th} < -50mV$ Moderate inversion:  $-50mV < V_{GS} - V_{th} < 250mV$

Strong inversion:  $250mV < V_{GS} - V_{th}$

To find out how much the transistor is in the concrete inversion, the inversion factor IF is defined, [Ste08].

$$IF = \frac{I_{DSat}}{I_s} = ln^2 \left[ 1 + exp\left(\frac{V_p - V_s}{2U_T}\right) \right]$$

(14)

where

$I_{DSat} =$ saturation drain current

$I_s =$ Specific current

$V_p = \text{pinch-off voltage}$

$V_s =$ local voltage at source end of channel

The following table defines the relation between the inversion level and inversion factor IF.

| Weak Inversion     | IF < 0.1      |

|--------------------|---------------|

| Moderate Inversion | 0.1 < IF < 10 |

| Strong Inversion   | 10 < IF       |

Table 2: Operating regions definition with respect to the IF, [Ste08]

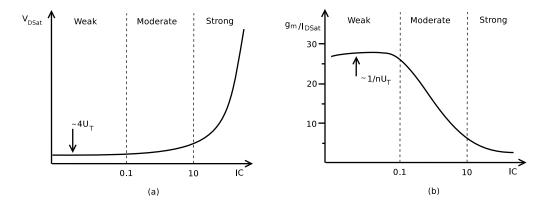

Figure 9:  $V_{DSat}$  and  $g_m/I_D$  parameters as a function of IF, [Ste08]

The following Fig.[9] shows two important MOS parameters (saturation voltage and  $g_m/I_D$  ratio) as a function of IF.

The saturation voltage  $V_{DSat}$  is the required voltage across drain-source terminal to keep it saturated. This parameter is often required to be low for better headroom. From Fig.[9(a)] is clear that minimum  $V_{DSat}$  is obtained in weak inversion and it is roughly equal to  $V_{DSat,min} \simeq 4U_T$ .

The headroom is the difference between  $V_{DS}$  and  $V_{DSat}$ . For instance, assume that NMOS transistor has a  $V_{DSat} = 140mV$  and  $V_{DS} = 180mV$ . The  $V_{DS}$  can be reduced by roughly 40mV till the MOS transistor is still in saturation region. This voltage reserve is called Headroom.

The  $g_m/I_D$  is a very important parameter because it shows the transconductance efficiency, see Fig.[9(b)]. The maximum is reached at weak inversion  $g_m/I_D \simeq 25$  (the maximum value depends on *n* which is technology parameter). The minimal value is reached in strong inversion.

On the other hand strong inversion provides the small device size and high bandwidth. This design tradeoffs are summarized by Fig.[10].

The IF factor is unique because all important parameters : saturation voltage  $V_{DSat}$ ,  $g_m/I_D$  ratio, output conductance  $g_{DS}$ , capacitances (in saturation region), intrinsic gain, transition frequency and noise can be directly calculated as a function of IF, [Ste08].

Thus the new design methodology called  $g_m/I_D$  is used. Possible design approach provides three degrees of freedom in design: drain current  $I_D$ , inversion factor IF and transistor length L.

The maximum current condition and designer choice set the drain current of each transistor. The IF factor is than chosen accordingly to required MOS performance. The following Eq.[15] gives than the W/L ratio <sup>1</sup>.

$$\frac{W}{L} = \frac{1}{IF} \frac{I_D}{I_s} \tag{15}$$

The last design step is the MOS length L choice. This choice is trade-off between high DC gain on one side and area, stability and speed on the other side. After this step the MOS width W is easily calculated.

<sup>&</sup>lt;sup>1</sup>The W/L ratio is often called an aspect ratio AR

Figure 10: Design tradeoffs as a function of IF, [BFJ<sup>+</sup>07]

## **3** Passive Devices

Fundamental passive devices are presented in this chapter (resistors and capacitors). Quality of passive devices is very important for analog IC design. Passive devices are used for determination of gain, time constant, compensation, current to voltage conversion etc. Low power applications require resistors with a large resistance value. In this case, resistors consume a significant area.

Unfortunately resistors and capacitors in CMOS process have temperature and voltage dependence. Moreover process and mismatch variations cause significant inaccuracy. These effects are presented in the next chapter.

## 3.1 Resistor

### 3.1.1 Sheet Resistance

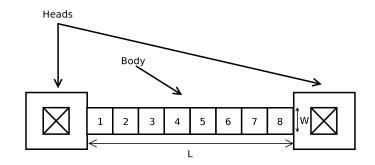

Generally, resistors are made of resistance body and heads, see Fig[11]. That is why the total resistance can be expressed by Eq.[16] and square resistance by Eq.[17]

$$R = 2R_{head} + R_{sqr} \frac{L}{W} \tag{16}$$

$$R_{sqr} = \rho/t \tag{17}$$

where

$R_{head}$  = head resistance W = body width L = body length  $\rho$  = material resistance t = thickness of square layer

Figure 11: A simple resistor layout

#### 3.1.2 Poly-Silicon Resistor

Poly-si (ie. poly crystal) is the most used type of resistor. The poly-si resistor can be manufactured with or without silicide layer. This layer is a mix of metal and silicon and it has better conduction ability. Silicide poly-si resistor has therefore generally smaller sheet resistance than non-silicide.

For instance, silicide poly-si in our process design kit (PDK-180 nm technology) has resistance about tens of ohm/square while non-silicide has about 200 ohm/square. Poly-si resistor is made of strip of resistive poly crystal material. Width and length of the strip can be calculated from final device resistance and sheet resistance.

Figure 12: A first order Poly-Si resistor model (Cross section)

From the picture above is clear that this strip structure has parasitic capacitances to the silicon substrate. These parasitic capacitances are distributed along the strip but for simplicity assume the first-order model that splits the total parasitic capacitance into two capacitors C1 and C2 see Fig.[12]

There are many types of resistor layout (meander, dog bone etc...). These layout technique should minimize impact of fabrication process.

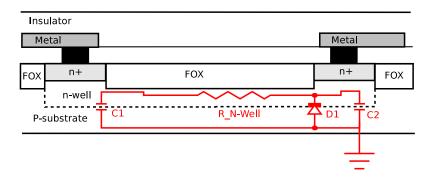

### 3.1.3 N-Well Resistor

This type of resistor is made by P or N lightly doped diffusion area and two contacts. This n-well resistor has sheet resistance 10-100 ohm/square depending on the dopant concentration. Unfortunately, a parasitic diode D1 (pn junction) is presented in this structure. Attention to correctly polarized pn junction must be paid.

Figure 13: N-well resistor without depletion layer (Cross section)

For simplicity, the first-order model can be also used, see Fig.[13]. However, the parasitic capacitors C1,C2 are junction capacitances and therefore their values depend on the voltage across the resistor. So the total capacitance can change due to the voltage. Moreover width of the depletion region is voltage dependent, so the total resistance of diffusion resistor is nonlinear. These negatives can be problematic for analog design, where constant resistance and capacitance values are generally required.

#### 3.1.4 MOS Resistor

The third method to realize resistor on chip is due to the MOS transistor operating in triode region. Assuming NMOS transistor the following condition must be set in order to achieve triode region, see Eg.[18]

$$V_{DS} = \langle V_{GS} - V_{th} \tag{18}$$

Figure 14: NMOS transistor, output characteristic

The resistance of mosfet resistor is calculated by Eq.[19], [All02].

$$rds = \frac{1}{(\mu_0 C_{ox}(W/L)(V_{GS} - V_{th}))}$$

(19)

where

$\mu_0 = \text{carrier mobility}$   $C_{ox} = \text{oxide capacitance}$  W/L = geometric size of transistor channel (width and length)

Eq.[19] shows that resistance of triode NMOS transistor can be tuned by the gate-source voltage  $V_{GS}$  which is indeed an important advantage. Second advantage is a possibility of a large resistance value in the compact area.

On the other hand, non-linearity is a disadvantage of MOS resistor.

## 3.2 Capacitors

In this section three basic capacitor types are presented: metal-metal capacitor, pn junction capacitor and MOS capacitor. Capacitors have important role in the analog circuit design. They are often used for the signal filtering and for the stability compensation. Capacitors are essential part of charge pump and dynamic random access memory (DRAM) circuits.

#### 3.2.1 Metal-Metal Capacitor

Assuming a simple plate capacitor that contains two parallel plates and dielectric material between them, Eq.[20] gives the total capacitance.

$$C = \varepsilon_{ox} \left(\frac{S}{t_{ox}}\right) \tag{20}$$

where

$\varepsilon_{ox}$  = permittivity of the insulator between plates S = plate area  $t_{ox}$  = spacing between plates

It is clear from the Eq.[20] that the total capacitance is linear and a big S and  $\varepsilon_{ox}$  or small  $t_{ox}$  are required for the large value of capacitance.

Fortunately metal-metal capacitor can be realized by two plates with dielectric material between them (this structure is called parallel-plate). If the edge and parasitic capacitors are neglected, Eq.[20] is valid. Spacing between plates is in order of  $0.1 - 10\mu m$  (depending on technology), [Car12]. Silicon dioxide (SiO<sub>2</sub>) is often used as dielectric material with  $\varepsilon_{ox} \cong 3.9\varepsilon_{o}$ , [Car12].

Fig.[15] show poly-poly capacitor Cpp with parasitic capacitances Cp. The most important parasitic capacitance Cbp is formed between the bottom plate of poly layer and the substrate. Therefore it is called bottom plate parasitic capacitance. It is clear that value of bottom plate parasitic capacitance can be large due to the large plate area.

The parallel-plate structure can be made of different elements, for instance by metal-metal, metal-substrate, metal-diffusion area, poly-poly, polymetal etc...

Figure 15: Poly-poly capacitor with parasitic capacitances (Cross section)

#### 3.2.2 Pn Junction Capacitor

Reverse-biased pn junction has a charge-storage effect that is represented by the junction capacitor  $C_j$ . This junction capacitor  $C_j$  is formed by a bottom capacitor and a sidewall capacitor. Behaviour of the junction capacitor is given by Eq.[21], [All02].

$$C_j = \frac{C_{jb}}{(1 + \frac{V_R}{\Phi_0})^{m_j}} + \frac{C_{jsw}}{(1 + \frac{V_R}{\Phi_{0S}})^{m_{jsw}}}$$

(21)

where

$C_{jb}, C_{jsw}$ = zero-bias bottom pn capacitance for bottom, sidewall  $\Phi_O, \Phi_{OS}$ = pn build potential for bottom, sidewall  $m_j, m_{jsw}$ = pn grading coefficient for bottom, sidewall  $V_R$ = applied reverse voltage

Pn junction capacitor provides large value of capacitance because depletion region can be thin and its relative permittivity is high ( $\varepsilon_r = 11.8$ ), [Car12]. Furthermore, it is obvious from the Eq.[21] that the junction capacitance can be tuned by reverse voltage  $V_R$  across it. This feature is often used for oscillators and radio-frequency applications.

Voltage dependence is not required in some applications. The next disadvantage is capacitance dependence on dopant concentration, which is difficult controlled. Furthermore, leakage current through junction capacitor can be problematic.

#### 3.2.3 MOS Capacitor

As mentioned in Eq.[20], larger capacitance value can be achieved by thin dielectric material  $t_{ox}$ . Gate oxide of the MOS transistor is the thinnest layer in CMOS process, [Car12]. Therefore MOS capacitor provides a good ratio of capacitance/area.

Assume NMOS transistor now, if the positive voltage Vdd is applied to the gate electrode, a conductive channel is formed by attracted electrons. This channel creates with gate electrode plates of gate capacitor and gate oxide is a dielectric.

If source, drain and bulk are connected together, MOS transistor works as the capacitor, see Fig.[16]. Eq.[22] shows gate capacitance (sometimes called oxide capacitance).

Figure 16: (a) NMOS capacitor (Cross section), (b) NMOS cap. symbol

$$C_{ox} = W_{ef} L_{ef} \frac{\varepsilon_{ox}}{t_{ox}} = W_{ef} L_{ef} C'_{ox}$$

(22)

where

$W_{ef}L_{ef}$  = effective geometrical size of channel  $C'_{ox}$  = gate capacitance per area unit

Fig.[16] also shows next two capacitors  $C_{GDO}$  and  $C_{GSO}$ . These two capacitors are called overlap capacitances and they are formed by inaccuracy of diffusion process (expansion of source and drain area under gate).

$$C_{GDO} = C_{GSO} = C'_{ox} L_{diff} \tag{23}$$

where  $L_{diff}$  is a length of overlapped area.

The total capacitance of MOS capacitor is given by Eq.[24]

$$C_{MOS} = W_{ef} L_{ef} C'_{ox} + 2W_{ef} L_{diff} C'_{ox}$$

$$\tag{24}$$

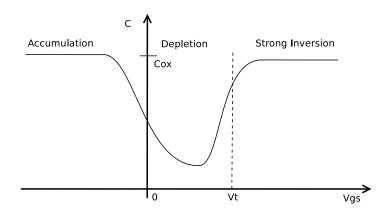

Unfortunately, gate capacitance  $C'_{ox}$  is dependent on voltage  $V_{GS}$  and it is not linear. Of course some minimal  $V_{GS,min}$  voltage needs to be ensured for proper work of MOS capacitor, see Fig.[17].

Figure 17: The variation of the gate capacitance with  $V_{GS}$  voltage

Note that MOS capacitor can operate in three regions: accumulation, depletion and strong inversion. These three regions are now discussed for NMOS transistor.

In accumulation region a negative voltage is applied on the gate. Thus mobile holes are attracted (accumulated) under the gate oxide. Capacitor is formed between gate electrode and substrate electrode. Unfortunately serial resistance is present and that is why accumulation region is not convenient choice for MOS capacitor.

If the gate voltage  $V_{GS}$  (smaller than threshold voltage  $V_{th}$ ) is applied, only a small number of electrons are attracted. Now, the area under the gate is said to be nearly depleted. It means depleted of free electrons and holes. From Fig.[17] is clear that total capacitance of MOS capacitor in depletion region (weak inversion) is small.

The last region is the suitable choice for MOS capacitor. Due to the large positive gate voltage a large number of electrons are attracted. Thus the area under gate oxide is no longer p-type but n-type. Moreover the parasitic serial resistance is smaller than in the accumulation region.

## 4 Voltage References

Voltage reference is a circuit that generates a specific output voltage. This output voltage should not depend on the load current, supply voltage, temperature, time or process corner. As mentioned before the voltage reference is essential component for ADC/DAC, memory and for circuit biasing. Thus it can be said that every complex integrated circuit (digital meters, smart sensors, threshold detectors, battery management systems etc..) needs some kind of voltage reference.

Before some voltage reference are presented, the temperature coefficient is introduced.

Temperature coefficient (TC) is an important parameter of a component that should be considered during the electronic design. TC describes the relationship between a change of parameter as a function of temperature.

With usage of Taylor polynom most of these functions can be expressed as follows:

$$\rho(T) = \rho(T_0) \left( 1 + \alpha(\Delta T) + \beta(\Delta T)^2 + \gamma(\Delta T)^3 + \dots \right)$$

(25)

where

$\Delta T$  = difference between temperature T and nominal temperature  $T_0$   $\rho(T_0)$  = parameter  $\rho$  at temperature  $T_0$  $\alpha, \beta, \gamma$  = are temperature coefficients

If TC coefficients of higher order  $(\beta, \gamma,...)$  are negligible then we can consider the dependency to be linear. The Eq.[25] can then be written as:

$$\rho(T) = \rho(T_0) \left(1 + \alpha(\Delta T)\right) \tag{26}$$

It's clear that the parameter  $\alpha$  describes the general tendency of the relationship.

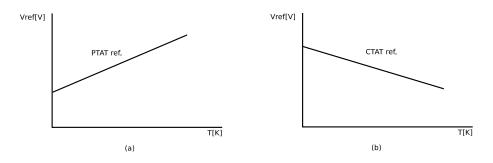

For example, if the parameter  $\rho$  is the reference voltage  $V_{ref}$  and  $\alpha$  is greater than zero then the value of  $V_{ref}$  increases with temperature. This phenomenon is called PTAT (Proportional To Absolute Temperature), see Fig.[18(a)]. If the  $\alpha$  is smaller than zero then the  $V_{ref}$  decreases with temperature and it is called CTAT (Complementary To Absolute Temperature), see Fig.[18(b)].

Figure 18: (a) PTAT and (b) CTAT voltage references

In next section PTAT and CTAT system are shown.

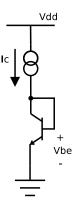

#### 4.0.4 CTAT

Simple diode is used in order to generate CTAT TC. Diode or bipolar transistor can be used to obtain pn junction/diode. NPN transistor in Fig.[19] has base and collector connected.

In this configuration the base-emitter junction is exploited to obtain a diode. If positive voltage is applied to pn junction, forward biased region is entered. Relationship between I-V is approximated by Eq.[27] called Shockley's equation.

$$I = I_s \cdot exp\left(\frac{V}{nU_T} - 1\right) \tag{27}$$

where

n = material coefficient and its value is about 1.05 - 1.1. For simplicity, this coefficient is often considered to be equal to 1.  $U_T =$  thermal voltage, given by Eq.[28]

Figure 19: CTAT voltage realization

$I_s$  = saturation current, its value is in range  $10^{-12} - 10^{-18}$  [Sed13].

$$U_T = kT/q \approx 26mV/K \qquad T = 300K \tag{28}$$

where

k = Boltzmann's constant = 1.38e-23 J/K

T = the absolute temperature in Kelvins = 273 + temperature in °C

q = the magnitude of elementary electron charge = 1.60e-19 C

It can be derived, [Sed13]:

$$\partial V be / \partial T \cong -2mV/K$$

(29)

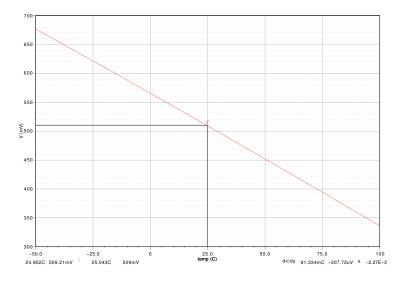

The temperature behaviour of diode connected bipolar transistor (i.e transistor with shorted base and collector, see Fig.[19]) was simulated. The  $\partial Vbe/\partial T$  of NPN (Area=0.36 $\mu m^2$ , 180nm PDK) is -2.27mV/K at room temperature, see simulation result Fig.[20].

Figure 20: Temperature behaviour of the diode

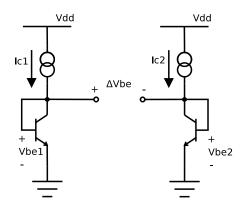

## 4.0.5 PTAT

Fig.[21] shows topology that provides PTAT TC. Assuming two identical NPN bipolar transistors Q1 and Q2, each one has a different DC bias current. Their base and collector are connected and thus they behave like a diode. Eq.[30] is simplified Shockley's equations and it describes current through diode and from the same equation voltage  $V_{be}$  is expressed by Eq.[31].

$$I_c = I_s \cdot exp(V_{be}/U_T) \tag{30}$$

$$V_{be} = \frac{kT}{q} \cdot \ln(I_c/I_s) \tag{31}$$

Eq.[32,33] show voltage across these two BJTs

$$V_{be1} = U_T \cdot ln(I_{c1}/I_s)$$

(32)

$$V_{be2} = U_T \cdot \ln(I_{c2}/I_s) \tag{33}$$

$$\Delta V_{be} = V_{be2} - V_{be1} = U_T \cdot \ln(I_{c2}/I_{c1}) \tag{34}$$

Figure 21: PTAT voltage realization

Eq.[34] shows that  $\Delta V_{be}$  includes thermal voltage  $U_T$  and from Eq.[31] it is evident that this expression is rising with temperature  $(U_T = kT/q)$ . Therefore  $\Delta V_{be}$  is rising with temperature and  $\Delta V_{be}$  is PTAT. Next term  $ln(I_{c2}/I_{c1})$  is a design choice of different currents. The same circuit can be build with the same currents  $I_{c1} = I_{c2}$  and use different area of pn junction. Or both principles together can be used, i.e. different current and area. Eq.[35] shows  $\Delta V_{be}$  relation expressed by the current density  $J_c$ .

$$\Delta V_{be} = V_{be2} - V_{be1} = U_T \cdot \ln(J_{c2}/J_{c1}) \tag{35}$$

Advanced topologies of voltage references are usually based on one of the previous mentioned phenomenons. Therefore they are PTAT or CTAT systems. Unfortunately TC is not sufficiently small for many applications and therefore bandgap reference (BGR) is used. The BGR combines PTAT and CTAT to achieve almost zero TC.

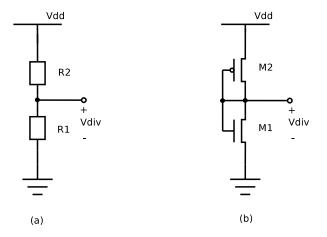

#### 4.0.6 Simple Type Reference

**Voltage divider.** A well know discrete form of voltage divider uses resistors, Fig.[22(a)], or capacitors. The voltage divider formed with resistors has the advantage of simplicity and temperature insensitivity but supply dependence and the power dissipation are a problem. Large resistors are required to minimize current through the resistor divider.

Voltage divider formed with MOS transistor is more space efficient and its behaviour is better described (BSIM3V3 or EKV model describe transistor).

Figure 22: (a) resistor only divider, (b) MOS only divider

The MOS-only divider generates a fraction of the supply voltage. If the PMOS and NMOS transistor have the same drain current  $I_{D1} = I_{D2}$  then Eq.[36] is valid.

$$\frac{\beta_1}{2}(V_{div} - V_{thn})^2 = \frac{\beta_2}{2}(V_{dd} - V_{div} - V_{thp})^2 \tag{36}$$

Output voltage  $v_{div}$  can be then expressed by Eq.[37]

$$V_{div} = \frac{V_{dd} - V_{thp} + \sqrt{\frac{\beta_1}{\beta_2}} V_{thn}}{\sqrt{\frac{\beta_1}{\beta_2}} + 1}$$

(37)

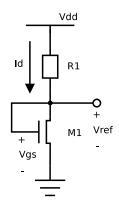

Voltage reference MOS-Resistor. Fig.[23] shows the simple voltage reference made by resistor and diode connected MOS transistor (diode connection guarantee the saturation region). The reference voltage  $V_{ref}$  is equal to the voltage  $V_{GS}$  of the MOS transistor M1.

$$I_D = \frac{V_{dd} - V_{ref}}{R_1} = \frac{\beta}{2} (V_{ref} - V_{thn})^2$$

(38)

$$V_{ref} = V_{thn} + \sqrt{\frac{2I_D}{\beta}} \tag{39}$$

Figure 23: MOS-resistor voltage reference

Eq.[38,39] describes mentioned circuit.

### 4.0.7 Advanced Reference Topology

Voltage reference is used to set proper bias point in many cases. Therefore, the more precise reference the better choice. These advanced references are based on one of the following effects.

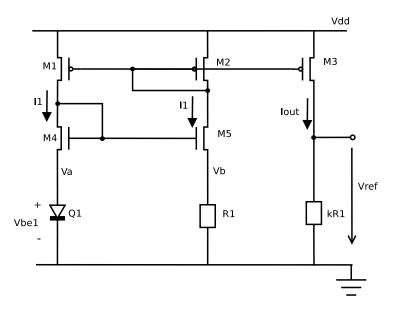

Voltage reference based on Vbe, [DB11]. Voltage on forward polarized diode is about 0.7 V (it depends on temperature and current density). Due to MOS transistors M4, M5 diode voltage is repeated on resistor R1, see Fig.[24]. The current I1 through resistor R1 is defined by Eg.[40]. This current is mirrored by PMOS mirror M2-M3 into the output branch. On the output resistor kR1 reference voltage  $V_{ref}$  is generated and it is described by Eq.[41]

$$I_1 = \frac{V_{be1}}{R_1} \tag{40}$$

$$V_{ref} = kR_1 I_{out} = kR_1 \frac{(W/L)_3}{(W/L)_2} I_1 = k \frac{(W/L)_3}{(W/L)_2} V_{be}$$

(41)

Figure 24: Voltage reference exploiting  $V_{be}$

The reference voltage  $V_{ref}$  can be tuned by multiplying factors k and  $\frac{(W/L)_3}{(W/L)_2}$ .

Temperature behaviour of diode forward voltage can be estimated as -2mV/K and it is CTAT. Temperature on chip can rapidly change due to a chip self-heating. Of course, an ambient contribution is another important factor. Temperature working range might be wide (it depends on application), it is -50 - 100 °C in our case. Voltage reference based on base-emitter voltage  $V_{be}$  has variation about 300mV only due to the diode behaviour. Another temperature dependent devices are not taken into account.

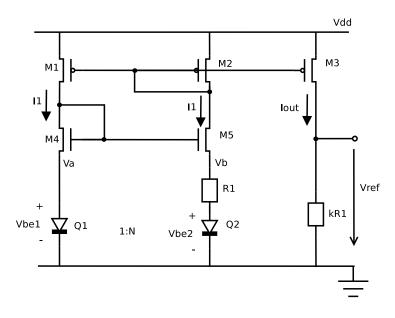

Voltage reference based on Ut, [DB11]. Fig.[25] presents the voltage reference based on thermal voltage  $U_T$ . Note that two diodes Q1 and Q2 have a different area ratio 1 : N. Thus voltage across diodes Q1, Q2 is not equal. Transistors M1, M2, M4 and M5 formed advanced mirror that ensure equality of voltages  $V_a$  and  $V_b$  and current through branches. Therefore voltage drop on resistor R1 obtain the thermal voltage  $U_T$ , as Eq.[42] shows.

$$I_1 = \frac{V_{R1}}{R_1} = \frac{\Delta V_{be}}{R_1} = \frac{U_T}{R_1} ln(N)$$

(42)

Current  $I_1$  is mirrored by MOS transistors M2 and M3 into output branch. The reference voltage  $V_{ref}$  can be expressed by Eq.[43]

$$V_{ref} = kR_1 I_{out} = kR_1 \frac{(W/L)_3}{(W/L)_2} I_1 = kU_T ln(N) \frac{(W/L)_3}{(W/L)_2}$$

(43)

where k and  $\frac{(W/L)_3}{(W/L)_2}$  terms can tune value of output voltage  $V_{ref}$ . Due to the PTAT coefficient in Eq.[43] temperature behaviour of circuit is PTAT.

Figure 25: Voltage reference exploiting  $U_T$

# 4.1 Bandgap Reference (BGR)

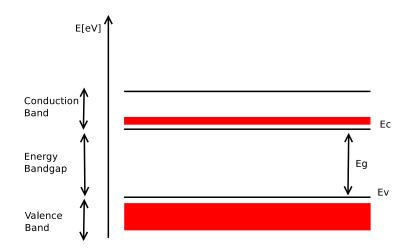

The name Bandgap has originates from the physics nature of the silicon. Fig.[26] shows a simplified energy band diagram of semiconductor, [Bak10].

Figure 26: A simplified energy band diagram

The Ec line indicates bottom edge of the conduction band and Ev is top edge for valence band. The distance between these two bands is the bandgap energy Eg. This bandgap energy decreases as the temperature increases, see Eq.[44],[Bak10].

$$E_g(T) = E_g(0) - \frac{\alpha T^2}{T + \beta}$$

(44)

where  $E_g(0)$ ,  $\alpha$ ,  $\beta$  are fitting parameters for different material (Ge,Si,GaAs). For the silicon and 300K temperature, Eq.[44] can be rewritten as

$$E_g(300) = 1.166 - \frac{0.473 \cdot 10^{-3} \cdot 300^2}{300 + 636} \cong 1.12eV$$

(45)

The result of Eq[45], 1.12eV is an amount of energy that electron needs to overcome gap between the valence and conduction band.

The theoretical output voltage of BGR is also equal to 1.12V, therefore it is called bandgap. BGR is one of the most popular voltage references due to minimized TC. Moreover some current references are based on BGR circuits. After the explanation of BGR function a few implementations of BGR are presented.

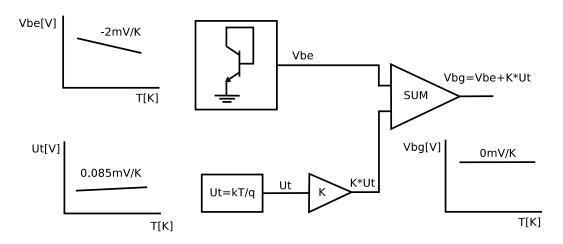

#### 4.1.1 Bandgap Basic Principle

As mentioned before, BGR is a circuit exploiting CTAT and PTAT to compensate temperature dependence.

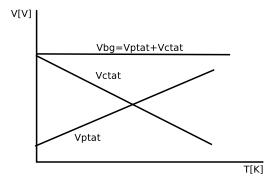

Figure 27: Zero TC due to PTAT and CTAT

As chapter [4.0.5] shows, the thermal voltage  $U_T = kT/q$  has a positive temperature coefficient (PTAT) and it rises by +85uV/K. Voltage baseemitter  $V_{be}$  has a negative temperature coefficient (CTAT) and its drop is about -2mV/K. Ideally a zero TC is achieved by adding these two voltages, see Fig.[27]. It is evident that PTAT and CTAT are different scales, therefore PTAT is multiplied by constant K to ensure their mutual compensation. Then Eq.[46] is valid and it is a basic relation for BGR.

$$V_{bq} = V_{be} + KU_T \tag{46}$$

Fig.[28] shows a principle of ideal BGR reference. Ideal means that output voltage  $V_{bg}$  has zero TC. Unfortunately there are reasons why the zero TC is never obtained. For instance voltage variations of  $V_{be}$  are not linear due to the higher order of TC. Moreover supply voltage  $V_{dd}$  changes, mismatch and process variation have also undesirable effect. Mismatch and process variation are discussed in chapter [5].

Figure 28: Principle of bandgap

# 4.2 Bandgap Basic Topology

# 4.2.1 Voltage Adding Topology

Fig.[29] shows voltage adding BGR topology [All02], that contains a Opamp, diodes, mosfets and resistors.

Assuming ideal Opamp we can write Eq.[47]

$$V_a = V_b = V_{be1} \tag{47}$$

The current  $I_{Rb}$  can be defined by the Eq.[48] below.

$$I_{Rb} = V_{Rb}/R_b = \Delta V_{be}/R_b = U_T \frac{\ln(N)}{R_b}$$

$$\tag{48}$$

Output voltage  $V_{ref}$  can be expressed by adding voltage across resistor  $R_{bg}$  and voltage  $V_b$ , Eq.[49].

$$V_{ref} = V_{rbg} + V_b \tag{49}$$

Voltage  $V_{rbg}$  can be expressed by the following Eq.[50].

$$V_{rbg} = R_{bg}I_{Rb} = R_{bg}\left(U_T \frac{ln(N)}{R_b}\right)$$

(50)

a final relation for  $V_{ref}$  is written Eg.[51].

Figure 29: Voltage summing topology

$$V_{ref} = V_{rbg} + V_b = \frac{R_{bg}}{R_b} (U_T ln(N) + V_{be1})$$

(51)

From Eg.[51] a typical  $PTAT(U_T)$  and  $CTAT(V_{be1})$  terms are expressed. This circuit provides, from its nature,  $V_{bg}$  around 1.12 V and therefore supply voltage cannot be lower than 1.12 V. Due to this limitation, this topology is not suitable for low voltage reference.

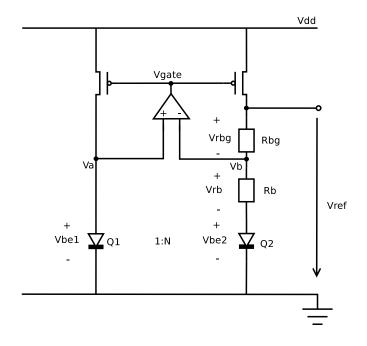

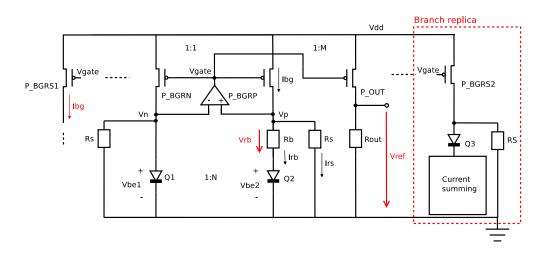

#### 4.2.2 Current Summing Topology

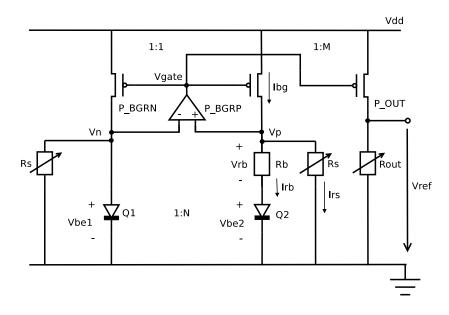

This concept was invented by H. Banba, H. Shiga and collective [BSU<sup>+</sup>04]. The main advantage is sub-1-V operation with selectable output voltage  $V_{bg}$ . Fig.[30] presents this topology.

Voltages  $V_p$  and  $V_n$  are the same due to the Opamp and feedback loop. Feedback loop is made by the PMOS transistor P-BGRN, P-BGRP, which controls currents through branches. Because these PMOS devices have the same  $V_{GS}$  voltage, the currents through branches are the same.

Figure 30: Principle of current Bandgap

From these considerations, the following equations are valid.

$$I_{bg} = I_{rb} + I_{rs} \tag{52}$$

$$V_p = V_n \tag{53}$$

$$V_{ref} = M(R_{out}(I_{rb} + I_{rs})) \tag{54}$$

Currents  $I_{rb}$  and  $I_{rs}$  are expressed by Eq.[55,56]

$$I_{rs} = \frac{V_{be1}}{Rs} \tag{55}$$

$$I_{rb} = \frac{V_{rb}}{R_b} \tag{56}$$

where  $V_{rb}$  is  $\Delta V_{be}$ .

$$V_{rb} = \Delta V_{be} = U_T ln(J_{c2}/J_{c1}) \tag{57}$$

With Eq. [52, 54, 55, 56, 57] a final Eq. [58] for output voltage  $V_{bg}$  is written.

$$V_{ref} = M \frac{R_{out}}{R_s} \left( V_{be1} + \frac{R_s}{R_b} U_T ln(N) \right)$$

(58)

In Eq.[58] the term  $(V_{be1} + \frac{R_s}{R_b}U_T ln(N))$  is bandgap voltage itself. It obtains both PTAT term  $(U_T)$  and CTAT term  $(V_{be1})$  and its value is about 1.12 V as we can see from the voltage adding topology.

Notice that by the resistor ratio  $R_{out}/R_s$  and by the multiple factor M, the output voltage  $V_{ref}$  can be scaled.

The PMOS current mirror is set to saturation region with  $V_{ds}$  voltage about 120-140 mV, the  $V_p$  or  $V_n$  has maximum value about 0.7 V (this voltage is set by diode Q1 in low temperature case). So the current BGR has potential to work at the low supply voltage around 0.85 V. Unfortunately, building a high-gain low-voltage low-offset rail-to-rail Opamp can be quite difficult.

# 5 Offsets and Technology Variations

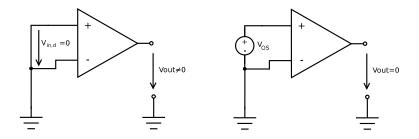

## 5.1 Offset Definition

The zero offset is one of the most wanted attributes of the circuit. Because it can cause large error in high gain Opamp application and it generally limits the precision of the analog design. Let's have a single output Opamp with input terminals tied together. The differential input voltage  $V_{in,d}$  (voltage between the input terminals) is zero and the output voltage should be also zero (according to Eq.[59]).

$$V_{out} = A_V \cdot V_{in,d} \tag{59}$$

Unfortunately, this is not true and therefore  $V_{out} \neq 0$ . The offset voltage can be defined as the differential input voltage  $V_{OS}$  that is required for the zero output voltage, see Fig.[31].

Offset can be divided into systematic offset and random offset. The systematic one is caused by designer.

The random offset is caused by technological variations. It cannot be usually predicted because it is random. Fortunately, statistical result can

Figure 31: Definition of offset

be obtained by Monte Carlo simulation. The technology variations are now introduced.

## 5.2 Technology Variations

Technology variations have significant effect on analog precision and influence device performance. Clearly, geometrical size of manufactured MOS transistor differs from geometrical size of designed transistor (due to many difficult fabrication steps).

These effects can be categorized to process variations and mismatch variations. The process variation is applied on whole wafer, while mismatch variations are applied on each individual device.

#### 5.2.1 Process Variations

There are many sources of process variations, for instance different temperature in fabrication steps, different dopant concentration, different thickness of growing oxide etc.

Several device parameters are used to estimate the impact of process variations. These models are called process corners. Generally slow and fast corner is defined for PMOS and NMOS devices. Junction capacitances and threshold voltage  $V_{th}$  in slow corner case are larger than expected in TT corner (TT corner is a case without any process variations). Therefore digital circuits are slower in slow corner.

On the other hand, fast corner reduces threshold voltage  $V_{th}$  and junction capacitances and that is why the digital devices are faster.

Five corners: SS, SF, FS, FF and TT are presented.

SS (NMOS slow, PMOS slow)SF (NMOS slow, PMOS fast)FS (NMOS fast, PMOS slow)FF (NMOS fast, PMOS fast)TT (NMOS typical, PMOS typical)

Every design should be tested in different corners, temperatures and supply voltages.

#### 5.2.2 Mismatch Variation

As mentioned earlier, process variations are applied on the whole wafer, but mismatch variations are applied on each device. For instance, two identical designed MOS transistors have random differences in their parameters (threshold voltage  $V_{th}$ , body factor  $\gamma$ , technological factor  $\kappa$ , geometrical ratio W/L). These random variations can be established by the Gaussian distribution with an average  $\mu$  and a spreading  $\sigma^2$ . According to Pelgrom's model [PTV98], following Eq.[60,61,62] describes MOS mismatch variance.

$$\sigma^2(V_{th}) = \frac{A_{vth}}{\sqrt{WL}} \tag{60}$$

$$\sigma^2(\kappa) = \frac{A_\kappa}{\sqrt{WL}} \tag{61}$$

$$\sigma^2(\gamma) = \frac{A_\gamma}{\sqrt{WL}} \tag{62}$$

where  $A_{vt}$ ,  $A_{\kappa}$ ,  $A_{\gamma}$  are experimental constants depending on technology. It is clear that WL size must be increased for better matching (i.e. for mismatch variations reduction). Unfortunately, mismatch variations could rise with an improper chip layout. Therefore the following layout techniques should be used. For instance, matching devices should be placed on the same isotherm, thus the temperature difference should be minimized. Matching devices should have the same orientation and optionally the same area ratio. Centroid layout topology or dummy devices should be used for better matching, [SW94].

The main goal of mismatch and process optimization is to make a robust design. If the designed circuit is robust the technology variations does not affected its performance. Moreover the wafer yield is higher. The wafer yield is a number of acceptable chips produced per wafer. It is clear that the higher the wafer yields lead to a higher profit.

# 6 Circuit Design

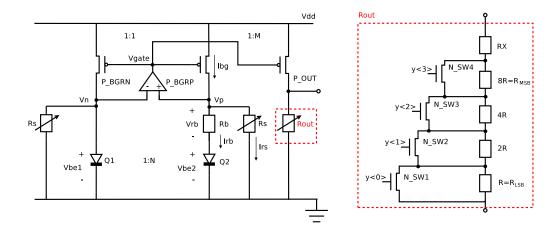

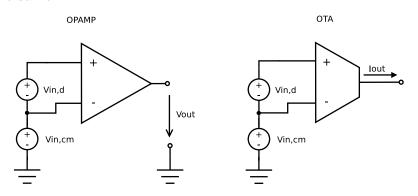

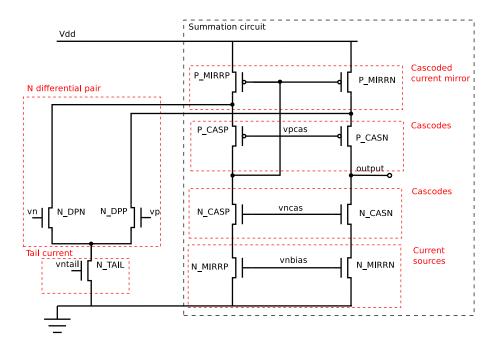

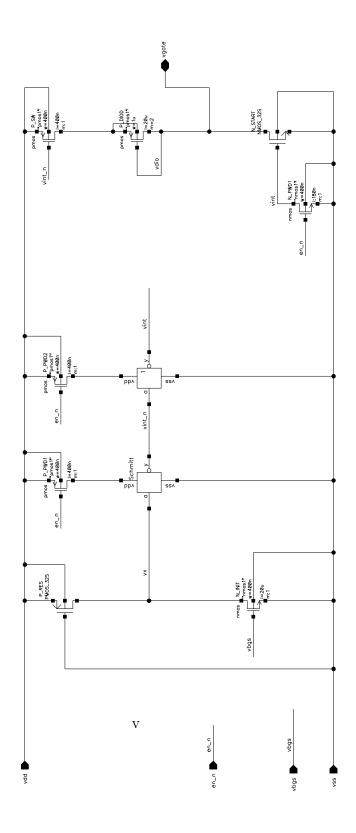

Bandagap core, trimming circuit, operational transconductance amplifier (OTA) and start-up circuit are the main parts of chosen topology. Design of these four circuit blocks are presented in this chapter.

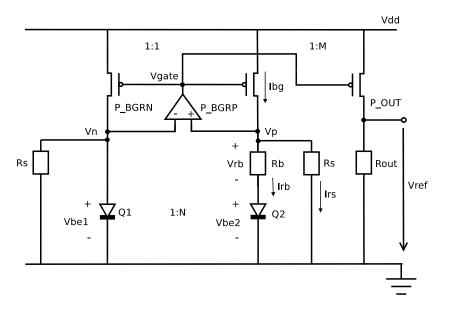

# 6.1 Design of the Bandgap Core

According to specification, the current summing BGR was chosen, [BSU<sup>+</sup>04]. This topology is introduced in chapter [4.2.2] and it is shown again in FIG.[32]

Figure 32: Principle of the current BGR

Values of Rb, Rs, Rout, N and multiplying constant M are derived for proper BGR design. These values can be calculated from Eg.[63] derived in chapter [4.2.2].

$$V_{ref,WOF} = M \frac{R_{out}}{R_s} \left( V_{be1} + \frac{R_s}{R_b} U_T ln(N) \right)$$

(63)

Note that Eq.[63] shows the  $V_{ref,WOF}$  voltage without the offset. Values M and ratio  $\frac{R_{out}}{R_s}$  are used only for the absolute  $V_{ref,WOF}$  value scale. Eg.[64]

shows the partial derivative of the bandgap voltage term  $\left(V_{be1} + \frac{R_s}{R_b}U_T ln(N)\right)$  over the temperature.

$$\frac{\partial V_{ref}}{\partial T} = \frac{\partial \left( V_{be1} + \frac{R_s}{R_b} U_T ln(N) \right)}{\partial T} = \frac{\partial V_{be1}}{\partial T} + \frac{R_s}{R_b} ln(N) \frac{\partial U_T}{\partial T}$$

(64)

To obtain ideally zero TC the Eg.[64] is equal to zero.

$$0 = \frac{\partial V_{ref}}{\partial T} = \frac{\partial V_{be1}}{\partial T} + \frac{R_s}{R_b} ln(N) \frac{\partial U_T}{\partial T}$$

(65)

The exact value of partial derivation  $\frac{\partial V_{bel}}{\partial T}$  was simulated at temperature T = 300K, see Fig.[20].

$$\frac{\partial V_{be1}}{\partial T} = -2.27mV/K \tag{66}$$

The  $\frac{\partial U_T}{\partial T}$  can be estimated by Eq.[67].

$$\frac{\partial U_T}{\partial T} = \frac{\partial \left(\frac{kT}{q}\right)}{\partial T} = \frac{k}{q} = \frac{1.38 \cdot 10^{-23}}{1.60 \cdot 10^{-19}} = 86.2\mu V/K \tag{67}$$

Eq.[68] is obtained by substitution of Eq.[66],[67] into the Eq.[65]

$$0 \simeq -2.27 \cdot 10^{-3} + \frac{R_s}{R_b} ln(N) (86.2 \cdot 10^{-6})$$

(68)

Let's express the  $\frac{R_s}{R_b}$  ratio.

$$\frac{R_s}{R_b} \simeq \frac{2.27 \cdot 10^{-3}}{86.2 \cdot 10^{-6} \cdot \ln(N)} \simeq \frac{27.5}{\ln(N)}$$

(69)

From Eq.[69] it is clear that current density ratio N must be chosen. This parameter said, how many times current density in diode Q1 is larger than in diode Q2. This parameter has a significant effect on the reference generator performance.

Assume that the Opamp has an input referred offset voltage  $V_{OS}$ . Therefore Eq.[70] is valid.

$$V_n = V_p + V_{OS} \tag{70}$$

Currents  $I_{bg}$ ,  $I_{rb}$  and  $I_{rs}$  are again derived.

$$I_{bg} = I_{rb} + I_{rs} \qquad I_{rb} = \frac{V_{rb} \cdot V_{OS}}{R_b} \qquad I_{rs} = \frac{V_{be} \cdot V_{OS}}{R_s} \tag{71}$$

Thus the reference voltage  $V_{ref}$  is expressed by the Eq.[72]

$$V_{ref} = R_{out} \cdot I_{bg} = R_{out} \left( \frac{V_{rb} \cdot V_{OS}}{R_b} + \frac{V_{be} \cdot V_{OS}}{R_s} \right)$$

(72)

After few calculation steps, Eg.[73] is derived. This relation shows unwanted dependence of the  $V_{ref}$  on the offset voltage  $V_{OS}$

$$V_{ref} = V_{ref,OF} + V_{OS} = \frac{R_{out}}{R_s} \left( V_{be1} + \frac{R_s}{R_b} U_T ln(N) + V_{OS} (1 + \frac{R_s}{R_b}) \right)$$

(73)

Mismatch variations of the BGR core and the Opamp are the main contributors of the input offset voltage  $V_{OS}$ . Unfortunately, mismatch reduction is not easy task and every Opamp has the input referred offset. From Eq.[73] is clear, that a small  $\frac{R_s}{R_b}$  ratio can reduce the effect of  $V_{OS}$  on the  $V_{ref}$ . The large value of the N parameter provides small  $\frac{R_s}{R_b}$  ratio, Eq.[69].

Moreover for good matching, the common centroid geometry is used. Thus N equal to  $n^2 - 1$  is required for the square topology, see Fig.[33]. The N parameter is chosen to be equal 24.

$$\begin{array}{c|c}

1:24 \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

& & \\

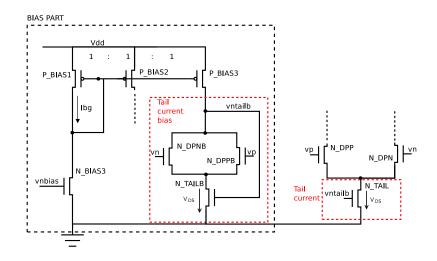

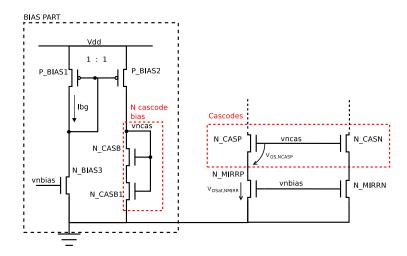

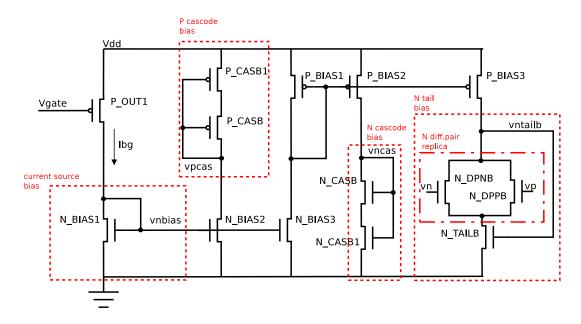

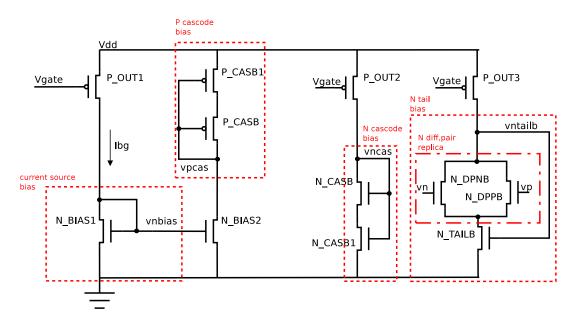

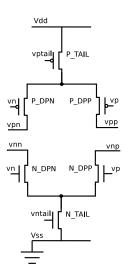

& & \\