# **Czech Technical University in Prague**

### FACULTY OF ELECTRICAL ENGINEERING

Department of Electrotechnology

### **MASTER'S THESIS**

### **Czech Technical University in Prague**

#### FACULTY OF ELECTRICAL ENGINEERING

Department of Electrotechnology

### **MASTER'S THESIS**

Quantify quality parameters during conformal coating process of printed circuit board

Kvantifikace kvalitativních parametrů v procesu lakování desek plošných spojů

Student: Jan Umlauf

Academical year: 2014/2015

České vysoké učení technické v Praze Fakulta elektrotechnická

katedra elektroenergetiky

# ZADÁNÍ DIPLOMOVÉ PRÁCE

#### Student: Jan Umlauf

Studijní program: Elektrotechnika, energetika a management Obor: Elektroenergetika

Název tématu: Kvantifikace kvalitativních parametrů v procesu lakování desek plošných spojů

#### Pokyny pro vypracování:

- 1) Seznamte se s kontaminací a technologií lakování desek plošných spojů.

- 2) Na vybraných vzorcích proveďte posouzení kontaminace desek plošných spojů a posuďte kvalitu laku.

- 3) Výsledky posouzení porovnejte a vyhodnoťte.

Seznam odborné literatury:

[1] IPC normy

[2] ABEL M., CIMBUREK V.: Bezolovnaté pájení v legislativě i praxi, ABE.TEC, Pardubice 2005, ISBN 80-903597-0-1

- [3] MACH P., SKOČIL V., URBÁNEK J.: Montáž v elektrotechnice, ČVUT Praha, 2001

- [4] HWANG J. S.: Modern Solder Technology for Competitive Electronics Manufacturing

#### Vedoucí: Ing. Karel Dušek, Ph.D.

Platnost zadání: do konce letního semestru 2015/2016

L.S.

prof. Ing. Pavel Ripka, CSc. děkan

Ing. Jan Švec Ph.D. vedoucí katedry

V Praze dne 1. 4. 2015

### Declaration

I hereby declare that I wrote presented Master's thesis by myself and I stated every used information resource in accordance with Methodical instruction about abidance of ethical principles applied during creation of university's works.

# Prohlášení

Prohlašuji, že jsem předloženou práci vypracoval samostatně a že jsem uvedl veškeré použité informační zdroje v souladu s Metodickým pokynem o dodržování etických principů při přípravě vysokoškolských prací.

V Praze dne

# With special thanks,

The greatest merit on this thesis has my leader and mentor Ing. Pavel Hanzlík, who lead my through, gave advices and improved me as a professional and human. I would like to thank to the head of the thesis Ing. Karel Dušek Ph.D. who aided me in enormous way. I was able to finish my work. There was also a lot of help from my colleagues, who listened, opposed and provided their support at time of need.

### Content:

| Abstract                                              | 8   |

|-------------------------------------------------------|-----|

| Key words                                             | 8   |

| Introduction                                          | 9   |

| Technical introduction into standards                 | 10  |

| Microsectioning                                       | 11  |

| SMT line theory                                       | 22  |

| Wave soldering line theory                            | 27  |

| Conformal coating line theory                         | 32  |

| Ionic contamination theory                            | 35  |

| Printed circuit board's contamination                 | 37  |

| Experiment NO.1                                       | 37  |

| Overall contamination through the production          | 42  |

| Experiment NO.2                                       | 44  |

| Contamination added by manipulation                   | 45  |

| Experiment NO.3                                       | 49  |

| SMD lines comparison                                  | 56  |

| SMD paste influence                                   | 60  |

| Resin and flux test qualification                     | 62  |

| How oxygen at SMD oven affects contamination          | 64  |

| Contamination temperature dependency                  | 68  |

| Solder waved printed circuit board                    | 73  |

| Conformal coating qualification                       | 79  |

| General overview                                      | 79  |

| Color                                                 | 83  |

| Viscosity                                             | 88  |

| Tinten test                                           | 90  |

| Zestron resin test                                    | 92  |

| Zestron flux test                                     | 97  |

| Ionic contamination                                   | 99  |

| Uniformity                                            | 101 |

| Thickness                                             | 109 |

| Mash cut – adhesion test                              | 116 |

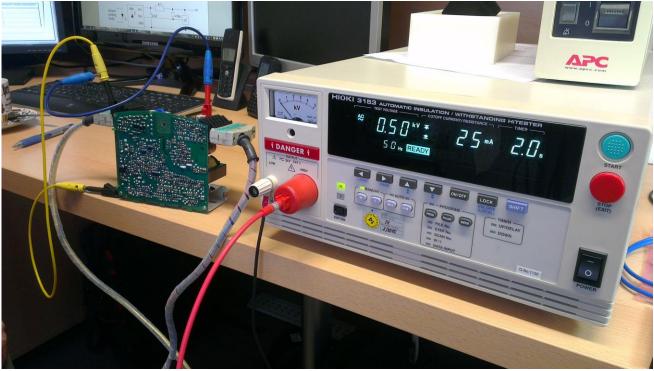

| Dielectric withstanding voltage                       | 120 |

| Tape test – adhesion test                             | 124 |

| Double coating                                        | 128 |

| Does conformal coating line meets quality?            | 131 |

| Tinten test, second                                   | 132 |

| Zestron resin test, second                            | 134 |

| Zestron flux test, second                             | 136 |

| Ionic contamination, second                           | 137 |

| Uniformity, second                                    | 138 |

| Thickness, second                                     | 141 |

| Mash cut – adhesion test, second                      | 144 |

| Tape test – adhesion test, second                     | 146 |

| Dielectric withstanding test, supplier                | 147 |

| IPC specified printed circuit board, test of adhesion | 151 |

| Conclusion                                            | 157 |

| Literature                                            | 158 |

| List of abbreviations                                 | 159 |

### Abstract:

Main objective of this thesis is quality assurance of conformal coating process. Proper quality parameters and characteristics are evaluated and quantified. Quantification exactly and objectively reflects reality and allows us to improve processes. Conformal coating is mentioned only partly. Thesis is focused on incoming goods. Contamination of printed circuit boards is main interest. Effects caused by contamination and reduction of contamination are suggested in conclusion.

# Abstrakt:

Hlavním cílem této práce je zajištění kvality lakovacího procesu. K tomu je potřeba najít a zvolit optimální kvalitativní parametry, jejichž vyčíslení nejpřesněji a nejobjektivněji vyjadřuje zkoumanou skutečnost. Samotný proces lakování je probírán spíše okrajově, hlavním bodem zájmu je vstupní materiál. Zvláštním předmětem zájmu je kontaminace desek plošných spojů. V závěru je shrnut vliv na lakování a možnosti snížení kontaminace.

# Key words:

Conformal coating, quality, printed circuit boards, contamination, ionic contamination

# Klíčová slova:

Lakovací proces, kvalita, desky plošných spojů, kontaminace, iontová kontaminace

### Introduction:

Conformal coating is used as protection to chosen base. In this work, printed circuit board is being coated. Importance is given to the dielectric quality and protection against moistening.

Characteristics before application are crucial. Viscosity allows us to properly apply the lacquer. While it's surface tension is important when it has to form a bond with board. When drying time would be too long, coating could not be used in production due to time and resources spend in oven. Bonding on the basic level and ability to not create transitions is relevant for double coating or reparations.

Parameters of the produced printed circuit board are eighty percent of success. It is the top priority to inspect the boards prior to lacquer. While changing coating is easier than improving the process, the processes are keys to success. Ionic contamination of the board is inspected through the production. Flux and resin residues are partly link to the ionic contamination as it reflects cleanliness, but residues have to be inspected independently. Flux residues attract humidity and can eventually lead to delamination.

How to coat the board is skill requiring experience. Lines taken in order to bring good results, smoothness and economy of the programing of the conformal coating line, cleanliness and handling precautions are learned through the quantification process. Thickness is optimized. Uniformity, equability and adhesion are evaluated and compared to the norms.

Quantification of quality parameters has simple meaning. On many occasions, more pictures, studies, tables and models are used instead of words. Numbers are quality performance meters. There are paragraphs and topics in this thesis, but it can be sorted into three: quality of the printed circuit board in production, quality of the coating and coating process as an interaction between those two.

"Measurement is the first step that leads to control and eventually to improvement. If you can't measure something, you can't understand it. If you can't understand it, you can't control it. If you can't control it, you can't improve it."

Dr. Harrington, H. James. CIO (Sep 1999), p. 19.

### List of standards and description:

Proper set of test methods must be chosen in order to objectively evaluate the process. Introduction into standards helps with basic orientation.

# IPC J-STD-001. chapter 8: Requirements for Soldered Electrical and Electronic Assemblies

This document describes methods for electronic assembly manufacturing and processing soldering materials. Criteria for materials, verification methods for solder joints and assemblies.

#### IPC-A-610. 10.4: Acceptability of Electronic Assemblies

This norm helps quality assurance to choose whatever part can be used or not. Pictures, microsections and guidance is provided to make a right decision.

#### IPC-TM-650. Environmental test methods

Norm provides specification of environmental test methods. Lot of information is taken from this standard.

#### IPC-TM-650. 2.3.25 Detection and Measurement of Ionizable Surface Contaminants by Resistivity of Solvent Extract

This method should be highlighted as half of thesis relies on it. Although IPC specifies 1,56  $\mu$ g NaCl Eq./cm<sup>2</sup>, those requirements are much higher in industry.

#### IPC TP 1113. Circuit Board Ionic Cleanliness Measurement

Manual describes methods and limitations of the ionic contamination measurement and influences of various flux types.

#### IEC – 68-2

Those are methods for climatic reliability testing of electronic assemblies. IEC 60068 determines suitability of components, assemblies and other parts in usage transportation and storage under different climatic conditions.

# IPC-HdbK-830. Guidelines for Design, Selection and Application of Conformal Coatings

This handbook provides assistance to make choice regarding conformal coating. What can be achieved by conformal coating application and how to verify the results.

#### **Review of**

IPC-TM-650. 2.1.1.2 Microsectioning—Semi or Automatic Technique Microsection Equipment

This method specifies procedure for metallographic specimen preparation through microsectioning. Process's goal is exact evaluation of laminates, copper foils, plating and mainly coating. This process is actually often applied as a solution for unclear cases concerning electronics or mechanical issues.

More than often the safety procedures have to be followed. Either from the point of view of material and environment (refer to Material Safety Data Sheet = MSDS) or from the point of view of assembly itself, where it's disassembly might be dangerous.

Used apparatus contain grinder, sample alignment tools, mount molds, marble plate for correct mounting, pressure system capable to store the coupon at around 2 bars, potting material, air extraction area during curing time, polishing equipment, abrasive paper an polishing cloths, diamond abrasive, polishing lubricant, micro etch solution and microscope.

It is important to follow recommended steps in order to create the good microsection sample or coupon. Then the quality is going to be kept and evaluation of the sample is going to bring the results.

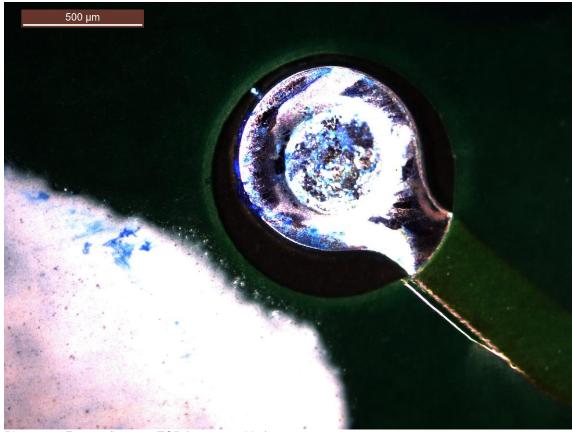

The key in this process is initial selection. More often the product or assembly is very big and therefore selecting the proper position to microsection and also the correct plane might be the hardest decision that can either lead to results or prolong the evaluation. When the place is chosen, then the correct cut-off method (Picture T1) must be made. Abrasion by grinder or directly by blades has to be done sensitively in order to not damage the evaluated area that would change the result and decisions. According the IPC the edge should be around 2 mm from the evaluated areas. From the experience, 3 or 4 mm is suitable even for coating analysis.

After the sample is taken, it is necessary to polish the edges by abrasive paper to prevent the burrs. Inspection of sample afterwards is required. If sample is damaged, it is required to take new one. It is necessary to solder the sample in order to properly inspect plated-through holes. Correct approach is first applying the flux and let it be activated, then placing it into the lead-free solder bath (Picture 2) for 10 +1/-0 s @ 288 °C. European Union suggests several alloys that conform with RoHS standard (Restriction of Hazardous Substances) Sn96,5Ag3,5. For solder paste there is often 0,75 of Cu at the expense of Sn. This provides thermal shock and evaluation of solder wettability.

Note: Mostly the solder shock evaluation was not used, because of it's damage to the inspected coating. Nevertheless it is important to note this step.

Correct mounting of the sample is important in reducing the process time. Alignment tool must correctly attach the sample but it is not allowed to damage the sample. Marble surface is also a great help in this (sometimes) endeavor.

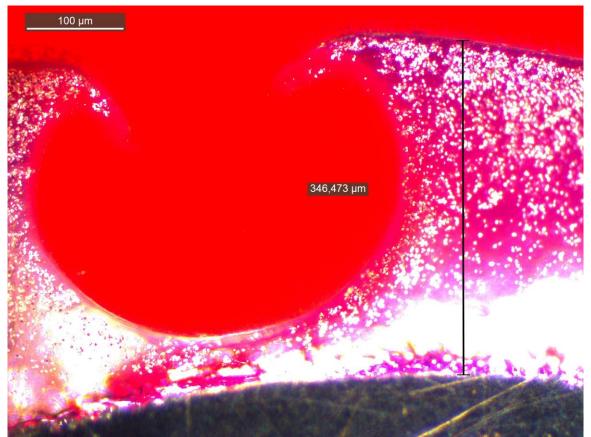

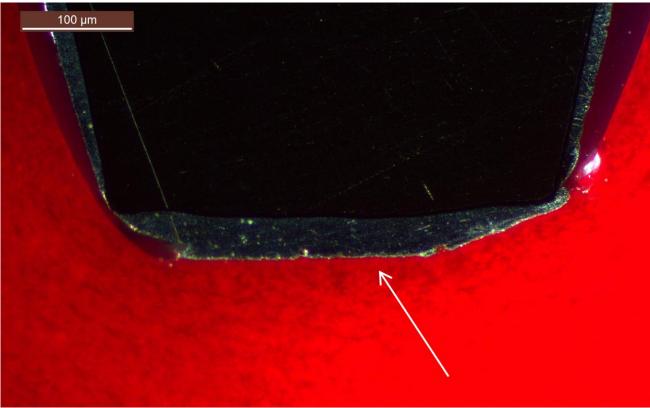

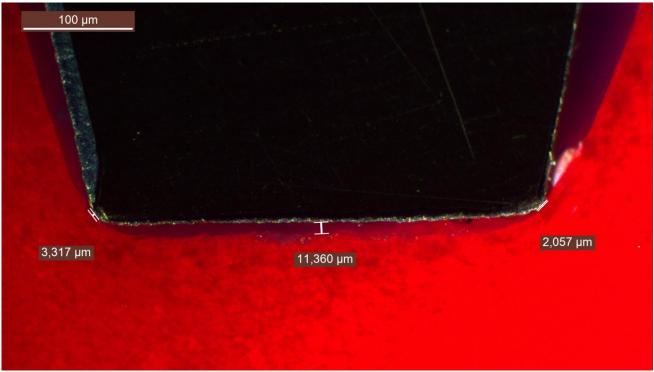

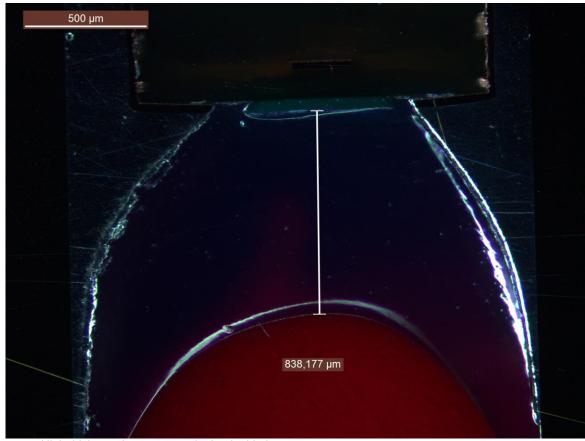

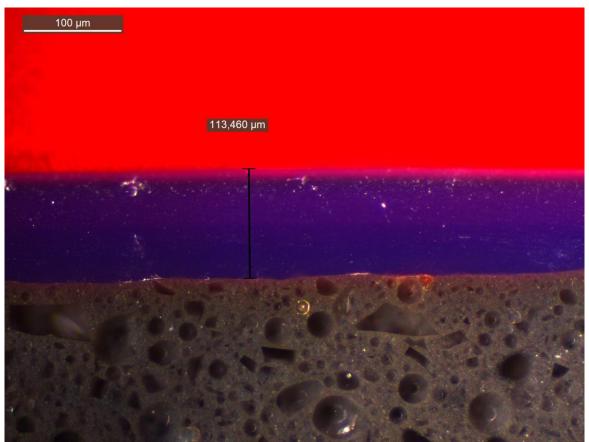

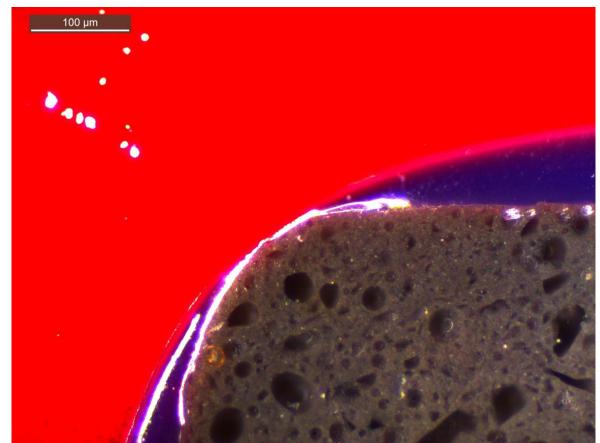

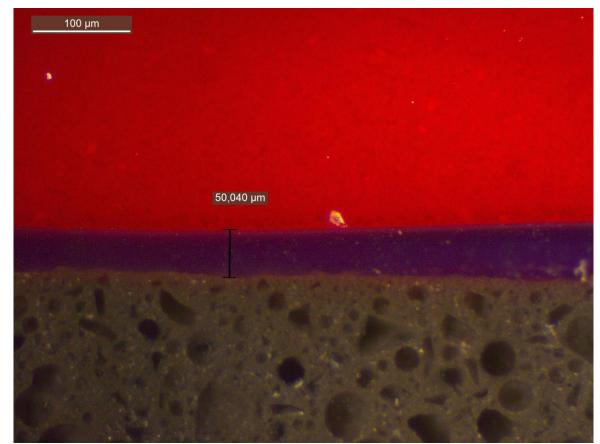

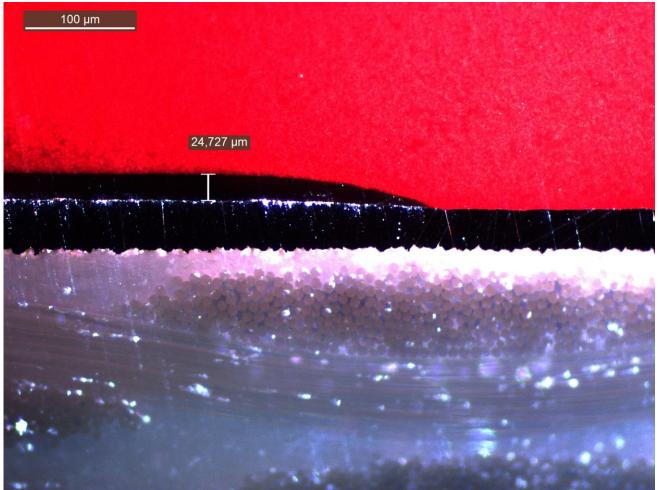

Note: Project to find suitable potting material was initiated, because the standard epoxy was not usable for the microsection analysis as it corrupted the coating (Picture T6). After that no thickness measurement was possible or meaningful. Possible solutions for this problem were found. See the dedicated project after this section.

According the IPC potting material must have a low shrink rate, and the cure temperature must be less than 93 °C. Potting material is in most cases composed of two elements, it is important to mixing them in right rate and carefully.

Plastic or rubber container for potting material with sample is suggested. If the material is not very plastic, release agent should be used. Hardening process is fast, lot of heat is produced and voids can be present in the microsection. Pressure pot is desired to prevent voids occurrence. Pressure around 2 bars is enough, when increased temperature would be used, than for 50 °C, it is around 1,75 bars. This is for safety (because the pot has some limits) and can

be calculated to match the exact environment according the equation of state, where only pressure and temperature are variables. Increased temperature is used for rapid hardening, general oven is recommended. Air extraction system is important for personal safety.

Creating a flexible traceability system is desirable. Permanently mark the specimen after curing is finished. Good specimen is without voids in whole volume, without gaps between the material and sample and PTHs are completely filled. It has to be solid in order to be grinded and polished. Picture T4 shows such grinding and polishing machine with chemistry

Grinding of the sample has in general three steps. Abrasive paper increases the grit size through the process (P180, P400 and P1000). Revolutions per minute around 200, water cooled and residues separation are key parameters. IPC also suggests pressure for automatically prepared specimens. With abrasive grit size change, it is key to also rotate the sample by 90 °. Careful manipulation (to not scratch the surface) is important for the final products.

Specimen has PTHs, evaluated part, SMD component etc. in the center. It is upright unless specified otherwise. Scratches has size same as abrasive grit size paper. No residues are present on the sample. Surface is planar and therefore polishing is going to be easy, otherwise whole sample is not going to touch the polishing cloth.

Two or three steps of polishing with napless and nap type of cloth deliver good results. Revolutions can be kept or decreased. It highly depends on the type of the polish abrasive. Cleaning between steps should not be overlooked. There is no water present during the polishing to clean it. Same quality characteristics apply after polishing.

Microetch solution and cleaning are last steps when copper is being evaluated. It allows visual inspection of the copper. It is important to distinct the plated and galvanized copper.

Picture T1: Edging saw

Picture T2: Solder bath

Picture T3: Extraction system necessary during curing time

Picture T4: Grinder and polisher

Picture T5: Microsection coupons, different epoxy is necessary is used

Picture T6: Evaluation station, Microscope is required, Leica 500x

#### **Overall project to find suitable filler for microsections**

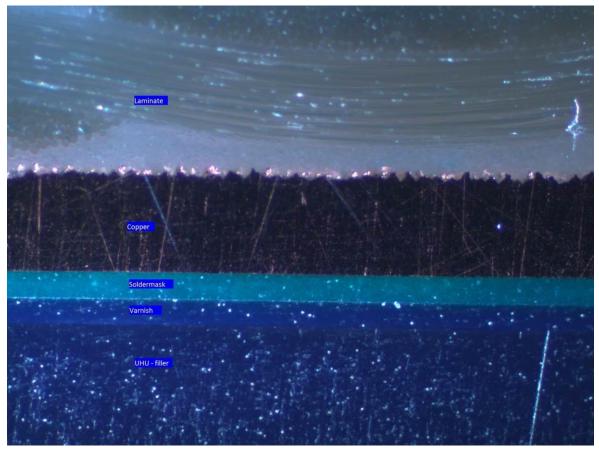

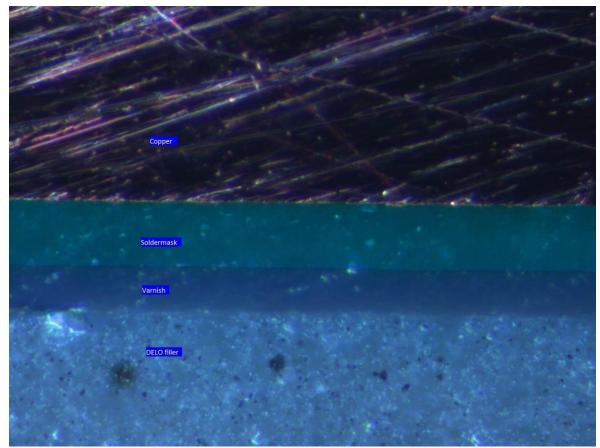

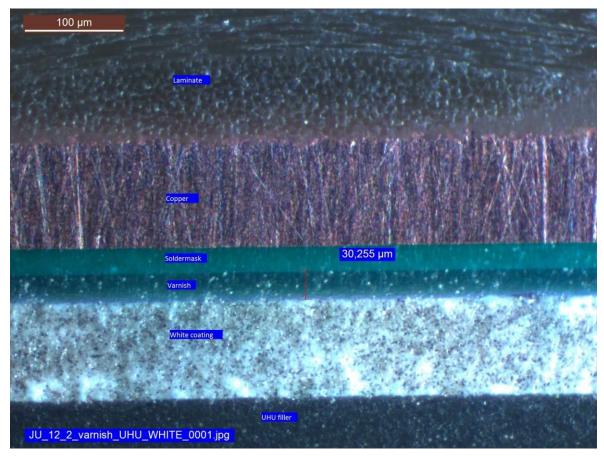

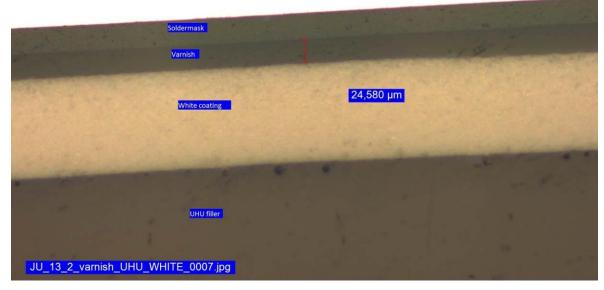

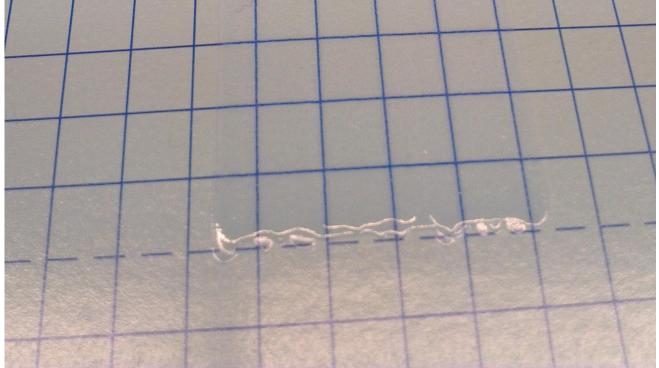

Varnish was corrupted by our standard epoxy. After that no thickness measurement was possible or meaningful. Possible solutions for this problem were found.

#### Adhesive/filler:

UHU DELO Using other types of adhesive. such as or DELO has very long solidify period (around 6-8 hours) and on light it has very little contrast against varnish. On the other hand it has no negative influence on varnish. Using UV light this filler has best contrast between varnish and filler. Chosen way is using double component adhesive UHU. Hardening process takes about 20 minutes under increased temperature in oven (90 °C). Other possible way is using water based coating. Tested BALAKRYL UNI white. It creates protective layer that also serves as contrast film. Epoxy filler is possible. This time it damages paint and not varnish. UHU adhesive is still better choice.

Coating can serve as contrast film, that has no impact on varnish or filler. S6005 based paint damaged varnish. Same issue was with paint in spray.

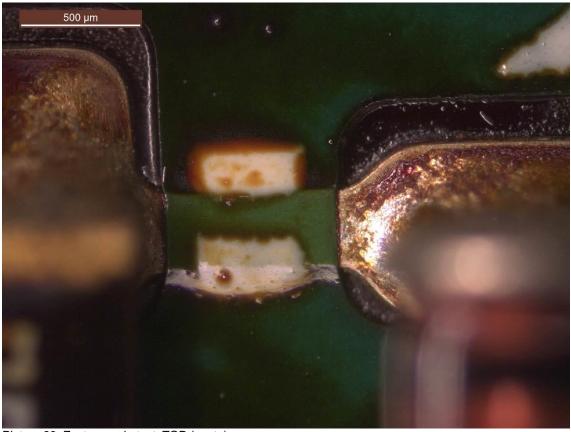

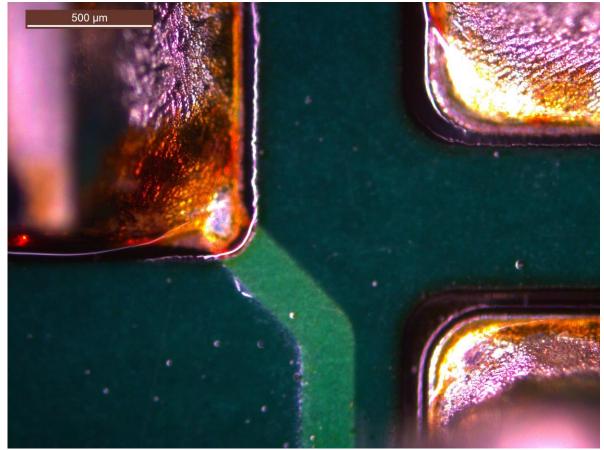

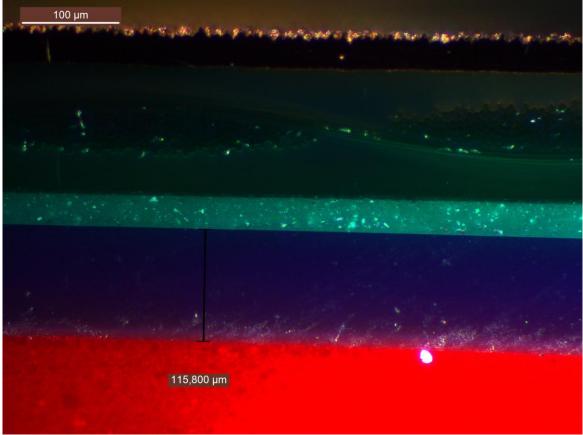

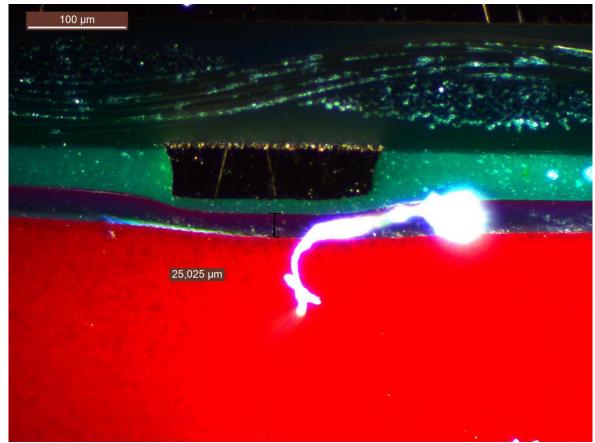

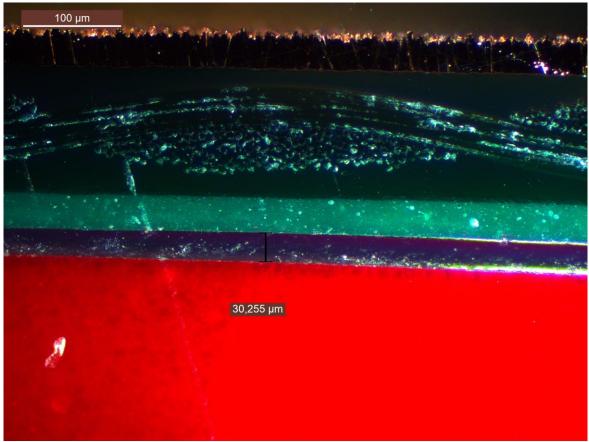

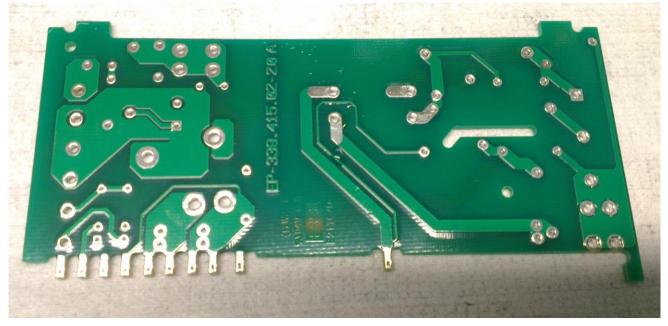

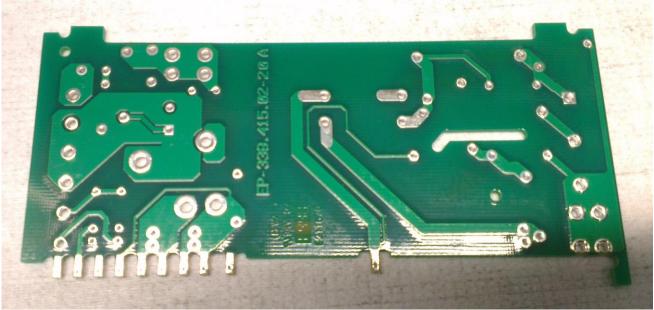

Picture T7: Microsection sample

Picture T8: Microsection sample

Qualification thesis

Picture T9: Microsection sample

Qualification thesis

#### **Results:**

Based on microsections, UHU torns varnish apart from solder/soldermask. It is not clear if it is caused by intense stress. Only on certain areas this has happened. Those could have been already damaged or at least weakened.

On our test PCBs everything was fine. Layer was new but dried and also three times thicker.

This issue requires deeper test. Another and better fillers should be studied. Or temperture could be decreased. But this would make process slower and leakage worse.

In the end for the future project the standard industry potting material (red colored) was used. Chemical unreactivity, good contrast, leakage and time consumption are more or less solved. It looks like it will be necesseary to let the microsection solidify longer in order to achieve microsection without any damage caused by our test process. Issue concerning higher adhesion between varnish and filler to varnish and soldermask, which tears varnish off. Goal is to deliver best possible and accurate results.

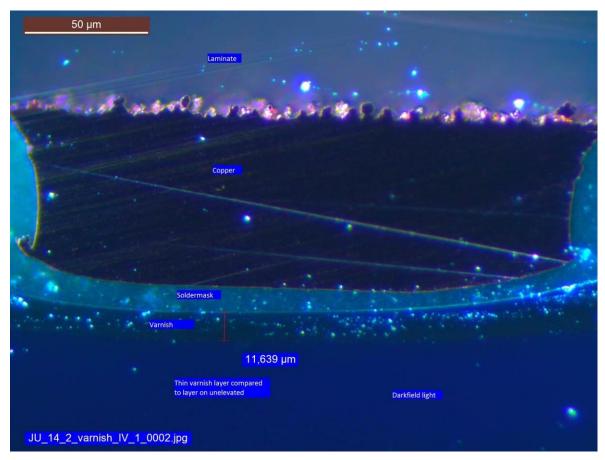

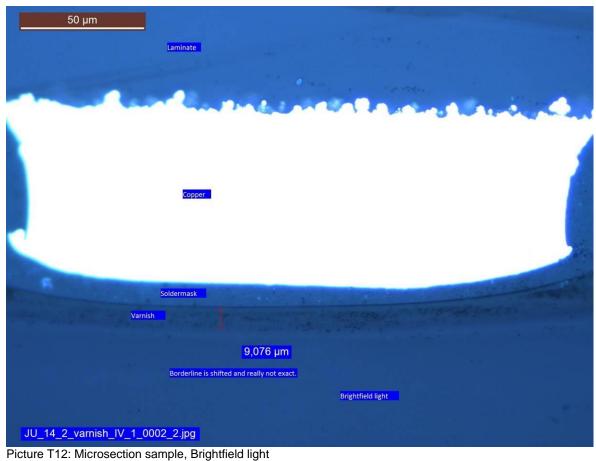

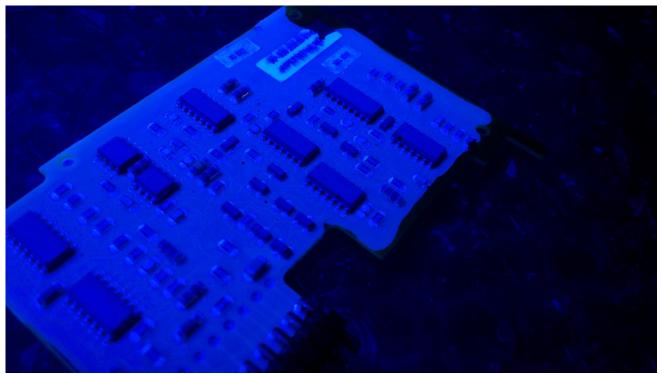

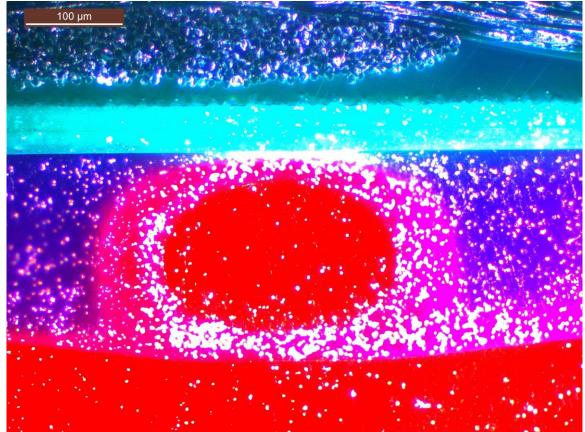

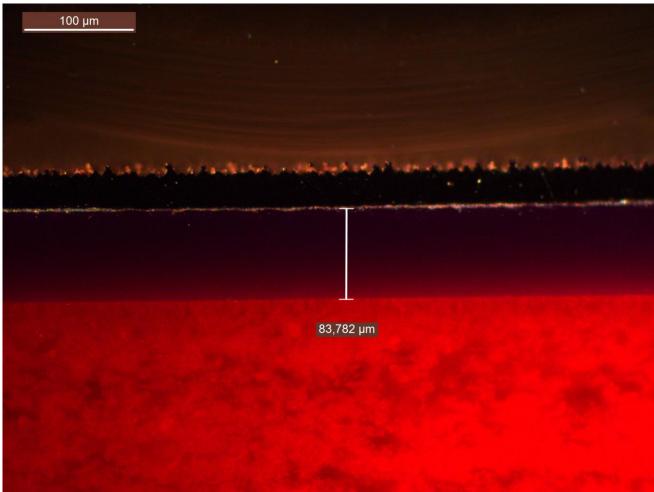

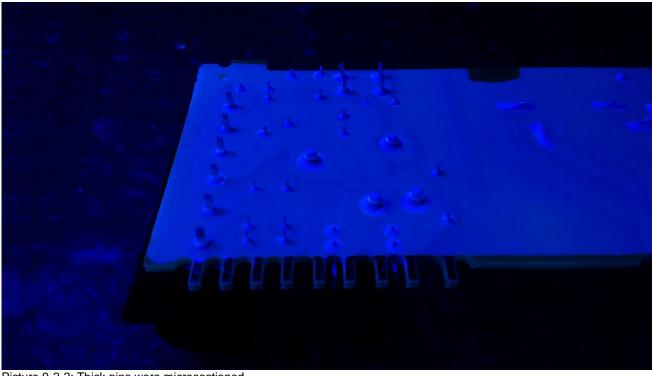

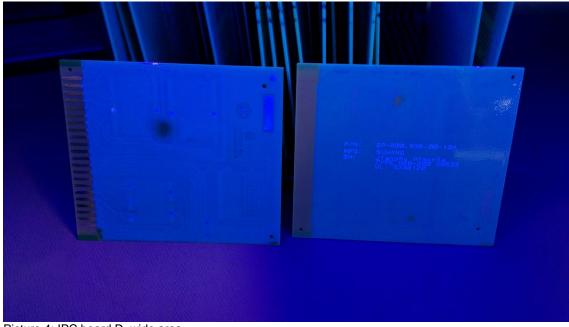

#### Light:

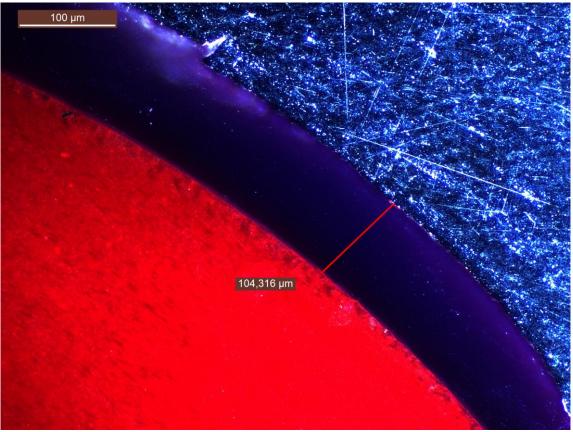

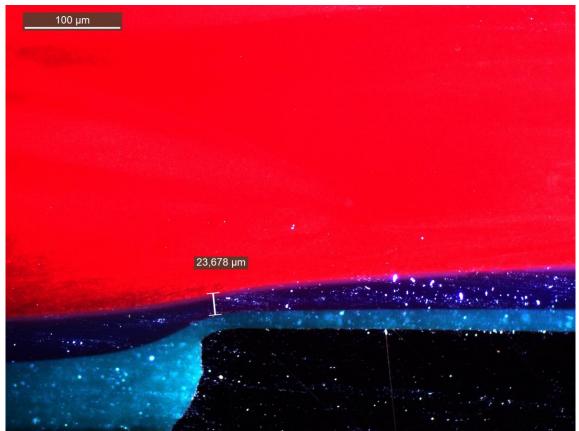

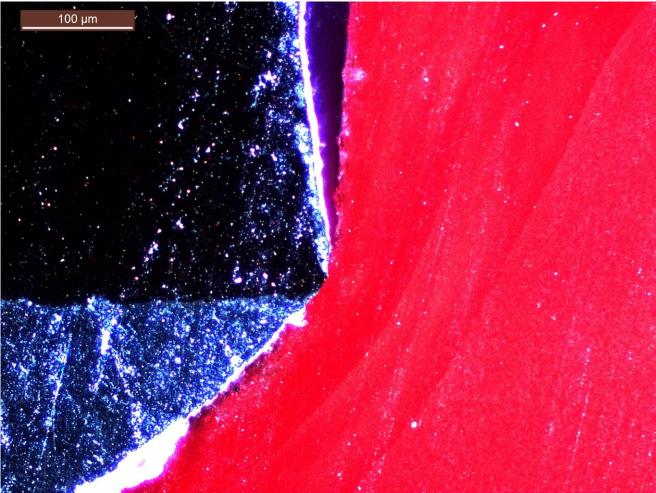

Different types of microsection's and PCBA's lightning were used. UV – ultraviolet for increasing contrast between varnish and filler or soldermask. In microscope it is not always clear if darkfield lightning (DF) is prefered to brightfield lightning (BF). Different situations require different approches.

Results: In the majority of cases DF is used. Higher contrast is what is neccesseary for thickness measurement and good orientation in microsection. Sometimes BF was good as second picture for clear and full view on given situation.

Also for best results BF is very sensitive fine tuning. Eg. Gamma correction, saturation, exposure, atc.

Picture T11: Microsection sample, Darkfield light

Qualification thesis

#### SMT line theory

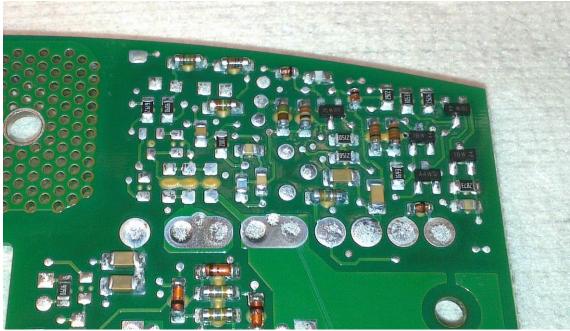

SMT stands for surface-mount technology. It is a method for production of electronic circuits. Most critical is distinction between SMD (surface-mount device) placement and classic THT (through-hole technology). Placement is on the PCBs (printed circuit boards). In general the SMD is smaller than it's THT counterpart as it possesses no pins or short leads.

Assembly of such circuit is cheaper and consumes less energy. Higher components densities can be reached. Big power transformers, chokes and coupling capacitors still require the THT. In general both technologies are used together to bring the best results. SMT comes first, because it would be impossible to mount the components with transformers, also volume under big THT components can be used. Wave soldering would not be as effective and THT components would face the reflow oven. Manipulation with SMDs is easier, etc. There are too many reasons.

Three critical pieces of drawn electrical circuit are wires, components and transitions. Wires are represented by printed circuit board, components are SMDs and transitions are created by solder paste (or paste). Physical bond to the PCB is created either by solder paste or glue.

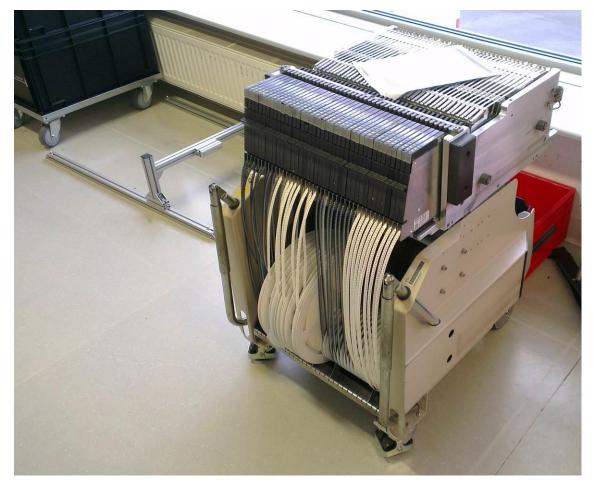

Parts of SMT line (Picture T13) are boards storage, rotation and carrier machine, applicator of paste and glue through stencil, placement machine, which is critical and most precise, reflow oven and AOI (automatical optical inspection).

Often the components are hold only by solder joints. Evaluated SMT line has on RLP or reflow side of boards only this type of connection. Those solder joints are created through the solder paste activation in reflow oven. Adhesive is used on the WLP or wave side of the board, which is solder waved after assembly with the rest of the THT components. Those joint are created between SMD's solder PCB. often contacts and pads on the Solder paste is

Sn95,75Ag3,5Cu0,75 alloy plus flux. Those are small particles, mostly in ball shape that are melted together, while flux cleans the pad and SMD's contact from residues, oxides etc., forming a bond.

Solder paste is applied through stainless steel stencil with brush (Picture T14). It has to be processed in certain time as it has limited usability. Glue is applied in the same manner in case of SMDs that are later wave soldered.

Pick and place machine (Picture T15) takes components from the reel (Picture T16) and places them on the PCB. It places tenths of thousands assemblies per hour while skilled operator can do hundreds. It takes the component with air jet.

Reflow oven (Picture T17) is the critical piece of the technology process. While position of the pads, paste and components can create lot of issues, reflow process, proper setup of the temperature profile and timing, atmosphere etc. is vital. Techniques and theory is described in the experiment, where it is linked to the quality parameters. Temperature from the oven is delivered to the board through the radiation and/or through convection. Two temperatures are critical. Low temperature must allow bond to be formed, paste activated, etc. High temperature is risk for the parts. Tension between board and component can crack SMD.

Evaluated SMT line did not possess washing machine, which is often composed of IPA (isopropyl alcohol) plus water and sonic cleaning. Waste disposal is an issue and logistics and storage is problematic. There are MSL (Moisture sensitivity level) SMDs that require special care and storage (Picture T18). Paste and process is designed as no-clean. Best results and pricier are through cleaning.

In general, SMT can be introduced to the industry, where certain processes are prepared. Company is mid to big size and investments in millions are option. Skilled personal is required (technology, repairs and visual inspection). Delivered results are then worth the input.

Picture T13: SMT line overview

Picture T14: Machine with stencil for paste aplication

Picture T15: Pick and place machine

Picture T16: Reels with SMDs

Picture T17: Reflow oven

Picture T18: Drying cabinet for MSL > 1 SMDs

#### Wave soldering

Wave soldering (Picture T19) is the process that creates electrically conductive bond between printed circuit board and components. It is used for THT components and for surface mounted components. It saves costs and time. Quality is also higher. Upgrade from wave soldering is to selective soldering method.

In order to use the wave soldering (Picture T21), several conditions have to be fulfilled. It is necessary to have PCB designed with solder resist or solder mask. It prevent solder to be attached everywhere, only where joints are exposed. It is also important to create enough pad spacing. This ensures that no short circuit is going to occur.

There are several steps before quality joint is formed. Everything begins with right design, but first the relatively clean board has to be assembled. Pins are on the bottom of the board. Board enters the machine, where flux is applied to the bottom. Flux is activated at the preheat section (Picture T22) and evaporates cleaning the board. When board has proper temperature, so the shock from solder wave is small, it reaches the wave solder and solder attaches to the exposed conductive parts. It is cooled by forced convection on naturally (Picture T23). Joint is formed.

No board, surface and joint is clean enough, therefore fluxing is necessary. It cleans and removes oxidation in same way as flux during reflow does. Flux is applied to the soldered side. Joints are going to be of low quality when there is not enough of it. Or if too much is applied there is going to be lot of residues left on the board. It causes degradation and possibly a failure. Flux is applied by the spray.

Heat absorbed during wave soldering is far greater than during manual soldering. It is the most severe portion during manufacturing and life cycle. During production board can withstand 1 or 2 wave soldering with 3 being the

top. It also takes a lot of load during reflow (or double reflow). Preheat minimizes the thermal shock and decreases failure rate. Even heating is ensured by hot air and also infra-red heaters. Another important reason is proper flux activation.

In general, wave soldering should be considered as very production and goal oriented method for creating a quality solder joint. However this method puts a lot of stress on the board. High contamination levels are expected.

Selective soldering is more precise and therefore does not damage the board by heat. It is also better with SMT process components. There are SMT components that are designed for wave and components that are not. In quality and price are the differences. The most recent laser technology completely removes stencils (masks) from the process. It is very precise and requires perfect programming, but delivers best results.

Picture T19: Wave soldering line

Picture T20: Preheating area

Picture T21: Area with wave soldering

Picture T22: Electronics for preheating

Picture T23: Cooling is not forced

Picture T24: Cleaning is necessary step

### Conformal coating line

Conformal coating is protective material used on printed circuit boards. Humidity, dust particles, chemicals and direct electric break through are prevented from causing any issues to the product. It is also better solution than potting as coated boards are easily repairable. Mechanical stress and vibrations are decreased. It is especially relevant at high temperatures. It is also in conformance with increasing the assembly density.

Inline variety (Picture T25) for printed circuit boards uses spraying technology. It is the evaluated method. Brush coating is undesirable as it requires skilled operator that devotes a lot of time into work. Quality is also highly variable to robotically applied layers. It is nevertheless used for repairing or after electrical circuit was repaired. Inline sprayed ones are highly uniform, cost oriented, stable in time and has many additional features that prevent failures. Dipping is another technology that can be used. It requires printed circuit board to be designed in certain way as sprayed ones are designed with different properties in mind. It is also repeatable and very importantly, coating covers every device and piece of board. This disqualifies a lot of boards to be coated in this way. No heat sinks, light emitting diodes or potentiometers can be present at time of coating. Dipping is perfect method for winding goods manufacturing as coating creates precise cover required by those products.

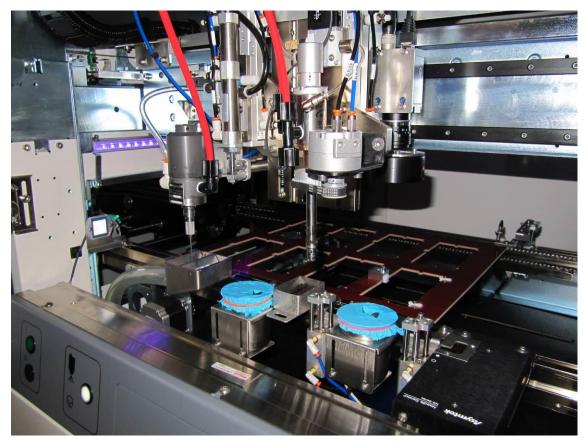

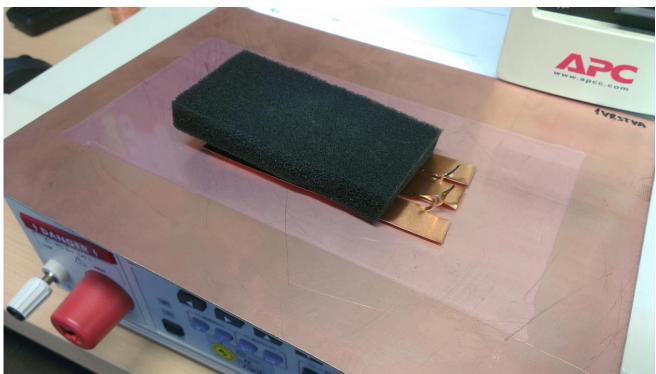

Inline spray technology is highly selective and upgradable according new specifications. Pressured at around 5 bars coating is applied by precise jet (Picture 27). Viscosity and therefore volume of thinner must be kept at defined tolerances. Layer thickness is controlled through the jet's speed while pressure and flow is constant in time.

Board or whole product enters line in mask that holds it tightly. It is necessary step for line manufacturing. Same method is used for wave soldering.

When first layer (in most cases, BOT or bottom one is chosen as first) is coated than board proceeds to the manipulator that rotates the board, so that TOP side coating can be applied.

Accelerated curing by oven (Picture T26) is introduced, because (time) efficiency is essential for mass production. Temperature profile is applied for around 30 minutes. Proper temperature decreases curing time and prevents damage of the coating. Accelerated curing and drying is not as beneficial to the water based coatings as they always require more time than acrylic based ones.

It is important to understand, that in those coating there is a thinner and filler. Thinner evaporates and only filler is left on board. Therefore there is a volume and mass difference. Wet and dry films can be measured and evaluated, but with difference in thickness. In this report I am going to address the dry film thickness unless specified otherwise.

There are epoxy, silicone, polyurethane, amorphous fluoropolymer based coatings except for mentioned acrylic and water based coatings.

Picture T25: Conformal coating line

Picture T26: Oven

Picture T27: Most precise machinery (head) of the conformal coating line

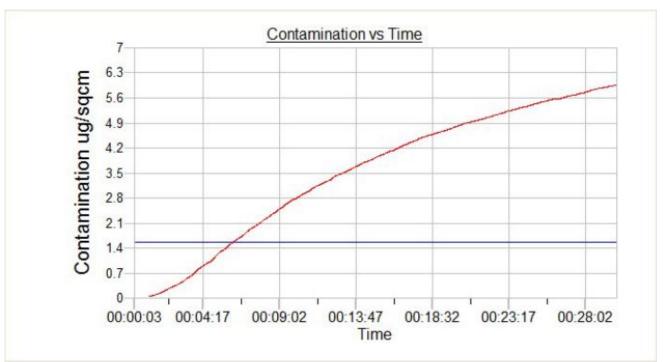

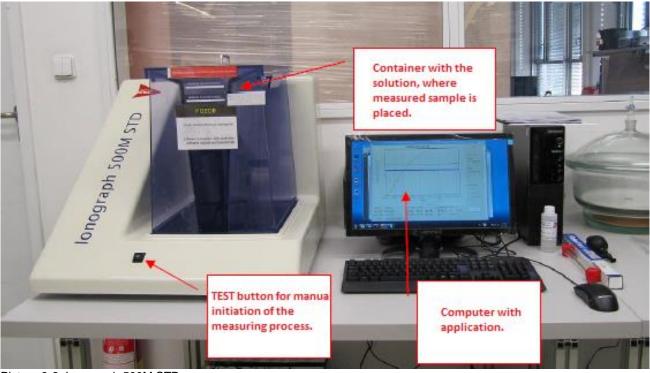

#### Ionic contamination theory

lonic contamination is quality parameter of product that refers to the amount of dissolvable conductive elements on the specimen. It is mostly referenced to the surface area.

lonic contaminants such as bromide, fluoride, potassium, sodium, organic acids or chloride can cause many quality issues and failures. Conductivity of those ions cause electrical leakage. Metal migration and corrosion is present.

Ionic contamination present on the board becomes more active in highly humid ambient. Conductivity on surface is increased.

Mixture of 75 % (in volume) of isopropyl alcohol (IPA) and 25 % deionized water (DI water) is used as extraction medium that dissolves residues from evaluated printed. Theory behind this mixture is that water is substance with high polarity and IPA with low polarity. Substances with similar polarity can be dissolved. Therefore this solution has ability to dissolve low polarity and high polarity substances.

When the ions are dissolved solvent's conductivity is increased. It is measured pre and after the dissolving. Solution is continuously filtered and cleaned to be used again. Direct voltage (DC) is applied and conductivity is measured. As a reference grams of NaCl are used. It is also important to note the surface's area.

There are several limitations. It is only a partly cleanliness factor. Only ions and only dissolvable ions are measured. (In reality, there are none ions on the surface, those are in neutral form and ions are formed when this stable substance is dissolved into IPA + DI-water mixture. Mechanical particles (dust, dirt, burrs, etc.) are problematic as it contaminates the device itself. It is ionography and not ionospectrography based test. It is not possible to evaluate components separately. Another disadvantage is in insufficient exposures that

can always occur and therefore nothing is dissolved, measured and recorded. It is desirable to use resin and flux detection tests in addition to evaluate state as a whole. Test also does not indicate where the highest concentration of the ionic contamination is. It is an averaging method. So everything might seem to be ok, while there will be one or two highly densely contaminated areas. This is also proven by experiment.

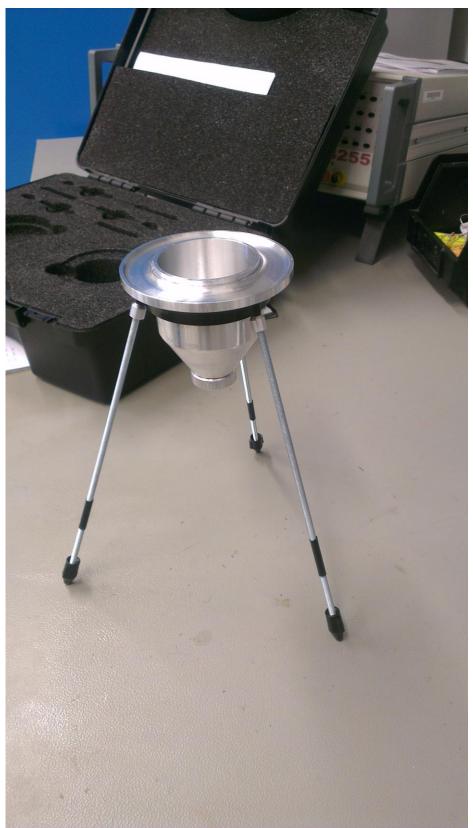

Picture T28: Ionograph with accessories

# Goal:

Main goal of the test is to find out how much contamination is added to the PCBA by SMD and wave soldering process. This study must be continued by experiments that analyze added contamination from other sources to prevent data corruption.

# About testing tooling:

Contamination is measured by lonograph 500M STD from Invicta UK, developed by SCS Coating. We do not use ionic chromatography.

Contamination is measured in µg.cm<sup>-2</sup> Eq NaCl. It is average over whole PCB. NaCl is reference. It is not lon-contamination-spectrometer, which measure each element separately. In text I won't mention this unit again, any number linked to contamination is in those.

Residues are indicated by Zestron resin test and Zestron flux test. Those are visual tests, contamination degree is observed by reaction, but it is not quantifiable.

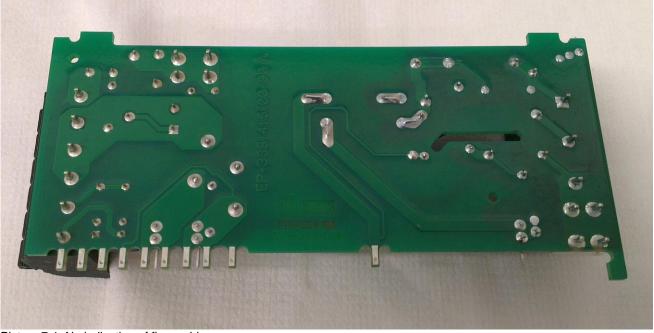

# **Experiment No. 1**:

Quantifying contamination of delivered boards and our assembly process eq. manipulation, SMD assembly, reflowing in oven and wave soldering. During THT assembly parts variation, operators and ambient is involved. This was removed from experiment.

# Introduction:

With all the measurement done what I can say with certainty is that no matter what process we were observing, one sample at a time is not enough. Measurement takes long periods of time (from as little as 5 min to 1 hour). More measurements can be done over time, but one or two per day is not enough. Almost no trends can be extracted from data taken. Without knowledge of the

Almost no trends can be extracted from data taken. Without knowledge of the process, without knowledge of any additional contaminations brought from ambient, it will be very challenging to gain value from tests.

PCBs were stored in suitable area. All manipulation in gloves, transport in clean packs. For exception that are noted there was no physical contact.

# Handling:

This part contains my observations. It might bring some questions and disagreements. And that is the reason why I stated my standings on this matter. As my intentions are to make this process better and clear. I followed instructions with sole exception where doing so to the extreme would change nothing as I explain in paragraphs that come.

I was very careful during manipulation with samples. I handled PCBs, calipers, hydrometer and other possibly sensitive material in gloves (or in at least one glove). My assumption is that even if I was wearing both, my results would be the same or worse. If I would stay in laboratory and my operation would be limited I would wear both, which I did.

Second hand was used for shield (lonograph) manipulation, operating computer (keyboard + mouse) and such. This was precautious, because in this way there is no possibility I would touch anything with my naked hand. Those basic things that need to be done are in fact sources for contamination. This way I was mentally forced to not switch or change hands. It was not stressful and without any higher control over myself.

During wave soldering process I used Solder process operator to handle everything that could be source of contamination for my gloves. PCBAs manipulation was my sole and peerless purpose in this regard.

### Data:

Far most contaminating process is wave soldering. Contamination goes from twice to four times values of fail point.

Expected trend of autonomous self-cleaning process was not found. It could be there but is clouded in high variation of data. Let's say if cleaning would be 3-10 % per day and standard deviation would be around 20-30 % of the mean, then there is no way to find it.

Wave soldering was done twice. Testing was different. First time there were weights put onto PCB (to match the pressure put on the PCB from soldering wave). Those weights were highly contaminated and even left traces of this contamination on the PCB. Nevertheless during second test this was bypassed by second PCB working as a shield. I take it as not a fully standard procedure, because regularly THT components add substantial amounts of weight. On the other hand, that option seems to be present. Then it should be traced as well even if it is not a direct cause from the wave.

Contamination was varying in time. In case of RLP contamination was growing instead of decreasing. Storage and manipulation was not an issue. If this is caused by ambient so be it. PCB was stored in regular conditions.

Calipers and I suspect that hydrometer also are contaminants by themselves. Because hydrometer is placed into solution during pre-test I see no bigger issue with that. But calipers are used during test and subsequently interfere with measurement. This was measured to 0,04. It is considerable amount. Clean/delivered PCB has contamination 0,03-0,05. Not an issue with PCBA (0,5-3).

# Flux and resin contamination:

Delivered, manipulated, reflow side, wave side pre and after wave on none of those samples were found traces of flux or resin contamination. White or brown areas suggesting anything are not present at all.

From this I suspect that our manufacturing process is without any issues in this way.

(Since then I found major issues. This statement was wrong, but at that time, everything lead me to believe so. See next experiments.)

# Verification:

Unquestionable data are most important. With this in mind I did verification process twice, whenever data looked corrupted. Even in shorter periods than suggested. Both were without any doubts.

lonograph needs to be calibrated with specifically prepared and defined solution. It is similar to resistance and inductance calibration before RLC measurement with RLC analyzer.

### Mined data:

First tests were always done directly after process or in 1 hour.

#### **Delivered PCBs:**

Delivered PCBs taken directly from the MBB are not contaminated at all. Contamination of 0,04 are minimal measured levels. I even took one from the top and one from the middle. Results are the same.

#### Manipulated PCBs:

During manipulation nothing considerable happens. Results are 0,08. It is twice as much, but initial levels are very low. It is caused more by deviation than anything else. Other possible source for contamination is packaging.

As a manipulation I consider standard process of unpacking and preparation for SMD assembly. Packaging (for delivery between SMD and laboratory) was added.

#### RLP (without components), RLP with components (only reflow side):

I would like to put those two under one paragraph to compare differences. Contamination grows to 0,50 for assembled board and to 0,90 for unassembled one. This shows us, that SMDs are not contaminants. Rather paste and adhesive are.

Here our expectations were torn apart. Instead of "cleaning" contamination grew. Could be contaminated from elsewhere, but I see no way how.

#### WLP (RLP + WLP side):

WLP and RLP side has lower contamination than RLP side by itself. This bears very interesting information. WLP process could be very clean (as there is no increase). Or contamination could be here after autonomous RLP side cleaning this ends in similar levels, thus making RLP assembly measurement corrupted. Also this measurement can be corrupted, but I suspect, that no cleaning

between takes place as higher levels are expected. Deviance is last possibility that can not be excluded and is surely present too.

#### Calipers contamination:

Calipers were tested once and this test is therefore very limited. I put calipers into solution for 30 sec – 1 min (according my feeling to match the duration I usually spend). It brought contamination to 0,04.

### **Closure:**

There are two possible ways how to close this project. We can either accept that contamination is highly unstable and close this in this way. We collected some basic data, so it was very important insight into this domain.

If we want to match this process correctly I expect, that at least 20-30 samples per single area are necessary. Delivery and manipulation looks ok, this work can be shaved off. My proposition if we go this way would be 18 samples on RLP side another 18 RLP+WLP and 32 after wave. I would do only one test of resin and flux test on PCBAs after wave soldering.

Note: 18 = 3x6 (3 samples at a time in 6 batches, twice first day and then next four in 5-6 days to cover one week

32(30) = 5x6 + 2 (5 samples at a time in 6 batches) + RTZ + FTZ Those are two packages per 40 PCBs.

### Graphs and tables:

| Delivered      |      | Manipulation  |      | Reflow + Past | te   |

|----------------|------|---------------|------|---------------|------|

| 26.5.2014 8:40 | 0,04 | 30.5.14 11:10 | 0,13 | 30.5.14 12:37 | 0,96 |

| 26.5.2014 8:55 | 0,02 | 30.5.14 12:13 | 0,07 | 30.5.14 12:56 | 0,82 |

| 26.5.2014 9:05 | 0,05 | 30.5.14 12:25 | 0,05 |               |      |

| μ              | 0,04 | μ             | 0,08 | μ             | 0,89 |

Table 1: Contamination levels, experiment no. 1, "Board A"

| RLP (reflow + pa<br>components |      | WLP          |      | After wave (te | st 1) | After wave (test | t 2) |

|--------------------------------|------|--------------|------|----------------|-------|------------------|------|

| 30.5.14 13:19                  | 0,52 | 2.6.14 13:11 | 0,44 | 4.6.14 10:23   | 5,95  | 6.6.2014 12:04   | 2,88 |

| 30.5.14 18:18                  | 0,47 | 3.6.14 10:06 | 0,44 | 4.6.14 16:04   | 6,44  | 6.6.2014 17:35   | 3,56 |

| 31.5.14 7:49                   | 0,58 |              |      | 5.6.14 18:38   | 5,57  | 7.6.2014 6:16    | 3,07 |

| 1.6.14 8:18                    | 0,74 |              |      | 7.6.14 7:01    | 5,71  | 8.6.2014 7:37    | 2,97 |

| 3.6.14 9:31                    | 0,96 |              |      |                |       |                  |      |

Table 2: Contamination levels, experiment no. 1,"Board A"

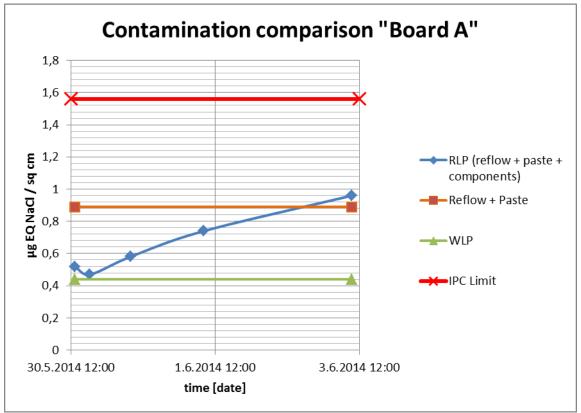

Graph 1: Contamination levels in time, SMD subprocesess, experiment no. 1,"Board A"

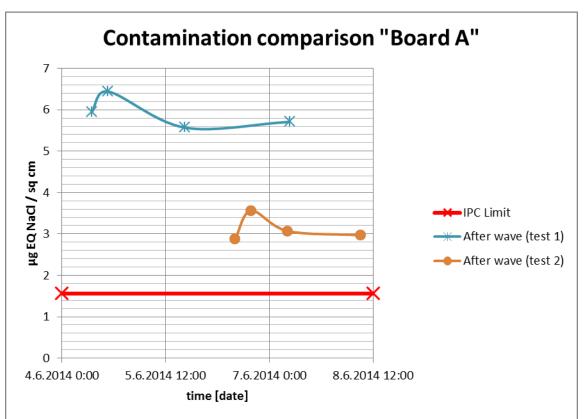

Graph 2: Contamination levels in time, Wave soldering, experiment no. 1,"Board A"

# **Experiment No. 2:**

Second experiment evaluates SMD and Wave soldering process.

### Goal:

Main goal of the test is to find out how much contamination is added to the PCBA by SMD and wave soldering process. This study must be continued by experiment, that analyze added contamination from other sources to prevent data corruption.

This is a second run of the tests. Very much can be gained by cross analysis.

# **Basics:**

Selected sample was part of the bigger order and was treated just as any other part. Manipulation was done in regular manner (income, storage and SMD line). I entered into process after SMD assembly and moved APs to the solder process (to cross THT assembly).

Those boards were manufactured on SMD line No.: 1 As opposed to the past test, where it was done on No.: 2. Soldering took place in the A (in both cases).

# Timin<u>g</u>:

Assembled boards were first measured after 3 hours (SMD mounting). Then those boards were soldered after approximately 24 hours. Again were measured, right after that. Another is planned after 1, 3 and 5 days.

One measurement takes 30 to 60 minutes (plus regeneration and manipulation). Measurement is contamination dependent (there is a correlation).

# Sample size:

Whole order was 40 boards. 40 boards were assembled. 20 measured and 20 soldered. Then those soldered were also measured.

20 was separated into 4 batches. Measurement is done directly after test, 1, 3 and 5 days. It is necessary as it took 5 hours to properly test single batch.

# Additions:

Additional 24 boards were tested. Except for delivered ones, all other boards were designated to be scrapped. Before anything those were first cleaned in the IPA.

This gives us some thoughts about what can happen and what can be gained or lost by selected actions.

| Purpose                        | Sample size |

|--------------------------------|-------------|

| Delivered and packed "board B" | 4           |

| Cleaned and labeled            | 4           |

| Neat finger prints             | 4           |

| Sweaty fingers                 | 4           |

| Dirty gloves                   | 4           |

| Fall to the ground             | 2           |

| Lying in the oven              | 2           |

Table 3: Sample sizes, experiment no. 2

| Contamination [µg eq NaCl . cm <sup>-2</sup> ] |      |  |  |  |  |

|------------------------------------------------|------|--|--|--|--|

| Action                                         | μ    |  |  |  |  |

| Sweaty fingers                                 | 0,22 |  |  |  |  |

| Neat fingers                                   | 0,06 |  |  |  |  |

| Dirty gloves                                   | 0,09 |  |  |  |  |

| Fall to ground                                 | 0,16 |  |  |  |  |

| Inside oven                                    | 0,05 |  |  |  |  |

| Clean + label                                  | 0,09 |  |  |  |  |

Table 4: Contamination levels from operations, experiment no. 2

# **Results:**

#### Delivered "Board A2":

| Contamination [µg eq NaCl . cm <sup>-2</sup> ] |       |      |      |       |  |  |

|------------------------------------------------|-------|------|------|-------|--|--|

| μ                                              | σ     | Min  | Max  | c [%] |  |  |

| 0,38                                           | 0,073 | 0,30 | 0,44 | 19,4  |  |  |

Table 5: Contamination from supplier, experiment no. 2

#### After SMD assembly:

| Contamination [µg eq NaCl . cm <sup>-2</sup> ] |      |      |      |      |      |      |

|------------------------------------------------|------|------|------|------|------|------|

| t [date]                                       | 1    | 2    | 3    | 4    | 5    | 6    |

| 18.9.2014 9:30                                 | 2,31 | 2,22 | 1,88 | 2,23 | 1,97 |      |

| 19.9.2014 9:12                                 | 2,83 | 2,53 | 2,27 | 2,29 | 2,31 |      |

| 21.9.2014 9:15                                 | 2,27 | 2,11 | 2,62 | 2,29 | 2,70 | 1,89 |

| 23.9.2014 8:27                                 | 2,19 | 2,41 | 1,94 | 1,83 | 2,25 | 1,61 |

| Contamination [µg eq NaCl . cm <sup>-2</sup> ] |       |       |      |      |  |  |

|------------------------------------------------|-------|-------|------|------|--|--|

| μ                                              | σ     | c [%] | Min  | Max  |  |  |

| 2,12                                           | 0,186 | 8,8   | 1,88 | 2,31 |  |  |

| 2,45                                           | 0,239 | 9,8   | 2,27 | 2,83 |  |  |

| 2,31                                           | 0,305 | 13,2  | 1,89 | 2,70 |  |  |

| 2,04                                           | 0,297 | 14,6  | 1,61 | 2,41 |  |  |

Table 6: Added contamination by SMD, experiment no. 2

$$\mu$$

= 2,23  $\mu$ g eq NaCl . cm<sup>-2</sup>

#### After solder wave:

| Contamination [µg eq NaCl . cm <sup>-2</sup> ] |      |      |      |      |      |   |

|------------------------------------------------|------|------|------|------|------|---|

| t [date]                                       | 1    | 2    | 3    | 4    | 5    | 6 |

| 19.9.2014 15:45                                | 5,24 | 5,15 | 5,76 | 5,32 |      |   |

| 20.9.2014 12:21                                | 6,47 | 6,26 | 6,92 |      |      |   |

| 22.9.2014 9:57                                 | 7,15 | 5,95 | 7,04 | 6,22 | 5,59 |   |

| 24.9.2014 10:36                                | 8,73 | 6,88 | 8,07 | 7,17 | 5,85 |   |

| Contamination [µg eq NaCl . cm <sup>-2</sup> ] |       |       |      |      |  |  |  |

|------------------------------------------------|-------|-------|------|------|--|--|--|

| μ                                              | σ     | c [%] | Min  | Max  |  |  |  |

| 5,37                                           | 0,271 | 5,0   | 5,15 | 5,76 |  |  |  |

| 6,55                                           | 0,337 | 5,1   | 6,26 | 6,92 |  |  |  |

| 6,39                                           | 0,682 | 10,7  | 5,59 | 7,15 |  |  |  |

| 7,34                                           | 1,110 | 15,1  | 5,85 | 8,73 |  |  |  |

Table 7: Added contamination by Wave soldering, experiment no. 2

$\mu$  = 6,41  $\mu$ g eq NaCl . cm<sup>-2</sup>

µ - mean

- $\sigma$  standard deviation

- c variation coefficient =  $\sigma/\mu$

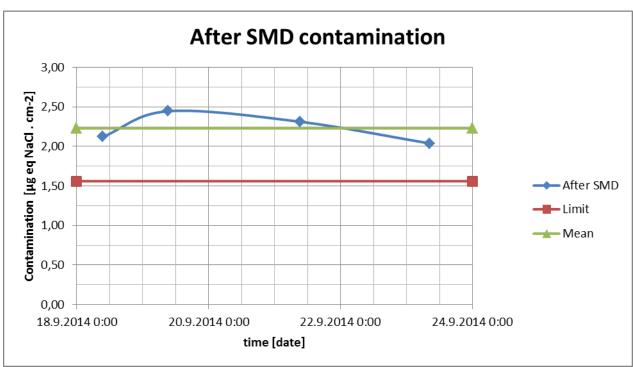

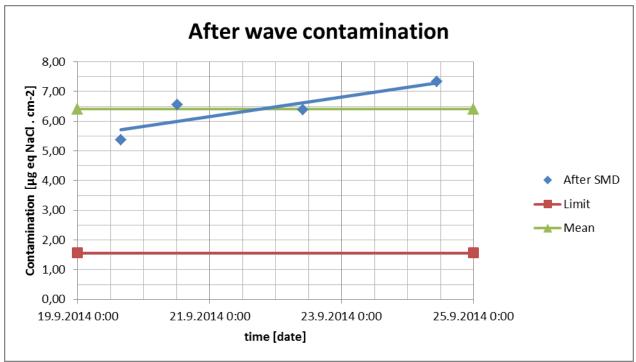

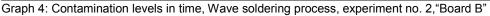

Graph 3: Contamination levels in time, SMD process, experiment no. 2,"Board B"

#### Results (second = actual experiment):

Delivered – SMD, Delta Contamination =  $1,85 \mu g eq NaCl \cdot cm^{-2}$ SMD – Soldered, Delta Contamination =  $4,18 \mu g eq NaCl \cdot cm^{-2}$

# Past time- for comparison, SMD 2 line assembly:

# **Results (first experiment):**

After SMD  $\mu$  = 0,65  $\mu$ g eq NaCl . cm<sup>-2</sup>

Initial contamination was  $\mu$  = 0,04  $\mu$ g eq NaCl . cm<sup>-2</sup>

After wave  $\mu$  = 3,12  $\mu$ g eq NaCl . cm<sup>-2</sup>

Delivered – SMD, Delta Contamination = 0,61 µg eq NaCl . cm<sup>-2</sup>

SMD – Soldered, Delta Contamination = 2,47 µg eq NaCl . cm<sup>-2</sup>

# **Commentary:**

There are 20 samples for each. There is always some variance in the process. It is followed by differences in operator and laboratory worker, even laboratory equipment or cleanliness of gloves. Time variance can not be offset as it takes around 1 hour to measure each sample. This brings us to 3 days at minimum. So my guess is sample size is optimal.

# Comparison:

Different SMD contamination is one thing that stands out. There is a big difference, even if additional possible contaminants and deviation of process are included.

My conclusion is higher cleanliness of SMD line 2. Possibly due to cleaning/maintenance during KW 18 (tests took place KW 20). While on SMD line 1 maintained during KW 29 and evaluated during KW 38.

Soldering process also shows high difference. But it is high variance process and highly uncontrollable (I had my doubts and already rejected few results). As even a weight, that is placed on the board can move and change the results. Variation is increasing with time.

Results show, that during time contamination is increasing/decreasing to some equilibrium. This process looks to be longer than 5 days.

|                   | SMD contamination                | Wave contamination               |

|-------------------|----------------------------------|----------------------------------|

| First experiment  | 0,61 µg eq NaCl.cm <sup>-2</sup> | 2,47 µg eq NaCl.cm <sup>-2</sup> |

| Second experiment | 1,85 µg eq NaCl.cm <sup>-2</sup> | 4,18 µg eq NaCl.cm <sup>-2</sup> |

Table 8: Contamination levels comparison

There is not exact answer to the given question. Variance is very high. I propose to check contamination (after SMD) regularly, on just single board and find out more. I would do one or two boards per week and per SMD line.

We need to get process under control. No matter the current state. There are more variables to be quantified. Those are time, line 1/2, input material, assembly, maintenance period, etc.

Incoming boards are relatively all right. Those are not perfect, but would easily pass. Most contamination is wave soldering, then SMD assembly and manipulation.

# **Experiment No.3:**

Deep evaluation of possible contamination sources on SMD assembly only.

## **Testing:**

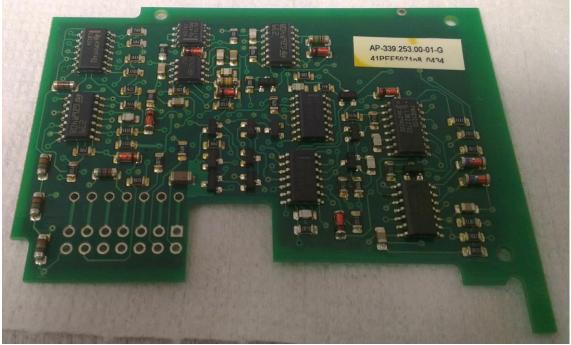

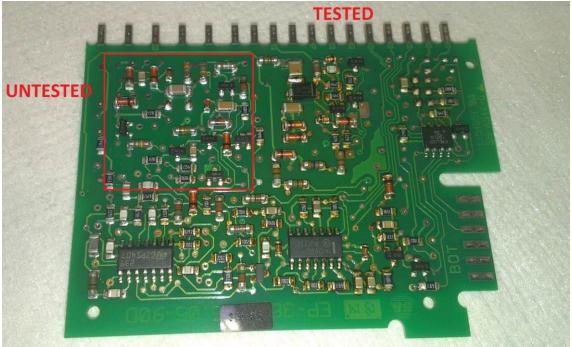

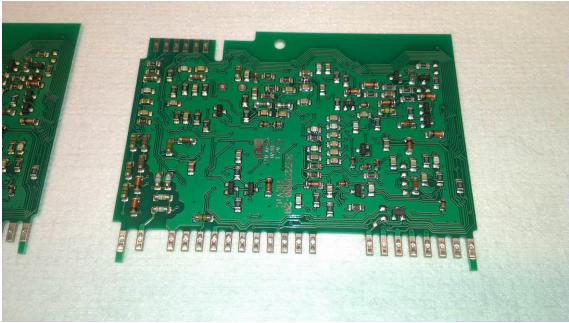

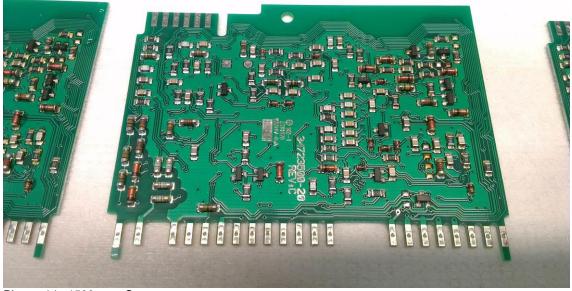

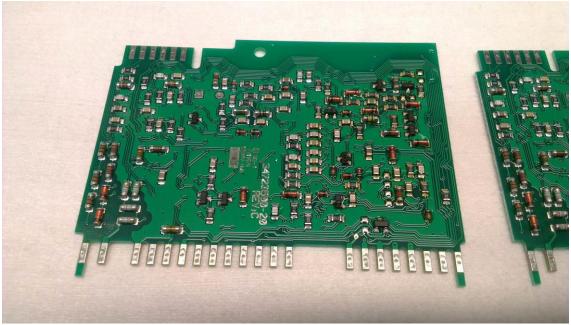

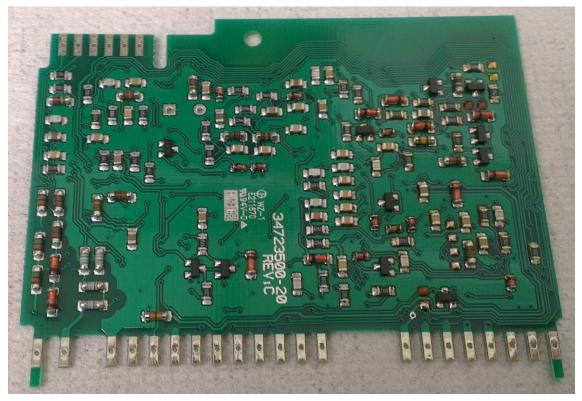

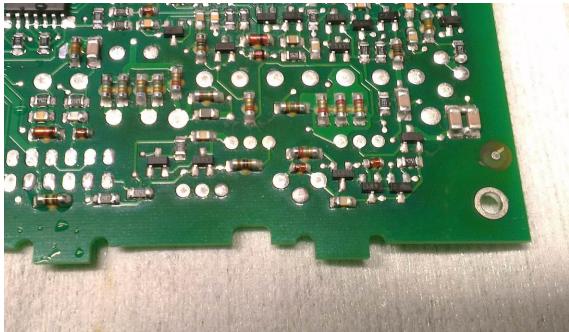

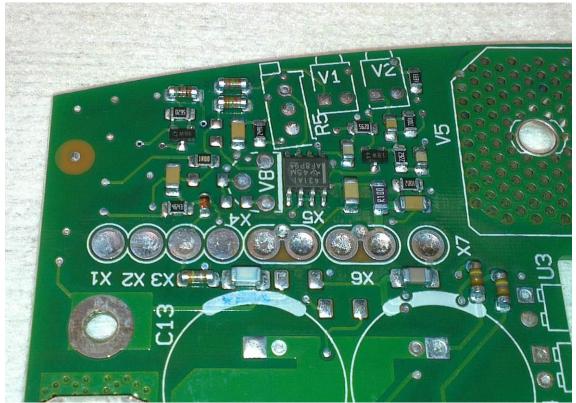

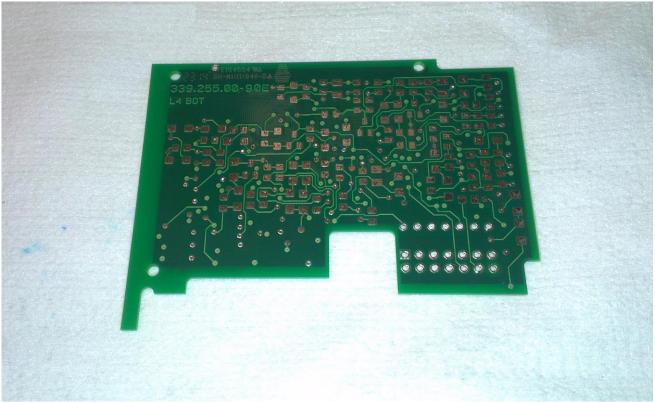

#### "Board B"

Module PCBA was solely done on SMD line 2. Those were taken from serial batch. Handling and production are those, that are regularly used.

### Three types of tests were done:

Contamination has different characteristics and methods are different. Residues from paste, soldermask's impurities, handling issues etc. In general methods, which are used have variable and attributive (more or less) results. Ionic contamination is measured in  $\mu$ g eq NaCl . cm<sup>-2</sup>. Zestron resin and flux tests (with upcoming tinten test) are visual test, that show presence of residues.

#### Ionic contamination:

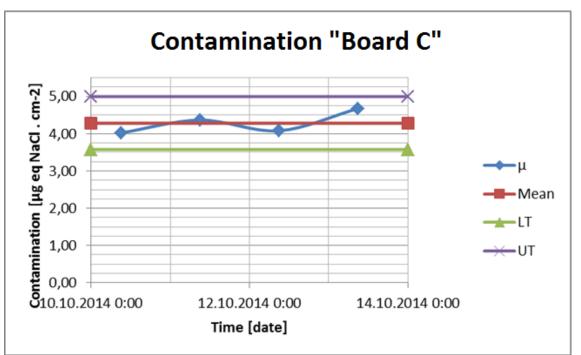

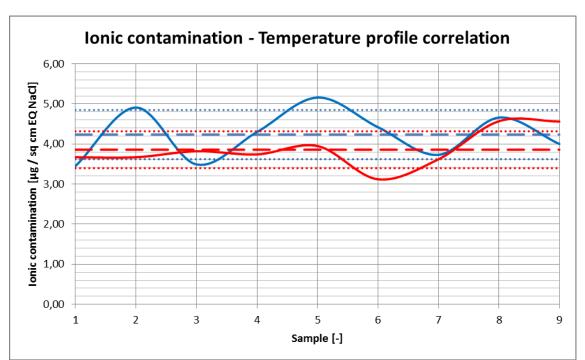

Four times six boards were measured. Time variance is a lot lower than general variance of the sample batch, time dependence is not findable. Based on graph no. 1, we can confirm results within  $\sigma$  range.

Contamination levels are three times higher (see table no. 1) than those suggested by IPC. (1,56  $\mu$ g eq NaCl . cm<sup>-2</sup>)

| Contamination [µg eq NaCl . cm <sup>-2</sup> ] |                                                |       |       |      |      |  |

|------------------------------------------------|------------------------------------------------|-------|-------|------|------|--|

| t [date]                                       | μ                                              | σ     | c [%] | Min  | Max  |  |

| 10.10.2014 9:00                                | 4,02                                           | 0,671 | 16,7  | 3,16 | 4,97 |  |

| 11.10.2014 9:00                                | 4,37                                           | 0,352 | 8,1   | 4,01 | 4,78 |  |

| 12.10.2014 9:00                                | 4,08                                           | 0,628 | 15,4  | 3,18 | 5,09 |  |

| 13.10.2014 9:00                                | 4,68                                           | 1,015 | 21,7  | 3,71 | 6,66 |  |

|                                                | Contamination [µg eq NaCl . cm <sup>-2</sup> ] |       |       |      |      |  |

|                                                | μ                                              | σ     | c [%] | Min  | Max  |  |

|                                                | 4,29                                           | 0,711 | 16,6  | 3,16 | 6,66 |  |

Table 9: Contamination, Double RLP, Experiment No. 3, "Board C"

Graph 5: Contamination of "Board C"

#### Flux test:

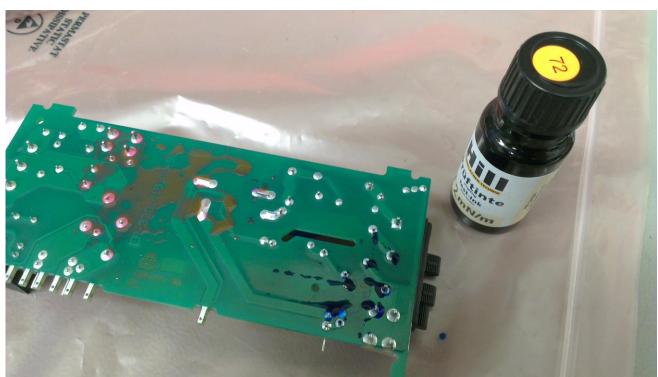

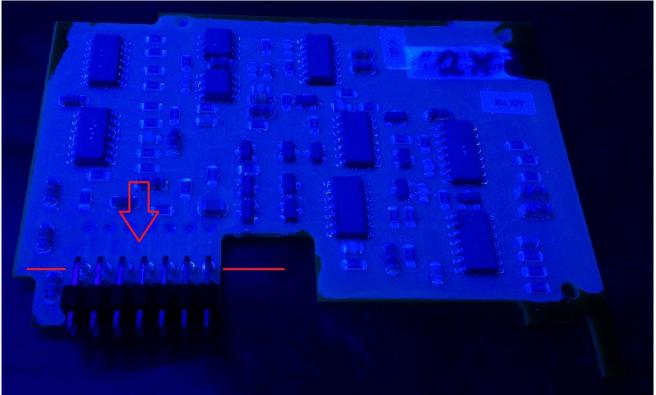

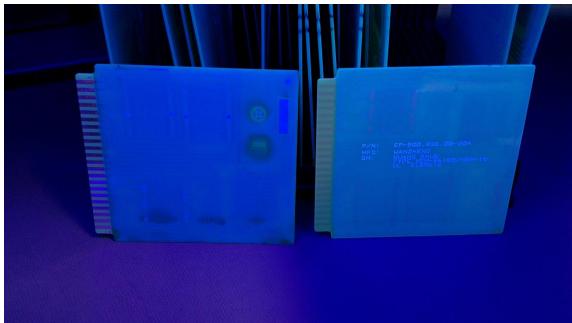

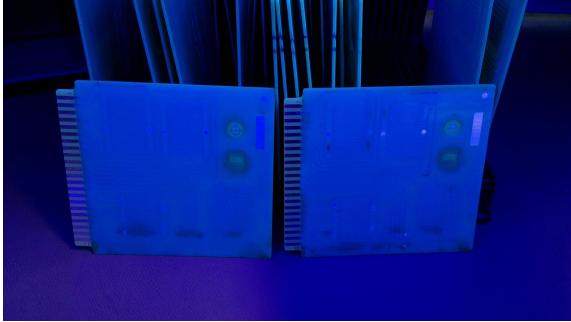

There is no reaction to flux. Board and assembly are free of those residues.Blue color in the top right corner would be misinterpretation (label) – picture no.1.

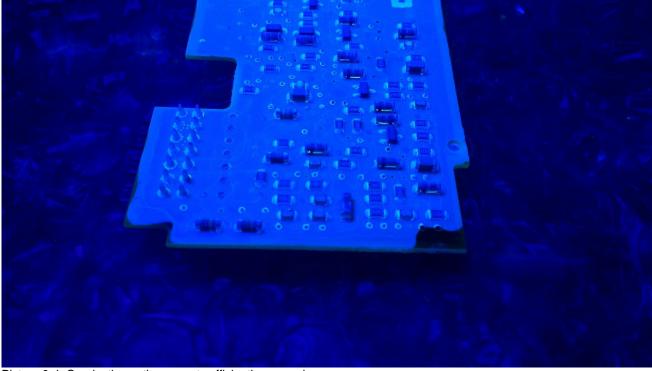

Picture 1: Perfect ZFT on "Board C"

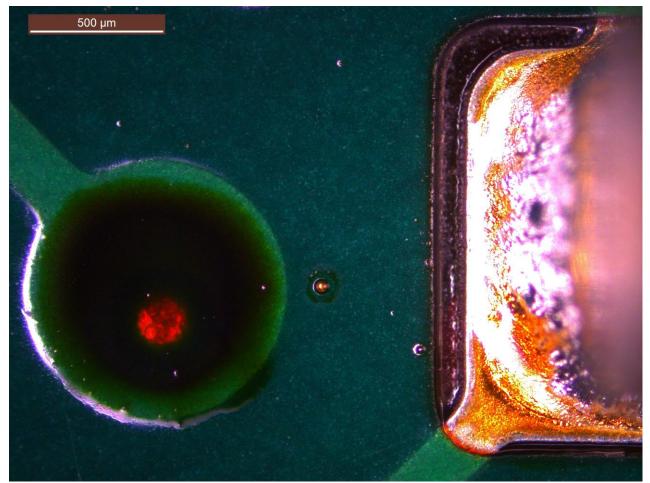

#### Resin test:

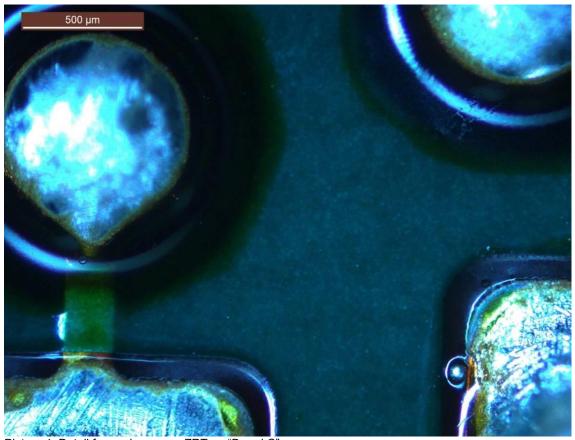

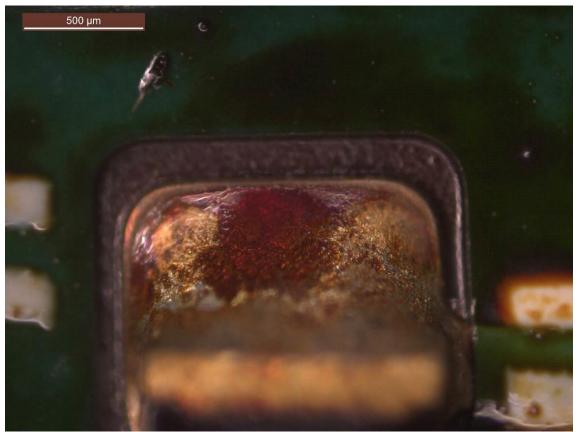

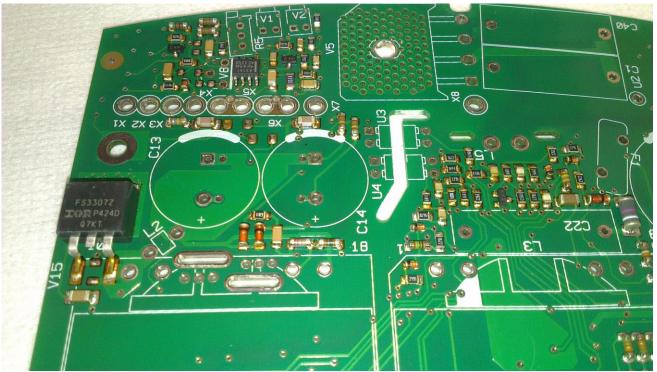

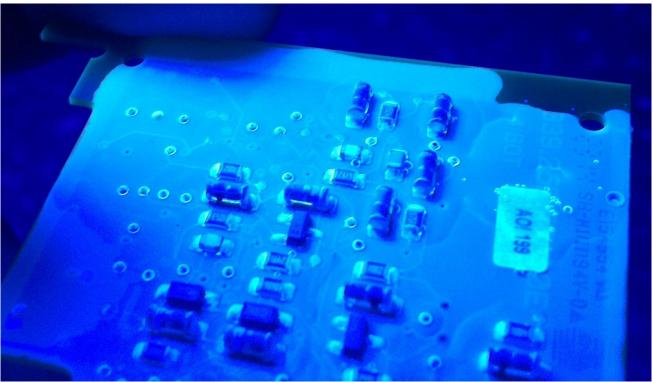

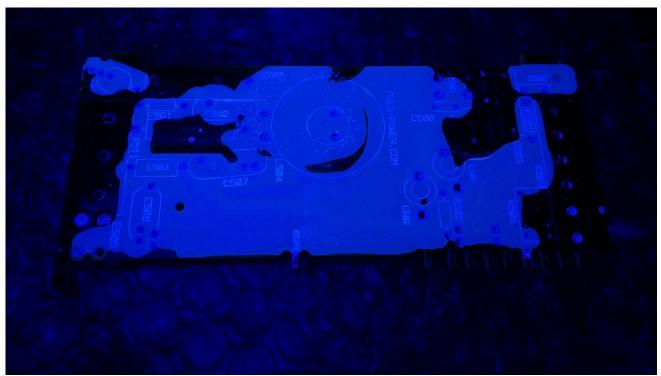

Results show us "very" **high resin residues** from reflow (double reflow, paste) – picture no. 2, no. 3 and no. 4.

Picture 2: ZRT on "Board C"

Picture 3: ZRT on "Board C"

Picture 4: Detail from microscope ZRT on "Board C"

# Comparison to chinese "Board B":

Chinese "Board C" is same (in matter of resin residues) as our "Board C" board. It is same even after long time since it was manufactured.

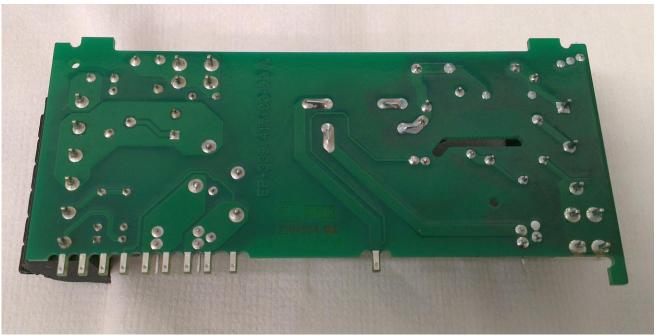

Chinese "Board B" is in good shape. It is similar to CZ results. Main boards after wave soldering are fine.

Picture 5: ZRT on chinese "Board C":

Picture 6: ZRT on chinese "Board C-2":

Note: Affected boards after RLP showed substantially higher resin contaminant levels than boards after wave soldering.

# Additional resin testing:

It is not single issue, but general one. This PCB was measured and even three weeks after it was manufactured it shows same results.

Picture 7: ZRT on "Board D"

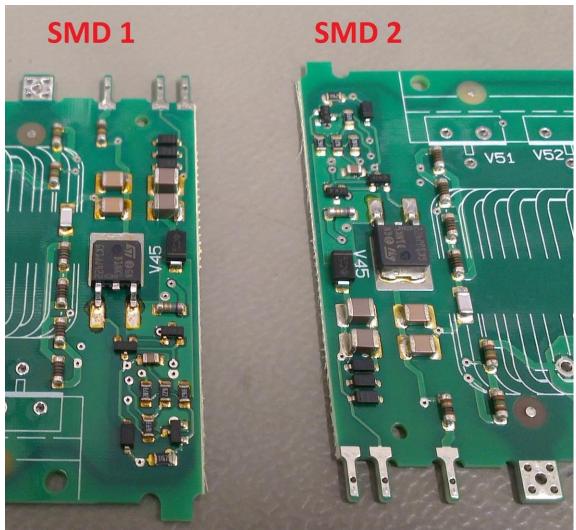

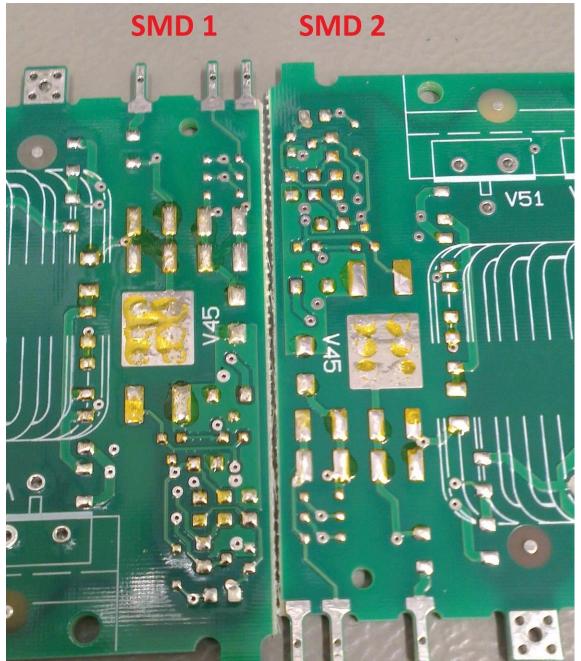

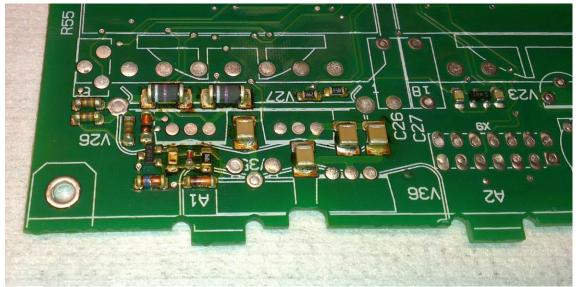

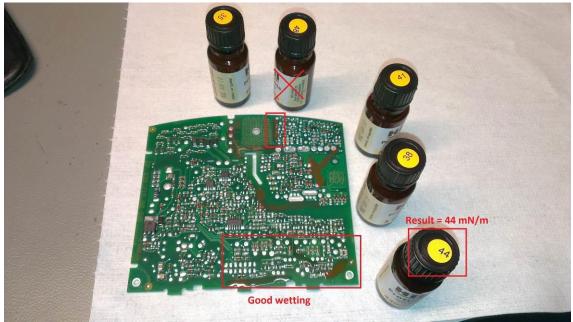

## CZ SMD lines comparison:

"Board E" was taken as standard (I would like to note, that reason for wide range of used boards is simply to be more flexible, time and resources effective as I do test in subordination to manufacturing.)

"Board E" was compared partly assembled (one reflow side) and in second test only paste was applied. This was done one SMD 1 and SMD 2. By comparison we found, that by resin (and also ionic contamination) test **SMD 1 adds more contamination** to the board. In case of ionic contamination it is by 30 %. Zestron resin test is somehow similar (more or less **by 30 %**).

| Multiply [%]      |       |       |              |  |  |

|-------------------|-------|-------|--------------|--|--|

| Affection by SMDs |       | Line  | s difference |  |  |

| SMD 1             | 69,23 | 38,64 | Paste        |  |  |

| SMD 2             | 82,09 | 28,85 | Assembly     |  |  |

| Mean              | 75,66 | 33,74 |              |  |  |

| Chosen            | 75,00 | 30,00 |              |  |  |

Table 10: Comparison contamination of "Board E", see paragraph under table

Table can be easily misinterpreted. SMD line 1 adds more contamination to the board between 30 and 40 % (higher sample might be required). PCB is more contaminated when it is not assembled (more paste is present and "visible" to spectrometer).

Picture 8: Comparison ZRT on "Board E"

Picture 9: Comparison ZRT on "Board E"

### **Results:**

#### Ionic contamination:

lonic contamination of PCBA (SMD) is higher than specified by IPC. In case of module boards it is 2 or 3 times higher. Main boards have lower results. My calculations leads me to believe, that levels are based on pads area. Module boards have higher density of SMDs and are double reflowed. Important will be results broad by practical conformal coating. If those will not fail and process will be under control, then we can manufacture and constantly improve our methods.

#### Resin and flux tests:

Pasted areas shows resin residues. From this perspective wave soldering is clean process. Flux residues are not present on either module or main boards.

#### Comparison tests:

SMD line 1 is 30 % more contaminated than SMD line 2. Resin tests are similar in this manner. There is a different nitrogen atmosphere, which might be a reason. Additional testing is planned.

Resin test are same on CZ and CN side of RLP and wave soldering.

## SMD Paste influence:

<u>Measured contamination</u> is one measured by ionic spectrometer.

<u>SMD</u> is line used to manufacture those.

<u>Unmasked fraction</u> is size of pads related to whole board (not based on gerber data, additional precision might be required).

<u>Reference contamination</u> is measured contamination related to unmasked fraction of the board.

Results are quite constant, which gives me assumption, that contamination is highly based on contamination brought by paste.

Results are altered by several coefficients, which might or might not be questioned.

| Partnumber: | Measured<br>Contamination<br>[µg.cm <sup>-2</sup> - board]: | SMD:    | Unmasked<br>fraction<br>[%]: | Reference<br>contamination [µg.cm <sup>-</sup><br><sup>2</sup> - paste]: |

|-------------|-------------------------------------------------------------|---------|------------------------------|--------------------------------------------------------------------------|

| "Board B"   | 4,29                                                        | Only 2  | 16,24                        | 28,39                                                                    |

|             |                                                             | One on  |                              |                                                                          |

| "Board F"   | 1,02                                                        | 2       | 3,79                         | 26,70                                                                    |

| "Board G"   | 4,43                                                        | Only 2  | 18,78                        | 27,67                                                                    |

|             |                                                             | One on  |                              |                                                                          |

| "Board E"   | 2,23                                                        | 2       | 5,92                         | 31,23                                                                    |

| "Board D"   | 4,30                                                        | 1 and 2 | 17,33                        | 28,32                                                                    |

All of those tests are on higher sample sizes to be relevant.

Table 11: Referencing contamination to pasted area

#### Results are around 30 µg.cm<sup>-2</sup> EQ NaCl related to cm<sup>-2</sup> of pasted area.

#### Calculation:

Reference = f (Measured contamination, Area of board, Area of pads, SMD line, Correction factor added during measurement -20 % added by components, incoming PCB correction)

#### **Basically:**

Reference = (Measured – initial contamination from supplier) \* (coefficient of added area by components) / (Unmasked fraction weighted by 1,30 coefficient according SMD 1 and 2 contamination difference)

#### Reasons:

Initial contamination is either measured or is set to 0,10  $\mu$ g.cm<sup>-2</sup> EQ NaCl according my experience. It is mostly important with lower contamination levels (around 0,80 – 1,00).

Coefficient of added area is important, because area is counted to physical area, while contamination measurement is based on increased area (which is actually higher due to added components).

SMD lines difference coefficient weights (just like weighting is used in mean counting) areas, because single board can be reflowed in both ovens. We needed one result to prove our thought had real basis, which still might or might not have. I have not counted type II error probability, which might be misleading anyway. But my results are based on fact, that module and main boards gone through this test and brought same results.

Different contamination levels, different unmasked areas, different SMD lines lead me to believe, that thought is right. Model is not perfect and paste is not sole contaminant. What we got is an insight.

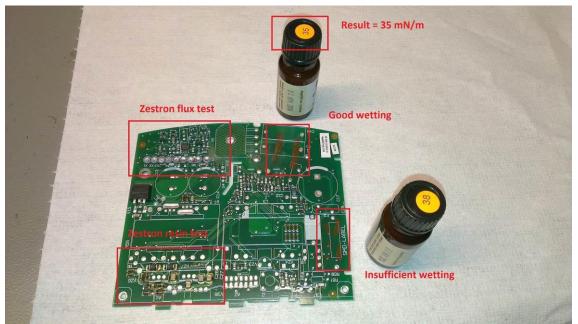

### **Resin test qualification:**

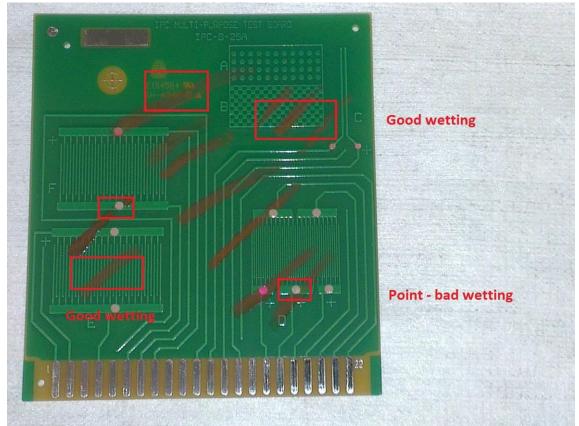

Those results are taken from prior testing (proposed new tin for soldering). There is an method/procedure of how it should be interpreted. But those are great samples for comparison. In this case it was soldering (not SMD paste). In top right is Zestron flux test (ZFT), in bottom left is Zestron resin test (ZRT). Breakdown is nothing means board is perfect. Slightly blue or yellow (brown) indicates beginning of issues. Higher reaction is identified by expressive coloring. Picture no. 10 is perfect example, how board should look like after testing. Only leftovers are on soldermask. Picture no. 11 has beginning issues and process according to standards could be passible, but has to be improved. Last picture - no. 12 shows major residues.

Picture 10: ZRT and ZFT comparisons

Picture 11: ZRT and ZFT comparisons

Picture 12: ZRT and ZFT comparisons

# How oxygen at SMD oven affects contamination:

# Testing:

Two parameters were set as critical, those were inspected. Ionic contamination and resin test.

Sample size was 4 pieces per testing level. Three are used for ionic contamination, one for resin test.

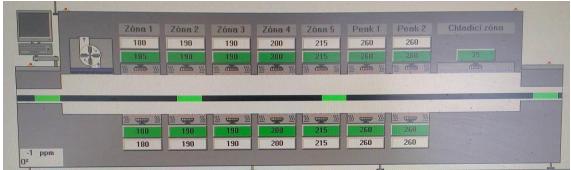

Three testing levels were inspected. According atmosphere analyzer, those were 700, 1500 and 10000 ppm of  $O_2$  in atmosphere. Measuring point was at soak. Soak is where flux is being activated.

Board H was set as standard. (Interestingly, in past Board D2, which is double reflowed showed same results as this single side reflowing.)

SMD line 2, which has better setup and lower  $O_2$  concentration (1000 vs 10000 ppm at reflow point).

| 0 <sub>2</sub> Concentration | 700 ppm | 1500 ppm | 10000 ppm |  |

|------------------------------|---------|----------|-----------|--|

| μ [μg EQ NaCl/sq cm]         | 3,97    | 3,00     | 1,28      |  |

|                              | 3,40    | 2,88     | 3,05      |  |

|                              | 3,07    | 3,67     | 2,19      |  |

|                              |         |          |           |  |

| μ [μg EQ NaCl/sq cm]         | 3,48    | 3,18     | 2,17      |  |

| σ [µg EQ NaCl/sq cm]         | 0,46    | 0,43     | 0,89      |  |

| c [%]                        | 13      | 13       | 41        |  |

### **Results:**

Table 12: Contamination as s function of atmosphere's quality

Standard deviation is very high. I would question those results. During samples preparation stage, atmosphere was not very stable.

On the other hand, it looks by my assumptions according resin test results. Even those are not to be taken as quantifiable.

Resin test was used only on board's fraction.

# How oxygen at SMD oven affects contamination:

### Future of the tests:

Because of setup instability additional testing with higher sample sizes would be required. I will cut 1 500 ppm and use standard (700 ppm) and higher (10 000 ppm).

Main board will be chosen as those seems to be more stable in results.

# **Pictures:**

Picture 13: 700 ppm O<sub>2</sub>

# How oxygen at SMD oven affects contamination:

Picture 14: 1500 ppm O<sub>2</sub>

Picture 15: 10000 ppm O<sub>2</sub>

# Second testing:

Two very distinguish atmospheres, first case was more or less atmosphere of standard process (circa 1 300 ppm of  $O_2$ , rest is  $N_2$ ). Second experiment was 18 000 ppm of  $O_2$ .

Measuring point was same eg. soak (part of the oven, where paste is activated).

| Contamination [µg EQ NaCl . cm <sup>-2</sup> ] |          |           |  |  |

|------------------------------------------------|----------|-----------|--|--|

| O <sub>2</sub>                                 | 1300 ppm | 18000 ppm |  |  |

| Samples                                        | 0,98     | 0,57      |  |  |

|                                                | 1,15     | 0,86      |  |  |

|                                                | 0,66     | 0,58      |  |  |

|                                                | 0,79     | 0,80      |  |  |

|                                                | 1,34     | 0,84      |  |  |

|                                                | 0,80     | 1,02      |  |  |

|                                                | 1,05     | 0,85      |  |  |

|                                                | 0,83     | 1,19      |  |  |

|                                                | 1,01     | 0,88      |  |  |

|                                                | 0,94     | 0,84      |  |  |

| μ                                              | 0,955    | 0,843     |  |  |

| σ                                              | 0,198    | 0,182     |  |  |

| с                                              | 20,7     | 21,6      |  |  |

C

20,7

21,6

Table 13: Second experiment - Contamination as s function of atmosphere's quality

# Evaluation:

Correlation between atmosphere's quality and ionic contamination was not found. Variance of the process is too high. It should be understood as it is not a source of differences between SMD 1's oven and SMD 2's oven.

Very limited range of atmosphere's quality was inspected. Highly inappropriate atmosphere would most likely have serious impact.

All results are hidden within variance of the process and tolerances of the measurement.

# Goal:

Improvement of cleanliness during reflowing process on SMD assembly is key. Is ionic contamination of PCBA's temperature dependent? Can activation of paste (flux) and complete removal of residues be achieved?

# Experiment:

Board H was taken as a sample. 40 boards were divided into two groups. First one was reflowed according general setup. Second one had increased temperature. Contamination was measured 9x2 times (two boards per measurement). Remaining boards were used on flux, resin and tinten test.

# Theory:

(Basic theory to back up the thinking.)

There are four stages in reflow oven: preheat, thermal soak, reflow and cooling. During preheat, thermal rising of 1 - 3 °C per second have to be kept (thermal stress caused to the SMD). Purpose of the thermal soak is activation of the flux and oxidation reduction of the pads. It should be around 1 - 2 minutes. During reflow time (20 - 40 s), solder is activated and joint is created, best possible wetting is desired. Maximal temperature have to be according the weakest component. At temperatures above 260 °C board can be damaged and intermetallic grows. Down ramping around 4 °C per second is recommended. Preheat and soak point temperatures were increased by 10 °C. Therefore activation of the flux should be better. While this increase will not damage the

board and also thermal rising is kept within limits. Speed of the line was not altered and therefore times were not changed.

# SMT process notes:

There are three types of heat profiles in the SMD RLP process. There is also one special for glue hardening. The highest one is for special power boards made of aluminum. Those boards absorb most energy. Lower is for the main boards and the lowest for the module boards.

Some of the difference between the main and module boards could be in this. On the other hand, tests with special board with thermometer were done to match the best profile. This is done on regular (one week) basis.

### **Results:**

No flux residues were detected. Resin test is positive in both cases. Tinten test measured 35 mN.m<sup>-1</sup> (no difference between two profiles). All results are according the long term measurements.

# Attachments:

Picture 16: Flux and resin test (regular profile)

Picture 17: Flux and resin test (profile + 10 °C)

| Contamination [µg . cm <sup>-2</sup> EG NaCl] |      |       |                            |      |       |  |  |

|-----------------------------------------------|------|-------|----------------------------|------|-------|--|--|

| Normal profile                                |      |       | Higher temperature profile |      |       |  |  |

| μ                                             | σ    | C [%] | μ                          | σ    | C [%] |  |  |

| 4,24                                          | 0,61 | 14,5  | 3,86                       | 0,46 | 11,9  |  |  |

Table 14: Contamination difference

Picture 18: Flux and resin test (profile + 10 °C)

Graph 6: Model to point out difference

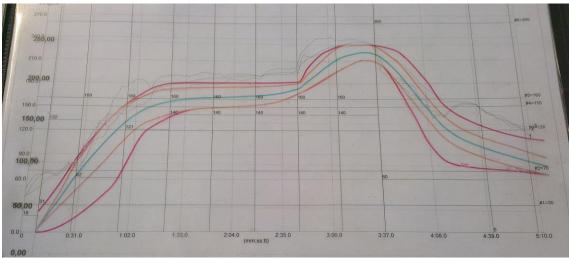

Picture 19: Measured temperature profile

Graph 7: Ionic contamination (Blue = regular, Red = higher temperature)

$$F = \frac{\widehat{\sigma}_1^2}{\widehat{\sigma}_2^2} = \frac{n_1(n_2 - 1) s_1^2}{n_2(n_1 - 1) s_2^2}$$

Calculation 1: Statistical relevance of variation (NOT Relevant)

$$T = \frac{m - \mu_0}{s} \cdot \sqrt{n - 1}$$

Calculation 2: Statistical relevance of means (ARE Relevant)

# **Evaluation:**

Contamination decreased with increased temperature. Difference is around 9 %. Statistical analysis proved, that those differences are relevant (on p = 5 %). And also variation differences are not relevant.

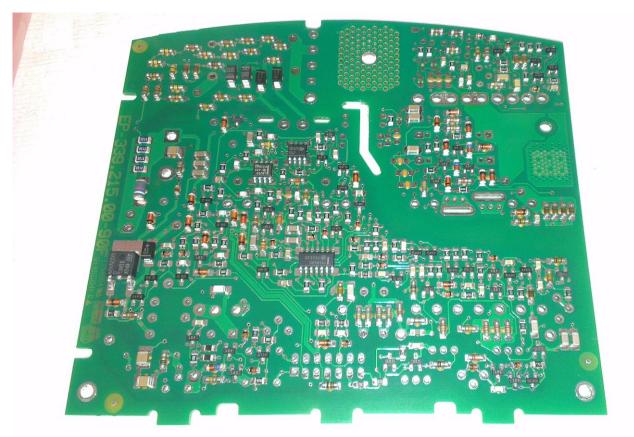

# Goal:

Goal is measurement of ionic contamination of board A, Zestron resin test, zestron flux test and tinten test.

### Notes:

Four samples – 3 measured for ionic contamination, last one taken for additional tests.

Boards went through standard process and manipulation. Boards were stored for around 14 days on stock.

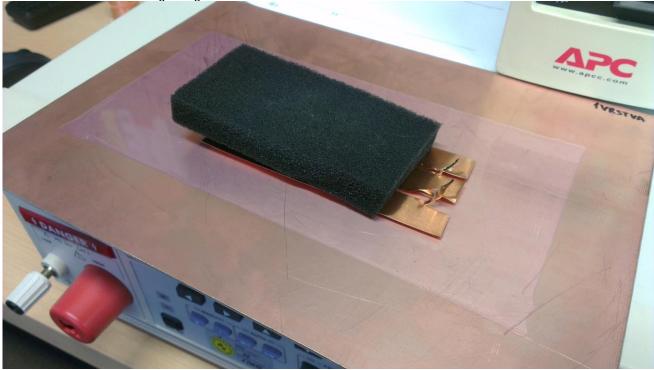

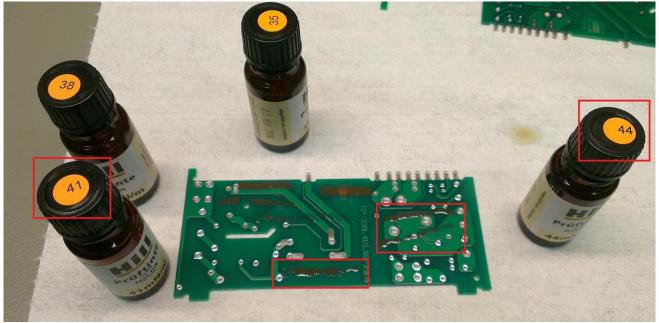

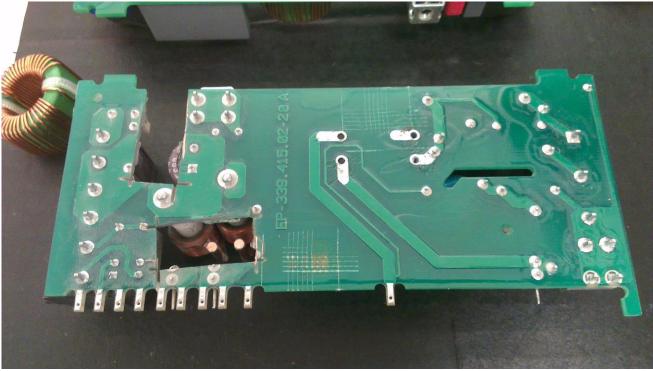

Waving on hall A (Friday = before weekend's maintenance). Boards without THT, additional weight on (shielded by another boards – contamination protection), see Picture 20.

Picture 20: Process of soldering

# **Results:**

| Conta | mination [ | μg . cm <sup>-2</sup> EC | Q NaCl] |

|-------|------------|--------------------------|---------|

| 1     | 2          | 3                        | μ       |

| 10,55 | 10,04      | 10,22                    | 10,27   |

Table 15: Contamination results

| Surface ten | sion [mN/m] |

|-------------|-------------|

| TOP         | BOT         |

| 35          | 44          |

Table 16: Surface tension (tinten test)

Picture 21: Zestron resin test, TOP (paste)

Picture 22: Zestron resin test, TOP (paste)

Picture 23: Zestron resin test, TOP (paste)

Picture 24: Zestron resin test, BOT (solder)

Picture 25: Zestron flux test, TOP (paste + solder)

Picture 26: Zestron flux test, TOP (paste + solder)

Picture 27: Zestron flux test, BOT (solder)

Picture 28: Zestron flux test, BOT (solder)

Picture 29: Tinten test, TOP (reflowed)

Picture 30: Tinten test, BOT (soldered)

# Evaluation:

This board is heavily contaminated. It does not look like, that contamination came from SMD process. Issues with flux residues are not regular and solder wave process is considered free of those issues. Every clue pointed toward maintenance would solve this. This matter is going to be deeply evaluated in the future, as SMD was first priority.

# CCQ – 0 – General introduction:

| Requirement/Specification: | Result/Measurement:    | Status:  |

|----------------------------|------------------------|----------|

| See dedicated chapters     | See dedicated chapters |          |

|                            |                        | ACCEPTED |

# Dense sum:

Qualification of first product is finished

General qualification is going to be finished after:

- IPC boards are evaluated

- Boards from EPN are examined (during another product evaluation)

- HT compatibility during product, that require such abilities

- Process audit

- External (outsourced) companies finish their testing

# **Possible improvements:**

#### Contamination

- Ionic contamination added during reflow and soldering process

- Resin residues added by reflow

- High surface tension of the board

#### Cleanliness

- Handling

- Possible gloves

- Protect the product from hairs, dust, particles and other impurities

#### Uniformity and thickness

- Lower variance of the thickness

- Keep thickness within tolerances (lower safety, upper wrinkles, adhesion, quality and therefore – safety)

- Lower thickness to lower the process costs

| >= RTT:        | Delivered (batch<br>from RTT) is OK.                                                        | NOK<br>(conditionally 22.10.2014 See results down.<br>accepted) RTT uses SL 1306.                                                                  |                                 |                                                                                  | Applies to RTT,<br>same conditions                                                                                                                                                                                                                                                                                                                                                                  | for both.                                                                 |                                                                                         |                                      |

|----------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------|

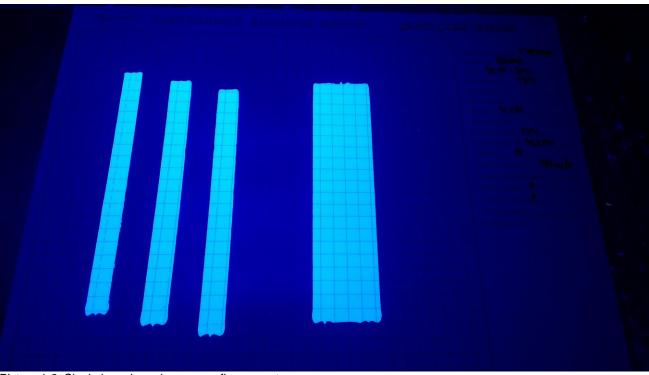

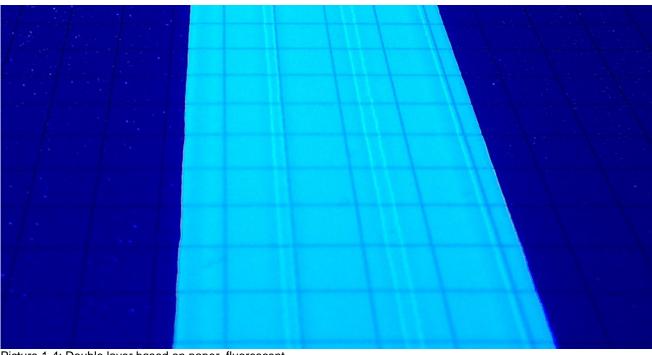

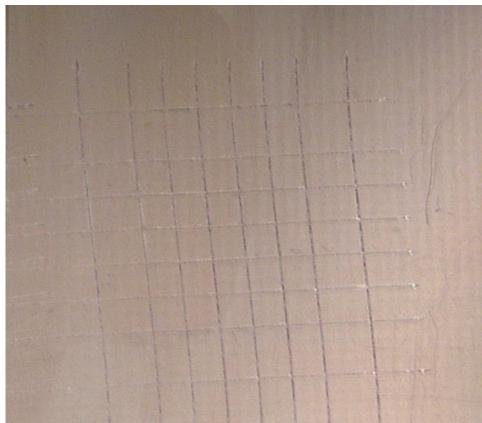

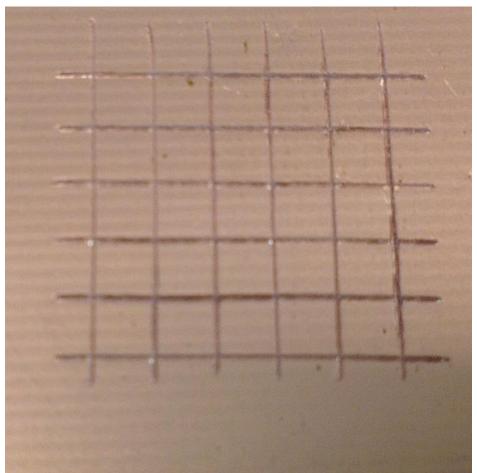

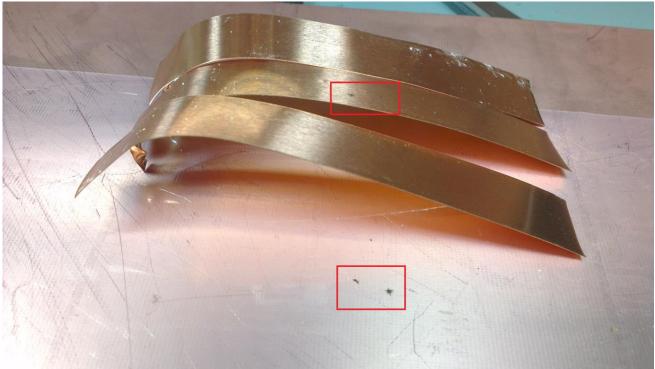

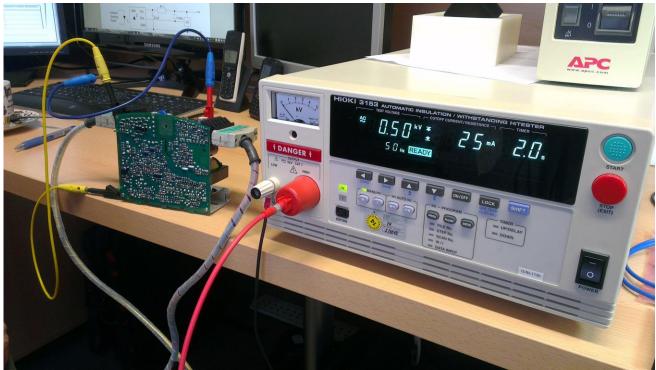

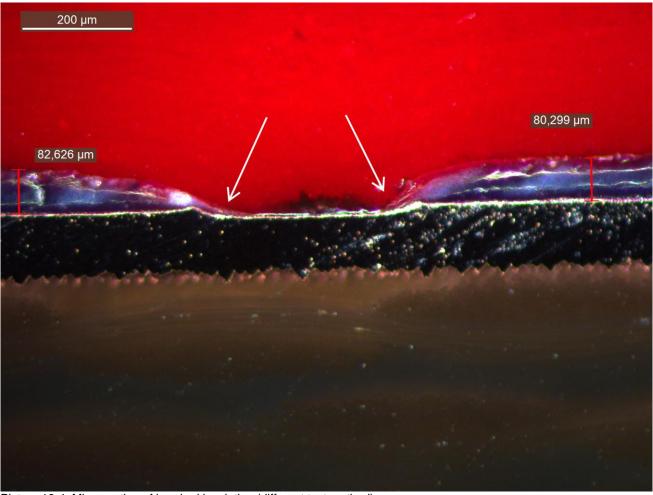

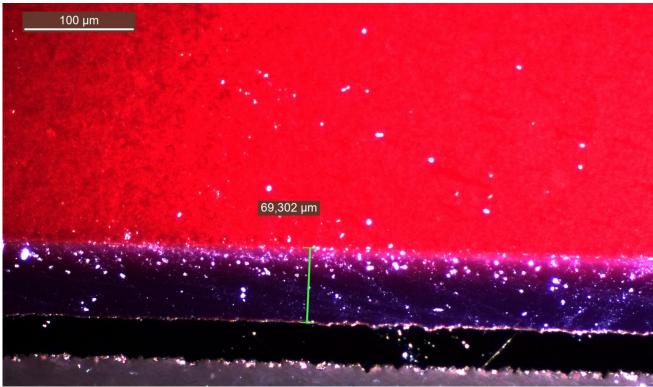

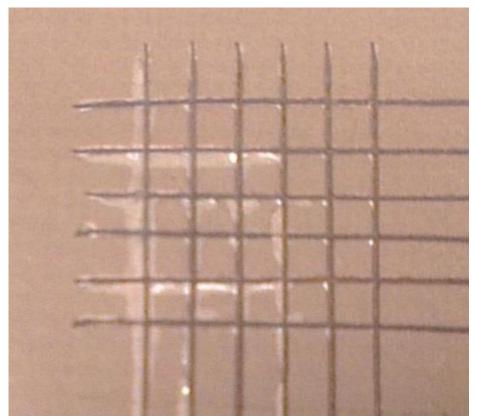

| Finished:      | 23.10.2014                                                                                  | 22.10.2014                                                                                                                                         |                                 |                                                                                  | 10.11.2014                                                                                                                                                                                                                                                                                                                                                                                          | 11.11.2014                                                                | 11.11.2014                                                                              | 11.11.2014                           |