Czech Technical University in Prague Faculty of Electrical Engineering Department of Electric Drives and Traction

Master Thesis

# Modulation Strategies for Voltage Converters

Bc. Jakub Kučka

Supervisor: Ing. Jan Bauer

Study Program: Electrical Engineering, Power Engineering and Management, Master

Study Branch: Electrical Machines, Apparatus and Drives

May 1, 2014

# Aknowledgements

I would like to thank to my supervisor Ing. Jan Bauer for a support, during working on this thesis and Ing. Vít Hlinovský for giving me his time during an absence of my supervisor.

I would also like to thank company teste for lending us Tectronix Power Analyzer.

# Declaration

I hereby declare that I have completed this thesis independently and that I have listed all the literature and publications used.

I have no objection to usage of this work in compliance with the act 60 Zákon č. 121/2000Sb. (copyright law), and with the rights connected with the copyright act including the changes in the act.

.....

# Abstract

This work presents modulation theories for voltage source inverter and matrix converter. It proposes one new modulation method for voltage source inverter, optimized for switching losses minimization. To verify the methods, a modulator design is implemented in VHDL for both converter topologies.

# Abstrakt

Táto práca prezentuje modulačné teórie pre klasický napäťový striedač a pre maticový menič. Navrhuje novú modulačnú metódu pre napäťový striedač, optimalizovanú na spínacie straty. K overeniu popísaných metód boli modulátory pre oba meniče implementované vo VHDL.

# Contents

| 1        | Intr | roducti | on        |                                                | 1        |  |  |  |  |  |

|----------|------|---------|-----------|------------------------------------------------|----------|--|--|--|--|--|

| <b>2</b> | The  | eory    |           |                                                | <b>2</b> |  |  |  |  |  |

|          | 2.1  | -       | e Source  | Inverter                                       | 2        |  |  |  |  |  |

|          |      | 2.1.1   | Function  | nality                                         | 2        |  |  |  |  |  |

|          |      | 2.1.2   | Restrict  | ions                                           | 4        |  |  |  |  |  |

|          |      | 2.1.3   |           | Vector and $\alpha, \beta, 0$ - Transformation | 4        |  |  |  |  |  |

|          |      | 2.1.4   | Known     | Modulation Methods                             | 4        |  |  |  |  |  |

|          |      |         | 2.1.4.1   | Amplitude Modulation                           | 4        |  |  |  |  |  |

|          |      |         | 2.1.4.2   | Sinus Modulation                               | 5        |  |  |  |  |  |

|          |      |         | 2.1.4.3   | Modulation with 3rd Harmonic Injection         | 7        |  |  |  |  |  |

|          |      |         | 2.1.4.4   | Space Vector Modulation                        | 8        |  |  |  |  |  |

|          | 2.2  | Matrix  | c Convert | ter                                            | 10       |  |  |  |  |  |

|          |      | 2.2.1   | Function  | nality                                         | 10       |  |  |  |  |  |

|          |      | 2.2.2   | Modula    | tion Methods                                   | 12       |  |  |  |  |  |

|          |      |         | 2.2.2.1   | Modulation Duty-Cycle Matrix Strategies        | 13       |  |  |  |  |  |

|          |      |         | 2.2.2.2   | Direct Space Vector Modulation                 | 15       |  |  |  |  |  |

|          |      |         | 2.2.2.3   | Indirect Space Vector Modulation               | 15       |  |  |  |  |  |

|          |      | 2.2.3   | Matrix    | Converter Restrictions                         | 21       |  |  |  |  |  |

|          |      |         | 2.2.3.1   | Input Filter                                   | 21       |  |  |  |  |  |

|          |      |         | 2.2.3.2   | Protection Clamp Circuit                       | 22       |  |  |  |  |  |

|          |      |         | 2.2.3.3   | Bidirectional Switches                         | 22       |  |  |  |  |  |

|          |      | 2.2.4   | Commu     | tation Methods                                 | 22       |  |  |  |  |  |

|          |      |         | 2.2.4.1   | Commutation Schema                             | 23       |  |  |  |  |  |

|          |      |         | 2.2.4.2   | Four Step Voltage Commutation                  | 23       |  |  |  |  |  |

|          |      |         | 2.2.4.3   | Two Step Current Commutation                   | 24       |  |  |  |  |  |

|          |      |         | 2.2.4.4   | Output Current Polarity Measurement            | 24       |  |  |  |  |  |

| 3        | Nev  | v Mod   | ulation   | Method for VSI                                 | 26       |  |  |  |  |  |

|          | 3.1  | Princi  | ple       |                                                | 26       |  |  |  |  |  |

|          | 3.2  | -       | -         | ation of Switching Losses                      | 27       |  |  |  |  |  |

|          |      | 3.2.1   | Switchin  | ng Losses by Sinus Modulation                  | 28       |  |  |  |  |  |

|          |      | 3.2.2   |           |                                                |          |  |  |  |  |  |

|          |      | 3.2.3   |           | e Switching Losses                             | 30       |  |  |  |  |  |

|          | 3.3  | Verific |           | Simulation                                     | 32       |  |  |  |  |  |

|          |      | 3.3.1   | Simulat   | ion Parameters                                 | 32       |  |  |  |  |  |

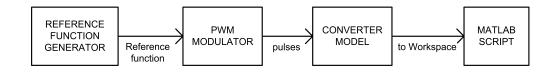

|   |     | 3.3.2    | Simulation Model                                                                                                                                            |

|---|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     |          | 3.3.2.1 Reference Function Generator                                                                                                                        |

|   |     |          | 3.3.2.2 PWM Modulator                                                                                                                                       |

|   |     |          | 3.3.2.3 Converter Model                                                                                                                                     |

|   |     |          | 3.3.2.4 Matlab Script                                                                                                                                       |

|   |     | 3.3.3    | Results                                                                                                                                                     |

|   | 3.4 | Conclu   | 1sion                                                                                                                                                       |

|   |     |          |                                                                                                                                                             |

| 4 |     | olicatio |                                                                                                                                                             |

|   | 4.1 | Contro   | ol System Hardware                                                                                                                                          |

|   |     | 4.1.1    | isa_io2avalon                                                                                                                                               |

|   | 4.2 | Voltag   | ge Source Inverter                                                                                                                                          |

|   |     | 4.2.1    | Converter Loser                                                                                                                                             |

|   |     |          | $4.2.1.1  \text{Description}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              |

|   |     |          | $4.2.1.2  \text{Connectors}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                               |

|   |     | 4.2.2    | Modulator Description                                                                                                                                       |

|   |     |          | 4.2.2.1 VSI_top                                                                                                                                             |

|   |     |          | $4.2.2.2  \text{avalon\_decoder}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                          |

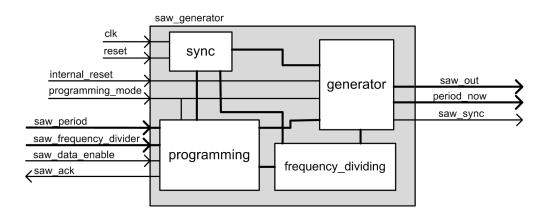

|   |     |          | $4.2.2.3$ saw_generator $\ldots$ $45$                                                                                                                       |

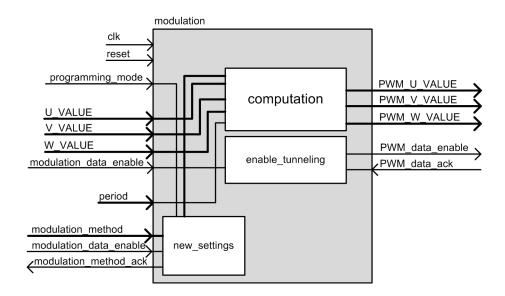

|   |     |          | 4.2.2.4 modulation                                                                                                                                          |

|   |     |          | 4.2.2.5 PWM unit                                                                                                                                            |

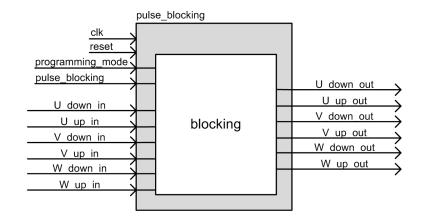

|   |     |          | 4.2.2.6 pulse_blocking                                                                                                                                      |

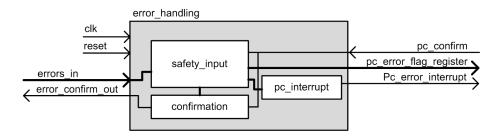

|   |     |          | $4.2.2.7$ error_handling $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 47$                                                                |

|   |     | 4.2.3    | VSI Registers Description                                                                                                                                   |

|   |     | 4.2.4    | VSI C Header                                                                                                                                                |

|   |     | 4.2.5    | VSI Demo Code                                                                                                                                               |

|   | 4.3 |          |                                                                                                                                                             |

|   | 1.0 | 4.3.1    | Matrix Converter Prototype                                                                                                                                  |

|   |     | 1.0.1    | 4.3.1.1 Description                                                                                                                                         |

|   |     |          | 4.3.1.2 Connectors                                                                                                                                          |

|   |     | 4.3.2    | Modulator Description     55                                                                                                                                |

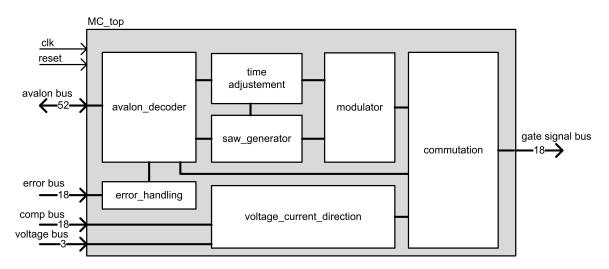

|   |     | 4.0.2    | $4.3.2.1  MC_{top}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                        |

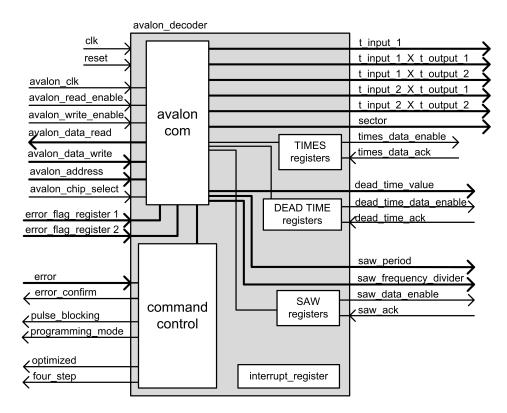

|   |     |          | 1                                                                                                                                                           |

|   |     |          |                                                                                                                                                             |

|   |     |          | 4.3.2.3 saw_generator                                                                                                                                       |

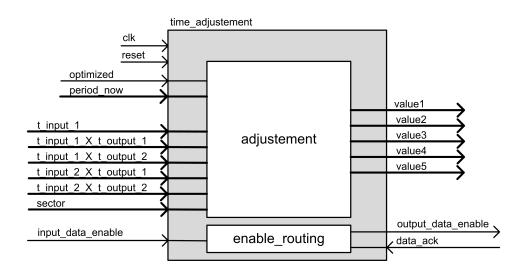

|   |     |          | $4.3.2.4  \text{time}_{\text{adjustement}}  57$                                                                                                             |

|   |     |          | 4.3.2.5 modulator                                                                                                                                           |

|   |     |          | 4.3.2.6 commutation                                                                                                                                         |

|   |     |          | $4.3.2.7  \text{four\_step\_commutation} \dots \dots$ |

|   |     |          | $4.3.2.8  \text{two\_step\_commutation}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                   |

|   |     |          | 4.3.2.9 voltage_current_direction                                                                                                                           |

|   |     |          | $4.3.2.10  \text{current\_decoder}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                        |

|   |     |          | $4.3.2.11  \text{error}\_\text{handling}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                  |

|   |     | 4.3.3    | Registers Description                                                                                                                                       |

|   |     | 4.3.4    | MC C Header                                                                                                                                                 |

|   |     | 4.3.5    | MC Manual UI                                                                                                                                                |

|   |     | 4.3.6    | MC Demo Code                                                                                                                                                |

| <b>5</b> | Experimental Results                                                                                    | 69 |

|----------|---------------------------------------------------------------------------------------------------------|----|

|          | 5.1 Voltage Source Inverter                                                                             | 69 |

|          | 5.1.1 Measurement Stand Description                                                                     | 69 |

|          | 5.1.2 Measured Curves                                                                                   | 70 |

|          | 5.1.3 Losses Measurements                                                                               | 72 |

|          | 5.2 Matrix Converter                                                                                    | 74 |

|          | 5.2.1 Measurement Stand Description                                                                     | 74 |

|          | 5.2.2 Measured Curves                                                                                   | 75 |

| 6        | Conclusion                                                                                              | 77 |

| Bi       | bliography                                                                                              | 78 |

| A        | CD                                                                                                      | 80 |

| В        | Switching Patterns Lookup Table                                                                         | 81 |

| С        | VSI C Header Printout                                                                                   | 83 |

|          | C.1 vsi_def.h                                                                                           | 83 |

|          | C.2 vsi_def.c $\ldots$ | 85 |

| D        | MC C Header Printout                                                                                    | 86 |

|          | D.1 $mc_{def.h}$                                                                                        | 86 |

|          | D.2 mc_def.c $\ldots$  | 88 |

# List of Figures

| 2.1          | Schemes of Voltage Source Inverter                                                                                       | 2               |

|--------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.2          | Simplified Schema of Voltage Source Inverter                                                                             | 3               |

| 2.3          | Line to Line Voltages During One Period and Switching Function.                                                          | 4               |

| 2.4          | Space Vector of Amplitude Modulation in $\alpha, \beta, 0$ Coordinates                                                   | 5               |

| 2.5          | Generation of Switching Functions for IGBT Gates using Sinus Modulation .                                                | 6               |

| 2.6          | Space Vector of Sinus Modulation in $\alpha, \beta, 0$ Coordinates                                                       | 6               |

| 2.7          | Modulation with 3rd Harmonic Injection Reference Function                                                                | 7               |

| 2.8          | Space Vector of 3RDM in $\alpha, \beta, 0$ Coordinates                                                                   | 8               |

| 2.9          | Space Vector Modulation Reference Function                                                                               | 9               |

| 2.10         | Space Vector of Space Vector Modulation in $\alpha, \beta, 0$ Coordinates                                                | 9               |

| 2.11         | Principle Scheme of Matrix Converter                                                                                     | 10              |

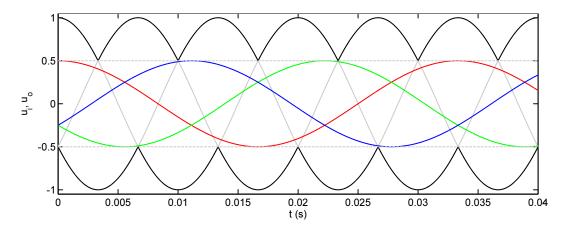

| 2.12         | Alesina-Venturini Reference Function Example, $f_1 = 50$ Hz, $f_2 = 30$ Hz, $A = 0.5$                                    | 14              |

| 2.13         | Alesina-Venturini Optimum Reference Function Example, $f_1 = 50$ Hz, $f_2 = 30$ Hz                                       | z,              |

|              | $A = 0.866 \dots $ | 14              |

| 2.14         | Direct Space Vector Modulation                                                                                           | 15              |

| 2.15         | Principle Schema of Matrix Converter Indirect Modulation Stages                                                          | 16              |

| 2.16         | Indirect Space Vector Modulation                                                                                         | 18              |

| 2.17         | Schema of Matrix Converter built at Czech Technical University                                                           | 21              |

| 2.18         | Practical configuration of a bidirectional switch: (a) common collector IGBT                                             |                 |

|              | switch, (b) common emitter IGBT switch, (c) diode bridge switch, (d) an-                                                 |                 |

|              | tiparallel RGIGBT switch                                                                                                 | 22              |

| 2.19         | Commutation Principle Scheme                                                                                             | 23              |

| 2.20         | Four Step Voltage Commutation Algorithm                                                                                  | 23              |

| 2.21         | Two Step Current Commutation Principle                                                                                   | 24              |

| 2.22         | Current Polarity Measurement Principle                                                                                   | 25              |

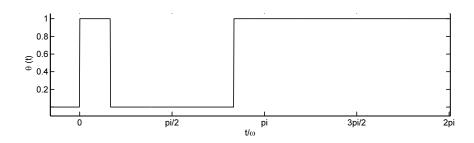

| 3.1          | New Modulation Reference Function                                                                                        | 26              |

| 3.2          | Space Vector of New Modulation in $\alpha, \beta, 0$ Coordinates                                                         | $\frac{20}{27}$ |

| 3.3          | Masking Function $\ldots$               | 21<br>30        |

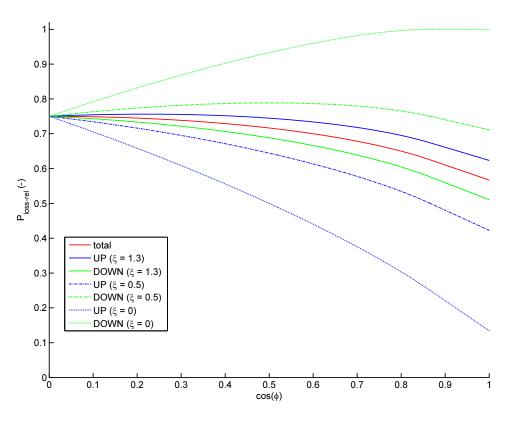

| 3.3          | Relative Losses Derived Analytically.                                                                                    | 31              |

| $3.4 \\ 3.5$ | Simulation principle.                                                                                                    | 32              |

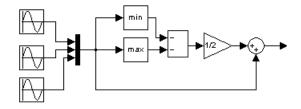

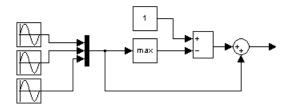

| 3.6          | SM Reference Function Generator                                                                                          | 33              |

| 3.0<br>3.7   | SVM Reference Function Generator                                                                                         | 33              |

| 3.8          | NewM Reference Function Generator                                                                                        | 33<br>34        |

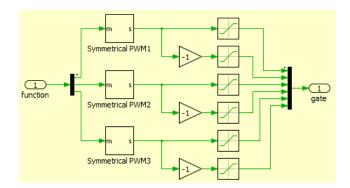

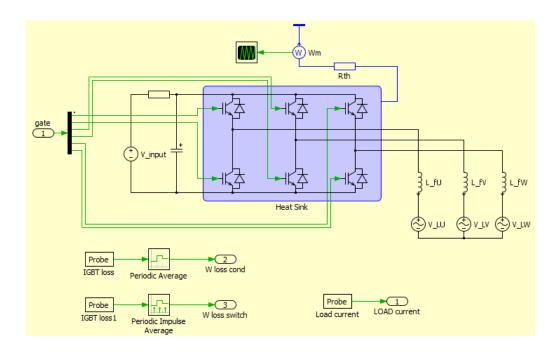

| 3.8<br>3.9   | Plecs Circuit VSI PWM Modulator.                                                                                         | 34<br>34        |

| 3.9<br>3.10  |                                                                                                                          | 34<br>35        |

| 0.10         |                                                                                                                          | <b>J</b> J      |

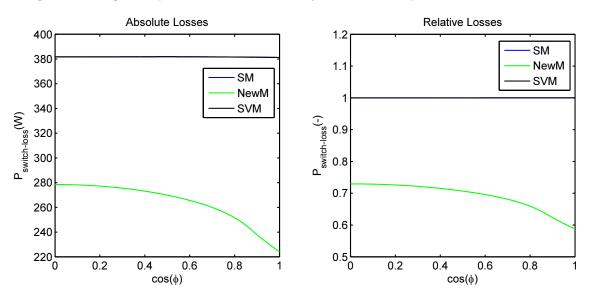

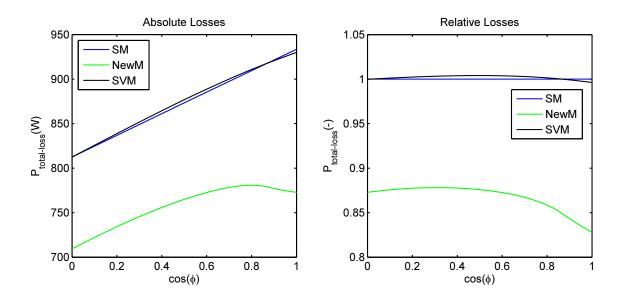

| 3.11 | Switching Losses of Converter for Different Modulations                     |  |  |  |  |  |  |  |

|------|-----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 3.12 | Total Losses of Converter for Different Modulations                         |  |  |  |  |  |  |  |

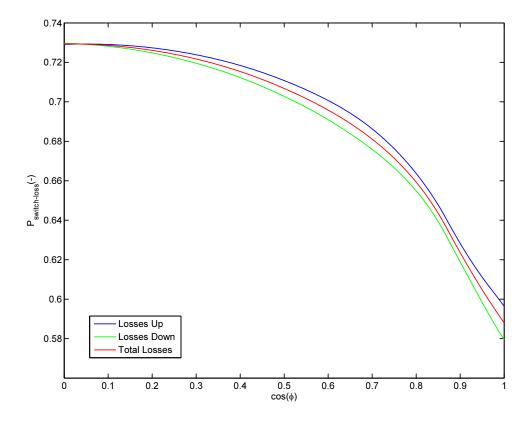

| 3.13 | Relative Losses and its Distribution using New Modulation                   |  |  |  |  |  |  |  |

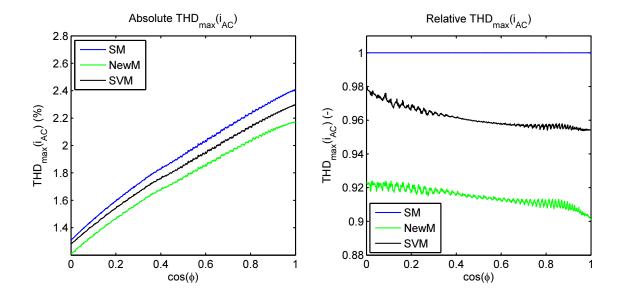

| 3.14 | Total Harmonic Distortion of Output Current for Different Modulations 38    |  |  |  |  |  |  |  |

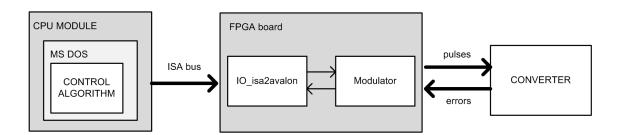

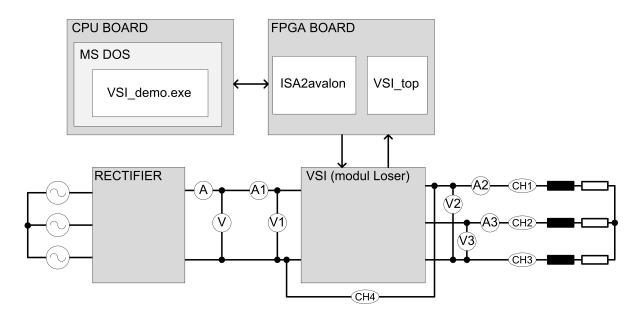

| 4.1  | Control System Hardware Connection                                          |  |  |  |  |  |  |  |

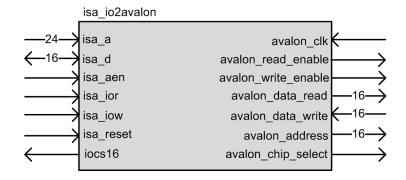

| 4.2  | Bridge isa_io2avalon                                                        |  |  |  |  |  |  |  |

| 4.3  | Picture of Converter Loser, from [4]                                        |  |  |  |  |  |  |  |

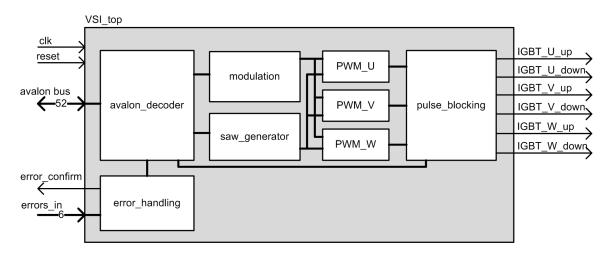

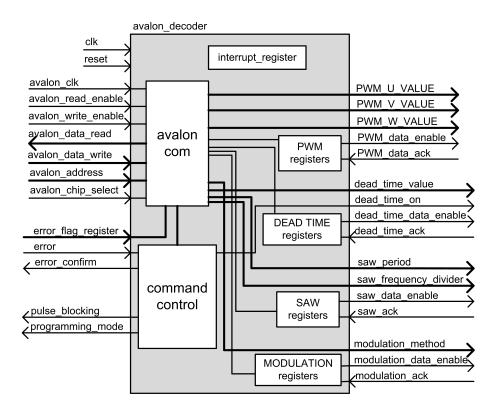

| 4.4  | Top modulator entity VSI_top                                                |  |  |  |  |  |  |  |

| 4.5  | Control entity avalon_decoder                                               |  |  |  |  |  |  |  |

| 4.6  | Saw function signal generator saw_generator                                 |  |  |  |  |  |  |  |

| 4.7  | Modulation calculations unit modulation                                     |  |  |  |  |  |  |  |

| 4.8  | Pulse Width Modulation PWM unit                                             |  |  |  |  |  |  |  |

| 4.9  | Pulse Blocking Unit                                                         |  |  |  |  |  |  |  |

| 4.10 | Error Handling Unit                                                         |  |  |  |  |  |  |  |

| 4.11 | Picture of Matrix Converter Prototype 53                                    |  |  |  |  |  |  |  |

|      | Top modulator entity $MC_{top}$                                             |  |  |  |  |  |  |  |

|      | Control entity avalon_decoder                                               |  |  |  |  |  |  |  |

| 4.14 | Time Period Adjusting Unit time_adjustement                                 |  |  |  |  |  |  |  |

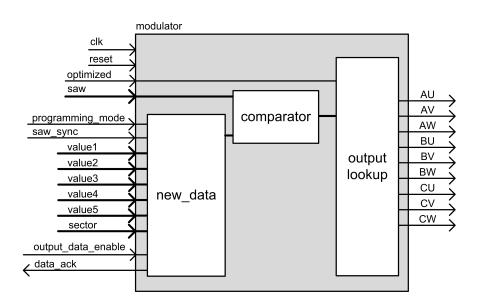

| 4.15 | Modulation Unit modulator                                                   |  |  |  |  |  |  |  |

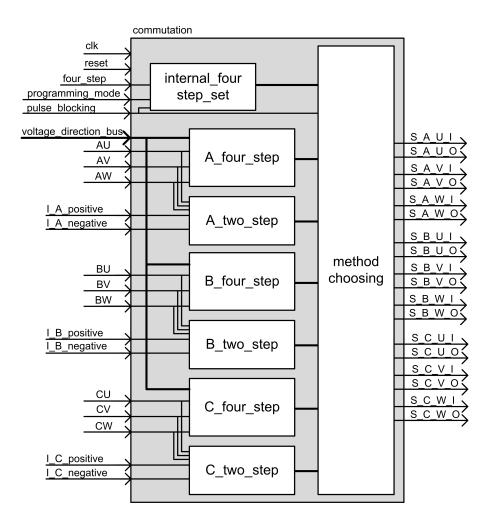

| 4.16 | Commutation Unit commutation                                                |  |  |  |  |  |  |  |

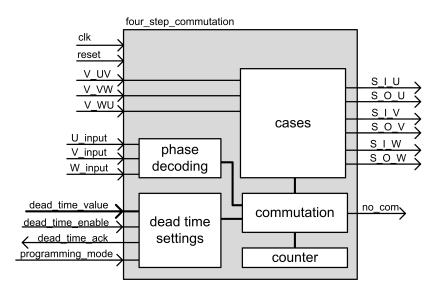

| 4.17 | Four Step Voltage Commutation Unit four_step_commutation                    |  |  |  |  |  |  |  |

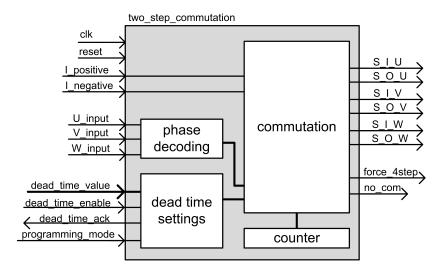

| 4.18 | Two Step Current Commutation Unit two_step_commutation 61                   |  |  |  |  |  |  |  |

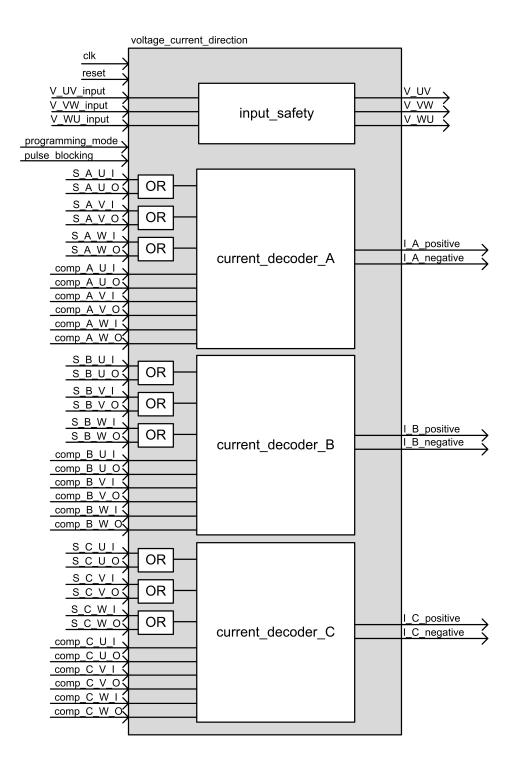

| 4.19 | Polarity Detection Unit voltage_current_direction                           |  |  |  |  |  |  |  |

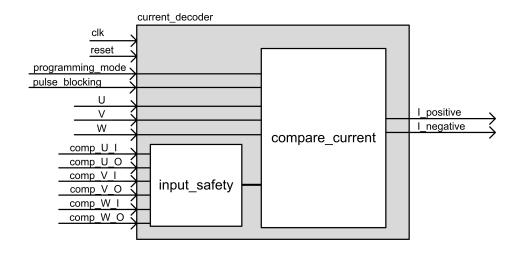

| 4.20 | Output Current Polarity Detection Unit current_decoder.       63            |  |  |  |  |  |  |  |

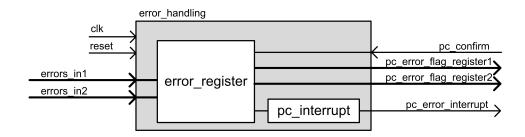

| 4.21 | Error Capturing Unit error_handling                                         |  |  |  |  |  |  |  |

| 5.1  | VSI Measurement Stand Scheme                                                |  |  |  |  |  |  |  |

| 5.2  | VSI Measurement Stand Photo                                                 |  |  |  |  |  |  |  |

| 5.3  | Measured Sinus Modulation Time-Function Curves                              |  |  |  |  |  |  |  |

| 5.4  | Measured Space Vector Modulation Time-Function Curves                       |  |  |  |  |  |  |  |

| 5.5  | Measured New Modulation Time-Function Curves                                |  |  |  |  |  |  |  |

| 5.6  | Measured VSI Efficiency for Different Modulation Methods as a Function of   |  |  |  |  |  |  |  |

|      | Power Factor                                                                |  |  |  |  |  |  |  |

| 5.7  | Measured VSI Relative Losses for Different Modulation Methods as a Function |  |  |  |  |  |  |  |

|      | of Power Factor                                                             |  |  |  |  |  |  |  |

| 5.8  | Measured VSI current THD for Different Modulation Methods as a Function     |  |  |  |  |  |  |  |

|      | of Power Factor                                                             |  |  |  |  |  |  |  |

| 5.9  | MC Measurement Stand Scheme                                                 |  |  |  |  |  |  |  |

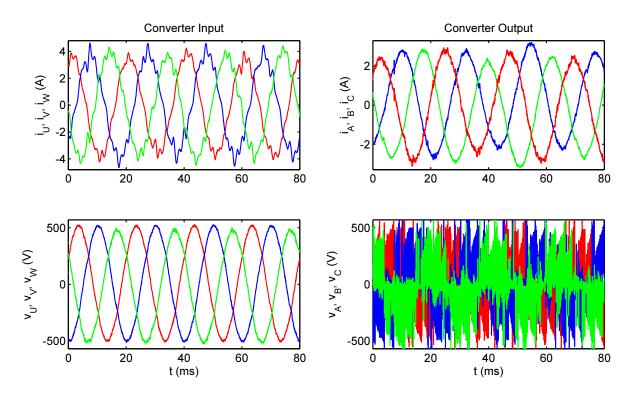

| 5.10 | Measured Voltages and Currents on Matrix Converter Prototype, $f_{out} =$   |  |  |  |  |  |  |  |

|      | 35 Hz, $M_o = 1.15$ , optimized pattern and four step voltage commutation   |  |  |  |  |  |  |  |

|      | are present                                                                 |  |  |  |  |  |  |  |

| 5.11 | Measured Voltages and Currents on Matrix Converter Prototype, $f_{out} =$   |  |  |  |  |  |  |  |

|      | 20 Hz, $M_o = 1$ , optimized pattern and two step current commutation are   |  |  |  |  |  |  |  |

|      | present                                                                     |  |  |  |  |  |  |  |

| 5.12                                                                            | Measured | Voltages | and | Currents | on | Matrix | $\operatorname{Converter}$ | Prototype, | $f_{out} =$ |  |

|---------------------------------------------------------------------------------|----------|----------|-----|----------|----|--------|----------------------------|------------|-------------|--|

| 45 Hz. $M_{\rm o} = 0.9$ , unoptimized pattern and two step voltage commutation |          |          |     |          |    |        |                            |            |             |  |

| 40 nz, $M_0$ = | = 0.9, | unopumized | pattern ar | ia two step | vonage | commutation |    |

|----------------|--------|------------|------------|-------------|--------|-------------|----|

| are present.   |        |            |            |             |        |             | 76 |

# List of Tables

| 2.1 | Table of Switching States for VSI                                        |

|-----|--------------------------------------------------------------------------|

| 2.2 | Table of Matrix Converter Switching States    11                         |

| 2.3 | Table of Virtual Rectifier Switching States    18                        |

| 2.4 | Table of Virtual Inverter Switching States    19                         |

| 2.5 | Table of Vector Interpretation According to Particular Sectors.       19 |

| 2.6 | Non-optimized Switching Pattern                                          |

| 2.7 | Optimized Switching Pattern for Odd Sum of Sectors                       |

| 2.8 | Current Polarity Interpretation                                          |

| 3.1 | Simulation Parameters                                                    |

| 4.1 | Measured approximate times of writing and reading cycle                  |

| 4.2 | Nominal Parameters of Converter Loser                                    |

| 4.3 | Table of connector "PULSES" pins, their interpretation in DIRECT MODE    |

|     | and connection to FPGA board                                             |

| 4.4 | Table of connector "ERROR" pins, their interpretation and connection to  |

|     | FPGA board                                                               |

| 4.5 | Nominal Parameters of Matrix Converter Prototype                         |

| 4.6 | Matrix Converter Driver Connector Signals and Wiring                     |

| 4.7 | FPGA Board Driver Mapping                                                |

| 4.8 | Voltage Polarity Measurement Wiring                                      |

# **Used Shortcuts**

| 3RDM   | Modulation with a 3rd Harmonic Injection |

|--------|------------------------------------------|

| AC     | Alternating Current                      |

| A/D    | Analog to Digital                        |

| AM     | Amplitude Modulation                     |

| CPU    | Central Processing Unit                  |

| DC     | Direct Current                           |

| DSVM   | Direct Space Vector Modulation           |

| FPGA   | Field Programmable Grid Array            |

| FSM    | Final State Machine                      |

| GND    | Ground                                   |

| IGBT   | Insulated Gate Bipolar Transistor        |

| IO     | Input Output                             |

| ISA    | Industry Standard Architecture           |

| ISVM   | Indirect Space Vector Modulation         |

| MC     | Matrix Converter                         |

| MS DOS | Microsoft Disk Operating System          |

| NC     | not connected                            |

| PCI    | Peripheral Component Interconnect        |

| PLL    | Phase Locked Loop                        |

| PWM    | Pulse Width Modulation                   |

| R      | readable                                 |

| RGIGBT | Recessed-Gate IGBT                       |

| SM     | Sinus Modulation                         |

| SVM    | Space Vector Modulation                  |

| THD    | Total Harmonic Distortion                |

| UI     | User Interface                           |

| VHDL   | VHSIC Hardware Description Language      |

| VSI    | Voltage Source Inverter                  |

| W      | writable                                 |

# **Used Physical Variables**

- Eenergy

- dissipated energy

- $\begin{array}{c} E_{\scriptscriptstyle loss} \\ f \end{array}$ frequency

- i, Icurrent

- klinearization coefficient

- Mmodulation degree

- p, Ppower

- $\begin{array}{c} P_{\scriptscriptstyle loss} \\ t \end{array}$ dissipated power

- time

- v, Vvoltage

- angle between voltage and current  $\phi$

- angular speed ω

# **Explanation of Variable Symbols**

| x(t)                     | dependency of variable $x$ on time                            |

|--------------------------|---------------------------------------------------------------|

| $x_{,1}(t)$              | first harmonic of variable $x(t)$                             |

| X                        | value of DC variable                                          |

| $\vec{x}_{\alpha\beta0}$ | space vector of $x_{1,2,3}$ in $\alpha, \beta, 0$ coordinates |

| $X_{RMS}$                | effective value of variable $x(t)$                            |

| $\bar{x}$                | mean value of variable $x(t)$                                 |

| $\hat{x}$                | amplitude of value $x(t)$ (only for periodic functions)       |

| $\underline{X}$          | phasor of variable $x(t)$                                     |

| $x_{max}$                | maximal value of $x(t)$                                       |

| $x_{min}$                | minimal value of $x(t)$                                       |

| $x_{ref}$                | reference value for $x(t)$                                    |

|                          |                                                               |

# Chapter 1 Introduction

In this work, two different converter topologies will be presented. The task of this work is to describe their modulation methods and then implement them in VHDL to verify their functionality.

The Voltage Source Inverter and Matrix Converter were chosen to be presented. The intention is to present modern converters, which are also available at the Department of Electric Drives and Traction, so the that the modulators can be practically verified on prototypes.

Voltage Source Inverter (VSI) is a well known converter, which is very often used in industry and in electrical traction drives. This work explains its modulation strategies and is proposing a new modulation strategy. The task of the new modulation strategy is to lower switching losses of the converter.

The switching losses are currently forming one of the biggest parts of the dissipated power. The amount of dissipated power negatively influences the efficiency of the converter and a cooling system size. The act of lowering this losses, might cause a lowering of a price of the converter.

Matrix Converter (MC) is a relatively novel converter type, which is not presently market-common. The main advantage of DC storage part absence is not that significant in comparison to its overall complexity and high amount of needed active components. Although MC is not economically applicable at the moment, it might be useful in future and is still a topic of a recent research. This work explains its functionality and then focuses on Indirect Space Vector Modulation (ISVM) theory.

To verify functionality of modulation methods, modulators for the both converters mentioned are implemented in VHDL and tested using their converter prototypes at the university department.

# Chapter 2

# Theory

# 2.1 Voltage Source Inverter

**VSI** or "**Voltage Source Inverter**" is a controlled voltage converter. It transfers energy between a DC voltage circuit and an AC current circuit. It is capable of a four-quadrant work, which makes it useful for drive applications.

Since transistors with possible high switching frequency were presented, it is the most common type of converter in drive applications. It is well known and useful because of its simplicity and low THD.

Most of the VSI functionality and modulation principles are going to be explained here. Some more information on this topic can be found at [1] and [2].

### 2.1.1 Functionality

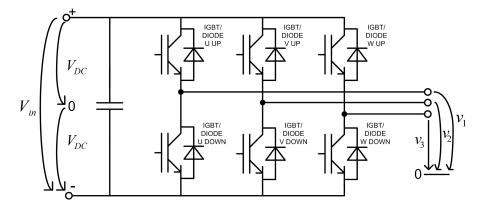

Figure 2.1: Schemes of Voltage Source Inverter

To understand VSI functionality, we have to define virtual zero "0" as the middle of the input DC voltage  $V_{in}$ . Therefore  $+V_{DC}$  is at the same potential as + terminal of input voltage and  $-V_{DC}$  is at the same potential as - terminal. It is obvious that:

$$V_{DC} = \frac{1}{2} V_{in} \tag{2.1}$$

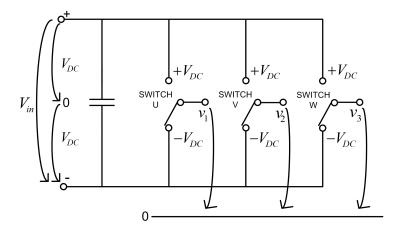

Figure 2.2: Simplified Schema of Voltage Source Inverter

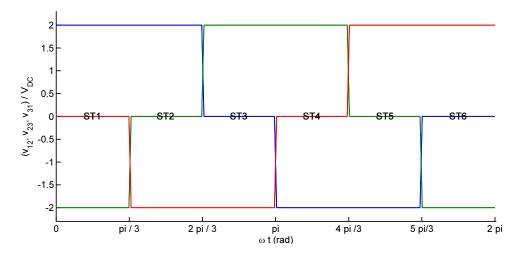

On principle, every IGBT and diode bridge works as an ideal switch (fig. 2.2). It is possible to see, that every output terminal can be connected to either  $+V_{DC}$  or  $-V_{DC}$  in every moment. This gives us eight switching states, which are to be seen in table. 2.1. In this table there are also displayed line to line voltage and value of common voltage  $v_0$  for every switching state.

| State | $v_1$     | $v_2$     | $v_3$     | $v_{12}$   | $v_{23}$   | $v_{31}$   | $v_0$                |

|-------|-----------|-----------|-----------|------------|------------|------------|----------------------|

| ST0   | $-V_{DC}$ | $-V_{DC}$ | $-V_{DC}$ | 0          | 0          | 0          | $-V_{DC}$            |

| ST1   | $+V_{DC}$ | $-V_{DC}$ | $-V_{DC}$ | $+2V_{DC}$ | 0          | $-2V_{DC}$ | $-\frac{1}{3}V_{DC}$ |

| ST2   | $+V_{DC}$ | $+V_{DC}$ | $-V_{DC}$ | 0          | $+2V_{DC}$ | $-2V_{DC}$ | $+\frac{1}{3}V_{DC}$ |

| ST3   | $-V_{DC}$ | $+V_{DC}$ | $-V_{DC}$ | $-2V_{DC}$ | $+2V_{DC}$ | 0          | $-\frac{1}{3}V_{DC}$ |

| ST4   | $-V_{DC}$ | $+V_{DC}$ | $+V_{DC}$ | $-2V_{DC}$ | 0          | $+2V_{DC}$ | $+\frac{1}{3}V_{DC}$ |

| ST5   | $-V_{DC}$ | $-V_{DC}$ | $+V_{DC}$ | 0          | $-2V_{DC}$ | $+2V_{DC}$ | $-\frac{1}{3}V_{DC}$ |

| ST6   | $+V_{DC}$ | $-V_{DC}$ | $+V_{DC}$ | $+2V_{DC}$ | $-2V_{DC}$ | 0          | $+\frac{1}{3}V_{DC}$ |

| ST7   | $+V_{DC}$ | $+V_{DC}$ | $+V_{DC}$ | 0          | 0          | 0          | $+V_{DC}$            |

Table 2.1: Table of Switching States for VSI

By choosing a combination of these eight switching states, we are able to get reference value of voltage on the output as mean value during one switching period. Common methods providing this are PWM or duty-cycle calculation (explained in 2.2.2.3).

# 2.1.2 Restrictions

Instead of ideal switches, IGBTs with diodes are used. As IGBTs do not turn off immediately, it could lead to short circuiting of the input capacitor, what would cause overcurrent and possible converter destruction. Thus, a short period of time is needed between every switching, when both IGBTs are turned off. This time period is called "dead time" and it will have to be included in a modulator design.

# **2.1.3** Space Vector and $\alpha, \beta, 0$ - Transformation

For modulation to be explained it has to be  $\alpha, \beta, 0$  - transformation defined. A power invariant transformation (2.2) was chosen to be used.

$$\vec{x}_{\alpha\beta0} = \begin{bmatrix} x_{\alpha} \\ x_{\beta} \\ x_{0} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} x_{1}(t) \\ x_{2}(t) \\ x_{3}(t) \end{bmatrix}$$

(2.2)

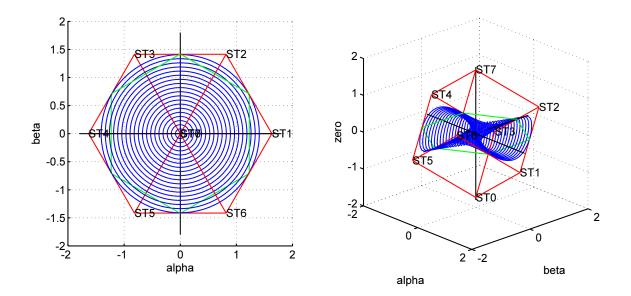

Vector  $[x_{\alpha} \ x_{\beta} \ x_0]$  is called space vector  $\vec{x}_{\alpha\beta0}$ . To hold a sinusoidal line to line output voltage, a projection of space vector to  $\alpha, \beta$  plane ("zero plane") has to be a vector rotating with constant angular speed on a circle (to keep the amplitude constant).

## 2.1.4 Known Modulation Methods

To introduce modulator functionality, some of known modulation methods for VSI are presented.

### 2.1.4.1 Amplitude Modulation

Figure 2.3: Line to Line Voltages During One Period and Switching Function.

AM or "Amplitude Modulation" is the oldest known modulation method. It is the simplest method, with a switching frequency matching the frequency of a generated function. An important disadvantage of this method is a very high THD factor. Another disadvantage is that output voltage amplitude depends on an input voltage level. It was used frequently in past, when a low switching frequency was a significant advantage. With use of IGBT transistors, this method is very uncommon.

The principle of this method is based on a simple switching between the switching states ST1 to ST6, where every switching state is active for one sixth of period. As it was already mentioned before, the amplitude of output voltage is controlled by adjusting of an input DC voltage level. Therefore, a switching function for this method is influenced just by a period length. Switching function is shown in fig. 2.3.

Figure 2.4: Space Vector of Amplitude Modulation in  $\alpha, \beta, 0$  Coordinates.

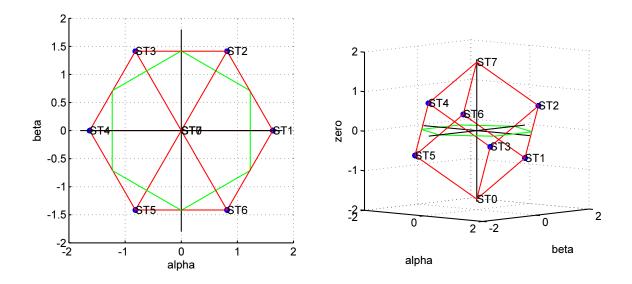

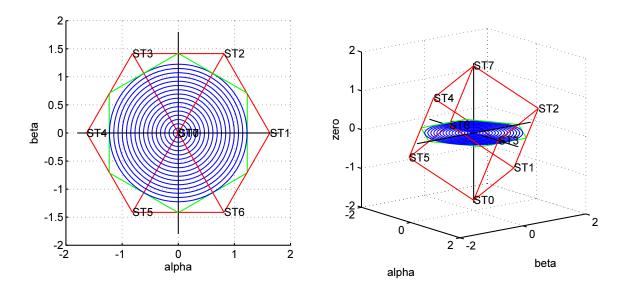

By observing the position of the space vector for this modulation, it is possible to see that it switches discontinuously between all of the switching states. The space vector is represented by the six blue points in fig. 2.4.

In all of the modulation figures in this chapter, the red lines represent the switching cube inside of which all possible space vector states are to be found. The vertexes of the cube are the basic switching states. Green lines represent an intersection of the cube space with the "zero plane". The resulting plane represents an area, where mean value of common voltage during one switching cycle is held at zero. Blue lines or points represent a trajectory of space vector, while using a chosen modulation method.

### 2.1.4.2 Sinus Modulation

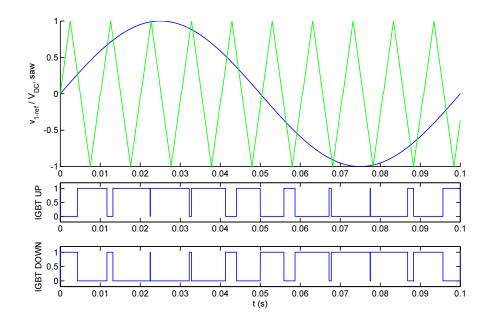

SM or "Sinus Modulation" is practically the simplest method to be understood. It is a method, where the switching function is generated by applying PWM on a sine reference

signal. Generation of this signal is explained in fig. 2.5.

Figure 2.5: Generation of Switching Functions for IGBT Gates using Sinus Modulation

The amplitude is controlled by adjusting an PWM reference signal. The switching frequency does not depend on the output function frequency. An adjustment of modulated signal is performed using modulation degree M.

Figure 2.6: Space Vector of Sinus Modulation in  $\alpha, \beta, 0$  Coordinates.

$$M = \frac{\hat{v}_{ref}}{V_{DC}} \tag{2.3}$$

Voltage  $\hat{v}_{ref}$  is a reference voltage amplitude.

As it is displayed in fig. 2.6, the sinus modulation holds the common voltage  $\bar{v}_0 = 0$  as a mean value during one switching cycle. Every blue line represents a space vector trajectory for different modulation degrees. Maximal modulation degree  $M_{max}$  is limited to value 1, otherwise the vector would exceed the switching cube space and it would come to overmodulation. The low maximal modulation degree is the reason why it is not the only used method (this method is chosen just for small frequencies in electrical drives, where there is not a need for higher modulation degree).

### 2.1.4.3 Modulation with 3rd Harmonic Injection

3RDM or "Modulation with 3rd Harmonic Injection" is a modulation, which solves the maximal modulation degree disadvantage of SM. Its main principle is to inject a common voltage function  $v_{0,ref}$  in all reference voltages. This function is chosen as one sixth of common 3rd harmonic of  $v_{1,ref}$ ,  $v_{2,ref}$  and  $v_{3,ref}$ . As this is a common part of voltage, which is the same in all of the phases, and the zero clamp is not grounded, it does not have any influence on output currents.

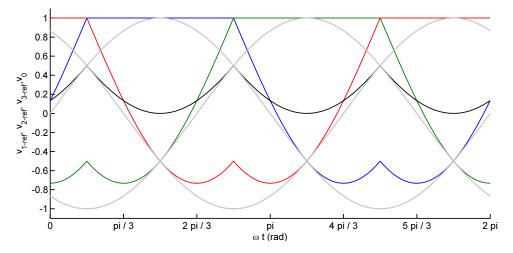

Figure 2.7: Modulation with 3rd Harmonic Injection Reference Function

For reference voltages

$$\begin{bmatrix} v_{1,ref}(t) \\ v_{2,ref}(t) \\ v_{3,ref}(t) \end{bmatrix} = M V_{DC} \begin{bmatrix} \sin(\omega t + \Psi) \\ \sin(\omega t + \Psi + \frac{2\pi}{3}) \\ \sin(\omega t + \Psi + \frac{4\pi}{3}) \end{bmatrix} + v_{0,ref}$$

(2.4)

where  $\Psi$  is an initial angle,  $v_{0,ref}$  is defined as:

$$v_{0,ref}(t) = \frac{1}{6} M V_{DC} \sin(3\omega t + 3\Psi)$$

(2.5)

With 3rd harmonic injection, it is possible to see (fig. 2.7), that a maximum of the reference function  $v_{ref,max}$  is lower then amplitude  $\hat{v}_{ref}$ . From fig. 2.8 left we can determine, that:

$$M_{max} = \frac{1}{\cos 30^o} = \frac{2}{\sqrt{3}} = 1.15470...$$

(2.6)

This is because, the space vector is not sticking to the "zero plane". This is observable in fig. 2.8.

Figure 2.8: Space Vector of 3RDM in  $\alpha, \beta, 0$  Coordinates.

### 2.1.4.4 Space Vector Modulation

SVM or "Space Vector Modulation" is a modulation strategy, which improves 3RDM. The great disadvantage of 3RDM is that an angular speed is needed to calculate the common voltage  $v_{0,ref}$ . An angular speed is not precisely directly measurable and therefore some kind of PLL is needed in a modulator design. This has a relatively great impact on a control stability. SVM, on the other hand, is a method which depends only on actual reference values, what makes it significantly advantageous.

For reference voltages system (2.4) is the common reference voltage defined as:

$$v_{0,ref}(t) = -\frac{\max\left(v_{1,ref}(t), v_{2,ref}(t), v_{3,ref}(t)\right) + \min\left(v_{1,ref}(t), v_{2,ref}(t), v_{3,ref}(t)\right)}{2}$$

(2.7)

Figure 2.9: Space Vector Modulation Reference Function

From fig. 2.9 and fig. 2.10, we can state, that this method has the same advantages as 3RDM, thou it is much easier to implement this method.

Figure 2.10: Space Vector of Space Vector Modulation in  $\alpha, \beta, 0$  Coordinates.

# 2.2 Matrix Converter

MC or "Matrix Converter" is a direct converter. It transfers the energy from an AC voltage circuit to an AC current circuit with sine currents on both sides and with a low THD. Usually, it transfers energy between mains and an AC motor or a power grid with another frequency.

Figure 2.11: Principle Scheme of Matrix Converter

This converter provides operation in all four quadrants, with optional frequency on the both sides (the frequency is limited only by switching frequency). Nevertheless the input power factor is often selected to 1, to keep the maximal transfer ratio between the output and input voltage amplitude of 0.866.

The main benefit of this converter is that there is no DC electrical storage part demand that might make the whole design more compact and it is also possible to start the converter quicker after connecting to mains (there is no need to load the DC capacitor) [6].

There are also few modifications of Matrix Converter topology available and they will not be presented here. If you need this information, please refer to [5].

## 2.2.1 Functionality

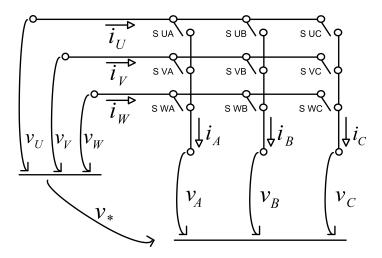

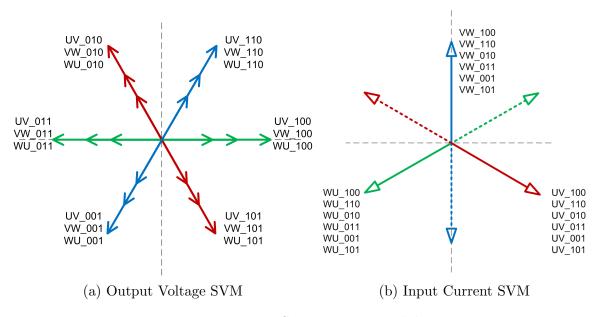

The main idea of this converter topology (fig. 2.11) is to convert energy directly by switching freely one of the input phases (U, V, W) to the output phases (A, B, C).

There are two important restrictions, which determine the count of possible switching states:

• Because of the voltage input source which must not be short circuited, an output phase can be connected just to one input phase at the same time.

• Because of the current output circuit which must not be opened, an output phase has to be constantly connected to some of the input phases.

Therefore every output phase has to be connected to exactly one input phase during the whole time and therefore  $3^3$  of switching states are available.

An overview of switching states is summarized in tab. 2.2. There are three main groups of switching states. The rotating switching states, labeled as Rot, are representing states, when an every output phase is connected to a different input phase. As it will be mentioned later, these switching states cannot be used for Indirect Space Vector Modulation. The second group labeled as UV/VU, VW/WV and WU/UW is a group of active switching states. The third group labeled as zero is a group of zero sequence switching states. There is also an ISVM interpretation included in the table.

|       | UA | UB | UC | VA | VB | VC | WA | WB | WC | ISVM interpretation            |

|-------|----|----|----|----|----|----|----|----|----|--------------------------------|

| Rot   | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | -                              |

|       | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | -                              |

|       | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | -                              |

|       | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | -                              |

|       | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | -                              |

|       | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | -                              |

| UV/VU | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | UV 001, VU 110                 |

|       | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | UV 010, VU 101                 |

|       | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | UV 011, VU 100                 |

|       | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | UV 100, VU 011                 |

|       | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | UV 101, VU 010                 |

|       | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | UV 110, VU 001                 |

| VW/WV | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | VW 001, WV 110                 |

|       | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | VW 010, WV 101                 |

|       | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | VW 011, WV 100                 |

|       | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | VW 100, WV 011                 |

|       | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | VW 101, WV 010                 |

|       | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | VW 110, WV 001                 |

| WU/UW | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | WU 001, UW 110                 |

|       | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | WU 010, UW 101                 |

|       | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | WU 011, UW 100                 |

|       | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | WU 100, UW 011                 |

|       | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | WU 101, UW 010                 |

|       | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | WU 110, UW 001                 |

| zero  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | UV 111, VU 000, UW 111, WU 000 |

|       | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | VU 111, UV 000, VW 111, WV 000 |

|       | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | WU 111, UW 000, WV 111, VW 000 |

Table 2.2: Table of Matrix Converter Switching States

With these switching states, using a modulation strategy, a required operation of MC can be obtained.

#### 2.2.2**Modulation Methods**

To ensure the expected converter operation a modulation has to be present. There are a few possible modulation methods suitable for MC.

Generally, all modulation methods expect symmetric sine voltage and current at the input and the output. In the following equations, input values are labeled with an index i and output values with an index o.

$$\begin{bmatrix} v_U(t) \\ v_V(t) \\ v_W(t) \end{bmatrix} = \hat{v}_i \begin{bmatrix} \cos\left(\omega_i t\right) \\ \cos\left(\omega_i t - \frac{2\pi}{3}\right) \\ \cos\left(\omega_i t - \frac{4\pi}{3}\right) \end{bmatrix}$$

(2.8)

$$\begin{bmatrix} v_A(t) \\ v_B(t) \\ v_C(t) \end{bmatrix} = \hat{v}_o \begin{bmatrix} \cos\left(\omega_o t + \Psi\right) \\ \cos\left(\omega_o t + \Psi - \frac{2\pi}{3}\right) \\ \cos\left(\omega_o t + \Psi - \frac{4\pi}{3}\right) \end{bmatrix} = A \cdot \hat{v}_i \begin{bmatrix} \cos\left(\omega_o t + \Psi\right) \\ \cos\left(\omega_o t + \Psi - \frac{2\pi}{3}\right) \\ \cos\left(\omega_o t + \Psi - \frac{4\pi}{3}\right) \end{bmatrix}$$

(2.9)

$$\begin{bmatrix} i_U(t) \\ i_V(t) \\ i_W(t) \end{bmatrix} = \hat{i}_i \begin{bmatrix} \cos\left(\omega_i t + \varphi_i\right) \\ \cos\left(\omega_i t + \varphi_i - \frac{2\pi}{3}\right) \\ \cos\left(\omega_i t + \varphi_i - \frac{4\pi}{3}\right) \end{bmatrix} = A \cdot \hat{i}_o \begin{bmatrix} \cos\left(\omega_i t + \varphi_i\right) \\ \cos\left(\omega_i t + \varphi_i - \frac{4\pi}{3}\right) \\ \cos\left(\omega_i t + \varphi_i - \frac{4\pi}{3}\right) \end{bmatrix}$$

(2.10)

$$\begin{bmatrix} i_U(t)\\ i_V(t)\\ i_W(t) \end{bmatrix} = \hat{i}_i \begin{bmatrix} \cos\left(\omega_i t + \varphi_i\right)\\ \cos\left(\omega_i t + \varphi_i - \frac{2\pi}{3}\right)\\ \cos\left(\omega_i t + \varphi_i - \frac{4\pi}{3}\right) \end{bmatrix} = A \cdot \hat{i}_o \begin{bmatrix} \cos\left(\omega_i t + \varphi_i\right)\\ \cos\left(\omega_i t + \varphi_i - \frac{2\pi}{3}\right)\\ \cos\left(\omega_i t + \varphi_i - \frac{4\pi}{3}\right) \end{bmatrix}$$

(2.10)

$$\begin{bmatrix} i_A(t)\\ i_B(t)\\ i_C(t) \end{bmatrix} = \hat{i}_i \begin{bmatrix} \cos\left(\omega_o t + \varphi_o + \Psi\right)\\ \cos\left(\omega_o t + \varphi_o + \Psi - \frac{2\pi}{3}\right)\\ \cos\left(\omega_o t + \varphi_o + \Psi - \frac{4\pi}{3}\right) \end{bmatrix}$$

(2.11)

A is a voltage transfer ratio. It is defined as:

$$A = \frac{\hat{v}_o}{\hat{v}_i} \tag{2.12}$$

Every switching state from tab. 2.2 can be written into a matrix form, forming switching state matrix  $\mathbb{S}$ .

$$\mathbb{S} = \begin{bmatrix} S_{UA} & S_{UB} & S_{UC} \\ S_{VA} & S_{VB} & S_{VC} \\ S_{WA} & S_{WB} & S_{WC} \end{bmatrix}$$

(2.13)

To meet the mentioned restrictions (every output phase has to be connected to exactly one input phase during the whole operation), the following equations have to be met.

$$\begin{bmatrix} S_{UA} + S_{UB} + S_{UC} \\ S_{VA} + S_{VB} + S_{VC} \\ S_{WA} + S_{WB} + S_{WC} \end{bmatrix} = \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix}$$

(2.14)

Because a voltage input and a current output are expected, we can determine the input currents and output voltages of the converter using switching state matrix.

$$\begin{bmatrix} u_A \\ u_B \\ u_C \end{bmatrix} = \mathbb{S} \cdot \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix} = \begin{bmatrix} S_{UA} & S_{UB} & S_{UC} \\ S_{VA} & S_{VB} & S_{VC} \\ S_{WA} & S_{WB} & S_{WC} \end{bmatrix} \cdot \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix}$$

(2.15)

$$\begin{bmatrix} i_U \\ i_V \\ i_W \end{bmatrix} = \mathbb{S}^{\mathrm{T}} \cdot \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix} = \begin{bmatrix} S_{UA} & S_{VA} & S_{WA} \\ S_{UB} & S_{VB} & S_{WB} \\ S_{UC} & S_{VC} & S_{WC} \end{bmatrix} \cdot \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix}$$

(2.16)

To obtain reference values of voltage and current, more switching states  $S_i$  have to be used during one switching cycle. To each of the switching states, there is related a duty cycle value  $d_i$ . The values of input current and output voltage are then synthesized after (2.17) and (2.18) as mean values during the whole switching period.

$$\begin{bmatrix} v_A \\ v_B \\ v_C \end{bmatrix} = \sum_{i=1}^{27} d_i \cdot \mathbb{S}_i \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix}$$

(2.17)

$$\begin{bmatrix} i_U \\ i_V \\ i_W \end{bmatrix} = \sum_{i=1}^{27} d_i \cdot \mathbb{S}_i^{\mathrm{T}} \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix}$$

(2.18)

The sequence of individual switching states during the switching cycle is called a switching pattern. There are many possibilities of choosing a pattern and there is also a degree of freedom by choosing which of zero switching states will be used. The selection of the pattern might influence THD, common mode voltage and switching losses.

As following, few modulation methods will be explained. The focus will be concerned mainly on Indirect Space Vector Modulation method. More information on the other modulation methods can be obtained at [6].

### 2.2.2.1 Modulation Duty-Cycle Matrix Strategies

The principle of Modulation Duty-Cycle Matrix Strategies is to calculate a duty cycle matrix, which defines a duty cycle period for every switch separately and then to combine switching states with according switching-state duty-cycle periods to relate to the duty-cycle matrix. Duty-cycle matrix  $\mathbb{D}$  is derived from (2.17) and (2.18).

$$\begin{bmatrix} v_A \\ v_B \\ v_C \end{bmatrix} = \sum_{i=1}^{27} d_i \cdot \mathbb{S}_i \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix} = \begin{bmatrix} d_{UA} & d_{UB} & d_{UC} \\ d_{VA} & d_{VB} & d_{VC} \\ d_{WA} & d_{WB} & d_{WC} \end{bmatrix} \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix} = \mathbb{D} \cdot \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix}$$

(2.19)

$$\begin{bmatrix} i_U \\ i_V \\ i_W \end{bmatrix} = \sum_{i=1}^{27} d_i \cdot \mathbb{S}_i^{\mathrm{T}} \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix} = \begin{bmatrix} d_{UA} & d_{VA} & d_{WA} \\ d_{UB} & d_{VB} & d_{WB} \\ d_{UC} & d_{VC} & d_{WC} \end{bmatrix} \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix} = \mathbb{D}^{\mathrm{T}} \cdot \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix}$$

(2.20)

There are two main methods using this strategy: Alesina-Venturini, Alesina-Venturini Optimum. There were proposed more methods, also called scalar, which are though just modified Alesina-Venturini Optimum Method [6].

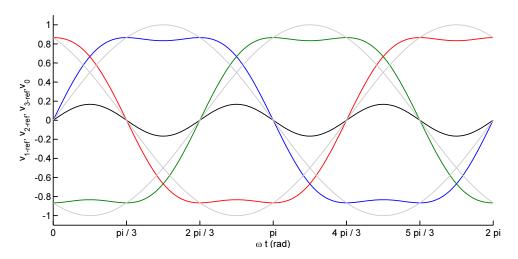

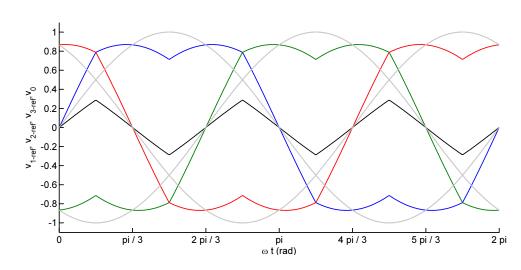

The Alesina-Venturini method calculates the solution directly without injecting any common reference voltage (according to (2.9)). This method's main disadvantage is the low voltage transfer ratio  $A_{max} = 0.5$ . The construction of voltage reference functions can be seen in fig. 2.12.

Figure 2.12: Alesina-Venturini Reference Function Example,  $f_1 = 50$  Hz,  $f_2 = 30$  Hz, A = 0.5

In the figure, the reference input voltage functions are colored gray, the reference output voltage functions are colorful.

The Alesina-Venturini Optimum method increases the voltage transfer ratio to 0.866 using an injection of common mode voltage into output voltage reference function. The reference function is then:

$$\begin{bmatrix} v_A(t) \\ v_B(t) \\ v_C(t) \end{bmatrix} = A \cdot \hat{v}_i \begin{bmatrix} \cos\left(\omega_o t + \Psi\right) \\ \cos\left(\omega_o t + \Psi - \frac{2\pi}{3}\right) \\ \cos\left(\omega_o t + \Psi - \frac{4\pi}{3}\right) \end{bmatrix} - \frac{A \cdot \hat{v}_i}{6} \cos(3\omega_o t + 3\Psi) + \frac{\hat{v}_i}{4} \cos(3\omega_i t)$$

(2.21)

The construction of voltage reference functions of Alesina-Venturini Optimum method can be seen in fig. 2.13.

Figure 2.13: Alesina-Venturini Optimum Reference Function Example,  $f_1=50~{\rm Hz},$   $f_2=30~{\rm Hz},\,A=0.866$

### 2.2.2.2 Direct Space Vector Modulation

The principle of Direct Space Vector Modulation is using Space Vector Modulation Theory originally researched for VSI. The main difference to the VSI theory is the larger amount of switching state options. Also, the length of particular voltage vectors varies during the time.

Similar to VSI, there is a rotating output reference voltage vector, which is synthesized using switching states. By MC DSVM, there are always four active vectors and one zero vector used. In fig. 2.14a, there is a DSVM diagram for output voltage. It is possible to see that in every sector six active vectors are available. Which four of them will be used is selected by input current modulation.

Figure 2.14: Direct Space Vector Modulation

In fig. 2.14b, there is a DSVM diagram for an input current. According to the output reference vector direction, current vectors direction is determined (full line in figure marks positive direction). The suitable vectors for synthesizing of an input current reference vector are then selected. By excluding two non passing output voltage vectors, four switching state vectors are obtained. Combining these four vectors with zero vector, duty cycles of particular switching states are calculated and the input current reference vector and the output voltage reference vector are synthesized.

This modulation method is not going to be used in implementation; therefore deeper calculations are not included. Deeper explanation of this method is to be found in [6].

### 2.2.2.3 Indirect Space Vector Modulation

The principle of ISVM is based on dividing the converter to two virtual stages. The first virtual stage is a virtual rectifier stage, where duty cycles for an input current reference vector

are calculated. The second stage is a virtual inverter stage, where duty cycles for an output voltage reference vector are calculated. The both stages are interconnected with virtual DC circuit. The principle schema is in fig. 2.15.

Figure 2.15: Principle Schema of Matrix Converter Indirect Modulation Stages

For ISVM, two new switching states matrices are defined:  $S_R$  for virtual rectifier stage and  $S_I$  for virtual inverter stage. The turned on switch signifies '1' in the switching state matrices and turned off is '0'. For the possible switching states, the standard VSI restrictions (every phase has to be connected either to  $+\frac{1}{2}v_{DC}$  or to  $-\frac{1}{2}v_{DC}$ ) and Current Source Rectifier restrictions (one phase has to be connected to  $+\frac{1}{2}v_{DC}$  and one to  $-\frac{1}{2}v_{DC}$ ) are relevant.

The virtual rectifier stage voltage equations can be written using virtual rectifier switching state matrix  $S_R$ .

$$\begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix} = \begin{bmatrix} S_{U+} & S_{U-} \\ S_{V+} & S_{V-} \\ S_{W+} & S_{W-} \end{bmatrix} \begin{bmatrix} \frac{1}{2} v_{DC} \\ -\frac{1}{2} v_{DC} \end{bmatrix} = \mathbb{S}_R \cdot \begin{bmatrix} \frac{1}{2} v_{DC} \\ -\frac{1}{2} v_{DC} \end{bmatrix}$$

(2.22)

Similar, we can derive virtual inverter stage voltage equations using  $\mathbb{S}_I$  as:

$$\begin{bmatrix} v_A \\ v_B \\ v_C \end{bmatrix} = \begin{bmatrix} S_{A+} & S_{A-} \\ S_{B+} & S_{B-} \\ S_{C+} & S_{C-} \end{bmatrix} \begin{bmatrix} \frac{1}{2}v_{DC} \\ -\frac{1}{2}v_{DC} \end{bmatrix} = \mathbb{S}_I \cdot \begin{bmatrix} \frac{1}{2}v_{DC} \\ -\frac{1}{2}v_{DC} \end{bmatrix}$$

(2.23)

By merging two equations into one, we get:

$$\mathbb{S}_{I}^{\mathrm{T}} \cdot \begin{bmatrix} v_{A} \\ v_{B} \\ v_{C} \end{bmatrix} = \mathbb{S}_{R}^{\mathrm{T}} \cdot \begin{bmatrix} v_{U} \\ v_{V} \\ v_{W} \end{bmatrix}$$

(2.24)

$$\begin{bmatrix} v_A \\ v_B \\ v_C \end{bmatrix} = \mathbb{S}_I \cdot \mathbb{S}_R^{\mathrm{T}} \cdot \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix}$$

(2.25)

$$\begin{bmatrix} v_A \\ v_B \\ v_C \end{bmatrix} = \begin{bmatrix} S_{A+} & S_{A-} \\ S_{B+} & S_{B-} \\ S_{C+} & S_{C-} \end{bmatrix} \cdot \begin{bmatrix} S_{U+} & S_{V+} & S_{W+} \\ S_{U-} & S_{V-} & S_{W-} \end{bmatrix} \cdot \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix}$$

(2.26)

$$\begin{bmatrix} v_A \\ v_B \\ v_C \end{bmatrix} = \begin{bmatrix} S_{A+}S_{U+} + S_{A-}S_{U-} & S_{A+}S_{V+} + S_{A-}S_{V-} & S_{A+}S_{W+} + S_{A-}S_{W-} \\ S_{B+}S_{U+} + S_{B-}S_{U-} & S_{B+}S_{V+} + S_{B-}S_{V-} & S_{B+}S_{W+} + S_{B-}S_{W-} \\ S_{C+}S_{U+} + S_{C-}S_{U-} & S_{C+}S_{V+} + S_{C-}S_{V-} & S_{C+}S_{W+} + S_{C-}S_{W-} \end{bmatrix} \cdot \begin{bmatrix} v_U \\ v_V \\ v_W \end{bmatrix}$$

(2.27)

Using equation (2.15), we can determine the transformation from the combination of virtual inverter and rectifier switching states to the matrix converter switching state.

$$\mathbb{S} = \begin{bmatrix} S_{A+}S_{U+} + S_{A-}S_{U-} & S_{A+}S_{V+} + S_{A-}S_{V-} & S_{A+}S_{W+} + S_{A-}S_{W-} \\ S_{B+}S_{U+} + S_{B-}S_{U-} & S_{B+}S_{V+} + S_{B-}S_{V-} & S_{B+}S_{W+} + S_{B-}S_{W-} \\ S_{C+}S_{U+} + S_{C-}S_{U-} & S_{C+}S_{V+} + S_{C-}S_{V-} & S_{C+}S_{W+} + S_{C-}S_{W-} \end{bmatrix}$$

(2.28)

As next, we will focus on the space vector modulation. The virtual inverter is modulated as a standard VSI. The virtual rectifier is modulated as a Current Source Rectifier. For following calculations power invariant  $\alpha$ ,  $\beta$ -transformation will be used:

$$\vec{x}_{\alpha\beta} = \begin{bmatrix} x_{\alpha} \\ x_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} x_1(t) \\ x_2(t) \\ x_3(t) \end{bmatrix}$$

(2.29)

Using  $\alpha$ ,  $\beta$ -transformation on equations (2.9) and (2.10), we can obtain relative reference vectors in  $\alpha$ ,  $\beta$  axes.

$$\vec{v}_{o,ref} = \begin{bmatrix} v_{o,ref,\alpha} \\ v_{o,ref,\beta} \end{bmatrix} = \frac{1}{\frac{1}{2}v_{DC}} \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} v_A(t) \\ v_B(t) \\ v_C(t) \end{bmatrix}$$

(2.30)

$$\vec{v}_{o,ref} = M_o \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} \cos\left(\omega_o t + \Psi\right) \\ \cos\left(\omega_o t + \Psi - \frac{2\pi}{3}\right) \\ \cos\left(\omega_o t + \Psi - \frac{4\pi}{3}\right) \end{bmatrix}$$

(2.31)

$$\vec{i}_{i,ref} = \begin{bmatrix} i_{i,ref,\alpha} \\ i_{i,ref,\beta} \end{bmatrix} = \frac{1}{i_{DC}} \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} i_U(t) \\ i_V(t) \\ i_W(t) \end{bmatrix}$$

(2.32)

$$\vec{i}_{i,ref} = M_i \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} \cos\left(\omega_i t + \varphi_i\right) \\ \cos\left(\omega_i t + \varphi_i - \frac{2\pi}{3}\right) \\ \cos\left(\omega_i t + \varphi_i - \frac{4\pi}{3}\right) \end{bmatrix}$$

(2.33)

Here,  $M_i$  and  $M_o$  are modulation degrees for input current and output voltage modulation. Because space vector modulation is used for the virtual inverter, maximal available modulation degree is  $M_{o,max} = 1.15470...$  The maximal available modulation degree for the virtual rectifier is  $M_{i,max} = 1$ .

$$M_o = \frac{\hat{v}_o}{\frac{1}{2}v_{DC}} \tag{2.34}$$

$$M_i = \frac{\hat{i}_i}{i_{DC}} \tag{2.35}$$

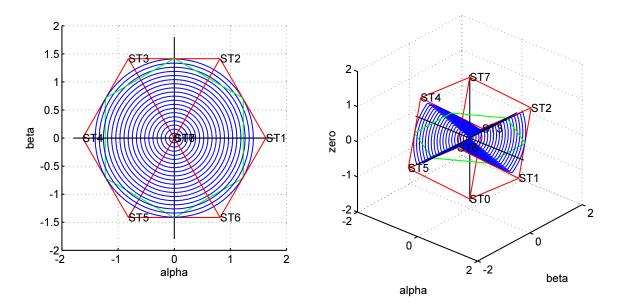

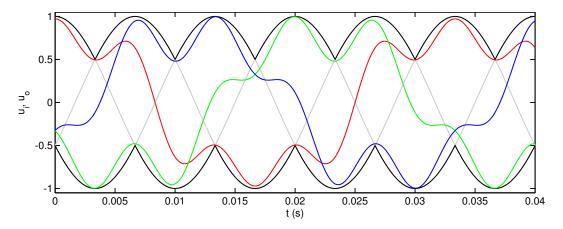

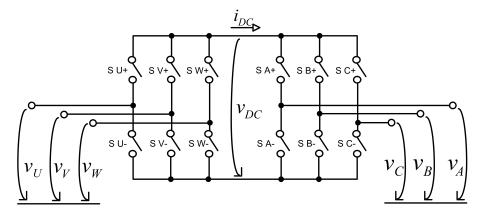

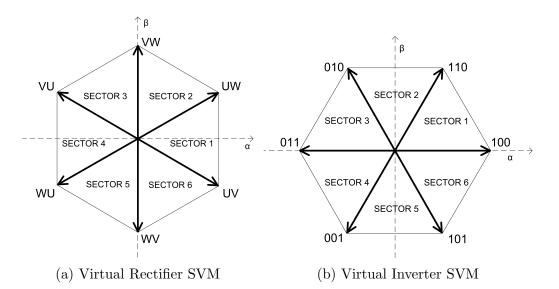

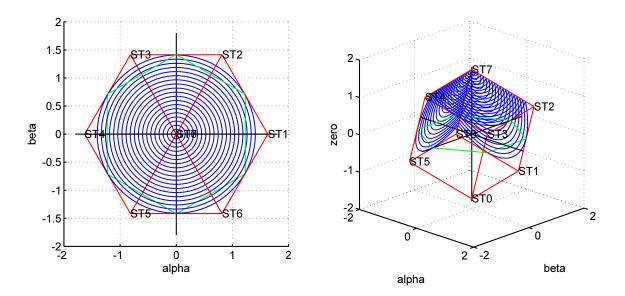

These mentioned reference vectors can be then synthesized using the virtual rectifier and virtual inverter switching state vectors. The switching state vectors for the virtual rectifier are in fig. 2.16a and tab. 2.3. The switching state vectors for the virtual inverter are in fig. 2.16b and tab. 2.4.

Figure 2.16: Indirect Space Vector Modulation

| Vector Name $\vec{s}$ | $s_{lpha}$            | $s_{eta}$             | Active Switches  |

|-----------------------|-----------------------|-----------------------|------------------|

| UV                    | $\sqrt{\frac{3}{2}}$  | $-\sqrt{\frac{1}{2}}$ | $S_{U+}, S_{V-}$ |

| UW                    | $\sqrt{\frac{3}{2}}$  | $\sqrt{\frac{1}{2}}$  | $S_{U+}, S_{W-}$ |

| VW                    | 0                     | $\sqrt{2}$            | $S_{V+}, S_{W-}$ |

| VU                    | $-\sqrt{\frac{3}{2}}$ | $\sqrt{\frac{1}{2}}$  | $S_{V+}, S_{U-}$ |

| WU                    | $-\sqrt{\frac{3}{2}}$ | $-\sqrt{\frac{1}{2}}$ | $S_{W+}, S_{U-}$ |

| WV                    | 0<br>0                | $-\sqrt{2}$           | $S_{W+}, S_{V-}$ |

Table 2.3: Table of Virtual Rectifier Switching States

Using a linear combination of two virtual inverter switching state vectors, it is possible to synthesize an output reference voltage vector. The vectors  $v_{i1}$  and  $v_{i2}$  are chosen according to a virtual inverter modulation sector (tab. 2.5).

$$\vec{v}_{o,ref} = d_{i1} \cdot \vec{v}_{i1} + d_{i2} \cdot \vec{v}_{i2} \tag{2.36}$$

Similarly, using linear combination of two virtual rectifier switching state vectors, it is possible to synthesize an input reference current vector. The vectors  $i_{r1}$  and  $i_{r2}$  are chosen

| Vector Name $\vec{s}$ | $s_{lpha}$                   | $s_{eta}$   | Active Switches          |

|-----------------------|------------------------------|-------------|--------------------------|

| 100                   | $2 \cdot \sqrt{\frac{2}{3}}$ | 0           | $S_{U+}, S_{V-}, S_{W-}$ |

| 110                   | $\sqrt{\frac{2}{3}}$         | $\sqrt{2}$  | $S_{U+}, S_{V+}, S_{W-}$ |

| 010                   | $-\sqrt{\frac{2}{3}}$        | $\sqrt{2}$  | $S_{U-}, S_{V+}, S_{W-}$ |

| 011                   | $-2\cdot\sqrt{\frac{2}{3}}$  | 0           | $S_{U-}, S_{V+}, S_{W+}$ |

| 001                   | $-\sqrt{\frac{2}{3}}$        | $-\sqrt{2}$ | $S_{U-}, S_{V-}, S_{W+}$ |

| 101                   | $\sqrt{\frac{2}{3}}$         | $-\sqrt{2}$ | $S_{U+}, S_{V-}, S_{W+}$ |

Table 2.4: Table of Virtual Inverter Switching States

according to a virtual inverter modulation sector (tab. 2.5).

$$\vec{i}_{i,ref} = d_{r1} \cdot \vec{i}_{r1} + d_{r2} \cdot \vec{i}_{r2} \tag{2.37}$$

|        | Virtua         | l Inverter     | Virtual Rectifier |                |  |

|--------|----------------|----------------|-------------------|----------------|--|

| Sector | $\vec{v}_{i1}$ | $\vec{v}_{i2}$ | $\vec{i}_{r1}$    | $\vec{i}_{r2}$ |  |

| 1      | 100            | 110            | UV                | UW             |  |

| 2      | 110            | 010            | UW                | VW             |  |

| 3      | 010            | 011            | VW                | VU             |  |

| 4      | 011            | 001            | VU                | WU             |  |

| 5      | 001            | 101            | WU                | WV             |  |

| 6      | 101            | 100            | WV                | UV             |  |

Table 2.5: Table of Vector Interpretation According to Particular Sectors.

In contrast with standard Active Front End topology, there is a synchronization needed between the first and the second stage (because there is not a DC storage part present). There are more possible switching patterns. In this work two of them will be implemented according to [6]. A non-optimized switching pattern follows:

|                            | $\vec{i}_{r1}$                        |                         |                            | $\vec{i}_{r2}$             |                            | $\vec{i}_{r1}$             |                            |                            |                            |

|----------------------------|---------------------------------------|-------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| $\frac{1}{2}$              | $\frac{1}{2} \cdot d'_{r1}$ $d'_{r2}$ |                         |                            |                            |                            |                            | $rac{1}{2} \cdot d'_{r1}$ |                            |                            |

| $\vec{v}_{i1}$             | $\vec{v}_{i2}$                        | $\vec{v}_0$             | $\vec{v}_{i2}$             | $\vec{v}_{i1}$             | $\vec{v}_{i1}$             | $\vec{v}_{i2}$             | $\vec{v}_0$                | $\vec{v}_{i2}$             | $\vec{v}_{i1}$             |

| $\frac{1}{2} \cdot d_{11}$ | $\frac{1}{2} \cdot d_{12}$            | $\frac{1}{2} \cdot d_0$ | $\frac{1}{2} \cdot d_{22}$ | $\frac{1}{2} \cdot d_{21}$ | $\frac{1}{2} \cdot d_{21}$ | $\frac{1}{2} \cdot d_{22}$ | $\frac{1}{2} \cdot d_0$    | $\frac{1}{2} \cdot d_{12}$ | $\frac{1}{2} \cdot d_{11}$ |

Table 2.6: Non-optimized Switching Pattern

The pattern table presents a sequence of the switching state vectors of the virtual

inverter and virtual rectifier together with duty-cycle period ratios. The duty-cycle ratios are calculated as follows:

$$d_{11} = d_{r1} \cdot d_{i1} \tag{2.38}$$

$$d_{12} = d_{r1} \cdot d_{i2} \tag{2.39}$$

$$d_{21} = d_{r2} \cdot d_{i1} \tag{2.40}$$

$$d_{22} = d_{r2} \cdot d_{i2} \tag{2.41}$$

$$d_0 = 1 - d_{11} - d_{12} - d_{21} - d_{22} \tag{2.42}$$

Because the length of a zero vector is defined by the virtual inverter, it is no need to include a zero vector by the virtual rectifier. Therefore the duty-cycle period is adjusted on the whole period:

$$d'_{r1} = \frac{d_{r1}}{d_{r1} + d_{r2}} \tag{2.43}$$

$$d'_{r2} = \frac{d_{r2}}{d_{r1} + d_{r2}} \tag{2.44}$$

It is possible to see, that while using the non-optimized pattern, there is a switching present during zero vector presence. The main task of the pattern optimizing is to remove this switching. Optimized pattern differs according to a sector sum (input sector number + output sector number). If the sum is even, the pattern is same as when non-optimized. If the sum is odd, the pattern is changed.

|                            | $\vec{i}_{r1}$             |                         |                            | $\vec{i}_{r2}$             |                            | $\vec{i}_{r1}$             |                         |                             |                            |  |

|----------------------------|----------------------------|-------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-------------------------|-----------------------------|----------------------------|--|

| $\frac{1}{2}$              | $\cdot d'_{r1}$            |                         | $d'_{r2}$                  |                            |                            |                            |                         | $\frac{1}{2} \cdot d'_{r1}$ |                            |  |

| $\vec{v}_{i2}$             | $\vec{v}_{i1}$             | $\vec{v}_0$             | $\vec{v}_{i1}$             | $\vec{v}_{i2}$             | $\vec{v}_{i2}$             | $\vec{v}_{i1}$             | $\vec{v}_0$             | $\bar{\vec{v}}_{i1}$        | $\vec{v}_{i2}$             |  |

| $\frac{1}{2} \cdot d_{12}$ | $\frac{1}{2} \cdot d_{11}$ | $\frac{1}{2} \cdot d_0$ | $\frac{1}{2} \cdot d_{21}$ | $\frac{1}{2} \cdot d_{22}$ | $\frac{1}{2} \cdot d_{22}$ | $\frac{1}{2} \cdot d_{21}$ | $\frac{1}{2} \cdot d_0$ | $\frac{1}{2} \cdot d_{11}$  | $\frac{1}{2} \cdot d_{12}$ |  |

Table 2.7: Optimized Switching Pattern for Odd Sum of Sectors

Both, the optimized and the non-optimized pattern lookup tables are to be found in appendix B.

To determine the influences on maximal voltage transfer ratio, we have to determine influences on the maximal  $u_{DC}$ , using energy conservation law.

$$P_i = P_{DC} \tag{2.45}$$

$$\frac{3}{2}\hat{i}_i\hat{u}_i\cos\varphi_i = u_{DC}i_{DC} \tag{2.46}$$

$$u_{DC} = \frac{3}{2} \frac{\hat{i}_i}{i_{DC}} \cos \varphi_i = \frac{3}{2} M_i \cos \varphi_i \tag{2.47}$$

From equation (2.47), we can determine that maximal voltage transfer ratio is available, for  $M_i = 1$  and  $\cos \varphi_i = 1$ .

### 2.2.3 Matrix Converter Restrictions

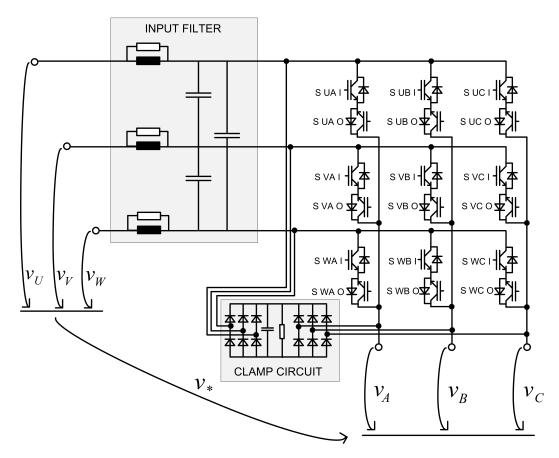

To build a Matrix Converter few restrictions have to be met. The ideal bidirectional switch has to be replaced with a combination of real switches, the input current distortion, caused by switching, has to be reduced by a filter and additional protection clamp circuit has to be added for a case of converter failure.

The schema of converter built at Czech Technical University at Department of Electric Drives and Traction is in fig. 2.17.

Figure 2.17: Schema of Matrix Converter built at Czech Technical University

### 2.2.3.1 Input Filter

The main task of the input filter (also drawn in fig. 2.17) is to reduce a current distortion caused by switching. Generally, a LC filter is chosen for this purpose. The converter prototype uses a series damped filter. More information about the input filter can be found in [6] and [5].

#### 2.2.3.2 Protection Clamp Circuit

The main task of the protection clamp circuit is to protect the converter from overvoltages and overcurrents. It consists of two rectifier bridges with a use of fast recovery diodes, which are connected to a storage capacitor. This capacitor should be able to store all energy from parasite inductions in case of an emergency breaking of the converter. More information on this topic can be found at [6] and [5].

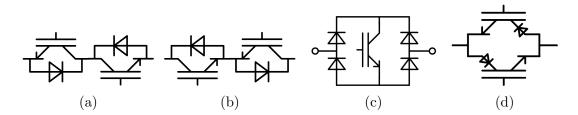

#### 2.2.3.3 Bidirectional Switches

There is a number of possibilities of emulating a bidirectional switch. The known opportunities are in fig. 2.18.

Figure 2.18: Practical configuration of a bidirectional switch: (a) common collector IGBT switch, (b) common emitter IGBT switch, (c) diode bridge switch, (d) antiparallel RGIGBT switch

The most common are configurations (a) and (b). An advantage of a common collector configuration is that drivers for both switches can use a same ground. At the university prototype, there is a common emitter configuration used.

The configuration (c) is not applicable for MC because there is not a safe commutation guaranteed. The configuration (d) is a configuration using novel components RGIGBT. Because of their relatively high price and relatively poor properties, they are not usable at the moment.

To obtain more information about bidirectional switches, please refer to [5].

### 2.2.4 Commutation Methods

To switch safely from one input phase to another without short circuiting them, there is a commutation demanded.

There are several commutation methods available. The commutation methods differ on the basis of how a commutation switching sequence is decided. There are current, voltage or combined commutation methods [5]. Every single commutation cycle is done mostly in two or four steps, depending on the particular method.

In this part, there will be two commutation methods explained, which will also be

implemented into a modulator design in a next chapter. To obtain more information about commutation methods, please refer to [5], [6] and [7].

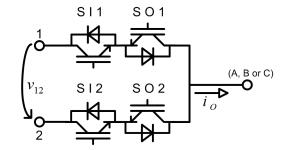

#### 2.2.4.1 Commutation Schema

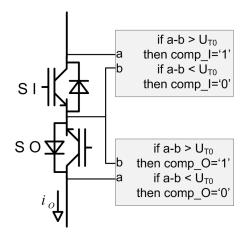

For commutation to be explained, a commutation scheme is presented in fig. 2.19.

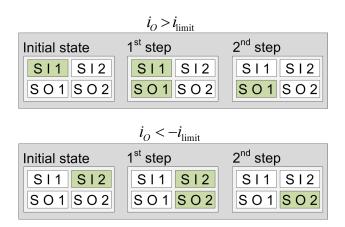

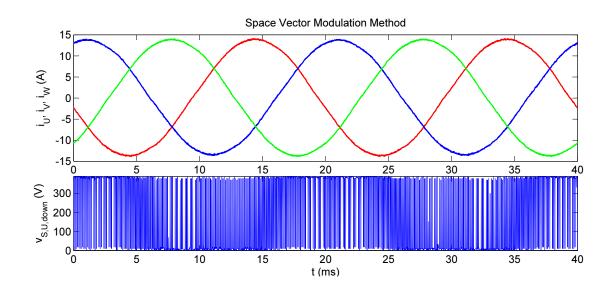

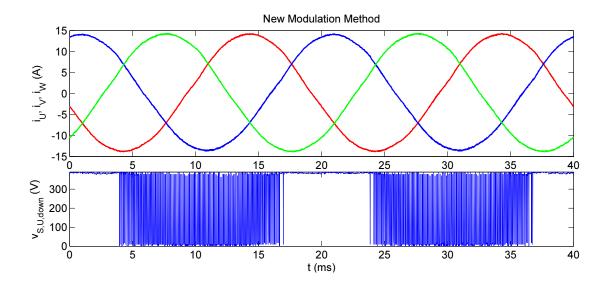

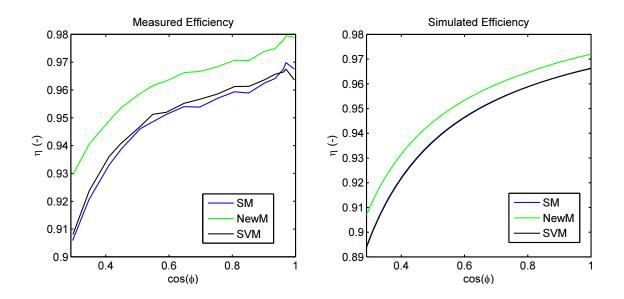

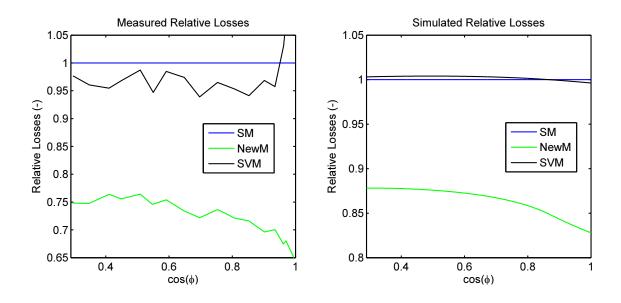

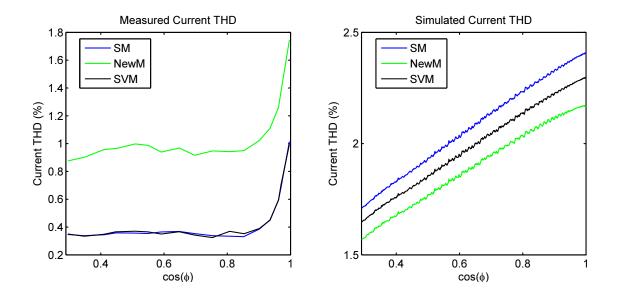

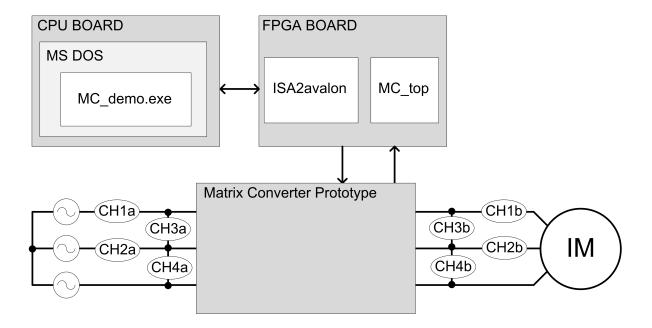

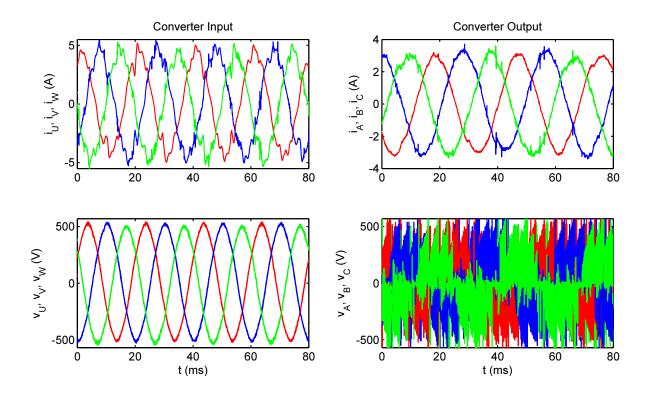

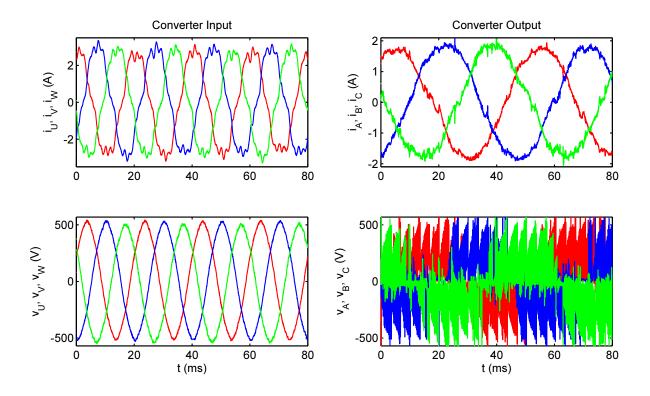

Figure 2.19: Commutation Principle Scheme