## CZECH TECHNICAL UNIVERSITY IN PRAGUE

## **Faculty of Electrical Engineering**

## **Department of Microelectronics**

**Habilitation thesis**

# THERMO-MECHANICAL DESIGN OF ELECTRONIC SYSTEMS

Ing. Jiří Jakovenko, Ph.D.

Prague, 2012

Habilitation Thesis Preface

#### **Preface**

My very special thanks go to the Prof. Miroslav Husák the head of department who trusted upon my efforts and encouraged me in taking specific research paths, who managed to introduce me into the academic research, which still enormously pleases me. I would like to thank Prof Pavel Hazdra for for valuable advice in writing of this work.

I would like to express my gratitude to all my colleagues at the department of Microelectronics for creating an atmosphere which is at the same time both relaxing and encouraging. In particular, I would like to thank the "Microsystem group", with whom I have had the great privilege of working.

I would like additionally acknowledge all people that share their professional knowledge with me: Tibor Lalinský (SAV Bratislava), Gabriel Vanko (SAV Bratislava), Robert Werkhoven (TNO Eindhoven), Jos Kunen (TNO Eindhoven), Xavier Perpina (CNM Barcelona), Xavier Jorda (CNM Barcelona, Peter Bancken (Philips Eindhoven), Jim Mahon (Cadence San Jose, US), Anand Raman (Cadence San Jose, US) and many others.

Some PhD students have taken the opportunity to contribute to the research described herein. I thank Jan Formánek, for his sincere enthusiasm and persisting work efforts in CSSL project.

Scientific research of any kind is unmanageable without funding. First and foremost, I would therefore like to thank the CSSL ENIAC Project (7-FP EU) – "Consumerizing Solid State Lighting",MorGaN – Project (7-FP EU – 2008-2011) – "Materials for Robust Gallium Nitride", NATO Science for Peace international project, GAČR Intelligent Micro and Nano Structures for Microsensors Realized with Support of Nanotechnology (2009-2013, GA102/09/1601), Miniature intelligent system for analyzing concentrations of gases and pollutants, particularly toxic (2010-2015, MV0/VG - Ministry of Interior).

My family, keeping the most important for the end, I tremendously have to thank them for everything they have meant to me the past years, for their patience and forbearance.

Habilitation Thesis Brief Summary

## **Brief Summary**

This work summarises my research results and activities carried out on Czech Technical University, Faculty of Electrical Engineering, Department of Microelectronics over the last seven years. The habilitation thesis has the intention to provide comprehensive work, which is focused on the design, numerical modeling and characterization of temperature affected electronic components and sensors. Relating link in this work is investigation of the thermomechanical phenomena in the design and optimization of new electronic systems and sensor structures together with estimation of lifetime and causes leading to failure.

The work describes thermal management design and reliability evaluation and new accelerated testing method of new 806 lumen SSL retrofit lamp that should replace current 400 lumen master LED glow lamp; design, modelling and characterization of new micro machined GaAs and GaN based high temperature hot plate thermal converters for metal oxide gas sensors; design and optimization of micromechanical GaAs based Microwave Power Sensor thermal converter topology and optimization of the dynamic behaviour of the sensor; and design and accurate numerical modelling of Drumskin pressure sensor packaging system with thermo-mechanical evaluation of stresses induced in the solder joints of the pressure sensor chip at high operating temperatures and different applied pressures.

#### **Anotace**

Tato práce si klade za cíl přehledně vyzdvihnout moje vědecké výsledky činnosti, kterých jsem dosáhl za posledních sedm let na katedře mikroelektroniky Českého vysokého učení technického v Praze, Fakultě elektrotechnické. Jednotící linií této habilitační práce je teplotněmechanický návrh, počítačové modelování a charakterizace elektronických systémů a mikro senzorů. Práce se soustřeďuje zejména na modelování a charakterizaci teplotních vlivů z hlediska mechanického návrhu elektronických komponent a mikro senzorů a také problematikou určení životnosti a potenciálních slabých míst návrhu.

Prvé téma práce se zabývá potřebou zavedení moderních technologií výkonných světelných zdrojů, které jsou zejména aktuální po ukončení výroby 60 W žárovek v Evropské unii k 1. září 2011. Dnes jsou k dispozici dvě alternativní technologie: úsporné zářivky nebo světelné zdroje založené na technologii LED. Osvětlení pomocí LED diod je v posledních několika letech velice rychle se rozvíjející alternativou, která představuje díky nízké spotřebě, vynikající účinnosti a vysoké životnosti budoucnost ve svícení nejenom v průmyslu, ale především v domácnostech. Dalšími nespornými výhodami LED osvětlení je možnost inteligentního řízení světelného výstupu jako např. barevné teploty a intenzity, atd. Práce detailně popisuje návrh nové LED žárovky se světelným výstupem 800 lumenů (ekvivalent 60 W), návrh elektronických částí jako je elektronická deska s LED, dále otázkou teplotního managementu a předpovídání spolehlivosti. Světelné zdroje založené na LED technologii se kromě vynikající účinnosti také vyznačují extrémně dlouhou životností (25 – 50 tis. hodin). Testování doby života takových

Habilitation Thesis Brief Summary

systémů je velice obtížné právě díky dlouhé době životnosti. Klíčovou problematikou v této oblasti je odhalení potenciálních mechanismů vedoucích k selhání a určení jejich umístění. V práci jsou popsány nové metody pro zrychlené testování elektronických komponent polovodičových světelných zdrojů. Numerické modelování teplotně-mechanických jevů s výpočtem životnosti je konfrontováno s nově vyvinutými systémy pro testování životnosti a spolehlivosti.

Další rozsáhlé téma, kterým se práce zabývá, se soustřeďuje na problematiku využití III-N polovodičů v moderních MEMS senzorech. Polovodičové materiály ze skupiny III-N mohou být velice atraktivní pro návrh MEMS (Micro-Electro-Mechanical-Systems) senzorů. Tyto materiály vykazují vynikající piezoelektrické vlastnosti, jsou přímo kompatibilní s tranzistory s vysokou pohyblivostí elektronů (HEMT), mají velmi dobrou mechanickou stabilitu epitaxních vrstev umožňující integraci s MEMS senzory a jsou použitelné při vysokých teplotách se zachováním piezoelektrických vlastností. Díky těmto vlastnostem jsou předurčeny ke konstrukci miniaturních senzorů, které pracují při vysokých teplotách. V práci jsou popsány návrhy několika druhů MEMS senzorů založených na III-N materiálech (senzory pro detekci koncentrace plynů, tlakové senzory pro vysoké teploty využívající piezoelektrický transdukční mechanismus v HEMT struktuře). Nedílnou problematikou vysokoteplotních senzorů je také problematika návrhu vhodného pouzdra, která je také v práci diskutována.

Poslední téma, zaměřené na návrh analogových integrovaných obvodů, se mírně odchyluje od výše zmíněné problematiky a její jednotící linie. Jelikož však tvoří velice podstatnou část mého vědeckého působení na ČVUT, dovolil jsem si jej zařadit do této práce.

## List of symbols and abbreviations

|   | LIST OI SY            | ilibois aliu abbi eviatiolis                                               |

|---|-----------------------|----------------------------------------------------------------------------|

|   | AC                    | Alternating current                                                        |

|   | ADC                   | Analog Digital Converter                                                   |

|   | AMS                   | Analog Mix Signal                                                          |

|   | CFL                   | Compact Fluorescent Lamp                                                   |

|   | CMOS                  | Complementary Metal Oxide Semiconductor                                    |

|   | CTU                   | Czech Technical University in Prague                                       |

|   | DC                    | Direct current                                                             |

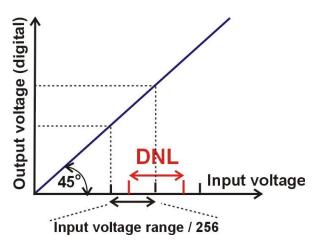

|   | DNL                   | Differential Non Linearity                                                 |

|   | EVM                   | Error Vector Magnitude                                                     |

|   | FEA                   | Finite Element Analysis                                                    |

|   | FEM                   | Finite Element Method                                                      |

|   | HALT                  | Highly accelerated life testing                                            |

|   | HEMT                  | High Electron Mobility Transistor                                          |

|   | IC                    | Integrated Circuit                                                         |

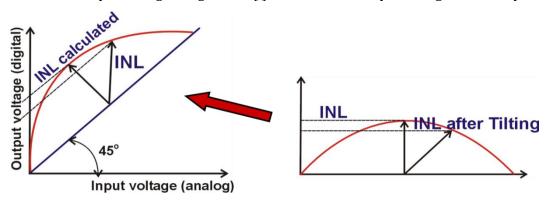

|   | INL                   | Integral Non Linearity                                                     |

|   | IR                    | Infra-Red                                                                  |

|   | LED                   | Light Emitting Diode                                                       |

|   | MBE                   | Molecular Beam Epitaxy                                                     |

|   | MEMS                  | Micro Electro Mechanical Systems                                           |

|   | MOCVD                 | Metal Organic chemical vapour deposition                                   |

|   | MSPS                  | Mega Samples Per Second                                                    |

|   | MTC                   | Micromechanical Thermal Convertor                                          |

|   | P-T                   |                                                                            |

|   |                       | Power to Temperature conversion characteristics Generated internal heat    |

|   | Q                     |                                                                            |

|   | RF                    | Radio Frequency                                                            |

|   | RFMPS                 | Radio Frequency Microwave Power Sensor                                     |

|   | SSL                   | Solid State Lightning                                                      |

|   | TIM                   | Thermal Interface Material                                                 |

|   | TS                    | Temperature sensor                                                         |

|   | VCO                   | Voltage Controlled Oscillator                                              |

| _ | WLAN                  | Wireless local area network                                                |

|   | $C_p$                 | Specific heat                                                              |

|   | E                     | Young's modulus                                                            |

|   | $H_1$                 | Constant of hyperbolic sine function constitutive model by Schubert at al. |

|   | k                     | Thermal conductivity                                                       |

|   | $k_B$                 | Boltzmann constant                                                         |

|   | n<br>T                | Constant of hyperbolic sine function constitutive model by Schubert at al. |

|   | T                     | Temperature                                                                |

|   | Tj                    | Junction temperature                                                       |

|   | α                     | Constant of hyperbolic sine function constitutive model by Schubert at al. |

|   | $\alpha_E$            | Thermal expansion                                                          |

|   | ε                     | Equivalent total strain                                                    |

|   | $\epsilon_{cr}$       | Equivalent creep strain                                                    |

|   | Eel                   | Equivalent elastic strain                                                  |

|   | $\epsilon_{ m pl}$    | Equivalent plastic strain                                                  |

|   | $\epsilon_{	ext{th}}$ | Equivalent thermal strain                                                  |

|   | λ                     | Thermal Conductivity                                                       |

|   | ν                     | Poisson ratio                                                              |

|   | σ                     | Equivalent stress                                                          |

|   | $\sigma_{A}$          | Equivalent alternating stress                                              |

|   | $\sigma_{\text{M}}$   | Equivalent mean stress                                                     |

|   | $\sigma_{\text{MAX}}$ | Maximum of equivalent stress                                               |

|   | $\sigma_{\text{MIN}}$ | Minimum of equivalent stress                                               |

|   |                       |                                                                            |

Habilitation Thesis Table of contents

## **Table of contents**

| P  | refac  | e      |                                                                       | 2  |

|----|--------|--------|-----------------------------------------------------------------------|----|

| В  | rief S | umm    | ary                                                                   | 3  |

| A  | notac  | e      |                                                                       | 3  |

| Li | ist of | symł   | ools and abbreviations                                                | 5  |

| T  | able ( | of cor | ntents                                                                | 6  |

| 1  | Int    | trodu  | iction and Author contribution                                        | 9  |

|    | 1.1    | Ba     | ckground and Motivation                                               | 9  |

|    | 1.2    | 0rg    | ganization of the habilitation thesis                                 | 9  |

|    | 1.3    | Res    | search Contribution                                                   | 10 |

| 2  | So     | lid St | ate Lamp design                                                       | 14 |

|    | 2.1    | Мо     | tivation and author contribution                                      | 14 |

|    | 2.2    | Int    | roduction and state of the art                                        | 15 |

|    | 2.2    | 2.1    | SSL lighting technologies, design, life time and reliability          | 16 |

|    | 2.2    | 2.2    | SSL lamp thermal management, thermo-mechanical issues and reliability | 18 |

|    | 2.2    | 2.3    | SLL lamp reliability                                                  | 21 |

|    | 2.3    | De     | sign of new 806 lumen SSL retrofit lamp                               | 22 |

|    | 2.3    | 3.1    | Retrofit lamp design requirements and components                      | 22 |

|    | 2.3    | 3.2    | Methodology for light output improvement                              | 23 |

|    | 2.3    | 3.3    | Thermal simulation and validation of reference 8W master LED glow     | 24 |

|    | 2.3    | 3.4    | Thermal design and management of new 806 lumen SSL lamp               | 35 |

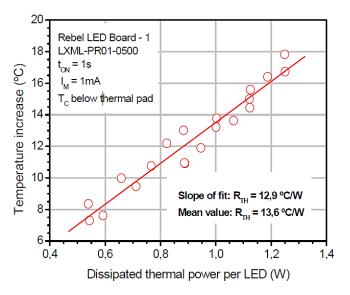

|    | 2.4    | Th     | ermal evaluation and characterization of SSL lamp LED board           | 37 |

|    | 2.4    | ł.1    | LED board model                                                       | 37 |

|    | 2.4    | ł.2    | Thermal simulation and thermal resistance validation                  | 38 |

|    | 2.4    | ł.3    | Thermo-mechanical numerical modelling                                 | 40 |

|    | 2.4    | ł.4    | LED board thermo-mechanical simulation                                | 42 |

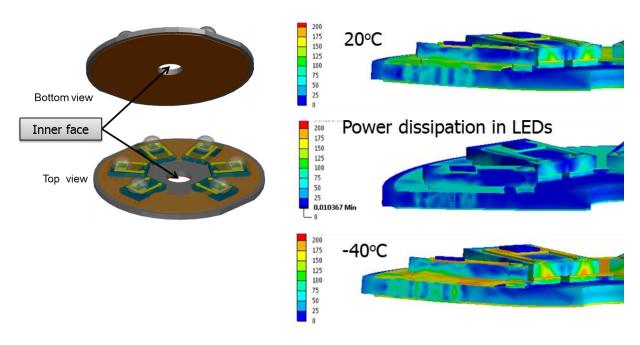

|    | 2.5    | Ne     | w LED board designs                                                   | 45 |

|    | 2.5    | 5.1    | LED Boards design and models                                          | 45 |

|    | 2.5    | 5.2    | Thermo-mechanical evaluation of designed LED boards                   | 49 |

|    | 2.6    | Aco    | celerated characterization methods for SSL LED boards                 | 51 |

|    | 2.6    | 5.1    | General description and work motivation                               | 51 |

|    |        |        |                                                                       | 6  |

|   | 2.6.         | 2 Methodology of acceleration testing method for LED boards               | 51    |

|---|--------------|---------------------------------------------------------------------------|-------|

|   | 2.6.         | 3 Lead less solder joints fatigue models - theory                         | 53    |

|   | 2.6.         | 4 LED board life time calculation - high speed mechanical cycling         | 58    |

|   | 2.6.         | 5 Failure detection                                                       | 65    |

|   | 2.6.         | 6 Measurement results                                                     | 67    |

|   | 2.6.         | 7 Different LED board technologies life time comparison                   | 68    |

|   | 2.6.<br>effe |                                                                           | creep |

|   | 2.6.         | 9 Low speed mechanical cycling measurement                                | 75    |

|   | 2.7          | Summary and conclusions                                                   | 78    |

|   | 2.7.         | 1 Future work:                                                            | 79    |

| 3 |              | N, GaAs and Silicon based Micromechanical Free Standing Hot Plates for G  |       |

|   | 3.1          | Motivation and author contribution                                        |       |

|   | 3.2          | Introduction and state of the art                                         | 81    |

|   | 3.3          | Hot plates design                                                         | 81    |

|   | 3.4          | Hot plate modelling                                                       | 83    |

|   | 3.4.         | 1 Hot plates fabrication                                                  | 86    |

|   | 3.5          | Summary and Conclusion                                                    | 87    |

| 4 | Des          | sign and Characterization of GaAs MEMS thermal converter                  | 88    |

|   | 4.1          | Motivation and author contribution                                        | 88    |

|   | 4.2          | Introduction and state of the art                                         | 89    |

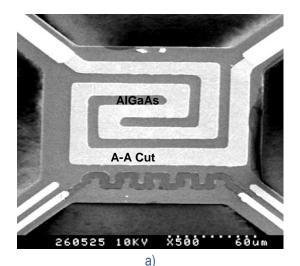

|   | 4.3          | Micromechanical Thermal Converter design and models                       | 90    |

|   | 4.3.         | 1 Thermal analysis                                                        | 92    |

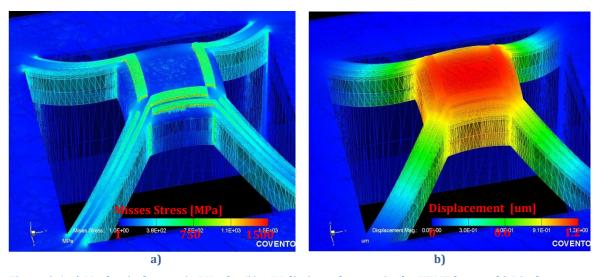

|   | 4.3.         | 2 Thermal stress and displacement evaluation                              | 94    |

|   | 4.3.         | 3 Influence of the gate width on maximal temperature of MTC structure     | 95    |

|   | 4.4          | Summary and conclusions                                                   | 96    |

| 5 |              | ermo mechanical and piezoelectric design of the pressure sensor for hars  |       |

|   |              | ironment                                                                  |       |

|   | 5.1          | Motivation and author contribution                                        |       |

|   | 5.2          | Introduction and state of the art                                         |       |

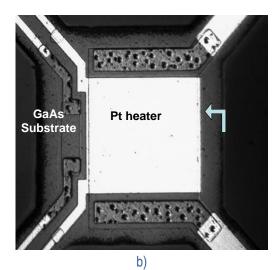

|   | 5.3          | GaN and AlGaN/GaN -based structures with HEMT as piezoelectric sensing el | ement |

|   | 5.3.         | 1 Cantilever sensor structure                                             | 99    |

|   | 5.3.         | 5                                                                         |       |

|   | 5.3.         | 3 Circular HEMT (C-HEMT) sensor structure                                 |       |

|   |              |                                                                           | 7     |

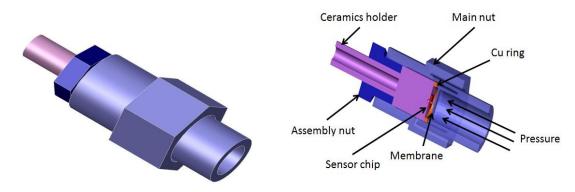

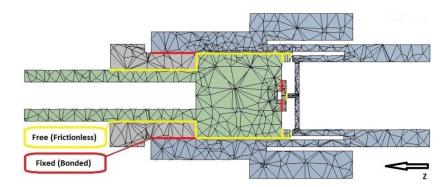

|    | 5.4   | Pressure sensor package 3D model                                               | 104 |

|----|-------|--------------------------------------------------------------------------------|-----|

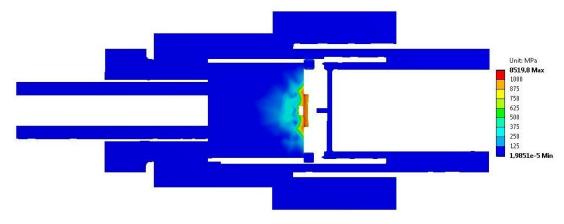

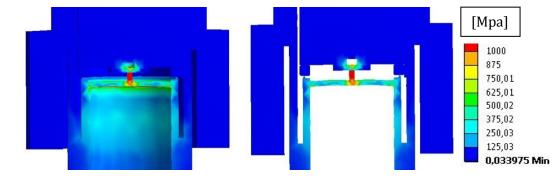

|    | 5.5   | Thermo-mechanical simulation and thermal cycling                               | 104 |

|    | 5.6   | Simulation of influence of the whole package on encapsulated sensor structure. | 106 |

|    | 5.6.  | 1 Pressure sensor packaging                                                    | 107 |

|    | 5.6.  | 2 Simulation conditions and linkage connections                                | 107 |

|    | 5.6.  | 3 3D model and material properties                                             | 108 |

|    | 5.6.  | 4 Thermo-mechanical simulation                                                 | 108 |

|    | 5.7   | Summary and Conclusions                                                        | 110 |

| 6  | IC d  | esignesign                                                                     | 112 |

|    | 6.1   | Wireless Design Flow for RF development Kit - R&D for Industry                 | 112 |

|    | 6.1.  | 1 Motivation and author contribution:                                          | 112 |

|    | 6.1.  | 2 State of the art                                                             | 113 |

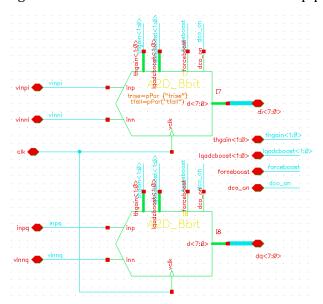

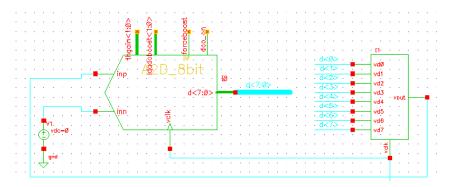

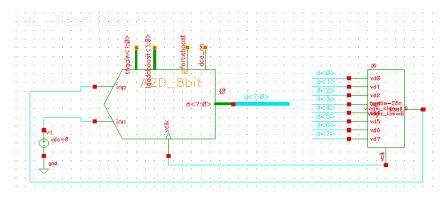

|    | 6.1.  | B Dual I/Q 8-bit pipeline ADC Verilog-AMS model                                | 115 |

|    | 6.1.  | 4 Summary of Wireless Design Flow                                              | 121 |

|    | 6.2   | IC design – PhD students leadership                                            | 122 |

|    | 6.2.  | Optimization tool for analog circuit design                                    | 122 |

|    | 6.2.  | Design of capacitor-less LDO regulator in CMOS technology                      | 122 |

|    | 6.2.  | B Design and validation of an SMPS power distribution network                  | 123 |

|    | 6.2.  | ESD MOSFET model fitting by differential evolutionary optimization             | 124 |

| 7  | Gen   | eral conclusions and future perspectives                                       | 125 |

|    | 7.1   | Future research and possibilities for improvements                             | 126 |

| 8  | Bib   | iography                                                                       | 127 |

| Aj | ppend | ix I: Curriculum Vitae                                                         | 133 |

| Aj | ppend | ix II: List of publications related to the habilitation work                   | 135 |

| Aj | ppend | ix III: Projects                                                               | 136 |

| Αį | ppend | ix IV: Internships                                                             | 138 |

#### 1 Introduction and Author contribution

### 1.1 Background and Motivation

Since defence of my PhD thesis elaborated in 2004 my professional activities in the field of research and education had been related to the two main activities. The first topic follows a research activities carried out during my PhD that has been with initiation of new projects extended to design and numerical modelling of new thermally based MEMS gas sensors and pressure sensors. Another parallel activity came with design of a new SSL lamp concept. The second activity has been focused on the design of integrated circuits and systems. In this field I made a four-month internship within Cadence Company in 2005 where I worked as a member of R&D team concentrated on development of a new RF CMOS development kit. After the end of internship I become an external contractor for above mentioned R&D team.

The main purpose of this work is to provide a comprehensive summary dedicated to the design, numerical modeling and characterization of thermally affected electronic components and micro sensors. This corresponds to the first activity stated above. Relating link in this work is the investigation of thermo-mechanical phenomena during the design and optimization process of new electronic systems and micro sensor structures (typically based on GaN and GaAs materials) together with estimation of components lifetime and explanation of the effects leading to system failure.

## 1.2 Organization of the habilitation thesis

The main section of this work is organised to six chapters that describe my research activities over the last seven years. Each chapter begins with a short "Motivation and author contribution" that outlines the main research goals referred to the research presented in the chapter and definition of my own contribution that is related to the working context. This explanation is followed by description of research importance in defined area. Each chapter is concluded and results are discussed together with reflections on possibilities for improvement of the results. Moreover, continuation of the research in that field is added.

**Chapter 2** titled "**Solid State Lamp design**" describes design of new 806 lumen SSL retrofit lamp that should replace current 400 lumen master LED glow lamp. The chapter describes my research activities in thermal modelling and validation of master LED glow retrofit lamp, thermo-mechanical evaluation of master LED glow. Design of new LED boards for 806 lumen lamp is described in detail. Development of new accelerated characterization methods for SSL LED boards together with reliability and life time modelling of LED boards is reported in the end.

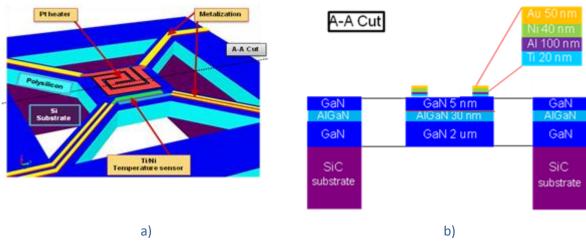

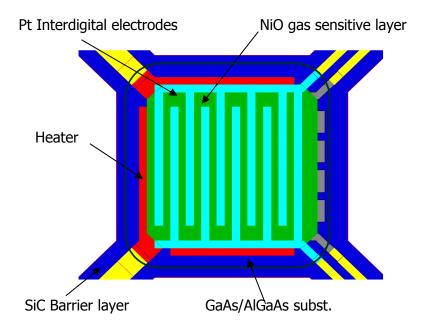

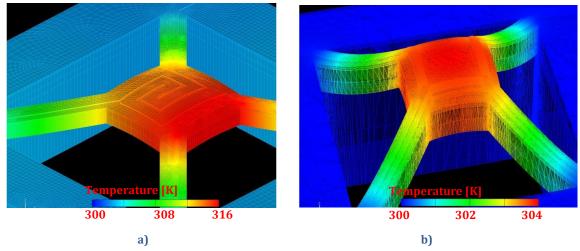

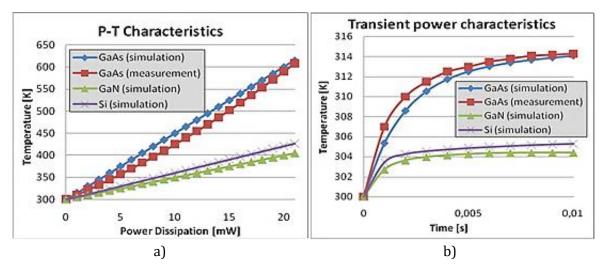

Chapter 3 titled "GaN, GaAs and Silicon based Micromechanical Free Standing Hot Plates for Gas Sensors" has the intention to provide the reader with an outlook on the approaches that have been used to design new micro machined GaAs and GaN based hot plate thermal

converters, which are considered to operate with high temperature metal oxide gas sensors. These sensors can analyse various gases, such as CO,  $H_2$ , NOx and hydrocarbons.

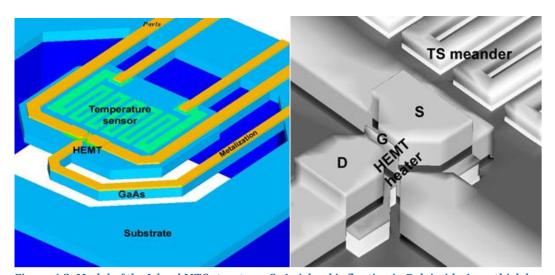

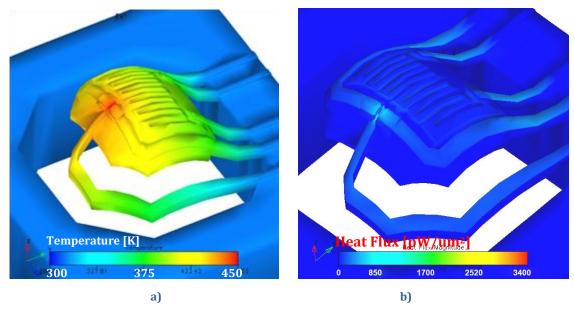

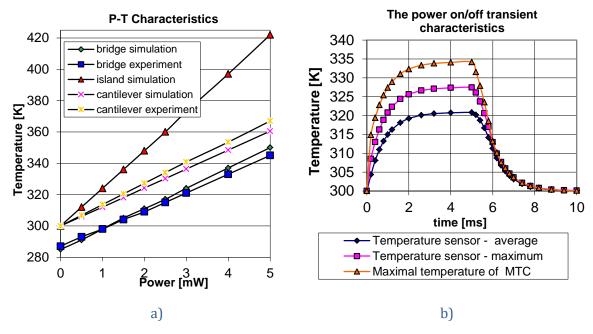

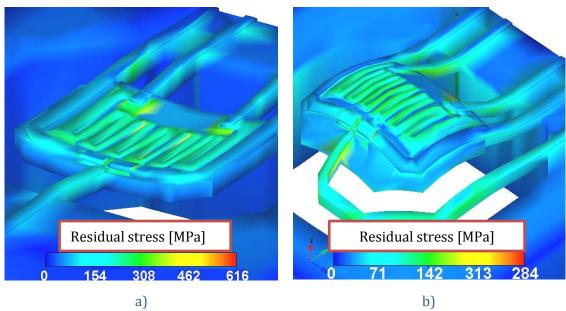

**Chapter 4** titled "**Design and Characterization of GaAs MEMS thermal converter**" outlines the design and thermomechanical modelling of the new GaAs based RF Microwave Power Sensor (RFMPS) microsystem. The chapter discusses the procedure for performing a thermomechanical analysis of thermal GaAs-based MEMS devices. Main focus is on increasing reliability which requires temperature distribution controlling in single parts of the device and definition of high thermo-mechanical stressed areas that can be critical in relation to the mechanical failure of the device.

Chapter 5 titled "Thermo mechanical and piezoelectric design of the pressure sensor" presents numerical modelling of ZnO-passivated AlGaN/GaN-based circular high electron mobility transistor (C-HEMT) designed for new pressure sensor. Thermomechanical behavioural study focusing on the extremely high temperature pressure sensor package is outlined. The study provides accurate modelling and simulation of Drumskin pressure sensor packaging system developed by IVF (Sweden). Research is mainly focused on thermal evaluation of induced stress in the solder joints and in the glass frit that is used to seal the sensor chip at high operating temperatures.

**Chapter 6** titled "**IC design**" presents some results of my activities performed in Cadence, San Jose, CA and following activities carried out during next three years with Cadence RF R&D team. This chapter does not belong fully in the main section of presented work, which aims to seamlessly handle the problems of lifetime and thermal design of electronic systems. The chapter has been included because IC design research and teaching activities at the CTU forms an important part of my professional work.

Scientific contributions and general conclusions of this habilitation thesis work are summarized in chapter 7.

#### 1.3 Research Contribution

Habilitation thesis summarises my research results carried out at Czech Technical University in Prague, Faculty of Electrical Engineering, Department of Microelectronics.

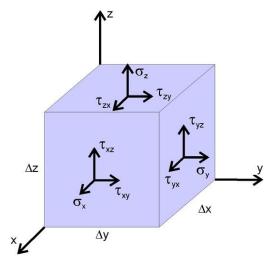

The research work presented in this work could be characterised by a cross-disciplinary approach that brings together theoretical aspects, numerical modelling and experimental techniques of thermal and thermomechanical phenomena which takes place in micro sensors and electronics systems and components. The work has the objective to provide comprehensive summary of research focused on the design, numerical modeling and characterization of temperature affected electronic components and sensors. Relating link in this work is examination of the thermo-mechanical phenomena in the design and optimization of new sensor structures, estimation and calculation of electronic system lifetime and effects that results a failure of the electronic system. Thermomechanical stress induced in an electronic system composed from diverse materials (that have a different coefficient of thermal expansion) could be the main cause of catastrophic failure, especially when the

system operation temperature is high or when the temperature alternate in an extensive range. For the reason that reliability of newly developed electronic systems is one of the major criteria, numerical modelling and optimization of thermomechanical stresses are key issues during new system development. State of the art in numerical modeling of thermo-mechanical phenomena of electronic components is to determine the behavior of the entire system at critical locations. Detailed examination of the physical phenomena leading to the discovery of failure mechanisms have been carried out. In particular cases, where the dimensions of the system are several orders of magnitude larger than examined location, the multi-scale numerical modelling approach has been used.

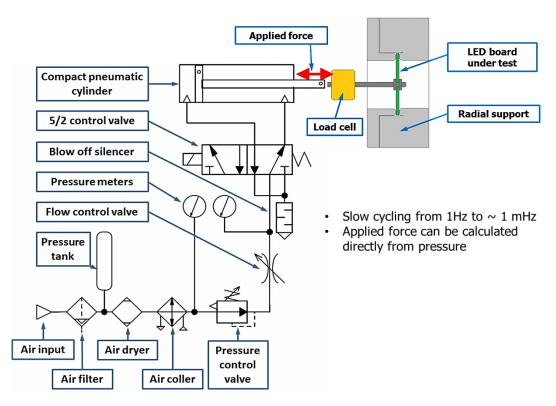

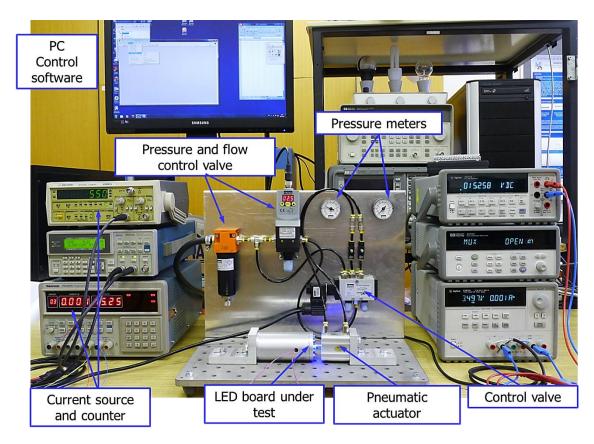

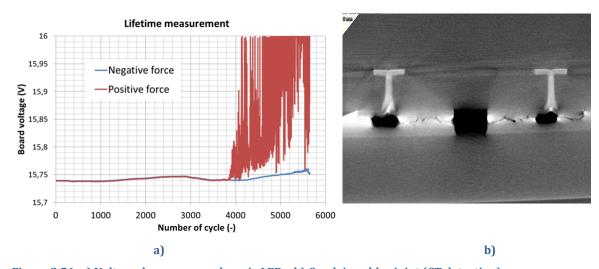

The main attention of the thesis in particular is given to thermal and thermomechanical numerical modelling and characterization of solid state lightening (SSL) LED Lamp. More insights are observed in the thermal and thermo-mechanical behaviour. Different lamp shapes are also explored (Chapter 2.2.2). The work presents an accurate 3-D modelling of several LED board technologies. More efforts are concentrated on thermal modelling, thermo-mechanical evaluation and lifetime prediction of newly designed LED boards in order to compare their performances. These LED boards are proposed as a possible replacement technology for existing FR4 board used in current 400 lumen retrofit SSL lamp (Chapter 2.4). The advantages of these innovative LED board technologies are discussed. Moreover, innovative approach in modelling and validation of 800 lumen retrofit SSL lamp is proposed. Lifetime numerical analysis have been carried out to study reliability and lifetime limits of each new component, using thermal boundary conditions which was extracted from the thermal simulation of a whole SSL lamp (Chapter 2.3). Additionally, thermal cycling that lead to the LED board failure due to thermal fatigue have been calculated and validated. Elastic-plastic analysis with temperature dependent stress-strain material properties has been performed. The objective of new design is to optimize not only the thermal management by thermal simulation (Chapter 2.3), but also to find potential problems from mechanical failure point of view (Chapter 2.4.3). Development of a new methodology for reliability design of SSL LED boards is discussed (Chapter 2.5). One of the most valuable scientific contributions of this part is development of accelerated characterization testing methods for SSL lamp LED boards. New method replaces traditional thermal cycling or power cycling characterization test, which is very timeconsuming (Chapter 2.6). This methodology is based on creep relaxation effects in solder joints (Chapter 2.6.8). Accumulated creep strain (or accumulated energy) in solder joints has to be defined during thermal cycle that is followed by calculation of equivalent mechanical force that imply comparable accumulated creep strain value in solder joint regions of interest. This new accelerated tests can dramatically speed up reliability evaluation process keeping testing accuracy in the range of 20%.

Correct knowledge of mechanical and thermal properties of essential materials used in micro sensors and MEMS is critical for optimum geometric and functional design. The extraction of precise physical properties is rather difficult due to the size effects and the complexity of the assemblies. Further work is intended to present new design, modelling and characterization of micro machined GaAs and GaN based hot plate thermal converters, which are considered to operate with high temperature metal oxide gas sensors that can analyse various gases, such as CO, H2, NOx and hydrocarbons (Chapter 3). New solution increases sensitivity (through the use of new materials as GaAs and GaN) and decreases power consumption, due to the miniaturization and MEMS technology that replaces wide spread screen printing technique on

small ceramics substrates. Newly designed free standing MEMS membrane provides very good thermal isolation between the heated gas sensitive active part and substrate, which remains nearly at ambient temperature. The work discusses needs for sensitivity and selectivity increase that can be realised by higher temperature of active gas sensing parts. However, well developed silicon technology is thermally limited up to 300 °C, while use of new materials as GaN (Chapter 3.2) brings advantage of much higher operational temperature (up to 1000 °C). The work focuses on new hot plates design (Chapter 3.3) and compares performance of three hot plate substrate material, e.g. Silicon, GaAs and GaN. State of the art in high temperature MEMS design is correct thermomechanical modelling and optimization of uniform thermal distribution in active sensing area (Chapter 3.4). Thermo-mechanical analyses ware used to simulate steady state and transient thermal performance. The mechanical coupling was included to optimize mechanical integrity of the hot plates. Simulation results were compared with the experiment in the case of GaAs hot plate (Chapter 3.4).

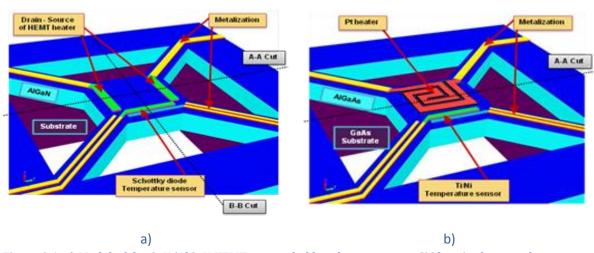

Another work that can be included to this portfolio has the intention to provide with design and characterization of the new GaAs based Microwave Power Sensor (MPS) microsystem (Chapter 4). Transmitted power is the most important quantity considered in RF systems. Usual approach to transmitted power measurement is based on the detection of absorbed power waves (incident and reflected) that requires complicated multiple power meter structures and need complex calibration. An improved method of the absorbed power measurement is based on thermal conversion where, absorbed radio frequency (RF) power is transformed into thermal power inside of a thermally isolated system. This section discusses the micromechanical thermal convertor design (Chapter 4.3) and procedure for performing a thermomechanical analysis of thermal GaAs-based MEMS devices (Chapter 4.3.1). It will provide the general procedure how thermal analysis should be made and model equations used to describe conduction, convection, radiation and mechanical effects caused by inhomogenous temperature distribution. By means of thermo-mechanical simulations, we propose a GaAs Micromechanical Thermal Converter design and a layout of the active sensor elements (HEMT heater and a temperature sensor TS) placed on the MTC structure. Simulation results were compared with the experiment. The main scientific contribution of this session is Design and optimization of micromechanical GaAs based Microwave Power Sensor thermal converter topology in terms of the temperature distribution and optimization of the dynamic behaviour of the RFMPS system with respect to changes of the input RF power dissipation, which is generated by integrated HEMT transistor.

Many industrial applications require electronic devices that can operate in harsh environments such as an extreme heat, high pressure, large electric fields or chemically aggressive environment. For such applications III-Nitrides (III-Ns) are very attractive semiconductor materials that can be used for pressure and stress sensor applications because of their excellent piezoelectric properties

Chapter 5 deals with numerical modelling of ZnO-passivated AlGaN/GaN-based circular high electron mobility transistor (C-HEMT) designed for new stress sensor which can be potentially applied for dynamic high temperature pressure sensing (Chapter 5.3). High temperature devices need special package design that stands for extreme conations. Next section deals with accurate modelling and simulation of high temperature pressure sensor packaging system and thermomechanical evaluation of mechanical stresses induced in the solder joints and the glass frit that is used to seal the pressure sensor chip at high operating temperatures and different

applied pressures (Chapter 5.4). The most critical problem with packaging for high temperature environments is accumulated thermo-mechanical stress induced during thermal cycling process by the different temperature expansion coefficients of materials used for the packaging and interconnect (Chapter 5.5). Evaluation of the package influence on encapsulated sensor structure at high operating temperatures and different applied pressure has been also investigated (Chapter 5.6).

The last part of this thesis is focused on IC design research activities (Chapter 6). I am aware that this chapter does not fit entirely into coherence with previous topic. On the other hand, the IC design constitutes an essential part of my research and teaching activities on CTU. Therefore I decided extend this work by this section. Chapter provides an overview of the most important activities in the last seven years, with couple of examples.

#### The most valuable scientific contributions:

- Development of accelerated characterization testing method for LED boards that replaces traditional thermal cycling of power cycling characterization test by LED board mechanical bending method;

- Design, modelling and characterization of new micro machined GaAs and GaN based high temperature hot plate thermal converters for metal oxide gas sensors that can analyse various gases (CO,  $H_2$ , NOx, hydrocarbons);

- Design and optimization of micromechanical GaAs based Microwave Power Sensor thermal converter topology in terms of the temperature distribution and optimization of the dynamic behaviour of the RFMPS system with respect to changes of the input RF power dissipation, which is generated by integrated HEMT transistor;

- Numerical modelling of ZnO-passivated AlGaN/GaN-based circular high electron mobility transistor (C-HEMT) designed for new stress sensor to be potentially applied for dynamic high temperature pressure sensing;

- Design and accurate numerical modelling of drumskin pressure sensor packaging system and thermomechanical evaluation of mechanical stresses induced in the solder joints and the glass frit that is used to seal the pressure sensor chip at high operating temperatures and different applied pressures

## 2 Solid State Lamp design

This chapter deals with design of new 806 lumen SSL retrofit lamp that should replace current 400 lumen master LED glow lamp. The research work has been done in frame of the ENIAC JU project CSSL<sup>1</sup> that aims to develop and demonstrate inexpensive smart solid-state light sources through improvements in technology and application opportunities.

Intention of this chapter is to collect current research results published by the author (see table) into one coherent unit, which is completed by detailed research review, theory basis and new unpublished results describing a new accelerated LED board lifetime calculation and validation methods.

Table 2-1: published works related to the chapter

| Paper title                                                                         | Full<br>reference |

|-------------------------------------------------------------------------------------|-------------------|

| Design for reliability of solid state lighting systems                              | [1]               |

| High power solid state retrofit lamp thermal characterization and modelling         | [2]               |

| Thermo-mechanical evaluation and life time simulation of high power LED lamp boards | [3]               |

| Thermal resistance investigations on new leadframe-based LED packages and boards    | [4]               |

| Thermal simulation and validation of 8W LED lamp                                    | [5]               |

#### 2.1 Motivation and author contribution

LED (Light-emitting diodes) lamps are a fast emerging technology which is considered as the true alternative to the Compact Fluorescent Lamp (CFL). At present days we can see many commercial products that are usually available for professional use; however there is not often any LED retrofit lamps that can fulfil traditional expectations of consumers in terms of lamp shape, price, light output and other functionalities.

#### My own research contribution can be summarized in following research areas:

- Development of calibrated thermal model of master LED glow retrofit lamp with validation(together with my PhD student Jan Formanek) (chapter 2.2.2)

- Design of new 806 lumen retrofit lamp (as a member of design team) (chapter 2.3)

- Calibrated thermo-mechanical and reliability model of LED board for master LED glow retrofit lamp (together with my PhD student Jan Formanek) (chapter 2.5).

<sup>&</sup>lt;sup>1</sup> The Consumerizing Solid State Lighting (CSSL) project aims to demonstrate affordable Smart Solid State Light sources for consumers via both technology and application routes. The proposed CSSL project works vertically across the entire value chain from embedded electronics, LED die, light source, consumer luminaires, controls and dimmer to partnerships with utility companies in order to bring SSL retrofit products to European consumers with innovative pricing scheme.

- Design and evaluation of new LED boards from thermal, mechanical and reliability point of view (together with my PhD student Jan Formanek) (chapter 2.5.2)

- Development of new accelerated characterization methods for SSL LED boards (together with my PhD student Jan Formanek) (chapter 2.6)

- New accelerated validation method of LED boards that replaces traditional thermal cycling test (together with my PhD student Jan Formanek) (chapter 2.6.8)

#### 2.2 Introduction and state of the art

In the last few years the use of SSL (Solid state lighting) lamps has been increasing almost exponentially. Solid-state lighting has the potential to revolutionize the future lighting industry. It is predicted that the LED replacement lamp market will speed up progresses in commercially available LED performance in the next a few years, as well as cost reduction are expected. SSL technology uses semiconductor light-emitting diodes (LEDs) as sources of lights instead of wildly used incandescent electrical filaments or plasma in fluorescent lamps. The term "solid state" is derived from meaning that light is emitted by solid-state electroluminescence. One of the biggest advantages in comparison to incandescent lighting is that SSL produces a light with reduced heat generation or other parasitic energy dissipation. Other benefits that come with SSL technology are: more than ten times longer life time in comparison with incandescent light technology, better quality of light output (LEDs produce minimum ultraviolet and infrared radiation), smaller volume of light bulb (if needed). Table 2-2 compares SSL lamps to incandescent and fluorescent lamps from power dissipation and life time point of view. The data are related to 800 lumen light output:

Table 2-2: Commercially available lamp comparison

| Lamp type                   | Incandescent | Fluorescent | SSL lamp        |  |  |

|-----------------------------|--------------|-------------|-----------------|--|--|

|                             |              |             |                 |  |  |

| Input Power (W)             | 60           | 18          | 12              |  |  |

| Life time (hours)           | ~1000        | ~ 8000      | 20 000 - 50 000 |  |  |

| Retail price                | <1€          | 5-10€       | 10-35€          |  |  |

| <b>Total Radiant Energy</b> | 81%          | 51%         | 20-30%          |  |  |

| Visible light               | 8%           | 21%         | 25-30%          |  |  |

| Infra-red emission          | 73%          | 37%         | ~0%             |  |  |

Moreover, a typical SSL lamp is fully dimmable (depends on driver type) like an incandescent bulb, but unlike a fluorescent lamp that has tendency to flicker. SSL lamps also do not emit ultraviolet radiation. That can cause problems to wallpaper and artwork fading. SSL lamps colour can be easily shaded from cool blue to warm yellow to suit all preferences. Further aspect which is very important today is that SSL technology is considered to be "green technology" which means that environmentally harmful materials as mercury, lead, etc., are not used.

On the other hand, SSL lamps cost considerably more than incandescent lamp. However, when life time of SSL lamps and long term energy consumption are taken into account, money saving can be more apparent in behalf of SLL technology. Moreover, the future SSL costs are expected to be reduced dramatically.

#### 2.2.1 SSL lighting technologies, design, life time and reliability

Light emitting diodes historically have been used for indicators at the beginning and produced low quantities of heat. Bob Biard and Gary Pittman found in 1961 that GaAs emit infrared radiation when electric current is applied [6]. The first practical visible-spectrum LED was technologically advanced in 1962 by Nick Holonyak [7]. While the efficacy of these first LEDs was extremely low (~ 0.1 lm/W), research was continued to improve the technology over the next four decades, achieving higher efficiencies and expanding the range of emission wavelengths through the engineering of new III-V semiconductor alloys. Well known Moore's Law predicts the doubling of the number of Si transistors in a chip every 18–24 months. In the same way for LEDs, luminous flux (measured in lm) appears to follow Haitz's Law, which predicts that LED flux per package doubles every 18–24 months for more than 30 years [8]. Today we are seeing even more fast progress.

From the time of invention, LEDs have been used in many industrial applications as for example: displays (outdoor displays, electronic scoreboards), LCD back lighting [9] (mobile phones, notebooks, cameras, monitors, TVs, etc.), automotive lighting [10], in communication technologies. The introduction of high brightness LEDs with white light output have managed to a movement towards general indoor and outdoor illumination applications [11]. The increased electrical driving currents have focused more attention on the thermal management and new designs of LED power packages. The luminous efficiency of LEDs brakes 200 lumens per watt in 2011<sup>2</sup> and the thermal challenges are opening new research areas from LED chip design level to the system level thermal management.

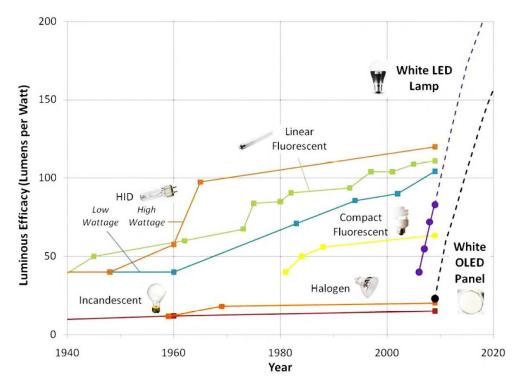

Figure 2.1 shows historical and Predicted Efficacy of Light Sources [12]. Note: today a new LED with efficiency over 200 lumens has been already introduced.

-

<sup>&</sup>lt;sup>2</sup> 200 lumens per watt were achieved by CREE LEDs with a colour temperature of 4579k and nominal drive current of 350mA.

Figure 2.1: Historical and Predicted Efficacy of Light Sources [12]

To generate white light output for general illumination, a narrow spectral band of an LED's must be transformed into white light or more discrete emissions must be mixed. White-light LED conversion is typically based on three common approaches:

- phosphor-conversion;

- discrete colour-mixing;

- hybrid consisting of phosphor (white) and monochromatic packages (or different LEDs in a single package).

The phosphor-converting LEDs produce white light by converting of the blue light (generally around 460 nm) emitted directly from the LED die with light emission converted by a phosphor [13]. Some of this light is emitted directly, and some of it is down-converted by a phosphor from the 460 nm wavelength to longer wavelengths (e.g., green, yellow, red) with wide-band emissions that is mixed with the blue to produce white light. Main disadvantage of phosphor-conversion technology is difficulty of maintaining consistent-quality of white light due to changes of the temperature, thickness of the phosphor layer, variation of the humidity and aging. As a consequence, noticeable discrepancies in output colour can occur from one LED to another.

**Discrete colour-mixing** create the white light by colour mixing optics to mix the light output from discrete colored sources. The major advantage of the colour-mixing technology is that it does not contain phosphor that eliminates scattering losses in the emitting of white light. The biggest problem is the absence of efficient green light LEDs. Unfortunately this is main factor that significantly limits achievable efficacy. Moreover, mixing of discrete colours requires multi-die mounting and sophisticated optics.

#### 2.2.2 SSL lamp thermal management, thermo-mechanical issues and reliability

This section summarises most important issues that has to be taken into account while designing new high power SSL lamp. Main goal of this text is to review the latest thermal management technologies with respect to SSL lamp lifetime and reliability and show the state of the art in modern SSL lamp design.

#### 2.2.2.1 Thermal management

Almost all modern light sources convert electric power into radiant energy and heat in various proportions. While incandescent lamps emit mostly infrared (IR), with a small amount of visible light, SSL lamps generate little or no IR or UV, but convert only 20%-30% of the power into visible light. The rest is converted to the heat that must be conducted from the LED die and through LED package to the underlying LED board, heat sink and housing. Table 2-3 shows the proportions of input power to heat and radiant energy conversion for various white light sources. Almost all total radiant energy in case of SSL lamp is converted to visible light. This is main advantage above incandescent and fluorescent lamps. On the other hand big portion of the heat is generated here. This is a reason why thermal management is perhaps the most important aspect of successful SLL lamp system design.

Moreover the effectiveness of whole SSL lamp system is not only related to LEDs light conversion, but also to the driver losses, and power dissipation in light conversion element. Most of the input power in an LED converts to heat rather than light (about 70% heat and 30% light).

| Table 2-3: Estimated proportions of input power to heat and radiant energy (including visible light) |

|------------------------------------------------------------------------------------------------------|

| conversion for various white light sources                                                           |

| Lamp type                   | Incandescent | Incandescent Fluorescent |        |

|-----------------------------|--------------|--------------------------|--------|

| Infra-red emission          | 73%          | 37%                      | ~0%    |

| Heat                        | 19%          | 42%                      | 70-80% |

| <b>Total Radiant Energy</b> | 81%          | 58%                      | 70-80% |

| Visible light               | 8%           | 21%                      | 25-30% |

| Total energy                | 100%         | 100%                     | 100%   |

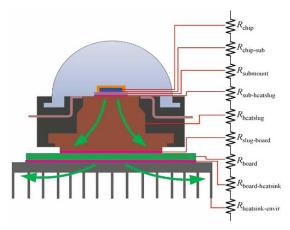

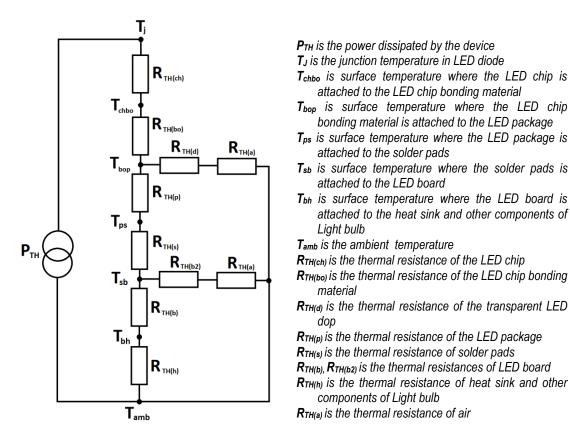

If the heat is not removed, the LEDs run at high temperatures, which not only lower their efficiency, but also make the LED less reliable. The dissipated heat of these components is removed by conduction within the SSL lamp system and by convection and radiation outside the lamp on a heat sink and bulb surface. Thermal management of SSL lamp is a key issue impacting not only efficiency (in lm/W), but also colour consistency and of course, lifetime. The junction temperature of LED components depends on the heat generation caused by loses during light emitting and thermal dissipation within the SSL lamp from the LED die through the LED package, board, heat sink and finally to the ambient (Figure 2.2, [14]). In order to have the junction temperature as low as possible, it is necessary to minimize all thermal resistances, starting with the LED component, itself. In addition, several packaged LEDs are connected in

series on a substrate (LED board) in SSL lamp, increasing the challenges to face during their thermal design.

Figure 2.2: Thermal resistance network of Luxeon LED (there are at least four interface resistances. These interfaces are bottlenecks of heat conduction and should be paid special attention) [14]

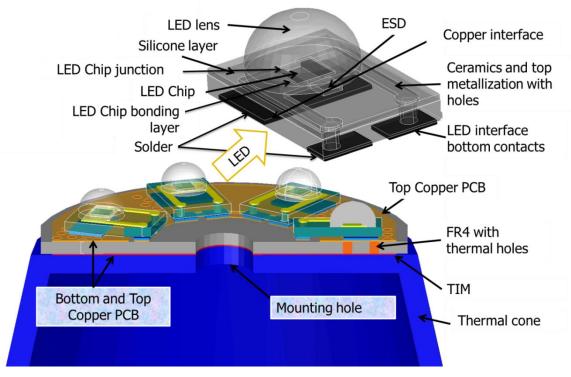

LEDs are typically encapsulated in a transparent resin, which is a poor thermal conductor. Nearly all produced heat is conducted through the back side of the LED chip. SSL lamp cooling system is composed of many parts. LED chip is usually connected by flip-chip technology to LED package that create a thermal path from LED junction to bottom side of the package solder pads. One or more LEDs packages are typically spread out on LED board which is typically attached by TIM (thermal interface layer) to extension thermal cone that conducts heat to heat sink where the heat is distributed to ambient. Moreover another heat sources in SSL lamp are an electronic driver and phosphorus conversion dome.

In 1998, Lumileds developed the first high-power LED packaging³ – Luxeon, which embeds a metal large shell size for heat dissipation. This package has been adopted as main packaging type by many corporations such as Osram and Seoul Semiconductor. This packaging method reduces thermal resistance to about 10 K/W and can dissipate heat power up to 5W [15]. In 2006, with the improvement of used materials and attach technologies, the Luxeon K2 package can allow junction temperature up to 150°C for white LED with a driven current up to 1.5 A [16]. To reduce costs and increase the reliability issues, a ceramic based package has been developed by Lumileds (the Rebel component [17]), CREE and others. On the other hand, the thermal resistance of these packages remains typically above 10 K/W. Some of the SSL lamp manufacturers (Osram [18], Nichia [19], Cree [20]) have developed efficient metal based packages which were derived from the Luxeon concept. Those packages are known as leadframe based packages.

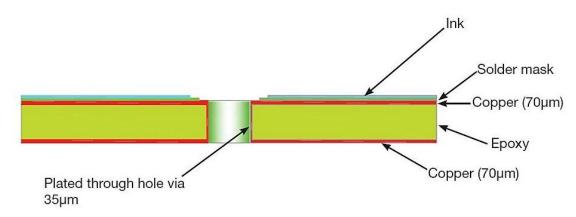

LED boards (on which power LEDs are often mounted) technologies that has been developed and used recently uses FR4 boards, metal-core printed circuit boards (MCPCB), IMS (Insulated Metal Substrate). LED board is then attached to a heat sink where TIM (thermal interface layer) that improves heat transfer is used. The TIM's thermal resistance will also vary depending on the type of material used.

\_

<sup>&</sup>lt;sup>3</sup> Patent no. 6,274,924 "Surface mountable LED package. Filed 11/5/1998, granted 8/14/2001.

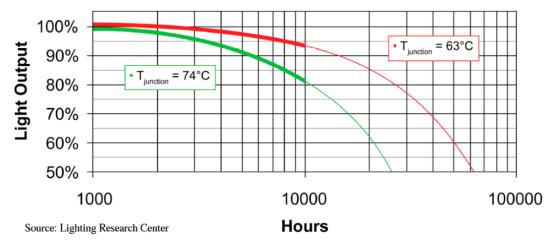

Heat and changes of LED temperature directly affects both short-term and long-term LED performance [21]. The short-term performance effects mostly colour shift and reduced light output while the long-term performance results accelerated lumen depreciation and thus shortened useful life. LED operation at higher temperature radically accelerates lumen depreciation and shortened useful lifetime. The Figure 2.3 shows the light output over time for two identical LEDs driven at the same current but with an 11°C difference in LED junction temperature<sup>4</sup>. Estimated useful lifetime (according 70% lumen normative) reduced from about 37,000 hours to about 16,000 hours. A 10 degrees increase in temperature reduces LEDs life by approximately 50% and each following 10 degrees increase will reduce fixture life by another 50%!

Figure 2.3: Useful life time of high brightness white LEDs at different operating temperatures [22]

In a compact SSL lamp design, the light engine components such as LEDs, drier ICs and electronic components, sensors and phosphor convertor have to be kept in a limited space. Moreover, the required high light output causes high temperatures dissipation inside the limited size of the SSL lamp engine. This can be especially critical for LED junction temperature and driver components temperature. Most of today research works that are dealing with SSL lamp design and thermal management are focusing on the virtual prototyping based on thermal management, thermo-mechanical modelling and reliability predicting, improving of materials selection and fabrication aspects (packaging, connection and integration technologies). Another very important aspect is thermal separation of the LED driver circuitry and phosphor light conversion dome from the LED board. This avoids the heat generated by the driver and light conversion element from raising the LED junction temperature. However, improvement of the lifetime of LEDs at higher operating temperatures has been reached in recent years. Leading manufacturers of high-power white LEDs estimate a lifetime to around 50,000 hours assuming operation at 700 mA constant current at maintained junction temperatures up to 120°C [18] [20]. The LED junction temperature is affected by drive current, thermal path and ambient temperature. Because necessary light output power is given by drive current at given ambient temperature, the LED temperature can be lowered by optimizing of the thermal path.

<sup>&</sup>lt;sup>4</sup> Experimental data sampled to 10,000 hours and extrapolated beyond

#### 2.2.3 SLL lamp reliability

SSL lamps have properties that difference them from traditional lamps (incandescent, CFL, etc). The most distinguishing features are low power consumption and expected long lifetime. SSL lamps are composed from higher number of diverse components than conventional incandescent lamps. Failure mechanisms are then much different. Conventional incandescent lighting systems fail usually catastrophically, when the filament burns through and no light is emitted anymore. The lifetime of these conventional lamps are usually defined as the time that half of all lamps have failed (B50) [23]. The intensity and change of emitted colour does not play significant role here.

On the other hand, SSL lamps don't usually fail catastrophically. Catastrophic failures can appear when an electronic component or solder join breaks. As an alternative the light output of SSL lamps frequently decreases over time<sup>5</sup>. Lifetime, or "useful life", is defined as decrease of light output power in lumens. The mostly spread normative that has been adopted by many companies is SSL certification which states that an SSL lamp fails when it's light output drops below 70% of the initial light output (L70) [24] [23] [25]. For example the CSSL lifetime specification of 12,000 h (B50L70) indicates that the expected light output of at least 50% of all 60W replacement lamps has to be maintained to a level of 70% (the lumen maintenance level) of the initial 806 lumen light output for a period of 12,000 h<sup>6</sup>.

Light degradation in SSL systems can have several reasons and also many different locations: the LEDs themselves, LED package, additional optical sub-systems (LED lens, light conversion dome,...), the driver current output, the connections and interfaces between components, change of operating temperature, etc. [24]. As SSL lighting systems are envisaged to have lifetime (depending on the specific application, thermal management) up to 50,000 h, qualification over the rated lifetime become very problematic before the design of whole SSL system. Unfortunately, up to now there does not exist globally accepted standard tests for SSL lamp reliability issues [26]. One method of LEDs lifetime prediction is accelerated test approach. In this test estimated life time is multiplied by acceleration factor. Therefore, fast and reliable and cost-effective qualification procedures that are based on accelerated tests are required. Some known accelerated tests is based on the simultaneous or sequential application of thermal, mechanical, moisture and electrical loads. Modelling of acceleration factors is usually used to predict long life of SSL lamp components at specific conditions [26]. Chapter 2.6 in this work describes a new "Highly Accelerated Life Testing" (HALT) test methods for LED board testing<sup>7</sup>.

<sup>&</sup>lt;sup>5</sup> Some reasons has been already mentioned in chapter 2.2.2.1

<sup>&</sup>lt;sup>6</sup> CSSL project specification document

<sup>7</sup> In the semiconductor industry so-called 'highly accelerated stress testing' (HAST) is used combining elevated temperatures, moisture and electrical loads. In electronics industry 'highly accelerated life testing' (HALT) is applied imposing mechanical vibration with temperature increases and electrical loads

#### 2.3 Design of new 806 lumen SSL retrofit lamp

This chapter deals with design of new 806 SSL retrofit lamp that should replace current 400 lumen master LED glow lamp.

SSL (Solid State Lighting) lamps can have a life time up to 50 000 h, but the life time among others effects strongly depends on LED die temperature [23]. Good thermal and thermomechanical management of LED lamps is very important and design of all other parts must be optimized for reliability. In this design process thermal and thermo-mechanical issues play a key role.

Heat dissipation and LED temperature were not a problem when low power LEDs were used. However, in today's high power LED applications thermal management issues must be taken into account [27] to not only ensure light maintenance and quality of LED lamps, but also their life time and reliability. Lamp materials and electronics can age at high operational temperature affecting light output [28]. In today's high-power LED applications, these aspects must be taken into account when predicting light quality, life time and whole system reliability. In such applications, the substrate on which LED devices are soldered (LED board) can become critical [2].

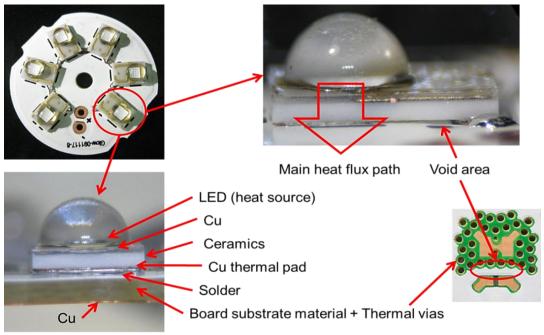

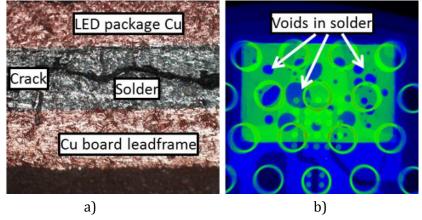

The most critical parts of a LED lamp design from the reliability point of view are LED package and LED board [25] [29] [30]. A LED board usually contains several packaged LED dies (6-12). In a LED package a semiconductor die is usually soldered on ceramics and connected by wire or flip-chip bonding. The LED package is then soldered on the LED board.

The most important objective in LED thermal management is to limit the temperature of LED dies and thermal stresses in solder connections, as these parts are the most critical ones for the useful lifetime of the LED lamp [31] [32] [33] [34]. Contrary to the conventional incandescent lighting, LED lamps in general do not fail catastrophically but, as light output is a function of temperature and time, the light output decreases to an unacceptable level in time. ASSIST (Alliance for Solid-State Illumination System) defines life time as the time on which light output has degraded to 70% of the initial output [13].

#### 2.3.1 Retrofit lamp design requirements and components

Most important SSL retrofit lamp requirement is lamp shape (a lot of customers want a "traditional" light bulb shape to replace old incandescent light bulbs). But not only shape is important. Light colours, distributed light angle, dimming possibilities are other very important aspect that must be taken into account.

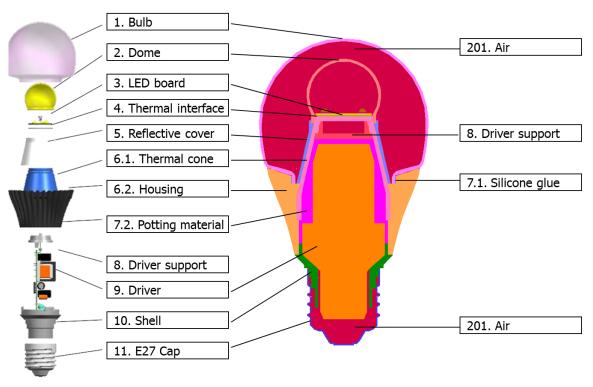

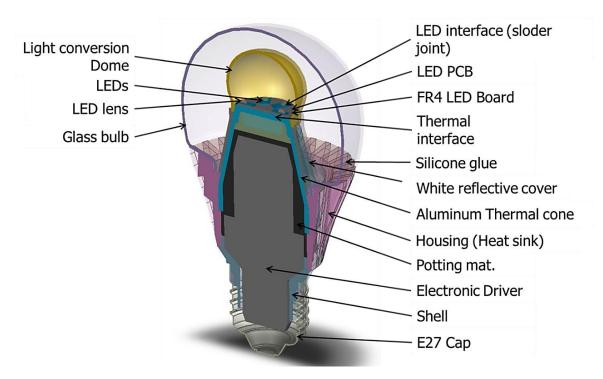

Figure 2.4 shows a cross-section of retrofit shape SSL lamp with most important parts. Core of the lamp is LED board that include six high powers LED ceramic packages that are soldered on FR4 PCB board. The LED package contains one thermal and two electrical copper pads. Each LED package cover small silicon lens that widening light beam angle. High power LEDs are typically based on GaN solid state semiconductors that emit light in a narrow blue range of the visible spectrum. Blue light has to be converted into white or yellow-white light, comparable to the spectrum of incandescent light bulbs. In this case a remote polycarbonate spherical

conversion dome is used. The dome is mounted on the top of LED board. Another purpose of remote dome is wide angle light distribution. SSL lamp contains also an electronic driver board, which is composed of AC-DC power suppliers, DC-DC converter and current driver controller. The driver maintains the electrical, dimming and optical properties of LEDs [5].

LED board is mounted on top of an alumna thermal cone that dissipates a heat from LEDs and driver (that is embedded in a potting material) to a thermal conductive polymer housing (heat sink). Standard E27 cap is used for lamp mounting. White polyimide reflective cover is attached to thermal cone that reflect the light. A driver support mechanically mounts the driver and thermal interface layer (deposited between LED board and aluminium alloy thermal cone) improve thermal dissipation.

Figure 2.4: Master LED Glow 8 W lamp parts [5]

#### 2.3.2 Methodology for light output improvement

This section proposes a design flow for development of LED lamp models and characterization and validation of the models. The result is calibrated thermal model that can be used for further design and new LED lamp parts development.

#### LED lamp models development steps

- Preliminary selection of (existing) LED lamp components, identifying of thermal properties, thermal management possibilities and defining of available packaging materials.

- Stepwise modelling of simplified LED lamp concept, incorporating more components until the LED lamp is modelled completely.

- Performing simulation on detailed sub-models and thermal boundary conditions transfer from complete model simulated in previous activity. Materials and components data are

used in to simulate the performance of the conceptual designs; special attention is given to materials interfaces.

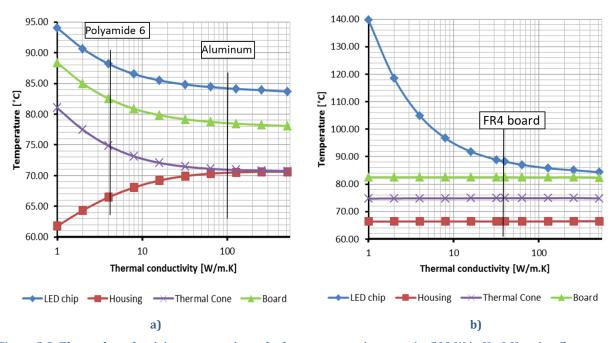

- Variation of heat management in simulations, within the constraints of the simplified model. Parameter study of thermal material properties is carried on to investigate influence of material thermal conductivity to each LED lamp component.

- Modification of material properties and simulation software, depending on the results validation from LED lamp models characterization and validation.

- Identification of thermal resistances of critical LED lamp components.

- Calculation of thermal distribution for new 806 lumen lamp.

- Development of the new LED lamp design methodology for 806 lumen lamp.

#### LED lamp models characterization and validation steps

- Physical material properties characterization required for the simulations.

- Development of a method for LED board material thermal conductivity measuring; method suited for development purposes as well.

- Thermal characterization of the LED lamp.

- Software Validation, comparison of measured and simulated results. Identifying of sources of difference.

The above proposed steps are developed for new 806 lumen lamp, but can be successfully transferred to any other SSL lamp.

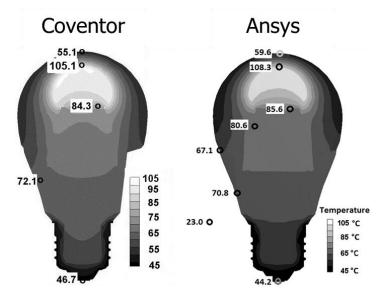

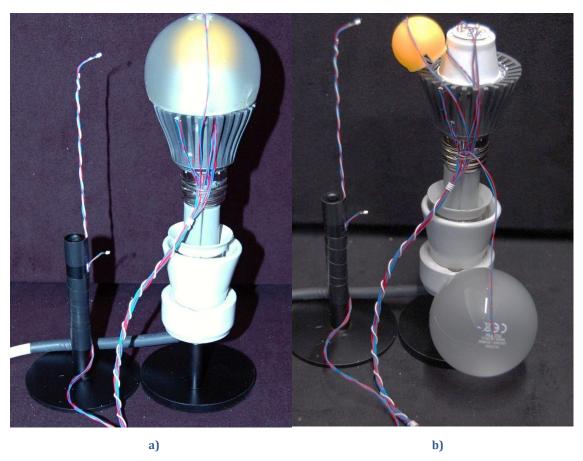

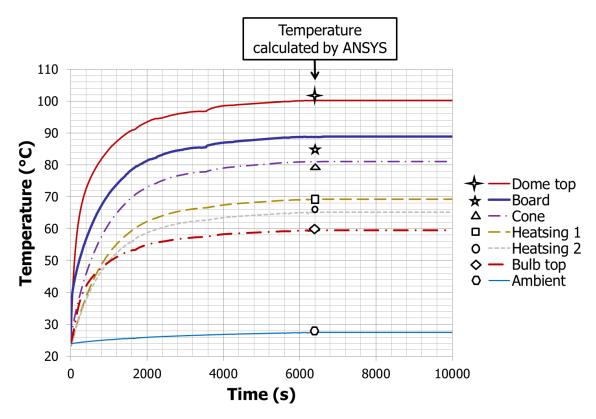

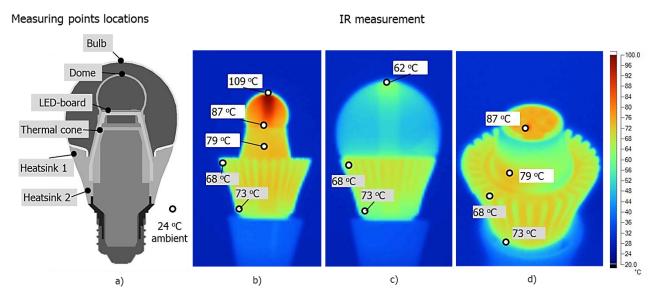

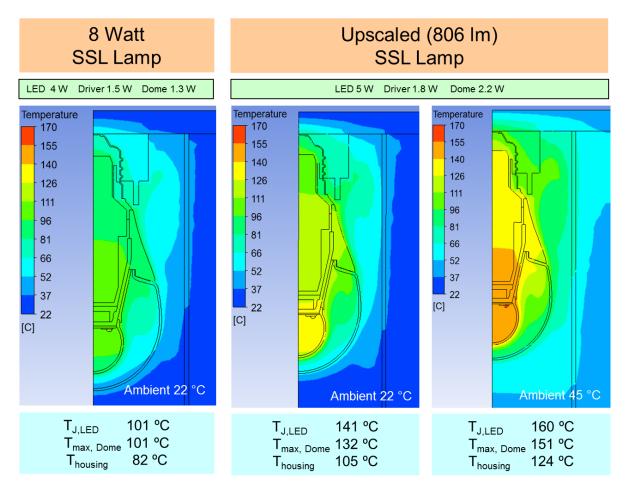

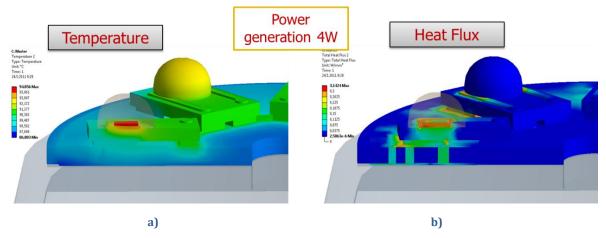

#### 2.3.3 Thermal simulation and validation of reference 8W master LED glow

Main purpose of this work has been to get closer to understand thermal phenomena in SLL retrofit LED lamp. For an evaluation Philips 8W master LED glow has been chosen<sup>8</sup>. Thermal management is of critical importance for performance, reliability and life expectancy of a SSL LED lamp. Heat generation and flow inside a lamp will cause a thermo-mechanical loading of the components initiating material and performance degradation and earlier failures. Therefore the multi-target simulation models (such as thermal, thermo-mechanical, reliability and optics) have been integrated to conduct multi-physics simulation of reference master LED glow to provide integrated inputs for new design. Simulations are carried out with ANSYS and CoventorWare software tools to compere not the same simulation methods. The integrated simulation results have been validated experimentally using an existing 8W SSL lamp. Designed simulation models result in new applicable design approach for new 12 W retrofit SSL lamps.

Materials properties (especially thermal conductivity) parametric study has been performed to determine problematical parts that transfer heat from power LEDs to ambient. Solutions for future 12 W retrofit SSL lamp design are proposed. Modelling of SSL lamp has brought more understanding in the design of new lamp shape with new materials. Moreover, explanation of thermal effects inside of SSL lamp can predict light quality, life time and reliability.

<sup>8</sup> The work was done in frame of CSSL project that should develop new 12 W SSL lamp based on Philips 8W master LED glow

#### 2.3.3.1 Thermal model of 8W master glow LED lamp

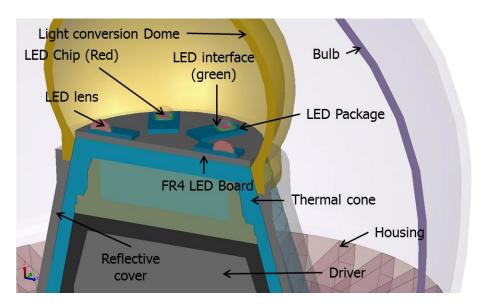

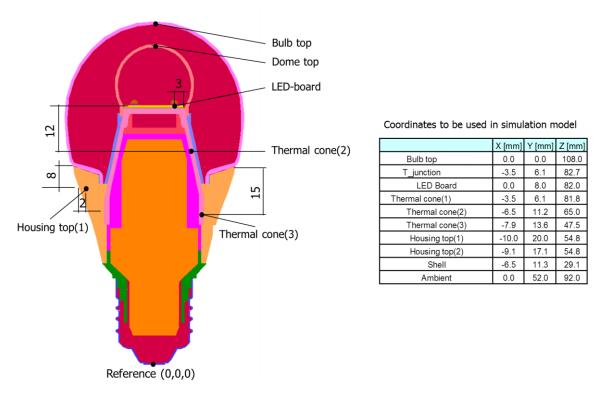

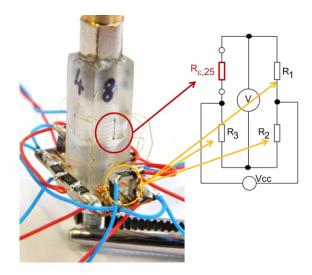

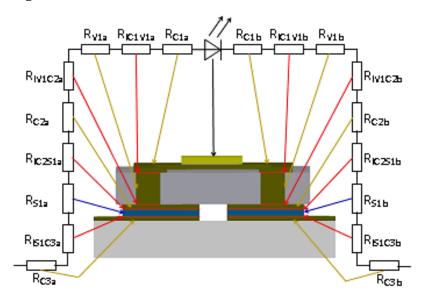

The conception and design of the geometric model is very significant phase in 3D FEM simulation. The realistic geometry of existing SSL lamp is naturally complex and is composed by many parts and materials. A complete three-dimensional model of retrofit 8W LED Lamp was designed taking into account all essential details (Figure 2.5). The model characterizes a retrofit LED lamp including six blue power LEDs mounted on PCB board. LED GaN wafer is flip-chipped on ceramic package that includes one thermal and two electrical copper pads. Each LEDs chip is covered by a small silicon lens widening a light beam angle (Figure 2.6) [2].

Figure 2.5: SSL Lamp 3-D model includes sixteen different compact parts. Air inside light bulb and inside light conversion dome was included to the model [2]

An essential phase of three-dimensional finite element simulation is definition of the mesh type and mesh generation since it has great impact to the accuracy of the final results. The SSL lamp FEM model mesh has been generated properly detailed to get an acceptable accuracy. Because of the non-orthogonal parts in the model, tetrahedrons elements are used to (which merge and extrude all layers) create a continuous mesh. To keep number of nodes as small as possible, the element distribution is adapted to the shape of the bodies; it means that the number of elements is only increased to capture small features in the model where high heat flus is expected. By this technique we are able to keep computing time at reasonable level. The designed models contain approximately 490,000 nodes depending on the model version [2].

Figure 2.6: Detailed view on LED board placed on aluminium alloy thermal cone. The board includes six LED with Al203 package and LED chip [2]

#### 2.3.3.2 Material properties database

One of the most important inputs in FEM modelling that mostly affect validity of simulation results is not only precision of 3D model and its mesh, but also the accuracy of the material properties data. In the SSL lamp simulation model (Figure 2.5) twelve different materials are used. Thermal and mechanical coefficients for each of these materials were collected from different sources [35] [36] [37] [38] [39] [40] [41]. The most problematic issue is identifying component material type properly. For example, some material properties of SSL lamp components are not defined consistently in different sources that refer to not the same values. To resolve this difficulty, the average value of the given material quantities has been used. Another problem arises when some components are simplified as in case of electronic driver. The driver is composed from PCB board and many electronic components. Detail model will be very complex. In current model the driver was simplified to one component where thermal material properties have been estimated<sup>9</sup>.

The thermal and mechanical material properties used for the modelling of the LED lamp are summarized in Table 2-4.

\_

<sup>&</sup>lt;sup>9</sup> This simplification was considered only for the first thermal evaluation. More complex model has been designed for the driver in further simulations

|                 | Thermal para | ermal parameters |           | Mechanical parameters |         |                |  |

|-----------------|--------------|------------------|-----------|-----------------------|---------|----------------|--|

| Material        |              | Specific         |           |                       |         | References     |  |

|                 | Thermal      | heat             | Thermal   | Young's               | Poisson |                |  |

|                 | Conductivity | Ср               | expansion | modulus               | ratio   |                |  |

|                 | λ [W/mK]     | [J/kgK]          | α [e-6/K] | E [GPa]               | ν[-]    |                |  |

| GaN             | 130          | 490              | 5.6       | 200                   | 0.4     | [25] [37]      |  |

| Aluminium alloy | 100          | 880              | 23.4      | 70                    | 0.3     | [42]           |  |

| Copper          | 400          | 385              | 17.0      | 110                   | 0.4     | [42]           |  |

| Brass Ni        | 122          | 380              | 20.0      | 100                   | 0.3     | [38] [40]      |  |

| Glass           | 1.10         | 840              | 8.0       | 70                    | 0.3     | [38] [42]      |  |

| Polycarbon      | 0.20         | 2000             | 50.0      | 5                     | 0.3     | [36] [39] [38] |  |

| Silicone        | 0.22         | 1460             | 220.0     | 1                     | 0.5     | [36] [35] [38] |  |

| Silicone filler | 2.00         | 1460             | 220.0     | 1                     | 0.5     | [41]           |  |

| PBT             | 0.27         | 1700             | 25.0      | 9                     | 0.3     | [38] [40]      |  |

| Polyamide6      | 4.0          | 1130             | 40.0      | 15                    | 0.40    | [38] [40]      |  |

| FR4             | 4.0          | 1085             | 23.4      | 70                    | 0.3     | [42]           |  |

| LED board       | 40           | 1085             | 23.4      | 70                    | 0.3     | Estimated      |  |

Table 2-4: SSL Lamp thermal and mechanical material properties used for LED lamp simulation [5]

#### 2.3.3.3 Thermal modelling

To obtain and compare steady state and dynamic thermal distribution of LED lamp ANSYS, ANSYS-CFX and CoventorWare finite element simulation tools have been used. The steady-state heat conduction equation shown below is solved to obtain temperature distribution for specified thermal boundary conditions, including natural convection and radiation. The Fourier equation for temperature distribution can be written as follows [43]:

$$div(\lambda gradT) = \rho c \frac{\partial T}{\partial t} - p,$$

(2.1)

where  $\lambda$  [W m<sup>-1</sup> K<sup>-1</sup>] is coefficient of thermal conductivity,  $\rho$  mass [kg m<sup>-3</sup>], c [J kg<sup>-1</sup> K<sup>-1</sup>] thermal capacity and p specific heat [W m<sup>-3</sup>]. Coefficient of thermal conductivity is not constant in wide temperature range. The value of heat flux can be expressed as:

$$q = -\lambda \cdot gradT \qquad [W.m-2], \qquad (2.2)$$

If the solid body is heated up by constant power generation and cooled down constantly by surrounding environment then the temperature distribution will reach steady state. For Cartesian coordinate the temperature distribution can be obtained by solving following equation [44]:

$$\nabla^2 T(r,t) + \frac{Q(r,t)}{\lambda} = \frac{1}{\alpha} \frac{\partial T(r,t)}{\partial t}$$

(2.3)

#### Convection

Ambient of SSL lamps is air that can move freely around LED lamp surface and also in the lamp bulb. Natural convection plays dominant role in cooling and heat sink design. It depends on specific dimensions and shapes of the device.

The density of heat flux under the convection is given [44]:

$$q = \alpha \cdot \Delta t = \alpha \left( t_{st} - t_{t} \right) \quad [\text{W.m}^{-2}], \tag{2.4}$$

where  $\alpha$  [W.m<sup>-2</sup>.s<sup>-1</sup>] is heat transfer coefficient given by criteria equation (see below),  $t_{st}$  is wall temperature of solid body,  $t_t$  is gas or liquid surrounding temperature and A contact area. Criteria equation can be found in literature in following form for instance [44]:

$$Nu = f(Re, Gr, Pr, ....), \text{ where}$$

(2.5)

$$Nu = \frac{\alpha L}{\lambda_{tek}}$$

,  $Re = \frac{c \cdot L}{v}$ ,  $Pr = \frac{v}{a} = \frac{\eta \cdot c_p}{\lambda}$ ,  $Gr = \gamma \cdot \Delta t \cdot \frac{gL^3}{v^2}$ ,  $Pe = \frac{c \cdot L}{a} = \text{Re} \cdot \text{Pr}$

Criteria equation for natural convection can be expressed in the form [44]:

$$Nu = C \cdot (Gr.\Pr)^n, \tag{2.6}$$

*C* and *n* constants depends on the value of the product Gr.Pr according Table 2-5:

Table 2-5: value of C and n depends on Gr.Pr [45]

| Gr.Pr                                  | С     | n     |

|----------------------------------------|-------|-------|

| < 1.10-3                               | 0.45  | 0.03  |

| 1.10 <sup>-3</sup> ≅ 5.10 <sup>2</sup> | 1.18  | 0.125 |

| $5.10^2 \cong 2.10^7$                  | 0.54  | 0.25  |

| 2.10 <sup>7</sup> ≅ 1.10 <sup>13</sup> | 0.195 | 0.333 |

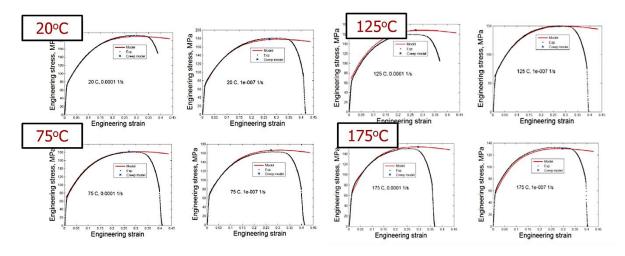

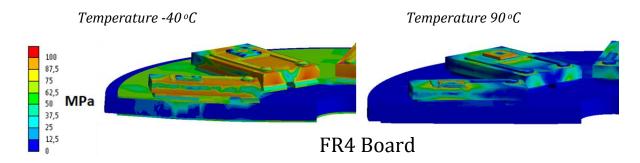

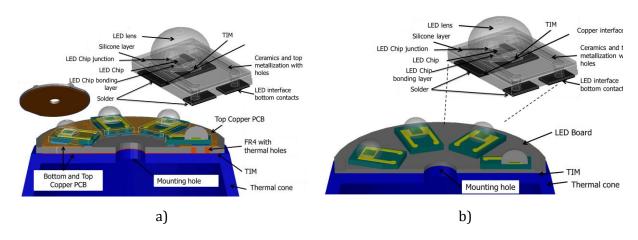

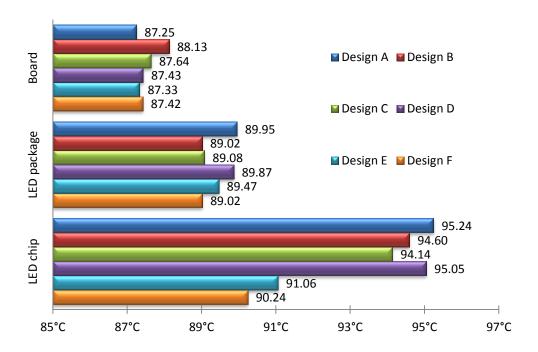

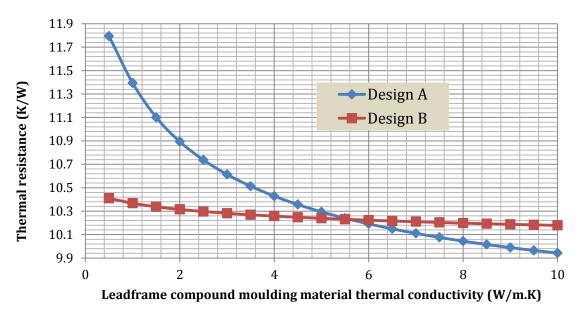

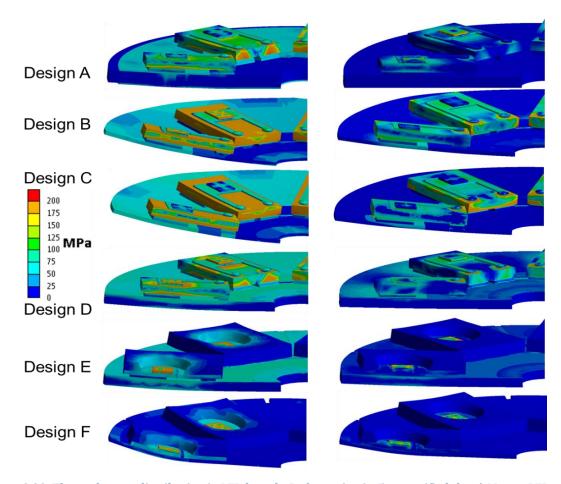

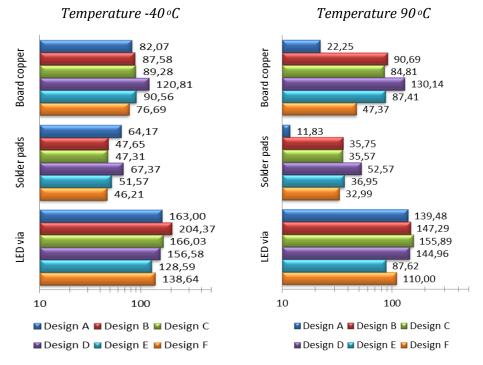

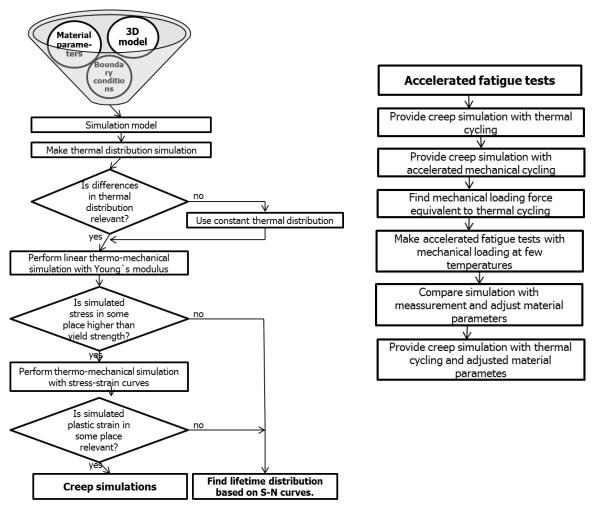

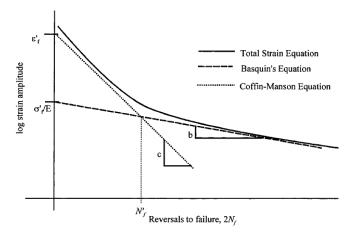

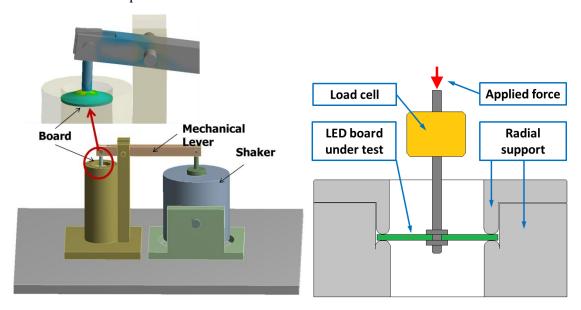

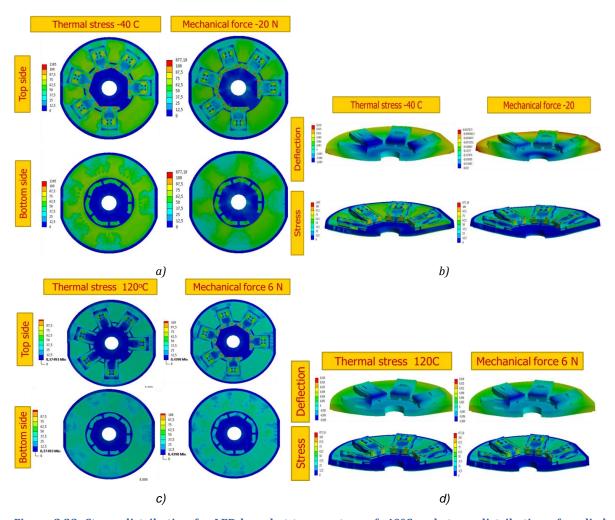

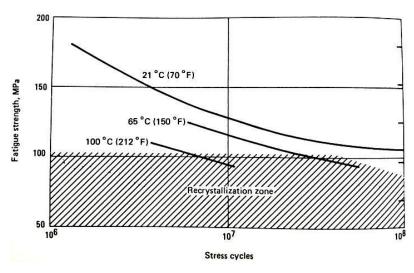

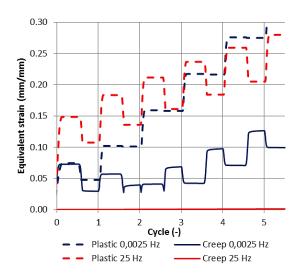

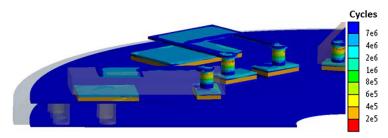

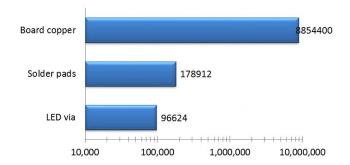

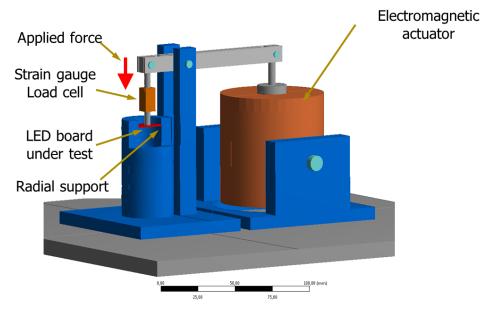

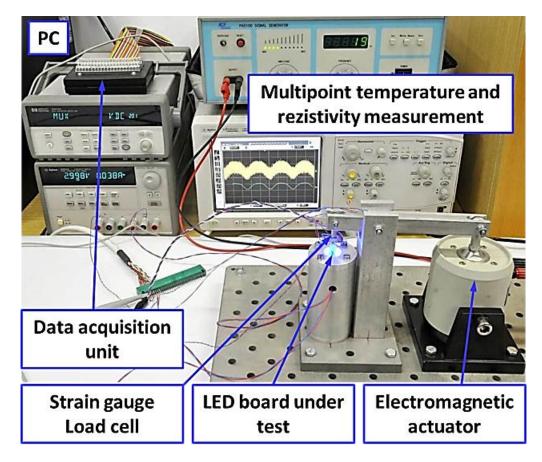

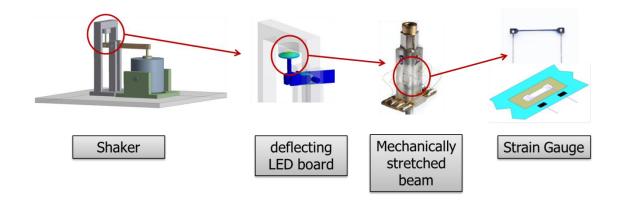

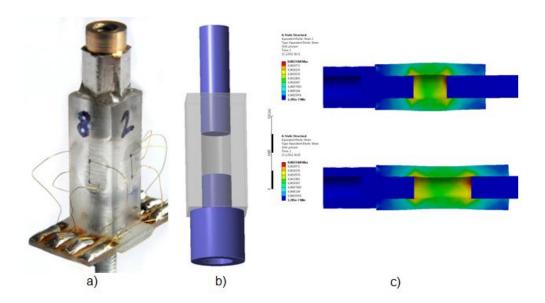

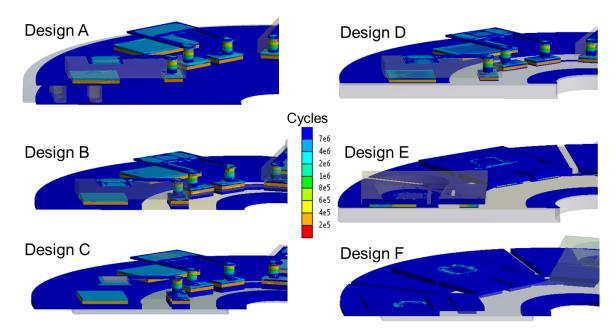

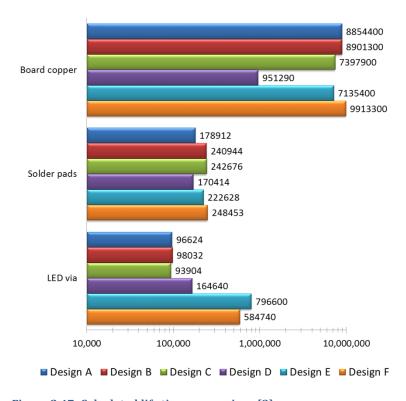

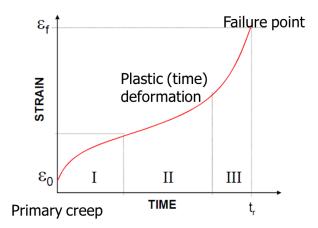

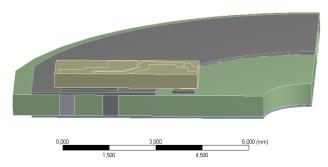

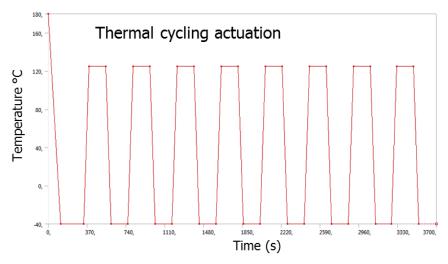

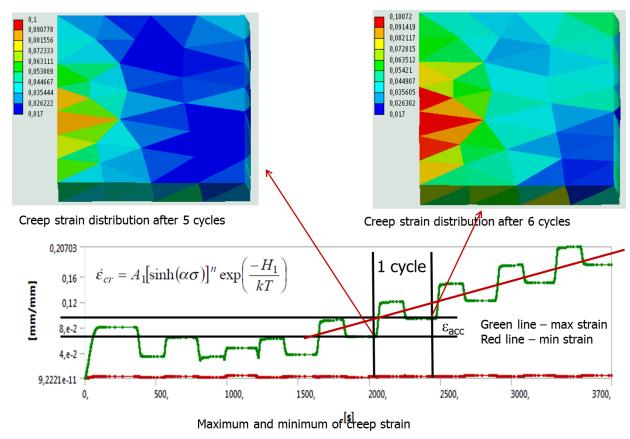

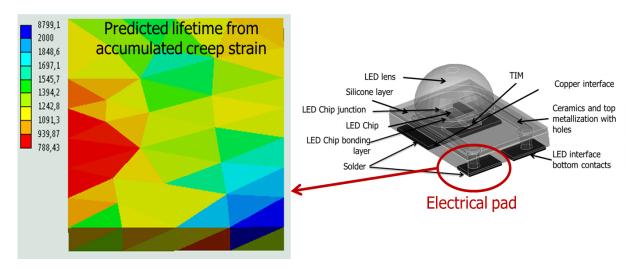

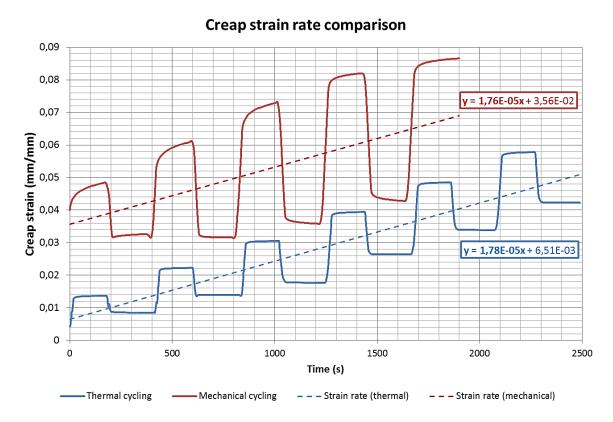

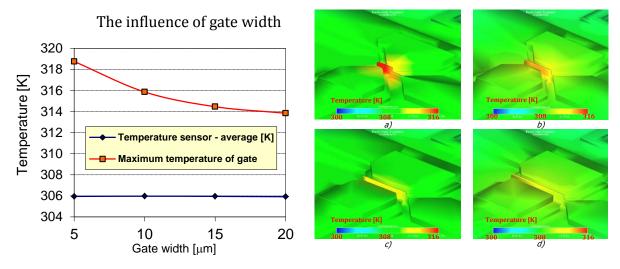

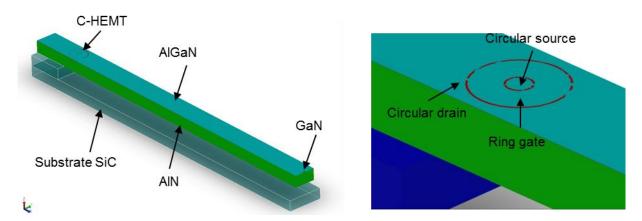

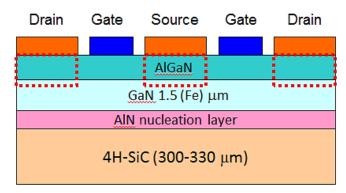

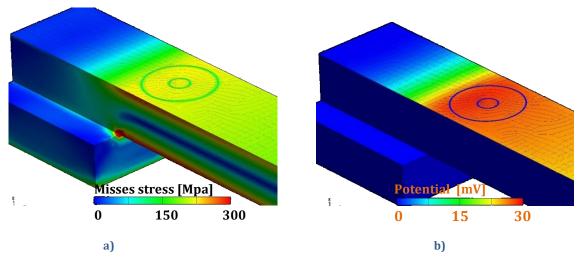

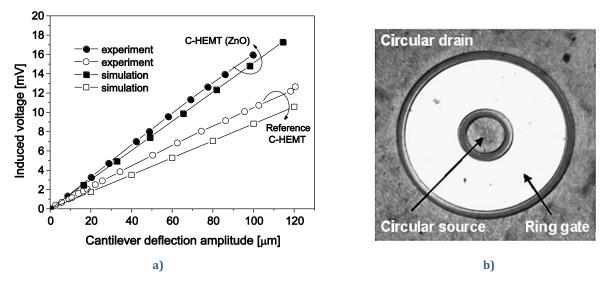

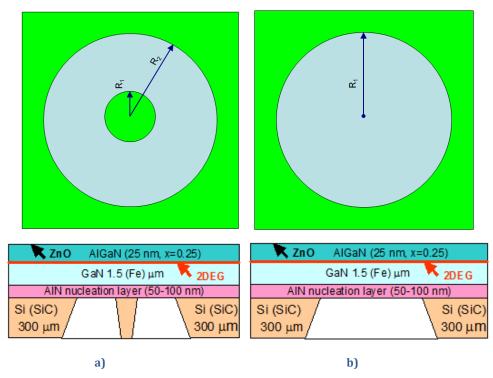

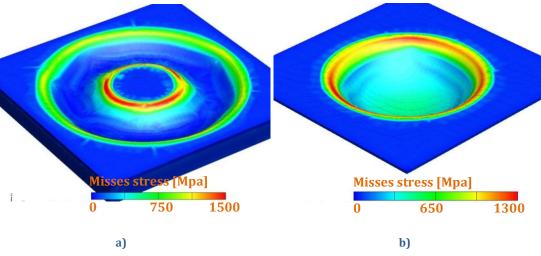

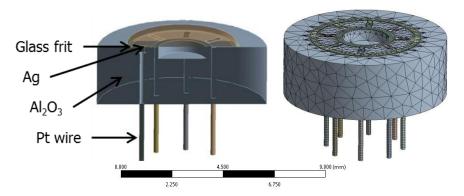

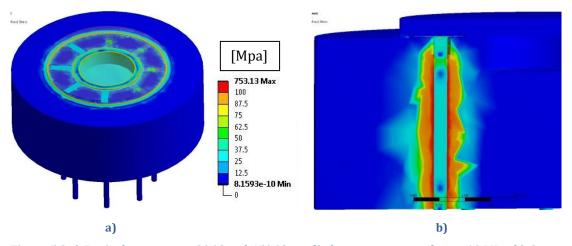

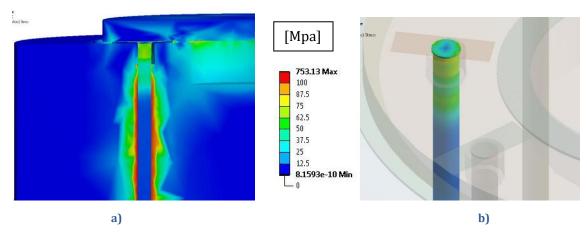

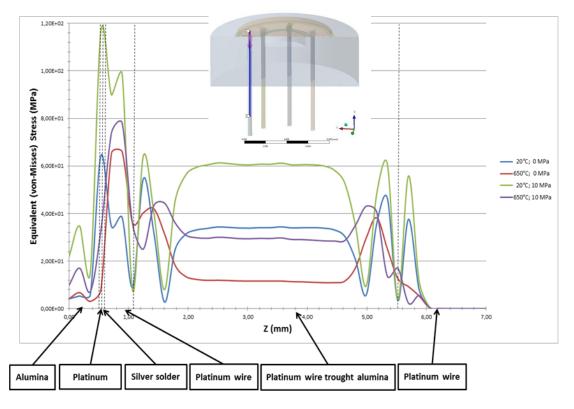

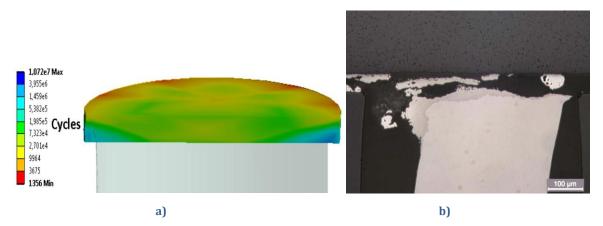

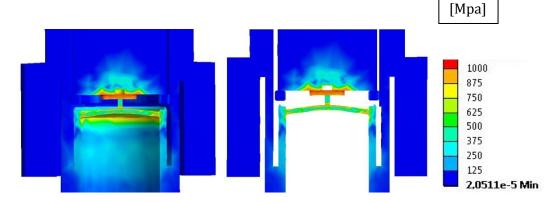

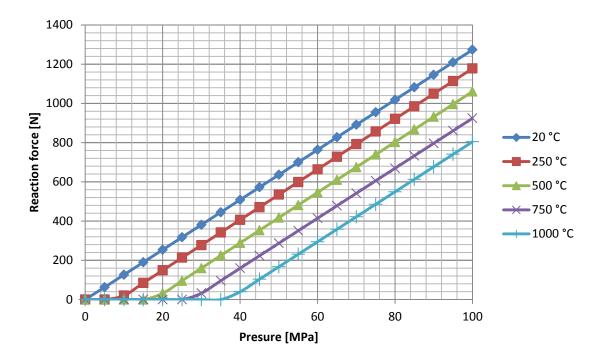

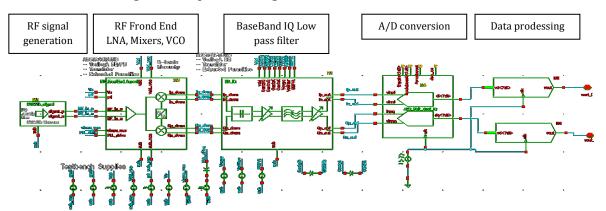

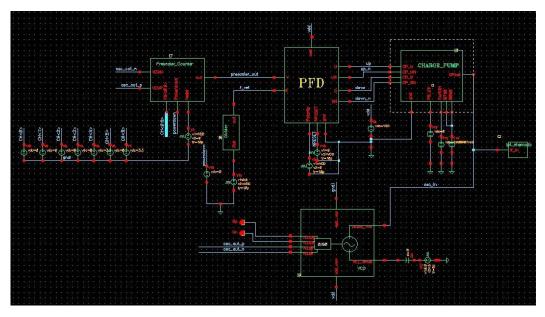

#### Radiation