Czech Technical University in Prague Faculty of Electrical Engineering Department of Microelectronics

### **Doctoral Thesis**

#### **Column-parallel Sampling for a Monolithic Pixel Detector**

by

Ing. Pavel Vančura

Supervisor: Doc. Ing. Jiří Jakovenko, Ph.D Co-supervisor: Ing. Miroslav Havránek, Dr. rer. nat.

Doctoral degree study programme: P2612 Electrical Engineering and Information Technology Specialization: 2612V015 Electronics

Prague, January 2022

#### Supervisor:

Doc. Ing. Jiří Jakovenko, Ph.D Department of Microelectronics Faculty of Electrical Engineering Czech Technical University in Prague Technická 2 160 00 Prague 6 Czech Republic

#### **Co-Supervisor:**

Ing. Miroslav Havránek, Dr. rer. nat. Physics Department Faculty of Nuclear Sciences and Physical Engineering Czech Technical University in Prague Břehova 7 115 19 Prague 1 Czech Republic

# Declaration

I hereby declare I have written this dissertation thesis independently and quoted all the sources of information used in accordance with methodological instructions on ethical principles for writing an academic thesis.

Date:

Signature:

# Acknowledgement

This research has been partially supported by the Grant Agency of the Czech Technical University in Prague, grant No. SGS SGS20/175/3T/13, and by the Centre of Advanced Applied Sciences co-financed by the European Union with the number:  $CZ.02.1.01/0.0/0.0/16_019/0000778$ .

## Abstrakt

Tato dizertační práce se věnuje vývoji převodníku analogového signálu na digitální (ADC) s postupnou aproximací (SAR) a využitím plně diferenciální architektury pro monolitický pixelový detektor (MAPS) Spacepix-2 v technologii 180 nm SoI CMOS. MAPS detektory představují aktuální trend ve fyzikáních experimetech detekce částic o vysokých energiích (HEP). Kromě fyzikálních experimentů jsou tyto detektory hojně využívány v lékařských a kosmických aplikacích. ADC umístěné pod pixelovou maticí v MAPS detektoru se nazývá sloupcové ADC. Ve standardní architektuře pixelový detektor využívá pro každý sloupec jedno sloupcové ADC a analogové signály z pixelů jsou digitalizovány řádek po řádku. Hlavním problémem při návrhu diferenciálního sloupcového SAR ADC je jeho limitovaná šířka, která je dána šířkou pixelu. Spacepix-2 má šířku pixelu 60 μm. Při řešení tohoto problému byla navržena nová architektura v 8-bit a 10-bit verzi, ve které jedno sloupcové SAR ADC je použito pro vzorkování signálů ze dvou sloupců. Plocha SAR ADC se tedy zvětší na 120 µm. Tato nová architektura přispívá ke zlepšení rychlosti vzorkování, linearity, zmenšuje šum a dokonce i snižuje spotřebu SAR ADC. Navržené řešení jednoho sloupcového SAR ADC v 8-bit verzi dosahuje rychlosti vzorkování 4 MSps a spotřeby 200 µW při napájecím napětí 1.8 V. 10-bit verze dosahuje stejných parametrů s vyšší spotřebou 250 µW.

#### Klíčová slova:

SAR, ADC, MAPS, sloupec, pixel, vyčítací, elektronika

## Abstract

This thesis concerns the development of a fully differential analog to digital converter (ADC) with successive approximation (SAR) for a monolithic pixel detector (MAPS) Spacepix-2 in 180 nm SoI CMOS technology. MAPS detectors represent the actual trend in high-energy physics experiments (HEP). Besides HEP experiments are MAPS detectors often used in medical and space applications. ADC placed under the column of the MAPS pixel matrix is called column ADC. A single ADC for a single column is used in standard architecture. Analog signals from pixels are digitized row by row. The main problem of the differential column SAR ADC design is a limited width determined by the pitch of the pixel. The Spacepix-2 pixel pitch is 60  $\mu$ m. This thesis proposes a new SAR column ADC architecture in 8-bit and 10-bit versions, where each ADC has multiplexed input to two columns. The layout area is doubled to 120  $\mu$ m. This new architecture helps achieve higher speed, linearity, low noise, and low power consumption of the proposed SAR ADC. The 8 bit column ADC reaches sampling rate 4 MSps, average power consumption is 200  $\mu$ W from a 1.8 V power supply at ten frames per second readout frequency. The 10 bit version achieves the same parameters with the higher power consumption of 250  $\mu$ W.

#### Keywords:

SAR, ADC, MAPS, column, pixel, read-out, electronics

# Contents

| In       | trodu | uction   |                                | 1  |

|----------|-------|----------|--------------------------------|----|

|          | Moti  | ivation  |                                | 2  |

|          | Aim   | s of the | Thesis                         | 3  |

|          | Stru  | cture of | f the Thesis                   | 3  |

| 1        | The   | oretica  | al Background                  | 4  |

|          | 1.1   |          | 8                              | 6  |

|          | 1.2   |          |                                | 6  |

|          | 1.3   |          |                                | 8  |

|          | 1.4   |          |                                | 9  |

| <b>2</b> | 8-bi  | t Colu   | mn SAR ADC 1                   | .2 |

| _        | 2.1   |          |                                | 12 |

|          |       | 2.1.1    |                                | 4  |

|          |       | 2.1.2    |                                | 4  |

|          |       | 2.1.3    |                                | 15 |

|          |       |          |                                | 17 |

|          |       |          | -                              | 17 |

|          |       |          |                                | 9  |

|          |       |          |                                | 21 |

|          |       |          |                                | 21 |

|          |       | 2.1.4    |                                | 22 |

|          |       | 2.1.5    | Layout                         | 23 |

|          |       | 2.1.6    | Bandgap Voltage Reference      | 23 |

|          |       | 2.1.7    | Layout of all 32 Column ADCs 2 | 24 |

| 3        | 10-b  | oit Col  | umn SAR ADC 2                  | 26 |

|          | 3.1   | 10-bit   | column ADC architecture        | 26 |

|          | 3.2   |          |                                | 29 |

|          |       | 3.2.1    |                                | 29 |

|          |       | 3.2.2    |                                | 31 |

|          |       | 3.2.3    | • -                            | 31 |

|          | 3.3   | Layout   |                                | 33 |

| <b>4</b> | Software and Electronics for Spacepix Detector Read-out | 38        |

|----------|---------------------------------------------------------|-----------|

|          | 4.1 Spacepix Daughter-boards                            | 38        |

|          | 4.2 Fast Read-out Interface (FURRy)                     | 40        |

|          | 4.3 ASPIRE                                              | 40        |

|          | 4.4 ADC measurement setup                               | 41        |

|          | 4.5 Inject                                              | 43        |

| <b>5</b> | Results                                                 | 44        |

|          | 5.1 8-bit column ADC results                            | 44        |

|          | 5.2 10-bit column ADC Results                           | 47        |

|          | 5.2.1 The Spacepix-2 ASIC measurement                   | 47        |

|          | 5.2.2 The Spacepix-2-lin-A ASIC Measurement             | 50        |

| Co       | onclusion                                               | 60        |

| Su       | ummary of Scientific Contribution of this Thesis        | <b>62</b> |

| Co       | ompleted Aims                                           | 62        |

| Fu       | ture Work                                               | 63        |

|          | Bibliography                                            | 64        |

|          | Publications of the Author                              | 66        |

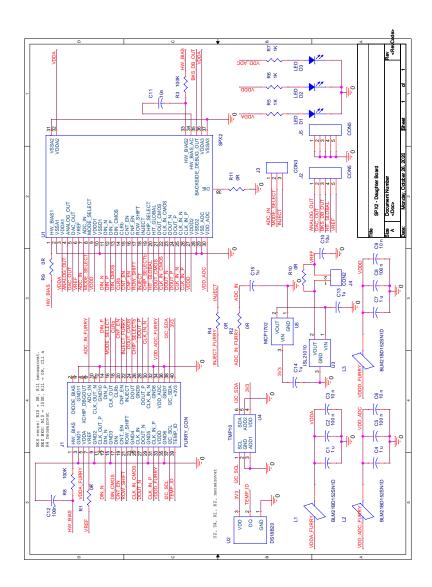

| A        | Spacepix-1 Daughterboard PCB                            | 68        |

| в        | Spacepix-2 Daughterboard PCB                            | 70        |

# List of Figures

| 1.1  | 1 1                                                                                                                                               | 5  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  |                                                                                                                                                   | 5  |

| 1.3  | The SAR ADC block diagram.                                                                                                                        | 7  |

| 1.4  | The single-ended and differential successive approximation cycle                                                                                  | 7  |

| 1.5  | An illustration of the major problem solved in this thesis                                                                                        | 8  |

| 2.1  |                                                                                                                                                   | 12 |

| 2.2  |                                                                                                                                                   | 13 |

| 2.3  | 11                                                                                                                                                | 14 |

| 2.4  | 1 1                                                                                                                                               | 15 |

| 2.5  |                                                                                                                                                   | 15 |

| 2.6  | 8                                                                                                                                                 | 16 |

| 2.7  |                                                                                                                                                   | 6  |

| 2.8  |                                                                                                                                                   | 17 |

| 2.9  |                                                                                                                                                   | 8  |

| 2.10 | 8                                                                                                                                                 | 8  |

| 2.11 | U I                                                                                                                                               | 9  |

|      | 0                                                                                                                                                 | 9  |

|      |                                                                                                                                                   | 9  |

|      |                                                                                                                                                   | 20 |

|      |                                                                                                                                                   | 21 |

|      |                                                                                                                                                   | 21 |

|      | I O                                                                                                                                               | 22 |

|      | 1 0 0( )                                                                                                                                          | 22 |

| 2.19 | The FSM circuit diagram                                                                                                                           | 23 |

|      |                                                                                                                                                   | 23 |

|      | v                                                                                                                                                 | 24 |

| 2.22 | The layout of 32 column ADCs                                                                                                                      | 25 |

| 3.1  | The 10-bit column ADC block diagram, the input signals on the left side<br>going though buffers to ADC driver. FSM controls the asynchronous con- |    |

|      | 1 0                                                                                                                                               | 27 |

| 3.2  | <b>9</b> 0                                                                                                                                        | 28 |

| 3.3  | The 10-bit SAR ADC block schematic                                                                                                                | 28 |

| 3.4  | The 10-bit version comparator design                                                                             |

|------|------------------------------------------------------------------------------------------------------------------|

| 3.5  | An example of 3-bit folded CDAC design                                                                           |

| 3.6  | The compensation of parasitic capacitances of CDAC                                                               |

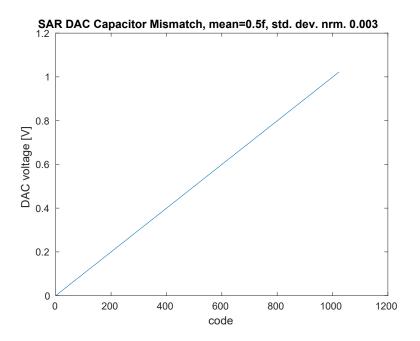

| 3.7  | The capacitor mismatch simulation in Matlab                                                                      |

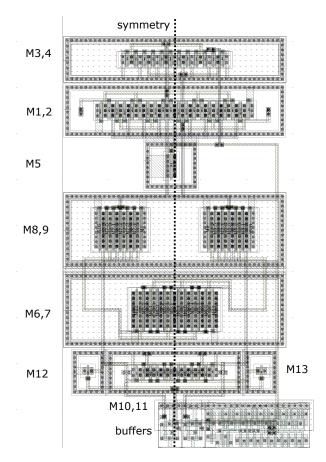

| 3.8  | The layout of the comparator                                                                                     |

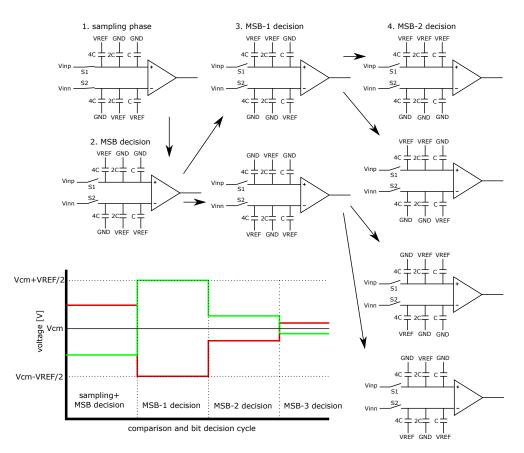

| 3.9  | The used switching scheme. $34$                                                                                  |

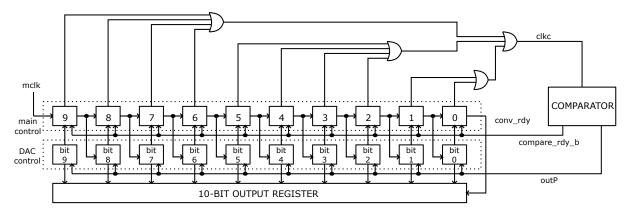

| 3.10 | The simplified block diagram of the asynchronous 10-bit SAR logic 34                                             |

| 3.11 | The timing diagram of single SAR logic bit (not to scale) [1]                                                    |

| 3.12 | The main control and DAC control finite state diagrams [1]                                                       |

| 3.13 | The DAC control                                                                                                  |

| 3.14 | The main control $\ldots \ldots 33$ |

| 3.15 | The 10-bit column ADC layout                                                                                     |

| 3.16 | The 10-bit column ADC layout in detail                                                                           |

| 4.1  | The functional illustration of the read-out flow for XCHIP03 and Spacepix                                        |

|      | MAPS detectors                                                                                                   |

| 4.2  | The Spacepix-1 daughter PCB                                                                                      |

| 4.3  | The Spacepix-2 daughter PCB                                                                                      |

| 4.4  | The Fast Read-out Interface (FURRy)                                                                              |

| 4.5  | ASPIRE                                                                                                           |

| 4.6  | The used ADC measurement setup                                                                                   |

| 5.1  | The simulated DNL                                                                                                |

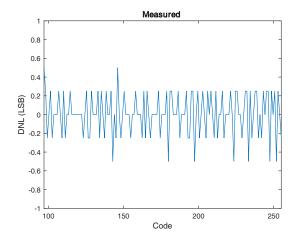

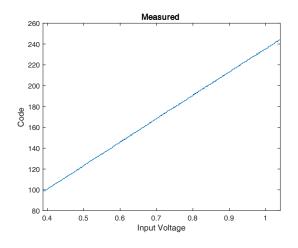

| 5.2  | The simulated INL                                                                                                |

| 5.3  | The measured DNL                                                                                                 |

| 5.4  | The measured INL                                                                                                 |

| 5.5  | The measured transfer function                                                                                   |

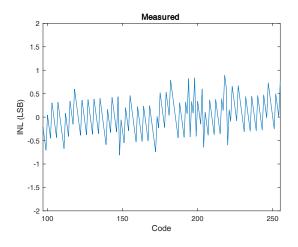

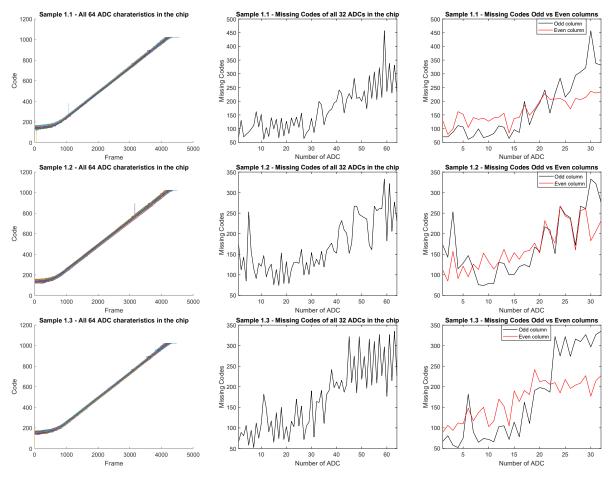

| 5.6  | The missing codes measurement of chip samples 1.1-1.3                                                            |

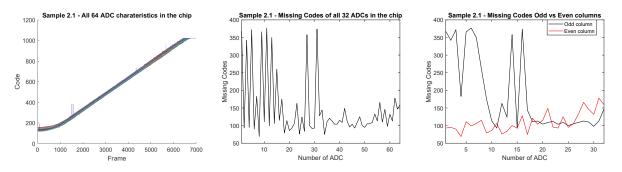

| 5.7  | The missing codes measurement of chip sample 2.1                                                                 |

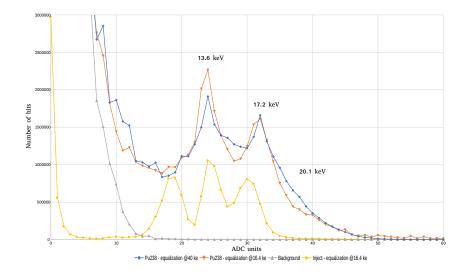

| 5.8  | The Plutonium-238 spectrum measurement with the Spacepix-2 detector 50                                           |

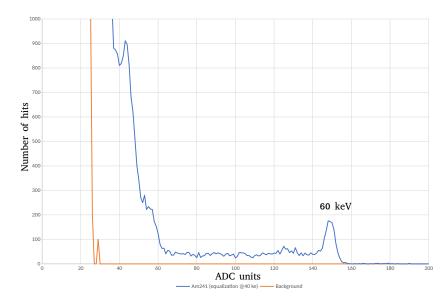

| 5.9  | The Americium-241 spectrum measurement with the Spacepix-2 detector 51                                           |

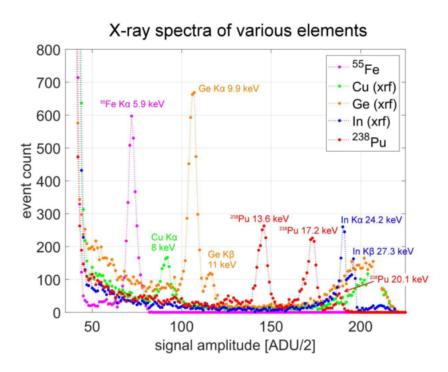

| 5.10 | The measured spectra of different particles with the XCHIP-03 MAPS de-                                           |

|      | tector                                                                                                           |

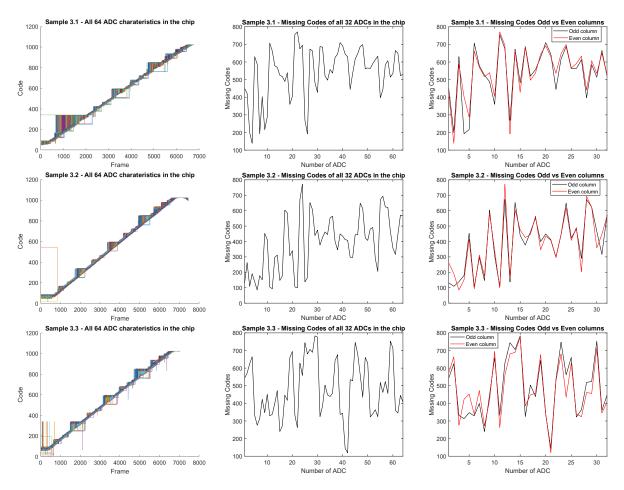

|      | The Missing codes measurement of chip sample 3.1-3.3                                                             |

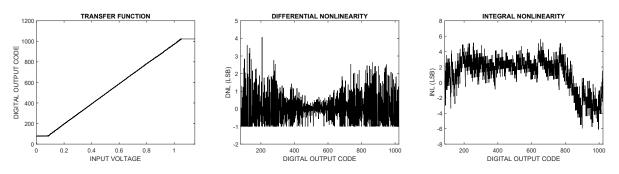

| 5.12 | The measured transfer function and calculated INL, DNL of ADC 11 in the                                          |

|      | Spacepix-2-lin-a ASIC. $54$                                                                                      |

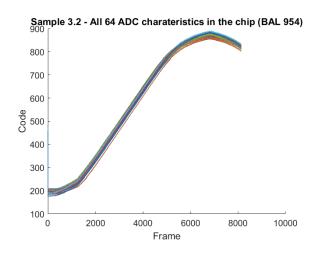

| 5.13 | The measurement of the sample 3.2 with BAL control voltage settings at                                           |

|      | the level 954                                                                                                    |

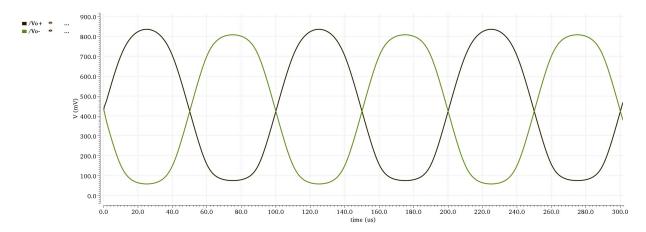

|      | The simulation of the ADC driver output when 954 BAL settings 55                                                 |

| 5.15 | The comparison of the DAC control FSM simulation between the standard                                            |

|      | cells design in Fig. 2.12 (on the left) and the transistor logic design in Fig.                                  |

|      | 2.11 (on the right). $\ldots$   |

| 5.16 | The missing codes comparison of post-layout simulation with enabled 150 |    |

|------|-------------------------------------------------------------------------|----|

|      | GHz optimization of proposed 10-bit SAR ADC with 0.5 fF capacitor in    |    |

|      | CDAC (on the left) and 1 fF capacitor in CDAC (on the right).           | 57 |

| 5.17 | The microphotography of manufactured 10-bit column ADC used in the      |    |

|      | Spacepix-2-lin-a ASIC.                                                  | 58 |

# List of Tables

| 1.1 | The comparison of existing ADC architectures                               | 6  |

|-----|----------------------------------------------------------------------------|----|

| 1.2 | The design parameters                                                      | 9  |

| 1.3 | The comparison of original and McGreary SAR ADC properties                 | 10 |

| 2.1 | The simulated transient noise of the comparator.                           | 20 |

| 4.1 | The ADC setting of the global configuration of the Space<br>pix-2 detector | 42 |

| 5.1 | The comparison of the proposed 8-bit design with other column SAR ADCs.    | 47 |

| 5.2 | The design differences between Spacepix-2 and Spacepix-2-lin-a ASICs       | 47 |

| 5.3 | The comparison of the proposed 10-bit design with other column SAR ADCs.   | 57 |

# Abbreviations

| ADC   | Analog to digital converter             |

|-------|-----------------------------------------|

| CDAC  | Capacitor analog to digital converter   |

| CMOS  | Complementary metal oxide semiconductor |

| ASIC  | Application specific integrated circuit |

| DCC   | Differential common centroid            |

| DD    | Displacement damage                     |

| DNL   | Differential nonlinearity               |

| FPGA  | Field programmable gate array           |

| FSM   | Finite state machine                    |

| FURRY | Fast read-out interface                 |

| HEP   | High energy physics                     |

| HCPD  | Hit counting pixel detectors            |

| HVT   | High voltage threshold                  |

| INL   | Integral nonlinearity                   |

| LET   | Linear energy transfer                  |

| LED   | Light emitting diode                    |

| LVT   | Low voltage threshold                   |

| LVDS  | Low-voltage differential signaling      |

| MAPS  | Monolithic active pixel sensor          |

| MBU   | Multiple bit upset                      |

| MoM   | Metal oxide metal                       |

| MSPS  | Milion samples per second               |

| PCB   | Printed circuit board                   |

| RHDB  | Radiation hardening by design           |

| SAR   | Successive approximation register       |

| SEE   | Single event effects                    |

| SEFI  | Single event functional interrupt       |

| SEGR  | Single event gate rupture               |

| SEL  | Single event latch-up       |

|------|-----------------------------|

| SET  | Single event transient      |

| SEU  | Single event upset          |

| SPI  | Serial peripheral interface |

| SoI  | Silicon on insulator        |

| TID  | Total ionising dose         |

| TNID | Total nonionising dose      |

| ToT  | Time over threshold         |

| USB  | Universal serial bus        |

|      |                             |

-

# Introduction

Pixel detectors have been used in high energy physics experiments (HEP) for the last three decades. The first hybrid pixel detectors were developed in the 1980 at CERN. These ionizing radiation detectors composed of an array of diodes and adjacent electronics are based on semiconductor technology. The hybrid detector forms two main elements, the semiconductor sensor and the read-out chip manufactured independently and connected by a bump-bonding process. The sensor part is principally made of doped silicon or cadmium-telluride. The read-out chip, also segmented to pixels, contains electronics to process an incoming electrical signal from the sensor. The advantage of the hybrid concept is in the use of an arbitrary sensor. The disadvantage is a higher cost and complexity.

Nowadays, semiconductor technologies offer ways to integrate the sensor part with high voltage reversely biased diodes and read-out electronics on the same substrate. These detectors are called monolithic active pixel sensors (MAPS). This approach has several advantages compared to the hybrid sensors: missing problems with bump bonding resulting in lower cost, the pixel can shrink with used technology maintaining functionality, low power consumption and low number of input/output pins.

The pixel detector technology was initially invented for experiments in the field of highenergy physics in CERN. However, this technology has extended to many commercial activities in widely differing application areas with ongoing development.

In medical applications, especially radiotherapy and CT scans, pixel detectors are used to measure X-ray in single-photon counting mode. The CT scan field trend is to visualize full-color images with a high resolution and provide a fast read-out interface.

Another application where a pixel detector takes its place is a chemical, physical and structural analysis of a material. It helps better understand a variety of materials, from proteins, polymers to metals and building materials.

Space dosimetry experiments use pixel detectors for radiation monitoring, particle tracking, and recognition. These detectors must be able to work in extreme radiative environments. In this application are often the sensors integrated with an ADC to sample the incoming signal information. Data are then sent and analyzed on Earth. It allows researchers to study the radiation environment in space.

Typically, a MAPS detector consists of a pixel matrix and readout electronics on the same substrate. The pixel matrix has some rows and some columns. Analog signals from pixels are digitized row by row using ADCs placed under each column. Such ADC is called column ADC. This thesis proposes a new fully differential column SAR ADC architecture for Spacepix-2 MAPS detector in 8-bit and 10-bit versions in 180 nm SoI CMOS technology. Spacepix-2 has pixel pitch of 60 µm. The problem is that the pixel pitch limits the width of the ADC layout. Internal capacitive DAC layout in SAR ADC is significantly complicated. This thesis provides the new solution where a single ADC digitizes signals from two columns doubling the layout width to 120 µm. This approach permits to use of fully differential SAR ADC architecture that improves linearity, speed and decreases the noise of ADC.

## Motivation

A current converted to a voltage is generated when a particle hits the sensor in a pixel. Two ways exist how to process this voltage signal. The first is the time over threshold method (ToT), where the deposited energy of the particle in a sensor is proportional to the time when the voltage is over the threshold. The second is the ADC method, where the peak voltage signal of deposited energy of a particle left in a sensor is measured. These principles are explained in the first chapter 1. The ADC method provides more information about radiation environment than the ToT method. The disadvantage of the ADC method is in more complexity. The primary motivation is to design low power, fast enough, and linear ADC with a moderate resolution for MAPS pixel detector dedicated for space applications. MAPS detector combining sensor, ADC, and fast digital readout allows a user to study radiation environment in space, creating opportunities for interesting scientific experiments in space missions. Regardless of the space missions, this concept may also be helpful in other applications like CT scans, radiotherapy, and structural analysis of a material. A differential SAR ADC architecture provides several benefits compared to a single-ended design. However, the differential architecture needs two CDAC causing the problem to implement only in 60 µm width. Another challenge is to use a minimum unit capacitance in CDAC and reach proper linearity. The secondary motivation is to successfully solve these design challenges.

## Aims of the Thesis

Aims of the thesis are following:

- 1. Design fully differential column-parallel SAR ADC (8-bit and 10-bit) for a monolithic pixel detector in 180 nm SoI CMOS technology.

- 2. Reach conversion speed at least 2 MSps.

- 3. Use a low power asynchronous architecture.

- 4. Decrease capacitive DAC capacitance to minimum.

- 5. Provide a high input impedance.

- 6. Convert single-ended signal from a pixel to fully-differential signal at the ADC inputs.

#### Structure of the Thesis

Chapter 1 provides necessary theoretical background for better understanding the rest of the thesis. It addresses the difference between hybrid and MAPS detectors, the importance of the ADC measurement in HEP experiments, primary SAR ADC working principle, comparison ADC architectures, problem statement, design parameters, and state of the art (related work).

The following two chapters 2 and 3 describe the new proposed design of column SAR ADC for Spacepix MAPS detector in 8-bit and 10-bit versions. Designing the 8-bit version is more accessible because there are lower requirements for the comparator design and CDAC layout design. For this reason, the 8-bit column SAR ADC is designed first, and then the same architecture is extended by two more bits to the 10-bit version.

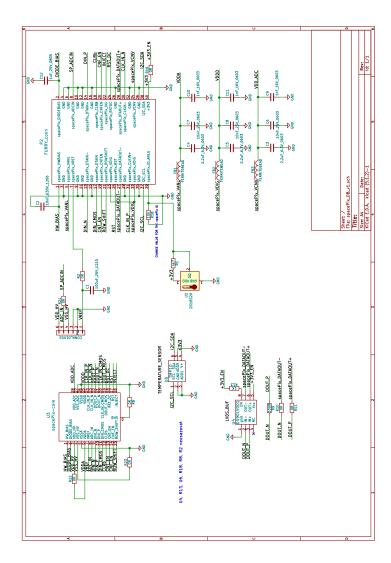

Chapter 4 describes the necessary electronics, measurements methods, design of PCBs, and software tools for data transfer and processing from Spacepix-2 MAPS detector ASIC.

Chapter 5 shows measured ADC characteristics, integral and differential non-linearities, power consumption, sampling rate and compares the proposed solution with another existing column ADCs. This chapter also shows measuring spectra with the implemented Spacepix-2 MAPS ASIC.

# Chapter 1 Theoretical Background

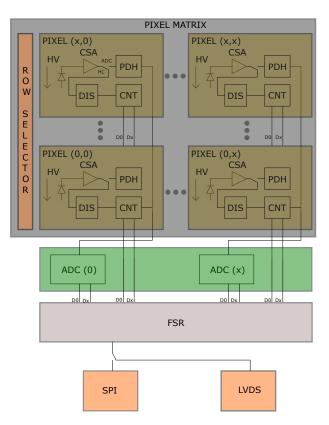

A simplified block diagram of the Spacepix MAPS detector ASIC is illustrated in Fig. 1.1. Each pixel contains the sensor diode reversely biased by a high voltage (HV) in a magnitude of 100-150 V. A particle hitting the sensor generates a current pulse converted to voltage pulse by a charge summing amplifier (CSA). Then the signal is connected to peak detector hold (PDH) if the detector works in ADC mode or to discriminator (DIS), assuming that the sensor operates in counting mode (HC).

In the hit counting mode, the CSA output voltage goes up when a particle hits the sensor. If this peak voltage value is over a certain (adjustable) threshold, the counter (CNT) starts counting. Data are then stored in the fast shift register (FSR) and finally read out digitally using SPI or LVDS. The hit counting mode is primarily dedicated to soft X-ray radiation imaging.

In the ADC mode, the CSA output voltage goes up to the maximum value proportional to the energy left by the detected particle in the detector. Peak detector hold (PDH) holds the maximum peak voltage value. This value is sampled by the ADC and stored in the FSR. All ADCs are placed under each column. For this reason, it is called column ADC. Sensor peak voltage signals are sampled row by row, and data are read-out digitally in the same way as in the hit counting mode. The ADC mode provides information about the energy of particles useful for dosimetry applications.

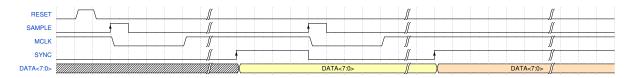

Spacepix-2 ASIC is controlled external signals that allow the user to perform row shifting, reset, load configuration, test individual blocks, and read data from the detector.

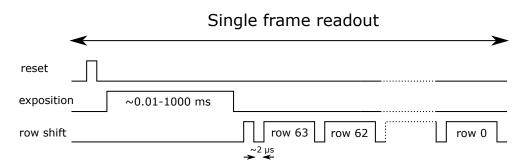

Fig.1.2 illustrates a frame detector readout of the Spacepix MAPS detector. At the beginning of the frame, the reset signal occurs to set the detector to its initial state - the reset pulse width of around 200 ns. Then the exposition time takes place, getting the sensor diodes on. A particle hitting the sensor creates voltage proportional to energy left by the detected particle in the detector at the PDH output (ADC input). After the exposition time, the first rising edge of the row shift signal selects row 63. At the falling of the row shift signal is PDH voltage output of pixels from row 63 sampled. Sampling takes some time, and then the data are stored in the shift register. The second row shift rising edge selects row 62, and row 63 data are sent out from the detector. Single row readout time depends on the readout frequency. At 50 MHz it is 20.48 µs. At the second falling edge of the row

Figure 1.1: The principal illustration of a MAPS detector ASIC.

shift signal are sampled voltages of pixels in row 62. The readout continues in the same manner up to row 0. The time for sampling should be as short as possible to cut the readout time to a minimum. However, concerning the time duration of the other signals is one µs reasonable compromise.

Figure 1.2: The timing diagram of the Spacepix MAPS detector readout.

| ADC architecture | Power consumption | Speed     | Area     | Resolution |

|------------------|-------------------|-----------|----------|------------|

| Sigma-delta      | low               | low       | low      | very high  |

| SAR              | very low          | high      | moderate | moderate   |

| Flash            | high              | very high | large    | low        |

| Integrating      | low               | low       | low      | low        |

| Pipeline         | high              | very high | moderate | high       |

Table 1.1: The comparison of existing ADC architectures.

## 1.1 Choice of the ADC Architecture

The first step to the realization of sampling in the proposed Spacepix architecture is to answer question where to place the ADC. One option is to place ADC in the pixel. However, this choice has two disadvantages. The first is the limited pixel size of  $60 \times 60 \ \mu\text{m}^2$  used in Spacepix-2 ASIC. The second disadvantage is increased power consumption. A better way to place the ADCs is under columns and sample signals from pixel row by row. This approach is called column-parallel sampling. It reduces power consumption and the layout constraints only in width, not in length.

The second step in column-parallel ADC design is choosing the most suitable ADC architecture. This choice is the crucial step as it determines the complexity and performance of the entire solution. Three basic requirements for column-parallel ADC for MAPS detector are low power consumption, moderate resolution (8-10 bits), moderate layout area, and high speed. The following table 1.1 compares the existing ADC architectures.

According to table 1.1 is the most suitable SAR ADC architecture. It provides low power consumption, sampling rates up to 5 MSPS, moderate layout area, and sufficient resolution. Sigma-delta and integrating converters are slow for the given application. The flash converter has high power consumption and low resolution. The pipeline ADC also has higher power consumption in comparison with SAR ADC architecture.

## **1.2 SAR ADC Architecture**

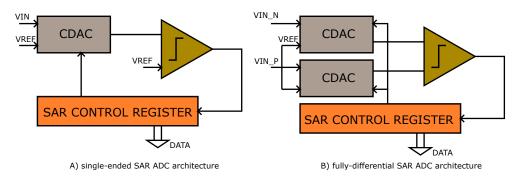

Fig. 1.3 illustrates a simplified SAR ADC block schematic. The ADC circuit consists of a digital to analog converter (DAC), comparator, and SAR control register. Transistors or resistors can be used for the CDAC realization. However, to maintain a low power consumption is the DAC preferably implemented using capacitors, called CDAC. Such SAR architecture is called SAR ADC with charge redistribution because the charge stored in CDAC capacitors is redistributed between capacitors within an approximation cycle resulting in an effective low power ADC design.

In Fig. 1.3A is shown a single-ended architecture with one of the comparator inputs connected to a reference voltage. When the sampling period occurs, the top plates of all capacitors in CDAC are switched to the ground, and the bottom capacitor plates are connected to the input voltage. The control SAR algorithm then switches the MSB ca-

Figure 1.3: The SAR ADC block diagram.

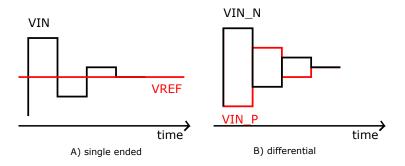

pacitor to the reference voltage. According to the comparison result, the output leaves MSB changed to the reference voltage or the ground. The algorithm continues in the same manner up to LSB. A three-bit example single-ended approximation cycle is illustrated in Fig 1.4A. The one of problems of the single ended architecture is that any voltage noise presented at the reference voltage higher in peak value than 1 LSB affects accuracy of ADC. A power supply fluctuations also deteriorate a proper ADC operation. The preferred choice is to use the fully differential architecture that effectively suppress these difficulties.

Figure 1.4: The single-ended and differential successive approximation cycle.

The fully differential architecture, principally illustrated in Fig. 1.3B, employs the same control algorithm with the difference that the input voltage is connected differentially to two CDACs and capacitors in both CDACs are switched inversely. This architecture has benefits in higher noise immunity and low process variability. Another advantage is the two times larger voltage magnitude of LSB. The comparator design of the fully differential architecture is more relaxed because charge injection does not affect ADC performance. It allows the designer to use low power dynamic comparator architecture. On the other hand, fully differential design takes over more layout areas. Fig. 1.4B illustrates the differential approximation cycle.

### **1.3** Problem Statement

The purpose of this thesis is to design SAR column ADC for the Spacepix MAPS detector ASIC. The differential SAR ADC architecture, briefly described in section 1.2, provides essential ADC performance benefits. Therefore, the task is to design a fully-differential SAR column ADC.

The first problem in designing such architecture is to convert a single-ended signal from the sensor to a fully differential signal at the ADC inputs. The column ADC thus must contain a single-ended to differential voltage converter. Such converter has to be fast enough to accomplish a fast sampling rate (at least 2 MSPS) parameter. The power consumption of the converter has to be as low as possible to maintain low power operation. A compromise between speed and power consumption has to be made.

In the case of the proposed MAPS detector is the pixel width 60  $\mu$ m. Therefore, ADC layout width is limited to 60  $\mu$ m. The major problem is to design fully differential column SAR ADC with 60  $\mu$ m width and maintain speed, linearity, and low power consumption. This problem is illustrated in Fig. 1.5.

Figure 1.5: An illustration of the major problem solved in this thesis.

The largest area in the SAR ADC with charge redistribution takes the CDAC layout. The CDAC can be realized using a split capacitor method or binary scaling method [2]. The binary-weighted DAC architecture is preferable because it provides better linearity with a smaller unit capacitor. The 8-bit version contains 256 unit capacitors. The 10-bit version contains unit 1024 capacitors. Therefore, the unit capacitor has to be as small as possible to shrink the area. Capacitance has to be also as low as possible to reduce power. The combination of the small unit capacitors and parasitic capacitances between them and substrate complicates the CDAC design. Furthermore, the pixel with is the limit. For fully differential architecture are needed two CDACs. Moreover, the comparator layout has to

| Design Parameter  | Value                 | Units |

|-------------------|-----------------------|-------|

| ADC architecture  | SAR ADC with          |       |

|                   | charge redistribution |       |

| Number of bits    | 8-10                  |       |

| Power consumption | <300                  | μW    |

| Speed             | 2                     | MSPS  |

| Layout width      | 60                    | μm    |

| Layout length     | 1000                  | μm    |

Table 1.2: The design parameters.

be perfectly symmetrical in the differential architecture. These problems solve this thesis. The table 1.2 summarize the column ADC design parameters.

#### 1.4 Related Work

From a historical perspective, the first 11-bit, 20 kSps vacuum tube successive approximation ADC was patented in 1963 [3]. The internal DAC represents the first known use of equal currents switched into an R/2R resistor ladder. The first CMOS SAR ADC was published in 1975 [4]. Internal DAC is implemented as capacitive DAC (CDAC) containing the sample and hold circuit. Comparator reference is ground, and a slightly different approximation algorithm is used. An input signal is sampled to the entire DAC capacitance and efficiently re-used. This technique is today known as charge redistribution, making SAR ADC popular in low power applications.

In table 1.3 is shown comparison of properties between McGreary [4] and original SAR ADC method. Green table fields are preferred properties defining SAR ADC development from the past to the present. Below is the list of preferred properties:

- 1. Avoid needs for resenting; it wastes energy.

- 2. DAC voltage should be able to go up and down.

- 3. Common mode level comparison at the mid-scale.

- 4. DAC should not go outside from supplies.

- 5. Top plate sampling

A differential DAC solves the first and the fourth problems since DAC voltage can go up and down easily and cannot go outside from the supplies. In the original differential SAR ADC architecture [5] are, during the sampling phase, all capacitors connected between ground (top plate) and input voltage (bottom plate). However, the input voltage can be sampled at the top plate, and the bottom plates are grounded as well [6]. The top

| Method   | $V_{IN}$ shift | Comparison        | CM-level | $V_{DAC}$ out of range | $V_{DAC}$ | Overshoot   |

|----------|----------------|-------------------|----------|------------------------|-----------|-------------|

| Original | No             | $V_{DAC}$ to hold | Variable | No                     | Up/Down   | No problem  |

| McGreary | Yes            | $V_{DAC}$ to 0    | Fixed    | Yes (negative)         | Down      | Needs reset |

Table 1.3: The comparison of original and McGreary SAR ADC properties

plate sampling uses inverters at the bottom plates of capacitors that are switched between ground and a voltage reference.

In the original differential SAR ADC architecture goes common-mode too low, making the comparator design difficult. This problem is solved by switching MSB to ground and other bits to reference voltage during the top plate sampling [1]. Then the approximation algorithm always converges toward reference voltage mid-scale. It simplifies the comparator design.

Liu et al. [6] first presented a customized Metal-oxide-Metal (MoM) capacitor for CDAC that they called a cage capacitor with capacitance 4.5fF. A similar CDAC design is used in the proposed 8-bit SAR ADC in chapter 2. Harpe et al. [1] propose an even smaller value of the unit capacitor in CDAC, only 0.5 fF and effective CDAC layout. This approach is used for the proposed 10-bit SAR ADC in chapter 3.

Besides the column-parallel sampling approach exists another ways of signal digitization used in FE-14 [7], [8], or Timepix [9] chips. However, these pixel detectors do not measure the signal amplitude by an ADC but rather use the Time over Threshold (ToT) method for charge digitization in each pixel. ToT relies on a small current discharging a chargesensitive amplifier with a constant rate. It isn't easy to keep the discharge current uniform and stable across the pixel matrix. Therefore, the ADC approach has been chosen for Spacepix detectors.

SAR ADC with charge redistribution in SoI processes was published by Culurciello et al. [10], and Dasgupta et al. [11]. However, these designs are not column-ADC's and consume a lot of power, not suitable for space applications. One of the first attempts to implement a column SAR ADC with charge redistribution is the XCHIP03 chip [12], [13]. The XCHIP03 design used a single-ended 10-bit SAR ADC.

# Chapter 2 8-bit Column SAR ADC

This chapter describes the 8-bit version of column-parallel SAR ADC[A.1] design used in the SpacePix-1 MAPS detector [14].

# 2.1 Proposed 8-bit column ADC architecture

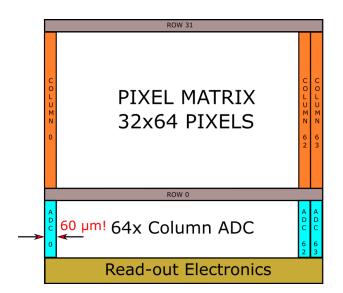

The proposed asynchronous column SAR ADC is used in the Spacepix-1 MAPS detector. The size of the pixel matrix is 32 rows and 64 columns. The novelty of the proposed solution, published in 2020 [A.1], is that a single ADC converts signals from two columns, odd and even. Data from the ADC are moved to the row shift register (RSR) and then read out serially from the chip with a fast digital interface. An illustration of the Spacepix-1 pixel detector is depicted in Fig. 2.1.

Figure 2.1: The Spacepix-1 MAPS detector illustration.

Figure 2.2: The proposed column ADC architecture.

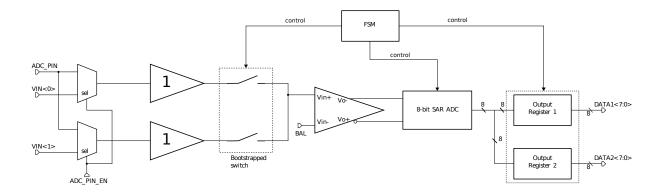

A simplified block diagram of the proposed 8-bit column ADC is shown in Fig. 2.2. Input signals from odd and even columns are connected to VIN<0> and VIN<1>. These inputs are fed through the input demultiplexers where the signal ADC\_PIN\_EN selects VIN<1:0> or the external pin ADC\_PIN. This external pin serves for testing purposes. The input buffers are used to increase the input impedance of column ADC. In the proposed design, the buffer was realized by a standard two-stage operational transconductance amplifier (OTA) with input capacitance 220 fF.

Two bootstrap switches [15] serve as a multiplexer controlled by the finite state machine (FSM). The output from the bootstrap switches is connected to the ADC driver. The FSM selects one of the inputs. The bootstrap switch design is used in order to maintain good linearity resulting in low distortion. The bootstrap switch is described in Section 2.1.1.

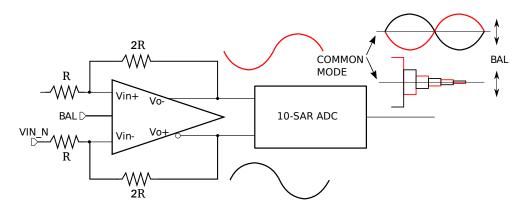

The ADC driver is a fully differential amplifier that drives the differential SAR ADC inputs. The main task of this block is to convert a single-ended signal to a differential signal with a fast settling time. The BAL signal sets the common mode. The ADC driver is described in detail in Section 2.1.2.

The 8-bit asynchronous SAR ADC with charge redistribution is described in Section 2.1.3. The output data from the ADC are latched into one of the output registers. The SAR ADC and output registers are also controlled by the FSM.

The FSM was implemented by standard digital cells and is described in Section 2.1.4. The FSM turns on the bootstrap switch at input VIN $\langle 0 \rangle$  in the initial state. A conversion cycle is initiated at the falling edge of an external that perform row shifting, principally illustrated in Fig. 1.2. An analog value of the signal VIN $\langle 0 \rangle$  is digitized and latched to the output register 1. Immediately after conversion VIN $\langle 0 \rangle$ , the FSM switches off VIN $\langle 0 \rangle$  and turns on VIN $\langle 1 \rangle$ , waits some time to settle the ADC driver output and initiate the second conversion. After the second conversion, is data latched into the output register 2. The individual circuits are described in the following subsections.

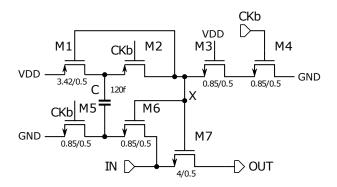

#### 2.1.1 Bootstrapped switch

CMOS switches suffer from several imperfections that can be alleviated by bootstrapping. A single transistor switch suffers from a limited input range as input voltage approaches to  $V_{DD}$  -  $V_{TH}$ . It can be alleviated by a complementary switch topology where NMOS and PMOS transistors provide the whole input voltage range. However,  $R_{ON}$  resistance of the complementary structure varies with  $V_{IN}$  distorting the signal. The bootstrapped switch preserves  $R_{ON}$  constant as the voltage at the node X varies according to  $V_{IN}$ , it improves linearity.

The bootstrapped switch uses a standard circuit [15]. The modified design is shown in Fig. 2.3. The used technology, 180nm silicon on insulator (SoI) process, provides NMOS and PMOS transistors with break down voltage of 1.98 V and 5 V. The node X in Fig. 2.3 reaches a voltage level of up to 2.8 V. Therefore, there are used transistors with thicker gate oxides with a breakdown voltage of up to 5V.

Figure 2.3: The bootstrapped switch.

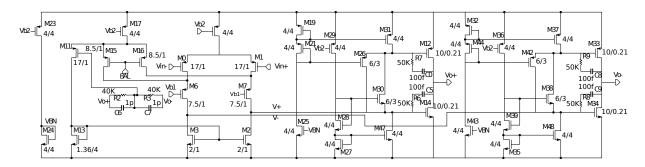

#### 2.1.2 ADC Driver

The proposed fully differential operation amplifier in Fig. 2.4 [16], drives fully differential SAR ADC inputs. The input stage forms the PMOS transistors M0, M1, cascodes M6, M7, current source M8 and current mirrors M2, M3 stabilized by a common-mode feedback. The common-mode feedback is composed of transistors M15, M16, M11, M13, which set a common mode level and the resistors R2, R3, capacitors C6, C7 senses the output voltage and cancel out differential signals. The transistors M12, M13, M26, and M30 are class AB output stage at output Vo+. Vo- is identical to Vo+. Resistors R7, R6, R8, R9 and capacitors C0, C5, C8, C9 form a frequency compensation. The remaining transistors are for biasing purposes. The advantage of this circuit is a large output swing of the class AB stage, fast settling time, and low output impedance. Using a fully differential amplifier with common-mode feedback for single-ended to differential signal conversion also has the advantage of small sensitivity to process variations.

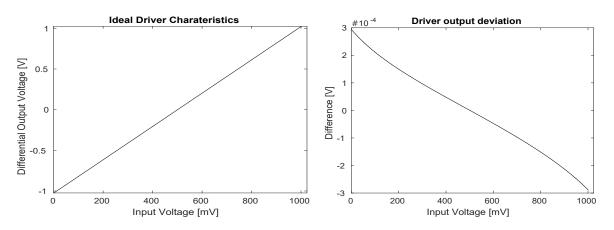

Voltage Vb1 is connected to the ground. The BAL voltage sets the common mode. The output voltage versus input voltage of the ideal characteristic is depicted in Fig. 2.5

Figure 2.4: The proposed ADC driver.

on the left. Note that the output voltage is equal to -1.024 V for the zero input voltage and +1.024 V for the maximum reference input voltage, which is also 1.024 V. Driver output deviation from ideal characteristic shows Fig. 2.5 on the right. The maximum deviation is 300 µW or 0.3 LSB. The Output settling time is less than 100 ns. Power consumption is 160 µW from 1.8 V power supply. The layout area is  $50 \times 115$  µm<sup>2</sup>.

Figure 2.5: The input and output voltage characteristics of the proposed ADC driver.

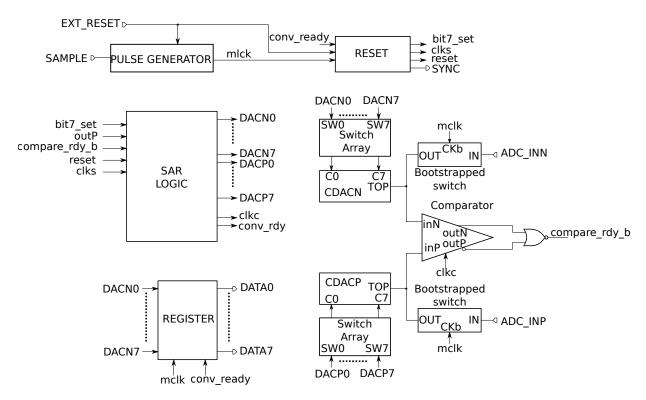

#### 2.1.3 8-bit SAR ADC

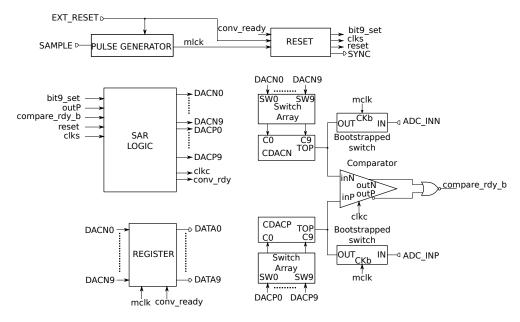

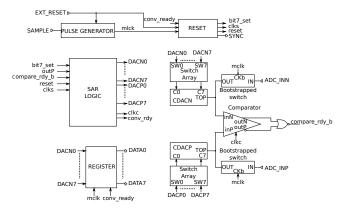

A block diagram of the proposed asynchronous 8-bit SAR ADC [A.2] is depicted in Fig. 2.6. Input or output pins are signed in capital letters and internal nets in italics. The primary switching principle, SAR logic, and comparator are identical with Harpe et al. design [1]. The switched capacitor DAC (CDAC) is different, explained below. A new pulse generator is added to generate the *mclk* signal at the falling edge of the SAMPLE signal. The *mclk* signal is used to sample the input analog voltage to CDACs through bootstrapped switches. A new reset circuit is added to generate a SYNC signal that is needed for the asynchronous AD conversion of signals from the left and the right column. The individual blocks different in comparison with [1] are explained below.

Figure 2.6: The 8-bit SAR ADC block diagram.

Figure 2.7: The SAR ADC Timing diagram (not to scale).

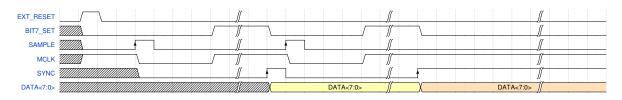

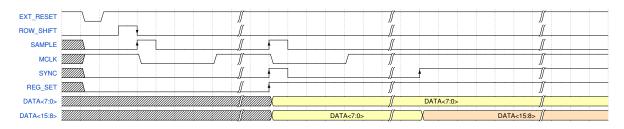

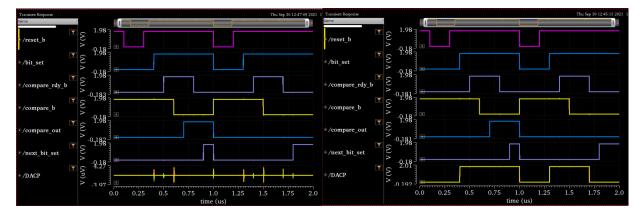

The asynchronous operation is depicted in Fig. 2.7. Before a conversion cycle takes place, the RESET signal goes high to set asynchronous logic to its low initial state. The ADC converter is in standby mode after reset. Another reset signal is generated internally by the signal  $conv_rdy$  when a conversion cycle has been completed. The converter goes on standby mode after every conversion. The pulse generator is a monostable circuit that generates a pulse mclk at the rising edge of the signal SAMPLE. An input differential signal is sampled to the CDACs when mclk is low. The SAR logic begins successive approximation when the mclk goes high. The SYNC signal goes high when the ADC finishes a conversion cycle. DATA are latched into the output register at the rising edge of SYNC. The SYNC signal goes low when the next conversion is required by the SAMPLE signal.

#### 2.1.3.1 Capacitive DAC

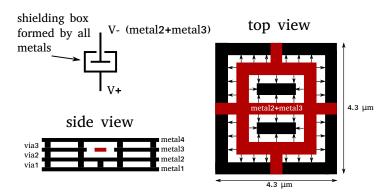

The Proposed switched capacitor DAC contains 256 customized MoM capacitors. Each unit capacitor has the dimensions  $4.24 \times 4.24 \ \mu\text{m}^2$ , with capacitance of  $4.5 \ \text{fF}$  [A.3]. Details of the unit capacitor is shown in Fig. 2.8. The metal 3 forms one pole and metals 1 or 4, the second pole of the capacitor. All metals including vias, except for gaps for the metal 3 pole, form a box structure that highly decreases parasitic capacitances. The CDAC layout area is 195x57.5  $\mu\text{m}^2$ , overall capacitance of switched capacitor DAC is 1.174 pF.

Figure 2.8: The proposed MoM capacitor.

#### 2.1.3.2 Asynchronous Dynamic SAR Logic

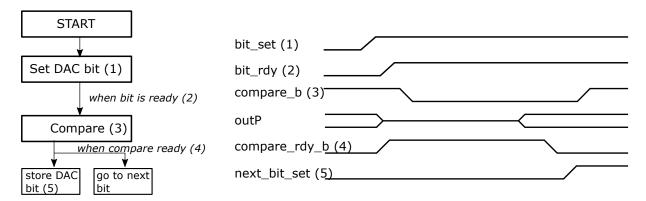

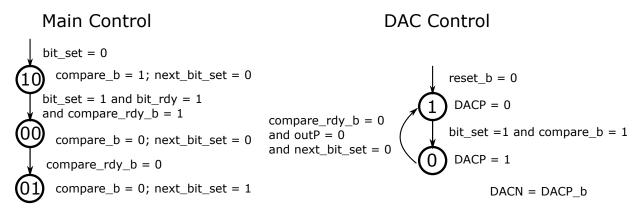

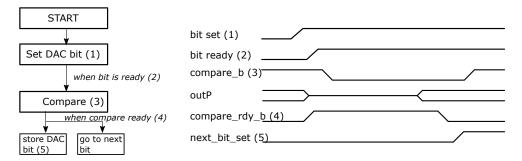

This asynchronous logic architecture is based on Harpe et al. [1] design. The proposed algorithm of the SAR ADC asynchronous controller performs a binary search algorithm in eight identical cycles. Fig. 2.9 shows state and timing diagram pro the single SAR bit. To achieve consecutive asynchronous operation, self-synchronization is used. Before each transition, a specific condition is checked to ensure that the previous step is finished before starting the next. First, the bit is set (1). When the bit is ready (2), the comparison is initiated (3). After some time the comparator is valid, which indicates by ready signal (4). Then, the next bit is initiated (5). The value of the bit decision is stored in the SAR register.

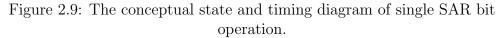

To implement logic in Fig. 2.9 is the operation split into two parts illustrated in Fig. 2.10. The main control starts in state 10. When the bit is set, the state changes to 00 where *compare\_b* requests comparison. The condition *compare\_rdy\_b* test if the comparator is ready. Then the state changes to 01 to hand over the next bit iteration by enabling *next\_bit\_set*. The DAC control starts in state 1 where the DAC bit is turned off. When the *bit\_set* is requested and the comparator result and conditions *next\_bit\_set* and *compare\_rdy\_b*, the state changes back to 1 or remains in the state 0.

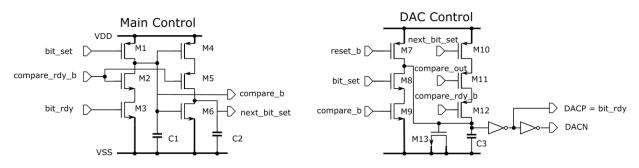

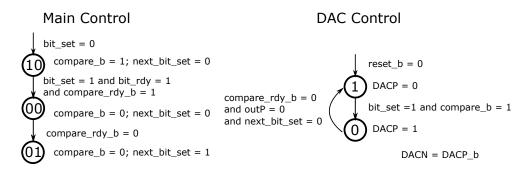

Different approaches can realize both state machines in Fig. 2.10. Interesting realization by Harpe et al. [1] illustrates Fig. 2.11. This is effective and low-power solution.

Figure 2.10: The state diagram of the main control and the DAC control.

On the other hand, this realization is problematic in the MAPS detector application because the reset signal sets capacitors C1, C2, and C3 at the beginning of the frame readout. Sampling takes place right after the acquisition time. C1, C2, and C3 are based on parasitic capacitances verified by simulation. As the detector's acquisition time is variable in time, it is complex to set these capacitances properly. Therefore, the realization in Fig. 2.11 is not guaranteeing the reset state of the state machines because the sampling does not occur immediately after the reset, and a leakage current influences parasitic capacitances.

Another more robust approach to realize the main control and the DAC control is with standard cells in the used technology. This realization is shown in Fig. 2.12. The benefit is the stability of signal states after reset with no dependency on time. This implementation is more robust for the target application.

The modular asynchronous logic concept is illustrated in Fig. 2.13. The signal mclk initiates the 10-bit conversion. Each module generates clock pulses (clkc) for the comparator through OR gates. The comparison is allowed by  $compare\_rdy\_b$  signal from the comparator. The  $compare\_rdy\_b$  generates a NOR gate connected at the differential comparator output (not illustrated). The result of a comparison, the signal outP, is sampled in each bit. When a conversion cycle is finished, the  $conv\_rdy$  signal latches data in the

Figure 2.11: The realization of state machine by Harpe et al.

Figure 2.12: The DAC control realization using standard cells.

clkc mclk COMPARATOR conv\_rdy 6 5 0 main contro compare\_rdy\_b DAC bit bit bit bit bit control outP 8-BIT OUTPUT REGISTER

Figure 2.13: The simplified block diagram of the asynchronous SAR logic.

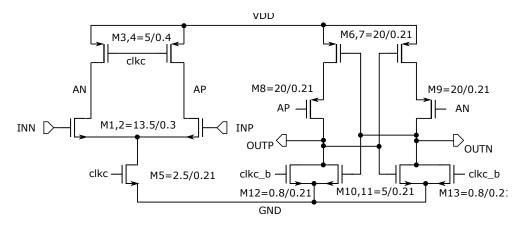

#### 2.1.3.3 Dynamic comparator

10-bit register.

The design of the comparator also uses Harpe et al. [1] architecture. A combination of low threshold (LVT) and high threshold (HVT) transistors is used. In each current branch is at least one HVT transistor used to avoid leakage current. The difference of the proposed comparator design is only in the transistors sizing as illustrated in Fig. 2.14.

The simulated offset of the comparator reaches almost 30 mV. However, in the differential architecture, the comparator offset causes only the ADC transfer function offset and has no impact on ADC linearities. The noise of the comparator is simulated using

Figure 2.14: The dynamic comparator design.

| Differential voltage $[\mu V]$ | Wrong decisions |

|--------------------------------|-----------------|

| 100                            | 64              |

| 200                            | 45              |

| 300                            | 35              |

| 400                            | 21              |

| 500                            | 12              |

| 600                            | 7               |

| 700                            | 6               |

| 800                            | 4               |

| 900                            | 2               |

| 1000                           | 1               |

Table 2.1: The simulated transient noise of the comparator.

transient noise analysis. The differential input voltage is swept from hundred microvolts up to tens of millivolts. In each step, some wrong decisions occur. The bad decisions are counted. The total number of decisions in each voltage level is one hundred. The number of wrong decisions at a particular voltage level shows Tab. 2.1.

The comparator noise can be calculated using the following formula 2.1 [17],

$$V_{n_{RMS}} = \sqrt{k_1 v_1^2 + k_2 v_2^2 \dots + k_n v_n^2}$$

(2.1)

where  $v_m$  is differential DC voltage at which  $k_m$  wrong decisions occur. The calculated comparator noise is 475 µV. That is for 8-bit ADC approximately 1/8 LSB if the voltage reference is 1.024 V.

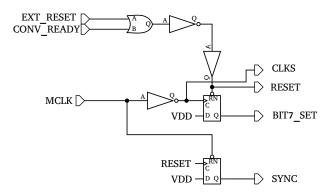

#### 2.1.3.4 Reset circuit

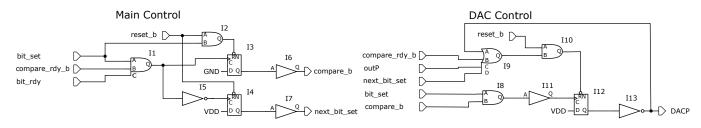

The reset circuit is an additional part of the SAR logic. The RESET signal is generated if the EXT\_RESET or  $conv\_rdy$  signal is received. This circuit also generates the signal BIT7\_SET on the *mclk* rising edge and SYNC when the conversion is finished. The signal SYNC is needed for the asynchronous double column conversion. The reset circuit is shown in Fig. 2.15 and a timing diagram in Fig. 2.16.

Figure 2.15: The reset circuit.

#### 2.1.3.5 Pulse Generator

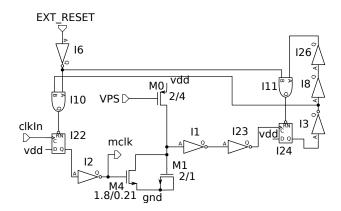

The pulse generator is a monostable circuit that generates an mclk pulse of defined length. The mclk signal is active low, used for sampling analog voltage to swithed capacitor DAC. The proposed pulse generator is illustrated in Fig. 2.17.

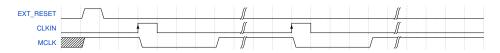

First of all, the *mclk* signal has to be initiated by EXT\_RESET. It turns on the transistor M4 to discharge MOS capacitor M1. M1 is charged by a constant current from current source M0 when the *mclk* is low at CLKIN rising edge (CLKIN is SAMPLE signal). The M0 current is adjusted by VPS voltage. I1 output goes low when the voltage at the M1 capacitor reaches a threshold voltage of the inverter. In this time, I24 Q output goes high and the short reset signal is generated by a delay line I8, I26 in order to reset I22, I24. *mclk* is low and circuit waits for next CLKIN rising edge. The timing diagram is shown in Fig. 2.18.

Figure 2.16: The reset circuit timing (not to scale).

Figure 2.17: The pulse generator.

Figure 2.18: The pulse generator timing (not to scale).

### 2.1.4 Column Control FSM

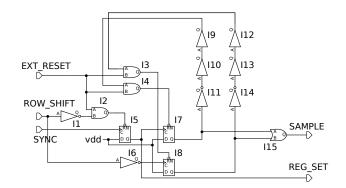

This simple finite state machine (FSM) controls AD conversion of the left and the right column. It controls the bootstrapped switches at the ADC driver input, latches output data into registers and also drives the SAMPLE signal of the SAR ADC. The circuit diagram is shown in Fig. 2.19 and the time diagram in Fig. 2.20. At first, the EXT\_RESET goes low to initiate the FSM to its state. The REG\_SET signal is low and turns on the even column connected by the bootstrapped switch. The first row of the pixel detector is selected at ROW\_SHIFT rising edge. The ROW\_SHIFT signal is held high until a voltage level is steady at the output of the input buffers. The first conversion cycle is initiated at ROW\_SHIFT falling edge by SAMPLE signal, generated by I8. The delay loop, composed of I12-I14, reset I8 when the SAMPLE signal goes low. I12 and I13 are delay buffers. The SYNC signal goes high when the first (odd column) conversion has finished. The ADC data are latched into both registers at the rising edge of SYNC and REG\_SET. At the same time, the second SAMPLE signal is generated and the second (even) bootstrapped switch is turned on (the odd bootstrapped switch is turned off) by the REG\_SET signal. At SYNC rising edge, the second (even) conversion cycle is initiated. The ADC data (even) are latched into one register by the rising edge of the SYNC when the second conversion cycle is finished. Data latched in both registers are moved to a shift register and are ready to be read out. The next conversion cycle can be initiated by ROW\_SHIFT when the data are moved into the shift register.

Figure 2.19: The FSM circuit diagram.

Figure 2.20: The FSM timing diagram (not to scale).

### 2.1.5 Layout

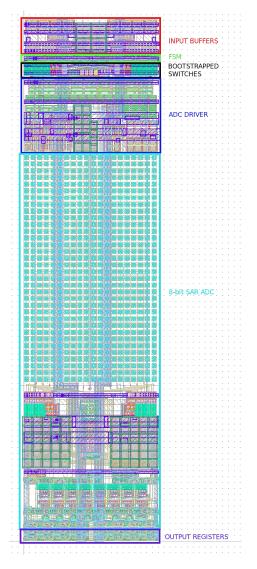

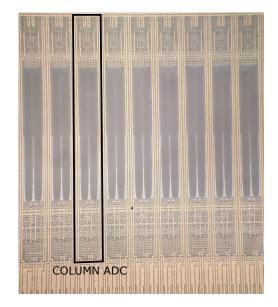

The layout is shown in Fig 2.21. A common centroid technique [A.5] is used for transistors in the comparator circuit of the SAR ADC and for transistors in the ADC driver. The common centroid technique helps to improve matching properties and eliminates analog single event transients invoked by impinging particles [18], [19]. The layout is kept as symmetrical as possible. At the bottom of the layout the output registers are placed for a simple connection of the readout circuits. A free place in the symmetrical structures are filled with decoupling capacitors. Driving signals, bias and power are connected on top of the layout by top metal in the used technology. The dimensions of the layout are  $445 \times 115 \text{ µm}^2$ . All 32 column ADCs are placed next to one another.

### 2.1.6 Bandgap Voltage Reference

The Spacepix-1 ASIC has integrated an on-chip bandgap reference with output voltage 1.024 V. In the case of 8-bit ADC is 1 LSB voltage step equals 4 mV. The bandgap voltage is decoupled by a large off-chip capacitor (10  $\mu$ F). When a conversion cycle occurs, the current charging the capacitors in CDAC is drained from the voltage reference and the associated capacitor. The bandgap's output resistance has to be low enough to supply sufficient current for all 32 ADCs without a significant voltage drop. This is verified by simulation.

Figure 2.21: The 8-bit column ADC layout.

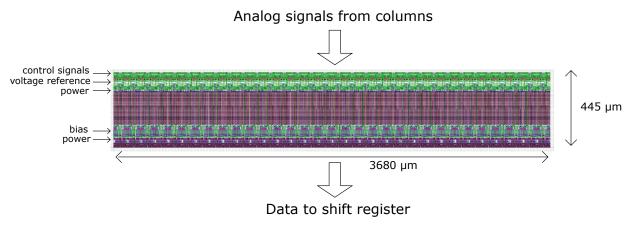

### 2.1.7 Layout of all 32 Column ADCs

This chapter so far described the design of the single 8-bit column ADC. However, placing all column ADCs one to the next brings other challenges that have to be solved. The layout design of single column ADC has to tie up the other as explained in section 2.1.5. Then is possible to place all 32 ADCs one to the following other as illustrates Fig. 2.22.

Single column ADC requires connecting power, bias signals, bandgap voltage reference, and control signals (reset and row shift) with the associated circuits in the chip. These connections realize thick top metals placed under the column ADCs leading through all 32 ADCs. Then is possible to connect signals with the related circuits in the chip from the left or the right side of the 32 ADC layout. Required metal thicknesses are calculated and verified by simulation. At the bottom, power lines at the bottom supply the SAR

Figure 2.22: The layout of 32 column ADCs.

ADCs, and power lines at the top supply the analog front-end (ADC driver, buffers, FSM). Analog signal from pixels coming for the top of the ADC input. Output data from ADCs to fast shift registers are connected from the bottom. The total layout length is 3680  $\mu$ m, and the high is 445  $\mu$ m.

# Chapter 3 10-bit Column SAR ADC

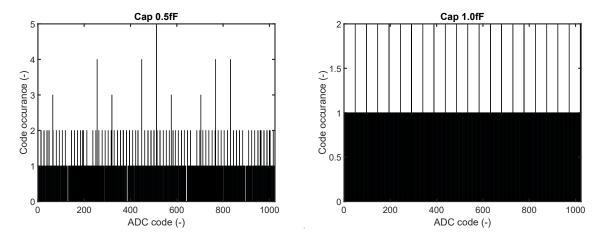

The problem to adequately design the 10-bit SAR column ADC for MAPS detector is the limited width of the layout and simultaneously to maintain the linearity of internal switched capacitor DAC (CDAC). The 8-bit SAR ADC architecture [A.1] provides doubled width of the ADC layout because the single ADC digitizes signals from two columns. This double sampling method is also used in this 10-bit version, and therefore the CDAC layout is more relaxed. However, to reduce the CDAC layout's height, the unit capacitor size in the 10-bit version has to be smaller in area because 1024 unit capacitors are needed instead of 256 capacitors in the 8-bit version. Design described in this chapter solves this problem and provides a 10-bit CDAC layout with a unit capacitor capacitance of only 0.5 fF and novel foldback architecture that reduce the layout height by half. The CDAC layout is even narrower than pixel size; therefore, it is possible to lead analog and digital pixel power supply through the ADC.

In comparison with the 8-bit version [A.1] are two more problems solved. The first is the comparator design with rescaled transistors and improved symmetrical layout. The second is the SAR logic redesign with extension by two more bits.

The chapter is organized as follows: Section 3.1 is a brief overview of the 10-bit column ADC architecture, section 3.2 describes design problems of CDAC, comparator, and SAR logic, and section 3.3 discusses layout design.

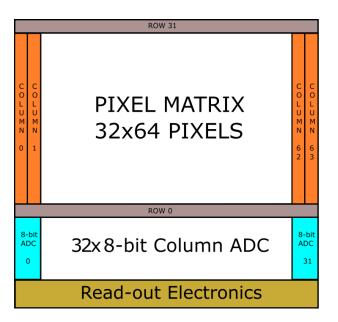

### **3.1** 10-bit column ADC architecture

The 10-bit column SAR ADC architecture, depicted in Fig. 3.1, exploits the same doublesampling method described in the 8-bit ADC version [A.1]. On the left side of the Fig. 3.1, input signals for odd and even columns are shown. The input multiplexers allow the user to connect signals from columns to ADC or an external pin for ADC testing purposes. The double sampling is initiated by a signal that performs row shifting. The input buffers provide high input resistance of the column ADC. The FSM successively controls the asynchronous AD conversion of the left and right column, and data are latched into output registers. The fully differential amplifier drives the fully differential SAR ADC inputs. The  $64 \times 64$  pixel matrix needs only 32 ADCs. This double-sampling architecture is described in detail in [A.1]. The 10-bit SAR ADC contains the following differences: Complementary metal-oxide-semiconductor (CMOS) switches instead of bootstrapped switches are used at the input of the fully differential amplifier (ADC driver); SAR logic and registers are extended by two more bits to 10-bits.

Figure 3.1: The 10-bit column ADC block diagram, the input signals on the left side going though buffers to ADC driver. FSM controls the asynchronous conversion and data are stored in the output registers.

Adjustable BAL and VIN\_N signals bring improvement compared to the 8-bit version design [A.1]. The VIN\_N signal allows the user to shift the input voltage range according to the following relation:

$$ADC_{vout} = V_{in} + (V_{IN\_N} - \frac{V_{ref}}{2}), \qquad (3.1)$$

where  $V_{in}$  is the voltage at the buffer input (VIN<0> or VIN<1>),  $V_{IN_N}$  is the adjustable voltage at the negative input of the ADC driver,  $V_{ref}$  is the ADC reference voltage and  $ADC_{vout}$  is the ADC value in volts. It is also possible to calculate ADC value in volts:

$$ADC_{vout} = \frac{V_{ref}ADC_{code}}{ADC_{maxcode}},\tag{3.2}$$

where  $ADC_{code}$  is 10-bit code of the sampled input voltage and  $ADC_{maxcode}$  is 1023 for a 10-bit ADC resolution. If the  $V_{IN_N}$  input is set to 512 mV and  $V_{ref}$  is 1.024 V, then the 10-bit binary approximation of input signal (ADC value) is equal to  $V_{in}$ . If the  $V_{IN_N}$  is set, for example, to 612 mV, then the ADC value is 100 ADC units (1 ADC unit = 1 LSB) lower then the  $V_{in}$ . The signal  $V_{IN_N}$ , if needed, is possible to make use for shifting the ADC transfer characteristic by a constant value.

The BAL signal control has also a significant benefit in this architecture. The BAL signal sets the common-mode level as depicted in Fig. 3.2. The differential input voltage shown as a sine wave is sampled to CDAC through bootstrapped switches inside of the SAR ADC (shown in Fig 3.3). Then, the approximation algorithm, also shown in Fig. 3.2, takes place.

Figure 3.2: The influence of the adjustable BAL signal on common mode.

Figure 3.3: The 10-bit SAR ADC block schematic.

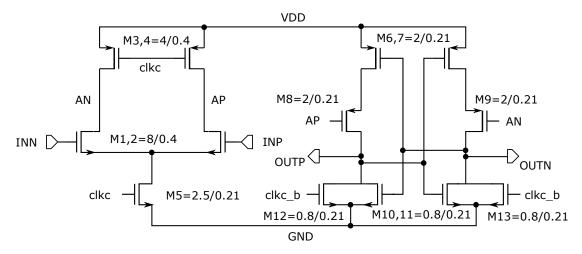

The top plates of all CDAC capacitors are connected to the input differential pair of the comparator. The approximation algorithm converges toward the common-mode that is set by the BAL signal. The comparator, shown in Fig 3.4, has a high voltage threshold (HVT) N-type metal-oxide-semiconductor (N-MOS) transistors at the differential pair input. The threshold voltage of HVT N-MOS in used technology is approximately 0.6 V.

When the comparator clock signal is at the low state, parasitic capacitances in the nodes AP and AN (shown in Fig. 3.4) are charged, and voltage at these nodes is equal to VDD. The output of the comparator resets transistors M12 and M13. When the clock goes high, M12 and M13 are switched off, AP and AN nodes start to discharge, and voltage at these nodes decreases according to the  $V_{GS}$  of M1 and M2. At the end of the successive approximation, the differences between  $V_{GS}$  of M1 and M2 are small, but the comparator has to

Figure 3.4: The 10-bit version comparator design.

decide correctly to reach the 10-bit resolution. When the BAL signal is set around the HVT N-MOS threshold voltage, the discharging of AP and AN nodes is slow, and the output latch has more time to decide correctly. On the other hand, when the BAL signal is set 200-300 mV above the HVT N-MOS threshold voltage, discharging capacitances in the AP and AN nodes is fast, and the latch may decide incorrectly. Therefore, the BAL control signal directly affects the accuracy and speed of the proposed SAR ADC architecture.

## 3.2 10-bit SAR ADC

Block schematic of the proposed 10-bit SAR ADC is illustrated in Fig. 3.3. The pulse generator, reset, and bootstrapped switches remain identical to ones in the 8-bit version [A.1]. Capacitors in CDAC are switched to the voltage reference or ground using inverters. The largest capacitor uses an inverter with N-MOS W/L ratio 8/0.21 and P-MOS W/L ratio 24/0.21. The remaining switches are scaled-down by a factor of two up to the minimum value. The register is also easily extended using two more standard D-type circuits available in the used technology. The comparator, CDAC, and modified SAR logic are described in the following subsections.

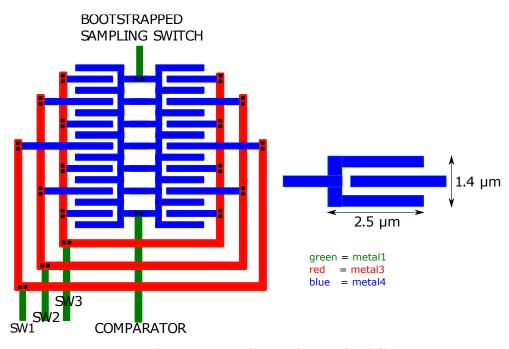

### 3.2.1 10-bit foldback CDAC

The CDAC used in the 10-bit SAR ADC is entirely different in comparison with the previous 8-bit version. The unit capacitor, shown in Fig. 3.5 right, is designed using only one metal layer with the capacitance of 0.5 fF. The 10-bit binary-weighted version has 1024 capacitors in total. The common centroid layout technique is used. A principal illustration of the CDAC structure is shown in Fig. 3.5 left.

A standard CDAC design [1] interconnects unit capacitors from one side of CDAC and the capacitors on the other side connected to the ground compensate parasitic capacitances. The proposed folded CDAC architecture interconnects unit capacitors from both sides as is shown in Fig. 3.5. This approach reduces the CDAC height by half. The node

leading from CDAC to the comparator is connected by metal 1 and capacitor interconnections by metal 3 to decrease parasitic capacitances between these sensitive nodes.

Figure 3.5: An example of 3-bit folded CDAC design.

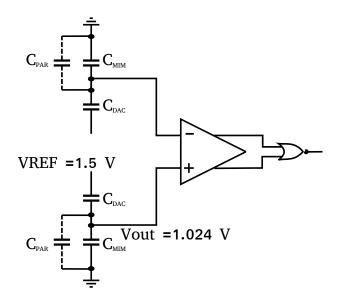

Parasitic capacitances at the top plates of capacitors in CDAC have to be compensated because CDAC's height is around 800 µm. This compensation is done by adding a Metalinsulator-Metal (MIM) capacitor to the comparator node and by increasing ADC reference voltage as illustrated in Fig. 3.6.

The capacitance of the MIM capacitor is calculated as

$$C_{MIM} = V_{REF} \frac{C_{DAC}}{V_{OUT}} - C_{DAC} - C_{PAR}, \qquad (3.3)$$

where  $V_{REF}$  is set to 1.5 V (bandgap reference voltage),  $V_{OUT}$  is the comparator input voltage,  $C_{DAC}$  is the total capacitance of CDAC equal to 512 fF, and  $C_{PAR}$  is the parasitic capacitance at the comparator input. The  $C_{PAR}$  is an unknown parameter that has to be determined by post-layout simulation. The  $C_{MIM}$  value is then easily calculated.

The second way to eliminate the parasitic capacitance at the comparator node is to leave  $C_{MIM}$  fixed and precisely adjust  $V_{REF}$  to get the linear transfer characteristic of the ADC. The capacitor mismatch was verified using Matlab software. Normalized standard deviation is calculated as

$$\frac{\sigma(C)}{C} = \frac{A_m^2}{WL},\tag{3.4}$$

where C is the nominal unit capacitance 0.5 fF,  $A_m$  is Pelgrom coefficient found in the documentation of the used technology, and WL are dimensions of the unit capacitor.

Figure 3.6: The compensation of parasitic capacitances of CDAC.

A calculated denormalized standard deviation was used for generating a set of all 1024 capacitors of both CDACs. Then the linearity was tested. Results, shown in Fig. 3.7, confirmed the ability of the capacitor design to reach desired 10-bit resolution.

#### 3.2.2 Dynamic Comparator

The comparator design is shown in Fig. 3.4. The differential pair gain is around 9, and the latch transistor sizes are properly selected by simulation. The input-referred noise, calculated according to normal distribution method [17], is estimated to be 245  $\mu$ V RMS (root mean square).

The comparator layout is shown in Fig. 3.8. Transistors are divided into odd fingers to connect dummy transistors and keep the same capacitance at the AP and AN nodes. The symmetry of the layout is essential in order to keep the same metal lengths of the critical nodes, AP, AN, and latch. The comparator output is buffered, because one of the outputs is connected to the SAR logic with a long metal with a large parasitic capacitance.

#### 3.2.3 Asynchronous SAR logic

Based on the reference [1], the asynchronous SAR logic utilizes a modular concept easily extendable from 8-bits to 10-bits. The used switching scheme is illustrated in Fig. 2.5. In the sampling phase is differential voltage connected to the capacitors top plates through switches S1 and S2. At the same time is MSB switched on VREF and other bits to the ground. The benefit of switching the MSB in the sampling phase is that successive approximation converges toward to common-mode  $V_{CM}$ . In the second step, switches are S1 and S2 off, and the comparator decides MSB bit. Then the algorithm tests individual bits

Figure 3.7: The capacitor mismatch simulation in Matlab

as illustrated in Fig. 2.5. Advantages of this low power switching scheme are convergence to common mode, no redundant switching, and simple components (inverters are used for the bottom plate switching.

The modular asynchronous logic concept is illustrated in Fig. 3.10. The signal mclk initiates the 10-bit conversion. Each module generates clock pulses (clkc) for the comparator through OR gates. The comparison is allowed by  $compare\_rdy\_b$  signal from the comparator. The  $compare\_rdy\_b$  generates a NOR gate connected at the differential comparator output (not illustrated). The result of a comparison, the signal outP, is sampled in each bit. When a conversion cycle is finished, the  $conv\_rdy$  signal latches data in the 10-bit register.

Single bit operation shows Fig. 3.11. The particular bit is set (1) with the signal  $bit\_set$ . The delay between signals  $bit\_set$  and  $bit\_rdy$  ensures voltage setting on CDAC (2). This delay has to be set by simulation. A comparison is initiated when the bit is ready with  $compare\_b$  (3). The comparator output outP is sampled when the signal  $compare\_rdy\_b$ goes low (4). The  $compare\_rdy\_b$  signalizes valid data on the comparator output. The next bit is operation is initiated by  $next\_bit\_set$  (5).

The main control and the DAC control in each of bit are simple state machines that can be specified using state diagrams shown in Fig. 3.12.

Harpe et al. [1] built DAC control and main control using few transistors and parasitic capacitances. SAR logic is initialized by a reset signal that charges the parasitic capacitances in their design. However, in the Spacepix-2 detector application, when a long period between samplings is used (a long acquisition time), these small capacitances are discharged by a leakage current that may result in an error in the SAR register. Therefore,

Figure 3.8: The layout of the comparator.

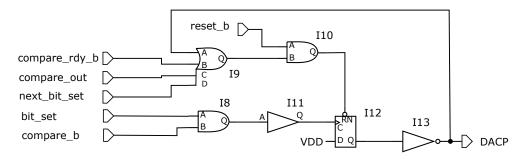

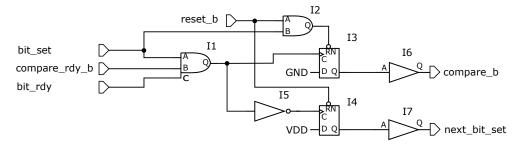

the DAC control in Fig. 3.13 and the main control in Fig. 3.14 are redesigned using standard cells in the used 180 nm SoI technology. The delay cells I6, I7 in the main control, and I11 in the DAC control are validated by a simulation to ensure the proper operation and settling time of CDAC switches.

### 3.3 Layout

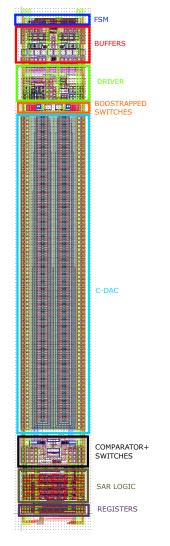

Individual column SAR ADCs are placed one next to the other. The total length of the layout is 923 µm and the width is 120 µm (2 × pixel size). The new column 10-bit ADC layout is shown in Fig. 3.15. On the top, analog front-end is placed consisting of the ADC driver, input buffers, CMOS switches and asynchronous FSM that drives successive conversion of the left and right columns. Two CDACs are in the middle of the layout. Above the CDACs, the sampling bootstrapped switches are placed to decrease the parasitic sensitive node length to a minimum. The bootstrapped switches connect the input voltage on the top of both CDAC's as illustrated in Fig. 3.5. Under the CDAC is placed the comparator and inverters for CDAC capacitors switching. The SAR logic and output registers are at the bottom.

Figure 3.9: The used switching scheme.

Figure 3.10: The simplified block diagram of the asynchronous 10-bit SAR logic.

Figure 3.11: The timing diagram of single SAR logic bit (not to scale) [1].

Figure 3.12: The main control and DAC control finite state diagrams [1].

Figure 3.13: The DAC control

Figure 3.14: The main control

Figure 3.15: The 10-bit column ADC layout

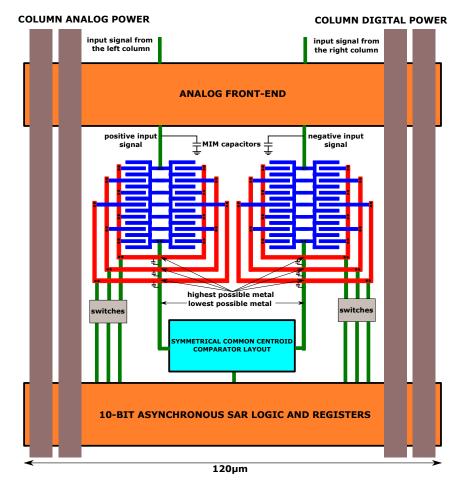

A detailed illustration of the layout is shown in Fig. 3.16. On the top, the inputs from the left and the right columns are connected to the analog front-end (buffers, ADC driver and FSM). Then, the differential input signal is switched to CDAC through bootstrapped switches when sampling occurs. On the top of CDAC, the MIM capacitors are used for CDAC parasitic capacitance compensation as explained in Fig. 3.6. The bottom of the capacitor top plates is connected to the comparator by the lowest possible metal. The highest metal makes the interconnection between unit capacitors in order to reduce parasitic capacitances in these critical metals crossings. Along the left and right side, power lines for digital and analog column power supply are lead without an interruption of ADC performance.

Figure 3.16: The 10-bit column ADC layout in detail.

## Chapter 4

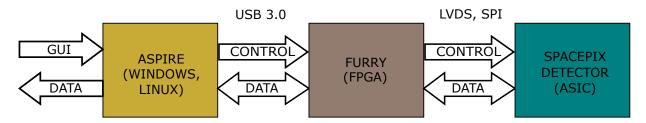

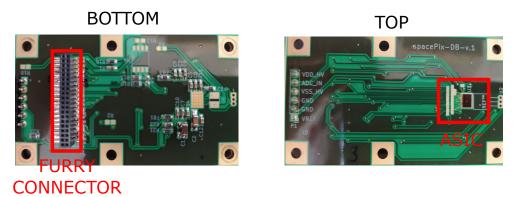

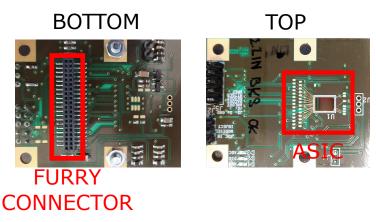

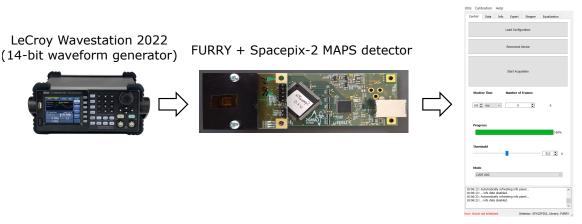

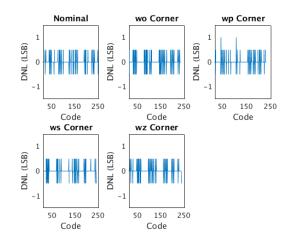

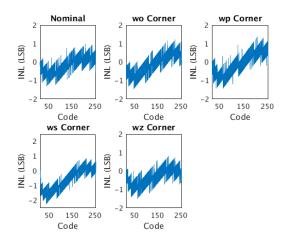

## Software and Electronics for Spacepix Detector Read-out