#### **Master Thesis**

Czech Technical University in Prague

F3

Faculty of Electrical Engineering Dapartment of Microelectronics

# JESD 204B Rx Controller Design

Bohdan Jůza

Supervisor: prof. Ing. Pavel Hazdra, CSc. Supervisor–specialist: Ing. Martin Hujer, Ph.D. Field of study: Electronics and Communications

**Subfield: Electronics**

May 2021

# ZADÁNÍ DIPLOMOVÉ PRÁCE

## I. OSOBNÍ A STUDIJNÍ ÚDAJE

| Příjmení: | Jůza | Jméno: <b>Bohdan</b> | Osobní číslo: | 466308 |

|-----------|------|----------------------|---------------|--------|

|           |      |                      |               |        |

Fakulta/ústav: Fakulta elektrotechnická

Zadávající katedra/ústav: Katedra mikroelektroniky

Studijní program: Elektronika a komunikace

Specializace: Elektronika

## II. ÚDAJE K DIPLOMOVÉ PRÁCI

| Název dip | lomové práce: |  |

|-----------|---------------|--|

#### Návrh Rx řadiče ve standardu JESD 204B

Název diplomové práce anglicky:

#### JESD 204B Rx Controller Design

#### Pokyny pro vypracování:

- 1. Seznamte se s protokolem JESD204 ve verzi B a C a multigigabitovými transceivery v Xilinx FPGA.

- 2. Porovnejte verze A, B a C protokolu JESD204, jejich výhody, nevýhody a jejich použití.

- 3. V jazyce Verilog2001 implementujte přijímací linkovou vrstvu protokolu JESD204B/C (kontrolér) s kódováním 8B/10B.

- 4. Ověřte funkci řadiče simulací na RTL úrovni pomocí referenční implementace s Xilinx JESD204C Tx IP a popřípadě validací na desce s FPGA.

#### Seznam doporučené literatury:

- [1] JESD204 standard, https://www.jedec.org/document\_search?search\_api\_views\_fulltext=jesd204

- [2] Úvod do přehledu JESD204 od Analog Devices,

https://www.analog.com/media/en/technical-documentation/technical-articles/JESD2 04B-Survival-Guide.pd

Jméno a pracoviště vedoucí(ho) diplomové práce:

#### prof. Ing. Pavel Hazdra, CSc., katedra mikroelektroniky FEL

Jméno a pracoviště druhé(ho) vedoucí(ho) nebo konzultanta(ky) diplomové práce:

#### Ing. Martin Hujer, Ph.D., Dialog Semiconductor CZECH, s.r.o., Klicperova 3208/12, Praha 5

Datum zadání diplomové práce: 26.01.2021 Termín odevzdání diplomové práce: \_\_\_\_\_

Platnost zadání diplomové práce: 30.09.2022

prof. Ing. Pavel Hazdra, CSc. prof. Ing. Pavel Hazdra, CSc. prof. Mgr. Petr Páta, Ph.D. podpis vedoucí(ho) práce podpis vedoucí(ho) ústavu/katedry podpis děkana(ky)

#### III. PŘEVZETÍ ZADÁNÍ

| Diplomant bere na vědomí, že je povinen vypracovat diplomovou práci samostatně, bez cizí pomoci, s výjimkou poskytnutých konzultac |

|------------------------------------------------------------------------------------------------------------------------------------|

| Seznam použité literatury, jiných pramenů a jmen konzultantů je třeba uvést v diplomové práci.                                     |

| •                     |                 |

|-----------------------|-----------------|

| Datum převzetí zadání | Podpis studenta |

# **Acknowledgements**

Firstly, I would like to thank the supervisor specialist of my master thesis Mr. Ing. Martin Hujer, Ph.D. from Dialog Semicondutor CZECH company for consultation and factual comments. Secondly, my thanks go to prof. Ing. Pavel Hazdra, CSc. from CTU in Prague for enabling and supervising of my thesis. An lastly, I would like to thank my family for their support during the whole study.

# **Declaration**

I declare that the presented work was developed independently and that I have listed all sources of information used within it in accordance with the Methodical instructions for observing the ethical principles in the preparation of university theses.

In Prague, 21 May 2021

Bohdan Jůza

## **Abstract**

The master thesis deals with the design of the receiving link layer according to the JESD204B standard. It introduces the history of the standard from its first version to the current revision C. It delves deeper into the theoretical foundations of the revision B, from the perspective of the link layer. Further, the designed modules themselves are described. First the main one and then the ones of which it consists. Finally, the verification process is also shown, most notably the simulation of the designed block. The possibility of implementing the device in FPGA for a proper verification is also outlined.

**Keywords:** Verilog, Xilinx, FPGA, JESD204, JESD204B

Supervisor: prof. Ing. Pavel Hazdra, CSc. CTU Faculty of Electrical Engineering, Technická 1902/2, 16027 Prague, Czech Republic

## **Abstrakt**

Diplomová práce se věnuje návrhu linkové vrstvy přijímače dle standardu JESD204B. Seznamuje s historií standardu od své první verze až po současnou revizí C. Hlouběji se věnuje představení teoretických základů revize B, a to z pohledu linkové vrstvy. Dále jsou popsány samotné navržené moduly. Nejprve ten hlavní a pak také ty, z kterých se skládá. Na závěr je rovněž ukázán proces verifikace, nejvíce pak simulace navrženého bloku. Nastíněna je i možnost implementace zařízení v FPGA pro plnohodnotnou verifikaci.

Klíčová slova: Verilog, Xilinx, FPGA, JESD204, JESD204B

**Překlad názvu:** Návrh Rx řadiče ve standardu JESD 204B

# **Contents**

| 1 Introduction                        | 1  |

|---------------------------------------|----|

| 2 Theoretical Background              | 3  |

| 2.1 JESD204 in General                | 3  |

| 2.2 Motivation to Use JESD204         | 3  |

| 2.3 Development of Revisions          | 4  |

| 2.3.1 Original JESD204                | 4  |

| 2.3.2 JESD204A                        | 5  |

| 2.3.3 JESD204B                        | 6  |

| 2.3.4 JESD204C                        | 7  |

| 2.4 LVDS compared to JESD204          | 7  |

| 2.5 Layer Architecture in JESD204B    | 8  |

| 2.6 JESD204B in Detail                | 10 |

| 2.6.1 Deterministic Latency           | 10 |

| 2.6.2 Device clock                    | 13 |

| 2.6.3 Frame and Multiframe Clock      | 14 |

| 2.6.4 Scrambling                      | 14 |

| 2.6.5 8B/10B Coding                   | 15 |

| 2.7 Link Layer Operation of Receiver  | 19 |

| 2.7.1 Code Group Synchronization      | 19 |

| 2.7.2 SYNC~ Signal Combining          | 21 |

| 2.7.3 Frame Synchronization           | 21 |

| 2.7.4 Lane Synchronization            | 23 |

| 2.8 Implementation of JESD204         |    |

| protocol in ASIC                      | 24 |

| 2.9 Xilinx Multigigabit Transceiver . | 25 |

| 2.10 Receiving Side of JESD204        |    |

| Protocol on FPGA                      | 27 |

| 2.11 Verilog                          | 28 |

| 3 Development of Receiving Link       |    |

| Layer of JESD204B Protocol            | 31 |

| 3.1 Development Tools                 | 32 |

| 3.1.1 Vivado Design Suite 2020.1      | 32 |

| 3.1.2 ModelSim PE Student Edition     |    |

| 10.4a                                 | 32 |

| 3.1.3 Cadence Xcelium                 | 32 |

| 3.2 Design                            | 33 |

| 3.2.1 Top Module of Receiving Link    |    |

| Layer of JESD204B                     | 33 |

| 3.2.2 Designed Submodules             | 38 |

| 3.3 Verification                      | 48 |

| 3.3.1 Simulation of Xilinx JESD204    |    |

| TX IP in Vivado                       | 48 |

| 3.3.2 Simulation of DUT               | 50 |

| 3.3.3 Simulation of DUT with Xilinx   |    |

| IPs                                   | 53 |

| 3.4 Synthesis                         | 59 |

| 5 Conclusion 6<br>Bibliography 6                 | 3.4.1 FPGA                    | 59 |

|--------------------------------------------------|-------------------------------|----|

| 4 Future Updates 6 5 Conclusion 6 Bibliography 6 | 3.4.2 ASIC                    | 60 |

| 5 Conclusion 6<br>Bibliography 6                 | 3.5 Validation on FPGA        | 6  |

| Bibliography 6                                   | 4 Future Updates              | 63 |

| <b>3</b>                                         | 5 Conclusion                  | 65 |

| A Contents on the enclosed CD 6                  | Bibliography                  | 67 |

|                                                  | A Contents on the enclosed CD | 69 |

# **Figures**

| 2.1 CMOS, LVDS and CML power                             |    |

|----------------------------------------------------------|----|

| consumption dependency on sample                         |    |

| rate [6]                                                 | 4  |

| 2.2 JESD204 original standard                            |    |

| illustration                                             | 5  |

| $2.3~\mathrm{JESD}204\mathrm{A}$ standard illustration . | 6  |

| $2.4~\mathrm{JESD}204\mathrm{B}$ standard illustration . | 6  |

| 2.5 System design using LVDS                             | 8  |

| 2.6 System design using JESD204                          | 8  |

| 2.7 Layer architecture of JESD204B                       | 10 |

| 2.8 Illustration of deterministic                        |    |

| latency                                                  | 11 |

| 2.9 Timing diagram illustration for                      |    |

| deterministic latency by SYSREF                          |    |

| [1]                                                      | 12 |

| 2.10 Serial implementation of                            |    |

| scrambler                                                | 15 |

| 2.11 Code group synchronization for                      |    |

| subclass 0                                               | 20 |

| 2.12 Code group synchronization for                      |    |

| subclasses 1 and 2                                       | 20 |

| 2.13 Illustration of SYNC~ signal                        |    |

| combining                                                | 21 |

| 2.14 Initial lane alignment sequence                     |    |

| with four multiframes [1]                                | 24 |

| 2.15 Illustration of example                             |    |

| implementation of JESD204 in ASIC                        | 25 |

| 2.16 GTP RX Transceiver Block                            |    |

| Diagram [11]                                             | 26 |

| 2.17 Illustration of receiving side of                   |    |

| JESD204 protocol implemented on                          |    |

| FPGA                                                     | 27 |

|                                                          |    |

| 3.1 Graphical representation of                          |    |

| designed JESD204B receiver for                           |    |

| $NR\_OF\_LANES = 1 \dots$                                | 34 |

| 3.2 Simplified graphical representation                  |    |

| of internal structure                                    | 36 |

| 3.3 Graphical representation of the                      |    |

| module $cgs$                                             | 38 |

| 3.4 State machine implemented in                         |    |

| module $cgs$                                             | 39 |

| 3.5 Graphical representation of the                      |    |

| module $s3\_8b10b\_decoder$                              | 40 |

| 3.6 Graphical representation of the                      |    |

| module $cq$ $check$                                      | 40 |

| 3.7 State machine implemented in        |    |

|-----------------------------------------|----|

| module $cg\_chceck$                     | 41 |

| 3.8 Graphical representation of the     |    |

| module $clock\_gen$                     | 42 |

| 3.9 Graphical representation of the     |    |

| module frame_lane_align                 | 43 |

| 3.10 Illustration of data flow in the   |    |

| frame_lane_align module                 | 43 |

| 3.11 Graphical representation of the    |    |

| module $descrambler \dots$              | 46 |

| 3.12 Graphical representation of the    |    |

| $module \ controller \dots \dots \dots$ | 47 |

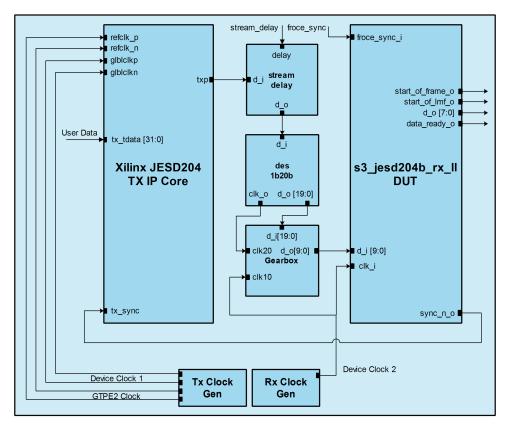

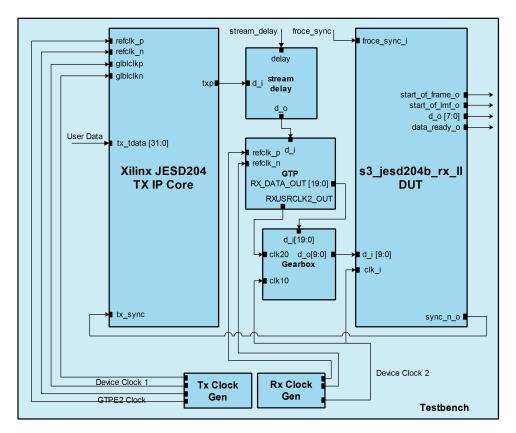

| 3.13 Idea scheme of simulation          | 49 |

| 3.14 Transmitter core overview [12].    | 50 |

| 3.15 Idea scheme of simulation          | 51 |

| 3.16 Code coverage of particular        |    |

| submodules                              | 53 |

| 3.17 Graphical representation of        |    |

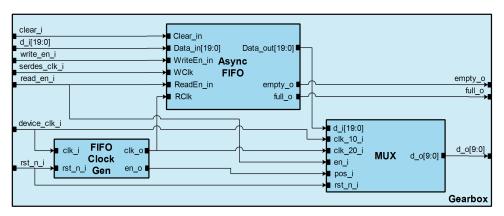

| $gearbox \dots gearbox$                 | 54 |

| 3.18 Idea scheme of simulation          | 55 |

| 3.19 Idea scheme of simulation          | 56 |

| 3.20 Screenshot of messages in          |    |

| simulation console                      | 57 |

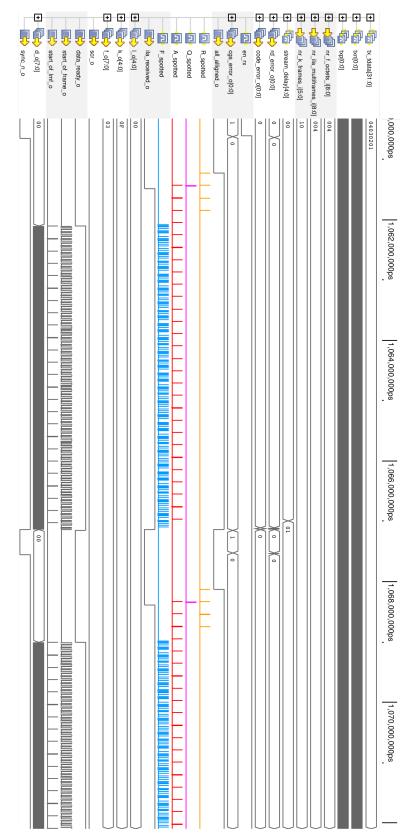

| 3.21 Screenshot of waveform             | 58 |

| 3.22 Data path illustration for         |    |

| validation on FPGA                      | 61 |

|                                         |    |

# **Tables**

| 2.1 Comparison between the CMOS,                       |     |

|--------------------------------------------------------|-----|

| LVDS and JESD204B in the pin                           |     |

| count for a 200 MSPS ADC [4]                           | 5   |

| 2.2 Comparison between LVDS and                        |     |

| JESD204 revisions                                      | 9   |

| 2.3 Electrical specifications for                      |     |

| JESD204B [5] [2]                                       | 10  |

| 2.4 Rules for 5B/6B encoding                           | 17  |

| 2.5 Rules for 3B/4B encoding                           | 17  |

| 2.6 Control characters used in                         |     |

| JESD204                                                | 18  |

| 2.7 Rules for running disparity                        | 18  |

| 2.8 Link configuration parameters [1]                  | 29  |

| 2.8 Link configuration parameters [1]                  | 29  |

| 3.1 Description of sharing submodules                  |     |

| in multiple lane configuration                         | 33  |

| 3.2 Ports description for the                          |     |

| JESD204B receiver                                      | 35  |

| 3.3 Parameters of designed block                       | 37  |

| 3.4 Ports description for the $cqs$                    | ٠.  |

| module                                                 | 38  |

| 3.5 Ports description for the                          | 30  |

| $s3\_8b10b\_decoder \text{ module } \dots$             | 40  |

| 3.6 Ports description for the <i>cg_check</i>          | 10  |

| module                                                 | 41  |

| 3.7 Ports description for the                          | 41  |

|                                                        | 44  |

| frame_lane_align module  3.8 Ports description for the | 44  |

| descrambler module                                     | 47  |

|                                                        |     |

| 3.9 Ports description for the <i>controller</i>        |     |

| module                                                 | 48  |

| 3.10 Ports description for the <i>gearbox</i>          | - 1 |

| module                                                 | 54  |

| 3.11 Parameters of the example                         |     |

| simulation                                             | 57  |

| 3.12 Parameters for synthesis                          | 59  |

| 3.13 Post-Synthesis utilization of                     |     |

| designed JESD204B receiver for                         |     |

| FPGA                                                   | 59  |

| 3.14 Post-Synthesis area report for                    |     |

| ASIC                                                   | 60  |

| 3.15 Post-Synthesis power report for                   |     |

| ASIC                                                   | 60  |

# Chapter 1

# Introduction

The master thesis deals with the design of the link layer of the receiver in the JESD204 standard, specifically in revision B. Four main goals were set for the work. The first one was an introduction to the JESD204 protocol in versions B and C, as well as to multigigabit transceivers within the Xilinx FPGA. The second task was to compare the individual versions A, B and C of the protocol with each other and to explain the advantages and disadvantages of their use in practice. The third and main goal was to design the link layer of the receiver itself in the specified standard with the 8B/10B coding using the Verilog2001 language. The fourth and last task was to verify the designed device by means of a RTL simulation using the reference Xilinx JESD204 TX IP core and possibly verify the system on a board with a FPGA. One side goal could be mentioned and it was designing in the Verilog language, which was a new experience.

The work itself is divided into five chapters including this introduction and the final conclusion. The first part after the introduction presents the theoretical basis of the JESD204 protocol. It deals with the reason for its implementation, the motivation why to use it, the comparison of individual versions with each other, which are also juxtaposed with the LVDS technology for a parallel signalling. Additionally, it focuses on the revision B itself, listing its main benefits and improvements over previous versions. The section focused on the link layer follows, its implementation was the main goal of this thesis. At the end of the chapter, there are also two sections focusing on Verilog and multigigabit transceivers within the Xilinx FPGA. The third chapter outlines the design of the receiver itself. At the beginning, the tools that were used for the development are listed. It is followed by presenting the designed block. The attention is focused on the design of the developed block from the outside. Then it forms a description of its internal connection with the designed submodules and their internal arrangement is described. The next section is dedicated to the verification of the developed device. It deals mainly with simulations in various simulation tools, the simulation procedure and lists other circuits that had to be designed with regard to the fact, that the resulting receiver was supposed to be validated on the board with a FPGA. The final information within this chapter is about the synthesized design of 1. Introduction

the developed receiving link layer of the JESD204B protocol. The last but one chapter then outlines the direction in which the proven work could be followed up in the future and finally there is a conclusion at the end of this thesis.

# Chapter 2

# **Theoretical Background**

## 2.1 JESD204 in General

Analog to digital converters (ADC) and digital to analog converters (DAC) are becoming steadily more and more accurate and faster. It means that their interface is getting larger in the count of pins needed to transport the data and the output or input frequency has also grown. This is the reason, why the interface JESD204 was developed several years ago and has undergone revisions to make it even more suitable for this case of use. The JESD204 interface comes out with some crucial advantages over the conventional CMOS (Complementary Metal-Oxide-Semiconductor) and LVDS (Low-Voltage Differential Signaling) interfaces. The implementation of the JESD204 on the FPGA (Field Programmable Gate Array) or ASIC (Application Specific Integrated Circuit) yields to the ability to keep up with faster sample rates of converters. It reduces the pin count, so the resulting device has a smaller package size. The reduction of the pin count also leads to a decrease of trace routes, which makes the board design much easier and offers a lower overall system cost. The scalability is another benefit. The JESD204 standard was introduced in 2006 and since then it has been updated in three revisions, which have improved its efficiency. The latest one is the JESD204C revision. [4]

## 2.2 Motivation to Use JESD204

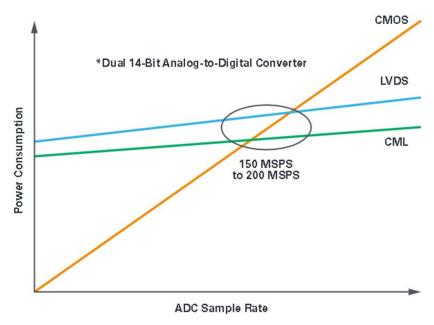

As requirements of converters were by time incessantly increasing, the development of their interface was performed too. For converters with a high data rate, wide resolution and demand for a low power consumption is currently JESD204, which uses the current mode logic (CML), concerned as the best way, how to transport the data for the further processing in a FPGA or ASIC. The CMOS technology lacks in the power consumption in higher speeds. The LVDS allows higher data rates, but it is also limited, due to the driver architecture and the necessity of the synchronization of all lanes, where the number of lanes could be significantly great. These statements are summarized in the figure 2.1 for the use with a dual 14-bit ADC. [4]

Figure 2.1: CMOS, LVDS and CML power consumption dependency on sample rate [6]

As stated above, the CML technology requires a fewer portion of pins at the same speed and resolution, as it is a serialized communication, when not talking about low data rates. Differences between technologies in this aspect are illustrated in the table 2.1. There is a comparison for a 200 MSPS ADC with a various number of channels and resolution. From the number of pins for each interface it is evident the advantage of using the JESD204B. It can be stated that the use of the JESD204 is not appropriate in cases of lower sample rates, approximately 150 MSPS, and if a minimal latency across the communication chain is needed. [3] [4]

# 2.3 Development of Revisions

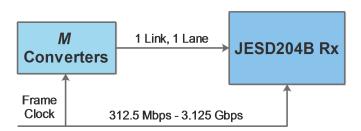

## 2.3.1 Original JESD204

The original version of the JESD204 was launched in 2006. The standard was designed for a multigligabit serial data link between a converter, or multiple converters, and a receiver or transceiver, most often a device such as a FPGA or ASIC. This original version was limited for only one link connecting converter, or converters, and a receiver. The link could only consist of one lane. The illustration of this version is shown in the figure 2.2. The lane in the figure is a physical medium transporting a serialized data between M converters and a receiver. It is achieved by means of a differential pair working with the CML technology. As could be seen, the exactly same frame clock is provided for both sides, for converters and for a receiver. The source

| Number of<br>Channels | Resolution | CMOS<br>Pin Count | LVDS<br>Pin Count | JESD204B<br>Pin Count |

|-----------------------|------------|-------------------|-------------------|-----------------------|

| 1                     | 12         | 13                | 14                | 2                     |

| 2                     | 12         | 26                | 28                | 4                     |

| 4                     | 12         | 52                | 56                | 8                     |

| 8                     | 12         | 104               | 112               | 16                    |

| 1                     | 14         | 15                | 16                | 2                     |

| 2                     | 14         | 30                | 32                | 4                     |

| 4                     | 14         | 60                | 64                | 8                     |

| 8                     | 14         | 120               | 128               | 16                    |

| 1                     | 16         | 17                | 18                | 2                     |

| 2                     | 16         | 34                | 36                | 4                     |

| 4                     | 16         | 68                | 72                | 8                     |

| 8                     | 16         | 136               | 144               | 16                    |

**Table 2.1:** Comparison between the CMOS, LVDS and JESD204B in the pin count for a 200 MSPS ADC [4]

and load impedances were defined as  $100\,\Omega\pm20\,\%$  and the differential voltage at the nominal value of 800 mV. The original version also supported the 8B/10B encoding. All above aspects led to the defined lane data rate within limits 312.5 Mb/s and 3.125 Gb/s. The standard became very popular and the first revision was needed. The goals were mainly about dealing with the increasing speed and resolution of converters. [1] [4]

Figure 2.2: JESD204 original standard illustration

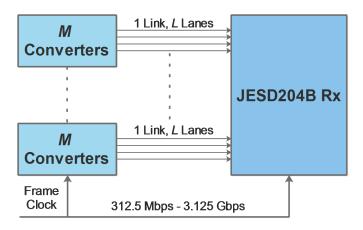

#### 2.3.2 JESD204A

In 2008 the new revision of the standard called JESD204A came into the market. The main improvement was a support of multiple aligned serial lanes with multiple converters, as could be seen in the figure 2.3. Other specifications as the lane data rate, electrical specifications and the frame clock distribution remained unchanged. Now, it was possible to meet the maximum data rate 3.125 Gb/s for converters with a high sample rate and high resolution due to multiple aligned serial lanes. However, in the revised standard one important feature was missing. It was a deterministic latency, which is crucial for a correct interpretation of the received digital data in

some applications. This was the reason for developing a new revision of the standard. [4]

Figure 2.3: JESD204A standard illustration

#### 2.3.3 JESD204B

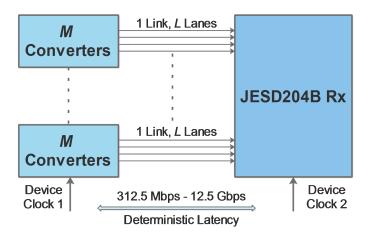

The improved revision JESD204B was released in 2011. The key element missing in previous ones, deterministic latency, was since then included. Furthermore, several other features were introduced. Firstly, the supported data rate was raised up to 12.5 Gb/s. Three grades of devices differing in the data rate were distinguished. Speed grade 1 supports up to 3.125 Gb/s, the second one supports up to 6.375 Gb/s and the last one supports up to 12.5 Gb/s. They have also different electric specifications. Secondly, the common source of the frame clock was omitted and the main clock source specific for each device became a device clock. The figure 2.4 shows the illustration of the JESD204B revision. The JESD204B will be described in more detail further in the thesis. [1]

Figure 2.4: JESD204B standard illustration

#### 2.3.4 JESD204C

The latest revision, JESD204C, was launched in 2017. It brings some further improvements of the revision B to achieve a greater data rate and more efficient transport of the payload data. The revision's C definition of the physical layer allows to greatly increase the data rate up to 32 Gb/s, while also providing a backward compatibility to the revision B. The efficiency improvement is mainly caused by changing the encoding scheme. Newly, it supports the 64B/66B and 64B/80B encoding beyond the 8B/10B encoding. They have a shorter coding overhead, so there is more place for data bits. Devices are similarly divided into device classes as in the previous revision in order to provide driver/receiver pairs that have varying amounts of a signal integrity processing to reduce the power in shorter channels. The downside of this revision can be a not full backward compatibility with the JESD204A revision. [2]

## 2.4 LVDS compared to JESD204

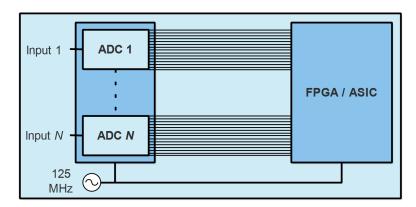

The parallel low voltage differential signalling (LVDS) is an older method to interface converters on a FPGA or ASIC. It was revised lastly in 2001 and it was a replacement of the RS-422 and RS-485 protocols, which had a higher power consumption and lower bandwidth. The LVDS uses differential signals with low voltage swings for a high speed data transmission.

The first problem of this technology lies in the low bandwidth for a use case with modern converters. The bandwidth of a differential LVDS wire is theoretically limited to 1.9 Gb/s, but in the real world it is maximally about 1.0 Gb/s. The second problem is a need of a great number of interconnects, as converters have a wider resolution. Therefore the JESD204 interface was developed. [5]

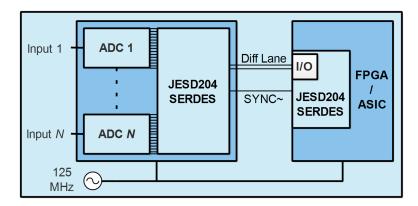

Figures 2.5 and 2.6 are illustrating differences in a system design using the LVDS for a parallel data transportation, respectively the JESD204 interface. It could be clearly seen that the JESD204 reduces the number of traces and the complexity of routing, simplifies the synchronization and the design is easily scalable. [5]

The table 2.2 summarises differences between the LVDS and all current revisions of the JESD204 standard. [1] [2] [5]

Figure 2.5: System design using LVDS

Figure 2.6: System design using JESD204

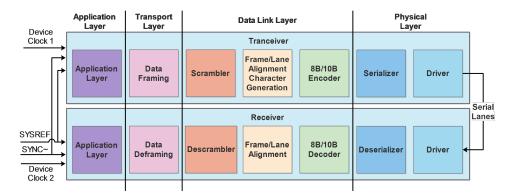

# 2.5 Layer Architecture in JESD204B

Similarly like the TCP/IP protocol, the JESD204 is divided into four individual layers, each with its own function. The layers are named as application layer, transport layer, data link layer and physical layer. The illustration of the layer composition is in the figure 2.7. [1]

#### Application Layer

The application layer is used for a special configuration and data mapping. Thanks to the specific framing of bits and other options, it is possible to achieve a reduction in the power consumption or to ensure a better data transfer from a converter with an atypical bit width. In that case, it is crucial to have configured the transceiver and receiver in the exactly same way. [8]

#### Transport Layer

The main task of the transport layer is to map samples from converter or converters to non-scrambled octets. There are several possibilities, how the mapping is done [1]:

| Function                  | LVDS | JESD204 | rev.A  | rev.B  | rev.C                        |

|---------------------------|------|---------|--------|--------|------------------------------|

| Specification<br>Realease | 2001 | 2006    | 2008   | 2011   | 2017                         |

| Max Lane<br>Rate [Gb/s]   | 1.0  | 3.125   | 3.125  | 12.5   | 32.0                         |

| Multiple<br>Lanes         | No   | No      | Yes    | Yes    | Yes                          |

| Lane<br>Sync              | No   | No      | Yes    | Yes    | Yes                          |

| Multidevice<br>Sync       | No   | Yes     | Yes    | Yes    | Yes                          |

| Deterministic<br>Latency  | No   | No      | No     | Yes    | Yes                          |

| Harmonic<br>Clocking      | No   | No      | No     | Yes    | Yes                          |

| Coding<br>Scheme          | No   | 8B/10B  | 8B/10B | 8B/10B | 8B/10B<br>64B/66B<br>64B/80B |

**Table 2.2:** Comparison between LVDS and JESD204 revisions

- Single converter single-lane link

- Multiple converters within the same device single-lane link

- Single converter multi-lane link

- Multiple converters within the same device multi-lane link

The frame is then formed by a concatenation of F octets. There is also an option of sending more than one sample from a single converter in a single frame. This must be defined by the number S. [1]

#### Data Link Layer

Implementing the data link layer is the main purpose of this thesis and will be discussed in more detail later.

#### Physical Layer

The data serialization is realized in the physical layer. The physical layer contains serializer/deserializer (SerDes) blocks, drivers, receivers, and CDR. Also, the physical layer indicates the data rate speeds. As mentioned above, the JESD204B is divided into three grades. The maximum supported speed in JESD204B is 12.5 Gbps. The table 2.3 summarizes the electrical specifications for each grade. [8]

Figure 2.7: Layer architecture of JESD204B

| Parameter                           | Grade 1    | Grade 2   | Grade 3   |  |

|-------------------------------------|------------|-----------|-----------|--|

| Line Rate [Gbps]                    | 3.125      | 6.375     | 12.5      |  |

| Out Differential                    | 500 1000   | 400 750   | 260 770   |  |

| Voltage [mVppd]                     | 500 - 1000 | 400 - 750 | 360 - 770 |  |

| Out Rise/Fall                       | 50         | 30        | 24        |  |

| Time [ps]                           | 30         | 30        | 24        |  |

| Out Total                           | 0.35       | 0.30      | 0.30      |  |

| Jitter (p-p UI)                     | 0.55       | 0.50      | 0.30      |  |

| p-p UI = peak-to-peak Unit Interval |            |           |           |  |

**Table 2.3:** Electrical specifications for JESD204B [5] [2]

## 2.6 JESD204B in Detail

This section will cover a closer look to the JESD204B interface, its features and standardizations. Some basic information were already provided in the section 2.3.3. According to the assignment, the main focus will be devoted to the link layer.

### 2.6.1 Deterministic Latency

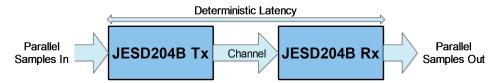

In the engineering, a latency is a designation for the time elapsed between an action and reaction, or also the time required for the signal to pass between a point A and point B. For a JESD204 link is the point A the parallel input to the JESD204B transmitter and the point B corresponds to the parallel output of the JESD204B receiver's buffer. If so, it can be talked about the deterministic latency. It is important to not get confused with the term link delay. The link delay has an endpoint as an input to the receiver's buffer. The figure 2.8 illustrates the meaning of the deterministic latency. [1] [4]

Figure 2.8: Illustration of deterministic latency

The JESD204B standard is divided into three subclasses according to how they achieve the deterministic latency:

- Subclass 0 deterministic latency is not supported

- Subclass 1 deterministic latency by means of signal SYSREF

- Subclass 2 deterministic latency by means of signal SYNC~

#### Subclass 0

Due to a backward compatibility to the JESD204A revision is the JESD204B containing the subclass 0. The deterministic latency is not supported in this case. This could be useful for implementing the revision B with some older devices designed for the revision A. The subclass 0 has also different requirements for the SYNC~ signal from the subclass 1, as listed below. [4]

SYNC~ signal requirements (corresponding with the subclass 2) [1] [4]:

- The SYNC~ signal and receiver's and transmitter's frame clock must be synchronous.

- The SYNC~ can not be AC coupled.

- The device clock to the SYNC~ delay  $(t_{DS\_R})$  at the receiver device pins must be specified.

- The setup and hold time for the SYNC~ to the device clock at the transmitter must be specified.

The lane alignment in subclass 0 is achieved by means of an elastic buffer. The buffer is applied on each lane in the link. All incoming characters are stored in these buffers during the initial lane alignment sequence (ILAS) and after the arrival of the last lane's first start of multiframe control character (/R/=K28.0), all buffers are released at the exactly same time. The same mechanism is applied also for the subclass 1 and 2, however the release time differs. [4]

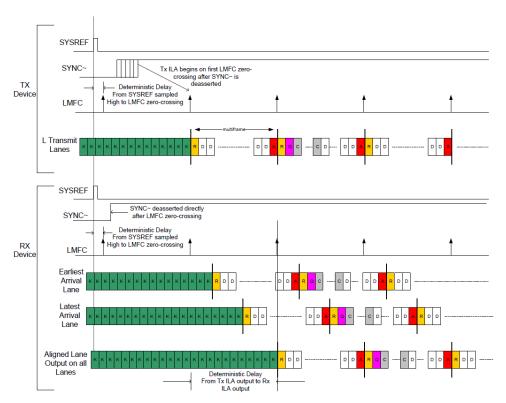

Figure 2.9: Timing diagram illustration for deterministic latency by SYSREF [1]

#### Subclass 1

In a technical practice, there are many applications where we need not only the synchronization across one link or multiple devices, but also we need to know the exact latency of the information transfer from the converter to the logical device. It means the deterministic latency in this case. For instance, some ADCs realize their calibration by means of a feedback loop and for this is a knowledge of the latency a crucial requirement. In other words, the arriving of the data must be stable after every power cycle. [4]

In the subclass 0, the receiver was monitoring all lanes until the first /R/ control character on latest lane arrived. Then the sample data were released. This solution is not counting with the time variation between each power cycle. The subclass 1 is synchronizing the release to the external SYSREF signal. This is done by the phase aligning of the local multiframe clock (LMFC) to the SYSREF signal. The illustration of the timing in the subclass 1 could be seen in the figure 2.9. The application of the subclass 1 is suitable for the data rate above 500 MSPS. [4]

Requirements for subclass 1 [1] [4]:

- The delay between the leading edge of the SYSREF signal and the frame and multiframe boundary must be specified for all devices in the JESD204B system.

- The buffer depth is defined by the receive buffer delay (RBD) and is ranging from 1 to K frame cycles. Mostly is the RBD set to 32.

- If the system needs a multichip synchronization between JESD204 devices, the use of the exactly same model of the converters is required. Otherwise, there could be problems with the deterministic latency.

- The inter-device lane skewness must be minimized.

- The device clock and SYSREF generation from the same clock source is required. The inter-device skewness must be also minimized.

#### Subclass 2

If a particular application requires a reduction of the pin and net count, it is appropriate to use the realization of the deterministic latency by means of SYNC~ signal. This is called subclass 2. The subclass 2 is suitable for the data rate below approximately 500 MSPS. The provision of the deterministic latency this way is possible because the SYNC~ is derived from the receiver's LMFC. Using this knowledge, the synchronization between the receiver and transmitter can be ensured. [1] [4]

#### 2.6.2 Device clock

One improvement, which the JESD204B revision came up with, was the absence of the clock interconnection between the transmitter and receiver. Each device has its own device clock. The device clock is a timing reference specific for each device, but it must be derived from the common source, the source clock. The frequency of the device clock and frame or multiframe clock may vary. This means that each device has to generate its own local frame and multiframce clock with exactly the same frequency in a receiver and transmitter. [1]

Relationships between device clocks, frame or multiframe clocks differs across particular subclasses as follows:

- Subclass 0: Specified by the device implementer [1]

- Subclass 1: The multiframe period shall be a whole number of device clock periods [1]

- Subclass 2: The multiframe period shall be a whole number of device clock periods. Additionally, the TX device clock period shall be a whole number of RX device clock periods, or the RX device clock period shall be a whole number of TX device clocks periods. [1]

## 2.6.3 Frame and Multiframe Clock

The importance of the frame clock is in the establishing of the interface from the link layer to the application layer and conversely. The data are composed into multiframes, which are aligned with the local multiframe clock (LMFC). The clock reference is called local, if it is derived from the device clock. In other words, when the clock is not directly supplied on the input to the device. The phase alignment of the LMFC is intended by the SYSREF signal for the subclass 1 or by the SYNC~ signal for the subclass 2, not supported in the subclass 0. [1]

Requirements for frame and multiframe clocks are as follows:

- Identical frame frequency across all devices [1]

- Identical multiframe frequency across all devices [1]

- Both derived from the device clock [1]

- Phase aligning of the frame clock and LMFC within each device [1]

- The SYSREF for the subclass 1 and the SYNC~ for the subclass 2 intends the phase of the frame clock and LMFC [1]

- For multiple links, each above requirement is applied separately on each link [1]

#### 2.6.4 Scrambling

The scrambling is an optional function in the JESD204, however, all devices shall support this technique. If the octets transmitting in the JESD204 system are repetitive frame to frame, there is a possibility of an occurrence of the spectral peaks. This can lead to problems with the electromagnetic compatibility (EMC), DC offsets or interferences. The application of the scrambling also makes the spectrum data-independent. On the other hand, this operation can have some negative effects. One disadvantage could be a switching noise, whose amount may be so great, that the disabling of the scrambling would be advantageous. [1]

The scrambling operation is located between the transport and link layer. There is one scrambler per a particular lane. The enabling of the scrambling means that all scramblers and descramblers on all links and all lanes are enabled. There is no support for a mixed mode. [1]

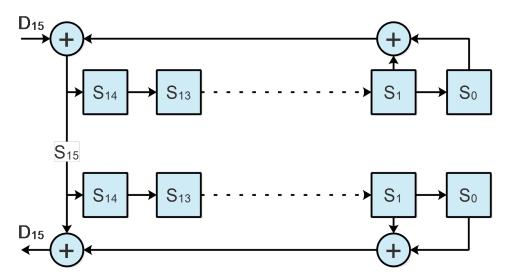

The scrambler shall be of the self-synchronous type with the polynomial  $1 + x^{14} + x^{15}$ . [1] The serial implementation is illustrated in the figure 2.10

One important thing is the initial state of the scrambler. In order to not send repetitive octets, the scrambler must have initiated internal registers.

Figure 2.10: Serial implementation of scrambler

It is recommended to preset the upper eight registers to logical 1 and lower seven registers to logical 0. For descrambler, there is no need for presetting registers as the descrambler is self-synchronized. [1]

## 2.6.5 8B/10B Coding

Before transmitting to the receiver, the data are encoded by the 8B/10B coding. An 8-bit octet is encoded to a 10-bit character, which is then transmitted. This coding scheme is used to achieve a DC balance on lanes and a bounded disparity. The coding ensures, that the count of ones and zeros in the 20-bit long sequence does not differ more than by two and it is impossible to have more than five ones or zeros in a row. Such changes in states are useful for the clock recovery. [7]

The 8B/10B coding is separated in two processes. An input octet is divided in two groups, the lower 5 bits portion and upper 3 bits portion. The first group is encoded to a 6-bit sequence and second group to a 4-bit sequence. These sequences are concatenated together and this is how the 10-bit character is made. The code group (CG) characters are called as D.x.y, where x ranges from 0 to 31 and y ranges from 0 to 7. In addition, 12 special characters (control characters) are defined. They are called as K.x.y and indicates some special events. [7]

The rules for the 5B/6B encoding are summarized in the table 2.4 and the rules for the 3B/4B encoding are summarized in the table 2.5. Control characters, which are used in the JESD204, are summarized in the table 2.6.

## Running Disparity

As mentioned above, 8B/10B coding is DC balanced. It means, that in long period the counts of ones and zeros are equal. In other words, the ratio between ones and zeros is exactly 50 %. This is achieved by the fact, that the difference between ones and zeros in each coding group (5B/6B and 3B/4B) is in range from -2 to +2. At the end of the 8B/10B coding is the difference either +1 or -1. This is called as the running disparity (RD). [7] The rules for calculating the running disparity for each sub-block are as follows.

The running disparity at the end of any sub-block is positive, if

- the count of ones is greater than count of zeros in a sub-block [7],

- the six-bit sub-block is 000111 [7],

- the four-bit sub-block is 0011. [7]

The running disparity at the end of any sub-block is negative, if

- the count of ones is lower than count of zeros in a sub-block [7],

- the six-bit sub-block is 111000 [7],

- the four-bit sub-block is 1100. [7]

If none of the condition above occurred, the running disparity at the end of the sub-block is the same as the running disparity at the beginning of the sub-block. [7]

The rules for the running disparity are summarized in the table 2.7.

| I             | nput       | RD-    | RD+    | RD+ Input     |       | RD-     | RD+    |

|---------------|------------|--------|--------|---------------|-------|---------|--------|

|               | Octet      | Ence   | oded   | ed Octet      |       | Encoded |        |

| $\mathbf{CG}$ | ${f Bits}$ | Bits   |        | $\mathbf{CG}$ | Bits  | Bits    |        |

|               | EDCBA      | abo    | edei   |               | EDCBA | abcdei  |        |

| D.00          | 00000      | 100111 | 011000 | D.16          | 10000 | 011011  | 100100 |

| D.01          | 00001      | 011101 | 100010 | D.17          | 10001 | 100011  |        |

| D.02          | 00010      | 101101 | 010010 | D.18          | 10010 | 010     | 011    |

| D.03          | 00011      | 110    | 001    | D.19          | 10011 | 110010  |        |

| D.04          | 00100      | 110101 | 1010   | D.20          | 10100 | 001011  |        |

| D.05          | 00101      | 101001 |        | D.21          | 10101 | 101010  |        |

| D.06          | 00110      | 011001 |        | D.22          | 10110 | 011010  |        |

| D.07          | 00111      | 111000 | 000111 | D.23          | 10111 | 111010  | 000101 |

| D.08          | 01000      | 111001 | 000110 | D.24          | 11000 | 110011  | 001100 |

| D.09          | 01001      | 100101 |        | D.25          | 11001 | 100     | 110    |

| D.10          | 01010      | 010101 |        | D.26          | 11010 | 010     | 110    |

| D.11          | 01011      | 110100 |        | D.27          | 11011 | 110110  | 001001 |

| D.12          | 01100      | 001101 |        | D.28          | 11100 | 001110  |        |

| D.13          | 01101      | 101100 |        | D.29          | 11101 | 101110  | 010001 |

| D.14          | 01110      | 011100 |        | D.30          | 11110 | 011110  | 100001 |

| D.15          | 01111      | 010111 | 101000 | D.31          | 11111 | 101011  | 010100 |

| not used      |            | 111100 | 000011 | K.28          | 11100 | 001111  | 110000 |

Table 2.4: Rules for  $5\mathrm{B}/6\mathrm{B}$  encoding

| Inp                    | out    | RD-             | RD+                     | Input                      |       | RD-                   | RD+  |

|------------------------|--------|-----------------|-------------------------|----------------------------|-------|-----------------------|------|

|                        | Octet  | Encoded<br>Bits |                         |                            | Octet | Encoded<br>Bits       |      |

| $\mathbf{C}\mathbf{G}$ | Bits   |                 |                         | $\mathbf{C}\mathbf{G}$     | Bits  |                       |      |

|                        | HGF    | fghj            |                         |                            | HGF   | $\operatorname{fghj}$ |      |

| D.x.0                  | 000    | 1011            | 0100                    | K.x.0                      | 000   | 1011                  | 0100 |

| D.x.1                  | 001    | 1001            |                         | K.x.1                      | 001   | 0110                  |      |

| D.x.2                  | 010    | 0101            |                         | K.x.2                      | 010   | 1010                  |      |

| D.x.3                  | 011    | 1100            |                         | K.x.3                      | 011   | 11                    | 100  |

| D.x.4                  | 100    | 1101            | 0010                    | K.x.4                      | 100   | 1101                  |      |

| D.x.5                  | 101    | 1010            |                         | K.x.5                      | 101   | 01                    | 101  |

| D.x.6                  | 110    | 0110            |                         | K.x.6                      | 110   | 1001                  |      |

| D.x.P7                 | 111    | 1110            | 0001                    | K.x.7                      | 111   | 0111                  | 1000 |

| D.x.A7                 | 111 03 | 0111            | 0111 1000               | P7 or A7 selected to avoid |       |                       | roid |

| D.A.M                  |        | 0111 1000       | 5 times 0 or 1 in a row |                            |       |                       |      |

**Table 2.5:** Rules for 3B/4B encoding

| Char | CG     | Octet Bits<br>HGFEDCBA | Encoded<br>abcdeifghj<br>RD- | Encoded<br>abcdeifghj<br>RD+ | Note                                   |  |

|------|--------|------------------------|------------------------------|------------------------------|----------------------------------------|--|

| /R/  | K.28.0 | 00011100               | 0011110100                   | 1100001011                   | Start of multiframe                    |  |

| /A/  | K.28.3 | 01111100               | 0011110011                   | 1100001100                   | Lane<br>alignment                      |  |

| /Q/  | K.28.4 | 10011100               | 0011110010                   | 1100001101                   | Start of link<br>configuration<br>data |  |

| /K/  | K.28.5 | 10111100               | 0011111010                   | 1100000101                   | Code group synchronization             |  |

| /F/  | K.28.7 | 11111100               | 0011111000                   | 1100000111                   | Frame alignment                        |  |

**Table 2.6:** Control characters used in JESD204

| Previous | Disparity of | Disparity | Next |

|----------|--------------|-----------|------|

| RD       | Code Word    | Chosen    | RD   |

| -1       | 0            | 0         | -1   |

| -1       | ±2           | +2        | +1   |

| +1       | 0            | 0         | +1   |

| +1       | ±2           | -2        | -1   |

**Table 2.7:** Rules for running disparity

# 2.7 Link Layer Operation of Receiver

The main goal of this thesis was the implementation of the link layer of the JESD204B interface on the receiver's side. Link layer processes will be described in following subsections.

## 2.7.1 Code Group Synchronization

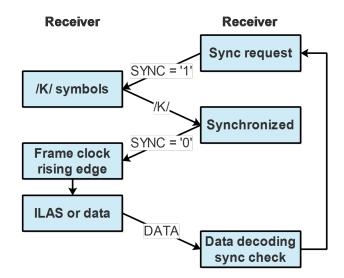

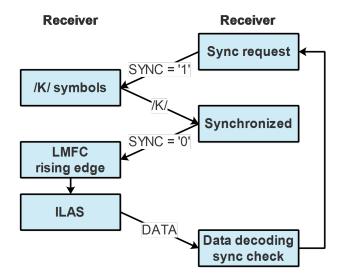

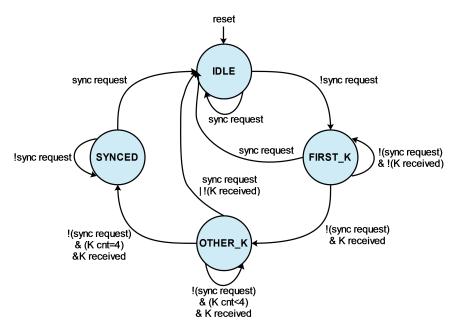

The code group synchronization is a process used to detect the start and the end of the character transmitted via the serial interface after the deserialization. This is provided by the receiving of /K/ control characters. When the receiver issues the synchronization request via the SYNC~ interface, the transmitter begins to emit the K symbols. The receiver detects the K symbols and wait until the reception of four K symbols in a row. After this, the receiver is synchronized and deasserts the SYNC~ interface. [1]

At this point, the subsequent procedures of the JESD204B are divided according to the subclasses.

For the subclass 0 transmitters are the rules as follows:

- After the detection of the deactivation of the synchronization request by all receivers, the K symbols continue to being transmitted by transceivers until the start of the next frame. [1]

- With the start of the next frame, transmitters transmit the initial lane alignment sequence (ILAS). [1]

For subclasses 1 and 2 transmitters are the rules as follows:

- After the detection of the deactivation of the synchronization request by all receivers, the K symbols continue to being transmitted by transceivers until the next local multiframe clock boundary. (There is an option to use also some later LMFC boundary by programming it so) [1]

- With the start of the next frame following the chosen LMFC boundary, transmitters begin to transmit the ILAS. [1]

#### Code Group Synchronization Check

After the achievement of the synchronicity, characters are further transmitted to the following design. Although, there is a possibility, that invalid octet is received. The invalidity can be caused by the running disparity error or code error. These errors are detected by the 8B/10B decoder. Whenever the invalid character is received, the code group synchronization enters to the check phase. During this phase, the design starts counting valid and invalid characters. There are two options, which may occur. The first option is, that three invalid characters are detected and the synchronization request is issued.

The second variant is the detection of four consecutive valid characters and entering to the normal, synchronized, phase. It must be stated, that during the checking phase characters are still proceeding to the further logic, even if the character is invalid. [1]

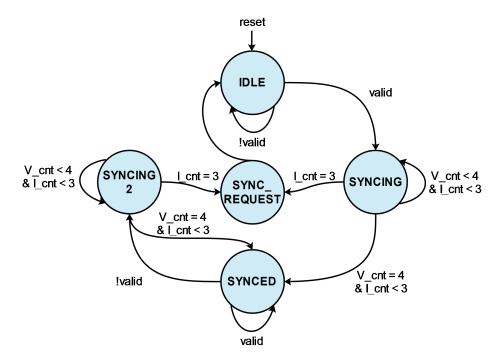

The code group synchronization process is illustrated in the figure 2.11 for the subclass 0 and in the figure 2.12 for subclasses 1 and 2 supporting the deterministic latency. [1]

Figure 2.11: Code group synchronization for subclass 0

Figure 2.12: Code group synchronization for subclasses 1 and 2  $\,$

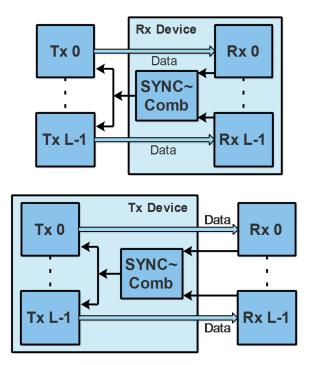

## 2.7.2 SYNC~ Signal Combining

Synchronization requests from single links can be combined into one signal when using multipoint links. Using this technique can one single receiver affect all other receivers combined by the SYNC~ interface. If one of the receivers issues a synchronization request, all transmitters begin to emit /K/ symbols. This is mandatory for subclass 0 devices, because of aligning the ILAS generation across all links. [1] The combination can be done in two possible ways:

- inside the receiver device, [1]

- inside the transceiver device. [1]

The illustration of both implementations is in the figure 2.13.

Figure 2.13: Illustration of SYNC∼ signal combining

## 2.7.3 Frame Synchronization

#### Initial Frame Synchronization

At the beginning of the link establishment, the first non /K/ symbol (also called comma) is the indication of the start of the frame. The length of the frame is defined by the number F, number of octets per frame. This means that the next rising edge of the frame clock is associated with the resetting of the octet counter. [1]

#### Alignment Characters

There are two types of alignment characters in the JESD204B. They are represented as special characters /F/=K28.7 and /A/=K28.3. The use of the /A/ character is possible only if both, transceiver and receiver, supports lane synchronization. [1]

#### Character Replacement without Scrambling

In this part, the thesis will focus on that cases, when both sides support the lane synchronization.

Rules for character replacement are as follows:

- If the octet on the last position of the frame, which is about to be transmitted, is the same octet as in the previous frame, the octet shall be replaced by the /F/ character. However, this position must not be the last octet of the multiframe. Another situation, when the /F/ character is not inserted, is, if the /F/ character was replaced in the previous frame. [1]

- Analogously, if the same octet is at the end of the multiframe, the octet is replaced by the /A/ character. This is also the case, if the /F/ was sent in the previous frame. [1]

- Receiver shall store the data from the previous frame and if the /F/ or /A/ is received, the receiver shall replace the control character with the octet stored on the same position as in the previous frame. [1]

#### Character Replacement with Scrambling

Similarly like the previous subsection, this part of the thesis will focus on that cases, when both sides support the lane synchronization.

Rules for character replacement are as follows

- If the scrambled octet on the last position of the frame, which is about to be transmitted, is equal to 0xFC, the octet shall be replaced by the /F/ character. However, this position must not be the last octet of the multiframe. [1]

- Analogously, if the scrambled octet of the value 0x7C is at the end of the multiframe, the octet is replaced by the /A/ character. [1]

- Receiver shall replace /F/ or /A/ characters with 0xFC, respectively 0x7C, on the input of the descrambler. [1]

## Frame Alignment Correction

The frame realignment is realized as follows:

- If two alignment characters are received at the same position, which is not as expected for the current frame align, without an interruption of the alignment character at the correct position, the realignment is done in the accordance to detected two alignment characters. [1]

- If the lane alignment is issued, it indicates a "cross coupling" and there is no need for waiting for two alignment characters as in the previous point. The frame realignment is realized after detecting one alignment character. [1]

- There shall be an option to disable the process described in the previous points on the receiver's side. Realignment could be problematic, if not enough alignment characters are emitted or if the realignment could cause the lane alignment and latency error. [1]

## 2.7.4 Lane Synchronization

#### Initial Lane Synchronization

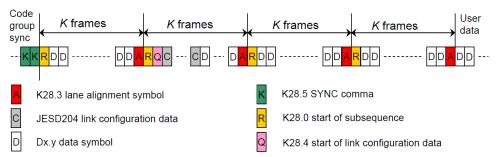

Before the reception of the user data, the initial lane alignment must be achieved. The initial lane alignment sequence (ILAS) usually consists of 4 multiframes (in some cases it can be up to 256 multiframes, this must me programmable). Each of the multiframe is started with the /R/ character and ended with the /A/ control character. Because of the possible difference in the lane delays, this character can be received at a different time. After the reception of the first /R/ character, each receiver start to store the incoming data in the buffer and they raise the "ready" flag. When all receivers have detected the first /R/ character and raised their flags, they start to propagate the stored data from the buffer for a further logic processing. In addition, the multiframe consists of K frames. The K is ranging form 1 to 32 frames and this value shall be also programmable. [1]

During the ILAS, each multiframe is introduced by the /R/ control character and ended with the /A/ control character. The second multiframe is specific. It transmits configuration information about the JESD204B link. These information are introduced with the /Q/ control character. The figure 2.14 is showing the ILAS with four multiframes.

Meanings of parameters transmitted during the ILAS are summarized in the table 2.8.

Figure 2.14: Initial lane alignment sequence with four multiframes [1]

#### Lane Alignment Monitoring and Correction

After ILAS, the payload of user data begins to transmit over the JESD204B link. At this time, the lane alignment is monitored and eventually corrected. It is made by means of monitoring the arrivals of /A/ characters. [1]

The rules for the dynamic realignment are analogous to those ones presented for the frame realignment:

- If two /A/ characters are received at the same position, which is not as expected for the current lane align, without an interruption of the /A/ character at the correct position, the realignment is done in the accordance to detected /A/ characters. [1]

- If the frame alignment is issued and it indicates a "cross coupling", there is no need for waiting for two /A/ characters as in te previous point. The lane realignment is realized after detecting one /A/ character. [1]

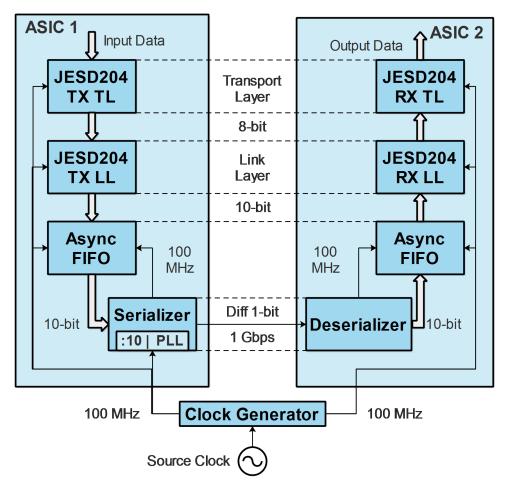

# 2.8 Implementation of JESD204 protocol in ASIC

The main goal of this thesis was to develop a receiving link layer of the JESD204B protocol suitable for use in an ASIC. The implementation in an ASIC of the whole data path from the JESD204 transmitter to the receiver is shown in the figure 2.15. The configuration with one lane and 100 MHz frequency is presented. Input data are mapped into octets in the transport layer of the JESD204 protocol. Octets are proceeded to the link layer, where data are coded by 8B/10B coding scheme and optionally scrambled. Data are subsequentially written to the asynchronous FIFO from where are read by a serializer, which is an analog circuit used for serializing the data. An asynchronous FIFO is a device used to cross clock domains. Serial bits are then differentially transmitted from the transmitting ASIC to the receiving ASIC. Data are there describilized and via another asynchronous FIFO provided to the receiving JESD204 link layer. Data are there descrambled and decoded and in the transport layer demapped from octets. The clocking source is common for both ASICs and each ASIC is provided with its own device clock for JESD204 devices.

Figure 2.15: Illustration of example implementation of JESD204 in ASIC

# 2.9 Xilinx Multigigabit Transceiver

The pressure at increasing transfer speeds over long distances using fewer wires has led to the use of multi-gigabit transceivers (MGT). Multi-gigabit transceiver is a digital SerDes device, which can operate at serial rates higher than 1 Gb/s. In the case of vision of a deployment of the JESD204B receiver developed in this thesis in the Nexys Video FPGA with built in Artix@-7 XC7A200T chip made by Xilinx, we talk about the 7 series FPGAs GTP transceiver. [11] There is no possibility of implementing an analog SerDes in FPGA.

As Xilinx declare, the 7 series FPGAs GTP transceiver is a power-efficient transceiver, supporting line rates between 500 Mb/s and 6.6 Gb/s. The maximum rate is limited by a particular device. [11]

The key elements within the GTP RX transceiver are: [11]

- Analog Front End

- Out-of-Band Signalling

- Equalizer

- Clock Data Recovery

- Fabric Clock Output Control

- Margin Analysis

- Polarity Control

- Pattern Checker

- Byte and Word Alignment

- 8B/10B Decoder

- Elastic Buffer

- Gearbox

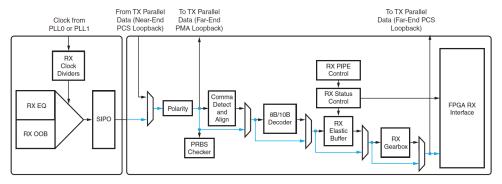

Many of them are irrelevant for the use with the designed JESD204B receiver and are bypassed. The block diagram of the GTP transceiver is displayed in the figure 2.16. The blue line illustrates the use case for this thesis.

Figure 2.16: GTP RX Transceiver Block Diagram [11]

## 2.10 Receiving Side of JESD204 Protocol on FPGA

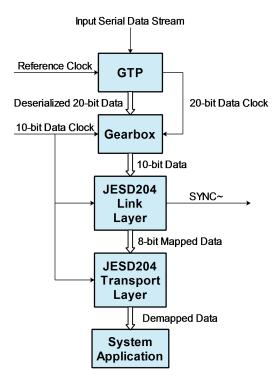

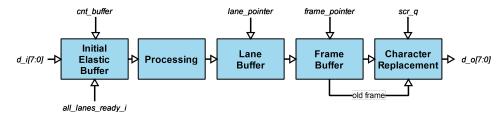

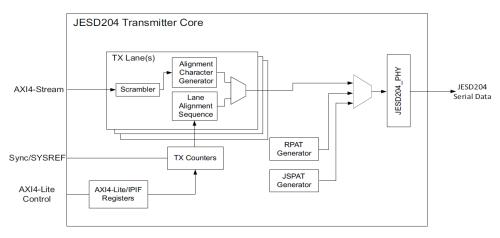

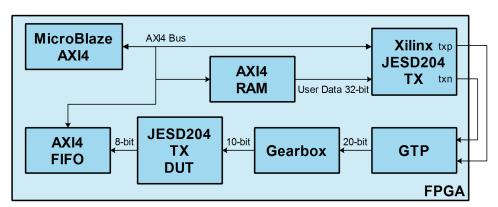

In the figure 2.17 there is a visualisation of the receiving side of the JESD204 system on a FPGA. Bit widths displayed are corresponding to the configuration with one lane per link. The first block in the chain is a multigigabit transceiver, because on a FPGA there can not be any analog SerDes implemented. It is supplied with a reference clock of the declared frequency. In case of this thesis, it just descrializes the data stream into 20-bit wide words. These words with a corresponding clock signal are then transmitted to the gearbox. This block is used for a conversion of the 20-bit data into 10-bit words synchronized to the second clock domain provided, because the receiver in this thesis was designed for a 10-bit input. The gearbox block is described further in the subsection 3.3.3. The 10-bit wide data with the corresponding clock domain are then transmitted to the designed block, the receiving link layer of the JESD204B protocol. Operations presented in sections above are performed there. The module is outputting the data octets. In the JESD204 protocol, the transport layer is responsible for demapping the data from octets and the data are then provided for a particular application.

**Figure 2.17:** Illustration of receiving side of JESD204 protocol implemented on FPGA

## 2.11 Verilog

A few words about Verilog language will follow. Verilog belongs to a group of HDL (Hardware Description Language) languages used to design PLD (Programmable Logic Device), FPGA applications and also ASICs (Application Specific Integrated Circuits). Another language of this kind is VHDL or SystemVerilog. Both Verilog and VHDL were originally developed for simulation and documentation purposes, not for synthesis. Many of their constructs have signs of it and are not synthesizable, while are dedicated for modelling. [10]

The basic characteristics of the Verilog language are listed below [10]:

- Open standard There is no requirement for a license from the owner to build a design, unlike some other HDL languages.

- Device independent design They allow the designer to work without selecting the target circuit first.

- Portability It is possible to simulate the designed circuit based on the same source text, which will then be used for the synthesis and implementation in the target circuit. The source code can be processed in various simulators and in synthesizers from various manufacturers. The simulated text can then be used in various target circuits in the future, which is made possible by the fact that Verilog supports the hierarchical structure of projects, where the created system consists of subblocks.

- ASIC compatibility In case of successful launch on the market, the description of the design in HDL languages can be used as a basis for its implementation in the ASIC circuit suitable for large series.

The basic version of Verilog was adopted as IEEE (*Institute of Electrical and Electronics Engineers*) Standard No. 1364 in 1995. Constructs conforming to this standard are referred to as Verilog-95 constructs. Based on the experience with this version, a new version was adopted in 2001, Verilog-2001. A number of modifications and improvements have been made to this version and are supported by most current design systems. And in this version is also written this diploma thesis. [10]

| Parameter     | Description                        | Range | Value      |  |

|---------------|------------------------------------|-------|------------|--|

|               | Number of adjustment resolution    | _     |            |  |

| ADJCNT        | steps to adjust DAC LMFC           | 0-15  | Binary     |  |

|               | Subclass 2 only                    |       |            |  |

|               | Direction to adjust DAC LMFC       |       |            |  |

| ADJDIR        | 0 – Advance                        | 0-1   | Binary     |  |

|               | 1 – Delay                          | 0-1   | Dinary     |  |

|               | Subclass 2 only                    |       |            |  |

| BID           | Bank ID - Extension to DID         | 0–15  | Binary     |  |

| CF            | Number of control words            | 0-32  | Binary     |  |

|               | per frame clock per link           |       | Dinary     |  |

| CS            | Number of control bits per sample  | 0–3   | Binary     |  |

| DID           | Device (= link) ID number          | 0-255 | Binary     |  |

| F             | Number of octets per frame         | 1-256 | Binary – 1 |  |

| HD            | High Density format                | 0-1   | Binary     |  |

|               | JESD204 version                    |       |            |  |

| JESDV         | 000 - JESD204A                     | 0-7   | Binary     |  |

|               | 001 - JESD204B                     |       |            |  |

| K             | Number of frames per multiframe    | 1–32  | Binary – 1 |  |

| $\mid L \mid$ | Number of lanes per                | 1-32  | Binary – 1 |  |

|               | converter device (link)            |       | Ü          |  |

| LID           | Lane ID number (within link)       | 0-31  | Binary     |  |

| M             | Number of converters per device    | 1-256 | Binary – 1 |  |

| N             | Converter resolution               | 1–32  | Binary – 1 |  |

| N'            | Total number of bits per sample    | 1–32  | Binary – 1 |  |

| PHADJ         | Phase adjustment request to DAC    | 0-1   | Binary     |  |

|               | Subclass 2 only                    | 0 1   | Billary    |  |

| $\mid S \mid$ | Number of samples per              | 1–32  | Binary – 1 |  |

|               | converter per frame cycle          |       |            |  |

| SCR           | Scrambling enabled                 | 0-1   | Binary     |  |

|               | Device Subclass Version            |       |            |  |

| SUBCLASSV     | 000 - Subclass 0                   | 0-7   | Binary     |  |

| SOBCERIOS     | 001 – Subclass 1                   |       | Dinary     |  |

|               | 010 – Subclass 2                   |       |            |  |

| RES1          | Reserved field 1                   | 0-255 | Binary     |  |

| RES2          | Reserved field 2                   | 0-255 | Binary     |  |

| CHKSUM        | Checksum $\sum$ (all above fields) | 0-255 | Binary     |  |

|               | mod 256                            | 0 200 | Zinary     |  |

**Table 2.8:** Link configuration parameters [1]

## Chapter 3

# Development of Receiving Link Layer of JESD204B Protocol

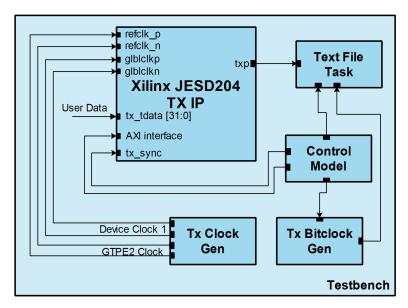

At the beginning of the chapter, there will be presented tools, which were used for the development of the design, for the behavioral simulation and also for the verification.

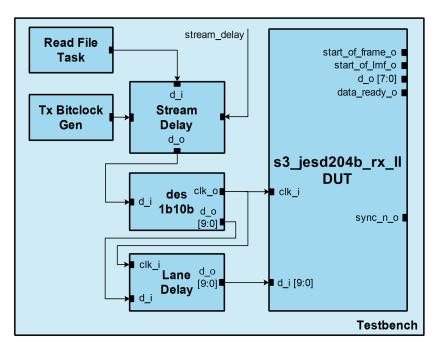

This chapter will further cover information about designed receiver itself. Then subblocks resulting in the desired receiver will be described. To make the explanation easier, the use with only one serial lane will be covered (unless otherwise stated), but the design is supporting the cases with more serial lanes between the transmitter and receiver.

A section about the verification process will follow. There will be presented simulations, which were done during the development. Subsections will gradually guide through particular steps of the simulation process. Several modules, which were designed for the simulation purposes, will be described.

The fourth section is dealing with the physical representation of the designed block representing the link layer of the JESD204B receiver. The utilization inside the Xilinx FPGA xc7a200tsbv484-1 and for ASIC realized in the TSMC 28HPC+ technology will be outlined.

The last section is in short describing the validation in the chosen FPGA. Mainly the idea of this operation is discussed.

It must be stated that after a discussion with the supervisor of the thesis it was decided to implement only the subclass 0 of the JESD204B receiver and it was done due to the time pressure before the submitting of the thesis. For this reason, only subclass 0 will continue to be discussed in the work, and all blocks are fully compatible only with this subclass.

## 3.1 Development Tools

During the design flow of the JESD204B several tools were used. The first one was Vivado Design Suite 2020.1, see subsection 3.1.1, the second on was ModelSim PE Student Edition 10.4a, see subsection 3.1.2 and the last one was Cadence Xcelium, see subsection 3.1.3.

#### 3.1.1 Vivado Design Suite 2020.1

The first development tool was XIlinx Vivado Design Suite in version 2020.1. Vivado Design Suite is a development environment from the Xilinx company for a synthesis and analysis that supports both VHDL and Verilog languages. It includes many tools that allow developers to properly debug Xilinx's FPGA or CPLD circuitry. This software is free to download in its HL WebPACK<sup>TM</sup> Edition. [9] At first, the premise was to utilize this tool for everything, because it is suitable for the code development, for the simulations and also for the verification with Xilinx IP intellectual property cores. However, it was found that simulations are too much time consuming even with just the original design and for simulations with Xilinx IP cores it was only hardly usable. So it was decided to write the design and do the basic simulations in another software described below in subsection 3.1.2. The chosen tool was ModelSim PE in its Student Edition 10.4a.

Another problem related with Vivado and the migration to ModelSim was the import of Xilinx IP cores to ModelSim. After some research was found, that the current version of the Vivado, which had to be used in case of generating the JESD204B Tx IP core, is not compatible with the most recent student version of ModelSim in order to transfer the IP core to the ModelSim. This fact led to the simultaneous design and simulation in both programs.

#### 3.1.2 ModelSim PE Student Edition 10.4a

ModelSim delivered by Mentor Graphics is an alternative to Vivado in means of the developing and simulating the digital design, but for the needs of this thesis its performance was in simulations much more effective. But of course it has its limitations explained above. So, for the simulations purposes it was necessary to generate the data stream from the Xilinx IP core, save it to the text file and and then work with this file within the ModelSim environment.

#### 3.1.3 Cadence Xcelium

In the end of the development of the receiver, another tool was used and it was Cadence Xcelium. Access to this software was provided by Dialog Semiconductor company. The use of this tool was necessary especially when simulating the system with all Xilinx IP cores. This means when using reference Xilinx JESD204 IP core and Xilinx GTP IP core. In that case, it offers a much better performance than other tools used.

## 3.2 Design

The section will describe the designed top module and also several submodules, of which the receiver consists. The beginning will be devoted to the top module and the rest of the section will be about submodules. Blocks will be presented both from the outside and their internal arrangement and behaviour.

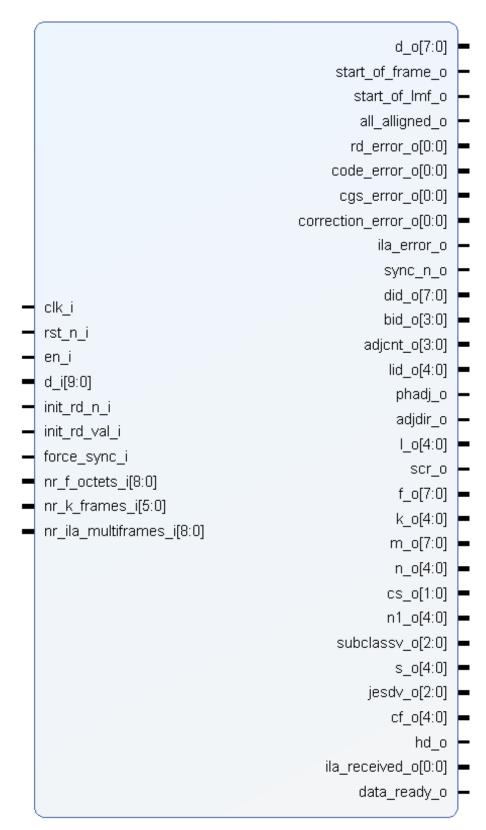

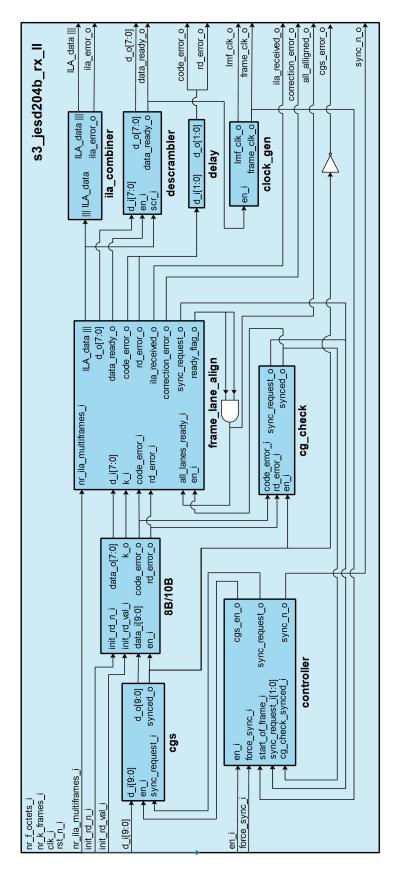

#### 3.2.1 Top Module of Receiving Link Layer of JESD204B

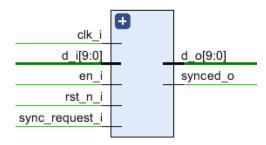

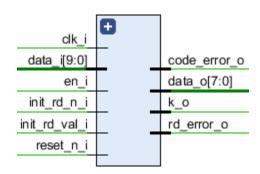

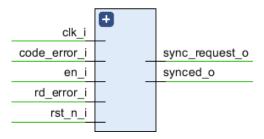

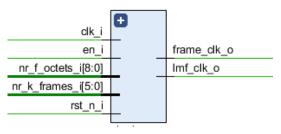

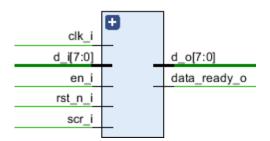

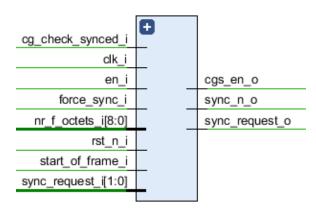

This subsection is presenting the top module, which is the desired designed JESD204B receiver, respectively its link layer part. The illustration for one lane configuration of it is in the figure 3.1. The table 3.2 is summarizing the meanings of input and output ports of the block. It should be stated, that it was decided for an implementation of 10-bit wide input data for a particular lane. This has been done due to the fact, that it is the simplest variant, however other possibilities are also suitable, for instance parallel processing of multiple data words. Finally, the figure 3.2 is displaying simplified internal structure of the design block. Input ports  $clk\_i$  and  $rst\_n\_i$ are not routed in the picture, but in fact they are delivered to all of the submodules. Input ports  $nr_f_ostets_i$  and  $nr_k_frames_i$  are not routed too, however they are delivered to submodules frame lane align, clock gen and only nr f ostets i to controller. Also output ports of ILA configuration data are simplified. They are packed into one port called ILA\_data. For detailed information about output ports see the table 3.2. For a configuration with multiple lanes, some of the submodules are shared for all lanes a some of them are instantiated for separate lanes. The table 3.1 is summarizing the information about this use.

| Submodule            | Shared / Separate |

|----------------------|-------------------|

| controller           | Shared            |

| cgs                  | Separate          |

| $s3\_8b10b\_decoder$ | Separate          |

| $cg\_check$          | Separate          |

| $frame\_lane\_align$ | Separate          |

| $ila\_combiner$      | Shared            |

| descrambler          | Separate          |

| clock_gen            | Shared            |

| delay                | Separate          |

**Table 3.1:** Description of sharing submodules in multiple lane configuration

The module must be instantiated with parameters to ensure the correct functioning. Meanings and ranges of the parameters are as in the table 3.3.

**Figure 3.1:** Graphical representation of designed JESD204B receiver for  $NR\_OF\_LANES = 1$

| Ports                         | I/O    | Description                                                               |

|-------------------------------|--------|---------------------------------------------------------------------------|

| clk_i                         | Input  | Clock input                                                               |

|                               |        | Reset signal, active low,                                                 |

| $rst\_n\_i$                   | Input  | asynchronously asserted,                                                  |

|                               | _      | synchronously deasserted                                                  |

| en_i                          | Input  | Enable signal                                                             |

| d_i[(L*10)-1:0]               | Input  | Input serialized 10-bit data                                              |

| init_rd_n_i                   | Input  | Running disparity initialization request, active low                      |

| $init\_rd\_val\_i$            | Input  | Initial value of running disparity                                        |

| force_sync_i                  | Input  | Input for issuing force resynchronization                                 |

| $nr\_f\_octets\_i$            | Input  | No. of octets per frame                                                   |

| $nr\_k\_frames\_i$            | Input  | No. of frames per multiframe                                              |

| $nr\_ila\_multiframes\_i$     | Input  | No. of ILAS multiframes                                                   |

| d_o[(L*8)-1:0]                | Output | Output 8-bit data                                                         |

| start_of_frame_o              | Output | Start of frame indicator, active high                                     |

| start_of_lmf_o                | Output | Start of multiframe indicator, active high                                |

| $all\_alligned\_o$            | Output | Indicator that all lanes are alligned, active high                        |

| rd_error_o[L-1:0]             | Output | Running disparity error output,<br>specific for each lane,<br>active high |

| $code\_error\_o[L-1:0]$       | Output | Code error output,<br>specific for each lane,<br>active high              |

| $cgs\_error\_o[L-1:0]$        | Output | Indicator of non-synchronized code group synchronization, active high     |

| ila_error_o                   | Output | Parameters detected during ILAS are not equal on all lanes, active high   |

| $correction\_error\_o[L-1:0]$ | Output | Indicator of overflowed correction<br>buffer, active high                 |