CZECH TECHNICAL UNIVERSITY IN PRAGUE FACULTY OF ELECTRICAL ENGINEERING DEPARTMENT OF MICROELECTRONICS

## Improvements in the Electrical Performances of MOSFETs in Integrated Circuits by Physical Mask Design

DOCTORAL THESIS

## ING. DALIBOR BARRI

PRAGUE, DECEMBER 2020

Ph.D. Programme: P 2612 Electrical Engineering and Information Technology Branch of Study: 2612V015 Electronics

Supervisor: doc. Ing. Jiří Jakovenko, Ph.D.

## STATEMENT OF ORIGINAL AUTHORSHIP

The work contained in this thesis has not been previously submitted to meet requirements for an award at this or any other higher education institution. To the best of my knowledge and belief, the thesis contains no material previously published or written by another person except where due reference is made.

in Prague, .....

.....

Dalibor Barri

### ACKNOWLEDGMENTS

I would like to thank my supervisor doc. Ing. Jiří Jakovenko, Ph.D., for professional guidance, valuable comments, and especially for willingness and patience in consultation. I would like to thank also my colleagues from CTU in Prague. Especially to doc. RNDr. Jan Voves, CSc., for his consultations and great cooperation. Furthermore, I would like to thank to my colleagues from STMicroelectronics for their patience and valuable expertise Special thanks Ing. Patrik Vacula, Ph.D., thev have provided me. to Ing. Vlastimil Kotě, Ph.D., for their ideas, consultations, and great cooperation. Also, I want to thanks to Ing. Milan Andrle, Ph.D., Ing. Tomáš Grešl, and Ing. Petr Švancara for technical support with measurement. Last but not least, I would like to thank my wife Lenka, my daughter Nikolka and the whole family, especially my grandmother Milada and my mother Soňa, for their overall sustained support during the time of my work.

### ABSTRACT

At present, the criteria for ecology and vital environment protection are rigorous and must be respected. However, despite the established rules, our initiative can prevent potential life disasters, as it is in this doctoral thesis. Living in a healthy environment is essential for all of us, and therefore this thesis focuses on research into improvements in the electrical properties of integrated fieldcontrolled transistors (MOSFET), which will ultimately reduce both environmental pressure and financial costs in the production of integrated circuits (IC). Reducing manufacturing costs and pressure on the environment is achieved by using smaller silicon wafer surfaces while retaining the original chip functionality. This is achieved by using the advanced diamond layout shape (DLS) gate pattern of MOS transistors (DLS MOSFETs) on the IC chip design that is subject of this thesis.

In this thesis, there are presented three innovative crucial knowledge of the DLS MOSFETs, such us novel analytical descriptions of the effective aspect ratio of DLS MOSFET, the way how to improve electrical performances of the MOSFETs, and the new precise model of the effective threshold voltage changes in the DLS MOSFETs. All these points are essential for the high-quality level design of integrated circuits with DLS MOSFETs and are defined for the first time in this thesis.

The new innovative approach of the effective aspect ratio calculation is based on the Schwarz-Christoffel (SC) transformation. It has been observed and proved by numerical calculations, 3D TCAD simulations, and measurements that the newly presented approach achieves much better results than already one existing method based on the longitudinal (parallel) corner effect (LCE) and parallel association of MOSFET with different channel length effect (PAMDLE). The measures have also demonstrated both the mentioned improvements and the effective threshold voltage changes in the DLS MOSFETs, respectively, where 1 124 samples in 160 nm BCD technology have been fabricated for this purpose.

### Abstrakt

V současnosti jsou kritéria na ekologii a ochranu životního prostředí velmi přísná a je nezbytné je dodržovat. Avšak, i navzdory zavedeným pravidlům, vlastní iniciativou můžeme předcházet možným životním katastrofám, jako je tomu v této doktorské práci. Žít v zdravém životním prostředí je důležité pro každého z nás, a proto se tato práce zaměřuje na výzkum v oblasti vylepšení elektrických vlastností integrovaných polem řízených tranzistorů (MOSFET), která v konečném důsledku sníží, jak tlak na životní prostředí, tak i finanční náklady při výrobě integrovaných obvodů (IO). Snížení výrobních nákladů a tlaku na životní prostředí je dosaženo použitím menších ploch křemíkových desek při zachování původní funkčnosti čipu. Toho je dosaženo použitím pokročilých kosočtvercových topologií MOS tranzistorů (DLS MOSFETů) na integrovaném čipu, která jsou předmětem této práce.

V této práci jsou představeny tři zásadní inovativní znalosti týkajících se DLS MOS transistorů, kterými jsou: nové analytické popsání efektivního poměru stran DLS MOSFETů, navržené řešení jak zlepšit elektrické vlastností u MOSFETů a nový přesný model efektivních změn prahového napětí v DLS MOSFETech. Všechny výše zmíněné body jsou zásadní pro vysoce kvalitní návrh integrovaných obvodů s DLS MOSFETy a jsou prvně publikovány v této práci.

Nový inovativní přístup výpočtu efektivního poměru stran je založen na Schwarz-Christoffelově (SC) transformaci. V této práci je jak číselnými výpočty či 3D TCAD simulacemi, tak i měřením pozorováno a prokázáno, že nově prezentovaný přístup dosahuje lepších výsledků, než-li tomu je u jiného přístupu založeným na podélných paralelních rohových jevech (LCE) a paralelních asociaci MOSFETů s různou délkou kanálu (PAMDLE). Měření na reálných vzorcích také prokázala, jak zmíněné vylepšení, tak i změny efektivního napětí v DLS MOSFETech. Za tímto účelem bylo vyrobeno 1 124 vzorků v 160nm BCD technologickém procesu.

### KEYWORDS

diamond layout shape MOSFET (DLS MOSFET), electrical performance of MOSFETs in integrated circuit, MOSFET effective aspect ratio  $(W/L)_{\text{eff}}$ , effective threshold voltage ( $V_{\text{th,eff}}$ ), rectangular layout shape MOSFET (RLS MOSFET), Schwarz–Christoffel transformation (SC transformation)

## Klíčová slova

diamantový tvar rozložení MOS transistoru (DLS MOSFET), elektrický výkon MOSFETů v integrovaném obvodu, efektivní poměr stran (W/L)<sub>eff</sub> u MOSFETů, efektivní prahové napětí ( $V_{\rm th,eff}$ ), obdélníkový tvar rozložení MOSFET (RLS MOSFET), Schwarz–Christoffelova transformace (SC transformace)

"Creativity is intelligence having fun." - Albert Einstein

## TABLE OF CONTENTS

| STAT | MENT OF ORIGINAL AUTHORSHIP                                | iii  |

|------|------------------------------------------------------------|------|

| Ack  | OWLEDGMENTS                                                | v    |

| ABST | ACT                                                        | vii  |

| ABST | АКТ                                                        | ix   |

| Key  | ORDS                                                       | xi   |

| Tabi | OF CONTENTS                                                | xv   |

| LIST | f Figures                                                  | xix  |

| List | F TABLES                                                   | xxv  |

| LIST | F ABBREVIATIONS                                            | xxvi |

| Сна  | fer 1: Introduction                                        | 1    |

| 1.1  | IOTIVATION                                                 | 1    |

| 1.2  | Thesis Outline                                             | 4    |

| 1.3  | AIMS OF THIS THESIS                                        | 5    |

| 1.4  | AUTHOR'S SCIENTIFIC CONTRIBUTIONS                          | 6    |

| 1.5  | TATE OF THE ART                                            | 8    |

| Сна  | TER 2: TECHNICAL BACKGROUND                                | 17   |

| 2.1  | PROBLEMS IN SCALING                                        | 19   |

|      | .1.1 Constant Field Scaling Theory                         | 23   |

|      | .1.2 GATE OXIDE VARIATION                                  | 24   |

|      | .1.3 Short Channel Effect (SCE)                            | 28   |

|      | .1.4 Drain-Induced Barrier Lowering (DIBL)                 | 30   |

|      | .1.5 SCE + DIBL                                            | 32   |

|      | .1.6 GATE-INDUCED SOURCE AND DRAIN LEAKAGE (GISL AND GIDL) | 35   |

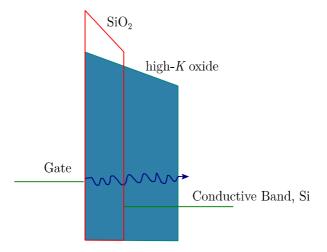

|      | .1.7 High-K Dielectrics                                    | 37   |

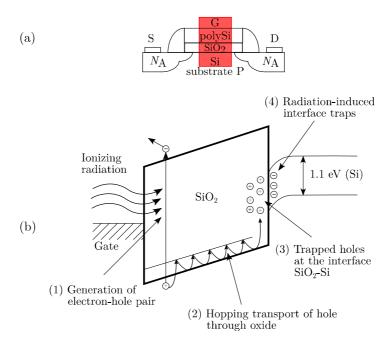

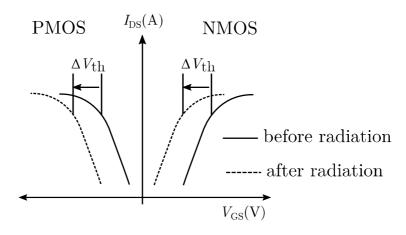

|      | .1.8 Total Ionizing Dose (TID) Effect                      | 39   |

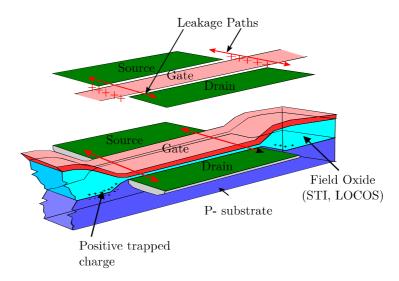

|      | .1.9 Hump Effect                                           | 42   |

| 2.2  | Review of Different MOSFET Gate Shape Architectures        | 44   |

|      | .2.1 Enclosed Layout Shape Topologies                      |      |

|     |       |       | Rectangular enclosed layout topology                       |      |

|-----|-------|-------|------------------------------------------------------------|------|

|     |       | . ,   | OCTAGONAL ENCLOSED LAYOUT TOPOLOGY                         |      |

|     |       | (D)   |                                                            |      |

|     |       | (E)   | CIRCULAR ENCLOSED LAYOUT TOPOLOGY                          |      |

|     |       |       | CIRCULAR ENCLOSED LAYOUT TOPOLOGY WITH OVERLAPPING         |      |

|     |       | (G)   | Application                                                | 55   |

|     | 2.2.2 | Νот   | E ENCLOSED LAYOUT SHAPE TOPOLOGIES                         | . 57 |

|     |       | (A)   | DIAMOND GATE LAYOUT SHAPE BASED ON THE "LONGITUDINAL COR   |      |

|     |       |       | EFFECT"                                                    |      |

|     |       | · /   | Ellipsoidal Gate Shape                                     |      |

|     |       | · /   | WAFFLE GATE SHAPE                                          |      |

|     |       | ( )   | WAVE SHAPE                                                 |      |

|     |       | (E)   | Z GATE SHAPE                                               | 66   |

|     | 2.2.3 |       | " LAYOUT SHAPE TOPOLOGIES                                  |      |

|     |       | ` '   | Cylindrical Gate Shape                                     |      |

|     |       | (B)   | TRAPEZOIDAL GATE SHAPE                                     | 70   |

| Сни | APTER | 3:    | Research Design of the DLS MOSFET                          | . 73 |

| 3.1 | Метн  |       | logy and Research Design                                   | 74   |

| 0.1 |       |       |                                                            |      |

|     | 3.1.1 |       | THODOLOGY                                                  |      |

|     |       | · · / | Symbolic-numerical computation                             |      |

|     |       | · /   | NUMERICAL COMPUTATIONS                                     |      |

|     |       |       | 3D DEVICE SIMULATIONS TOOL                                 |      |

|     |       | (D)   | EXPERIMENTAL MEASUREMENTS                                  | 75   |

|     | 3.1.2 | Res   | EARCH DESIGN                                               | . 76 |

| 3.2 | Instr | UME   | NTS                                                        | . 77 |

|     | 3.2.1 | Sof   | TWARE                                                      | 77   |

|     |       | (A)   | Symbolical and numerical calculations                      | 77   |

|     |       | (B)   |                                                            |      |

|     |       | (C)   |                                                            |      |

|     |       | (D)   | Physical mask design                                       | 80   |

|     |       | · · / | Post-processing and support programming                    |      |

|     | 3.2.2 | Sili  | CON WAFER                                                  | . 82 |

|     | 3.2.3 | Lab   | ORATORY EQUIPMENT                                          | 85   |

|     |       |       | Advanced wafer probing machine (Cascade Microtech 1200)    |      |

|     |       | ` '   | PROBE CARD                                                 |      |

|     |       | (C)   | Precision semiconductor parameter analyzer (Agilent 4156C) | 87   |

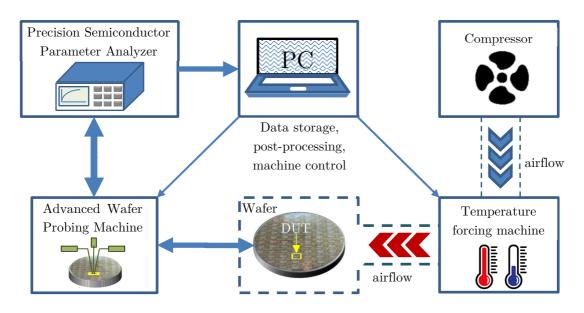

| 3.3 | Anal  | YSIS  | Setup                                                      | . 89 |

|     | 3.3.1 | Num   | MERICAL COMPUTATION SETUP                                  | 89   |

|     | 3.3.2 | Sim   | ULATION SETUP                                              | 89   |

|     | 3.3.3 | Mea   | ASUREMENT SETUP                                            | 91   |

|     |       |       |                                                            |      |

| Сна | PTER  | 4: Results, Analyses, and Discussions                                                                   |

|-----|-------|---------------------------------------------------------------------------------------------------------|

| 4.1 |       | YTICAL DESCRIPTIONS OF THE EFFECTIVE ASPECT RATIO OF DLS<br>FETS                                        |

|     | 4.1.1 | INTRODUCTION                                                                                            |

|     | 4.1.2 | THE INNOVATIVE ANALYTICAL DESCRIPTION OF THE DLS MOSFET BASED ON THE SCHWARZ-CHRISTOFFEL TRANSFORMATION |

|     | 4.1.3 | The Verification Methodology of the Innovative Expression<br>using MATLAB SC Toolbox                    |

|     | 4.1.4 | The Analytical Description of the DLS MOSFET Based on the LCE and PAMDLE                                |

|     | 4.1.5 | Results, Discussion and Comparison105                                                                   |

|     | 4.1.6 | Summary                                                                                                 |

| 4.2 |       | DVEMENTS IN THE ELECTRICAL PERFORMANCES OF THE DLS MOSFET<br>HYSICAL MASK DESIGN                        |

|     | 4.2.1 | INTRODUCTION                                                                                            |

|     | 4.2.2 | THEORETICAL DRAIN CURRENT ENHANCEMENT GIVEN BY SCHWARZ-<br>CHRISTOFFEL TRANSFORMATION OF THE DLS110     |

|     | 4.2.3 | 3D TCAD Simulations of the Drain-Source Current Enhancement                                             |

|     | 4.2.4 | Experimental Measurement of the Drain-Source Current<br>Enhancement In 160 nm BCD Technology Process    |

|     | 4.2.5 | <ul> <li>RESULTS, DISCUSSION AND COMPARISON</li></ul>                                                   |

|     | 4.2.6 | Summary                                                                                                 |

| 4.3 |       | ISE MODEL OF THE EFFECTIVE THRESHOLD VOLTAGE CHANGES IN THE MOSFETS                                     |

|     | 4.3.1 | INTRODUCTION                                                                                            |

|     | 4.3.2 | Threshold Voltage: Theoretical Background127                                                            |

|     | 4.3.3 | 3D TCAD Simulations of the Threshold Voltage129                                                         |

|     | 4.3.4 | Experimental Measurement of the Threshold Voltage132                                                    |

|     | 4.3.5 | Results, Discussion and Comparison                                                                      |

|     | 4.3.6 | SUMMARY                                                                                                 |

| Сна  | PTER 5: CONCLUSIONS AND SCOPE FOR FUTURE WORK 1 | 41  |

|------|-------------------------------------------------|-----|

| 5.1  | Conclusions                                     | 141 |

| 5.2  | Future Work                                     | 145 |

| 5.3  | FINAL WORDS                                     | 146 |

| Віві | IOGRAPHY 1                                      | .47 |

| Арр  | ENDIX A: LIST OF AUTHOR'S PUBLICATIONS 1        | 73  |

| Арр  | ENDIX B: RECOGNITIONS AND REVIEW 1              | 77  |

## LIST OF FIGURES

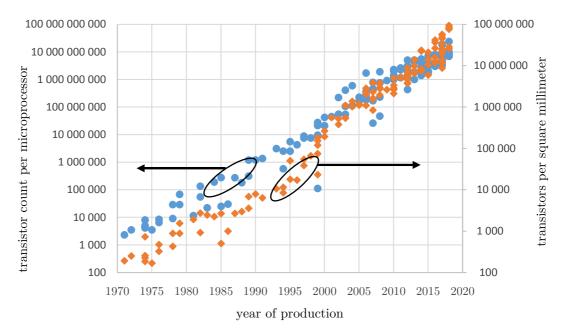

| Fig. 2.1: Transistor count per different microprocessors of many vendors (blue<br>circle symbol), transistor per square millimeter of different<br>microprocessors of many vendors (orange diamond symbol), data<br>from [61]                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

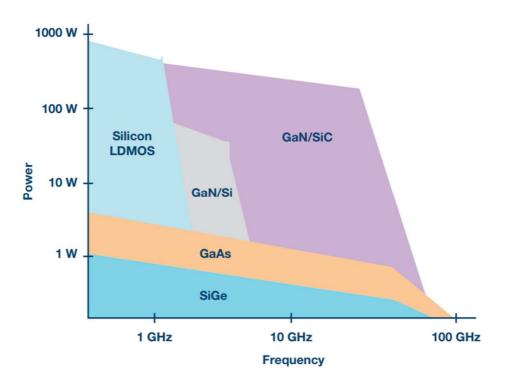

| Fig. 2.2: A process technology comparison of microwave frequency range<br>power electronics [69]                                                                                                                                                                                                                                           |

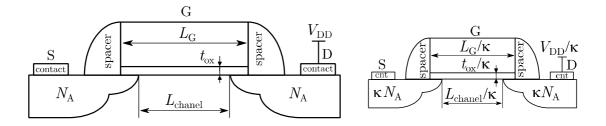

| Fig. 2.3: Illustration of MOSFET miniaturization. The sketch on the right hand is the scaled device according to the constant field rule 23                                                                                                                                                                                                |

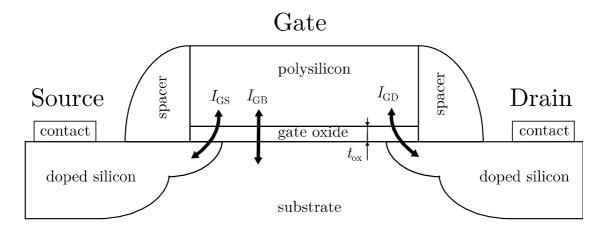

| Fig. 2.4: The overall gate tunneling current is the sum all the components tunneling current namely the gate-to-source, gate-to-drain and gate-to-substrate currents                                                                                                                                                                       |

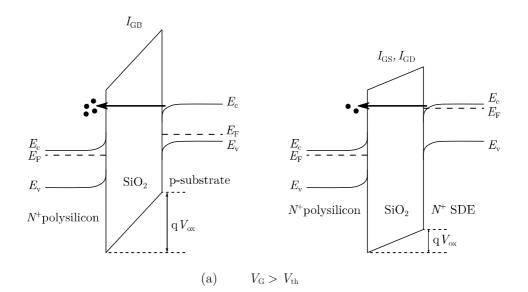

| Fig. 2.5: Gate bias dependent band diagrams and electron tunnelling in the channel $(I_{\rm GB})$ and the gate edge $(I_{\rm GS}$ and $I_{\rm GD})$ ; (a) $V_{\rm G} > V_{\rm th}$ (inversion mode), (b) $V_{\rm FB} < V_{\rm G} < 0$ V (depletion mode)27                                                                                 |

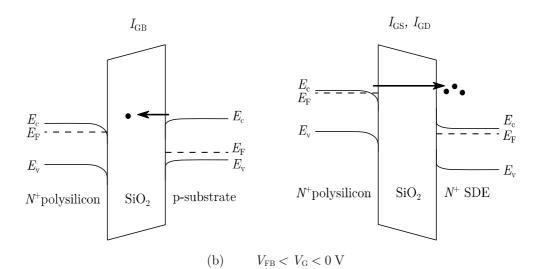

| Fig. 2.6: Problems in scaling of the gate oxide thickness leads to higher leakage gate current, and different breakdown voltage                                                                                                                                                                                                            |

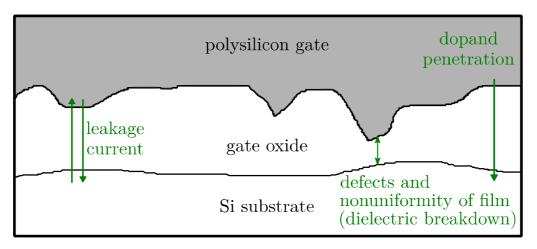

| Fig. 2.7: Charge sharing in a long channel (a) and short channel (b) of<br>MOSFET. In the case of the short channel, there is shown sub-<br>surface punch-trough. It means, the depleted regions around the<br>drain and source terminals, causing current to flow irrespective of<br>gate voltage (i.e. even if the gate voltage is zero) |

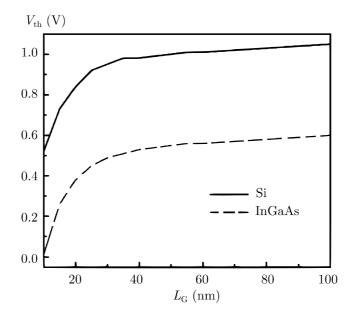

| Fig. 2.8: An example of threshold voltage vs. gate length for Si and InGaAs MOSFETs, inspired by [79]                                                                                                                                                                                                                                      |

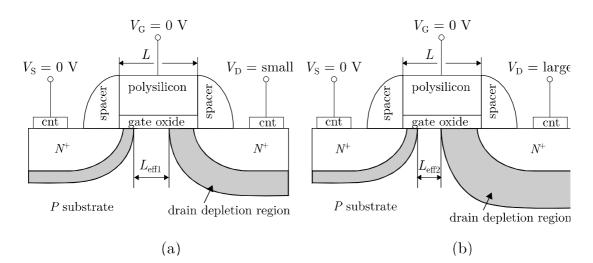

| Fig. 2.9: An example of modification depletion region in NMOSFET depending on different drain voltage: small drain voltage (a), and large drain voltage (b)                                                                                                                                                                                |

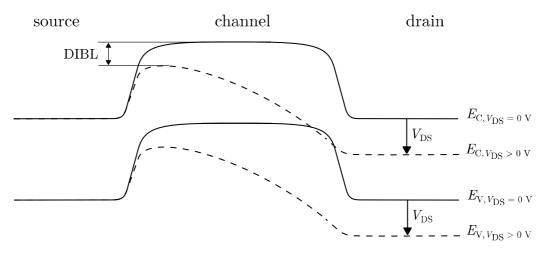

| Fig. 2.10: Comparison of schematic energy band diagrams near to surface of the NMOSFET with the drain voltage equal to zero volts (solid line) and with the drain voltage higher than zero volts                                                                                                                                           |

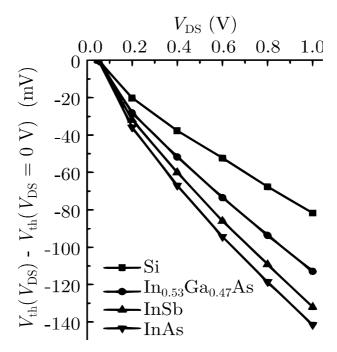

| Fig. 2.11: An example of DIBL comparison for various III-V-on-insulators NMOSFET, for the same technological parameters such as $W, L$ , and $t_{\rm ox}$ , insipred by [91]                                                                                                                                                               |

| Fig. 2. | 13: An e | example of  | energy conduc   | ctive band | s for differe | nt drain volt | tages |

|---------|----------|-------------|-----------------|------------|---------------|---------------|-------|

|         | and      | different   | MOSFET's        | lengths.   | Standard      | MOSFET        | (a),  |

|         | MOS      | FET with    | a short chann   | el (b), MO | OSFET with    | n a short cha | ınnel |

|         | and l    | DIBL effect | t (c), and ener | rgy conduc | ctive bands   | (d)           | 34    |

- Fig. 2.14: Cross-section of the NMOSFET (a), and illustration its energyband diagram (b) in the point of interest shown in (a)......35

- Fig. 2.17: MOS structure with the highlighted red part (a) where the ionizing radiation induce charge trapping and interface state generation (b).

- Fig. 2.21: Equivalent circuit of a hump effect (a) and hump effect on  $I_{\rm D}$ - $V_{\rm GS}$  characteristics of MOS transistors with body effect  $V_{\rm B} = -5.0$  V. 43

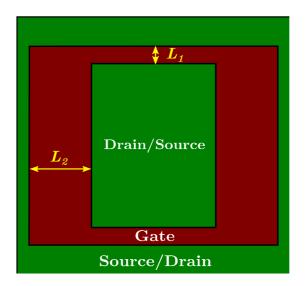

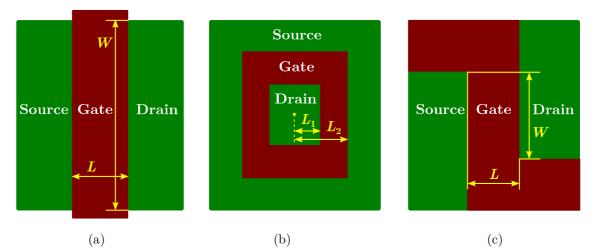

| Fig. 2.25: Rectangular enclosed layout topology with two different length $L_1$<br>and $L_2$                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

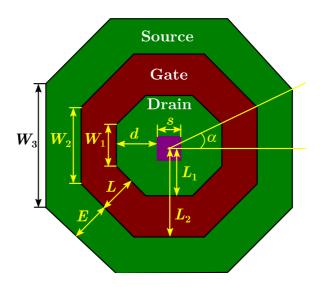

| Fig. 2.26: Basic top layout view of the octagon MOS transistor                                                                                                                                                                                                                                                            |

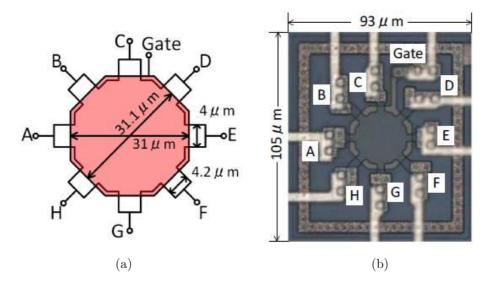

| Fig. 2.27: Octagon MOSFET device layout (a), microphotograph (b) [123].                                                                                                                                                                                                                                                   |

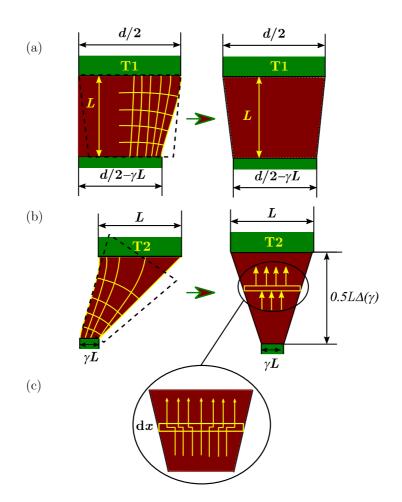

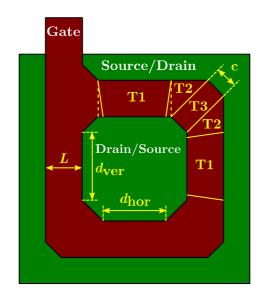

| Fig. 2.28: Annular enclosed layout topology with the decomposition of the broken corner square MOSFET into edge (T1), corner (T2), and linear corner                                                                                                                                                                      |

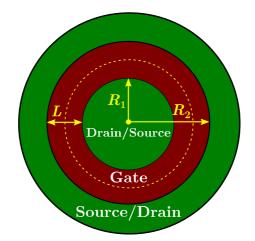

| Fig. 2.29: Gate-enclosed circular transistor shape                                                                                                                                                                                                                                                                        |

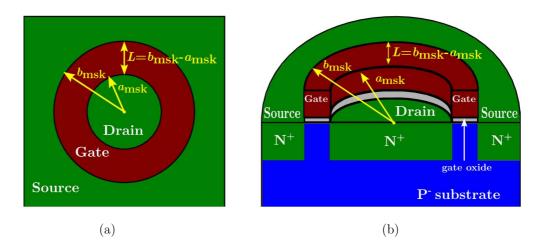

| Fig. 2.30: Basic top-view layout of conventional CGT (a) and its cross section (b)                                                                                                                                                                                                                                        |

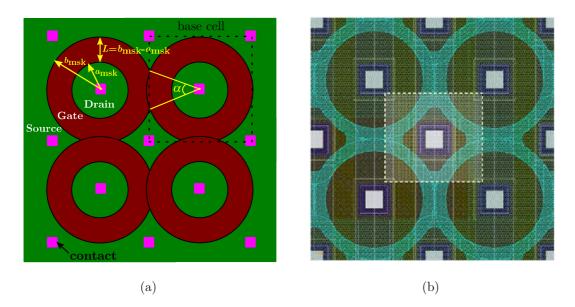

| Fig. 2.31: O-CGT layout top view (a) and its alternative physical design (b).                                                                                                                                                                                                                                             |

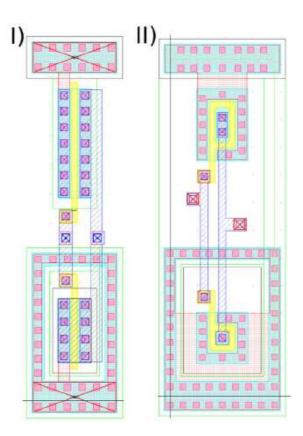

| Fig. 2.32: Physical design example of standard MOSFET (I) and gate-<br>enclosed MOSFET device (II) [118]                                                                                                                                                                                                                  |

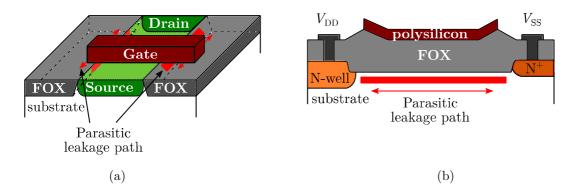

| Fig. 2.33: Representative cross section of leakage current path between source<br>and drain of the same device (intra-device) (a), and between<br>adjacent n-well regions of different devices (inter- device) (b) 56                                                                                                     |

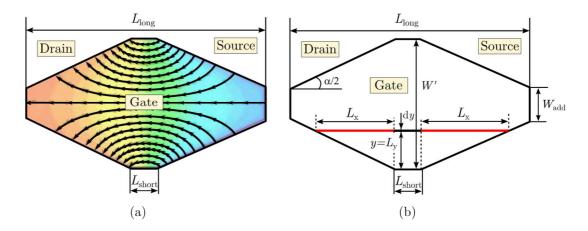

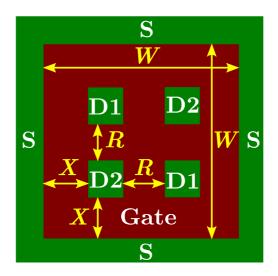

| Fig. 2.34: The 3D numerical simulation of longitudinal electrical field (LEF) along the channel of the diamond layout shape MOSFET (a), diamond channel electrically treated as a parallel association of an infinite number of MOSFETs (PAMDLE) with the infinitesimal width $(dy)$ and different channel length $(L_i)$ |

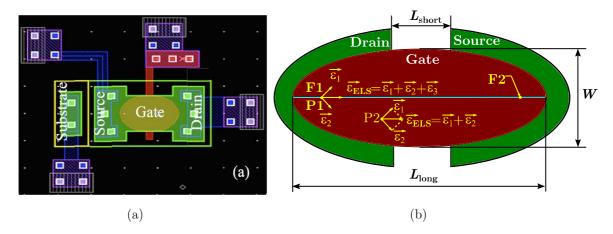

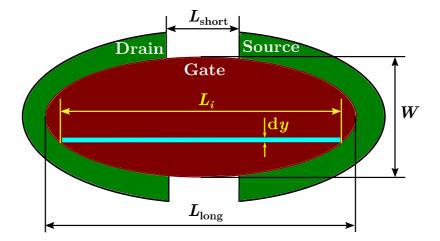

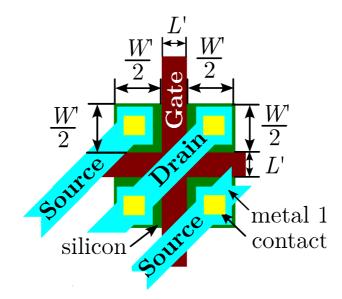

| Fig. 2.35: The ellipsoidal layout (a) and its superior view (b) with the indications of the LEF vector components in its structure, where $L_{\text{short}}$ and $L_{\text{long}}$ are the smallest and the highest dimensions of the channel length and W is the channel width, respectively                             |

| Fig. 2.36: Picture of an ELS MOSFET composed by infinite MOSFETs with aspect ratio of $dy/L_i$ , used to calculate the $L_{\text{eff,ELS}}$                                                                                                                                                                               |

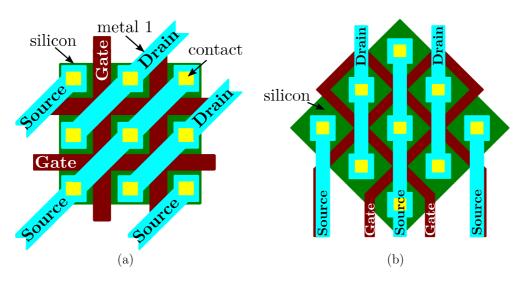

| Fig. 2.37: Waffle MOSFET structures with the interconnection for the source<br>and drain terminals oriented diagonal (a) or orthogonal (b) 62                                                                                                                                                                             |

| Fig. 2.38: The 2D cross diagonal waffle structure                                                                                                                                                                                                                                                                         |

| Fig. 2.39: The current mirror topology laid as waffle structure                                                                                                                                                                                                                                                           |

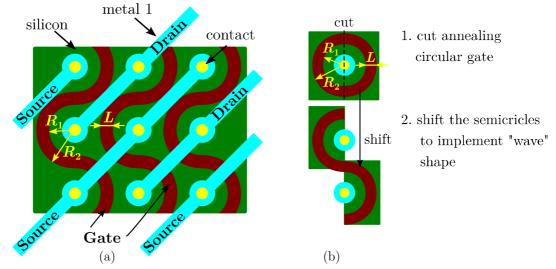

| Fig. 2.40: Layout view of the wave MOSFET structure (a) and its composition/realization (b)                                                                                                                                                                                                                               |

| Fig. | 2.41 | : An example of the Z layout gate shape MOSFET66                                                                                                                                                                                           |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

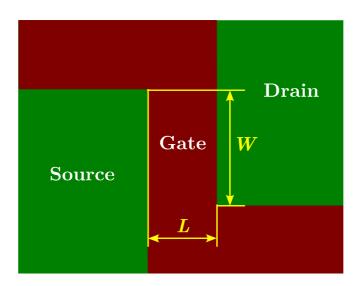

|      |      | : The conventional rectangular gate layout shape (a), the enclosed gate layout shape (b), the Z gate layout shape (c)                                                                                                                      |

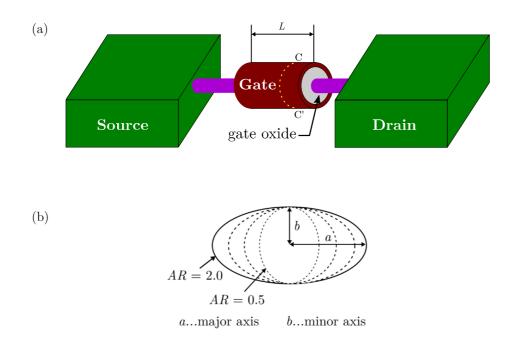

| Fig. | 2.43 | : Layout representatoin of cylindric gate shape (a) and its cross<br>section (b) along c-c' cutting line                                                                                                                                   |

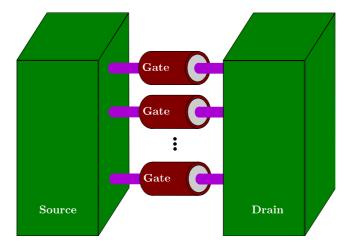

| Fig. | 2.44 | : llustration of CGAA-NW MOSFET with the stacked channel<br>(nanowires) to increase drain current capability                                                                                                                               |

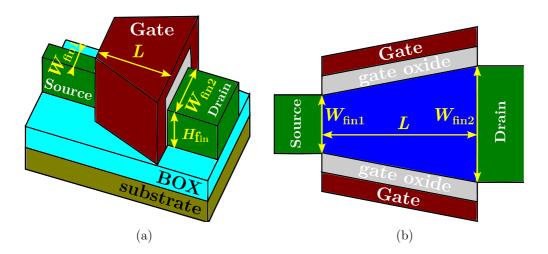

| Fig. | 2.45 | : 3D trapezoidal FinFET view (a), 2D cross-section of trapezoida<br>FinFET (b)                                                                                                                                                             |

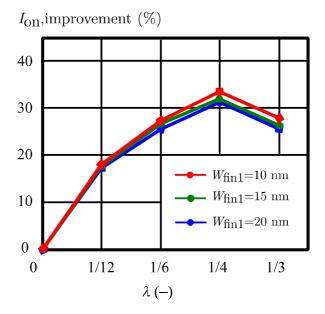

| Fig. | 2.46 | : Improvement of $I_{\rm on}$ as a function of the with different $W_{\rm fin1}$ 7                                                                                                                                                         |

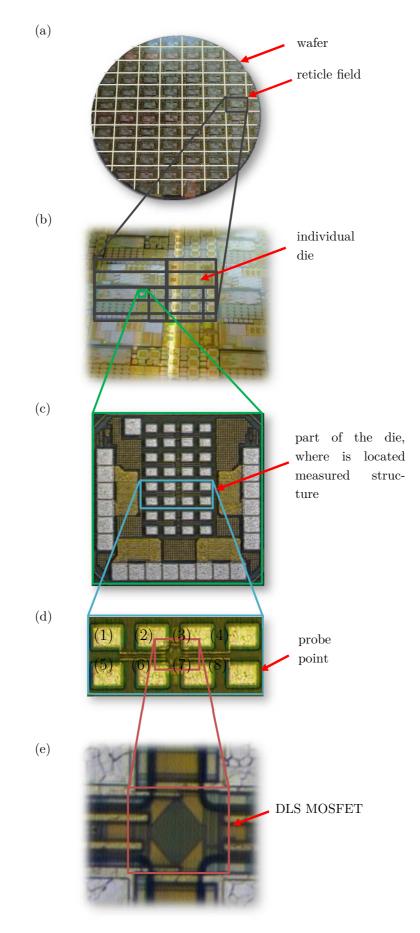

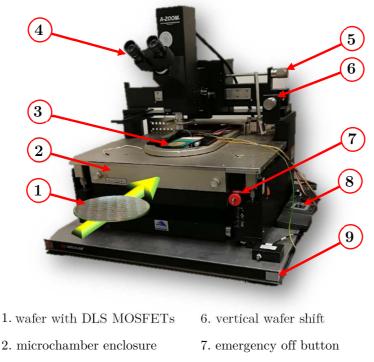

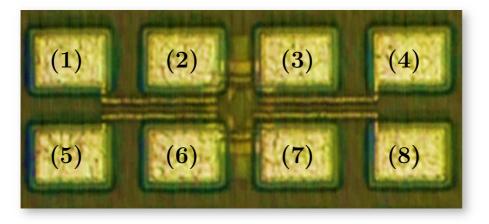

| Fig. | 3.1: | Photos of the measured sample directly on the wafer                                                                                                                                                                                        |

| Fig. | 3.2: | Advanced wafer probing machine                                                                                                                                                                                                             |

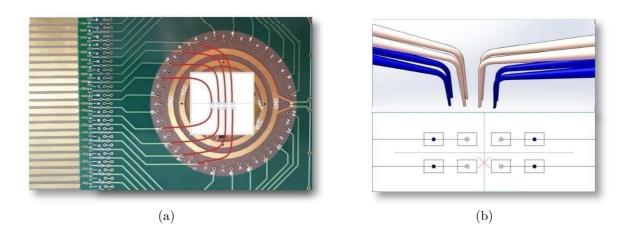

| Fig. | 3.3: | Probe card (a) and route planning of probe wires (b)                                                                                                                                                                                       |

| Fig. | 3.4: | Precision semiconductor parameter analyzer Agilent 4156C [161]. 8                                                                                                                                                                          |

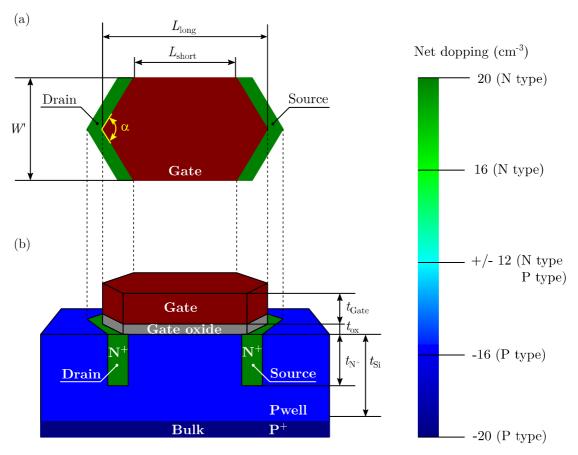

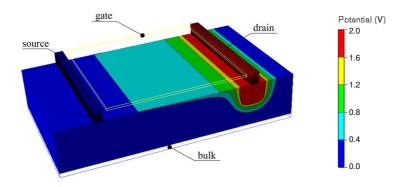

| Fig. | 3.5: | Diamond Layout Style (DLS) of the general N channel MOSFET<br>structure (a) 2D top-view of the structure, (b) 3D side-view of the<br>structure                                                                                             |

| Fig. | 3.6: | Measurement setup – flow chart                                                                                                                                                                                                             |

| Fig. | 3.7: | Sample ready for for-point measurement                                                                                                                                                                                                     |

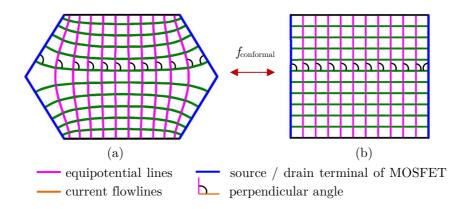

| Fig. | 4.1: | An example of conformal mapping. (a) before transformation (b<br>after transformation                                                                                                                                                      |

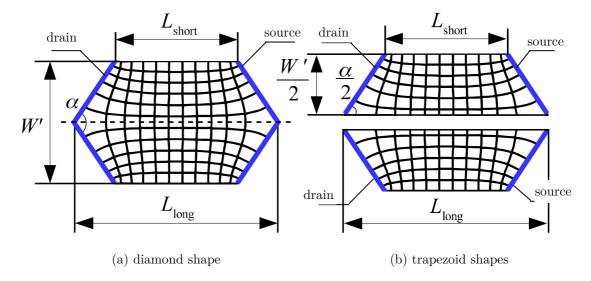

| Fig. | 4.2: | A DLS structure (a) split into two trapezoidal layout shapes (b). 99                                                                                                                                                                       |

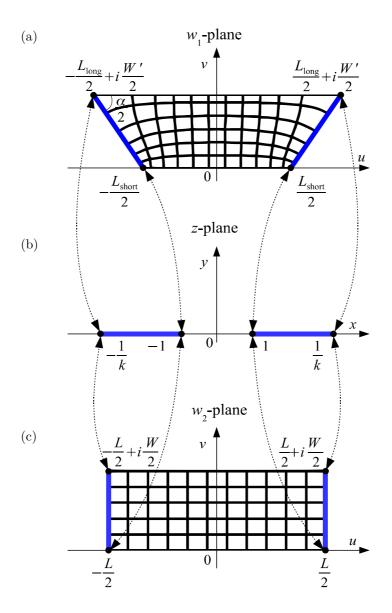

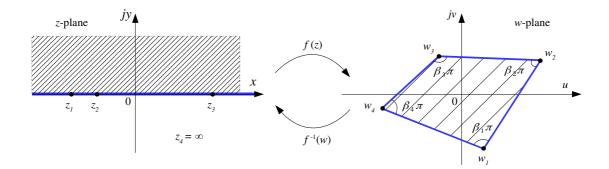

| Fig. | 4.3: | Schwarz-Christoffel mapping of a trapezoid (a) onto a rectangle (c by mapping through upper-half of the z-plane (b) 10                                                                                                                     |

| Fig. | 4.4: | SC mapping theorem from half z-plane onto a polygon in w-plan<br>                                                                                                                                                                          |

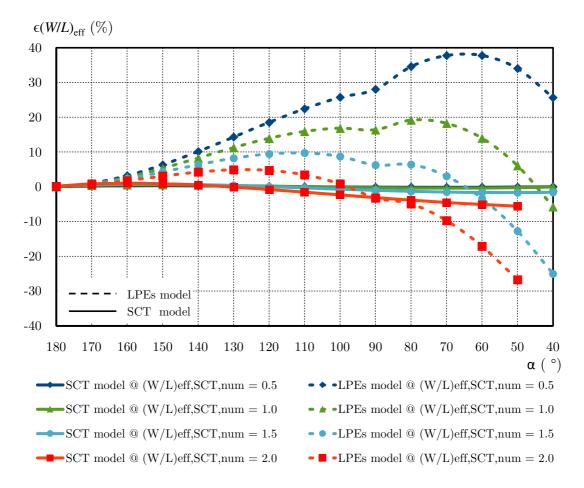

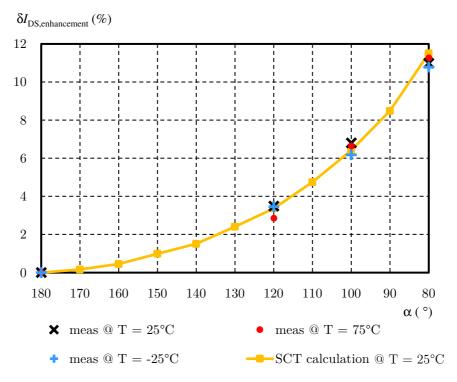

| Fig. | 4.5: | Calculated error of effective aspect ratio $(W/L)_{\text{eff}}$ depending on angl $\alpha$ between SCT model (solid line) and LPEs (LCE+PAMDLE model (dashed line) respectively and numerically simulated aspect ratio (MATLAB simulation) |

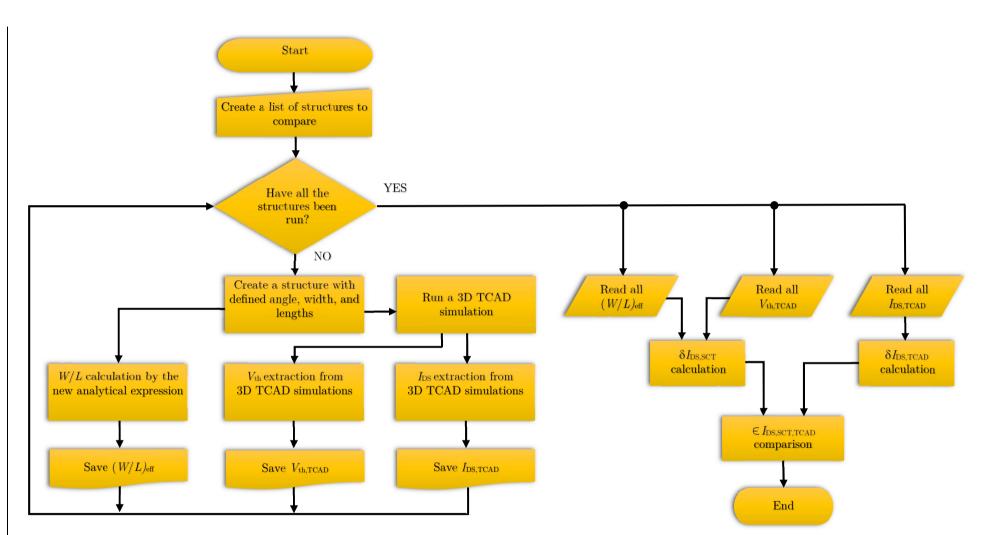

| Fig. | 4.6: | The flowchart calculation of the theoretical drain current gain given<br>by Schwarz-Christoffel transformation                                                                                                                             |

| Fig. | 4.7: | Potential examples of the RLS, DLS respectively of MOS transisto<br>for $(W/L)_{\text{eff}}$ equal to 1.0                                                                                                                                  |

| Fig. | 4.8: | Current  | density   | examples                 | of th | he ] | RLS, | DLS | respectively | of | MOS |

|------|------|----------|-----------|--------------------------|-------|------|------|-----|--------------|----|-----|

|      |      | transist | or for (V | $V/L)_{ m eff}$ equation | al to | 1.0  |      |     |              |    | 114 |

Fig. 4.9: Photography of the DLS NMOS transistor with the angle =  $100^{\circ}$  (a) and its pad out connections for four points measurements (b)... 116

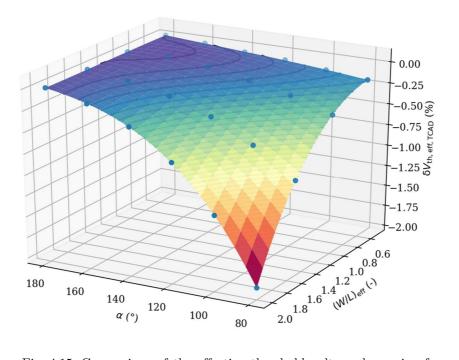

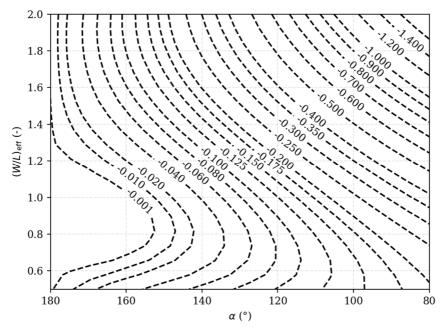

- Fig. 4.15: Comparison of the effective threshold voltage decreasing for DLS MOSFETs with the different effective aspect ratio  $(W/L)_{\text{eff}}$ ...... 130

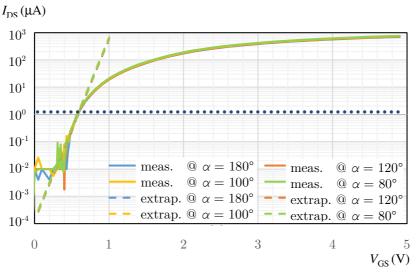

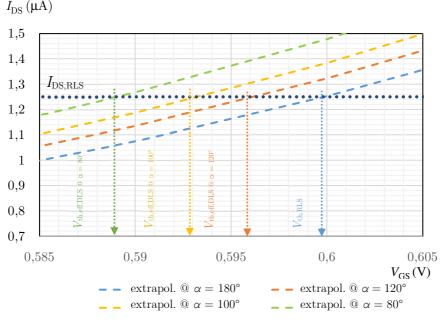

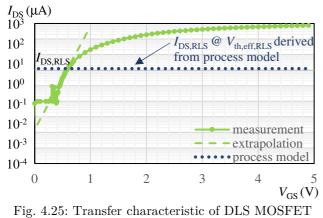

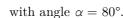

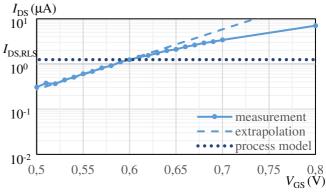

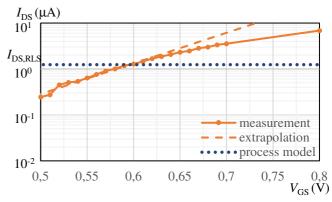

- Fig. 4.17: Transfer characteristics of DLS MOSFETs with angle  $\alpha = 180^{\circ}$  (blue), 120° (brown), 100° (orange), and 80° (green)......134

- Fig. 4.18: Transfer characteristics of DLS MOSFETs with angle  $\alpha = 180^{\circ}$  (blue), 120° (brown), 100° (orange), and 100° (green) in details.

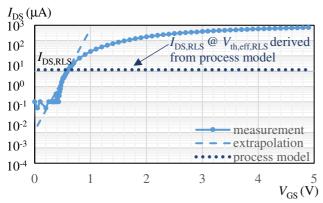

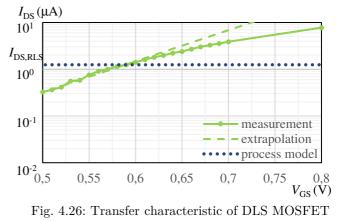

Fig. 4.19: Transfer characteristic of DLS MOSFET with angle  $\alpha = 180^{\circ}$ . 135

- Fig. 4.21: Transfer characteristic of DLS MOSFET with angle  $\alpha = 120^{\circ}$ . 135

| Fig. | 4.23: | Transfer | characteristic o | of DLS M | OSFET wit | h angle | $\alpha = 1$ | 00°. 135              |

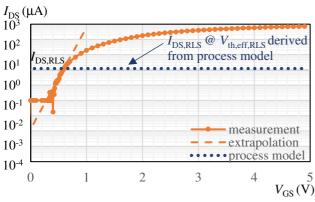

|------|-------|----------|------------------|----------|-----------|---------|--------------|-----------------------|

| Fig. |       |          | characteristic   |          |           |         | 0            |                       |

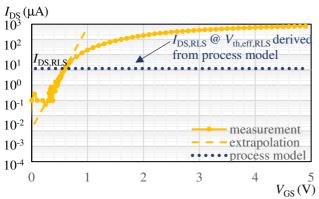

| Fig. | 4.25: | Transfer | characteristic o | of DLS M | OSFET wit | h angle | $\alpha = 8$ | 0° 135                |

| Fig. | 4.26: | Transfer | characteristic   | of DLS   | MOSFET    | with    | angle        | $\alpha = 80^{\circ}$ |

## LIST OF TABLES

|             | Comparison of electronic properties of Si with GaAs, GaN, SiC [64],<br>Ge, InAs [65], and diamond [66]21                                                                                                                                                            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Summary of the constant field scaling and the generalized scaling rules                                                                                                                                                                                             |

|             | Static dielectric constant $K$ and experimental bandgap for gate lielectrics                                                                                                                                                                                        |

| t]<br>p     | The ELS MOSFET and RLS MOSFET dimensions, $A_{\text{gate}}$ , $L_{\text{eff}}$ , and<br>the $L_{\text{eff}}$ reduction in relation to the RLS MOSFET in counterpart in<br>percentage due to the PAMDLE effect calculated by equation<br>(2.46)                      |

| Tab. 2.5: 7 | The parameters that were used for the device's simulation67                                                                                                                                                                                                         |

|             | Voltage Range, Resolution, and Accuracy (HRSMU = High<br>Resolution Source Monitor Unit)                                                                                                                                                                            |

| Tab. 3.2: C | Current Range, Resolution, and Accuracy (HRSMU)                                                                                                                                                                                                                     |

|             | Analysis of effective aspect ratio $(W/L)_{\text{eff}}$ for both LPEs and SCT cases of the DLS with various angles $\alpha$                                                                                                                                         |

|             | Dimensions of the measured and fabricated MOS transistors in BCD<br>60 nm technology                                                                                                                                                                                |

| fo<br>N     | Sample data of the enhancement saturation drain-source current $I_{\text{DS}}$<br>for both TCAD simulations and analytic calculations of the DLS<br>MOS transistor for the various angles $\alpha$ , the same aspect ratio equal<br>to 2.0 and the same active area |

|             | The simulated effective threshold voltage changes ( $\delta V_{\text{th,eff,TCAD}}$ ) of DLS MOSFETs for different effective aspect ratios ( $W/L$ ) <sub>eff</sub> 130                                                                                             |

|             | The measured effective threshold voltage changes ( $\delta V_{\text{th,eff,meas}}$ ) of DLS MOSFETs for different effective aspect ratios ( $W/L$ ) <sub>eff</sub> 133                                                                                              |

| Ν           | Summary of the effective threshold voltage changes of DLS MOSFETs for effective aspect ratio $(W/L)_{\text{eff}}$ equal to 2.0 and lifferent angles $\alpha$                                                                                                        |

## LIST OF ABBREVIATIONS

| Parameter   | Unit         | Description                                                               |

|-------------|--------------|---------------------------------------------------------------------------|

| 2D          | (-)          | <br>Two Dimensional                                                       |

| 3D          | (-)          | <br>Three Dimensional                                                     |

| А           | $(m^2)$      | <br>Active channel area of MOSFET                                         |

| В           | (-)          | <br>Bulk terminal of MOSFET                                               |

| CGAA        | (-)          | <br>Cylindrical Gate-All-Around                                           |

| $C_{ m GD}$ | (F)          | <br>Gate-drain parasitic capacitance                                      |

| $C_{ m GS}$ | (F)          | <br>Gate-source parasitic capacitance                                     |

| CMOS        | (-)          | <br>Complementary MOS                                                     |

| $C_{ m ox}$ | (F)          | <br>gate oxide capacitance                                                |

| D           | (-)          | <br>Drain terminal of MOSFET                                              |

| DC-DC       | (-)          | <br>Direct Current to Direct Current                                      |

| DIBL        | (-)          | <br>Drain-Induced Barrier Lowering                                        |

| DLS         | (-)          | <br>Diamond Layout Shape                                                  |

| DMOS        | (-)          | <br>Drain extended MOS                                                    |

| DUT         | (-)          | <br>Device Under Test                                                     |

| ELT         | (-)          | <br>Enclosed-Layout Transistor                                            |

| FEM         | (-)          | <br>Finite Element Method                                                 |

| FOM         | (-)          | <br>Figure-of-merit                                                       |

| G           | (-)          | <br>Gate terminal of MOSFET                                               |

| GAA         | (-)          | <br>Gate-All-Around                                                       |

| GIDL        | (-)          | <br>Gate-Induced Drain Leakage                                            |

| GPS         | (-)          | <br>Global Positioning System                                             |

| HV          | (-)          | <br>High Voltage                                                          |

| IC          | (-)          | <br>Integrated Circuit                                                    |

| $I_{ m D}$  | (A)          | <br>Drain current of MOSFET                                               |

| ITRS        | (-)          | <br>International Technology Roadmap for                                  |

|             |              | Semiconductors                                                            |

| $k_{ m B}$  | $(J K^{-1})$ | <br>Boltzmann constant $(k_{ m B} = 1.38 \cdot 10^{-23}  { m J  K^{-1}})$ |

| L           | (m)          | <br>Length of MOSFET                                                      |

| LDDMOS      | (-)          | <br>Low Doped Drain MOS                                                   |

| LOCOS       | (-)          | <br>Local Oxidation of Silicon                                            |

| LP          | (-)          | <br>Low Power                                                             |

| LPEs        | (-)          | <br>LCE+PAMDLE                                                            |

| MOS         | (-)          | <br>Metal Oxide Semiconductor                                             |

| MOSFET                  | (-)                    | <br>MOS Field Effect Transistor                 |

|-------------------------|------------------------|-------------------------------------------------|

| n <sub>i</sub>          | $(ions m^{-3})$        | <br>intrinsic doping concentration of silicon   |

|                         |                        | $(n_{ m i} = 1.45 \cdot 10^{10} ~{ m cm}^{-3})$ |

| $N_{ m ch}$             | $(\text{ions m}^{-3})$ | <br>is a channel doping                         |

| $N_{ m A}$              | $(\text{ions m}^{-3})$ | <br>acceptor impurity density in silicon        |

| $N_{ m D}$              | $(\text{ions m}^{-3})$ | <br>donor impurity density in silicon           |

| NC                      | (-)                    | <br>Negative Capacitance                        |

| PZT                     | (-)                    | <br>Piezoelectric polycrystalline               |

| O-CGT                   | (-)                    | <br>overlapping circular-gate transistor        |

| q                       | (C)                    | <br>magnitude of the electron charge            |

|                         |                        | $(q = 1.602 \cdot 10^{-19} \text{ C})$          |

| R&D                     | (-)                    | <br>Research and Development                    |

| RESURF                  | (-)                    | <br>Reduced Surface Field                       |

| RF                      | (-)                    | <br>Radio Frequency                             |

| RGT                     | (-)                    | <br>Rectangular Gate Transistor                 |

| RHDB                    | (-)                    | <br>Radiation Hardening by Design               |

| RLS                     | (-)                    | <br>Rectangular Layout Shape                    |

| S                       | (-)                    | <br>Source terminal of MOSFET                   |

| SC                      | (-)                    | <br>Schwarz-Christoffel                         |

| SCT                     | (-)                    | <br>Schwarz-Christoffel Transformation          |

| SG                      | (-)                    | <br>Surrounding Gate                            |

| Si                      | (-)                    | <br>Silicon                                     |

| SoC                     | (-)                    | <br>System-on-Chip                              |

| STI                     | (-)                    | <br>Shallow Trench Isolation                    |

| Т                       | (K,°C)                 | <br>Temperature                                 |

| TCAD                    | (-)                    | <br>Technology Computer-Aided Design            |

| $t_{\rm ox}$            | (m)                    | <br>gate oxide thickness                        |

| TID                     | (-)                    | <br>Total Ionizing Dose                         |

| VLSI                    | (-)                    | <br>Very Large Scale Integration                |

| $V_{ m bi}$             | (V)                    | <br>Built-in voltage of MOSFET                  |

| $V_{\rm BD}$            | (V)                    | <br>Breakdown voltage of MOSFET                 |

| V <sub>BS</sub>         | (V)                    | <br>Bulk-Source voltage of MOSFET               |

| V <sub>GS</sub>         | (V)                    | <br>Gate-Source voltage of MOSFET               |

| VD                      | (V)                    | <br>Drain voltage of MOSFET                     |

| V <sub>DS</sub>         | (V)                    | <br>Drain-Source voltage of MOSFET              |

| $V_{\rm Dsat}$          | (V)                    | <br>Drain saturation voltage of MOSFET          |

| V <sub>DD</sub>         | (V)                    | <br>Supply voltage                              |

| V DD<br>V <sub>FB</sub> | (V)                    | <br>Flatband voltage of MOSFET                  |

| $V_{\rm th}$            | (V)                    | <br>Threshold voltage of MOSFET                 |

| $V_{ m th,eff}$         | (V)                    | <br>Effective threshold voltage of MOSFET       |

| 117                         | $\langle \rangle$    |                                                                                               |

|-----------------------------|----------------------|-----------------------------------------------------------------------------------------------|

| W                           | (m)                  | <br>Width of MOSFET                                                                           |

| (W/L)                       | (-)                  | <br>Aspect ratio of MOSFET                                                                    |

| $(W/L)_{\rm eff}$           | (-)                  | <br>Effective aspect ratio of MOSFET                                                          |

| $x_{ m j}$                  | (m)                  | <br>Junction depth of MOSFET                                                                  |

|                             |                      |                                                                                               |

|                             | I                    |                                                                                               |

| α                           | ( °)                 | <br>Angle in diamond layout structure                                                         |

| γ                           | $(V^{1/2})$          | <br>body effect of MOSFET                                                                     |

| $\mathcal{E}_0$             | (F m <sup>-1</sup> ) | <br>vacuum permittivity, $\boldsymbol{\varepsilon}_0 = 8.854 \cdot 10^{-12} \text{ F m}^{-1}$ |

| $\mathcal{E}_{\mathrm{ox}}$ | (F m <sup>-1</sup> ) | <br>permittivity of oxide                                                                     |

| $\mathcal{E}_{\mathrm{Si}}$ | (F m <sup>-1</sup> ) | <br>permittivity of silicon                                                                   |

| $\mathcal{E}_{\mathrm{r}}$  | (-)                  | <br>relative permittivity of a material                                                       |

| $\phi_{ m p}$               | (V)                  | <br>channel/bulk potential                                                                    |

# CHAPTER 1

## INTRODUCTION

### 1.1 MOTIVATION

NowADAYS, the criteria for ecology and vital environment protection are rigorous and must be respected. The 2030 Agenda for Sustainable Development [1] provided a clear direction that the world must aim to tread a more economically, socially, and environmentally sustainable path. Except for the other, the plan is focused on improving the life quality for everyone and protecting our environment [1]. Currently, there is also think about the area of resource extraction in outer space [2] because, in extremes cases, mining on Earth also has not a positive impact on vital environment and ecology.

The idea of a technology roadmap for semiconductors can be traced back to a paper [3] by Gordon Moore in 1965, in which he stated that the number of components that could be incorporated per integrated circuit would increase exponentially over time. This would result in a reduction of the relative manufacturing cost per function, enabling the production of more complex circuits on a single semiconductor substrate. Since 1970, the number of components per chip has doubled every two years. This historical trend has become known as "Moore's Law". However, despite the established rules, our initiative can prevent potential life disasters, as it is in this work. Therefore, this work focuses on research into improvements in the electrical performances of integrated Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) [4, 5], which will ultimately reduce both environmental pressure and financial costs in the production of integrated circuits. Reducing manufacturing costs and pressure on the environment is achieved by using smaller silicon wafer surfaces while retaining the original chip functionality. It can be achieved by using the advanced diamond layout shape of MOS transistors (DLS MOSFETs) in the integrated circuits [6-8] such it is presented in this thesis.

Moreover, there is currently significant demand for analog high-frequency integrated circuits (ICs) with a chip area on a die as small as feasible [9]. This specific requirement can be realized by using DLS MOSFET as well. Typical applications of these ICs are for example DC-DC (Direct Current to Direct Current) converters for example in Bluetooth communication [10], touch-screen controllers in smart mobile phones [11], or power switches controllers in electronic fuses [12], where the key components should have the parasitic capacitance as small as possible. These parts include any analog circuit that switch-on/switch-off an analog control device. For example, it could be a power MOS (Metal Oxide Semiconductor) as a discharge device. In the switch-on/switch-off operation, there should be charged/discharged parasitic capacitance of the discharge devices. It has two impacts on applications. The first one is decreasing the maximal frequency of application systems for the specified current consumption. The operation cycle consumes additional electrical energy (e.g., from a battery of mobile phones) in each switching period. The next impact on applications is decreasing the lifetime of the mobile devices due to limited power energy in the battery, that is discharged by the switching frequency [13]. Into the category of mobile devices, we can sort devices such as (smart) mobile phone, (smart) watches, tablets, mobile GPS (Global Positioning System) devices, and so on.

Since the active area of the MOS Field Effect Transistor (MOSFET) has a direct influence on parasitic capacitance [14], the most effective way to improve these undesirable effects is to use different layout topologies that decrease the area of the MOSFET and keep or have better electrical performances. Moreover, the smaller active area of silicon dies allows to create smaller products, such as the smallest wireless sensor node for accurate cellular temperature measurement, which has just  $(360x400x150 \ \mu m)$  [15], or it opens market for the new applications such as electronic medical pills [16]. Considering the previous requirements, in this thesis is reported possibility how to satisfy the requirements.

Therefore, this thesis focuses on an exciting topic, which is how to improve the electrical performances of MOSFETs in integrated circuits by physical mask design. For this goal: the precise innovative analytical description of the effective aspect ratio of DLS MOSFETs is described for the first time, the improvements in the electrical performances of the DLS MOSFETs have been calculated, simulated, and measured in 180 nm BCD technology process, and the precise model of the effective threshold voltage has been numerically approximated, simulated, and compared with the measured data.

### 1.2 THESIS OUTLINE

This thesis is divided into five chapters, the first of which is this short introductory chapter, which describes the motivations, aims of this thesis, author's scientific contributions and state of the art. Next, chapter 2 discusses the problems in the scaling of integrated circuits and reviews different MOSFET gate layout shape architectures. Following this, chapter 3 describes the design and methodology adopted by this research to achieve the aims and objectives stated in section 1.3 of Chapter 1. Chapter 4 reports all the innovative results achieved in this doctoral thesis, such as innovative analytical description of the effective aspect ratio of DLS MOSFET, improvements in the electrical performances of the DLS MOSFET by physical mask design, and the new precise model of the effective threshold voltage changes in the DLS MOSFETs. Finally, chapter 5 discusses the conclusions arising from the finding of this thesis and proposes future work.

### 1.3 Aims of This Thesis

The aim of this thesis is to investigate and describe the way, how to improve electrical performances of MOSFETs' in integrated circuits. The main goals of this thesis are the following:

- Investigate how to improve electrical performances of MOSFETs' in integrated circuits by physical mask design without complex structural modification.

- Develop and innovatively describe the lateral DLS MOSFET structure with better performance in comparison with the standard rectangular layout shape MOS transistor.

- Investigate and develop an innovative approach that analytically describes the effective aspect ratio of DLS MOSFETs.

- Define a new expression, which continuously describes the DLS MOSFETs in the whole range of DLS MOSFETs angles.

- Research the improvements in the electrical performances (the drain-source current) of the DLS MOS transistors by the analytical model, 3D-TCAD simulations and measurement on real silicon samples.

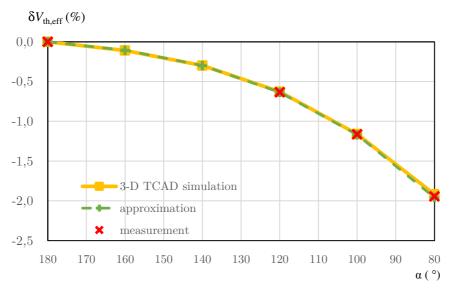

- Research and develop a new model of the interesting phenomenon related to the effective threshold voltage changes in the diamond layout shape MOS transistors.

All the above-mentioned goals are innovative, new, and never have been published before. These goals represent a possible new trend in semiconductor integrated circuits that improve MOS transistors' electrical performances, define a new methodology, and an innovative DLS MOSFET expression. The objectives further investigate and develop a new model of an interesting phenomenon related to effective threshold voltage changes in DLS MOS transistors.

### 1.4 Author's Scientific Contributions

The aims of this thesis are specified in the previous section of this Chapter 1, and the author's scientific contribution are highlighted in this part. The author's scientific contributions that have been achieved in this thesis are:

### • Analytical description of the effective aspect ratio of DLS MOSFETs

The new innovative analytical expression and methodology of calculating the effective aspect ratio of the MOSFET with the diamond layout shape gate pattern is described this thesis in section 4.1 for the first time. There has been used an innovative approach based on the conformal map function. As the conformal map function, the Schwarz-Christoffel transformation has been used. Both the new methodology and the new innovative analytical model, respectively, are described in section 4.1.2, verified with the 3-D TCAD simulations in section 4.1.3, and compared with the different methodology in section 4.1.4. The important results are described in section 4.1.5. All the mentioned results have been published in the impacted journal [6] **IEEE Transactions on Electron Devices, 2019, (Quartile 1).**

## • Improvements in the electrical performances of the DLS MOS transistors

The improvements in the electrical performances of the DLS MOSFETs are described in section 4.2 of this thesis for the first time. In sub-section 4.2.2, there is illustrated the theoretical drain-source current enhancement, and in the sub-section 4.2.3 is described the 3-D TCAD simulations of the drain-source current enhancement. Also, it has been measured on the real silicon samples fabricated in the BCD

160 nm technology process (section 4.2.4). All the theoretical, simulated, and measured data has been compared and summarized in section 4.2.5. The measurement results have been presented at an international conference [17] IEEE Proceedings of the 25<sup>th</sup> International Conference on Applied Electronics, 2020, and the complete data results have been published in the impacted journal [7] IEEE Transactions on Electron Devices, 2020, (Quartile 1).

### • Precise model of the effective threshold voltage changes in the DLS MOSFETs

The interesting phenomenon related to the effective threshold voltage changes in the diamond layout shape MOS transistors has been observed. This phenomenon has been analytically approximated by the new expression for the first time (section 4.3.3) and verified with the measured data in 4.3.4. All the important data are compared in section 4.3.5 and published in [8] **IEEE Transactions on Electron Devices, 2020, (under review, Quartile 1).**

#### 1.5 State of the Art

Since 1971, the number of functional components (transistors, capacitors, etc.) per chip has exponentially increased (doubled practically every two years), and this historical trend was widely accepted by the chip fabrication community (International Technology Roadmap for Semiconductors – ITRS), as a Moor Law. The ability of the semiconductor industry to follow with the Moor's Law has been the engine of the strong cycle: transistor scaling delivers a better performance-toprice ratio, and it drives exponential growth in the semiconductor market. This, in turn, allows for further investment in semiconductor technologies that support further scaling. For example, software growth makes Moor's law possible. Why? Because people buy new hardware because the software requires it [18]. To remember, in 1971 Intel, that time not a well-known small company, released its first-ever microprocessor, the 4004. The chip, sized 12 mm<sup>2</sup>, contained 2 300 transistors spaced by 10 µm gaps. To compare, the latest Intel IC product, the 10-core Intel<sup>®</sup> Core<sup>™</sup> i7 64-bit Extreme Edition processor, being only about x10 larger than the 4004, provides incredible computing power, having several billion transistors at a spacing of 10–14 nm [19]. In the case of uses smaller technology nodes, there should be kept in mind the problems in technology scaling. Section 2.1 "Problems in Scaling" provides more details on this interesting and important topic.

The semiconductor IC's surface areas have been increasing, although there are opportunities to use the latest scaled-down technologies nodes with smaller and smaller surface areas of used IC functional components. This is because current and future ICs are becoming more complicated than they have been in recent years [20]. So, the higher complexity of the ICs thus leads to an increase in their total surface area. Of course, the increased surface area of ICs also increases the costs of the final products. Therefore, many research and development (R&D) centers are looking for ways, how to save the costs of the final products. The general solution of it is to reduce the surface area of the MOSFET, but the same or better electrical performance should be maintained. As has been mentioned before, it can be achieved by using the proposed diamond layout shape MOS transistor which is the topic of this work.

Recent growth in the smart-power applications, wireless communication functionalities, mobile communication and other electronic systems in different CMOS technologies handling different functionalities like voltage regulation, signal conditioning, data conversion, and digital processing is one of the driving factors for advanced system-on-chip (SoC) solution [21-23] on the same silicon substrate. Accordingly, various subsystems, such as power management and RF (radio frequency) power amplifier, need to be fabricated using standard silicon process. However, exists other technologies using either GaN high-electron mobility transistors or SiC-based power MOSFETs due to their higher operation temperature, carrier mobility and breakdown voltage  $(V_{\rm BD})$  compared with silicon-based devices [24]. The integration of these GaN or SiC devices on the silicon substrate is not trivial [25]. Furthermore, difficulty in scaling of these compound semiconductor devices is also reported in [26]. Hence, for CMOS-based advanced SoCs, a Si-based design is still of interest and is discussed in this work. The following part summarizes the pros and cons of the current methods, how to get better MOSFETs performances for low voltage applications fabricated in CMOS technologies on silicon-based design.

In [27] is presented a solution, uses a negative capacitance (NC) as a universal digital and analog performance booster for complementary MOS transistors. A ferroelectric capacitor interconnecting with the gate stack of an MOS transistor creates a series connection and increases the total capacitance of the gate. In this approach, the gate stack is not a passive part of the transistor anymore and contributes to signal amplification. Specifically, the series structure brings an abrupt increase in the differential charge in the internal node by changing the gate voltage, thus providing a step-up voltage transformer [28, 29]. The ferroelectric performs two separate NC regions, demonstrating a zig-zag polarization

characteristic. This mainly happens due to the fact that the piezoelectric polycrystalline (PZT) is showing two main polarization domains and a multidomain ferroelectric capacitor in steady states cannot hold more than one negative capacitance domain at a time [30, 31]. As a result, the manifested polarization characteristic of the multi-domain ferroelectric is different from the S-shaped curve which is expected for a single-domain ferroelectric. Thus, the drawback of this NC-FET is in the hysteretic behavior due to the NC effect. This is trade-off between the hysteretic behavior and the performance-boosting.

In [32, 33] are presented methods that improve DC and RF behavior of drift MOS transistors. The drift MOS transistor is a high-voltage device of which the fabrication process is compatible with the standard CMOS processing steps. In many publications, the authors use different names for the same structures. For that reason, this work will be synchronized according to the naming convention as follows:

- The LDDMOS (Lightly Doped Drain/Source MOS) is a MOSFET that has a lightly doped (N<sup>-</sup>/P<sup>-</sup>) drain (LDD) below a spacer oxide region between the drain (N<sup>+</sup>/P<sup>+</sup>) terminal and the gate [34]. That region is shorter in comparison to drain-extended MOSFET.

- The drift MOS is a MOSFET that has LOCOS, FOX or STI between drain and gate terminal [35, 36].

- The drain-extended MOSFET [37] is a MOSFET that has an extended long region between the drain (N<sup>+</sup>/P<sup>+</sup>) terminal and the gate. That region is low doped and like a region in LDDMOS, but there is necessary to have special one extended mask.

- The LDMOS is a lateral double diffused MOSFET, also known as the DMOS. This kind of MOSFET has a lightly-doped region below the source terminal known as a P<sub>body</sub> for NLDMOS or N<sub>body</sub> for PLDMOS [38].

The upper drift MOS transistors have been detailed analyzed with other highvoltage MOS structures such as drain-extended MOS devices in [39]. Drift MOS transistors can sustain high terminal breakdown voltages due to the reduced surface field (RESURF) action, which makes it suitable for high-power applications [40], high-voltage line drivers or level shifters [41]. However, in that paper is written: to have better performances of drift MOS transistors, it is necessary to reduce the electron density under the drain  $N^+$  concentration doping. It has been realized by increasing the diffusion length of the drain terminal. Thus, the total area of the improved drift MOS is bigger than the standard drift MOS transistor, and this is the drawback of this improvement. Moreover, the drift MOSFET area is greater in comparison to standard MOSFET, which is fabricated with the same primary mask set for not high-voltage applications.

Nowadays, there is also a trend to improve the electrical performances of silicon-based MOSFET transistors through various vertical trench topologies, such as the conventional trench MOSFET, double trench MOSFET or for example superjunction trench MOSFET [42]. The source and drain terminals of the vertical trench MOSFETs are located on the opposite sides of the chip wafer. For this reason, the vertical trench MOSFET can be realized as discrete components, and this is not within the scope of this work. These trench MOSFETs are useful for high-voltage applications where hundreds and thousands of volts are needed as a discrete component [43].

Another category leading to improved performances of MOSFETs uses superjunction (SJ) topology [44]. SJ MOSFETs can be realized in such vertical structure as well as lateral structures. The vertical SJ structure has consisted of multiple  $P^-$  and  $N^-$  columns (pillars) to allow a higher drift region ( $N^-$  columns for SJ N-LDMOSFET) doping concentration than conventional power MOSFETs. The highly doped  $N^-$  column directly reduces the specific on-resistance. As a charge compensation concept, the excess charge in the  $N^-$  column is counterbalanced by the adjacent charges in  $P^-$  column, and thus high breakdown voltage is maintained due to high vertical electric field distribution [45]. The SJ structure breaks the traditional silicon limits for breakdown voltage and specific on-resistance in power MOSFETs. In [46] is reported study between vertical Si SJ MOSFETs and vertical GaN SJ MOSFETs, where breakdown voltage is  $V_{\text{BV,Si}} = 0.6 \sim 1.2 \text{ kV}$  and  $V_{\text{BV,GaN}} = 2.7 \text{ kV}$ , respectively and specific on-resistance  $R_{\text{on,sp}} = 2 \sim 10 \text{ m}\Omega \text{ cm}^2$  and  $R_{\text{on,sp}} = 0.78 \text{ m}\Omega \text{ cm}^2$ , respectively. The vertical SJ topologies cannot be used for very large scale integration (VLSI) onto a single chip due to its vertical topology. This topology is very useful for a realization of discrete components.

Such an example of superjunction topology is a lateral conventional superjunction LDMOS (CSJ LDMOS) and a lateral superjunction trench LDMOS (SJT LDMOS) [47]. In this case, the CSJ LDMOS has break-down voltage 169 V, and the other one has improved break-down voltage up to 218 V. SJT LDMOS has improved specific on-resistance  $(R_{\text{on,sp}})$  by decreasing it up 20 % also  $(R_{\rm on} = 9.28 \text{ m}\Omega \text{ cm}^2)$ . The disadvantage of these LDMOSes is their manufacturing process since two independent wafers are needed for their final implementation. These wafers are later folded to form one SJT LDMOS. It is a very expansive and critical step for mass production, and moreover it is not suitable for low-voltage applications as it has been recommended for the  $V_{\rm GS}$  higher than 5 V [47]. The similar results have been reached in [48], where double trench-gate drift MOSFET has been studied. Its break-down voltage and specific on-resistance have been  $V_{\rm BD} = 182 \text{ V}$  and  $R_{\rm on,sp} = 0.96 \text{ m}\Omega \text{ cm}^2$ , respectively. Of course, it depends on the doping concentration of a MOSFET. For this kind of MOSFET, the disadvantage is a much bigger structure in comparison to standard LDDMOSFET for not highvoltage applications.

The other categories are FinFETs and gate-all-around (GAA) MOSFETs structures. Let remind, over a span of decades, the scaling of CMOS technology has been a primary focus of the semiconductor industry in order to reduce the cost per function, increase speed, and reduce power [49]. The CMOS scaling was initially accomplished by shrinking device physical feature sizes [50], in particular, gatelength, and enabled by process innovations, such as scaled gate dielectrics, improved junction profiles, and new contact materials [51]. After many scaling steps, the scaling was not possible anymore, and therefore, the new FinFETs and GAA MOSFETs structures have been developed. The typical applications for them are in developing digital functional circuits such as different SRAM cell topologies [52], burst clock generator [53], but also, untypically, it could be used, such as bandgap references [54, 55]. The uses drawback of FinFETs and GAA MOSFETs (nanowires) for analog circuits is mainly in a dramatically higher source/drain resistance, and higher  $C_{GS}$  and  $C_{GD}$  parasitic capacitance.  $C_{GS}$  and  $C_{GD}$ are higher due to gate coupling to the trench diffusion contacts and to the epitaxial source/drain fill between fins. As a fin width of FinFETs ( $W_{\rm fin}$ ) is a small fraction of the fin pitch, junction capacitance to the wells is reduced, but the vertical well resistance is much higher. Finally, self-heating is worse given the higher area density of device currents [56]. In addition, the process variability accuracy of too small parts, such as FinFET's and nanowire's parts, is very low [57, 58]. Therefore, the FinFETs are desired for ultra-low voltage designs such as digital topologies (SRAM, clock generators, etc.) and not for analog circuits with the partially higher power requirements. Currently, innovation studies focus on the elimination of Gate-Induced Drain Leakage (GIDL) and off-state gate-leakage [59]. The off-state gateleakage is dominant for sub-micron technologies, and it is also a limiting factor in achieving ultra-low current consumption [60] of digital blocks. In the case of FinFETs, there is a possibility to have the width of the gate  $W_{\text{fin}}$  only in a few nanometers  $W_{\text{fin}} = 6 \text{ nm } [60]$ , and the same, of course, is valid as well as for nanowires (GAA).

So far, in this work, the improvements in the electrical performances of planar MOSFETs have been realized by complex structural modifications. These modifications have increased the active area of the MOSFETs (such as, for example, in the case of drift MOSFETs, drain-extended MOSFETs, etc.) or significantly changed its current-voltage (I-V) characteristic (NC-FETs). These modifications increase MOSFETs breakdown voltages or change the character of MOSFETs

output characteristics. It means, they do not increase the electrical performances of planar MOSFETs in terms of boosting current-voltage characteristics, and thus do not help in improvements in the electrical performances in both low power and low voltage applications, respectively. In other non-planar technology processes, such as the "3D" transistor, the modifications are suitable for ultra-low voltage applications. Into this category are sorted for example FinFETs, GAA MOSFETs, etc. However, these modifications cannot be realized in planar technologies. Therefore, here the question arises on how to improve the electrical performances of planar MOSFETs. Such as a promising way, how to improve the electrical performances of low voltage MOS transistors, is to change/modify its gate shape. As highlighted in section 2.2 "Review of Different MOSFET Gate Shape Architectures", the gate modification is a very actual topic and it is often discussed in terms of the improvements of electrical performances of the MOS transistors. Not all possible modifications have been detailed described and therefore, it needs to be explored in more details such it is in this thesis.

# Chapter 2

## TECHNICAL BACKGROUND

THIS technical background chapter demonstrates a thorough knowledge of the interesting field and provides arguments to support the study focus. The aim of this chapter is to delineate various theoretical positions and from these to develop a conceptual framework for the generation of hypotheses and setting up the research question.

The topic of this dissertation is to improve the electrical performances of planar MOSFETs in integrated circuits by physical mask design. The main goal of the improvements is to strengthen the output characteristics of MOSFETs or, in other words, to maintain the electrical performances of MOSFETs, but to use smaller active areas of MOSFETs for it. The following text proposes two different ways how to achieve this.

The first way how to save MOSFETs' areas and keep the same MOSFETs' performances is to down-scale the process. It allows us to maintain the original MOSFETs' performances and use the smaller MOSFET's active area for it. In the down-scaling process, there is a trade-off between the boosting, cost, and problems during the downscaling. Therefore, the following sections discuss the scaling

problems of MOSFETs such as technology field scaling theory, gate oxide variation, gate leakage, SCE, DIBL, GIDL, high-k, low-k, and other undesirable effects such as TID, and hump effect.

The second way how to save the areas and keep the same MOSFETs' performances is to modify the physical masks. Based on that, the other part of the next section presents various layout topologies of the MOSFETs such as circular gate shape with overlapping, cylindrical gate layout shapes, diamond layout shapes based on the "Longitudinal Corner Effect", enclosed layout shapes (square enclosed layout topologies, rectangular enclosed layout topologies, annular enclosed layout topologies, circular enclosed layout topologies), ellipsoidal gate shapes, octagonal gate shapes, trapezoidal gate shapes, waffle gate shapes, wave gate shape, Z gate shapes, which lead to better electrical performances of transistors.

This chapter reviews two different methods of MOSFETs' improvements in electrical performances in terms of mentioned requests to the silicon area. The first method is related to the technology process step, and the second one is related to the geometry modification of the MOSFETs' gate shape. Therefore, this chapter is organized as follows. The first section 2.1 ("Problems in Scaling") describes the problems that become with the IC technologies process downscaling for MOSFET devices and also describes a few specific parasitic effects of MOSFETs. The second section 2.2 ("Review of Different MOSFET Gate Shape Architectures") reviews many different MOSFET gates shape topologies resulting in improvements in electrical performances of MOS transistors.

#### 2.1 PROBLEMS IN SCALING

CMOS technology scaling has been a primary key for continuous progress in the silicon-based semiconductor industry. Scaling is followed by Moore's Law that provides a simple rule for transistor design to increase circuit density (Fig. 2.1) and speed for a few decades for digital design parts such as microprocessors units, SRAM, DRAM [61]. The improved circuit performances and density enable more complicated functionalities that require more integrated transistors on one single chip. However, as device scaling continues for the 21<sup>st</sup> century, it turns out that the historical growth doubled circuit density and increased performance followed by Moore's Law cannot be maintained only by the conventional scaling theory. Increasing leakage current does not allow further reduction of threshold voltage, which in turn prevents further supply voltage scaling for the speed improvement. Higher electric fields generated inside of the transistor worsen device reliability and increase leakage currents. Moreover, the required high channel doping causes significant challenges such as mobility degradation and random dopants induced threshold voltage fluctuations [62].

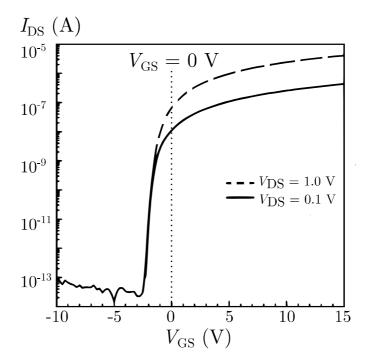

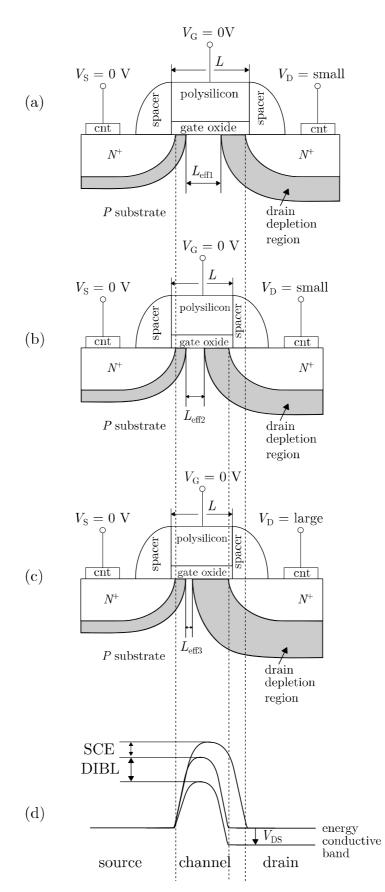

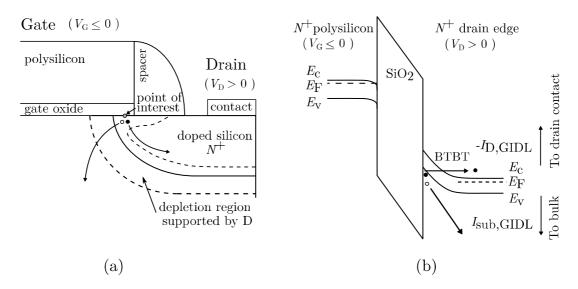

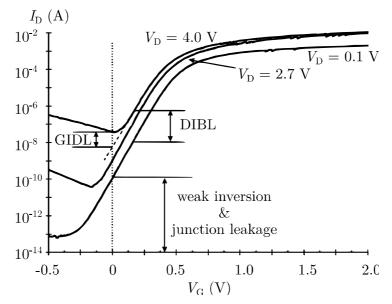

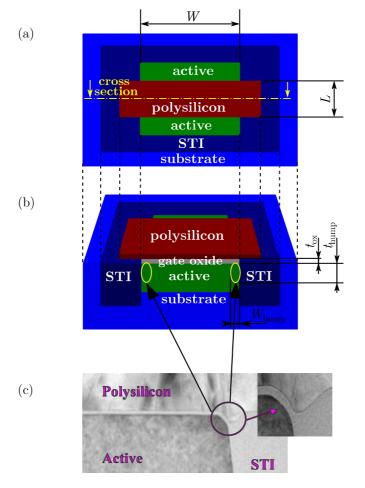

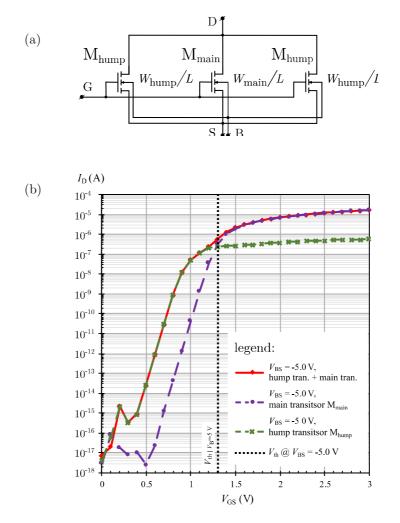

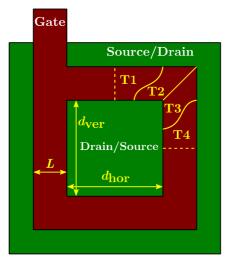

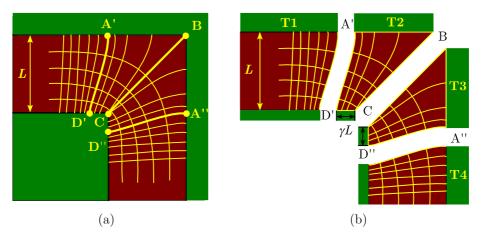

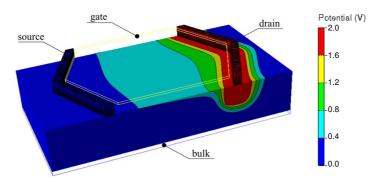

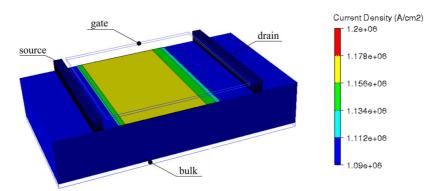

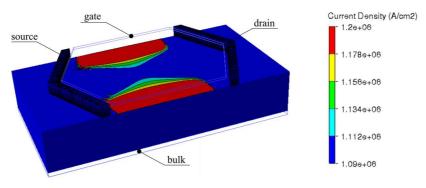

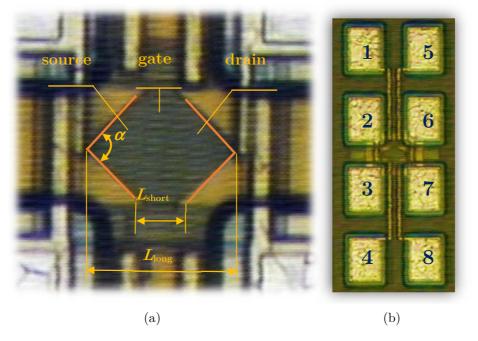

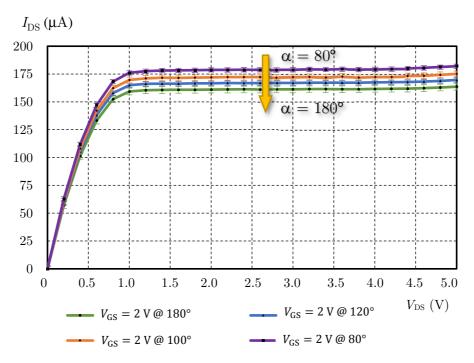

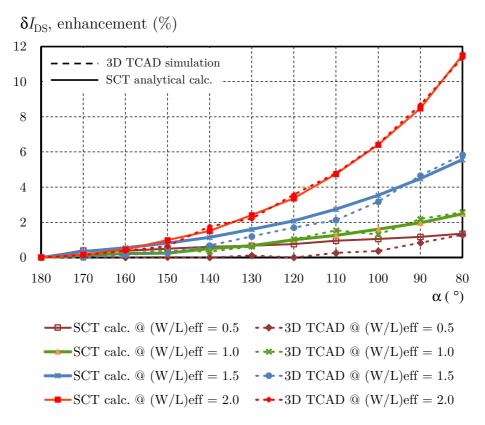

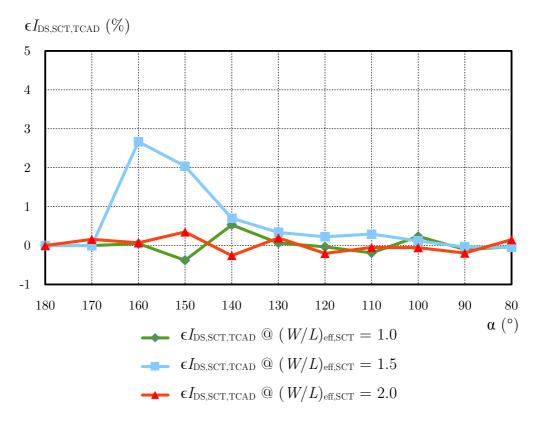

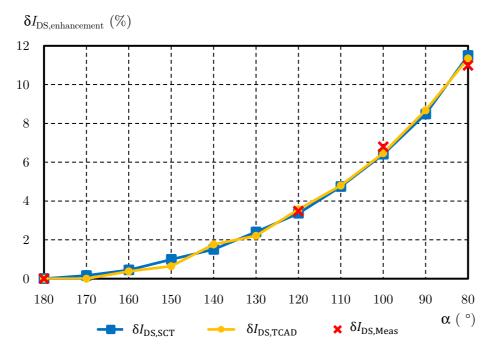

Fig. 2.1: Transistor count per different microprocessors of many vendors (blue circle symbol), transistor per square millimeter of different microprocessors of many vendors (orange diamond symbol), data from [61]