**Master Thesis**

Czech Technical University in Prague

Faculty of Electrical Engineering Department of Electric Drives and Traction

# FPGA Model Development of PMSM for Hardware-in-the-Loop Testing System

Bc. Vojtěch Štěrba

Supervisor: Ing. Tomáš Haubert, Ph.D. Field of study: Electrical Engineering, Power Engineering and Management Subfield: Electrical Drives July 2020

# I. OSOBNÍ A STUDIJNÍ ÚDAJE

| Příjmení:                                                      | Štěrba                   | Jméno: Vojtěch | Osobní číslo: 457076 |

|----------------------------------------------------------------|--------------------------|----------------|----------------------|

| Fakulta/ústav:                                                 | Fakulta elektrotechnická |                |                      |

| Zadávající katedra/ústav: Katedra elektrických pohonů a trakce |                          |                |                      |

| Studijní program: Elektrotechnika, energetika a management     |                          |                |                      |

| Specializace:                                                  | Elektrické pohony        |                |                      |

# II. ÚDAJE K DIPLOMOVÉ PRÁCI

| Název diplomové práce:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------|--|

| FPGA Model Development of PMSM for Hardware-in-the-Loop Testing System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |                                                  |  |

| Název diplomové práce anglicky:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                  |  |

| FPGA Model Development of PMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SM for Hardware-in-the-Loop Testing                       | g System                                         |  |

| Pokyny pro vypracování:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                           |                                                  |  |

| <ol> <li>Analyze current state in the field of Po<br/>2. Develop a real-time simulation with ha<br/>3. Analyze the current FPGA model of P<br/>4. Improve the PMSM FPGA model and</li> </ol>                                                                                                                                                                                                                                                                                                                                                                 | ardware-in-the-loop system for Power Inve<br>MSM machine. | erter ECU.                                       |  |

| Seznam doporučené literatury:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           |                                                  |  |

| <ol> <li>QUANG, Nguyen P. a Jörg-Andreas DITTRICH. Vector Control of Three-Phase AC Machines: System Development<br/>in the Practice . Aufl. Berlin, Heidelberg: Springer-Verlag, 2008. ISBN 9783540790280;3540790284;.</li> <li>WILSON, Peter. Design Recipes for FPGAs: Using Verilog and VHDL [online].Second. GB: Newnes, 2016;2015;. ISBN 9780080971292;0080971296;.</li> <li>BLYLER, John. Software-Hardware Integration in Automotive Product Development [online].Warrendale: SAE<br/>International, 2013. ISBN 0768080525;9780768080520;</li> </ol> |                                                           |                                                  |  |

| Jméno a pracoviště vedoucí(ho) diplo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | omové práce:                                              |                                                  |  |

| Ing. Tomáš Haubert, Ph.D., kated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dra elektrických pohonů a trakce F                        | EL                                               |  |

| Jméno a pracoviště druhé(ho) vedou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | cí(ho) nebo konzultanta(ky) diplomové                     | é práce:                                         |  |

| Datum zadání diplomové práce: 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.02.2020 Termín odevzdání (                              | diplomové práce: 14.08.2020                      |  |

| Platnost zadání diplomové práce: 30.09.2021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                           |                                                  |  |

| Ing. Tomáš Haubert, Ph.D.<br>podpis vedoucí(ho) práce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | podpis vedoucí(ho) ústavu/katedry                         | prof. Mgr. Petr Páta, Ph.D.<br>podpis děkana(ky) |  |

# III. PŘEVZETÍ ZADÁNÍ

Diplomant bere na vědomí, že je povinen vypracovat diplomovou práci samostatně, bez cizí pomoci, s výjimkou poskytnutých konzultací. Seznam použité literatury, jiných pramenů a jmen konzultantů je třeba uvést v diplomové práci.

Datum převzetí zadání

Podpis studenta

# Acknowledgements

I would like to express my gratitude to my supervisor Ing. Tomáš Haubert Ph.D. for the greatest support during my studies and opportunity to work on the topic of this thesis. Without his support and big effort I would have never completed this thesis. Furthermore I would like to thank to Bc. Rafael Banzhaf. His knowledge, experience and goodwill allowed this thesis to happen. Great gratitude goes also to all my Czech and German colleagues and friends who helped me during the thesis.

I would like to also thank my family for moral and material assistance since the beginning of my studies. Without them, I would have never gotten so far and I would have never finished the university.

The last acknowledgement goes to my girlfriend Peta for her never ending patience and support even in the coronavirus breakdown.

"Exactly!" said Deep Thought. "So once you do know what the question actually is, you'll know what the answer means." Douglas Adams, The Hitchhiker's

Guide to the Galaxy

# Declaration

Prohlašuji, že jsem předloženou práci vypracoval samostatně a že jsem uvedl veškeré použité informační zdroje v souladu s Metodickým pokynem o dodržování etických principů při přípravě vysokoškolských závěrečných prací.

In Prague, 5. July 2020

# Abstract

This thesis deals with the problematic of Hardware-in-the-Loop (HiL) systems for control units of High Power Inverters. The text describes the structure of the system for simulations of electric drives in real-time and other necessary components of the Hardware-in-the-loop system. A control unit from an electric vehicle without High Power Stage is connected to the HiL system and an FPGA card is used to simulate electric drives. All time-critical tasks are simulated on the FPGA card. Furthermore, all necessary mathematical models are presented in this work. They run on a real-time PC and calculate all the necessary physical quantities.

In the next part of the work I deal directly with HiL settings, connection with the control unit, bus simulations and implementation of the sensor part.

The third part of this work mathematically describes the models that are implemented on the FPGA card. This model is further extended to foreign phenomena that are neglected in the derivation.

At the end of the work I compare the model with real measurement.

**Keywords:** Mathematical modelling, Hardware-in-the-Loop, PMSM, FPGA, Electric vehicles, Vehicle dynamics, dSPACE

**Supervisor:** Ing. Tomáš Haubert, Ph.D. České vysoké učení technické v Praze, Fakulta elektrotechnická Technická 1902/2 Praha 6, 166 27

# Abstrakt

Tato práce se zabývá problematikou Hardware-in-the-Loop (HiL) systémů pro řídící jednotky výkonových měničů. V textu je popsána struktura systému pro simulaci elektrických pohonů v reálném čase a další nutné součásti Hardware-inthe-loop systému. K HiL systému je připojena řídící jednotka z elektrického vozidla bez výkonnové části a pro simulaci elektrických pohonů je zde použita FPGA karta. Na FPGA kartě jsou simulovány všechny časově kritické úlohy. Dále jsou v této práci představeny nutné matematické modely, které běží na real-time PC a počítají všechny nezbytné fyzikální veličiny.

V další části práce se zaobírám přímo nastavením HiL, propojením s řídící jednotkou, simulací datových sběrnic a implementací sensorové části.

V třetí části této práce jsou matematicky popsány modely, které jsou implementovány na FPGA kartě. Tento model je dále rozšířen, aby zahranoval jevy, které jsou v odvození zanedbány.

V závěru práce je model porovnán s reálným měřením.

**Klíčová slova:** Matematické modelování, Hardware-in-the-Loop, PMSM, FPGA, Elektrická vozidla, Dynamika vozidel, dSPACE

**Překlad názvu:** Vývoj PMSM modelu pro FPGA bla bla doplnit — Vývoj PMSM FPGA modelu pro Hardware-in-the-Loop testovací systém

# Contents

| 1 Introduction                                   | 1  |

|--------------------------------------------------|----|

| 1.1 Motivation                                   | 1  |

| 1.2 Goals of the Master thesis                   | 2  |

| 2 State of art -<br>Hardware-in-the-Loop systems | 3  |

| 2.1 Hardware-in-The-Loop systems                 | 3  |

| 2.2 HiL structure for Power Inverter<br>ECU      | 3  |

| 2.2.1 Real-Time PC                               | 4  |

| 2.2.2 Embedded Control Unit                      | 4  |

| 2.2.3 Electric Motor Simulation Card             | 4  |

| 2.2.4 Bus Simulation Card                        | 5  |

| 2.2.5 I/O cards                                  | 7  |

| 2.2.6 Other Hardware Equipment                   | 7  |

| 2.3 Electric motor simulations providers         | 8  |

| 2.3.1 dSPACE                                     | 9  |

| 2.3.2 ETAS                                       | 10 |

| 2.3.3 Opal RT                                    | 11 |

| 2.4 FPGA                                         | 13 |

| 2.4.1 FPGA design techniques                     | 14 |

| 3 HiL development                                | 17 |

| 3.1 Platform description                         | 17 |

| 3.1.1 ECU description                            | 17 |

| 3.1.2 ConfigurationDesk                          | 19 |

| 3.1.3 FlexRay                                    | 20 |

| 3.1.4 CAN                                        | 23 |

| 3.2 Mathematical models -<br>SCALEXIO            | 23 |

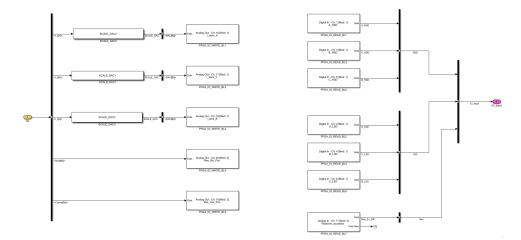

| 3.2.1 FPGA model - processor part                                                               | 24                                                                     |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 3.2.2 Load torque model                                                                         | 25                                                                     |

| 3.2.3 Battery model                                                                             | 30                                                                     |

| 3.2.4 Restbus model                                                                             | 34                                                                     |

| 3.2.5 Ld/Lq model and sensor simulation                                                         | 35                                                                     |

| 4 FPGA model analysis and<br>improvements                                                       | 37                                                                     |

| 4.1 Mathematical models - FPGA                                                                  | 37                                                                     |

| 4.1.1 Coordinate transformation                                                                 | 38                                                                     |

| 4.1.2 PMSM model                                                                                | 39                                                                     |

| 4.1.3 Resolver model                                                                            | 42                                                                     |

| 4.1.4 Power Inverter Model                                                                      | 43                                                                     |

| 4.1.5 Mechanic model                                                                            | 44                                                                     |

| 4.1.6 IO model                                                                                  | 45                                                                     |

|                                                                                                 |                                                                        |

| 4.2 PMSM Model improvements                                                                     | 46                                                                     |

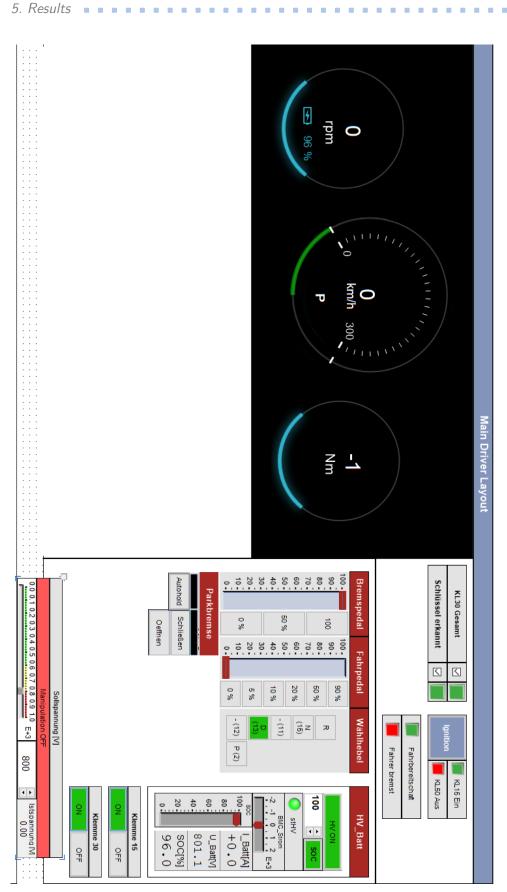

| <ul><li>4.2 PMSM Model improvements</li><li>5 Results</li></ul>                                 | 46<br><b>55</b>                                                        |

|                                                                                                 |                                                                        |

| <ul><li><b>5 Results</b></li><li>5.1 Platform configuration and</li></ul>                       | 55                                                                     |

| <ul><li><b>5 Results</b></li><li>5.1 Platform configuration and mathematical models</li></ul>   | <b>55</b>                                                              |

| <ul> <li><b>5 Results</b></li> <li>5.1 Platform configuration and mathematical models</li></ul> | <b>55</b><br>55<br>55                                                  |

| <ul> <li><b>5 Results</b></li> <li>5.1 Platform configuration and mathematical models</li></ul> | <b>55</b><br>55<br>55<br>61                                            |

| <ul> <li><b>5 Results</b></li> <li>5.1 Platform configuration and mathematical models</li></ul> | <b>55</b><br>55<br>61<br>62                                            |

| <ul> <li>5 Results</li> <li>5.1 Platform configuration and mathematical models</li></ul>        | <ul> <li>55</li> <li>55</li> <li>61</li> <li>62</li> <li>69</li> </ul> |

| <ul> <li><b>5 Results</b></li> <li>5.1 Platform configuration and mathematical models</li></ul> | 55<br>55<br>61<br>62<br>69<br>69                                       |

| <ul> <li><b>5 Results</b></li> <li>5.1 Platform configuration and mathematical models</li></ul> | 55<br>55<br>61<br>62<br>69<br>69<br>d                                  |

# **Figures**

| 2.1 dSPACE SCALEXIO Processing         Unit [1]            |

|------------------------------------------------------------|

| 2.2 dSPACE DS4302 CAN Interface<br>board [1] 5             |

| 2.3 FlexRay logo.[2] 6                                     |

| 2.4 Vector VX 1135 [3], Etas ES 891.1<br>[4] 8             |

| 2.5 dSPACE DS2655 FPGA base<br>board [1]                   |

| 2.6 dSPACE HV E-load module [5]. 11                        |

| 2.7 OP4200 simulator 12                                    |

| 2.8 Xilinx CLB structure [6] 13                            |

| 2.9 FPGA structure. [7] 14                                 |

| 2.10 System generator for DSP<br>blockset                  |

| 2.11 System Generator for DSP,<br>settings view 16         |

| 3.1 SCALEXIO Rack illustration [1] 18                      |

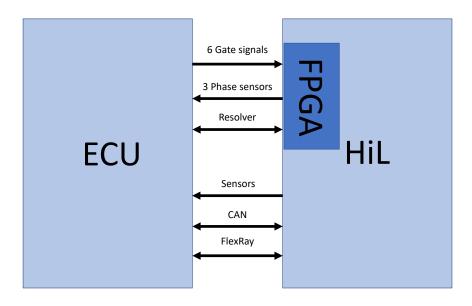

| 3.2 Schematic of HiL and ECU<br>connection 19              |

| 3.3 Example of ConfigurationDesk<br>connection             |

| 3.4 Example of FlexRay Configuration<br>Tool dSPACE [8] 21 |

| 3.5 Example of xml structure for PDU identification. 23    |

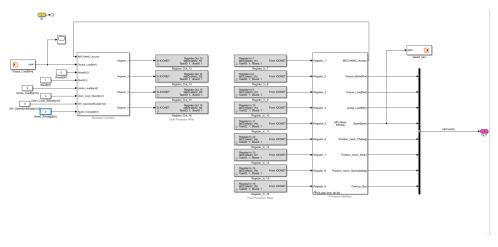

| 3.6 Structure and connections of the models 24             |

| 3.7 Measured brake pedal on race<br>track                  |

| 3.8 $M_{PMSM}$ measured on the race track                  |

| 3.9 Battery cell equivalent circuit                            | 31 |

|----------------------------------------------------------------|----|

| 3.10 Open-circuit voltage                                      | 33 |

| 3.11 Intermediate circuit - active state                       | 33 |

| 3.12 Intermediate circuit - active discharging                 | 34 |

| 3.13 $L_d$ map                                                 | 35 |

| 3.14 Example of temperature sensor curve                       | 36 |

| 4.1 Submodels structure on FPGA                                | 37 |

| 4.2 dSPACE XSG implementation of equation 4.12                 | 41 |

| 4.3 Resolver schematic [9]                                     | 42 |

| 4.4 Resolver SIN winding                                       | 43 |

| 4.5 Resolver COS winding                                       | 43 |

| 4.6 dSPACE XSG implementation of<br>mechanic - processor model | 45 |

| 4.7 dSPACE XSG implementation of<br>mechanic - FPGA model      | 45 |

| 4.8 Submodels structure on FPGA with 3D tables.                | 48 |

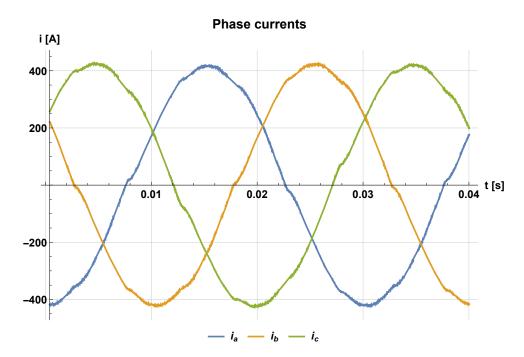

| 4.9 Measured phase currents                                    | 49 |

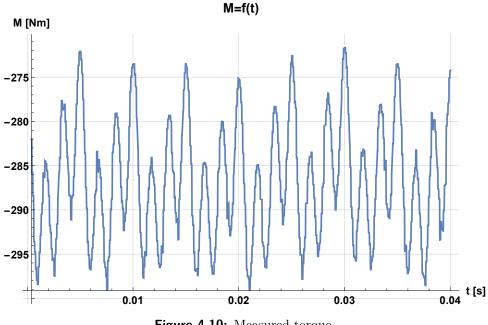

| 4.10 Measured torque                                           | 49 |

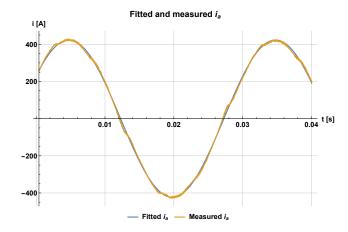

| 4.11 Measured and fitted $i_a$ current.                        | 50 |

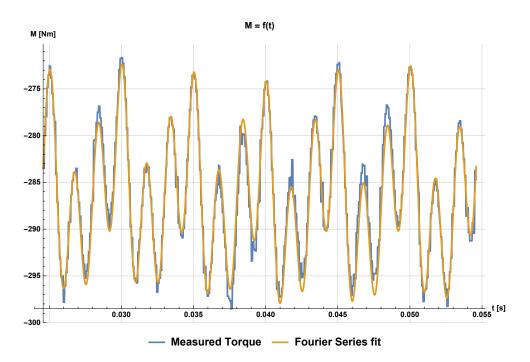

| 4.12 Measured and fitted torque                                | 51 |

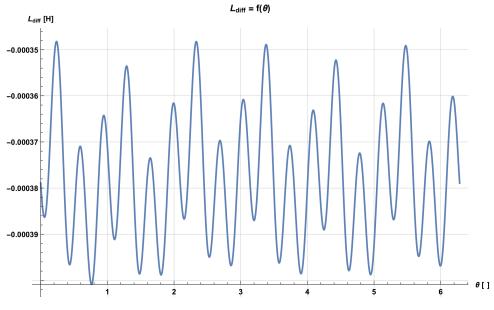

| 4.13 $L_{diff}$ as a function of rotor angle.                  | 52 |

| 4.14 $L_d$ as a function of $i_q$ and theta rotor angle        | 53 |

| 5.1 Flexray measurement with<br>Message Counter and CRC        | 56 |

| 5.2 Created cable harness                                         | 56      |

|-------------------------------------------------------------------|---------|

| 5.3 Example of created<br>ConfigurationDesk settings              | 57      |

| 5.4 Example of ControlDesk layout.                                | 58      |

| 5.5 Example of INCA interface for the ECU.                        | e<br>59 |

| 5.6 Example of CAN bus<br>implementation in<br>ConfigurationDesk. | 60      |

| 5.7 Example of FlexRay bus implementation.                        | 61      |

| 5.8 Final fit for the load torque model.                          | 61      |

| 5.9 Active Discharge of intermediate circuit.                     | 62      |

| 5.10 Model structure after<br>implementation of 3D tables         | 63      |

| 5.11 I/O submodel implementation.                                 | 64      |

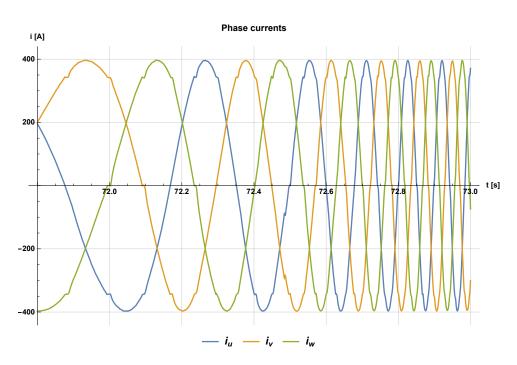

| 5.12 Phase currents during acceleration.                          | 64      |

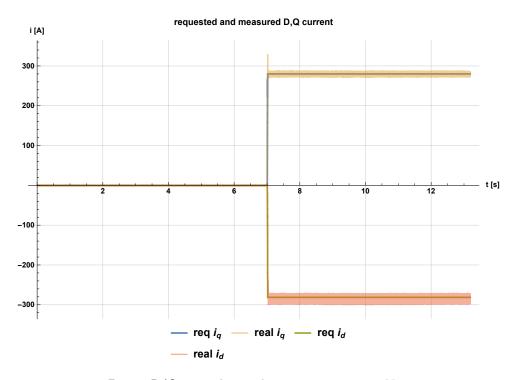

| 5.13 $i_d$ and $i_q$ with torque request 280 Nm                   | )<br>65 |

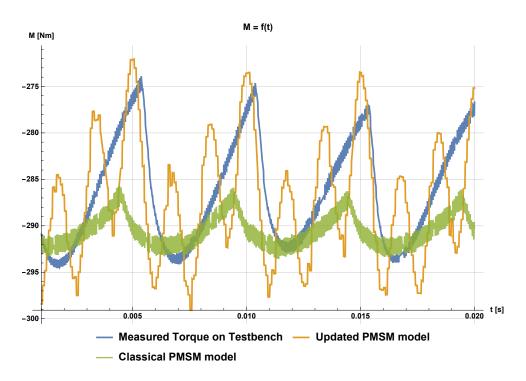

| 5.14 Torque comparison                                            | 66      |

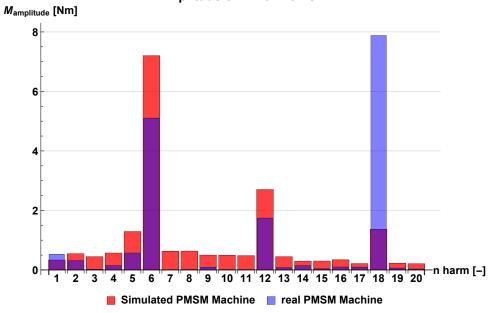

| 5.15 Amplitude comparison                                         | 66      |

| 5.16 Amplitude comparison                                         | 67      |

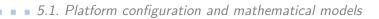

| 5.17 FPGA build report                                            | 67      |

# **Tables**

| 2.1 dSPACE FPGA boards $[1] \dots$         | 10 |

|--------------------------------------------|----|

| 2.2 Opal-RT FPGA solutions [10]            | 12 |

| 3.1 Specific values of battery cell        | 31 |

| 3.2 Time constants of intermediate circuit | 34 |

| 4.1 Common sensor equation values          | 46 |

# Chapter 1 Introduction

The segment of electric vehicle industry has been significantly growing during past years and there are major challenges ahead of the automotive industry. European cities and governments actively support transitions to low emission systems. As a result, European car producers need to develop electrical or hybrid vehicles.

More over during past years, new systems with autopilots are salesblockbusters. To develop those autopilot systems, new algorithms with an enormous software complexity have to be used and new hardware topologies must be considered to overcome related issues. In connection to that, car producers must ensure software reliability and safety. For their simplicity, Hardware-in-the-Loop automated testing systems are developed and used.

# 1.1 Motivation

Electric car consists of many different embedded control units and their connections. Major task is to provide safety and reliability for the costumers. Every minor system in the car has to be tested and verified to ensure its correct behaviour. With never-ending growth of software complexity, automated test system for execution and evaluation are the key milestones. During my studies on CTU FEE I found the problematic around electronic control system, power electronics, real-time simulations very challenging and interesting.

I have been actively working with these systems since my Bachelors thesis and I was given a great opportunity to work and develop new HiL system from scratch. With the gained experience, I tried to improve the system structure.

# 1.2 Goals of the Master thesis

The main goals of this master thesis are following:

- Analyse current state in the field of Power Inverter ECU testing.

- Develop a real-time simulation with hardware-in-the-loop system for Power Inverter ECU

- Analyse the current FPGA model of PMSM machine.

- Improve the PMSM FPGA model and verify it.

# Chapter 2

State of art - Hardware-in-the-Loop systems

# 2.1 Hardware-in-The-Loop systems

The Hardware-in-The-Loop (HiL) is a real-time operating system of multiple units for testing embedded control units in environmental models. The system consists of the unit under the test (UUT), dynamical models and signals for the simulation of needed environment. The system is operating in the real-time to provide results as close to reality as possible.

According to the best scenario all embedded systems would be tested in real environment, but usage of HiL system can reduce the costs of testing. Moreover, it's also possible to run tests, that would be hardly feasible in the real world. For example crash reactions or usage of the systems beyond the range of defined parameters.

The HiL testing is a last development stage before the UUT is released. This testing should provide an assurance that all systems operate correctly, and the final requirements are fulfilled. [11] [12]

# **2.2** HiL structure for Power Inverter ECU

This section provides overview of needed components and overall system structure for electrical machines simulations handling.

Hardware-in-the-Loop systems are nowadays built with a different purpose and different goals. The amount of testing scenarios options is depending on the purpose of the UUT and hardware equipment of UUT. This thesis mostly focuses on HiL testing of Power Inverter ECU, therefore usual HiL structure is presented, and possible simulation models are discussed.

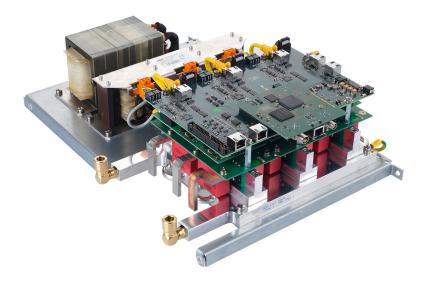

Figure 2.1: dSPACE SCALEXIO Processing Unit [1]

## 2.2.1 Real-Time PC

The main component of the HiL is a real-time running computer. This computer provides a real time simulation of mathematical models with time cycles usually around 1 ms. Real-time computers technology uses mostly standard commercial components for computers. Because of that, system can easily be updated to a newer hardware with higher computing power. Moreover the Real-Time PC is also operated via external User Control Computer. [1]

#### 2.2.2 Embedded Control Unit

Embedded Control Unit (ECU) is the key external component for HiL system. The ECU is the Unit Under Test (UUT). The ECU is usually the same hardware as hardware used in real product. Only additional parts for memory access and calibration are added, therefore it is possible to access internal variable values and easily flash a new software.

## 2.2.3 Electric Motor Simulation Card

Nowadays Power Inverter switching frequency continuously rises and frequencies around 10 kHz are not uncommon. Therefore, model calculations of corresponding physical reality must be carried with appropriate task rate to ensure that the model would match ECU predictions.

However, for this task period Real-Time PC is not suitable and special hardware for the simulation is used - FPGA cards.

"An FPGA is an integrated circuit (IC) that can be programmed for different algorithms after fabrication. Modern FPGAs consist of up to two million logic cells that can be configured to implement a variety of software algorithms. Although the traditional FPGA design flow is more similar to a regular IC

Figure 2.2: dSPACE DS4302 CAN Interface board [1]

than a processor, an FPGA provides significant cost advantages in comparison to an IC development effort and offers the same level of performance in most cases. Another advantage of the FPGA when compared to the IC is its ability to be dynamically reconfigured. This process, which is the same as loading a program in a processor, can affect part or all of the resources available in the FPGA fabric" [13]

#### 2.2.4 Bus Simulation Card

There are usually several ECU's connected in a co-working system (for example car). Those ECUs must cooperate together and therefore bus interface is used. In a HiL simulation usually only one ECU is connected and therefore the rest of bus traffic must be calculated and simulated. Moreover, reactions to bus messages are often considered as a basic test to be carried out with HiL.

Below listed communication protocols are used in automotive industry and therefore are introduced here as an example. [1]

- CAN, CAN FD

- FlexRay

- Automotive Ethernet

- LIN

#### FlexRay

FlexRay (from Flexible Ray) is an automotive network protocol. This protocol was developed by FlexRay consortium and nowadays major German car

.

Figure 2.3: FlexRay logo.[2]

manufacturers are using this protocol or used this protocol in history.

Flexray was developed with a goal to be a deterministic, fault-tolerant and high-speed bus system. Transmission speed can be up to 10 Mbits and compared to CAN, it can be used in dual channel configuration to increase the fault-tolerance. Differential twisted pair wiring is used together with characteristic impedance between  $80\Omega$  and  $110\Omega$ . ECUs can be wired in different topologies from Multi-drop, Star or Hybrid Network. [2]

FlexRay communication cycle is usually around 1 to 5 ms with 4 main parts in. [2]

Nowadays FlexRay is used for example in following companies.

- Audi

- Porsche

- BMW

- Lamborghini

#### CAN

The Control Area Network is a bus developed in 1986 by Robert Bosch GmbH. This protocol was developed with intention to have a new multimaster protocol with non-destructive arbitration mechanism and furthermore there was no need to have central bus master.

Nowadays, this protocol is widely used in different fields, even though automotive industry is still the biggest utilizer. This protocol can be described as a multi-master serial bus, that can connect various ECUs. Connection is made with two differentially wired cables, often noted as CAN-high and CAN-low. Usage of differential pair provides possibility to run the bus on different voltage levels and thus to have a higher interference resistance. Characteristic impedance is  $120\Omega$ . [14]

Various implementations of CAN higher layer protocols bus have been introduced, for example:

• • • • • • • • • • • • • • • • • • 2.2. HiL structure for Power Inverter ECU

- CANopen Industrial automation

- milCAN Military vehicles

- ARINC 812 Aviation industry

- NMEA 2000 Marine industry

In automotive industry, standards are handled by each manufacturer.

# 2.2.5 I/O cards

Nowadays ECU measures and controls multiple systems in reality. To ensure correct entry data for the ECU, additional I/O cards are usually added to HiL system. These IO cards are used e.g. temperature measurement simulations.

Typical I/O card consists of:

- Voltage analogue input/output

- Current analogue input/output

- Voltage digital input/output

- Resistor simulation

Nowadays, manufactures provide lot of specialized cards for various types of simulation. (Gearbox sensors etc.)

# 2.2.6 Other Hardware Equipment

In addition to all listed hardware, other measurement tools are often connected to a HiL system. Those devices are often used as a measurement, calibration, and prototyping tools. They provide possibility to verify bus traffic with external measurements, they also provide option to online calibrate and measure connected ECU. With those devices timing measurements or algorithms verifications can easily be evaluated.

As an example, calibrations devices that can be used are listed:

- Etas ES891

- Vector VX1135 base module

Furthermore, HiLs are often designed to be easily extended and connectible with other hardware units. Examples of those units are listed below.

**Figure 2.4:** Vector VX 1135 [3], Etas ES 891.1 [4]

- Failure Injection Unit

- Oscilloscope carrier

- External bus connectors

- Break-Out panel

# 2.3 Electric motor simulations providers

This section provides information about HiL system manufacturers for Power Inverters and system overview for electrical machines simulations.

Special hardware for electrical machines simulation must be used. There are several options on the market with different advantages and disadvantages in case of HiL electrical machines control testing. In following sections, various solutions of hardware are presented together with a model solutions.

Main manufacturers for Power Inverters Hardware-in-the-Loop testing systems are listed.

- dSPACE

- ETAS

- Opal-RT

• 2.3. Electric motor simulations providers

Figure 2.5: dSPACE DS2655 FPGA base board [1]

# 2.3.1 dSPACE

#### Signal level testing

This section describes dSACE HiL solutions on signal level testing. In this setup, High power stage is removed from the ECU and only logical signals are present.

There are several hardware solution offered by dSPACE, therefore, following hardware comparison table 2.1 is introduced. According to [1], these FPGA boards are designed for applications that require very fast, high-resolution signal processing, for example:

- Hybrid vehicle applications

- Electric drive applications

- FPGA-based electric drive simulation

- Power electronics simulation

- Electric motor control development

Moreover, every FPGA base board can be extended with I/O modules (DS2655M1, DS2655M2, DS5450 SC) to increase capabilities and amount of channels on the board.

dSPACE offers **RTI FPGA Programming Blockset**, **XSG Electric Components Library** and **XSG AC Motor Control Library** for effortless model implementations. Those components are implemented and developed via Xilinx<sup>®</sup> System Generator Blockset.

$<sup>^1\</sup>mathrm{DS6602}$  is also equipped with additional 4 GB on board RAM and 36 000 kbit Ultra RAM

|                     | Logic cells                         | Distributed RAM | Block RAM                |

|---------------------|-------------------------------------|-----------------|--------------------------|

| DS2655 7K160        | $162 \ 240 \ (DSP \ slices: \ 600)$ | 2 188 kbit      | $11~700~{\rm kbit}$      |

| DS2655 7K410        | $406\ 720\ (DSP\ slices:\ 1540)$    | 5~663 kbit      | $28\ 620\ \mathrm{kbit}$ |

| $\mathbf{DS6601}$   | $444\ 000\ (DSP\ slices:\ 1700)$    | 5 908  kbit     | 19,000 kbit              |

| $\mathbf{DS6602}^1$ | 1 143 000 (DSP slices: 1968)        | 9 800  kbit     | 34,600 kbit              |

Table 2.1: dSPACE FPGA boards [1]

RTI FPGA Programming Blockse provides RTI blocks for implementing the interface between the FPGA mounted on a dSPACE board and its I/O, and the interface between the dSPACE FPGA board and its computation node.

XSG Electric Components Library contains closed loop models of corresponding electrical machines. These models are calculated with high oversampling rate, where no PWM synchronizations are necessary.[15]

Models of following machines are provided with a corresponding inverter and sensor models [16]

- Permanent Magnet Synchronous Motor

- Brush-less DC motor

- Asynchronous Squirrel cage Induction Motor

#### High-Power testing

dSPACE is currently providing special system for power inverter testing, where the ECU is not tested on signal level, but the HiL system is built on so called **Hight-Voltage Electronic Load** solution. According to [1], one HV E-load module can be used with voltages up to 800 V and currents 70A/100A (continous/peak).

This module is directly designed for multiple parallel operations to support higher currents. This module must also be used together SCALEXIO unit, in which the model calculations are evaluated. [5]

Therefore, UUT directly operates in almost real environment thanks to which critical testing conditions, that cannot be performed with a real machine, can be evaluated.

# 2.3.2 ETAS

The ETAS ES5340 PCIe are internal computer cards developed specially for simulation of electrical motors in automotive industry.

Figure 2.6: dSPACE HV E-load module [5].

The ETAS ES5340 PCIe simulation boards are connected to the control computer motherboard by PCI slots. These cards can be used to simulate the behaviour of electric motors, combustions engines, IGBT stages and electrified power-trains. That means that various motors can be parametrized and simulated.

Simulation cards are connected to PWM gate control signals generated in the tested power inverters. IGBT stage with PMSM is simulated.[17]

According to [17], the main benefits of the ES5340 are following:

- Calculations are carried with a step size of 850 ns.

- Phase current prediction.

- Various sensors can be configured on each output.

- Software models (LABCAR-RTPC) are synchronized with the PWM period by means of a task trigger.

# 2.3.3 Opal RT

#### Hardware solution

Opal-RT is providing multiple industrial solution for easy HiL system development, Rapid Control Prototyping together with I/O expansion capabilities. Furthermore, user-friendly automation environment can be used in connection with Opal-RT systems. Following hardware systems are recommended for Power electronics simulations:

Figure 2.7: OP4200 simulator.

| Name          | Hardware Solution | Logic cells | Distributed RAM           | Block RAM      |

|---------------|-------------------|-------------|---------------------------|----------------|

| <b>OP4510</b> | Xilinx XC7K325T   | 326  080    | 4 000 kbit                | $16\ 020$ kbit |

| <b>OP5705</b> | Xilinx XC7VX485T  | 485  760    | $8 \ 175 \ \mathrm{kbit}$ | 37,080 kbit    |

Table 2.2:

Opal-RT FPGA solutions [10]

- OP4200

- OP4510

- OP5707

The eFPGASIM suite is used for testing and validation of power electronic systems and covers a wide range of applications, from renewable energy conversion to highly complex multi-modular converters. Developers can use eHS electrical solver to easily bring models to real-time simulation. E-machine simulations are based on Xilinx® Virtex®-7 FPGA. According to [18], it is possible to run basic machine model with minimum task of 100 ns.

#### Model solution

Opal RT offers their eFPGASIM Power electronix toolbox with Modular Multilevel Converter Models. This tool can be used for easy model development from prepared model or a user can directly access the model structure using Xilinx System Generator for DSP.

Opal RT FPGA Electric Machine Library includes following models:

Permanent Magnet Synchronous Machine (PMSM, IPM, BLDC, SPM)

Figure 2.8: Xilinx CLB structure [6]

- Variable D-Q model

- Spatial Harmonics model

- Induction Machine (DFIG, DFIM, Squirell Cage Induction Machine)

- Switched Reluctance Machine

Furthermore, Opal-RT provides possibility to import data measurements from Finite Element Analysis (FEA) tool for example JMAG-Studio, Infolytica's MotorSolve or ANSYS Maxwell. FEA is mostly useful, once classical models can't be used. For example due to big rotor asymmetry. [18]

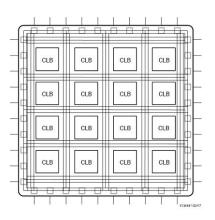

# 2.4 FPGA

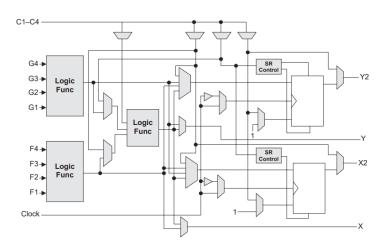

Field Programmable Gate Arrays (FPGAs) are semiconductor devices that are based around a matrix of configurable logic blocks (CLBs) connected via programmable interconnects. FPGAs can be reprogrammed to desired application or functionality requirements after manufacturing. FPGA design mostly fits applications, where the flexibility and re-usability are requirements altogether with high frequency operations 100 MHz. [6]

FPGAs are heterogeneous compute platforms and are made with various parts including Block RAMs, DSP slices and Programmable logic. Because of the selected structure, parallelism and pipelining can be used.

Basic structure of FPGA is following and is usually called Configurable Logic Block /CLB)[7]:

• Look-up table - This element performs logic operations

- Flip-Flop This register element stores the result of the LUT.

- Wires These elements connect elements to one another.

- Input/Output (I/O) pads These physical ports get data in and out of the FPGA.

# 2.4.1 FPGA design techniques

## VHDL

Nowadays, there are several options how to process algorithm device into the FPGA. One of those option is usage of VHDL. VHDL is a hardware description language often used for programming of FPGAs and other electronic integrated circuits.

When synthesizing VHDL language for usage on FPGA, there are three main specific functions to be executed. [6]

- 1. Mapping Logic functions mapped onto CLBs.

- 2. Placement CLBs placed on FPGA.

- 3. Routing Routed connections between CLBs

However, today algorithms are too complex to be manually mapped, and therefore synthesis software is used to turn VHDL into logic functions mappable into the FPGA. Due to the FPGA structure and its limited resources, algorithms size must be considered carefully and optimized.

Figure 2.9: FPGA structure. [7]

2.4. FPGA

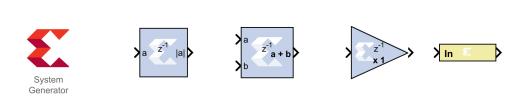

Figure 2.10: System generator for DSP blockset.

#### System generator for DSP

Another option how to program FPGA devices is nowadays System generator for DSP made by Xilinx. System generator for DSP is Matlab Simulink add-on designed to simplify FPGA development with all the benefits of the Simulink environment. In system generator for DSP, more than 100 RTL optimized Simulink blocks are present. Moreover, system design can be easily verified with online Simulink hardware accelerated simulations. This option is used by **dSPACE XSG libraries** and, therefore, FPGA model in this thesis is based on System generator for DSP. All information in the section are taken from [19].

Furthermore, direct code generation to packaged IP or low-level VHDL is possible with Timing and Resource analysis.

Various libraries are prepared for the developer, where some blocks are low-level (bit shifting or delays) and others can be described as high-level implementations (signal processing). Following examples of DSP libraries are listed:

- **Basic Elements** Standard building blocks for digital logic

- **Control Logic** Blocks for control circuitry and state machines

- **Data Types** Blocks that convert data types (includes gateways)

- **Floating-Point** Blocks that support the Floating-Point data type

- Math Blocks that implement mathematical functions

- Memory Blocks that implement and access memories

- **Tools** "utility" blocks

System generator supports calculation and design with different number data types such as Boolean, floating point and arbitrary precision fixedpoint values. This is in contrast with the fundamental Simulink number representation in double precision floating point and thus conversion blocks (Gateway In, Gateway Out) must be used, when DSP is used together with other Simulink blocks. Most of the Xilinx blocks can also deduce

#### 2. State of art - Hardware-in-the-Loop systems

| System Generator: PMSM_v2_Table/FPGA                                               | - 🗆 X            |  |  |

|------------------------------------------------------------------------------------|------------------|--|--|

| Compilation Clocking General                                                       |                  |  |  |

| Board :                                                                            |                  |  |  |

| > None                                                                             |                  |  |  |

| Part :                                                                             |                  |  |  |

| > Kintex7 xc7k160t-2fbg676                                                         |                  |  |  |

| Compilation :                                                                      |                  |  |  |

| > HDL Netlist                                                                      | Settings         |  |  |

| Hardware description language : VHDL li                                            | brary :          |  |  |

| VHDL vil_defaul                                                                    | lib              |  |  |

| Use STD_LOGIC type for Boolean or 1 bit wide gateway                               | 8                |  |  |

| Target directory :                                                                 |                  |  |  |

| .\sysgen                                                                           | Browse           |  |  |

| Synthesis strategy : Implementation                                                | n strategy :     |  |  |

| Vivado Synthesis Defaults $\checkmark$ Vivado Implementation Defaults $\checkmark$ |                  |  |  |

| Create interface document Create testben                                           | ch Model upgrade |  |  |

|                                                                                    |                  |  |  |

| Performance Tips Generate OK Apply                                                 | Cancel Help      |  |  |

Figure 2.11: System Generator for DSP, settings view

their data automatically to ensure no precision is lost. Overflow options are saturation, truncation, and overflow error.

Floating point number representation in DSP is in compliance with IEEE-754 standard for floating point arithmetic. User can select from Single, Double or Custom precision type. Single precision is 32 bits long, with 8 bits for the exponent, 24 bits for the fraction. Double precision is 64 bits. In Custom precision, user can freely decide bit width for exponent width and fraction width.

Algorithm functionality logic can easily be verified by Simulink interface. However, design must be furthermore verified with additional tools to make sure it will work on target device. **Timing Analysis** can be used to verify that timing requirements have been met in critical paths. **Resource Analysis** is the tool for verification of resources being used by HDL design and thus that design will fit into the target device.

# Chapter 3

# **HiL development**

In this chapter, development of the real-time HiL platform is discussed. All necessary steps for successful real-time simulations are presented. Cable harness for ECU connection is shown, followed by basic SCALEXIO settings. Furthermore, CAN and FlexRay implementations are discussed in connection with corresponding Restbus simulation models. Simulink models are presented.

# **3.1** Platform description

For the development of the HiL system, dSPACE SCALEXIO system was used. This system was bought by Porsche Engineering Services to provide automated ECU testing. However, there has been delay in the development of the ECU, that was supposed to be connected to HiL. Therefore, I had chance to use this platform for development of models mentioned in this thesis.

The SCALEXIO system in Porsche Engineering is a multicore system originally developed to be working with 3 ECUs. Therefore, this system is equipped with various I/O and BUS capabilities. Moreover, 2 FPGA DS2655 together with 6 DS2655m1 I/O modules are built in the HiL to provide accurate PMSM real-time simulations.

CAN, FlexRay, Lin and Automotive Ethernet bus systems can be simulated on the HiL system.

## **3.1.1 ECU description**

The ECU used in this thesis was originally developed for Porsche Taycan. Special derivation of this ECU with no High Power stage was used. Moreover, Porsche Taycan is already in production since 2019, thus ECU software is finalized.

Figure 3.1: SCALEXIO Rack illustration [1]

In the real vehicle, ECU works with 3 phase PMSM placed in the front axes and can work with DC current up to 300 A. High Voltage system is built on 800 V.

High Power stage is removed and therefore, all logic signals sent from High Power stage to ECU must be simulated to ensure proper behaviour.

#### Cable Harness

To provide conductive connection between the HiL and ECU, cable harness has to be used. This harness is made on specification of the manufacturer of the ECU and manufacturer of the HiL. Cable harness is terminated with dSPACE hypertac connector on the HiL side and various connectors on the ECU side.

Connections were made for following signal groups:

- Power Supply

- Bus

- CAN

- FlexRay

- Temperature sensors

- Current sensors (DC and AC)

- Voltage sensors

- Internal diagnostic

- Gate signals

- Resolver

Figure 3.2: Schematic of HiL and ECU connection.

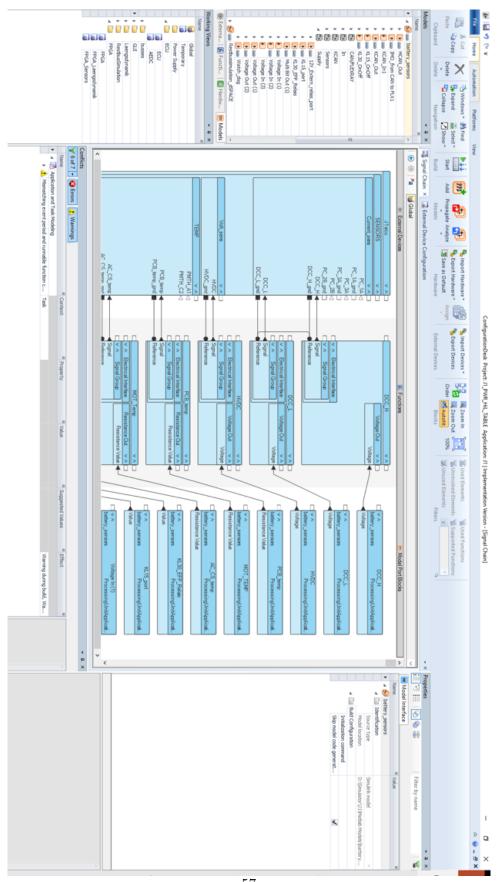

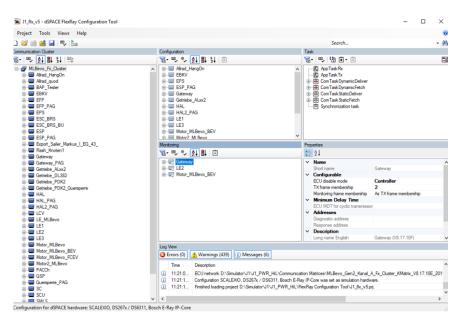

## 3.1.2 ConfigurationDesk

ConfigurationDesk is developed by dSPACE and is the main integration tool for HiL related processes. It provides graphical interface for implementation of behaviour models. It is possible to view the signal path from ECU through the I/O of the HiL to behaviour model.

When the SCALEXIO platform is connected to control PC, ConfigurationDesk automatically loads hardware description files from Platform and correct mapping on IO function can be finalized.

ConfigurationDesk is divided into 7 main working views, where following parameters can be managed.

**Project** - view set is general window for project management. Project version with all the changes are listed here, together with all important project related files

Model Function - is view, where creating and configuring of I/O functions in model structure, optimized for Simulink oriented users

**Signal Chain** - for working with complete signal chains, e.g., external devices, functions, and model port locks

Buses - view set for bus configuration

${\bf Tasks}$  - table for tasks configuration

3. HiL development

Figure 3.3: Example of ConfigurationDesk connection.

Multiple Models - for managing multiple models and multiple processing unit applications

**Builds** – for controlling the build process

In the developed simulation, default simulation task is set to 1ms, with model priority:

In signal chain view, all inputs and outputs mentioned in 3.1.1 are mapped to corresponding I/O pin and afterwards behaviour model is connected. To visualize this chain, following figure 3.3 is enclosed.

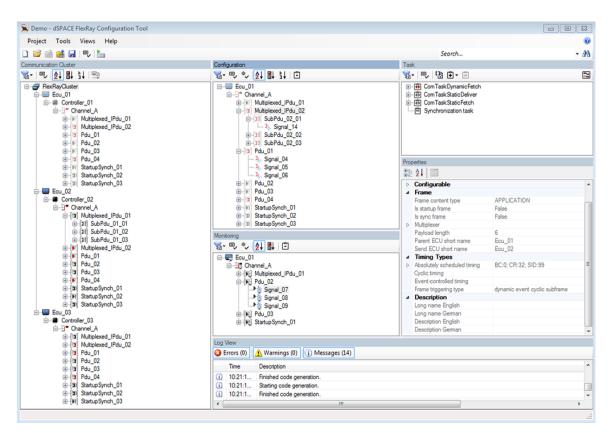

## 3.1.3 FlexRay

To implement FlexRay bus communication into SCALEXIO platform, another dSPACE software must be used. FlexRay Configuration Tool can be used to set up monitoring and simulation of FlexRay nodes.

Simulation is set up based on the communication matrix (FIBEX or AU-TOSAR XML). In the case of HiL simulations with one concrete ECU, user can set up the simulation by choosing the ECU and all other communication ECUs are directly created.

In the monitoring view, real ECUs connected to the HiL system must be placed in order to have access to received messages. Furthermore, user can add even simulated ECUs to the measuring window to easily verify bus traffic.

In the configuration view, simulated ECUs are entered, and their properties can be easily adjusted. Developer can adjust wake-up frames, signal scaling, minimal, maximal and default value etc.

In the task view, corresponding tasks for signal sending and receiving are created. Where Rx stands for messages sent from platform to ECU, Tx for messages sent from ECU to platform.

After successful set up, developer can generate RTI FlexRay Configuration Blockset for Simulink to have a possibility for behaviour model connection. [8]

. . . .

3.1. Platform description

Figure 3.4: Example of FlexRay Configuration Tool dSPACE [8].

#### E2E protection

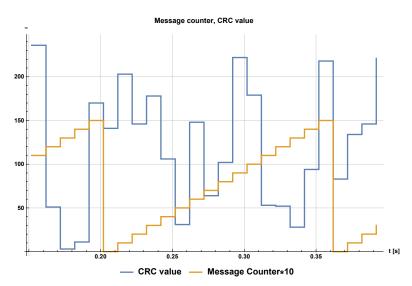

E2E (End-To-End) protection is implemented when data safety exchange must be ensured. When the E2E protection is used, faults in lower layers can be detected, and communication is protected against communication faults, such as random hardware faults introduced by the MCU hardware, communication peripherals, transceivers, communication lines or other communication infrastructure.

The main concept of E2E protection is to add additional parts to the message, where the sending ECU encodes information about the content of the ECU. Receiving ECU then decodes the information and compares it with the content of the message.

In the concept of the E2E, so called message counter is also present. Message counter increments with every sent message. Message counter has a define bit length and when the maximal possible number is reached, message counter is resettled to 0. [20]

**CRC.** Cyclic Redundancy Check is one of the methods, how to detect faults in the communication. In mathematical way, CRC can be described as a

3. HiL development

polynomial division. The data is interpreted as the coefficients of a giant polynomial which is divided by a given CRC polynomial. The remainder of this division is the CRC.

"Polynomial division of polynomial p(x) by another polynomial q(x) can be expressed as finding s(x) so that there is r(x) (the remainder polynomial) with a degree of less than the degree of q(x) s:

$$p(x) = s(x) \cdot q(x) + r(x) \tag{3.1}$$

Using this, the set of polynomial congruence classes F2[x]=pCRC(x) can be defi

ned: Each element r(x) within this set is one of the possible remainders and represents all polynomials which leave r(x) as the remainder when divided by pCRC(x). The computation of the CRC is a polynomial division which computes the remainder of our data-polynom (after it's multiplied by x N for technical reasons). So finally, calculating the CRC is defined as finding a polynomial b(x) so that there is an r(x) with a degree of less than N so": [21]

$$a(x) \cdot x^N = b(x) \cdot p_{CRC}(x) + r(x) \tag{3.2}$$

There are several more effective ways how to calculate CRC with bit-oriented algorithms. This is also the way, how the CRC algorithm is implemented

As direct implementation of chosen algorithm cannot be enlisted, algorithm mentioned in [20, p. 15] can be used as a close example of implementation.

- 4-bit counter is used (0 to 15) and counter is incremented with every sent message

- message key for the CRC calculation is 8 bits long.

- Each data, which is protected by a CRC owns a dedicated DataIDList which is deposited on the sender site and all the receiver sites.

Only the important PDUs, where data safety must be ensured, contain the E2E protection. Mostly messages regarding safety (Airbag or Active Discharging), control mode messages (requested control mod, requested torque), or battery management system messages.

To implement the above mentioned, C-code modules can be implemented in FlexRay Configuration Tool to provide access to bit format of the message. Moreover, FlexRay Configuration Tool also provides possibility to implement xml structure, where each PDU has assigned *ID* to be easily identified.

```

<frame>

<name>MSG_EM1_11</name>

<id>2049</id>

</frame>

<frame>

<id>2049</id>

</frame>

<id>2050</id>

</frame>

<frame>

<frame>

<id>2050</id>

</frame>

</frame>

```

**.** . . . .

Figure 3.5: Example of xml structure for PDU identification.

# 3.1.4 CAN

For CAN bus implementation and settings, ConfigurationDesk is used. In the card "Buses" user can upload corresponding bus description file (usually called K-Matrix). According to this description file, user can decide which messages should be simulated and which messages are sent by the real ECU.

User tab "Buses" has various subsection.

- **Bus Configurations** tab provides overview of the bus settings

- **Bus Access Requests** provides possibility to choose on which hardware board and channel is the simulation running

- **Bus Simulation Features** tab is used for setting-up of the simulated messages on the HiL system.

- **Bus Inspection Features** tab is used for setting-up of the receiving messages by the HiL system from ECU.

- **Bus Manipulation Features** tab is used for real-time manipulation in feed-through mode. (This mode is not used with HiL systems)

- **Bus Configuration Function Ports** tab is used for connections of the messages to Simulink models.

# **3.2** Mathematical models - SCALEXIO

Mathematical model is a system of differential equations describing certain physical aspects. Mathematical model of electrical machine provides possibility to study its behaviour in controlled conditions. In case of HiL testing, usage

#### 3. HiL development

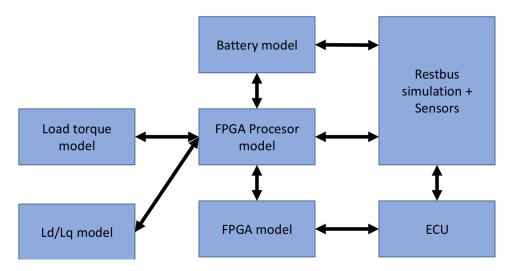

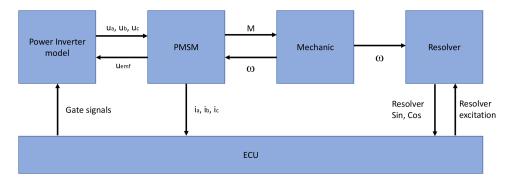

Figure 3.6: Structure and connections of the models.

of mathematical models can help to verify ECUs software and more over, study the system at its physical limits.

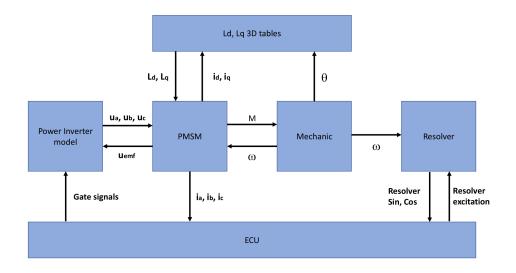

To provide overall system structure overview figure 3.6 is present. In this figure, models connection are shown altogether with the ECU. However these connections are only schematic. Full description can be found in section 3.1.1 and 4.1.

All models mentioned in this section are running on the processor board of the SCALEXIO system with task 1 ms.

## **3.2.1 FPGA model - processor part**

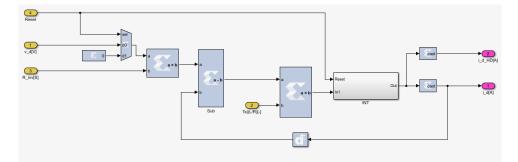

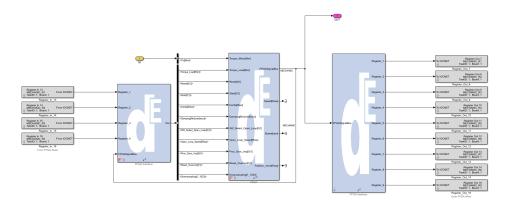

To handle real-time FPGA simulation on the dSPACE SCALEXIO platform, additional model running on the real-time PC must be added. This model works as an interface between FPGA calculations and ControlDesk for model control.

In this model, equivalent blocks for the structure created for FPGA are generated. This provides user option to parametrize the model, visualize its internal values and also connect calculated FPGA signals to other necessary systems.

dSPACE provides special Simulink models blocks to set up communication with the FPGA over the IOCNET (optical connection inside the SCALEXIO system). They are so called "Register blocks" and one block can handle up to 32 bits of data. Various calculations, that can be handled on the real-time pc are not time critical and are pre-evaluated on the real-time pc and then sent to FPGA. For PMSM sub-model, following parameters can be set up and online manipulated:

- Stator resistance  $R_s$

- $L_d$  and  $L_q$  inductance

- Flux of permanent magnets  $\Psi$

- Transformation constant

- Machine topology

Additionally, following signals are received from FPGA card.

- *i<sub>a</sub>*, *i<sub>b</sub>*, *i<sub>c</sub> i<sub>d</sub>*, *i<sub>q</sub>*

- M<sub>PMSM</sub>

- $\bullet$   $u_d, u_q$

- $\bullet$   $u_{emf}$

#### **3.2.2** Load torque model

Informations in following section are taken from [12].

As mentioned in section 4.1, electrical transients of the PMSM machine and corresponding mechanic is calculated inside of the FPGA card. These transients change with very short time constants and therefore classical Simulink model with time period around 1 ms is not suitable.

However,  $M_{load}$  changes with reasonable time constants and Simulink model for the torque load calculation can be used. Corresponding  $M_{load}$  components are described in the following paragraphs.

There are various forces in real car, which differ in the direction and their magnitude. In this subsection simplified load model of the car is described. The drag force, brake force, rolling resistance force is used in the calculation.

The motion of vehicle can be described by various differential equations with a different complexity. There are many simplifications introduced for purposes of this HiL system. To keep the the computing complexity low and also satisfy the precision of simulation, these quantities are taken in context. 3. HiL development

- The model is made as a longitudinal. Lateral movements of the vehicle are not calculated, because those quantities do not significantly affect power electronics.

- The vehicle is considered as ideal rigid.

- The resultant force is in the center of gravity

#### Gravitational force

Any two objects with a mass attract each other with a force called gravitational force. On earth gravity gives weight to physical object. This force is directly proportional to the product of their masses and inversely proportional to the square of the distance. For our proposes when the distance between a vehicle and Earth is from the Earth size point of view constant, we will consider a gravitational field with gravitational constant. Gravitation force is defined as [22]:

$$\vec{F}_q = m \cdot \vec{g} \tag{3.3}$$

Even though in the HiL testing road profile doesn't have to be simulated, in the section 3.2.2, the vehicle was moving on a real track where the track angle  $\alpha$  was changing. According to this, following equation can be written as:

$$\vec{F}_g = \vec{F}_g \cdot \sin \alpha = m \cdot \vec{g} \cdot \sin \alpha \tag{3.4}$$

#### Rolling resistance force

For better simulation results, rolling resistance was added to the load model of the vehicle. According to [22] rolling resistance is force acting in opposite direction of vehicle motion. The magnitude of the force is directly proportional to the normal component of the gravitation force. The equation (3.5) is describing rolling resistance force.

$$\vec{F}_{RollingRes} = \mu_0 \cdot |\vec{F}_g| \cdot \cos(\alpha) \tag{3.5}$$

where  $\mu_0$  is a friction coefficient.

Friction coefficient is strongly affected by many physical aspects and to simulate a correct behaviour of friction coefficient car velocity, temperature, materials of the wheels and surface, inflation of the tires and many more physical aspects must be taken in consideration. Simulation of all these parameters would take a lot of simulation time and as a result,  $\mu_0$  is considered to be constant with value of 0.01. This value is provided by [23]. [12]

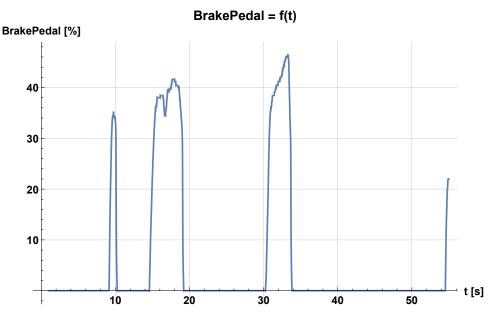

#### Brake pedal

Brake pedal is also simulated in vehicle dynamics model for the needs of HiL testing. Input for brake pedal is stimulated in GUI by slide-bar with value range 0 - 100. Braking force is then calculated by (3.6)

$$\vec{F}_{Brake} = \vec{Br} \cdot k \tag{3.6}$$

Br is the value stimulated via user interface, k is linear coefficient.

Even though this linear equation doesn't precisely describe non-linear physical phenomena, for the purposes of the HiL testing linear equation is sufficient.

Drag force

A drag force is the resultant force of forces acting opposite to the relative motion of any object moving in respect to the surrounding fluid. In the vehicle dynamic model is drag force implemented by following equation (3.7),

$$\vec{F}_{Air} = \frac{1}{2} \cdot \vec{v}^2 \cdot A \cdot C_D \cdot \rho_{Air} \tag{3.7}$$

where  $\vec{v}$  is vehicle velocity relative to fluid, A is the cross section area,  $C_D$  is a drag coefficient and  $\rho_{Air}$  is in this case density of air. This equation is formally identical to [24] as well as values used. [12]

### Resultant force

Resulting load force is calculated as sum of forces described in equations 3.7, 3.6, 3.5.

$$\vec{F}_{Load} = \vec{F}_{Air} + \vec{F}_{RollingRes} + \vec{F}_{Brake} + \vec{F}_g \tag{3.8}$$

$\vec{F}_{Load}$  is afterwards recalculated to appropriate torque with equation 3.10

$$\vec{F}_{Load} = \frac{1}{2} \cdot \vec{v}^2 \cdot A \cdot C_D \cdot \rho_{Air} + \mu_0 \cdot |\vec{F}_g| \cdot \cos(\alpha) + k \cdot Br + m \cdot \vec{g} \cdot \sin(\alpha)$$

(3.9)

3. HiL development

$$\vec{M}_{Load} = \vec{F}_{Load} \cdot r \tag{3.10}$$

. . .

Where r is the car wheel diameter.

#### Gear box

In order to keep the PMSM in better efficiency areas, there is a one speed gearbox in the car. Gear box mathematical model is simulated by equation (3.11). This simplified model is implemented for easy recalculation of load torques from side of the vehicle to the side of the EM-machine,

$$M_{Wheel} = M_{EM} \cdot i_i \tag{3.11}$$

where  $M_{Wheel}$  is torque on output shaft,  $M_{EM}$  is torque on input shaft from PMSM and  $i_i$  is a conversion ratio

$$i_i = \frac{\Omega_{in}}{\Omega_i} \tag{3.12}$$

This equation is identical to the equation used in [25].

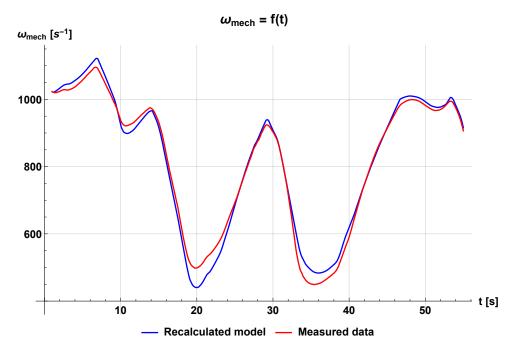

#### Parameters fitting

Even with the proposed load torque model, various parameters are unknown or inaccurate. Therefore Least square method of parameter fitting is introduced. This method uses numerical optimization in software Wolfram Mathematica and real vehicle measurement on race track.

Least square method is regression analysis method developed in the early 1800s by Karl Friedrich Gauss, Adrien Marie Legendr. The unknown parameters are estimated by minimizing the sum of the squared deviations between the data and the model. This method can be used for linear models with overdetermined parameters. [26]

Because torque load model is linear model in its parameters in polynomial form. This equation combines equation from load model 3.9 and 4.22 and fully describes movement equation.

$$M_{PMSM1}(t) + M_{PMSM2}(t) - \beta_0 sin(\alpha(t)) - \beta_1 \omega^2(t) - \beta_3 Br(t) - \beta_4 \epsilon(t) - \beta_5 cos(\alpha(t)) = 0$$

(3.13)

where  $M_{PMSM1}(t)$ ,  $M_{PMSM2}(t)$ ,  $\alpha(t)$ ,  $\omega(t)$ ,  $\epsilon(t)$ , Br(t) are time variant parameters, that can be extracted from a real car measurement, whereas  $\beta_i$  are unknown or problematically measurable parameters. To overcome this issue, equation 3.14 is furthermore adapted to following form, where a new member of equation is added with additional point measurement. Because this overdetermined system is solved by minimization, every member is also square powered. Driving torque is simplified as a sum of driving torques from front a rear machine.  $M_{PMSM1}(t) + M_{PMSM2}(t) = M_{PMSM}$ .

$$\sum_{t_1}^{t_n} (M_{PMSM}(t) - \beta_0 sin(\alpha(t)) - \beta_1 \omega^2(t) - \beta_3 Br(t) - \beta_4 \epsilon(t) - \beta_5 cos(\alpha(t)))^2 = 0$$

(3.14)

Using a numerical minimization method, corresponding  $\beta_i$  that fits the system with smallest deviation, is obtained. Fitted model is presented in the end of this thesis.

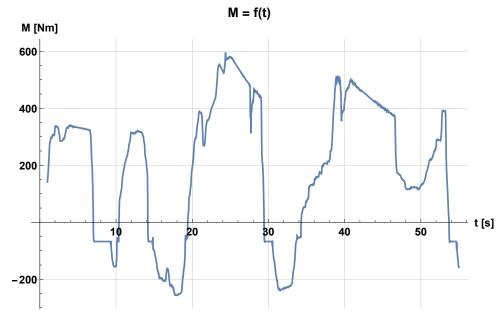

Figure 3.7: Measured brake pedal on race track.

Figure 3.8:  $M_{PMSM}$  measured on the race track.

## 3.2.3 Battery model

### Information in following section are taken from [12].

Nowadays, battery system is the most common storage of energy for automotive industry. Majority of electric cars is using battery system to provide electric power for motors. New types of batteries with bigger capacity and energy density are developed. Price of the battery system is continuously decreasing, but the battery is still one of the most expensive parts of an electric car.

There are several mathematical models of batteries with different complexity and accuracy. Electrochemical models can be used to optimize physical aspects of the batteries. However, the system complexity is unnecessarily complicated. [27]

Proposed battery model for PWR-Hil is based on electrical model combining current source and resistor. This battery system was mainly developed to observe the energy flow between the battery and the PMSMs. Another point was to test the power inverter behaviour in connection with battery and not to simulate the battery pack with its full complexity.

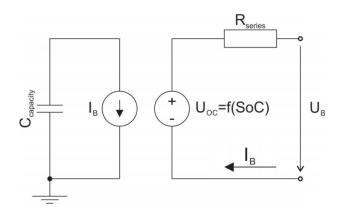

Consequently, battery model with equivalent circuit on figure 3.9 was chosen and following assumptions were made.

• Temperature of the battery cell does not change during the simulation. As a result temperature dependent values are considered to be constant.

Figure 3.9: Battery cell equivalent circuit.

| Property          | Value | $\mathbf{Units}$ |

|-------------------|-------|------------------|

| Nominal Voltage   | 3.7   | V/cell           |

| Charge up voltage | 4.2   | V/cell           |

| Cut off voltage   | 2.8   | V/cell           |

| Serial Resistance | 0.51  | $m\Omega$        |

Table 3.1: Specific values of battery cell

- Transient response of battery cell is not taken in account.

- Self discharging and ageing is not implemented.

- Serial battery resistance is SOC non-dependant.

Terminal voltage of one battery cell is calculated with equation 3.15

$$u_B = u_0 - R_{Series} \cdot i_B \tag{3.15}$$

Specific values of battery cell used in simulation are shown in table 3.1

#### Battery pack

In order to get the correct voltage on electrical machine, battery cells must be organized into a battery pack. Cells are connected in series and final voltage is described by equation 3.16.

$$u_{BP} = u_{Cell} \cdot n_S \tag{3.16}$$

where  $u_{BP}$  is terminal voltage of battery pack,  $u_{Cell}$  is voltage of one li-ion cell and  $n_S$  is number of cells connected in series. To increase the capacity

3. HiL development

of the battery pack, cells must be organized in parallel. Due to the same resistance, current splits equally between all of them.

$$i_{Cell} = \frac{i_{BP}}{n_P} \tag{3.17}$$

Where  $i_{BP}$  is terminal current of battery pack,  $n_P$  is number of packs connected in parallel.

In a real battery system, cells are not stressed equally, because the parameters are not the same. To avoid unnecessary ageing, battery is normally equipped with battery management system. [28]

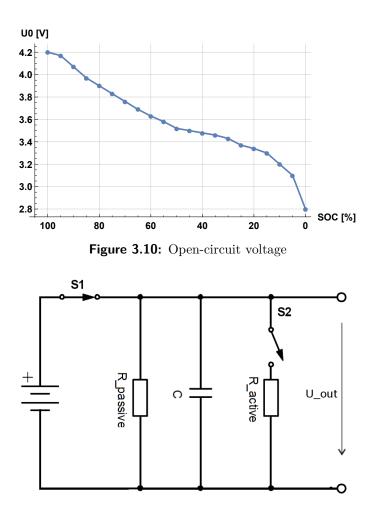

#### Open-circuit voltage

Open-circuit voltage changes with the state-of-charge (SOC) of the battery cell and there is a non-linear relation. As a result, open-circuit voltage is implemented as function of SOC. Battery model all together with car dynamic was programmed in Simulink and therefore this battery property was implemented as a look-up table. [28]

Function  $U_0(SOC)$  is shown on figure 3.10. When the battery is fully charged, SOC is equal to 1. When the battery is discharged SOC is equal to 0. Data for this model were internally provided and measured in Porsche Engineering Group.

SOC is function of battery current and can be described by equation 3.18,

$$SOC = \frac{1}{Q_C} \int i_B dt \tag{3.18}$$

where  $Q_C$  is battery capacity and  $i_B$  is a battery current. [28]

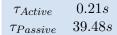

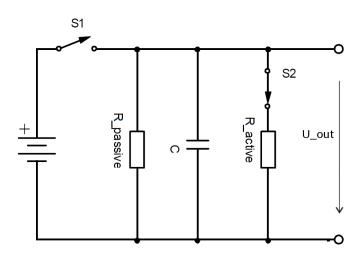

#### Intermediate circuit

Intermediate circuit, which is used in the real power inverter and in the simulation, can be described as intermediate circuit of voltage type. Large capacitor is connected to the battery on one side and to IGBT stage on other side. This capacitor is installed to stabilize voltage and as a source of peak energy. [29]

Nowadays, most of the power inverters are developed as voltage types in automotive industry.

Intermediate circuit is schematically shown on figure 3.11. The  $u_{out}$  can be calculated as

Figure 3.11: Intermediate circuit - active state.

$$0 = u_b(t) - \frac{1}{C} \int i_C dt \tag{3.19}$$

$$\frac{1}{C}\int i_C dt = u_{out} \tag{3.20}$$

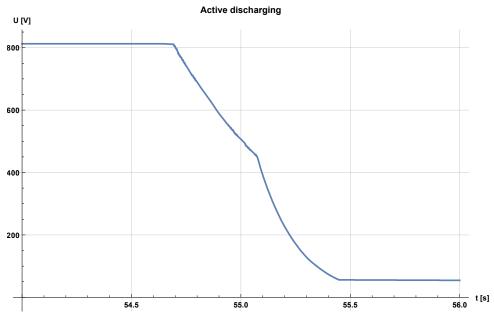

#### Active Discharging

Various conditions must be fulfilled to start active discharging of the intermediate circuit. These conditions are controlled by the power inverter ECU and the external safety computer. Active discharging must be activated in case of a crash or in case of a hardware emergency turn off.

Before the active discharging request is sent, battery contacts must be opened and battery must not be connected to the charger. Additional resistor

Table 3.2: Time constants of intermediate circuit.

Figure 3.12: Intermediate circuit - active discharging.

for discharging is then connected to the main capacitor and IGBT transistors are closed. According to internal requirements, intermediate circuit must be discharged under 60V in 5 seconds under any circumstances.

When the hardware is turned off, discharging of the main capacitor is done only by  $R_{passive}$  resistor. Time constants of active and passive discharging are shown in table 3.2

Active discharging is schematically shown on figure 3.12 and can be described with equation,

$$C \cdot \frac{\mathrm{d}u_{out}(t)}{\mathrm{d}t} = -\frac{u_{out}(t)}{R} \tag{3.21}$$

where R is in case of active discharging calculated as parallel combination of  $R_{Active}$  and  $R_{Passive}$ . In case of passive discharging, the resistor value equals to  $R_{Passive}$ .  $u_{out}(0)$  is voltage on capacitor in the moment of disconnection.

When the active discharging is activated by the ECU, big discharging currents are flowing through the resistor. In order not to burn down the discharging resistor, PWM switching is used.

## 3.2.4 Restbus model

Restbus simulation model provides interface between models and buses. This model collects all signals from various models, manipulate them and afterwards

• 3.2. Mathematical models - SCALEXIO

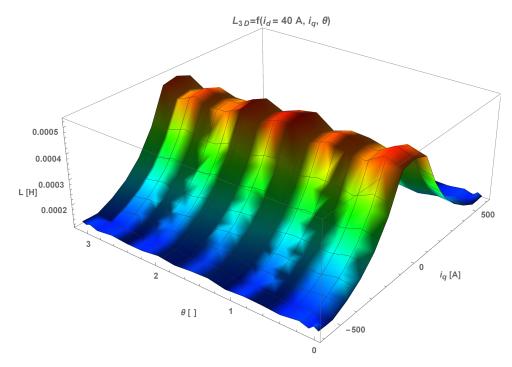

Figure 3.13:  $L_d$  map

send the signals to corresponding bus system.

As an example, brake pedal signal can be presented. This signal comes from GUI, afterwards is sent to PMSM model and also to connected ECU.

This model is taken from Porsche Engineering libraries.

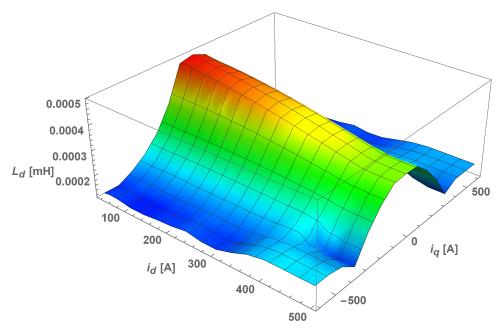

## **3.2.5** Ld/Lq model and sensor simulation

There are various non-linearities in real PMSM machine. Those linearities are neglected during the derivation of the mathematical model in order to get reasonable and solvable set of equation. Derivation of the PMSM model is described in details in section 4.1.2.

One of the neglected features is the magnetic hysteresis and saturation. To improve the overall simulation quality,  $L_d$  and  $L_q$  are implemented as a look-up table with following formula 3.22 and are presented on figure 3.13

$$L = f(i_d, i_q) \tag{3.22}$$

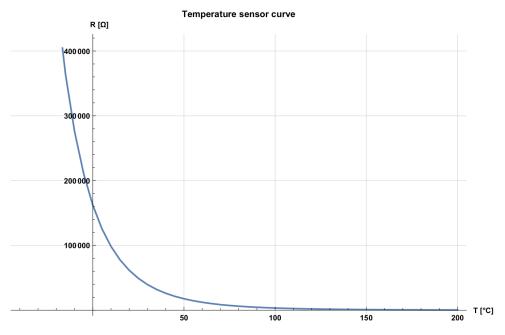

Additional non-linearities in the model are related to the sensor behaviour and their non-linear curves. Those relations are implemented as a table with saturation to over or under-values.

Figure 3.14: Example of temperature sensor curve.

## Chapter 4

## **FPGA** model analysis and improvements

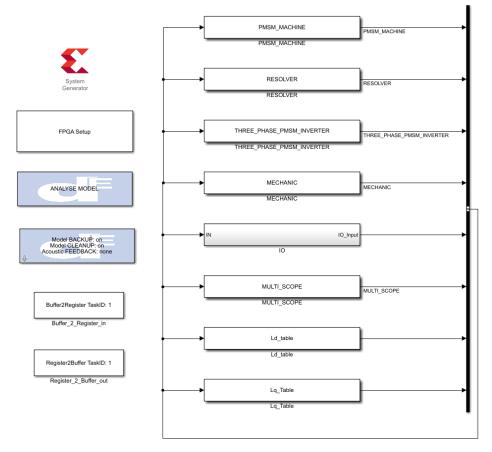

This section provides overview of PMSM machine features. Afterwards, mathematical model of synchronous machine is presented in corresponding form for PMSM machine. Model structure on FPGA card is presented altogether with other FPGA needed models for successful HiL simulation. In the end of the chapter, possible model improvements are shown.

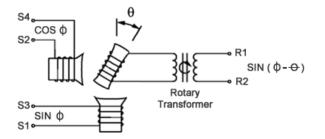

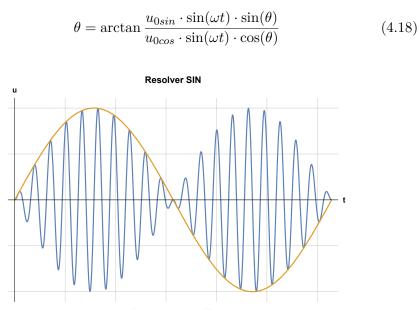

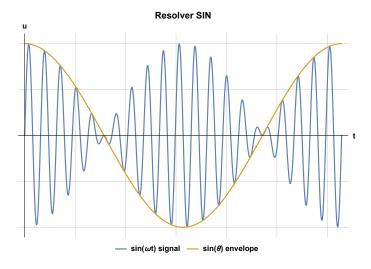

## 4.1 Mathematical models - FPGA