Czech Technical University in Prague Faculty of Electrical Engineering Department of Microelectronics

Diploma Thesis

### Design of the HW accelerator of the KECCAK hash function

Nikita Litvishko

Supervisor: Prof. Ing. Pavel Hazdra, CSc. Second Supervisor: Ing. Leoš Kafka, Ph.D.

Study Program: Electronics and Communication, Master Field of Study: Electronics

# ZADÁNÍ DIPLOMOVÉ PRÁCE

### I. OSOBNÍ A STUDIJNÍ ÚDAJE

| Příjmení:         | Litvishko                    | Jméno: Nikita | Osobní číslo: 456867 |

|-------------------|------------------------------|---------------|----------------------|

| Fakulta/ústav:    | Fakulta elektrotechnická     |               |                      |

| Zadávající kated  | ra/ústav: Katedra mikroelekt | troniky       |                      |

| Studijní program: | Elektronika a komunikace     |               |                      |

| Specializace:     | Elektronika                  |               |                      |

|                   |                              |               |                      |

### II. ÚDAJE K DIPLOMOVÉ PRÁCI

Název diplomové práce:

### Návrh HW akcelerátoru Keccak hashovacího algoritmu pro SoC platformu

Název diplomové práce anglicky:

Design of the HW accelerator of the Keccak hash function.

Pokyny pro vypracování:

1. Navrhněte akcelerátor pro Keccak hashovací algoritmus. Vyberte optimální interface pro integraci akcelerátoru v digitálním SoC (System-on-Chip).

2. Implementujte akcelerátor na úrovni RTL v jazyce Verilog2001. Ověřte funkci akcelerátoru simulací na RTL úrovni a validací na FPGA desce.

Porovnejte výkon akcelerátoru se softwarovou implementací tohoto hashovacího algoritmu ve vestavěném procesoru v FPGA. K softwarové implementaci použijte jádro Xilinx MicroBlaze.

Seznam doporučené literatury:

[1] The KECCAK reference, https://keccak.team/files/Keccak-reference-3.0.pdf

[2] KECCAK implementation overview, https://keccak.team/files/Keccak-implementation-3.2.pdf

[3] KECCAK in C, https://keccak.team/software.html https://keccak.team/obsolete/KeccakReferenceAndOptimized-3.2.zip

Jméno a pracoviště vedoucí(ho) diplomové práce:

### prof. Ing. Pavel Hazdra, CSc., katedra mikroelektroniky FEL

Jméno a pracoviště druhé(ho) vedoucí(ho) nebo konzultanta(ky) diplomové práce:

### Ing. Leoš Kafka, Ph.D., Adesto Technologies

Datum zadání diplomové práce: 28.01.2020

Termín odevzdání diplomové práce:

Platnost zadání diplomové práce: 30.09.2021

| prof. Ing. Pavel Hazdra, CSc. | prof. Ing. Pavel Hazdra, CSc.     | prof. Mgr. Petr Páta, Ph.D. |

|-------------------------------|-----------------------------------|-----------------------------|

| podpis vedouci(ho) práce      | podpis vedoucí(ho) ústavu/katedry | podpis děkana(ky)           |

### III. PŘEVZETÍ ZADÁNÍ

Diplomant bere na vědomí, že je povinen vypracovat diplomovou práci samostatně, bez cizí pomoci, s výjimkou poskytnutých konzultací. Seznam použité literatury, jiných pramenů a jmen konzultantů je třeba uvést v diplomové práci.

Datum převzetí zadání

Podpis studenta

## Aknowledgements

I would like to thank my school supervisor Pavel Hazdra for valuable comments on the thesis. Also I would like to express my gratitude to the second supervisor, Leoš Kafka, for his excellent management of the thesis, weekly consultations, professional advices both in the field of digital design and in organizing time and work, as well as for help in difficult places.

I also wish to acknowledge the whole Adesto Technologies collective for a friendly atmosphere and nice working place.

I would also like to thank my parents and relatives for the opportunity to study abroad, for the endless support both during my studies at the university and throughout my life. I am also grateful to my friends for their moral support.

Last but not least, I would like to thank my girlfriend Daria Uslontceva for moral support in difficult times, for walking this path with me from beginning to end and for believing that I will succeed.

# Declaration

I declare that the presented work was developed independently and that I have listed all sources of information used within it in accordance with the methodical instructions for observing the ethical principles in the preparation of university theses.

Prague, date .....

signature

# Abstract

The goal of this work is to propose an implementation of the KECCAK algorithm in FPGA and evaluate its effectiveness on the SoC platform. For this purpose we studied the theory behind SHA-3 hash function and KECCAK algorithm. We also chose the suitable interface to connect the implemented unit (accelerator) to the processor and wrote the firmware to access the accelerator from the processor. We evaluated the effectiveness of the implementation by comparing it with existing software implementation of SHA-3 hash function.

**Keywords:** hash function, hardware acceleration, digital design, FPGA, processor, communication interface, SoC

# Abstrakt

Cílem této práce je návrh implementace KECCAK algoritmu v FPGA a ověření jeho efektivity na SoC platformě. Pro tento účel jsme nastudovali teorii, která se týká SHA-3 hashovací funkce a KECCAK algoritmu. Také jsme vybrali vhodný interface pro připojení implementované jednotky (akcelerátoru) k procesoru a napsali firmware pro přístup k akcelerátoru z procesoru. Efektivitu implementace jsme ověřili pomocí porovnání této implementace s existující softwarovou implementací SHA-3 hashovací funkce.

${\bf K}{\bf l}$ íčová slova: hash funkce, hardwarová akcelerace, digitální návrh, FPGA, procesor, komunikační interface, SoC

# Contents

| 1        | Intr | oducti         | on                                                                                                                     |   |       |   |       |   | 1          |

|----------|------|----------------|------------------------------------------------------------------------------------------------------------------------|---|-------|---|-------|---|------------|

|          | 1.1  | Thesis         | Structure                                                                                                              |   |       |   | <br>• |   | 2          |

|          | 1.2  | Hash F         | Function                                                                                                               |   |       |   | <br>• |   | 3          |

|          | 1.3  | Comm           | on Hash Algorithms                                                                                                     |   |       |   |       |   | 4          |

|          |      | 1.3.1          | MD5 Message-digest Algorithm                                                                                           |   |       |   |       |   | 4          |

|          |      | 1.3.2          | SHA-1 and SHA-2 Secure Hash Algorithms                                                                                 |   |       |   |       |   | 4          |

|          |      | 1.3.3          | SHA-3 Secure Hash Algorithm                                                                                            |   |       |   |       |   | 5          |

| <b>2</b> | SH   | 4-3/KF         | ECCAK Algorithm Description                                                                                            |   |       |   |       |   | 6          |

| -        | 2.1  | ,              | e Construction and State Variables                                                                                     |   |       |   |       |   | 6          |

|          |      | 2.1.1          | Absorbing Phase                                                                                                        |   |       |   |       |   | 7          |

|          |      | 2.1.1<br>2.1.2 | Squeezing Phase                                                                                                        |   |       |   |       |   | 8          |

|          |      | 2.1.2<br>2.1.3 | Long Messages Processing                                                                                               |   |       |   |       |   | 8          |

|          |      | 2.1.0<br>2.1.4 | State Variables                                                                                                        |   |       |   |       |   | 8          |

|          | 2.2  |                | thm Steps                                                                                                              |   |       |   |       |   | 10         |

|          | 2.2  | 2.2.1          | Specification of $\theta$                                                                                              |   |       |   |       |   | 11         |

|          |      | 2.2.1<br>2.2.2 | Specification of $\rho$                                                                                                |   |       |   |       |   | 11         |

|          |      | 2.2.2<br>2.2.3 | Specification of $\pi$                                                                                                 |   |       |   |       |   | $12 \\ 13$ |

|          |      | 2.2.3<br>2.2.4 | Specification of $\chi$                                                                                                |   |       |   |       |   | 14         |

|          |      | 2.2.4<br>2.2.5 | Specification of $\iota$                                                                                               |   |       |   |       |   | 15         |

|          |      |                | •                                                                                                                      |   |       |   |       |   |            |

| 3        | -    |                | Analysis                                                                                                               |   |       |   |       |   | 16         |

|          | 3.1  | U              | arameters of the KECCAK for Hardware Implementation                                                                    |   |       |   |       |   | 17         |

|          | 3.2  |                | tion of Resources                                                                                                      |   |       |   |       |   | 18         |

|          | 3.3  | Conclu         | $sion \ldots \ldots$ | • | <br>· | • | <br>• | • | 20         |

| <b>4</b> | нм   | Accel          | erator Description                                                                                                     |   |       |   |       |   | <b>21</b>  |

|          | 4.1  |                | -<br>Diagram                                                                                                           |   |       |   |       |   | 21         |

|          | 4.2  | List of        | Ports                                                                                                                  |   |       |   |       |   | 22         |

|          | 4.3  | HW A           | ccelerator Hierarchy                                                                                                   |   |       |   |       |   | 24         |

|          |      | 4.3.1          | Main Control Unit                                                                                                      |   |       |   |       |   | 25         |

|          |      | 4.3.2          | Computational Core                                                                                                     |   |       |   |       |   | 27         |

|          |      | 4.3.3          | Internal Input and Output Memories                                                                                     |   |       |   |       |   | 28         |

|          |      | 4.3.4          | KECCAK Cell Unit                                                                                                       |   |       |   |       |   | 29         |

|          |      | 4.3.5          | XOR5 Auxiliary Block                                                                                                   |   |       |   |       |   | 31         |

|   | 4.4                                           | 4.3.6 Output Multiplexer                                                                                                                                                                                                                                                                                                                                    | $\frac{32}{32}$                                                                                                       |

|---|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 5 | <b>Des</b><br>5.1<br>5.2                      | ign FlowTools Used for DevelopmentVerification Environment                                                                                                                                                                                                                                                                                                  | <b>33</b><br>35<br>36                                                                                                 |

| 6 | Imp                                           | blementation Results                                                                                                                                                                                                                                                                                                                                        | 38                                                                                                                    |

| 7 | <b>SoC</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5 | <b>Block Design for Interface Selection</b> 7.1.1 Clock and Reset Generation7.1.2 MicroBlaze Processor7.1.3 AXI Interconnect7.1.4 AXI Central Direct Memory Access7.1.5 Local Memory Bus and AXI BRAM Controllers7.1.6 AXI4-Stream Data FIFOAddress SpaceInterface SelectionInterface Selection7.5.1 SHA-3 Accelerator7.5.2 AXI to APB Bridge7.5.4 AXI UART | $\begin{array}{c} 40 \\ 40 \\ 41 \\ 42 \\ 43 \\ 43 \\ 44 \\ 45 \\ 46 \\ 47 \\ 48 \\ 49 \\ 53 \\ 53 \\ 54 \end{array}$ |

| 8 | <b>Ana</b><br>8.1<br>8.2<br>8.3<br>8.4        | Alysis of Firmware Function         Data Transferring                                                                                                                                                                                                                                                                                                       | <b>55</b><br>58<br>60<br>61<br>62                                                                                     |

| 9 | 9.1<br>9.2<br>9.3<br>9.4                      | mparison of the SW and HW Approaches         FPGA Development Board                                                                                                                                                                                                                                                                                         | <ul> <li>65</li> <li>66</li> <li>67</li> <li>68</li> <li>73</li> <li>76</li> </ul>                                    |

# List of Figures

| 2.1 | The sponge construction $[5]$                                              | 7  |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Parts of the KECCAK- $f$ state [6]                                         | 9  |

| 2.3 | $\boldsymbol{\theta}$ applied to a single bit [6]                          | 12 |

| 2.4 |                                                                            | 13 |

| 2.5 |                                                                            | 14 |

| 2.6 |                                                                            | 15 |

| 4.1 | 0                                                                          | 22 |

| 4.2 |                                                                            | 26 |

| 4.3 |                                                                            | 26 |

| 4.4 | 1 0 0 1                                                                    | 27 |

| 4.5 | 1 1                                                                        | 27 |

| 4.6 | Block diagram of keccak-cell unit                                          | 30 |

| 5.1 | Development steps                                                          | 34 |

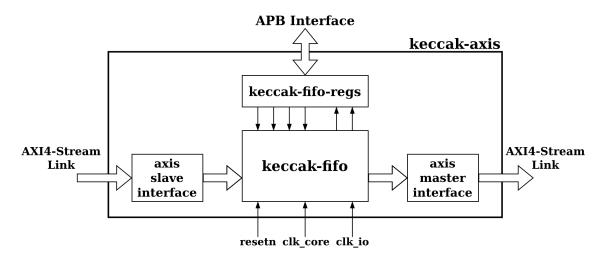

| 7.1 | Block design for verification and measurements of the suitable interface 4 | 41 |

| 7.2 |                                                                            | 49 |

| 7.3 |                                                                            | 50 |

| 7.4 | 0                                                                          | 51 |

| 7.5 | 0 0                                                                        | 51 |

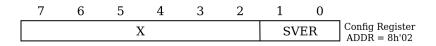

| 7.6 | keccak-axis block diagram                                                  | 53 |

| 8.1 | 8                                                                          | 55 |

| 8.2 | 1 5                                                                        | 59 |

| 8.3 | 1 1 5                                                                      | 59 |

| 8.4 | Ideal case of digest computation                                           | 62 |

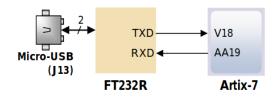

| 9.1 | USB/UART bridge [18]                                                       | 67 |

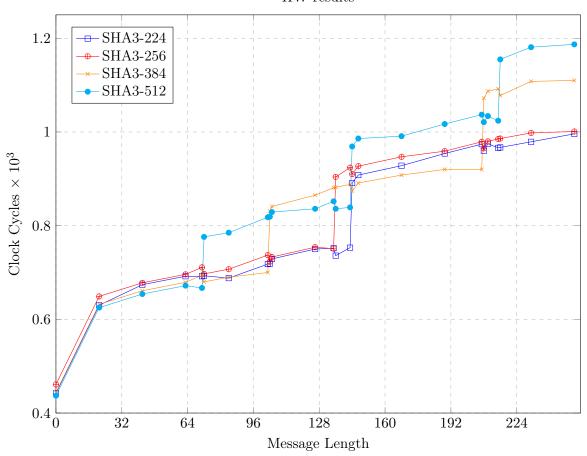

| 9.2 | Graph illustrating SHA-3 computation with accelerator                      | 72 |

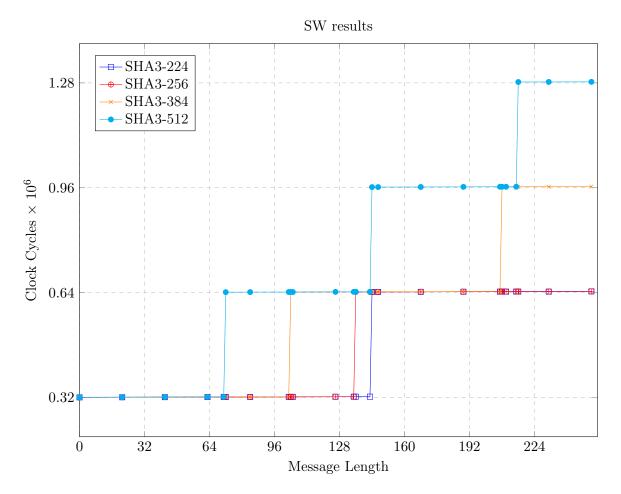

| 9.3 | 1 0 1                                                                      | 73 |

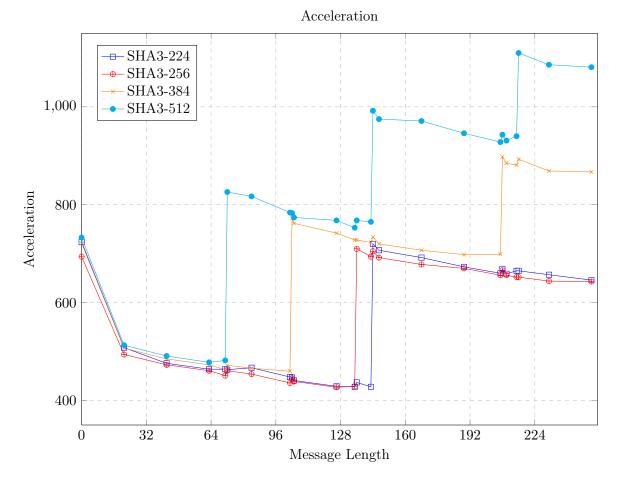

| 9.4 | The acceleration dependence on the message length and SHA-3 version $7$    | 74 |

# List of Tables

| $2.1 \\ 2.2$                                                                        | Round constants for the lane size 64 [9] $\dots \dots \dots$ | $\begin{array}{c} 11 \\ 13 \end{array}$      |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3.1                                                                                 | Estimation of resources                                                                                                                                      | 19                                           |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \end{array}$ | keccak-fifo signals description                                                                                                                              | 23<br>25<br>28<br>29<br>30<br>31<br>31<br>32 |

| $6.1 \\ 6.2$                                                                        | Number of blocks used in implementation                                                                                                                      | $\frac{38}{39}$                              |

| $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7$                                     | MicroBlaze address space                                                                                                                                     | $45 \\ 46 \\ 48 \\ 48 \\ 50 \\ 51 \\ 51$     |

| 8.1<br>8.2<br>8.3<br>8.4                                                            | Data processing                                                                                                                                              | 60<br>62<br>63<br>64                         |

| 9.1<br>9.2<br>9.3<br>9.4                                                            | SHA3-224 results                                                                                                                                             | 68<br>69<br>70<br>71                         |

# Acronyms

| Advanced Microcontroller Bus Architecture |

|-------------------------------------------|

| Advanced Peripheral Bus                   |

| Advanced eXtensible Interface             |

| Block Random Access Memory                |

| Clock Cycles                              |

| Central Direct Memory Access              |

| Clock and Reset Generation                |

| D Flip-Flop                               |

| Data Local Memory Bus                     |

| Direct Memory Access                      |

| Device Under Test                         |

| First In First Out Memory                 |

| Federal Information Processing Standards  |

| Field-programmable Gate Array             |

| Galois Field                              |

| Hardware Description Language             |

| Hardware                                  |

| Input/Output                              |

| Integrated Development Environment        |

| Instruction Local Memory Bus              |

| Intellectual Property                     |

| Linear-feedback Shift Register            |

|                                           |

### ACRONYMS

| LMB  | Local Memory Bus                               |

|------|------------------------------------------------|

| LUT  | Lookup Table                                   |

| MD   | Message-Digest Algorithm                       |

| MUX  | Multiplexer                                    |

| NIST | National Institute of Standards and Technology |

| PC   | Personal Computer                              |

| RC   | Round Constant                                 |

| RDEN | Read Enable                                    |

| RTL  | Register-transfer Level                        |

| SDK  | Software Development Kit                       |

| SHA  | Secure Hash Algorithm                          |

| SoC  | System on a Chip                               |

| SW   | Software                                       |

| UART | Universal Asynchronous Receiver-transmitter    |

| USB  | Universal Serial Bus                           |

| WREN | Write Enable                                   |

# Chapter 1

# Introduction

The main purpose of general-purpose processors is to execute any given task. Due to the fact that these processors are universal, their architecture is also universal and is not oriented on the execution of specific tasks. If there is a need to execute the specific task more effectively, then we can use the processor with different architecture or we can use a hardware acceleration. The hardware acceleration is the execution of a certain task on the hardware that is specifically designed to execute this task effectively. One example of the hardware accelleration that closely relates to this work is cryptographic accelerator, which is the unit that can execute all cryptographic operations more efficiently than the general-purpose processor.

The hardware acceleration takes place when the task requires the processing of large amount of data and complex mathematical operations. The excellent candidates for the hardware acceleration are the hash functions that are described in Section 1.2 in detail. Briefly, hash function takes an input message of an arbitrary length, applies complex mathematical algorithm and provides the output with fixed length. The most demanding part of every hash function is the data processing part that is realized with some complex algorithm. In this work we will concentrate ourselves on the SHA-3 hash function and the KECCAK algorithm that it uses [12], [6]. As we will see, the KECCAK algorithm is very time-consuming, because it requires the processing of large amount of data.

The KECCAK algorithm has a lot of software implementations in many different programming languages that can be found at [32]. One of the software implementations in C language will be chosen in this work for comparison with our hardware implementation. Beside the software implementations, there is one hardware implementation of the KECCAK algorithm in VHDL language [29]. In this work we concentrate ourselves on the KECCAK algorithm implementation in Verilog-2001 hardware description language.

Beside the effectively implemented data processing part of the accelerator, it is very important to optimally integrate the accelerator in the system, otherwise the acceleration will not make any sense. Our main goal is to create an effective and fast hardware implementation of the algorithm that can later be used to accelerate the processor's execution of the SHA-3 hash function, which uses the KECCAK algorithm. As a result of this work we want to have an IP core that can be used in any FPGA design with the processor.

### 1.1 Thesis Structure

In this work we first provide a brief introduction to the world of hash functions in Chapter 1, their purpose and different types of hash functions. The universal knowledge about hash functions help us to better understand the theory behind the SHA-3 function. In Chapter 2 we concentrate on the description of the SHA-3 hash function and the KECCAK algorithm that it uses. The theory described in that chapter helps us to understand how the KECCAK algorithm works and can be implemented effectively.

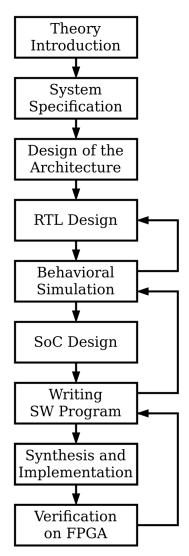

Chapter 3 contains an analysis of the KECCAK algorithm from the point of view of its implementation in FPGA. The analysis provided in this chapter is crucial to finding the optimal way to design the accelerator. The analysis of the algorithm is closely connected to the theory knowledge obtained in Chapter 2. It helps us to propose the parallel implementation of the algorithm where all bits of the internal state of KECCAK algorithm are processed in parallel. Chapter 3 focuses more on ideas about how the accelerator should be implemented and in Chapter 4 we realize these ideas and show the RTL design of the accelerator. We describe the hierarchy of the designed accelerator and the structure of the distinct modules. Also we show how the parallel approach has been implemented and how the accelerator operates. As a result of this chapter we have the computational core of the KECCAK algorithm, which yet does not contain any interface to communicate with the processor.

In Chapter 5 we talk about different development tools that we used throughout this work and what steps we followed during implementation. We also provide a detailed description about how the designed accelerator was verified during all development steps. Chapter 6 provides the results of logic implementation of the designed accelerator for a specific FPGA, where we analyze the utilization of the chip resources. We also describe the frequency at which it can operate and how the assumption about the number of logic cells from Table 3.1 differs from the implementation results.

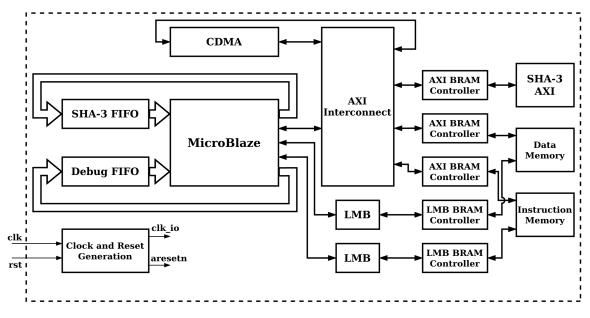

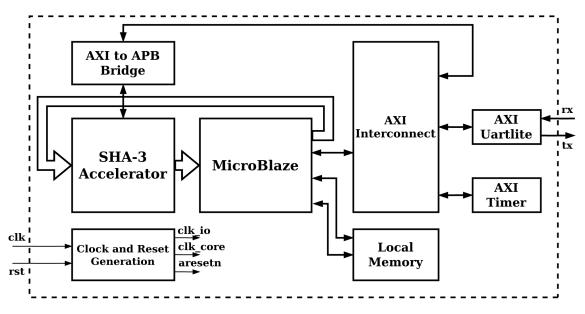

In Chapter 7 we describe two SoC designs. The main task of the first SoC design was to help us to indicate which communication interface better fits our application. We describe different types of interfaces, their advantages and disadvantages, and the simulation results. After the suitable interface has been chosen, we move to the second SoC design that helps us to evaluate the effectiveness of the designed accelerator in FPGA. In Chapter 8 we provide a firmware function that allows the processor to use the accelerator. We also analyze implemented function and describe its weak and strong sides. We divide the operation of the function into several categories and talk about each category in detail along with suggestions about how these categories can be improved and optimized. Firmware function from Chapter 8 also helps us to compare the time needed to execute the SHA-3 function with and without the accelerator. Chapter 9 contains the result of this comparison and provides the data that evaluate the effectiveness of the accelerator. The chapter contains the tables with measurements results and according graphs that visualize the comparison.

In Chapter 10 we summarize the results of this work and describe several difficulties that we faced throughout this work. We also provide a suggestion on how this work can be improved in future.

### 1.2 Hash Function

A hash function, or a hash algorithm, takes an input message of arbitrary length, mixes it in a certain way and gives a digest of the required length to the output. The input of the hash algorithm is called a "message", and the output is called a "digest" or simply a "hash value". Hash functions are ubiquitous, starting with generating pseudo-random sequences, encrypting passwords, and ending with digitally signed documents. All this poses a serious challenge for developers and scientists when creating hash algorithms, since the algorithms must exhibit a high level of reliability, good computing speed, flexibility in setting parameters, and relative simplicity in implementation.

In this work we concentrate ourselves on the hardware implementation of the SHA-3 family hash functions. Each of the SHA-3 functions is based on an instance of the KECCAK algorithm that National Institute of Standards and Technology (NIST) selected as the winner of the SHA-3 Cryptographic Hash Algorithm Competition [12]. We chose this hash function because it is well documented, has a lot of applications and can be effectively implemented in hardware. Software implementations of the KECCAK algorithm in different programming languages can be found in [32].

One of the main parameters of a hash function is its security. NIST defines three main criteria by which it is possible to judge the strength of hash algorithm [8]:

- 1. Collision resistance: how computationally difficult it is to find two input values at the input of a hash function, for which the same output result will be produced. It is measured in the amount of work needed to find such a collision. If the function had poor collision resistance, then the algorithm would be vulnerable to collision attacks, the essence of which is that an attacker can replace the original document with a fake one, but which has the same hash value as the original. The recipient of the signed message is then not able to distinguish the original from the fake, until he opens a document. Thus, a malicious program can be passed off as something else [28].

- 2. Preimage resistance: how computationally difficult it is to find the input value of the hash function for a given value at the output. It is measured in the amount of work required to search for an input message. Suppose that an attacker has obtained a table that stores users' password hashes. If a hash function with a small preimage resistance has been used, then it will not be difficult for an attacker to find the inverse images of the hash values and thus obtain users' passwords. Often attackers use prepared tables with hashes of simple and frequently used types of passwords [27].

- 3. Second preimage resistance: for a given input value  $x_1$ , how computationally difficult it is to find the value  $x_2$ , the hash of which will coincide with the hash of  $x_1$ . This is similar to collision resistance, but differs in that we know the value of  $x_1$  in advance. This allows the attacker to create fraudulent certificates at any time, not just at the time of certificate issuance [11].

There are a huge number of different hash functions and each function does not have to have each of the parameters listed above on the high. If the function does not show excellent

results in one of the parameters, this does not mean that it is unsuitable. Its certain qualities are important in certain tasks and the hash function can simply be used for another purpose. Since hash functions are used very often and are widely used, attacks against functions are also developing. Therefore, hashing algorithms are constantly being improved and existing ones are being replaced by new versions or are no longer used in some applications, if making a successful attack becomes an easy task.

### 1.3 Common Hash Algorithms

Now we will briefly look at several algorithms that were used in the past or are being used now. Each of these algorithms has a different internal structure, which is based on certain mathematical operations. Basically, these mathematical operations are cyclically repeated. Some of them, for example, determine the parity of a group of several bits, others differently shift (rotate) a section of a message, and so on. As we will see in Chapter 2, in the case of SHA-3 and, in particular, the used KECCAK algorithm, some operations remove the symmetry of individual iterations, while others are oriented on building a strong dependence of one bit on many other bits.

### 1.3.1 MD5 Message-digest Algorithm

MD5 [1] is a message-digest algorithm. The algorithm takes as input a message of arbitrary length and produces as output a 128-bit "fingerprint" or "message digest" of the input. It was created in 1991 by Ronald Rivest and was documented in April 1992. Algorithm was primarily designed as an extension of the MD4 message-digest algorithm. Nowadays MD5 is considered to be weak against attacks, such as collision attacks.

### 1.3.2 SHA-1 and SHA-2 Secure Hash Algorithms

SHA-1 and SHA-2 are two hash algorithms published by NIST. They are specified in the FIPS 180-4 standard [10] and were first released in the 1993 and 2001 respectively. The difference between them is in the internal structure and the length of the digest they generate. Both algorithms use padding of the input message, so that it can be divided into blocks with constant length, which are then processed sequentially.

**SHA-1** may be used to hash a message, M, having a length of l bits, where  $0 \le l < 2^{64}$ . The algorithm uses:

- Four different functions that are applied to the internal state of the algorithm

- Four internal constants that are XORed with the internal state every round

- Five internal variables used to store the intermediate results

- Five 32-bit hash values used at the output and updated every processed 512-bit block

The operation of the algorithm is divided into 4 steps with 20 iterations. The four functions and constants correspond to these steps and their purpose is to differently mix the bits of the message. Result after applying the function is stored into 5 internal variables, and iteration repeats. SHA-1 is able to produce only a 160-bit digest.

SHA-2 has a similar to SHA-1 structure. It is able to process a message having a length of l bits, where l is  $0 \leq l < 2^{128}$ . It also pads the message and divides it into the blocks of the length 512 bit. However, it is able to produce different output lengths, such as 224, 256, 384 and 512 bits. This is achieved by having different size hash values that store the output of the algorithm. For example, SHA-224 uses seven 32-bit values, so that in sum it gives exactly 224. SHA-512 uses eight 64-bit values. Similar to SHA-1, SHA-2 uses:

- Six different functions that are applied to the internal state of the algorithm

- Eight 32-bit internal variables used to store intermediate result

- The total of 64(80) internal constants each used in one function every round

The processing of one 512-bit block is divided into 64 or 80 rounds. SHA-224 and SHA-256 use 64 rounds; SHA-384 and SHA-512 both use 80 rounds. These rounds are not identical, since the different constant is used every time.

### 1.3.3 SHA-3 Secure Hash Algorithm

SHA-3 hash family functions were first published by NIST in 2015. They are specified in FIPS 202 standard [12] and use the KECCAK algorithm specified in [6]. SHA-3 is very different in structure from previous standards and has  $n_r$  rounds. The number  $n_r$  depends on the size **b** of the internal state of algorithm. SHA-3 lets us to choose such that  $\mathbf{b} = 25 \times 2^l$ , where l ranges from 0 to 6. Each round, further, consists of five steps that are being executed sequentially. Rounds are not identical due to the presence of the constants that differ for every round and are XORed with the part of the internal state. Internal state **s** that is **b** bits long is the only internal variable used to store the intermediate results of the algorithm. We provide the detailed description of the algorithm in Chapter 2.

## Chapter 2

# SHA-3/KECCAK Algorithm Description

SHA-3 hash function uses the KECCAK algorithm [6], developed by Guido Bertoni, Joan Daemen, Michäel Peeters and Gilles Van Assche. The basis of this algorithm is the sponge construction, which we will analyze in detail in Section 2.1. This construction allows to process input data of any length and create the digest of the required length. On one side, the function receives an input message, which is the only input to the hash function. Everything that happens with the message and the way it is processed is determined by the definition of a specific function. Inside the sponge, the input data are divided into blocks of the same length and the so-called permutation function is applied on them.

The permutation function, in the case of SHA-3, is specified by the KECCAK algorithm and called KECCAK-f permutation. Inside this function, the data are repeatedly mixed. We will analyze in detail each operation of the KECCAK algorithm in Section 2.2. When all input data has been processed, the required number of processed data bits is taken, and provided as an output of the hash function.

### 2.1 Sponge Construction and State Variables

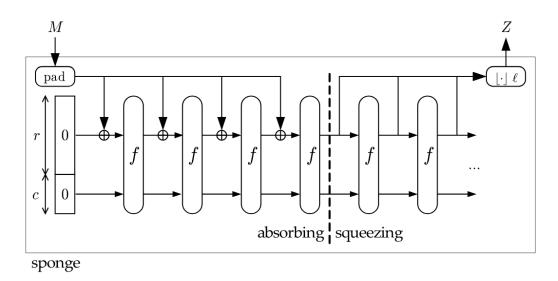

SHA-3 family hash functions are based on the sponge construction that is described in this section. We will refer to [12] and [5]. The sponge construction has the structure illustrated in Figure 2.1.

Figure 2.1: The sponge construction [5]

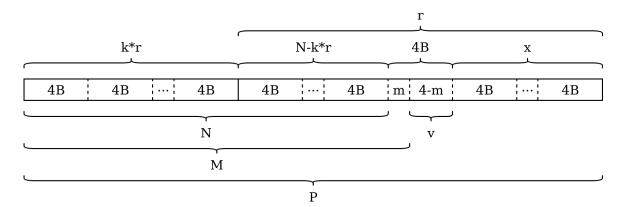

It has one input, which is the input message M and one output that is the output message Z. The input sequence of bits can have an arbitrary length, but it has to be padded to the message P which length is divisible by bit rate r. Before padding the two-bit suffix is appended to the message M to produce the input N to the pad function. In the case of SHA-3 hash functions the suffix is **01**.

Next, the multi-rate padding rule is applied to the new message N. By [5] the multi-rate padding is defined according to Definition 2.1.1.

**Definition 2.1.1.** Multi-rate padding, denoted by pad10\*1, appends a single bit 1 followed by the minimum number of bits 0 followed by a single bit 1 such that the length of the result is a multiple of the block length.

The block rate in the above definition is our bit rate r. The padding is provided even if the length of the input message M is already divisible by r. Let us call such message  $M_1$ and imagine that there is another message  $M_2$ , which after padding will result in message  $M_1$  and these two **different** messages will produce same output. To avoid this error, the message  $M_1$  should be padded.

Sponge construction has two phases: **absorbing** and **squeezing**. Both phases are described in Subsections 2.1.1 and 2.1.2.

### 2.1.1 Absorbing Phase

First of all, the internal state s consisting of outer and inner part with lengths of r and c respectively, is initialized to zero. The message P is divided into blocks  $P_i$ , each of the length r. The r-bit input message blocks are XORed into the outer part of the state, interleaved with applications of the function f. When all message blocks are processed, the sponge construction switches to the squeezing phase. Function f is realized using KECCAK-f

permutations that we will describe in Section 2.2. Absorbing phase can be described using Algorithm 1.

Algorithm 1: Absorbing phase [6]  $s = 0^{b}$ for i = 0 to  $|P|_{r} - 1$  do  $\begin{vmatrix} s = s \oplus (P_{i}) | 0^{b-r} \\ s = f(s) \end{vmatrix}$ end

### 2.1.2 Squeezing Phase

The second part of sponge construction is the squeezing phase. On the input side it receives the state s obtained in absorbing phase and on the output side it produces the bit sequence of desired length. First of all, the state s is truncated to its first r bits and assigned to  $Z_0$ . If the required output length l is greater than  $|Z_0|$ , then function f is applied to the state and new  $Z_1$  is taken and concatenated with  $Z_0$ . These steps are repeated until  $|Z| \ge l$ . Then Z is truncated to its first l bits and is given as an output of the sponge construction. All of the above can be described using Algorithm 2.

Algorithm 2: Squeezing phase [6]  $Z = \lfloor s \rfloor_r$ while |Z| < l do  $\begin{vmatrix} s = f(s) \\ Z = Z || \lfloor s \rfloor_r$ end return  $|Z|_l$

### 2.1.3 Long Messages Processing

Due to the design of the sponge absorbing stage, it can process messages of arbitrary length. The length of the message only affects the processing time, and does not affect the implementation of the hash function. All resources and blocks required to perform permutations can be reused, which is the benefit of using a sponge function.

### 2.1.4 State Variables

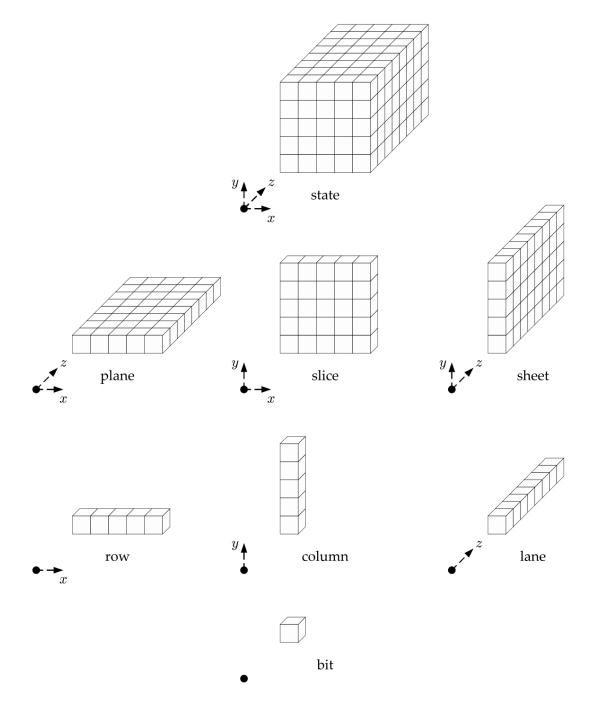

The state s is expressed and treated as a three-dimensional array with dimensions x, y and z. All the operations over x and y are taken modulo 5 and all the operations over z are taken modulo w = b/25 (in our case it is 64). We denote the three-dimensional state as a and one-dimensional state as s. The mapping between s and a coordinate systems is s[w(5y + x) + z] = a[x][y][z] [6].

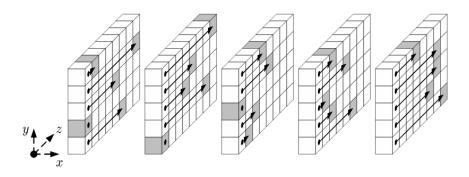

Since the state is a three-dimensional array, we can represent it as a cuboid, with sides x y and z. Next, we divide it into the components shown in Figure 2.2.

Figure 2.2: Parts of the Keccak-f state [6]

The parts of the state have the following properties in the case of SHA-3 [6]:

- plane is a set of  $5 \times 64$  bits with constant y coordinate

- slice is a set of  $5 \times 5$  bits with constant  $\boldsymbol{z}$  coordinate

- sheet is a set of  $5 \times 64$  bits with constant  $\boldsymbol{x}$  coordinate

- row is a set of 5 bits with constant y and z coordinates

- column is a set of 5 bits with constant x and z coordinates

- lane is a set of 64 bits with constant x and y coordinates

### 2.2 Algorithm Steps

SHA-3 hash function implements its permutation function using one of the KECCAK-f permutations. There are 7 permutations in total denoted as KECCAK-f[b], where  $\mathbf{b} = 25 \times 2^{\mathbf{l}}$ and  $\mathbf{l}$  ranges from 0 to 6. The four SHA-3 hash functions (SHA3-224, SHA3-256, SHA3-384 and SHA3-512) uses the KECCAK-f[1600] permutation, which means that the length of the state is 1600 bits.

KECCAK-f[1600] is an iterated permutation, consisting of a sequence of  $n_r = 12 + 2l$  (l = 6) rounds indexed with  $i_r$  from 0 to 23. Every round consists of five steps:

$$\begin{split} \mathbf{R} &= \iota \circ \chi \circ \pi \circ \rho \circ \theta, \text{ with} \\ \theta: \ a[x][y][z] \leftarrow a[x][y][z] + \sum_{y'=0}^{4} a[x-1][y'][z] + \sum_{y'=0}^{4} a[x+1][y'][z-1], \\ \rho: \ a[x][y][z] \leftarrow a[x][y][z-(t+1)(t+2)/2], \\ \text{with } t \text{ satisfying } 0 \leq t < 24 \text{ and } \begin{pmatrix} 0 & 1 \\ 2 & 3 \end{pmatrix}^{t} \begin{pmatrix} 1 \\ 0 \end{pmatrix} = \begin{pmatrix} x \\ y \end{pmatrix} \text{ in } \mathrm{GF}(5)2 \times 2 \\ \text{ or } t = -1 \text{ if } x = y = 0, \\ \\ \pi: \ a[x][y] \leftarrow a[x'][y'], \text{ with } \begin{pmatrix} x \\ y \end{pmatrix} = \begin{pmatrix} 0 & 1 \\ 2 & 3 \end{pmatrix} \begin{pmatrix} x' \\ y' \end{pmatrix}, \\ \chi: \ a[x] \leftarrow a[x] + (a[x+1]+1)a[x+2], \\ \iota: \ a \quad \leftarrow a + \mathrm{RC}[i_r]. \end{split}$$

The last step uses the 24 round constants  $\mathbf{RC}[i_r]$ . These are w-bit long and only applied to the first w bits of the state s. The value of the RC constant is defined as the output of a binary linear feedback shift register (LFSR), the values for KECCAK-f[1600] are defined as follows:

| RC[0]  | 0x00000000000000000 | RC[12] | 0x00000008000808B  |

|--------|---------------------|--------|--------------------|

| RC[ 1] | 0x000000000008082   | RC[13] | 0x80000000000008B  |

| RC[2]  | A8080000000008x0    | RC[14] | 0x800000000008089  |

| RC[3]  | 0x8000000080008000  | RC[15] | 0x800000000008003  |

| RC[4]  | 0x00000000000808B   | RC[16] | 0x800000000008002  |

| RC[5]  | 0x000000080000001   | RC[17] | 0x80000000000008x0 |

| RC[6]  | 0x8000000080008081  | RC[18] | A00800000000000x0  |

| RC[7]  | 0x800000000008009   | RC[19] | A000008000008x0    |

| RC[8]  | A80000000000000x0   | RC[20] | 0x800000080008081  |

| RC[ 9] | 0x000000000000088   | RC[21] | 0x800000000008x0   |

| RC[10] | 0x000000080008009   | RC[22] | 0x000000080000001  |

| RC[11] | A000008000000x0     | RC[23] | 0x8000000080008008 |

Table 2.1: Round constants for the lane size 64 [9]

The algorithm for each step mapping takes a thee-dimensional state array, denoted by a, as an input and returns an updated state array, denoted by a', as the output. The  $\iota$  step has a second input that is a round number. All step mappings require only bitwise Boolean operations and rotation. Now we will look at each of the five steps.

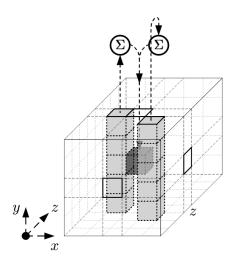

### **2.2.1** Specification of $\theta$

The first step mapping is  $\theta$ . This mapping is linear and translation-invariant in all directions.  $\theta$  applied to a single bit is illustrated in Figure 2.3. The primary goal of this mapping is to include the diffusion onto the hash function. Diffusion means that a single bit affects the value of many other bits and as a consequence a value of a single bit is affected by many other digits [2]. Again, its mathematical representation is the following:

$$\theta: \ a[x][y][z] \leftarrow a[x][y][z] + \sum_{y'=0}^{4} a[x-1][y'][z] + \sum_{y=0}^{4} a[x+1][y'][z-1]$$

The effect of  $\boldsymbol{\theta}$  is to XOR each bit in the state with the parities of two columns in the array.

Figure 2.3:  $\boldsymbol{\theta}$  applied to a single bit [6]

Symbol  $\Sigma$  indicates the XOR sum of all the bits in the column. As we can see, this step can be implemented using only XOR gates.

### **2.2.2** Specification of $\rho$

This step is intended to rotate each lane by some constant value that is calculated according to the definition of this step, which has the following mathematical representation:

$$\rho: \ a[x][y][z] \leftarrow a[x][y][z - (t+1)(t+2)/2]$$

with t satisfying  $0 \le t < 24$  and  $\begin{pmatrix} 0 & 1\\ 2 & 3 \end{pmatrix}^t \begin{pmatrix} 1\\ 0 \end{pmatrix} = \begin{pmatrix} x\\ y \end{pmatrix}$  in GF(5)2 × 2

or  $t = -1$  if  $x = y = 0$

The first equation shows us how the new bit position is calculated. The triangular numbers are used as the offsets. It can be seen with the equation (t + 1)(t + 2)/2 that represents triangular numbers. The second equation demonstrates how the coordinates of rotational constants are computed. The same matrix and principle is used here as in  $\pi$  step and the graphical representation can be found in Figure 2.5. The effect of  $\rho$  step mapping is illustrated in Figure 2.4.

Figure 2.4:  $\rho$  applied to the lanes [6]

Rotation constants and the appropriate coordinates are given in Table 2.2.

| Table 2.2: $\rho$ step offsets [6] | Table 2.2: | [6] |

|------------------------------------|------------|-----|

|------------------------------------|------------|-----|

|       | x = 3 | x = 4 | x = 0 | x = 1 | x = 2 |

|-------|-------|-------|-------|-------|-------|

| y = 2 | 153   | 231   | 3     | 10    | 171   |

| y = 1 | 55    | 276   | 36    | 300   | 6     |

| y = 0 | 28    | 91    | 0     | 1     | 190   |

| y = 4 | 120   | 78    | 210   | 66    | 253   |

| y = 3 | 21    | 136   | 105   | 45    | 15    |

Since all operations over the z coordinate are taken modulo w, these offsets can also be substituted with its value modulo 64. Without  $\rho$  step, the diffusion between slices would be very slow.

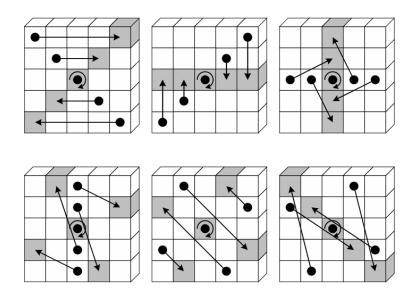

### **2.2.3** Specification of $\pi$

The third step mapping changes the x and y coordinates of every lane except for the first lane. New coordinates are calculated as follows:

$$\pi: \quad a[x][y] \quad \leftarrow a[x'][y'], \text{ with } \begin{pmatrix} x \\ y \end{pmatrix} = \begin{pmatrix} 0 & 1 \\ 2 & 3 \end{pmatrix} \begin{pmatrix} x' \\ y' \end{pmatrix}$$

$\pi$  step applied to a slice is shown in Figure 2.5.

Figure 2.5:  $\pi$  applied to a slice [6]

We can see that the bit with coordinates (0, 0, z) does not change its position. This step is translation-invariant in z-direction and can be implemented by addressing. Inspired by the software implementation [30] we combined the  $\rho$  and  $\pi$  steps into one for the optimization purpose.

### 2.2.4 Specification of $\chi$

The fourth step called  $\chi$  is the only non-linear mapping. Without it, the KECCAK-f round function would be linear, which means that the output of the round is the linear combination of the inputs and hence the input can be found by solving the system of linear equations. The mathematical representation of  $\chi$  step is the following:

$$\chi: a[x] \leftarrow a[x] + (a[x+1]+1)a[x+2]$$

The  $\chi$  step is shown in Figure 2.6.

Figure 2.6:  $\chi$  applied to a single row [6]

Thanks to  $\theta$  and  $\chi$  steps, every bit at the input of the round affects 31 bits at its output, and each bit at the output depends on the 31 bits at the input.

### **2.2.5** Specification of $\iota$

The last step in every round is the addition of a round constant which value is dependent on the current round. This mapping is aimed at disrupting symmetry between individual rounds. This function makes every round unique. The attacks, which are using symmetry (such as slide attacks) in hash functions, will not be effective against the hash function with asymmetrical rounds. This type of attacks is used against the ciphers and hash functions that use the identical permutation function every round [33]. All round constants can be found in Table 2.1. Every round constant is added only to the first lane.

## Chapter 3

# Algorithm Analysis

FPGA and custom digital circuits in general give us the ability to effectively process a large amount of data by splitting this data into parts and processing them in parallel. When examining the algorithm, it is very important to optimally break it into similar pieces, which can subsequently be processed simultaneously. This chapter is devoted to the analysis of the algorithm from the point of view of its implementation at the hardware level.

The digital designers, of course, have a completely different approach to solving the problem than the software engineers. Many things, such as logic operations, rotations and addressing, to name a few, are implemented quite easily and very efficiently at the hardware level. Efficiency is manifested both in the time required to perform these operations, and in the number of elements involved in its implementation. For example, the XOR operation in the FPGA technology is implemented by combinational logic using one logic cell (to be more precise, the lookup table), while in the processor (it may differ depending on the architecture), it is necessary to access the memory in which the variables are stored, pass them through the Arithmetic Logic Unit and save back to memory. The processing time is extended further due to memory latency and the pipelined nature of the processors.

Sequential execution of instructions allows the processor to process 32 or 64 bits at a time (depending on the architecture used), which for "load, compute, store" triple will require  $(1600/32) \times 3 = 150$  iterations to process the whole state s. It is possible that an effective solution can also be found for the software approach which allows the processing of the state quite efficiently. Refer to Chapter 2 in [9] that offers some implementation techniques, such as bit interleaving or plane-per-plane processing. However, using custom digital logic, we can create 1600 XOR cells that works in parallel, which will allow us to carry out the calculation as quickly as possible bounded just by the speed of the signal passing through a logic cell. Of course, it is logical to have a synchronous design implemented using sequential logic, so doing 1600 parallel XOR operations would take us one clock cycle.

It is also important to see the disadvantages that may be associated with the possible acceleration of some algorithms with the help of the hardware accelerator. Despite the fact that parallel computing can occur disproportionately faster than computing by the processor, it is necessary to evaluate whether it makes sense to use hardware acceleration. To clarify this idea, we give an example of the accelerator that requires frequent communication with the processor for its operation. In this design, a lot of time will be spent on communication between the accelerator and the processor. Communication runs on some internal bus, for example, on the AMBA protocol, and this bus is used by other parts of the chip, too, which reduces its throughput from the point of view of the accelerator. This system will spend most of the time forwarding messages, and the advantage that the accelerator gives us may not justify itself.

### 3.1 Key Parameters of the KECCAK for Hardware Implementation

In this section, we describe some aspects of the KECCAK algorithm that make it an ideal candidate for implementation at the hardware level. The structure of this section will be as follows: we call the property of the algorithm, describe why it is an advantage, and how it can be used in its implementation.

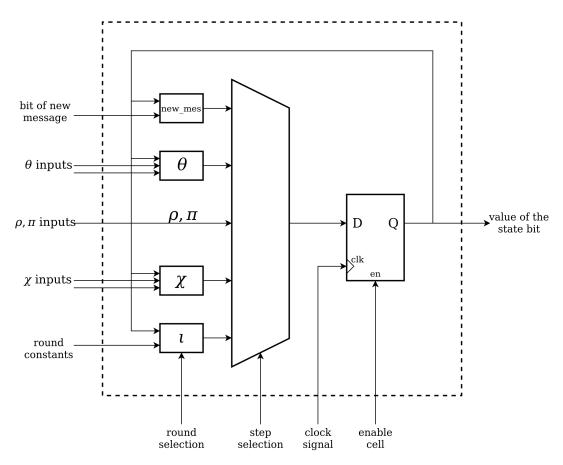

The entire computational process can be implemented using only basic logic gates and one register (DFF) per bit. In Subsection 2.2.1, which describes the  $\theta$  step, we can see the use of only addition operations modulo two, which is the XOR function. The  $\chi$  operation described in Subsection 2.2.4 uses multiplication, addition, and inversion, which implies blocks such as AND, XOR, and NOT. The  $\iota$  operation (Subsection 2.2.5) simply XORs the first lane with the round constant, that is, we use XOR cells. Steps  $\rho$  and  $\pi$  do not use any logic cells. The mentioned DFF is necessary for storing the bit value for one clock cycle. Using only the basic blocks allows us to implement the algorithm in FPGA.

There is no need to use additional memory to store the state value. Here it is meant that the current state value is used only to calculate a new value in the next clock cycle and is not used later. This statement is justified by the structure of the algorithm itself and the absence of any feed-forward loop of the state with further calculations. This property simplifies the implementation of the algorithm and allows the use of only simple sequential logic consisting of DFFs that store the values of individual bits and the combinational logic necessary to calculate new bit values.

It is possible to operate with all 1600 bits of the state s concurrently. Thanks to the DFFs, the value of each bit remains unchanged for one clock cycle and a new value can be calculated during this cycle. The new value of the bits depends only on the previous state value. This allows a parallel approach to implementation, meaning that bit values are calculated and overwritten at the same time. Parallelism can be very effectively realized in custom digital circuits.

Every step mapping of the KECCAK-f permutation function can be executed during one clock cycle. As noted earlier, the only element of the sequential logic is the DFF, which stores bit value, and everything else is implemented using combinational logic, allowing the calculation of the new bit values during one clock cycle. Moreover, inspired by software implementation[30], we combine  $\pi$  and  $\rho$  operations into one, which reduces the execution

time of each round by one clock cycle. One-clock cycle execution allows us to make an initial estimate of the complexity of our solution over time. To process each block  $P_i$  of message P,  $24 \times 4$ , that is, 96 clock cycles, are needed.

All rounds are identical (except for the  $\iota$  step), implying reuse of the blocks and same wiring/addressing. Steps  $\theta$ ,  $\chi$ ,  $\rho$  and  $\pi$  are independent of the current round and are performed identically throughout the entire computational process. It means that the blocks used to calculate the value of the bits can be reused in each round. Despite the fact that the  $\iota$  step is dependent on the round, its principle remains the same, namely, XORing the first lane with the round constant. The XOR operation can be reused, but we need a multiplexer, which will switch one of the XOR inputs to various constants, depending on the current round. Since the constants are given by the algorithm itself and are independent of the input message, they can be calculated at the design stage (see Table 2.1) and, when implemented, they will be hard-wired to the relevant values. This also simplifies the implementation of the algorithm by the fact that there is no need to add LFSR to calculate the constants.

There is no need to use any logic to implement  $\pi$  and  $\rho$  steps, since each bit will always be assigned the value of the exact other bit. For example, bit 576, after completing both steps, will be assigned the value of the 1411 bit. This can be calculated by simply substituting the coordinates of bit 576, that is, (4, 1, 0), in the formulas for  $\pi$  and  $\rho$ , which give us the coordinates of the bit, the value of which is the new value of bit 576. In each round, these coordinates will be the same for bit 576, as for all other bits, which allows us to get rid of the use of any shift registers and logic for rearranging lanes and can be used a simple hard-wired assignment of new addresses.

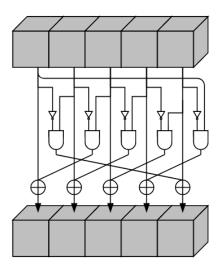

Following the advantages of the algorithm described above, the best solution in terms of speed is to choose a parallel implementation in which we will develop a universal block, later called the keccak-cell, which will allow us to perform all algorithm operations for one bit. Using the versatility of the cell, the KECCAK core will consists of 1600 instances of the keccak-cell, which will be interconnected in a certain way.

### 3.2 Estimation of Resources

Before writing the RTL code, it is needed to estimate required number of logic gates. The theoretical introduction given in Chapter 2, along with the analysis from the previous section, gives us an idea of how individual steps can be implemented. Since we have already decided that the algorithm can be implemented using only the basic logic cells, and these cells can be used repeatedly during the calculations, it is enough to calculate how many elements are needed to implement one round. Each subsequent round will reuse the same blocks and only different round constants will be used (which, as we decided before, does not require any cells and is simply connected to zeroes and ones).

We will implement each step based on its mathematical notation and the pseudocode given

in [6], so that even before writing the code it is possible to evaluate its complexity. In order to further simplify our task, we will calculate how much logic is needed for one bit. Due to the parallel implementation that we have chosen, this number will be just multiplied by 1600 then. A preliminary estimate of the number of elements needed to implement individual steps may differ from the actual implementation, but even this gives us a good idea of whether it makes sense to try to implement the algorithm in this way.

According to the technical documentation of the KECCAK algorithm [6], the following logic gates are needed to implement the single steps:

- 1.  $\boldsymbol{\theta}$  step needs two XOR5 gates and one XOR3 gate

- 2.  $\rho$  and  $\pi$  steps do not require any combinational logic and can be implemented by wiring

- 3.  $\chi$  step uses one NOT, one AND and one XOR

- 4.  $\iota$  step uses constants which can be pre-calculated on implementation stage

All steps and rounds are repeated cyclically and a multiplexer will be used to switch between the steps of the permutation function. Multiplexer will have a minimum of four inputs plus one control input. Four inputs correspond to the new values of this bit after performing a certain step of the function ( $\rho$  and  $\pi$  are combined into one step).

For the  $\iota$  step, we also need a multiplexer that switches between 24 round constants and changes its input every round. Due to the fact that the  $\iota$  step affects only the first lane, there is no need to have a multiplexer for each of the 1600 state bits. Since the lane length is 64 bits, we need 64 such multiplexers.

The presence of multiplexers also presupposes the presence of a control unit, which will gradually increment the control signal, responsible for changing the step, and also, every 4 clock cycles, change the number of rounds. We assume that the control unit does not take up much space in the design, compared with the computing core. The control unit can be implemented using several counters, multiplexers and a small number of standard cells.

After analyzing the individual parts, we can estimate the required number of elements. The implementation of the computational part of the algorithm will take approximately:

| Cell                 | For 1 bit | Total |

|----------------------|-----------|-------|

| AND                  | 1         | 1600  |

| XOR5                 | 2         | 320   |

| XOR3                 | 1         | 1600  |

| NOT                  | 1         | 1600  |

| DFF                  | 1         | 1600  |

| MUX6 (step select)   | 1         | 1600  |

| MUX24 (round select) | 1         | 64    |

In total we have only 5120 basic logic cells to implement every step, 1600 registers to store the bits values and 1664 multiplexers to implement the step and round selection. Modern FPGA chips can implement it without any problem.

### 3.3 Conclusion

In the previous two sections, we examined the properties of an algorithm implemented at the hardware level and explained why we chose a parallel implementation. In addition, we can say that the design of 1600 blocks can be automated, and how the state bits are interconnected can be calculated using the formulas given in Section 2.2.

## Chapter 4

# **HW** Accelerator Description

In this chapter, we present an implementation of the KECCAK algorithm in FPGA. The accelerator we developed can be connected to the processor using some interface for communication. In this chapter only the accelerator (without interface) is described. The accelerator supports all four SHA-3 hash functions (i.e. SHA3-224, SHA3-256, SHA3-384, SHA3-512). The internal architecture of the accelerator is the same for all four versions of the SHA-3 and only the maximum values of some counters in the control unit are changed. The version of SHA-3 can be dynamically changed after the processing of the message is completed.

The accelerator can be easily integrated into an existing system and connected to the processor via a communication bus. Integration and selection of a suitable environment for testing is described in Chapter 7.

Two clock domains are used: one frequency is used for the data processing part of the computing core itself, and the other for communication between the processor and the HW accelerator. Partitioning of the system into several domains is described in detail in Section 4.4.

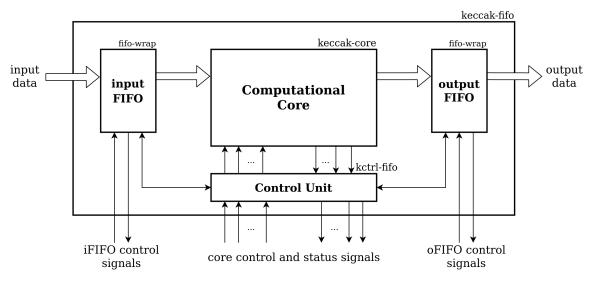

### 4.1 Block Diagram

We will begin the analysis of the accelerator by considering its block diagram. Figure 4.1 shows a simplified block diagram of the accelerator. For readability, the names of individual signals and their width are not shown.

Figure 4.1: Block diagram of the accelerator

All signals of the accelerator can be divided into the following five categories:

- Input data

- Control input FIFO

- Core control and status signals

- Control output FIFO

- Output data

Each group of signals refers to one of the blocks of which the accelerator consists. Each block will be described in Section 4.3, where their structure is analyzed in detail and a description of all signals is given.

Now, in brevity, the principle of operation of this accelerator can be described as follows: the input message is loaded into the input FIFO memory, from where it is then read by the computing core. The core is automated using a control unit, which is responsible for switching the necessary steps and rounds, as well as for sending status messages to the processor about the state of calculations. Upon completion of the calculations, the result is loaded into the output FIFO memory, from where it can subsequently be read by the processor. Despite the fact that the computation is automated, external control is still necessary, which will start loading the message and export the result.

### 4.2 List of Ports

This section describes all the input and output signals used by the accelerator. Signals are shown in Table 4.1. In addition to the signals, one parameter is used to determine the width

of the data.  $DATA\_WIDTH$  parameter can be set to either 32 or 64, depending on the processor architecture or chosen communication interface.

| Name              | Type | $\operatorname{Width}$ | Description                             |

|-------------------|------|------------------------|-----------------------------------------|

| msg_from_cpu_i    | Ι    | DATA_WIDTH             | Input message from the processor        |

| SHA3_version_i    | Ι    | 2                      | Select the SHA-3 version                |

| resetn_i          | Ι    | 1                      | Asynchronous reset. Active low          |

| clk_core_i        | Ι    | 1                      | Clock signal in the core domain         |

| clk_io_i          | Ι    | 1                      | Clock signal in the I/O domain          |

| run_comp_i        | Ι    | 1                      | Starts the computation: load and        |

|                   |      |                        | compute states                          |

| run_export_i      | Ι    | 1                      | Starts exporting of the digest          |

| wr_msg_en_i       | Ι    | 1                      | Enables writing message to input        |

|                   |      |                        | FIFO                                    |

| rd_dig_en_i       | Ι    | 1                      | Enables reading digest from output      |

|                   |      |                        | FIFO                                    |

| clr_i             | Ι    | 1                      | Resets the state $\boldsymbol{s}$ to 0s |

| compute_done_io_o | 0    | 1                      | Indicates the end of computation        |

| export_done_io_o  | 0    | 1                      | Indicates the end of exporting          |

| ififo_empty_io_o  | 0    | 1                      | Indicates if input FIFO is empty        |

| ififo_full_io_o   | 0    | 1                      | Indicates if input FIFO is full         |

| ofifo_empty_io_o  | Ο    | 1                      | Indicates if output FIFO is empty       |

| ofifo_full_io_o   | 0    | 1                      | Indicates if output FIFO is full        |

| dig_o             | Ο    | DATA_WIDTH             | Computed digest                         |

Table 4.1: keccak-fifo signals description

The  $msg\_from\_cpu\_i$  signal, which is 32-bit data that will be connected to a certain external bus during accelerator integration, represents an input message for which the hash value must be calculated. This signal passes directly to the input FIFO memory.

The SHA3\_version\_i signal is a two-bit signal that allows choosing the version of the SHA-3 function. The version is chosen by the processor and may be changed only after the whole message is processed.

The  $resetn_i$  signal is an asynchronous reset that is active low. This signal is used to initialize the whole system.

The signals  $clk\_core\_i$  and  $clk\_io\_i$  are clock signals in the computational and input/output domains, respectively. These domains will be described in detail in Section 4.4.

The  $run\_comp\_i$  signal starts the process of calculating the digest for one block of the input message. If the message has a length of more than one block, it is necessary to start the calculation several times using this command.

The *run\_export\_i* signal starts the process of loading the computed digest into the output FIFO memory. This command needs to be executed only once, when the whole message has already been processed. Later the processor can read the result from the output FIFO memory.

The signal  $wr_msg_en_i$  is connected to the internal input FIFO and allows writing to it the input message sent by the processor. After loading the message, the message will be read by the computing core and processed. Several different messages can be loaded into the memory, however, the accelerator itself is not able to distinguish which message the block belongs to, so it is necessary to control such situation with external signals.

The signal  $rd\_dig\_en\_i$  is connected to the output FIFO memory and allows the processor to read the calculated digest. Thanks to the use of FIFO memory, accelerator can store several different digests, which belong to different input messages and these digests can be read regardless of the current state of the computing core.

The  $clr_i$  signal initializes the state s to zeroes so that it is possible to start the calculation of the digest of the new message. Also, this signal can be used to abort all pending operations and switch the accelerator to the initial state.

The signal *compute\_done\_io\_o* indicates that the loading of the message into the computing core and its subsequent processing are completed and the core is ready for further work. Based on this signal, the processor decides whether it is necessary to start the calculation again (for example, if there are still unprocessed blocks of one message) or whether it is necessary to export the result to output FIFO memory.

The *export\_done\_io\_o* signal indicates the end of the process of exporting the digest to the output FIFO memory, and therefore, the ability to read data from the memory by the processor using the connected bus.

Four signals *ififo\_empty\_o*, *ififo\_full\_o*, *ofifo\_empty\_o* and *ofifo\_full\_o* give us information about the state of two FIFO memories, namely, if the each memory is empty or full. These signals are designed to prevent situations such as trying to write to a full memory or reading from an empty memory.

Finally, the signal *dig\_o*, which connects the output of the FIFO memory to an external bus connected to the processor. Using this signal, the calculated digest is transmitted to the processor.

### 4.3 HW Accelerator Hierarchy

Our implementation can be divided into several hierarchical levels and blocks, some of which are instantiated multiple times, forming a block standing in the hierarchy above.

#### 4.3.1 Main Control Unit

One of the main blocks inside keccak-fifo is kctrl-fifo. It is the main control unit that controls the calculation process itself, input and output FIFO memories, and also receives and sends status signals outside the block. Based on these signals, the calculation process can be started, stopped, and internal state *s* initialized to zeroes.

The list of signals used to communicate with the kctrl-fifo block is shown in Table 4.2 below.

| Name            | Type | Width | Description                                       |  |

|-----------------|------|-------|---------------------------------------------------|--|

| SHA3_version_i  | Ι    | 2     | Select the SHA-3 version                          |  |

| resetn_i        | Ι    | 1     | Asynchronous reset with rising edge synchro-      |  |

|                 |      |       | nized to core clock domain. Active low            |  |

| clk_core_i      | Ι    | 1     | Clock signal in the core domain                   |  |

| run_comp_i      | Ι    | 1     | Starts the computation: load and compute          |  |

|                 |      |       | states                                            |  |

| run_export_i    | Ι    | 1     | Starts exporting of the digest                    |  |

| clr_i           | Ι    | 1     | Resets the state $\boldsymbol{s}$ to 0s           |  |

| compute_done_o  | Ο    | 1     | Indicates the end of computation                  |  |

| export_done_o   | 0    | 1     | Indicates the end of exporting                    |  |

| load_en_o       | 0    | 1     | Enables reading from input FIFO                   |  |

| export_en_o     | 0    | 1     | Enables writing to output FIFO                    |  |

| step_sel_o      | 0    | 3     | Multiplexer control signal for step selection     |  |

| round_sel_o     | 0    | 5     | Multiplexer control signal for round selection    |  |

| kcore_out_sel_o | 0    | 3     | Multiplexer control signal for digest part selec- |  |

|                 |      |       | tion                                              |  |

| en_o            | 0    | 1600  | Enables keccak-cell DFFs                          |  |

Table 4.2: kctrl-fifo signals description

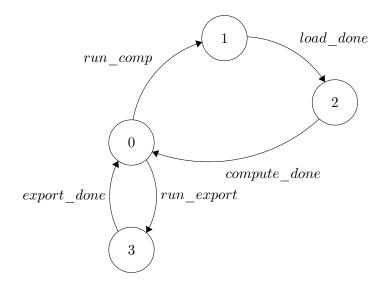

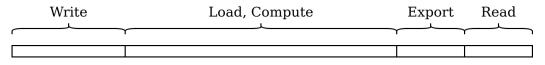

This block controls three tasks: loading a message, calculating the result and exporting the digest. To implement its operation we define the finite state machine with the total of 4 states. The first state is the IDLE(0) state, when the outputs of all cells are blocked and cannot be changed and all internal counters are stopped. As we can see in Figure 4.2, from this state system has the ability to go into the EXPORT(3) state and into the LOAD(1) followed by COMPUTE(2) states. After the command  $run\_comp$  is asserted, the system goes into a LOAD state and reads the data block from the input FIFO memory for the required number of clock cycles (based on the length of the read block). The number of clock cycles required to read the message can be calculated in advance, since the length of the block is always fixed for a specific version of SHA-3 function. The counter responsible for controlling whether the message was read, counts up to a certain point and then generate the signal *load\_done*. This signal changes the state machine from the LOAD state to the COMPUTE state.

Figure 4.2: kctrl-fifo states

In this state, several counters are used, which are responsible for generating control signals for each keccak-cell (described in Subsection 4.3.4). One of the counters counts from 2 to 5, that is, it switches the multiplexer between  $\theta$ ,  $\rho$  and  $\pi$  (performed simultaneously),  $\chi$ and  $\iota$ . When these steps are completed, the counter is cleared and begins to count again, moving to a new round. The second counter is used as a round counter, counting from 1 to 24. The counter value increases every four clock cycles, which are necessary to complete the four steps. The simultaneous overflow of both counters indicates the end of calculation of one message block. This generates a *compute\_done* signal, and the FSM returns back to the IDLE state. If there are still further data in the input FIFO memory related to the same message, the data-load and calculation process shall be started again. When the whole message was processed, the digest can be exported, using the *run\_export* signal, the state machine goes into the EXPORT state and writes the result to the output FIFO memory. This operation takes a fixed number of clock cycles, which depends on the digest length.

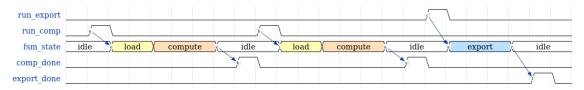

Figure 4.3 shows an approximate principle of operation of this state machine.

Figure 4.3: kctrl-fifo operation

As can be seen, the *run\_comp* signal switches the state machine to the message loading and starts the computational algorithm. At the end of the calculations, the *comp\_done* signal is generated, based on which the processor can either start the next block calculation again or start exporting the result. Figure 4.3 shows the operation of the control unit for a message consisting of two blocks. Despite the fact that the execution time for the calculation and export operations is shown as the same, calculations take up more time than exporting.

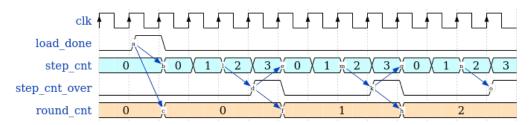

Figure 4.4 shows the control signals for multiplexers in keccak-cells at the beginning of calculations. We can see how the whole process is started by the *load\_done* command, after which the counters begin to increase.

Figure 4.4: kctrl-fifo operation in the beginning of computation

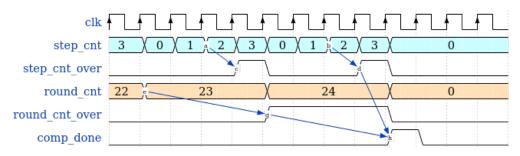

Figure 4.5 shows the last few cycles of the calculation state. When both counters overflow (that is, the last step and the last round are executed), the *comp\_done* signal is generated and the counters are cleared.

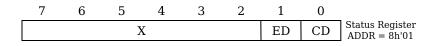

Figure 4.5: kctrl-fifo operation in the end of computation