# **Application of SiC MOSFET in Industrial Power Supplies**

## Bc. David Kudelásek

master's thesis

## 2019

Ing. Vladimír Janíček, Ph.D.

supervisor

## **Czech Technical University in Prague**

Faculty of Electrical Engineering, Department of Microelectronics

## ZADÁNÍ DIPLOMOVÉ PRÁCE

#### I. OSOBNÍ A STUDIJNÍ ÚDAJE

Příjmení:

Kudelásek

Jméno: David

Osobní číslo: 420333

Fakulta/ústav:

Fakulta elektrotechnická

Zadávající katedra/ústav: Katedra mikroelektroniky

Studijní program: Elektronika a komunikace

Studijní obor:

Elektronika

#### II. ÚDAJE K DIPLOMOVÉ PRÁCI

Název diplomové práce:

Aplikace MOSFET tranzistorů na bázi SiC v průmyslových napájecích zdrojích

Název diplomové práce anglicky:

Application of SiC MOSFETs in Industrial Power Supplies

#### Pokyny pro vypracování:

- 1. Zhodnot'te problematiku použití SiC MOSFET tranzistorů v průmyslových napájecích zdrojích.

- 2. Navrhněte měnič typu flyback s možností použití vysokonapěťových tranzistorů SiC, stejně tak jako tranzistorů Si. Vstupní napětí: 150 V DC - 1 kV DC, výstup 24 V, 100 W.

- 3. Simulujte a změřte spínací vlastnosti použitých tranzistorů. Analyzujte výsledky.

- 4. Otestujte funkčnost navrženého zdroje a změřte jeho parametry.

- 5. Porovnejte tranzistory SiC a Si podle účinnosti a teplotních měření.

- 6. Shrňte a zhodnoťe výhody použití Si či SiC tranzistorů.

#### Seznam doporučené literatury:

- 1) SHUR, Michael & collective; SiC Materials and Devices; World Scientific, 2006; ISBN: 9812773371

- 2) MOHAN, Ned; UNDELAND, T. M.; ROBBINS, W. P.; POWER ELECTRONICS Converters, Applications, and Design; Wiley; 1995; USA; ISBN: 0-471-30576-6

- 3) STMicroelectronics; AN4671, Application note: How to fine tune your SiC MOSFET gate driver to minimize losses; 2015

Jméno a pracoviště vedoucí(ho) diplomové práce:

Ing. Vladimír Janíček, Ph.D., katedra mikroelektroniky FEL

Jméno a pracoviště druhé(ho) vedoucí(ho) nebo konzultanta(ky) diplomové práce:

Datum zadání diplomové práce: 01.10.2019

Termín odevzdání diplomové práce:

Platnost zadání diplomové práce: 30.09,2021

ng. Vladimír Janíček, Ph.D. podpis vedoucí(ho) práce

podpis vedoucí(ho) ústavu/katedry

prof. Mgr. Petr Pata, Ph.D.

#### III. PŘEVZETÍ ZADÁNÍ

Diplomant bere na vědomí, že je povinen vypracovat diplomovou práci samostatně, bez cizí pomoci, s výjimkou poskytnutých konzultací. Seznam použité literatury, jiných pramenů a jmen konzultantů je třeba uvést v diplomové r

11.12, 2019

Datum převzetí zadání

Podpis studenta

## Acknowledgement

I would like to express many thanks to my supervisor Ing. Vladimír Janíček, Ph.D. for his suggestions and ideas towards this thesis. Also to STMicroelectronics Prague PowerLab, because without the collaboration this thesis most probably wouldn't exist.

A very special thanks go to Sanjin Kek and Magdalena Dědičová – for all the help and support during the development of this thesis!

## Declaration

I declare that the presented thesis was developed independently and that I have quoted all sources of information. This was made in accordance with the methodical instructions about ethical principles for writing academic thesis.

Abstract Abstrakt

Key of this master's thesis is to analyze, simulate, compare and discuss the application of Silicon-Carbide MOSFET in industrial power supplies. With consideration to driving SiC MOSFET with usual PWM controllers. The whole problem is demonstrated on 24V 100W Flyback converter, same as a comparison with standard silicon-based MOSFET.

Záměr této diplomové práce je analýza, simulace, porovnání a diskuze aplikace tranzistorů MOSFET na bázi karbidu křemíku v průmyslových zdrojích. Pozornost je věnována řízení SiC MOSFETů standartními kontroléry. Celá problematika je popsána na 24V 100W měniči typu Flyback, stejně tak jako porovnání se standartním křemíkovým MOSFETem.

Keywords Klíčová slova

SiC, SiC MOSFET, Industrial, Flyback

SiC, SiC MOSFET, Průmyslový, Flyback

## Contents

| 1 Introduction                                                       | 1  |

|----------------------------------------------------------------------|----|

| 1.1 About SiC                                                        | 1  |

| 1.1.1 SiC as wide bandgap semiconductor                              | 2  |

| 1.2 Industrial power supplies                                        | 3  |

| 2 Flyback design                                                     | 5  |

| 2.1 Brief review of Flyback operation                                | 6  |

| 2.2 Input section                                                    | 7  |

| 2.3 Chip selection                                                   | 8  |

| 2.3.1 High voltage startup                                           | 8  |

| 2.3.2 Soft-start and OCP                                             | 8  |

| 2.4 Flyback transformer                                              | 11 |

| 2.4.1 Transformer calculation with consideration to other components | 11 |

| 2.4.2 Core, bobbin and wire selection                                | 13 |

| 2.4.3 Designed transformer                                           | 16 |

| 2.5 Final schematic and PCB layout                                   | 17 |

| 2.6 EMI optimization                                                 | 20 |

| 2.6.1 Further improvements                                           | 21 |

| 3 Analysis of SiC driving and switching                              | 24 |

| 3.1 Problematics of driving SiC MOSFET                               | 24 |

| 3.2 Design of Gate-Drive module                                      | 25 |

| 3.2.1 Design topology and schematic                                  | 25 |

| 3.2.2 Gate-Drive transformer design                                  | 27 |

| 3.3 Focus on MOSFET parameters                                       | 29 |

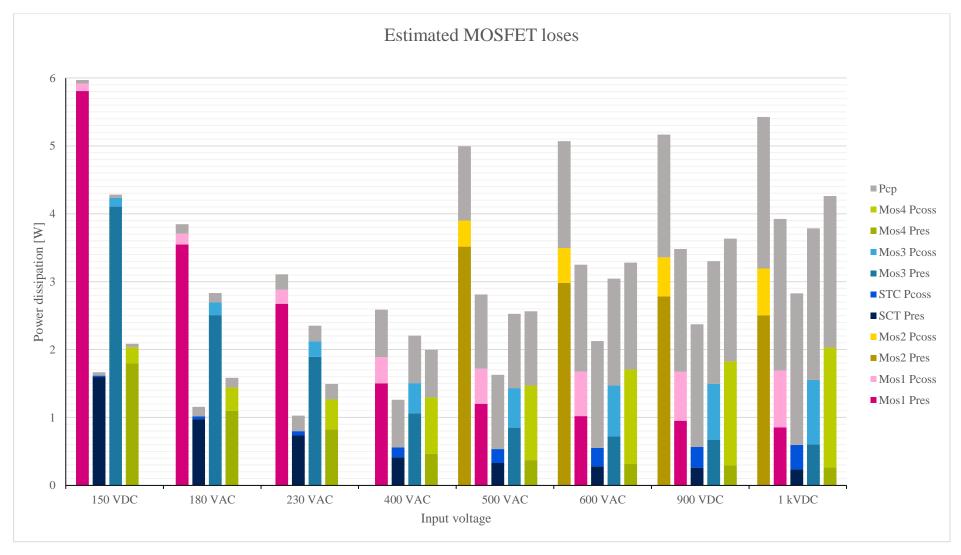

| 3.4 Losses estimation and simulation                                 | 29 |

| 3.4.1 Resistive losses                                               | 29 |

| 3.4.2 Switching losses                                               | 31 |

| 3.4.3 Losses estimation                                              | 34 |

| 4 Si vs SiC                                                          | 36 |

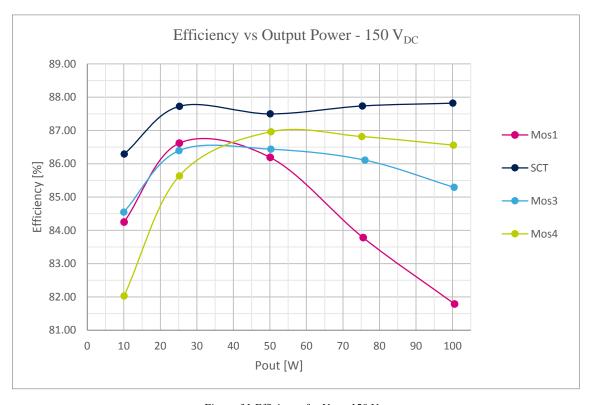

| 4.1 Efficiency measurement                                           | 36 |

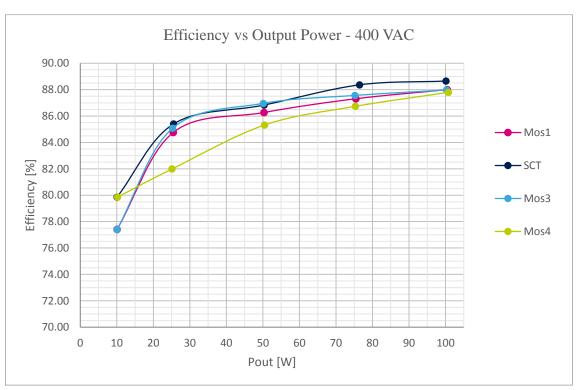

| 4.1.1 Lower input voltages                                           | 36 |

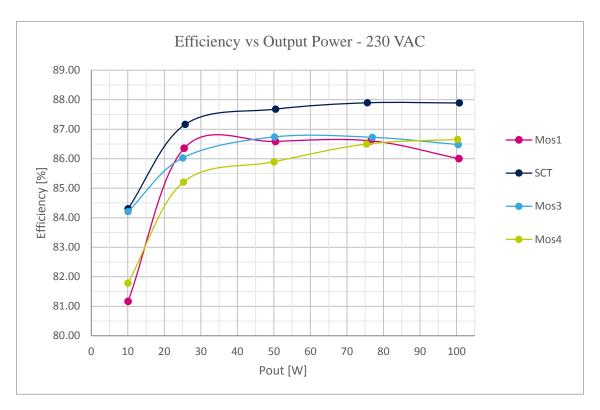

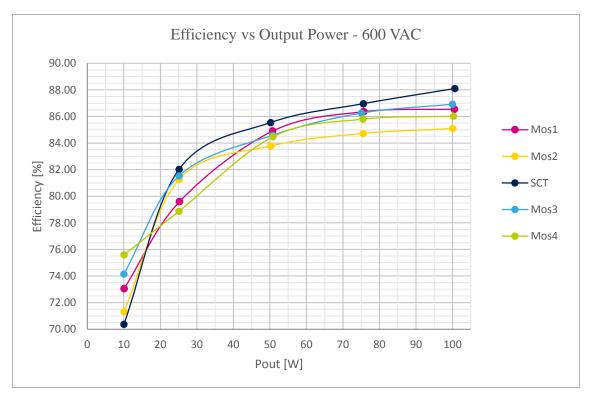

| 4.1.2 Midrange input voltages                                        | 37 |

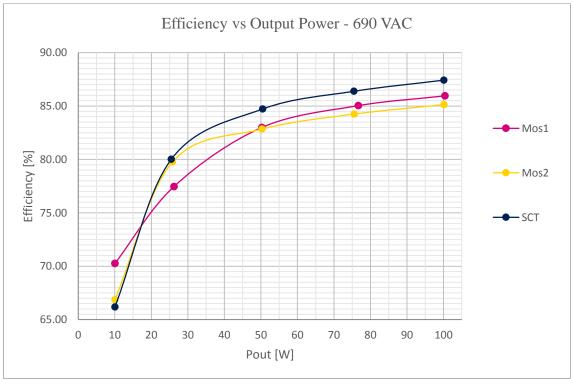

| 4.1.3 Higher input voltages                                          | 38 |

| 4.2 Assessment of losses estimation                                  | 41 |

| 4.2.1 Full load estimation                                           | 41 |

| 4.2.2 Estimation of efficiency depending on the load                 | 43 |

| 4.3 Switch-off behavior                                                  | 45 |

|--------------------------------------------------------------------------|----|

| 4.3.1 Slew rate                                                          | 45 |

| 4.3.2 Operation in saturation region                                     | 45 |

| 4.3.3 Further observation of saturation losses and limits of used method | 47 |

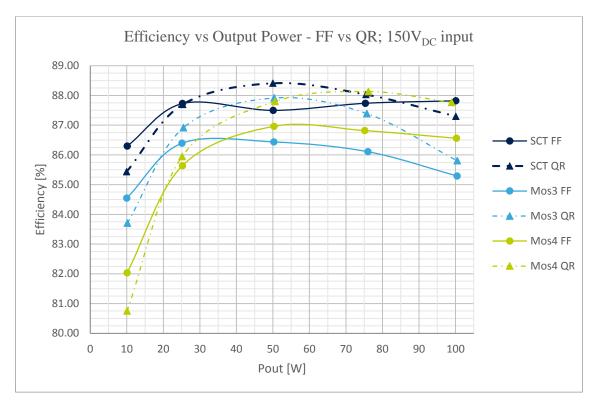

| 4.4 Quasi-resonant operation                                             | 50 |

| 4.4.1 Comparison between QR and FF                                       | 50 |

| 4.4.2 Effect of voltage and maximum frequency on QR                      | 55 |

| 4.5 Thermal measurements                                                 | 58 |

| 4.5.1 Junction temperature                                               | 59 |

| 4.5.2 Other thermal measurements.                                        | 60 |

| 5 Conclusion & Summary                                                   | 61 |

| Bibliography & Sources                                                   | 63 |

| Appendix A – The rest of efficiency measurements                         | 65 |

| Appendix B – Digital content                                             | 67 |

## List of figures

| Figure 1 Dunwoody's "wave-responsive device", w- parts are made of SiC; credit: [3]                                          | 1        |

|------------------------------------------------------------------------------------------------------------------------------|----------|

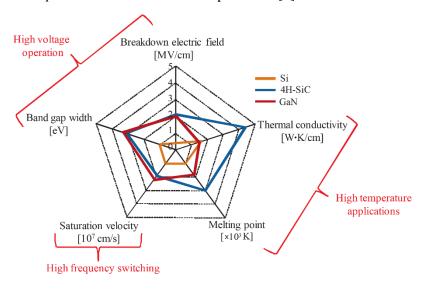

| Figure 2 Si, SiC and GaN comparison; credit: [4]                                                                             |          |

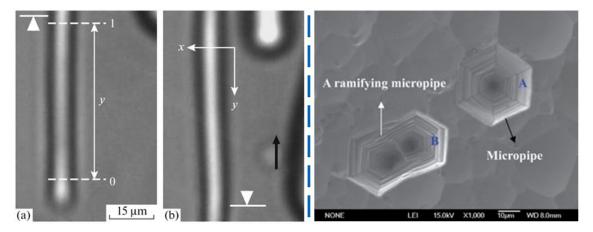

| Figure 3 Micropipes in transection (credit: [6]); cross-section (credit: [7])                                                | 3        |

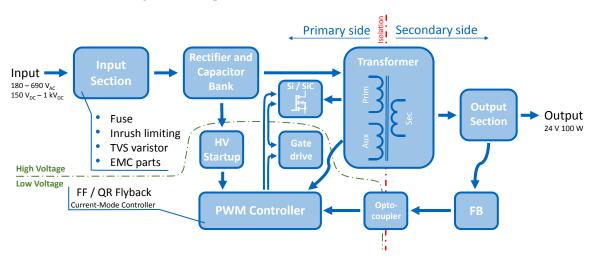

| Figure 4 Block diagram of designed converter                                                                                 | 5        |

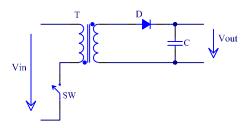

| Figure 5 Simplified flyback schematic                                                                                        | 6        |

| Figure 6 Input section                                                                                                       | 7        |

| Figure 7 HV startup circuit                                                                                                  | 8        |

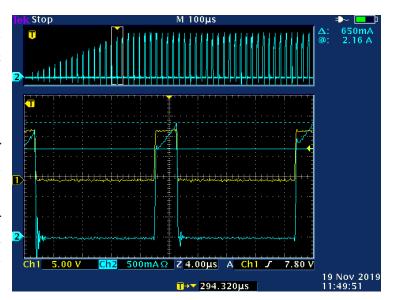

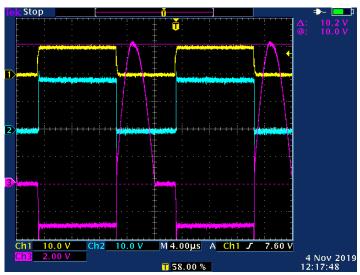

| Figure 8 CCM while starting (in: 150 V <sub>DC</sub> ,; loaded) <b>Yellow</b> – V <sub>GS</sub> <b>Blue</b> - I <sub>D</sub> | 9        |

| Figure 9 Soft-start circuit                                                                                                  |          |

| Figure 10 Currents in boundary DCM                                                                                           |          |

| Figure 11 Magnetic field vectors in air gap; credit: [25]                                                                    |          |

| Figure 12 Skin effect in round wire; credit: [21]                                                                            | 15       |

| Figure 13 Winding layers                                                                                                     |          |

| Figure 14 CF138 permeability vs magnetic flux density; credit: [26]                                                          |          |

| Figure 15 Board v1 in the front with connected Gate-Drive module (revealed later in subchar                                  |          |

| 3.2) and board v2 in the behind already with better fuse and final EMI components                                            | •        |

| Figure 16 Final schematic of flyback converter                                                                               |          |

| Figure 17 PCB layout for v1 - TOP layers are on the top, BOT on the bottom (not mirrored)                                    |          |

| Figure 18 PCB layout for v2 - TOP layers are on the top, BOT on the bottom (not mirrored)                                    |          |

| Figure 19 Conductive EMI measurement; Yellow: Quasi-peak L, Green: Average L, Gray:                                          |          |

| Quasi-peak N, Blue: Average N                                                                                                | 20       |

| Figure 20 - a) v1 routing b) v2 routing                                                                                      |          |

| Figure 21 PCBs EMI comparison: v1 – dark red (marker M1), v2 – blue (marker M2)                                              |          |

| Figure 22 Additional comparison: Top – standard capacitor bank; Middle – triple capacitor                                    |          |

| bank; Bottom - both                                                                                                          | 23       |

| Figure 23 - a) STW12N150K5 output characteristics b) SCT1000N170 output characteristic                                       |          |

| credit [8][9] 24                                                                                                             | -        |

| Figure 24 Gate-Drive module schematic                                                                                        | 25       |

| Figure 25 Parasitic capacitance effect; 1 - generator, 2 - V <sub>GS</sub> , 3 - V <sub>Aux</sub>                            |          |

| Figure 26 Gate-Drive module for board v1                                                                                     |          |

| Figure 27 Hopkinson's law illustration; credit: [21]                                                                         |          |

| Figure 28 Parasitic capacitances of Mos1, credit: [16]                                                                       |          |

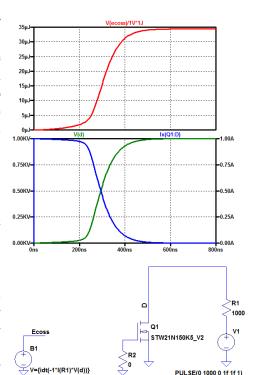

| Figure 29 C <sub>oss</sub> energy (Red trace) simulation.                                                                    |          |

| Figure 30 Estimated MOSFET losses                                                                                            |          |

| Figure 31 Efficiency for $V_{in} = 150 V_{DC}$                                                                               |          |

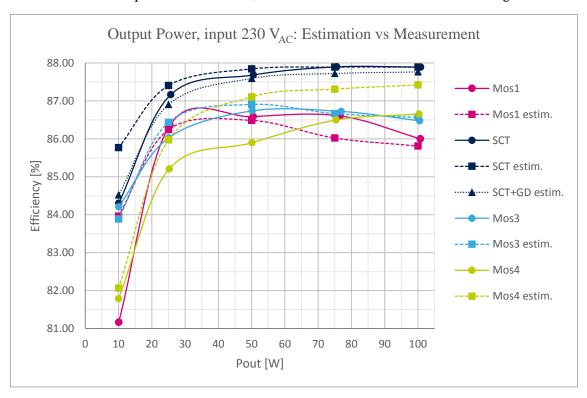

| Figure 32 Efficiency for $V_{in} = 230 V_{AC}$                                                                               |          |

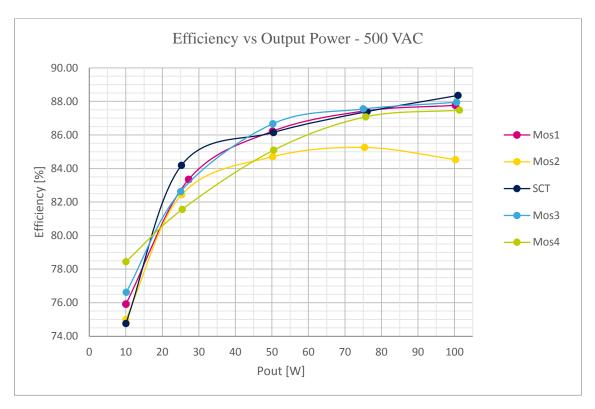

| Figure 33 Efficiency for $V_{in} = 500 V_{AC}$                                                                               |          |

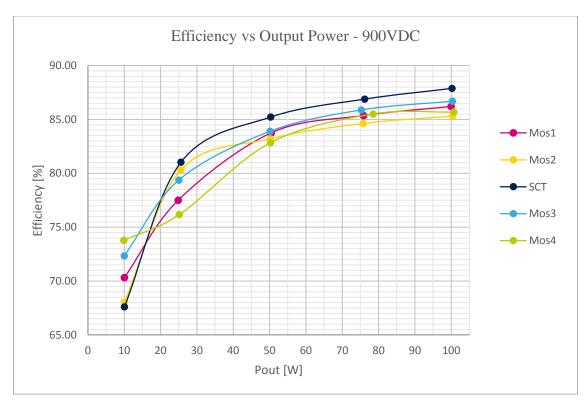

| Figure 34 Efficiency for $V_{in} = 900 V_{DC}$                                                                               |          |

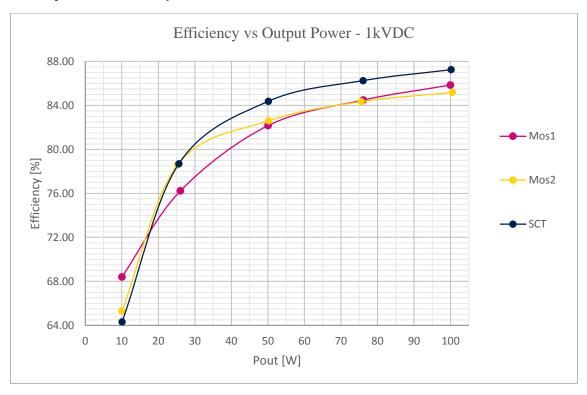

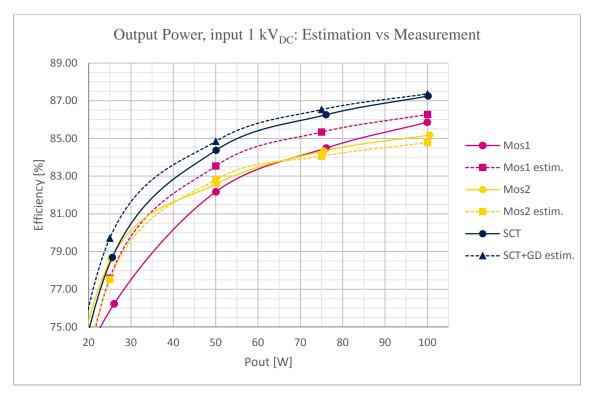

| Figure 35 Efficiency for $V_{in} = 1 \text{ kV}_{DC}$                                                                        |          |

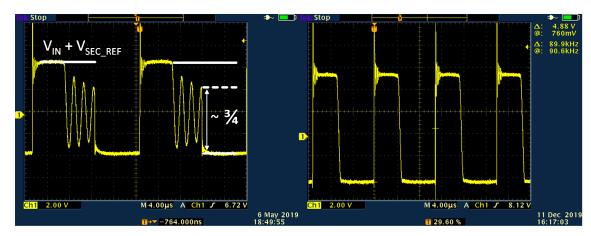

| Figure 36 Indirect transformer voltage measurement                                                                           |          |

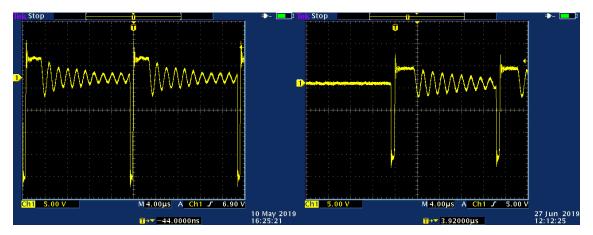

| Figure 37 Switching of a) SCT b) Mos1                                                                                        |          |

| Figure 38 Estimation vs measurement for 230V <sub>AC</sub> input                                                             |          |

| •                                                                                                                            |          |

| Figure 39 Estimation vs measurement for 1kV <sub>PC</sub> input                                                              |          |

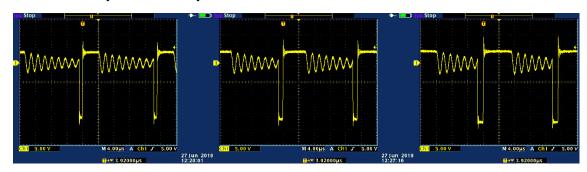

| Figure 40 Mos1 a) 25W load b) 50W load c) 75W load for 1kVDC                                                                 | 44       |

| Figure 39 Estimation vs measurement for $1kV_{DC}$ input                                                                     | 44<br>44 |

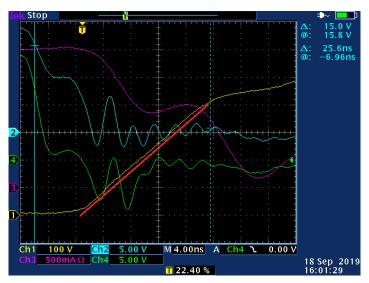

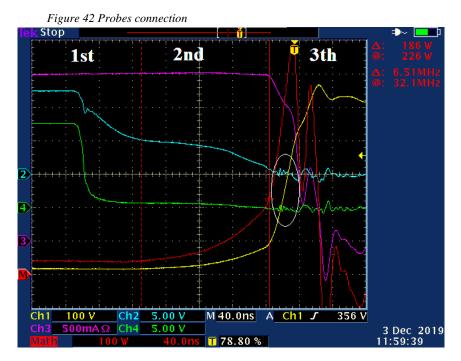

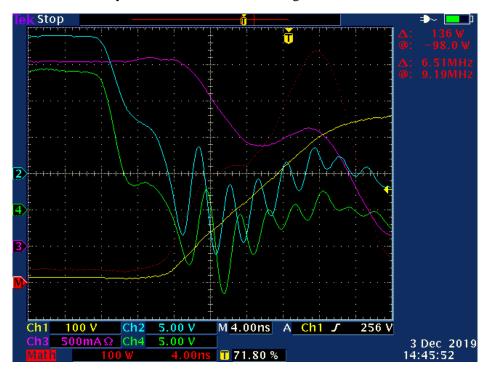

| Figure 43 Measured switch-off of Mos4 ( $R_G = 10 \Omega$ ); Ch1 – Drain, Ch2 – Gate, Ch3 – Drain | l    |

|---------------------------------------------------------------------------------------------------|------|

| current, Ch4 – Gate-Drive, Math – Ch1·Ch3                                                         |      |

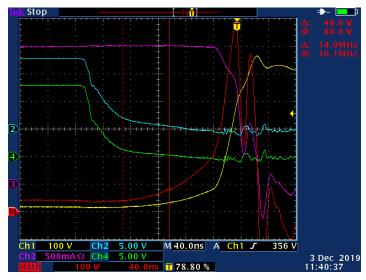

| Figure 44 Mos4 switch-off with $1\Omega$ gate resistor; Ch1 – Drain, Ch2 – Gate, Ch3 – Drain      |      |

| current, Ch4 – Gate Drive, Math – Ch1·Ch3                                                         | . 48 |

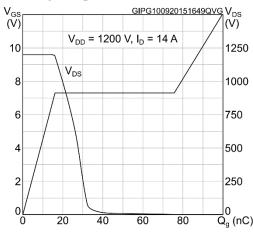

| Figure 45 Mos4 Gate charge vs V <sub>GS</sub> ; credit: [15]                                      | . 48 |

| Figure 46 SCT switch-off with 1Ω R <sub>G</sub> ; Ch1 – Drain, Ch2 – Gate, Ch3 – Drain current,   |      |

| Ch4 – Gate Drive, Math – Ch1·Ch3                                                                  | . 49 |

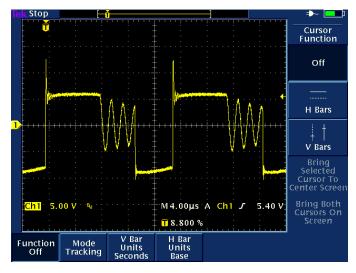

| Figure 47 Fixed-frequency switching                                                               | . 50 |

| Figure 48 Comparison FF vs QR for input voltage 150 V <sub>DC</sub>                               | . 51 |

| Figure 49 a) fixed-frequency switching b) quasi-resonant switching                                |      |

| Figure 50 SCT switching for 100W load, QR and 150 V <sub>IN</sub>                                 |      |

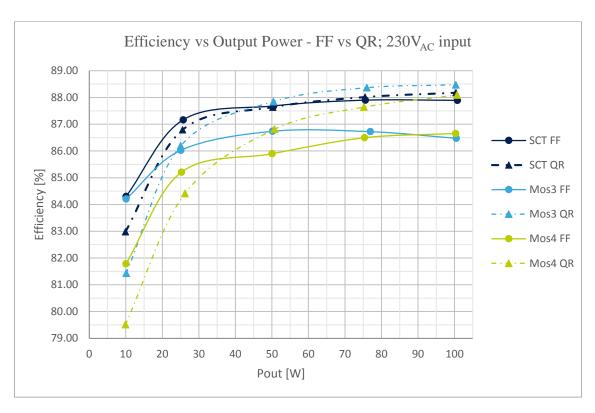

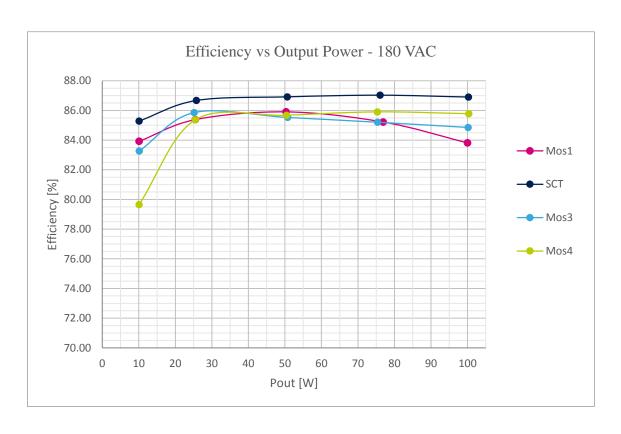

| Figure 51 Comparison FF vs QR for input voltage 230 V <sub>AC</sub>                               |      |

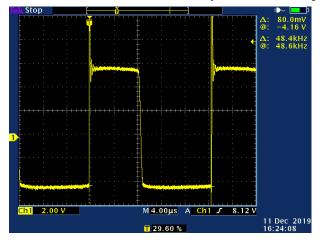

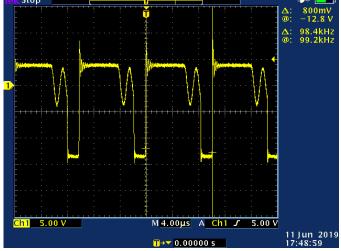

| Figure 52 Switching of SCT for FF, full load and 230V <sub>AC</sub> input                         | 53   |

| Figure 53 Switching of SCT for QR, 10W load and 230V <sub>AC</sub> input                          |      |

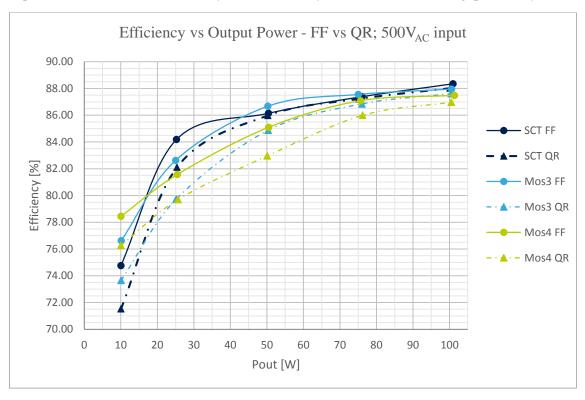

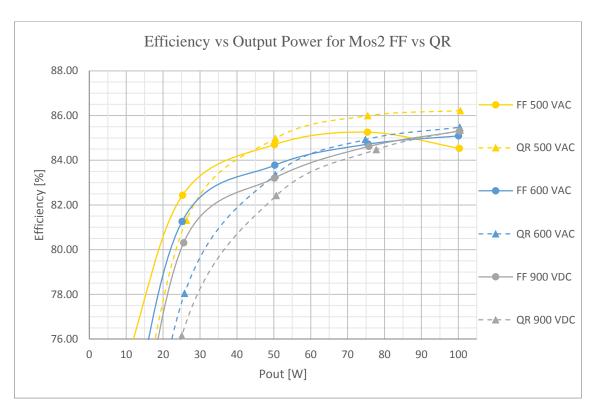

| Figure 54 Comparison FF vs QR for input voltage 500 V <sub>AC</sub>                               | . 55 |

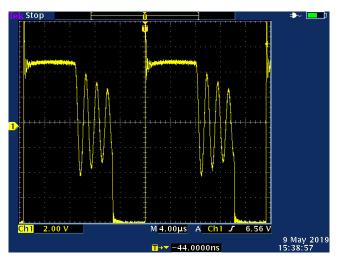

| Figure 55 Switching of Mos3 for QR, full load and 500V <sub>AC</sub> input                        | . 55 |

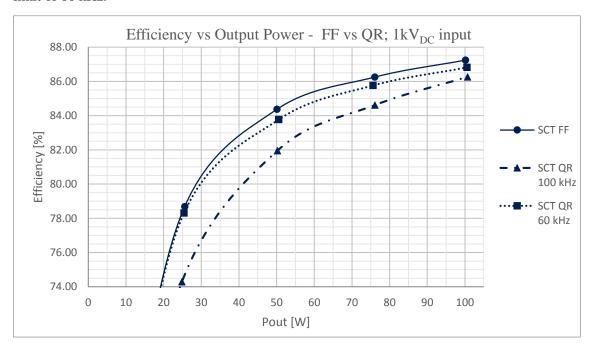

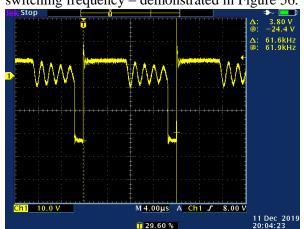

| Figure 56 Comparison of QR 100 kHz and 60 kHz with FF, 1kV <sub>DC</sub> input                    |      |

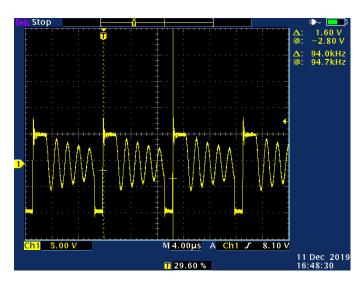

| Figure 57 Switching of SCT for QR 60 kHz, full load and 1kV <sub>DC</sub> input                   |      |

| Figure 58 Effect of QR on Mos2                                                                    | . 57 |

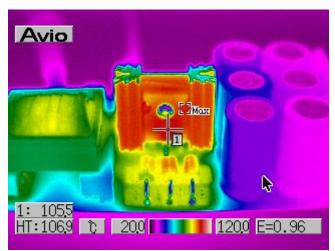

| Figure 59 Thermal measurements on board v1 with thermographic camera; Mos1 690V <sub>AC</sub> in  | put, |

| full load                                                                                         | _    |

| Figure 60 Capacitor bank temperature                                                              | . 60 |

| Figure 61 Output diode temperature, full load                                                     |      |

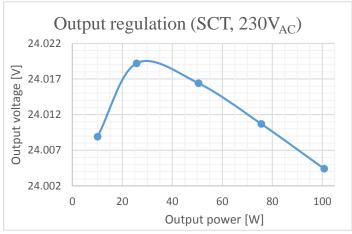

| Figure 62 Output regulation                                                                       |      |

|                                                                                                   |      |

## Abbreviations

SiC Silicon carbide

EMI Electro-magnetic interference

WBG Wide bandgap

FF Fixed frequency

QR Quasi-resonant

ST STMicroelectronics

HV High voltage

NTC Negative temperature coefficient thermistor

SMD Surface mount device OCP Overcurrent protection

CCM Continuous-conduction mode DCM Discontinuous-conduction mode

SS Soft-start

IC Integrated circuit

$\begin{array}{ll} AMR & Absolute\ maximum\ rating \\ PCB & Planar\ circuit\ board \\ R_{sense} & Current\ sensing\ resistor \end{array}$

CMM Common-mode

PSU Power supply unit

DC Direct current

AC Alternating current

UVLO Under-voltage lock-out

## 1 Introduction

This diploma thesis focuses on comparison of Si and SiC based MOSFETs. The whole problem is demonstrated on 100W flyback converter with high input voltage range: from 150  $V_{DC}$  up to 1  $kV_{DC}$ . After a brief introduction in the first chapter, the second chapter summarizes whole flyback design. The design is described thoroughly, because for valid measurement and data interpretation is necessary to understand it completely, know its limits and all parameters which can affect the measurement, mostly in a not preferable way.

The third chapter starts with Si and SiC MOSFET theoretical introduction. The necessity of different driving is discussed, therefore following section presents the idea of Gate-Drive module. There is also focus on losses estimation and from there efficiency prediction. Chapter four presents measurements and puts them in comparison with predicted / estimated values. As this is a multiple criteria problematic, each major one is included and measurements were optimized in order to separate them as much as possible for further observation.

Final evaluation of results is made in the last chapter, same as comparison of Si and SiC MOSFETs for this application based on measurements. Not only them, but the whole design is summarized for further optimization or improvements. As I firmly believe, all important data for closer observation or verification are attached in digital form on CD or in Attachments.zip for online version.

One more thing to say in the beginning: as this thesis is written in English, I'm going to use nomenclature typical for English-speaking countries, instead of Czech. This refers especially to voltage: V instead of U; any other possibly-different unit (e.g. duty cycle) will be described, so any misunderstanding is improbable.

#### 1.1 About SiC

Silicon carbide is in recent years well known as one of wide bandgap semiconductors. Depends on polytype (which are approx. 250), bandgap can be up to 3.3 eV. Besides of that, its synthetic form is being used in industrial sector since the end of 19<sup>th</sup> century. With hardness of 9 of Mohs scale is one of the most hard synthetic materials. As a stable chemical compound with excellent physical properties silicon carbide finds its place in abrasive, grinding and cutting industry.

In electronics, first use of SiC is dated not so long after. When Henry H. C. Dunwoody patented his Wireless-telegraph system in 1906, a "wave-responsive device" (Figure 1) was a truly important component. This was nothing else than a primitive point-contact diode which obtained signal rectification. And – it was based on silicon carbide.

Figure 1 Dunwoody's "wave-responsive device", w- parts are made of SiC; credit: [3]

Soon after that (in 1907) yellow and blue electroluminescent emission of SiC crystal was found by H. J. Round. Another, a "pre-breakdown" emission, had been discovered by O. Losev in 1923. Opposed to these early inventions, not so many devices were based on SiC. Except LEDs, no other semiconductor devices were made widely until 1990s.

[1] [2] [3]

#### 1.1.1 SiC as wide bandgap semiconductor

As semiconductors took their part in industrial sector, standard silicon parts shortly became insufficient for higher voltages. The debate on WBG semiconductors starts already in the 1950s and in the 1960, W. B. Shockley's *Introductory remarks on silicon carbide, a high-temperature semiconductor* was published [4].

Figure 2 Si, SiC and GaN comparison; credit: [4]

Finding a different compound element or instead of silicon sounded well: wider bandgap is more or less proportional with higher breakdown electric field, thus components for higher voltage and / or with smaller chip could be made. Also, not only the bandgap doesn't make silicon the best material for power devices: as it's illustrated in Figure 2, Si can be easily beaten in other parameters too. It's not a big surprise that new materials such as aluminium

nitride, gallium nitride and silicon carbide were tested. Even though WBG semiconductors are better (at least on paper), in these days' standard silicon components are still frequently used for high voltage applications.

It's mostly because the technology for Si components is well-known and proven after decades of production. Furthermore, this massive production decreases the price of Si chips. Opposed to, WBG semiconductors in the market starts from zero, with not as significant manufacturing progress as silicon industry. Just for illustration: Czochralski method is quite well known in electrical engineers' community as the only widely used method for making Si ingots. Those can be up to 2 m in height and weigh hundreds of kilograms. Unfortunately, this method is useless in SiC monocrystalline production. Instead, much more sophisticated and hence expensive Lely method is used. Based on sublimation an epitaxial growth in a low-pressure inert gas atmosphere, the result is quite poor compared to the Czochralski process: SiC *boules*<sup>1</sup> with maximum diameter 15 cm and useable height 20-25 mm, weighing not much more than one kilogram [5].

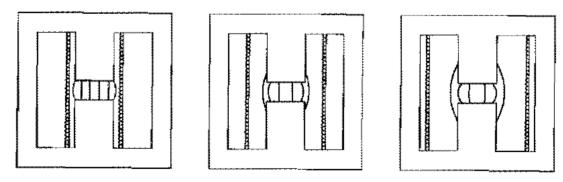

Yet another problem comes with SiC wafers: besides interstitial, substitution, vacancy or dislocation, another kind of defect appears in SiC boules – micropipe. Micropipes arise from vacancy, but of whole lattice, not a single molecule. Once this happens, they keep growing up

<sup>&</sup>lt;sup>1</sup> Official term for product of Lely method instead of ingots for Czochralski method [2]

with the crystal. They also spread up to approx. 10 µm in diameter, so large area is affected (for illustration Figure 3).

Figure 3 Micropipes in transection (credit: [6]);

cross-section (credit: [7])

Combination of difficult Lely method and small boules make SiC wafer cost higher than silicon. Because of micropipes, not whole area can be used. This is critical mostly for high-power devices: the larger chip area is required, the bigger possibility of conflict with micropipe. Besides this disadvantage, thanks to its characteristics, SiC devices need a smaller chip area compared to their equivalent Si device.

[2] [4] [5][7]

### 1.2 Industrial power supplies

Converter designed in this thesis aims for usage in industrial sector as auxiliary power supply. Industrial units and machinery use mains directly, or power supplies mostly in range from tents kilowatts up to one megawatt. Except those primary PSUs very often another – auxiliary – power supplies are required. Those are used for another necessary purposes, i.e. user interface, control units, cooling etc.

There are many requirements on industrial power supplies, which are different from standard (home and office) designs. Most importantly:

- Input Voltage: In Europe, typical industrial mains voltage is 690 V<sub>AC</sub>, also 400 V<sub>AC</sub> is frequently used, sometimes 500 V<sub>AC</sub>. This design should be as versatile as possible, so it should work on 230 V<sub>AC</sub> mains too. DC-powered machinery, and so the DC mains, aren't unusual, but the voltage is sometimes specifically defined by the manufacturer. In photovoltaic sector, currently heavily used value is 1 kV<sub>DC</sub>. Either way, auxiliary PSU often obtains safety functions, therefore they should handle undervoltage. Thus many of them have quite wide input voltage range.

- Input transient voltage protection: Especially heavy machinery may cause voltage transients to appear way more frequently than in standard mains. They can be caused also by natural events, but still industrial power supplies must manage stronger transient than home / office PSUs: up to 6 kV while the current may reach 3 kA [8]. This should be secured with a proper TVS, mostly varistor, same as all safety margins for component ratings should be respected.

- **Electromagnetic compatibility:** As any other device, industrial PSUs must fulfill EMC standards. For auxiliary PSU radiated emission is not so significant as from primary PSU

or the machinery, but still shielding (e.g. Faraday screen) should be used as a protection against it. This device is presumed to be used in Europe, so I will focus only on standard EN 55011 [9]. As design for industrial usage is in many ways more challenging, this may be the first easier part: as long as the factory (or any other industrial sector) have mains and ground-point different from residential and office buildings, milder Class-A limits applies to each device (milder for both radiated and conductive EMI). If this condition is not fulfilled, device is classified as Class-B and limits – if defined – are same as for standard devices.

• Fusing, inrush limiting and protections: Fuses have to safely break the circuit in every situation. This refers to higher voltage rating and because industrial mains have lower impedance, to higher breaking current capability too. As PSUs usually have some sort of capacitor bank, inrush current limiting must be secured, especially for voltage as high as 1 kV<sub>DC</sub>. Protections depends on design specification, but output overload, input undervoltage and thermal are common for most of them.

SiC devices are usually used in industrial sector for high power application like motor control or already mentioned primary power supplies. Idea of this thesis is to analyze their usage in auxiliary power supplies, because in this field Si devices are still mostly used and according to specification, SiC might be better.

## 2 Flyback design

Converter designed in this thesis was developed in cooperation with STMicroelectronics as a prototype for testing SiC MOSFETs and as a potential evaluation board. Therefore, mostly ST semiconductors were used and tested. However, (as declared above) all designs, layouts and measurements were made by the author.

For evaluation purposes the board had to be easily modifiable, all parts accessible and versatile for another design ideas. Usage in industrial sector requires ultra-wide input range, besides fulfilling electromagnetic interference limits, even susceptibility must be particularly considered.

#### **Parameters:**

Input voltage:  $150 \text{ V}_{DC} - 1 \text{ kV}_{DC}$ ;  $180 - 690 \text{ V}_{AC}$

Output: 24 V<sub>DC</sub>; 100 W; reinforced isolation

Besides smaller prototypes and special testing boards, two PCB designs were made. Gerber data for both of them are attached – \Attachments\Boards\v1 and \v2. First one was used as beta version for EMI optimisation, also few minor problems were solved using this board. Second version is the final version and – as I believe – flawless. Unless noted otherwise, v1 PCB was used for measurements (especially all presented efficiency data – they might slightly differ because of minor changes in the input section).

Figure 4 Block diagram of designed converter

Figure 4 simply describes designed converter. It's standard flyback topology, primary designed and tested for fixed-frequency operation, but also – revealed in subchapter 0– quasi-resonant mode was tested. It consists of three main (mostly independent) voltage circuits. First one in order of appearance from input is Primary side's High Voltage section (further under the abbreviation HV). This does not refer to definition of high voltage mains ( $\geq 1~\rm kV_{AC}$  or 1.5 kV<sub>DC</sub>), but since the voltage potential to internal ground is usually times higher than in any other section (in this case almost 100times) there's a convention to call it *High Voltage*. It provides power distribution to the rest of the converter (except startup sequence) through main transformer.

Second circuit is Primary side's Low Voltage section (abbr. LV), from where the controller is powered and it also drives the power MOSFET. It's not isolated from HV (shares common ground) and during startup is directly powered from it via linear regulator (HV startup,

described in 2.3.1). Not so long after converter starts switching, auxiliary winding starts providing sufficient voltage and LV section is powered from it. The third circuit is the secondary side. This is the only stabilized voltage circuit (via feedback; abbr. FB) – input voltage is given and LV voltage is defined by auxiliary voltage (which consist of secondary winding voltage and transient voltage spikes) thus it can vary a lot. The secondary side is also isolated, so even the FB needs isolation, which is secured with standard optocoupler.

### 2.1 Brief review of Flyback operation

Flyback topology is one of the off-line converters category, mostly used for low-power applications up to 100 W. It is one-switch converter derived from buck-boost topology as its isolated version. Instead of other one-switch off-line converter – forward – it uses its *magnetic* for storing energy during on-time and discharging it to the output during off-time; forward uses magnetic as a transformer: during on-time primary voltage is transferred to the output according to Faraday's law, core flux is demagnetized during off-time. I wrote flyback *magnetic* instead of *transformer* intentionally: buck-boost uses an inductor to store energy and flyback does the very same thing, the only difference is another winding used for discharging this energy; it doesn't use Faraday's law (applied for transformers) for its primary purpose. Technically, as this component exists, flyback magnetic can be called *coupled inductor*, but I will use the standard term: flyback transformer (from any point of view except nomenclature there's no difference between them). What is more, while magnetic have more than one winding Faraday's law applies in every case, no matter if its use for energy transfer or not – so using term *flyback transformer* is definitely correct.

[21] [24]

Figure 5 Simplified flyback schematic

Just to clarify a few terms used in this thesis, this paragraph summarizes flyback function. Principle schematic is shown in Figure 5. On the primary side (left), switch (MOSFET) turns on and starts charging the transformer **core flux**  $\Phi$ , also the voltage applied to the winding  $V_{prim}$  is **reflected** according to Faraday's law with transformer **turn ratio n** to the secondary side as  $V_{sec\_R}$ . According to switch state, two parts of each cycle are defined: **on-time t**<sub>on</sub> and

off-time  $t_{off}$ ; together forms period  $T = t_{on} + t_{off} = 1/f_{SW}$ , where  $f_{SW}$  is switching frequency. During on-time, output diode D is reverse-biased, during off-time core flux is demagnetized through output diode into output capacitor C. Also part of off-time can be idle time  $t_{res}$ : this represents the rest of off-time after the core is fully demagnetized and before the start of next on-time. During demagnetization, secondary winding acts like a current source of  $i_{sec(t)}$ , which causes secondary winding voltage  $V_{sec}$  and its **reflection** to primary  $V_{prim\_R}$ .

### 2.2 Input section

Every component had to fulfill voltage rating. Starting with input connector, then fuse, inrush current limiting NTC's, capacitors, surge protecting varistor, common mode choke and bridge rectifier. Picking a proper fuse was quite tricky – as written above, it must withstand inrush current while 1 kV is connected, but also current breaking capability must be sufficient.

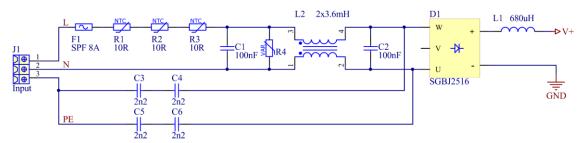

For evaluation purposes standard sized fuses (e.g. 5x20 mm) are the best option, unfortunately, none of those had  $1~kV_{DC}$  rating – besides voltage value, especially classification for breaking DC not so many of them have. As a compromise, 2A ultra-fast 6.3x32 mm fuse with combined holder also for 5x20 mm was tested and used in the v1 version, but failed. After that, the only acceptable fuse cartridge (used in v2) with 1~kV rating is industrial 10x38 mm. Fuse selected was Littelfuse SPF 8A: it fulfils  $1~kV_{DC}$  rating and its current breaking capability is 20~kA, which refers for  $1~kV_{DC}$  input to overall impedance of short circuit and mains equal or higher than  $50~m\Omega$ , which I firmly believe is safe enough. Figure 6 shows the input section (without input capacitor bank connected to nets V+ and GND).

Figure 6 Input section

For inrush current limiting NTCs R1-R3 and choke L1 are used (L1 is also used as differential mode choke for EMC optimisation). There are three NTCs because of the voltage rating:  $265\ V_{AC}$  for used EPCOS NTCs, which equals to amplitude of approx.  $375\ V_{DC}$ . For transient voltage suppressing varistor Littelfuse V1000LA160 was used with peak current rating 6,5 kA. EMI filter consist of C1-C6 and L2, this problematic is discussed in section 2.6. Instead of diodes 3-phase input bridge was selected to save space on the PCB, also it may be helpful for 3-phase adjustment.

Because input range starts at 180  $V_{AC}$ , from known parameters input capacitance was calculated  $\geq$ 40  $\mu F$  (for 50Hz mains). Considering PCB requirements, two 68  $\mu F$  / 400 V capacitors in parallel were put 3times in series, each pair is balanced with two 1206 SMD resistors in series (voltage rating of 1206 package is usually 200 or 250 V). Capacitor bank is shown in Figure 7 in section 2.3.1.

## 2.3 Chip selection

For versatility same as for high voltage the best option was the ST's L6566BH multimode controller. It allows both Fixed frequency (FF) and Quasi-resonant (QR) operation. Switching frequency during FF operation can be set by one resistor, same as maximum switching frequency for QR mode. It also includes many other features, like output overvoltage protection and input undervoltage protection useful for industrial power supplies.

[10]

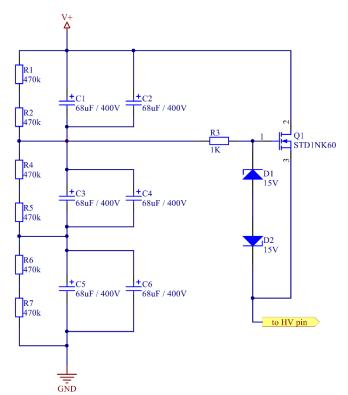

#### 2.3.1 High voltage startup

Although L6566BH's integrated high voltage startup allows 840 V as an absolute maximum rating, for this application it's still not enough. For this purpose, the circuit shown in Figure 7 was developed. Transistor Q1 acts as a simple voltage follower of voltage divided by input capacitors, approx.  $^2$ /3 of V+. While internal HV startup charging the VCC capacitor (I<sub>MAX</sub> 1.6 mA), the channel of Q1 is opened (Q1's threshold current is 250  $\mu$ A) and acts as typical voltage follower.

Figure 7 HV startup circuit

During off state HV pin voltage is biased only by leakage currents. Because those can variate by decades, it is necessary to protect both Q1 and HV pin by clamping Zener diodes D1 and D2.

Resistor R3 just fulfils the function of additional impedance in case of any voltage surges. It shouldn't affect any other function, only leakage currents may flow through, if any.

Technically, it is possible to connect HV pin directly between capacitors, but that's not fault-proof. It was tested, that if in case of some malfunction L6566BH's VCC is being continuously discharged and thus charged with HV pin, it unbalances the capacitors beyond safety limits. HV is not designed to

provide power continuously, but failure of

IC is still more acceptable than possible explosion of electrolytic capacitors.

[10] [11]

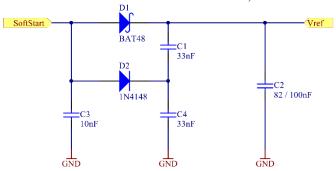

#### 2.3.2 Soft-start and OCP

L6566BH uses one capacitor (connected to SS pin) for both soft-start and overcurrent protection. While starting, this capacitor is charged from zero voltage with current

$i_{SS} = 20 \,\mu\text{A}$  (typ.). Once V<sub>SS</sub> reaches 2 V, soft-start ends. During this period, setpoint for primary winding current rises from zero to maximum.

After soft-start, voltage stays at 2 V until overcurrent appears. If it does, capacitor is charged again with current exactly one quarter of the soft-start current  $i_{SS}$ . If overcurrent lasts long enough that  $V_{SS}$  reaches 5 V, device stops switching. This allows covering the short-time overloading.

Even if this is quite handy feature for usual design, in this case it's not. During soft-start, L6566BH completely ignores COMP pin, to which feedback's optocoupler is connected. Also, while starting (output voltage is close to zero) converter operates in continuous-conduction mode. During on-time and for constant voltage, current through primary inductance can be described by following equation:

$$\frac{di_{(t)}}{dt} = \frac{v_{(t)}}{L} \to \Delta i_{Lprim} = V_{prim} \cdot \frac{t_{on}}{L_{prim}}$$

(1)

During off-time  $t_{off}$  the being core flux is demagnetized into output according to the same equation (1), only transferred to the output:  $t_{on} \rightarrow t_{off}$ ;  $prim \rightarrow sec$ . While starting output voltage is presumed equal 0 V, thus V in the equation represents just voltage drop on output diode and series resistances. (This is very simplified - e.g. no rise of the output voltage is counted in - but for demonstration purposes it's ok.) Hence even for short  $t_{on}$  during startup core flux might not be fully

Figure 8 CCM while starting (in: 150 V<sub>DC</sub>,; loaded) Yellow – V<sub>GS</sub> Blue - I<sub>D</sub>

demagnetized into output. To be exact, the continuous-conduction mode does not have to occur by definition, but it does because of the design parameters (demonstrated in Figure 8: in the middle is the 16<sup>th</sup> pulse and already in *quite deep*<sup>2</sup> CCM).

On-time  $t_{on}$  (to reach current setpoint) is inversely proportional to V, which is given by input voltage: for highest  $V_{IN}$  is the shortest, for lowest the longest. Considering FF operation, shorter on-time means longer off-time. Therefore, for higher input voltage a higher amount of core flux can demagnetized into output current during off-time. Because of that, output voltage reaches its nominal value faster. This also variates depending on load: for no load just output capacitors are charged and output voltage rises much faster. In every case must soft-start ends before nominal output voltage appears (most critical is 1 kV input and no-load), otherwise (because L6566BH ignores COMP pin), overvoltage occurs, which is no doubt insufficient condition.

To prevent this, it is obvious that soft-start time must be set for maximum input voltage and no load, therefore for other conditions overload state is triggered. This can last maximum

<sup>&</sup>lt;sup>2</sup> Quite deep according to ΔI<sub>prim</sub>/I<sub>prim\_avg</sub>

6times longer than soft-start (SS capacitor is charged from 2 to 5 V with quarter current). The most extreme conditions are 1 kV input and no-load (as mentioned above) and 150 V input and full-load.

In QR mode, instead of CCM during soft-start and DCM later, converter senses core demagnetization and then switches. Hence problem with soft-start is quite different, but still based on similar principle. To reach current setpoint,  $t_{on}$  is again inversely proportional to input voltage. Equation (1) for  $t_{on}$  is still valid, but with one difference: each period  $i_{Lprim}$  rises from zero to current setpoint. Nevertheless, for each current setpoint  $t_{off}$  is independent of input voltage. Off-time is defined by equation (2) where  $i_{Loff}$  is the actual value of primary winding current when transistor turns off and  $V_{sec}$  is voltage on secondary winding (actual output voltage + diode forward voltage drop) and n turns ratio.

$$t_{off} = \frac{\Delta i_{Lsec} \cdot L_{sec}}{V_{sec}} = \frac{n \cdot i_{Loff} \cdot \frac{L_{prim}}{n^2}}{V_{sec}} = \frac{i_{Loff} \cdot L_{prim}}{V_{sec} \cdot n}$$

(2)

While sensing the core demagnetization, it's for sure that  $\Delta i_{Lsec}$  drops down to zero, so it is correct to substitute  $\Delta i_{Lsec}$  with  $n \cdot i_{Loff}$  (considering ideal coupling). From equations (1) and (2) is obvious that not off-time but frequency changes. Besides this difference, soft-start problem for QR mode is the same: for higher input voltage and less or zero load output voltage rises faster.

As it eventuated from measurements and testing, soft-start capacitor could be designed for one exact board to cover all conditions, but because charging current  $i_{SS}$  can differ up to  $\pm 30\%$

Figure 9 Soft-start circuit

it's impossible to design one exact value with safe margins. In other words, one exact capacitor was found suitable for one exact board to cover both extremes, but with nearly no margin. Any variation even within capacitor tolerance may lead to malfunction. Utility designed to resolve the problem is demonstrated in Figure 9: this circuit allows to separate these two functions.

Capacitor C3 acts as usual soft-start capacitor and it's calculated to cover high input voltage and no-load cases. With fully loaded output and/or lower input voltage OCP is triggered. After reaching approx. 3.1 V (Vref/2 +  $U_{D2}$ ), soft start current starts charging divider consisting of C4 and C1. L6566BH's pin Vref is sink-source, so even if this current (5  $\mu$ A typ., 6.5  $\mu$ A max) would make any difference, it wouldn't matter. The function of D1 is described in the next paragraph. D2 is standard diode instead of Schottky diode for one simple reason: leakage current of ceramic capacitors C1 and C4 wouldn't balance the divider quick enough. While they are imbalanced after startup, any other short-durational overloading triggers immediately overload protection. To prevent this, balance resistors might be connected in parallel with capacitors, or D2 should be standard diode: as they have times higher reverse leakage current than Schottky diodes, capacitor divider is discharged back to balance.

D1 can be used to set preferable state: as described in L6566BH's datasheet [10] both overvoltage and overcurrent protections can lead to auto-restart or latch. If the protection is triggered, IC stops switching and waits until VCC falls below the turn-off threshold and proceeds to a new start-up sequence. In case auto-restart is enabled, then starts switching again, otherwise stays latched until it's restarted externally (disconnecting mains, discharging VCC to zero, etc.).

Auto-restart for OCP is enabled by clamping SS pin to less than 6.4 V (typ.), e.g. to  $V_{REF}$  pin which is implemented with D1 in Figure 9.

[10] [12]

### 2.4 Flyback transformer

Design of flyback transformer is good example of multiple-criteria problematic: core size, core magnetic, turns ratio, wire diameter, isolation, layers (interleaved or non-interleaved), also radiated EMI problematic may be included (shielding, start of winding, orientation). Professional flyback transformers are designed via software including all these parameters, but it can be also calculated and designed with good precision using only few equations.

In flyback design many components are bounded together, including transformer: from transformer parameters ratings for primary switch (i.e. Si / SiC MOSFET in this case) and output diode are defined. MOSFET maximum Drain-Source voltage and diode reverse voltage are defined with turns ratio. Turns ratio can define duty cycle, to which are bounded peak currents for both transistor and diode. To calculate the transformer, following parameters are necessary:

- **Switching frequency:** switching losses are proportional to switching frequency, but increase with the square of input voltage. Since input voltage is up to 1 kV, in order to minimizing them switching frequency was selected quite lower:  $\mathbf{f}_{SW} = 51.3 \text{ kHz}$

- Mode of operation: Discontinuous, Fixed-Frequency

- Input voltage: 150 V 1 kV

- Output: 24 V, 100 W

There are many approaches to calculate flyback transformer, often working with voltage related equations (e.g. [24]), but I prefer the approach from the current point of view. Many parameters have been neglected in order of simplicity and are discussed later. As first should be mentioned transformer coupling factor: until further notice, it's considered ideal, i.e. k = 1.

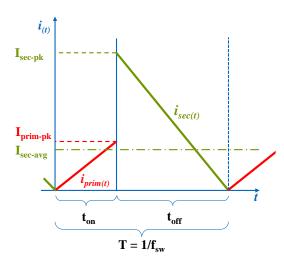

It is wise to set maximum power as a boundary condition to DCM, then parameters bounded with duty cycle can be defined easily. Considering linear permeability thus linear inductance, both primary and secondary winding currents have a triangular shape – Figure 10.

Figure 10 Currents in boundary DCM

#### 2.4.1 Transformer calculation with consideration to other components

Because of DCM, the output power can be determined as inductor energy per time, i.e. multiplied by switching frequency:

$$P_{sec} = \frac{1}{2} I_{sec-pk}^2 \cdot L_{sec} \cdot f_{sw} \tag{3}$$

$P_{sec}$  stands for power provided by secondary winding, i.e. output power  $P_{out}$  + all losses on the secondary side (mainly on output diode). While those losses are almost purely voltage drops and not leakage currents (current for feedback is neglected), output current  $I_{out}$  equals to secondary winding average current (substituting with eq. (1) and eq. (3)):

$$I_{sec-avg} = \frac{P_{sec}}{U_{sec}} = \frac{1}{2U_{sec}} I_{sec-pk}^{2} \cdot L_{sec} \cdot f_{sw} = \frac{1}{2U_{sec}} I_{sec-pk}^{2} \cdot \frac{t_{off} \cdot U_{sec}}{I_{sec-pk}} \cdot f_{sw} = \frac{1}{2U_{sec}} I_{sec-pk}^{2} \cdot \frac{t_{off} \cdot U_{sec}}{I_{sec-pk}} \cdot \frac{1}{T} = \frac{1}{2} \cdot \frac{t_{off}}{T} \cdot I_{sec-pk}$$

$$(4)$$

It is obvious from Figure 10 that  $I_{sec-avg}$  because of a triangular shape is equal to  $\frac{1}{2}$  of  $I_{sec-pk}$  during  $t_{off}$  and  $t_{off}$ /T is just averaging over the whole period. Since core flux is caused by current through primary winding,  $I_{prim}$  and  $I_{sec}$  are proportional with turns ratio (N means number of turns):

$$I_{sec-pk} = n \cdot I_{prim-pk}; \ n = \frac{N_{prim}}{N_{sec}}$$

(5)

and as magnetic flux unit Weber can be written as  $V\cdot s$ , duty cycle D can be calculated as:

$$D = \frac{t_{on}}{T} = \frac{n \cdot V_{sec}}{n \cdot V_{sec} + V_{in}} \tag{6}$$

All equations above presumed ideal state and only output diode losses were included. Now from required output parameters output current Isec can be calculated according to (4). It is wise to include all losses (estimated or calculated) and add them with some power margin (e.g. 10%) to  $P_{sec}$ : in case that the converter is loaded during startup with nominal load, due to low output voltage core can't be properly demagnetized and converter couldn't start. Also power consumption from any other winding (auxiliary in this case) must be included. Setting this increased  $P_{sec}$  to boundary condition of DCM requires one more parameter: the input voltage for equation (1). This should be set for minimum operating voltage, therefore for any higher voltage on-time for current setpoint shortens, so operation in DCM is guaranteed.

All these parameters are bounded with duty cycle and/or turns ratio; the best way to select them is with series of iterations. Also reflected voltages are bounded with them, therefore in this part of transformer design it is good to focus on primary side MOSFET and output diode too. Current relations are defined in equations above; maximum diode voltage  $V_D$  is:

$$V_D = V_{sec-R(max)} + V_{out} = \frac{V_{in(max)}}{n} + V_{out}$$

(7)

For MOSFET voltage rating it's necessary to include transformer leakage inductance (coupling factor k < I). This is caused by non-ideal coupling between primary and secondary winding, from circuit point of view it's correct to include it as another inductance put in series with primary inductance. It means that it's charged with primary inductance, but not discharged into output, therefore it must be discharged in different way. There are two common options – called snubber – to secure this, first is parallel RC combination, second is transil; both with diode in series to dissipate only the energy from leakage inductance. Transformer is usually designed to have leakage inductance in range 1.5 - 3%, so discharging leakage inductance in short time is presumed. In first circuit, the energy is mostly transferred to the capacitor and in the rest of off-time dissipated on the resistor. The disadvantage is – besides sometimes worse efficiency – that leakage inductance can slightly vary, thus can its energy and so the maximum capacitor voltage: maximum snubber voltage can be only estimated, not defined. Second option – transil – defines

the maximum snubber voltage nearly independent of dissipated current. Because this design often nears to the limits of safe operation, this is quite necessary. Transil should be selected for: a) safely discharging leakage inductance; b) having as small as possible leakage current with applied  $V_{\text{prim-R}}$  (for efficiency reason). Overall MOSFET voltage is  $V_{\text{in(max)}} + V_{\text{snubber}}$ .

Voltage reflected on primary winding  $(V_{\text{prim-R}})$  during demagnetizing through secondary is proportional to turns ratio:

$$V_{prim-R} = n \cdot V_{sec} \tag{8}$$

It is obvious that some compromise must be done: there is an effort to lower maximum rated voltage for both components (for lower price and better parameters), but for diode it means maximizing turns ratio (eq. (7)), but for MOSFET the opposite (eq. (8)). For the same reason it is wise to minimize effective / average currents though them – and this also refers to the exact opposite rule of turns ratio for both of them (eq. (5)).

In design like this, where output diode power dissipation is not negligible, component selection tends to Schottky output diode instead of standard one. In general, Schottky diodes have absolute maximum reverse voltage 200 V or lower, for operation conditions (i.e. ~80% of AMR) 160 V. This actually makes design slightly easier: one parameter is defined and iterations to select the best duty cycle or turns ratio have one value to relate to. From this parameter and defined parameters equation (7) can be calculated: turns ratio n = 7,35, which means that  $n \ge 7,35$  have to be used for Schottky diode. All other parameters mentioned above can now either be calculated or are already defined.

#### 2.4.2 Core, bobbin and wire selection

As parameters written above were all bounded together, core, bobbin and used wires are bounded similarly. Since primary inductance and its current is defined, the only core limit is maximum magnetic flux density  $^3$   $B_{max}$ . As written in the beginning of this subchapter, linear permeability was considered for all calculations. To obtain this, core magnetic flux density B must be lower than  $B_{sat}$ . More precisely, permeability is dependent on B (so is inductance), but for B nearing  $B_{sat}$ , permeability starts decreasing rapidly (depends on used core material). This is called core saturation and  $B_{sat}$  is usually defined for 10% or 30% inductance / permeability loss. Including real-world parameters makes situation more complicated. Each core size defines bobbin on which wires are wounded. To minimize losses, wire must have some thickness and from calculations defined number of turns: it may easily happen that the windings simply didn't fit into the bobbin. Same as in previous part, a few iterations are needed to find the best solution.

Before focusing on wires, it's necessary to calculate magnetic flux density to see if selected core can be used (or – if feasible – it needs iterations for ideal air gap). Just a reminder, equations and relations presented here are just simplifications – more or less – valid for flyback transformer design; overall magnetic relations are more complex. First, leakage inductance is neglected again, so inductor linkage flux<sup>4</sup> is presumed equal to:  $\Psi = N \cdot \Phi$ ; even if this is not matter-of-fact [21]. Using this, inductance can be defined from core parameters as shown in equation (9) (A is core cross-section area, l is core effective length and  $\mu$  is core permeability):

$$L = N^2 \cdot \mu \cdot \frac{A}{I}; L = N^2 \cdot A_l \tag{9}$$

The right part of equation (9) is just it's modification (used also in this design) where  $A_l$  is inductance factor. The un-modified equation includes permeability, which can be seen as

<sup>&</sup>lt;sup>3</sup> This is also called just *B-field* [24], I would rather stick to more precise name magnetic flux density [20]

<sup>&</sup>lt;sup>4</sup> Also marked as λ sometimes

function of temperature or magnetic field strength (H), thus inductor current: if any simulator is used for the design, this allows to calculate inductance more precisely for magnetic flux density nearing to  $B_{max}$ . If core with air gap is used (bellow is mentioned why it's purposeful for flyback), this equation is still valid, only it's easier to calculate using reluctance. Nevertheless, it leads to cross section of the air gap.

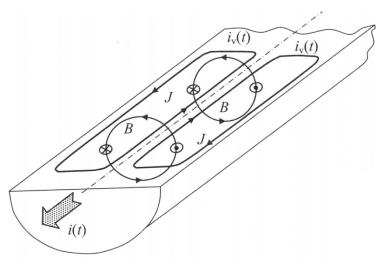

Figure 11 Magnetic field vectors in air gap; credit: [25]

One of many estimations made – and yet not named – is considering core permeability much higher than air permeability, so the magnetic can be described as *discrete* circuit: that means magnetic field is limited by core dimensions, thus all vector loops are inside the core. This can't be used for any air magnetic circuit (including air gap), because it has no borders. In Figure 11 is demonstrated how magnetic field vectors can change depending on winding distance. In this case modified or non-modified version of equation (9) can be used: inductance factor ( $A_l$ ) is defined by manufacturer for each air gap. It is also possible to estimate or calculate air gap reluctance, but in neither case can inductance be calculated just as function of current (just from permeability function): with permeability loss also both of these parameters change.

Two previous paragraphs outline one of many phenomena of flyback transformer design. As far as I'm familiar with this problematic or as it can be found in the listed literature in Bibliography & Sources, there are only two ways of design: using same or similar equations as I present in this thesis (including more or less parameters and estimating the effect of the rest), or design aided by simulation tools, mostly of magnetic behavior. Therefore: in this case phenomena like mentioned above can be taken into consideration, but not precisely calculated. Estimating discrete magnetic again, core flux density is given by following equation:

$$B = \frac{L \cdot I}{N \cdot A} \tag{10}$$

where A is effective core cross-section area. If equation (9) is substituted into (10), it can be demonstrated why it's useful to choose core with air gap:

$$B = \frac{L \cdot I}{N \cdot A} = \frac{N^2 \cdot A_l \cdot I}{N \cdot A} = \frac{N \cdot A_l \cdot I}{A}$$

(11)

Since inductance and current are defined from section 2.4.1, core air gap can be set for minimum core flux density. As B is proportional to number of turns, inductance increases with  $N^2$  so preferred value can be set. Back to the bounded parameters idea: minimizing B is good because of lower hysteretic losses and it also provides capacity for potential overloading, but more turns means longer wire, thus bigger parasitic resistance.

Not only wire length must be included into winding losses - skin effect (current displacing to the wire surface due to eddy currents; principle shown in Figure 12) can be a major issue. Proper calculation includes Kelvin's equation, which is Bessel function of a complex argument. Whole calculation is possible only directly from Maxwell's equations and not necessary for demonstration of the problematic [21]. The limit

Figure 12 Skin effect in round wire; credit: [21]

state for wire gauge is considered as  $\delta = d/2$ ; where d is wire diameter and  $\delta$  is skin depth defined as:

$$\delta = \sqrt{\frac{2\rho}{\omega \cdot \mu}} \tag{12}$$

modified to the limit frequency:

$$f_{max} = \frac{4\rho}{\pi \cdot \mu \cdot d^2} \tag{13}$$

where  $\rho$  is resistivity of used wire and  $\mu$  its permeability ( $\mu_{Cu} \approx \mu_0$ ).

This might be critical especially for secondary winding: as illustrated in Figure 10, high di/dt ratio is expected as primary-side MOSFET switches off. According to Fourier's series, higher harmonics are generated to achieve this shape. As secondary winding peak current may rise up to tens of amperes in this case, skin effect could negatively affect efficiency. It's recommended to choose wire diameter with  $f_{max}$  at least 10times higher than fundamental harmonic, which period is  $2 \cdot t_{off}$ . As  $f_{max}$  is inversely proportional to  $d^2$ , selecting proper gauge makes a big difference:  $f_{max}$  is approx. 17 kHz for d = 1 mm, but over 1,7 MHz for d = 0,1 mm (copper wire, resistivity  $\rho = 1,75 \, \mu\Omega \cdot \text{cm}$ ).

Wire selection includes proper insulation. For basic isolation using insulating tape between windings is often sufficient as winding-to-winding insulation; distance between wires and any other conductor (another wire, ferrite core) must be fulfilled also. In this case standard double-coated wire can be used, but for reinforced isolation it is necessary to use triple insulated wire (TIW) at least for one side. Additional isolation layer worsens the insulation factor:

$$k_i = \frac{d_{Cu}^2}{d^2} \tag{14}$$

where  $d_{Cu}$  is the conductor diameter (copper) and d whole wire diameter. TIW wire requires more space in bobbin than standard wire and also increases leakage inductance: as there is space between turns (exactly  $l_{space} = d - d_{Cu}$ ) magnetic field around wire can enclose the loop in this space which worsens the coupling with core.

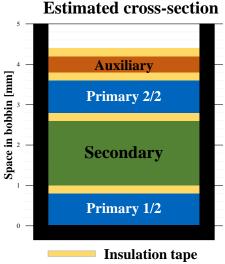

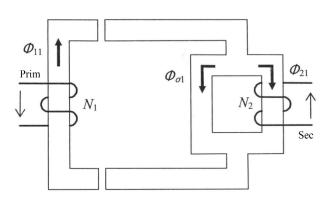

Referring back to Figure 11 and to the previous paragraph (reinforced isolation is required), in designed transformer two main things worsen leakage inductance (besides air gap effect): using TIW and position of winding. Position effect can be reduced by interleaving the layers: half of primary – secondary – the rest of primary instead of stacking secondary over primary can make a difference. As in one-switch flyback topology leakage inductance energy is just dissipated, lowering it improves efficiency. This also includes another disadvantage: primary-to-secondary capacitance caused by transformer is nearly doubled. Besides of minor negative effect on efficiency, this might cause trouble for EMI; further discussed in subchapter 2.6.

[19] [20] [21] [24] [25]

#### 2.4.3 Designed transformer

Output power 100 W is in general maximum power reasonable for one-switch flyback topology: as leakage inductance (typically  $\sim$ 3%) energy is only dissipated, another topology is adequate. To improve efficiency, interleaved transformer design was selected. For lower skin effect primary winding is wounded two times with thinner wire and secondary winding with litz: cable tangled from 100  $\mu$ m wires. All specifications are below:

#### Core:

Material: CF138 Type: ETD34 Gap: 1,1 mm $A_i$ : 143 nH

**Primary:**

$L_P$ : 585,7 µH

Turns: 64

Wire: 2x TIW 0,2 mm

**Secondary:**

$L_S$ : 9,15  $\mu$ H

Turns: 8

Wire: 6x Litz 40x 0,1 mm

**Auxiliary:**

$L_P$ : 3,58 µH

Turns: 5

Wire: 1x TIW 0,1 mm

Figure 13 Winding layers

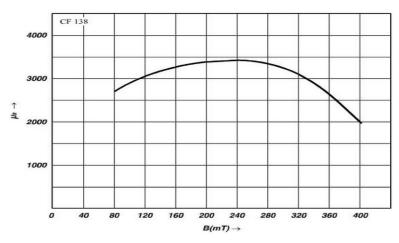

For minimum input voltage and from specification duty cycle D = 56,9% was calculated, primary winding peak current  $I_{prim-pk} = 2,84 A$ , thus maximum magnetic flux density  $B_{max} = 268 \, mT$ . For ETD34 is cross-section area  $A = 97,1 \, mm^2$  [26], but this number is the best achievable option: in case there is little offset between two halves of core this area decreases. For correction factor  $0,9 \, B_{max}$

Figure 14 CF138 permeability vs magnetic flux density; credit: [26]

grows up to approx. 300 mT. As illustrated in Figure 14, this is the maximum reasonable core flux density – as both permeability and  $B_{max}$  are dependent on temperature, there must be some

margin left. Output diode voltage drop was taken from datasheet [18] as 0,8 V, thus output current  $I_{sec} = 4,89 A$  for secondary winding peak current  $I_{sec-pk} = 22,7 A$ . As output power is defined 100 W, margin for losses and startup is 17,4 W (or %), which should be enough.

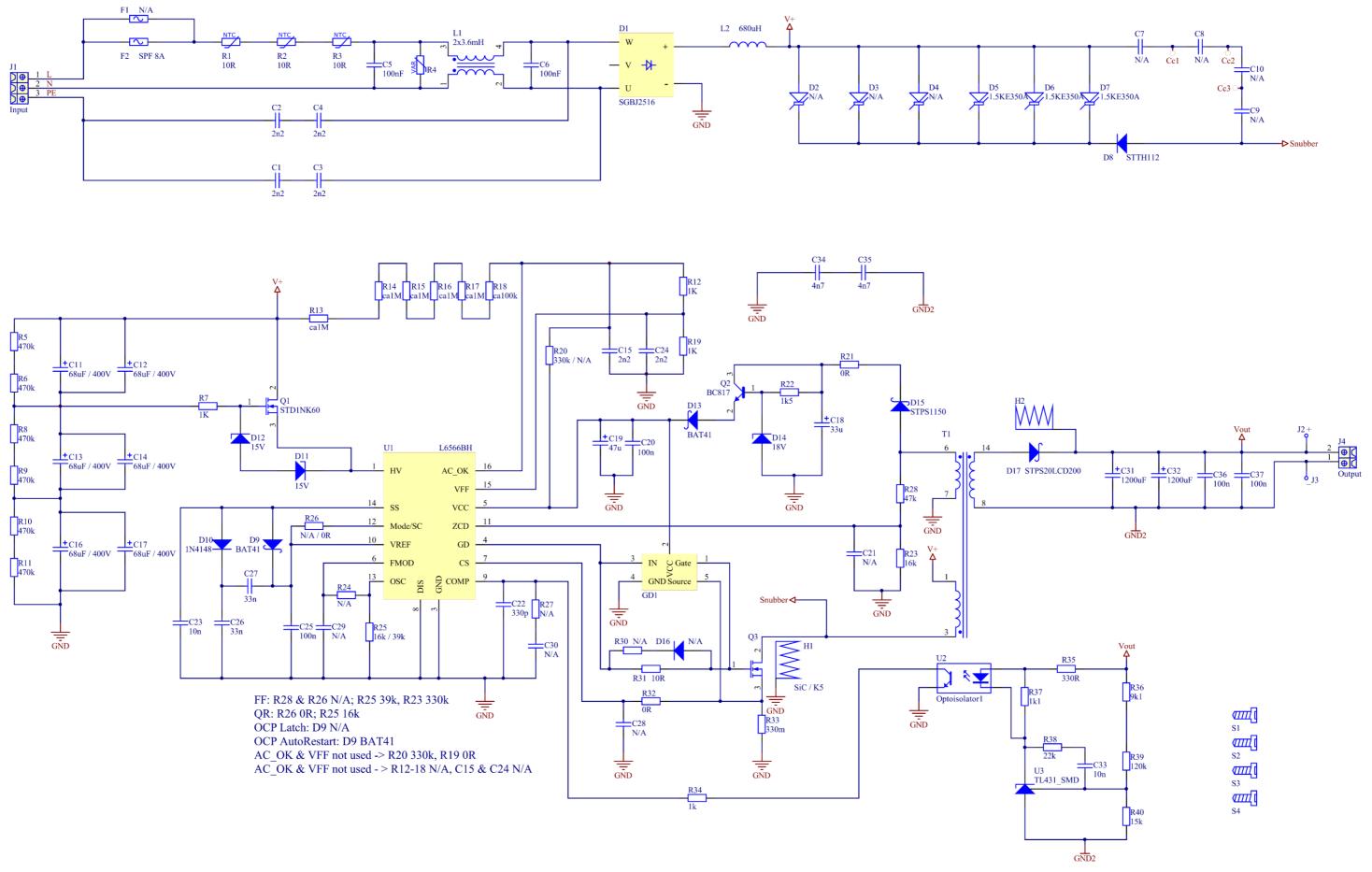

### 2.5 Final schematic and PCB layout

Final schematic is shown on the next page in Figure 16 or is located in  $\Delta tachments Boards 1$  and v2. This is the schematic for v2 board, the only difference from v1 is soft start circuit (discussed above in 2.3.2), first version had only SS capacitor. Also input section is slightly different: v2 was modified for final EMI components. As design was made for universal use and modifiability, many components are marked with N/A – not assembled. Photography of both boards is in Figure 15 – nearly the same schematic, layout slightly improved, very similar look.

Figure 15 Board v1 in the front with connected Gate-Drive module (revealed later in subchapter 3.2) and board v2 in the behind already with better fuse and final EMI components

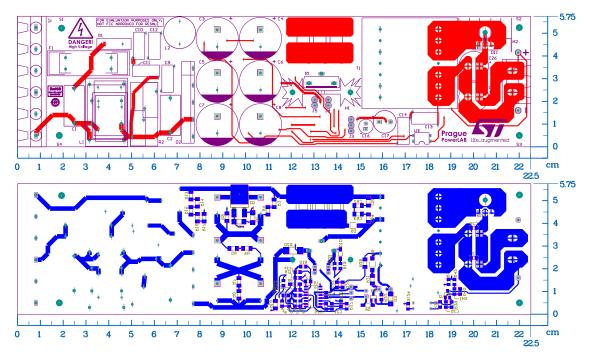

Figure 16 Final schematic of flyback converter

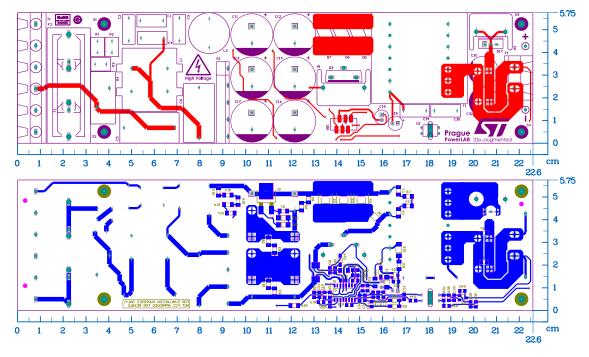

Both PCBs for v1 and v2 were routed in accordance with basic analog design rules, Primary side's LV ground is star-topology, the rest of design tends to daisy-chain topology according to the schematic (this is important especially for blocking capacitors). Primary side's LV and HV ground are connected together on the pad of the current sensing resistor for most precise current sensing. Special consideration was given to clearance according to applied voltage: input stage was routed with reinforces clearance and creepage, the rest with functional; between primary and secondary side both were optimized as wide as possible (on v2 board there is even a slot hole under optocoupler). All PCB GERBERs are located in \Attachments\Boards\v1 and \v2.

Figure 17 PCB layout for v1 - TOP layers are on the top, BOT on the bottom (not mirrored)

Figure 18 PCB layout for v2 - TOP layers are on the top, BOT on the bottom (not mirrored)

### 2.6 EMI optimization

This converter was designed for industrial usage; therefore, it must fulfill CISPR's EN 55011 standard [9]. As this converter creates radio-frequency interference as its side effect, it belongs to category 1. This category is further divided into classes A and B according to mains star point: if any residential or office building is connected to the same star point, Class-B limits must be fulfilled (which are same as for any other home or office device), otherwise Class-A limits applies (which allows to radiate higher values). As this is not defined by converter specification (and also for versatility purposes) design was optimized for rigorous Class-B limits. The design is only an evaluation board of auxiliary power supply: for non-laboratory usage (possible scenario after evaluating, testing and certification) it will be probably mounted together with another machinery parts in metal enclosure. Therefore, all EMI measurements focuses only for conductive, not for radiated EMI. Whole problematic was fine-tuned on v1 board, v2 board has final footprints for components listed below and in Bill of Materials.

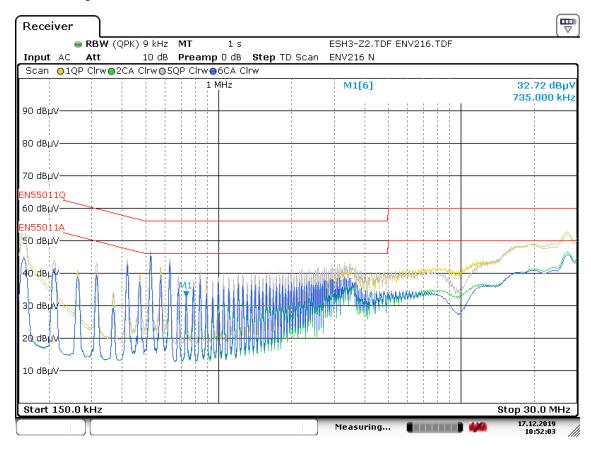

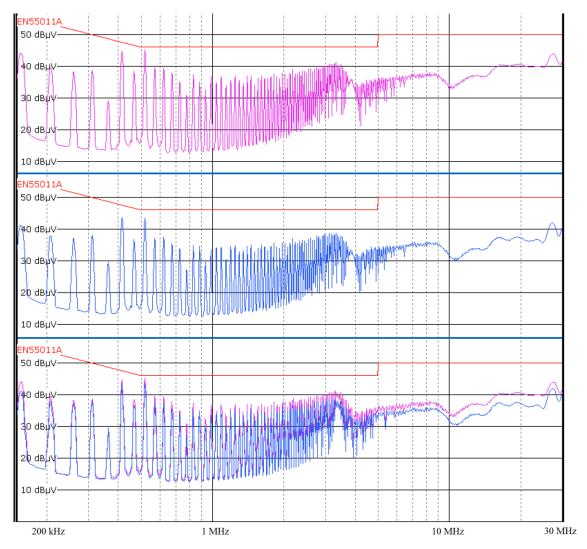

As shown in Figure 6 or in Figure 16, input section contains components for standard EMI filter topology. Capacitors C1-C4 are safety Y1 capacitors; because C5 and C6 are already fused, there's no necessity for class X safety rating. As common mode choke one of Coilcraft's 3750 Vrms was selected, again to fulfill voltage rating. Several chokes were tested, the best performance was made with E3502 combined with C5 and C6 both 100 nF. After proper component selection, conductive EMI was measured for input voltage 230  $V_{AC}$  and 100W load, shown in Figure 19:

Figure 19 Conductive EMI measurement; Yellow: Quasi-peak L, Green: Average L, Gray: Quasi-peak N, Blue: Average N

#### 2.6.1 Further improvements

As revealed in Figure 19, the design meets the EN 55011 EMI standard. It is also true that the margin to the limits for frequencies 500-650 kHz is not as extensive as preferable. Due to component tolerance and/or their aging (e.g. capacity loss for electrolytic capacitors) sooner or later the limits might be exceeded. Therefore, several ideas were tested for the possible third version, if solution on v2 would be found insufficient.

The first step was PCB design: this is the only cost-free option (besides testing same-cost components from different manufacturers). As mentioned above, the input section on the first v1 board was made for testing purpose, so universal or not big enough footprints were used. Furthermore, routing was made – as I firmly believe – properly. Therefore, I presume (and as written bellow based on measurement) that different input section routing on boards v1 and v2 have no effect at all on conductive EMI.

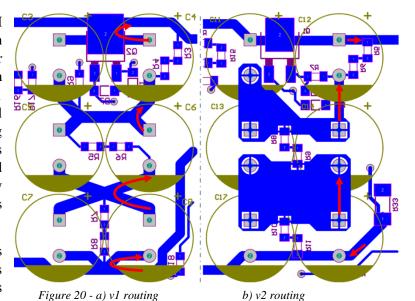

Additionally – what I believed that might have an effect – was input capacitor bank routing. As shown in

Figure 20 – a), v1 was routed for optimal decomposition of switching current ripple stress. This topology allows to load capacitors in parallel nearly equally (this topic is discussed in [23]).

However, this adds parasitic inductances in series with capacitors and (what's worse) parasitic inductance

between supply rails (V+, GND) and capacitor bank (estimated current flow is sketched with red arrows in Figure 20 Figure 20). That makes direct path for ripple from primary switch (on the

arrows in Figure 20 Figure 20). That makes direct path for ripple from primary switch (on the right side) to the input section (on the left side) and capacitor bank is connected via branch. This effect shouldn't apply at all for switching frequency 51.3 kHz, but may negatively affect the EMI results for frequencies 500-650 kHz.

To confirm that, second board v2 was designed to minimize areas of parasitic inductances placing capacitor's pins directly into supply rails and connecting them with polygons instead of X- or H-shaped routes. Again, as demonstrated in Figure 20-b) with red arrows, the ripple should be directly eliminated with the right side triple-series capacitors (as much as their parasitic inductance and resistance allows it) and then the rest with others on the left. This also causes undesirable disparity of stress on the first and second triplet, but mainly on higher frequencies and on switching frequency 51,3 kHz it should be negligible.

As the main problem seems to be the average and not the quasi-peak value, a further comparison is focused only on the average value. Also as traces for L and N are nearly the same for lower frequencies, only L are shown for better clarity.

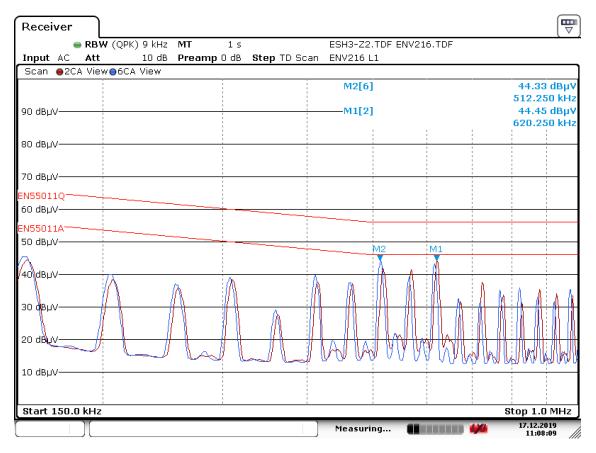

Figure 21 PCBs EMI comparison: v1 – dark red (marker M1), v2 – blue (marker M2)

New PCB layout made some difference, but instead of suppressing the problem it only transfers it to another frequency spike. As the amplitudes are almost identical (markers in Figure 21), the age-related question remains. Besides this effect v2 version has some differences on frequencies above 1 MHz, but as they are deeply below the limit, Figure 21 shows only range of interest.

After different layout didn't make huge difference, another focus was then on capacitor bank: quite common phenomenon of electrolytic capacitors is their low resonant frequency value, after which they show inductance behavior – impedance increases with frequency ([23]). This can be obtained by bypassing them with ceramic capacitors (typically 100 nF), because their resonant frequency is usually higher by orders. Unfortunately, used capacitors (Würth Elektronik 860241381006) have no simulation model or measured resonant frequency in their datasheet to verify this theory. Additionally, it was disproved with measurement – for frequencies around 1 MHz was approx. 1dB drop, but no difference in band 500-650 kHz.

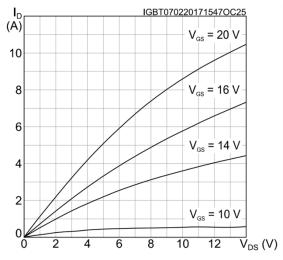

Figure 22 Additional comparison: Top - standard capacitor bank; Middle - triple capacitor bank; Bottom - both

Even if this was not sufficient improvement, it proves one thing: used electrolytic capacitors have in this band still low impedance. To see their effect, another triplet of capacitors in series was added – results are demonstrated in Figure 22: on the top standard v2 board (average L); in the middle v2 with three triplets of capacitors in series; on the bottom both together. In the observed band spikes drop about approx. 2-3 dB, which is quite good result: considering simple impedance divider, lowering the impedance to  $\frac{2}{3}$  gives drop -3,52 dB. Also, if the component aging worsens conductive EMI above limits, adding another capacitor triplet could solve the problem.

As was mentioned in 2.4.2 interleaving primary and secondary layers in transformer may worsen EMI, this is in my opinion the result. Before EMC optimization, capacitors C34 and C35 (used for bypass of primary and secondary grounds) were 2.2 nF. The results were horrible and increasing their values to 4.7 nF made a huge improvement. Their purpose is to lower the effect of transformer primary-to-secondary capacitance. Therefore, I presume the problem is the interleaving. Higher value might help, but then the design probably wouldn't meet requirements for safety isolation mains-to-output (sometimes titled *Line Leakage*). There is usually the limit 210  $\mu$ A; for maximum AC voltage 690 V and frequency 100 Hz (50 Hz after rectification) current through C34 and C35 is already approx. 102  $\mu$ A. Leakage current wasn't measured, but considering leakage currents through transformer isolation, converter might be near the limit even with this values.

## 3 Analysis of SiC driving and switching

## 3.1 Problematics of driving SiC MOSFET

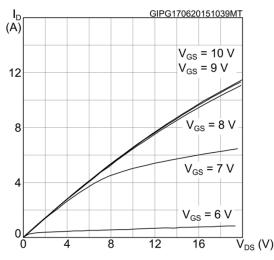

Currently, typical power MOSFETs for switching applications can be driven with 10V Gate-Source square wave. Even if 10~V for  $V_{GS}$  is often enough, they can withstand much higher voltage. Most of the standard power converter's ICs for use with external MOSFET are designed for these conditions. Driving SiC MOSFET may be slightly difficult, especially with one of these ICs. This whole problem is described below in this subchapter.

Figure 23 - a) STW12N150K5 output characteristics

b) SCT1000N170 output characteristics; credit [8][9]

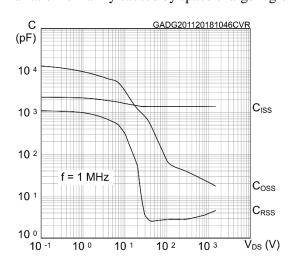

For switching purposes, operation in resistive region is the only acceptable mode during on-time. As mentioned, for most MOSFETs – e.g. for the measured one STW12N150K5 – 10 V of  $V_{GS}$  is enough to reach resistive region for any rated current. As it's obvious from output characteristics in Figure 23 slightly lower voltage shouldn't be a big problem either - curves for  $V_{GS}$  9 V and 10 V are nearly identical and the one for 8 V is still very similar. Opposed to Si, SiC MOSFETs are more sensitive to Gate-Source voltage (Figure 23 - b). This makes their switching more difficult: double value of  $V_{GS}$  is required same as it's precise value – 20% decrease (which is quite common tolerance) makes an unpleasant growth of on-time resistance – traces for  $V_{GS}$  20 V vs 16 V.

Besides output characteristics, another parameter of Gate-Source voltage must be taken into consideration. The absolute maximum rating of STW12N150K5's  $V_{GS}$  is  $\pm$  30 V, which is 3times more than ideal switching voltage. In case of any inappropriate handling or any voltage surges Gate is protected with clamping Zener diodes. The situation with SCT1000N170 is quite more complex:  $V_{GS}$  AMR is just + 25 V and – 10 V. With ideal On-time  $V_{GS}$  = 20 V there is not much headroom to AMR, exactly 25% (opposed to 200% of Si's MOSFET).

In general, ICs with external MOSFET use  $V_{GS}$  driving range approx. 10 V and higher. IC used in measured design of this diploma thesis (L6566BH) has its high-level range clamped to 15 V. Since it has no Gate voltage booster, minimum high-level voltage can be slightly lower than minimum operating voltage, which can decrease to 7.2 V. This may happen only for light-load, so Drain current limit will be the lowest possible and no damage threatens the MOSFET.

[13] [14] [19]

### 3.2 Design of Gate-Drive module

All circumstances described above require a complex solution of driving SiC MOSFET. The driving circuit must provide stable voltage with exact amplitude 18-20 V and no more: the absolute maximum rating of  $V_{GS}$  is not allowed for permanent operating condition; margin approx. 20% is recommended, hence maximum operating  $V_{GS} = 20$  V. This must be guaranteed even for the very first pulse after start-up.

Of course, simplicity and reliability are significant parameters, but low power consumption is very important: while starting, whole low-voltage section of primary side is powered from pre-charged VCC capacitor. Before auxiliary winding starts providing power, whole system must work properly and with low power consumption, so there's enough energy in the capacitor to span the delay.

It's obvious that some form of voltage booster will be necessary. Many of ICs use sort of charge pump with bootstrap capacitor, but this was evaluated as unsuitable solution. First, charge pump design for this application with discrete components (no suitable IC was found) might be considered as not as simple as required. More importantly, if the bootstrap capacitor gets discharged – e.g. in case of some malfunction – SiC transistor may operate in saturation region, which will be (most probably) destructive.

#### 3.2.1 Design topology and schematic

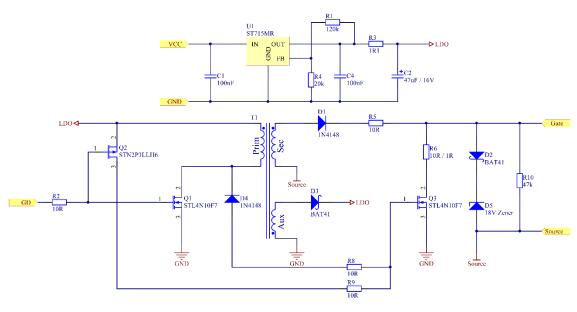

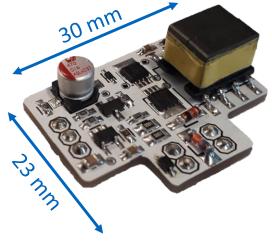

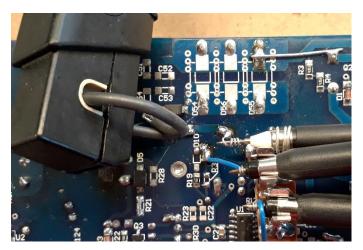

Instead of charge pump, transformer voltage booster shown in Figure 24 was designed. Whole concept was developed as simple Gate-Drive module which can be connected to the main PCB. With this solution it's easy to convert the board from driving Si MOSFET to driving SiC: just one resistor is soldered out (R31 in schematic) and GD module is connected. This is useful for valid comparison between Si and SiC MOSFETs: the very same components are used for different measurements, so any deviation from nominal value (which may affect the measurement) wouldn't differ.

Figure 24 Gate-Drive module schematic

Voltage stabilization is provided by linear voltage regulator U1 and the transformer's turns ratio. The LDO's bus voltage was set to  $8.75~\rm V$ : as for operating conditions L6566BH needs at least  $9.4~\rm V_{VCC}$ , the bus should be stable even near UVLO. Purpose of R3 is to increase the impedance of C2, so no problems with stability of U1 caused by driving capacitive load should occur.

During on-time, circuit can be described as forward converter: Q1 is switched on and voltage approx.  $V_{LDO}$  is applied on the primary winding. This voltage is transformed to the secondary winding according to Faraday's law:

$$V_{prim} = N_{prim} \cdot \frac{\mathrm{d}\Phi}{\mathrm{d}t}; V_{sec} = N_{sec} \cdot \frac{\mathrm{d}\Phi}{\mathrm{d}t} \rightarrow V_{sec} = V_{prim} \frac{N_{sec}}{N_{prim}}$$

(15)

Dots mark the winding's start and all windings are placed over each other with the same sense of rotation, thus core flux and voltage have the same polarity. Transformer T1 is considered ideal, so primary and secondary winding flux is the same. No-gap core was used for maximum inductance, so leakage flux is negligible. V<sub>sec</sub> is applied through D1 and R5 to the Gate of the SiC MOSFET. As V<sub>GS</sub> must be at the exact value, the end of the secondary winding is connected directly to the Source. D2 and D5 are protective clamp diodes against rising edge spikes caused by resonance between winding's inductance and parasitic capacitance.