# **Czech Technical University in Prague**

# **Faculty of Electrical Engineering**

**Department of Microelectronics**

## Master's thesis

**Design of an RC Oscillator for Automotive Applications**

**Author:** Bogdan Miasoiedov

**Supervisor:** prof. Ing. Miroslav Husák, CSc. **2019**

### ZADÁNÍ DIPLOMOVÉ PRÁCE

#### I. OSOBNÍ A STUDIJNÍ ÚDAJE

Příjmení:

Miasoiedov

Jméno: Bogdan

Osobní číslo: 439644

Fakulta/ústav:

Fakulta elektrotechnická

Zadávající katedra/ústav: Katedra mikroelektroniky

Studijní program: Elektronika a komunikace

Studijní obor:

Elektronika

#### II. ÚDAJE K DIPLOMOVÉ PRÁCI

Název diplomové práce:

Návrh RC oscilátoru pro automobilové aplikace

Název diplomové práce anglicky:

#### Design of an RC Oscillator for Automotive Applications

Pokyny pro vypracování:

- 1. Proveďte rozbor stávajícího stavu řešení obvodů RC oscilátorů pro automobilové senzorové aplikace, v přehledu se zaměřte na výhody a nevýhody, pro další řešení vyberte vhodnou architekturu obvodu.

- 2. Navrhněte obvod RC oscilátoru v technologii I4TÉ společnosti ON Semiconductor. Pro návrh využijte standardní postupy, tj. analýzu, simulace a eventuálně návrh layoutu. Základní požadované parametry pro návrh obvodu jsou: stabilita frekvence +/- 2 % v celém teplotním rozsahu od -40 oC do 175 oC, malá proudová spotřeba, dobrá fázová stabilita, možnost přesného nastavení frekvence oscilací, aby bylo možné kompenzovat vliv výrobního rozptylu parametrů součástek. Návrh a simulace proveďte v prostředí Cadence s použitím Spectre simulátoru.

- 3. Vyhodnoť te dosažené parametry navrženého obvodu a shrňte základní poznatky dosažené při návrhu.

Seznam doporučené literatury:

- 1. Neumann, P., Uhlíř, J.: Elektronické obvody a funkční bloky (I, II), ČVUT 2001

- MARTIN K. JOHNS A.D: "Analog Integrated Circuit Design", New York Wiley-& Sons Inc. 1997.

LAKER K., SANSEN W.: "Design of Analog Integrated Circuits and Systems", New York, McGraw Hill 1994.

- 4. GREGORIAN R., THEMES G.: "Analog MOS Integrated Circuits For Signal Processing", New York Wiley-Interscience

Jméno a pracoviště vedoucí(ho) diplomové práce:

prof. Ing. Miroslav Husák, CSc., katedra mikroelektroniky FEL

Jméno a pracoviště druhé(ho) vedoucí(ho) nebo konzultanta(ky) diplomové práce:

Datum zadání diplomové práce: 28.01.2019

Termín odevzdání diplomové práce:

Platnost zadání djplomové práce: 20.09.2020

prof, Ing. Pavel Ripka, CSc.

prof. Ing. Miroslav Husák, CSc.

podpis vedoucí(ho) práci

#### III. PŘEVZETÍ ZADÁNÍ

Diplomant bere na vědomí, že je povinen vypracovat diplomovou práci samostatně, bez cizí pomoci, s výjimkou poskytnutých konzultací. Seznam použité literatury, jiných pramenů a jmen konzultantů je třeba uvést v diplomové práci.

23.05.2019

Datum převzetí zadání

Podois studenta

### Declaration

| used in  | formation sources in accordance with the Methodological Guidance on Co | mpliance with Ethical |

|----------|------------------------------------------------------------------------|-----------------------|

| Principl | les in the Preparation of University Final Thesis.                     |                       |

| •        | ,                                                                      |                       |

|          |                                                                        |                       |

| Date:    |                                                                        |                       |

|          |                                                                        | Bogdan Miasoiedov     |

I declare that I have elaborated the presented thesis independently and that I have provided all the

#### Abstract

The thesis is aimed on the integrated relaxation oscillator design for automotive applications, that are characterized by harsh operation conditions and high robustness requirements.

Literature research was conducted to acquire necessary theoretical basis for comparative study of the recently proposed integrated oscillator designs to choose the oscillator architecture utilizing integrated-error feedback for the implementation.

High-level model simulations were conducted to predict negative influences on the system performance and to suggest blocks optimal parameters for the design.

The implementation of the designed blocks was discussed, and simulation results of the critical parameters were presented.

The designed oscillator simulations proved the consistency of the integrated-error feedback concept for practical realization. However, the designed system needs further improvements.

Key words: automotive electronics, relaxation oscillator, IEF

#### Abstrakt

Tato práce je zaměřena na návrh integrovaného relaxačního oscilátoru pro automobilové aplikace, které jsou charakteristické extrémními provozními podmínkami a vysokými požadavky na robustnost.

Z dostupné literatury byla provedena rešerše, která umožnila postihnout nezbytný teoretický základ pro komparativní studii nedávno představených designů integrovaných oscilátorů a také pomohla navrhnout architekturu oscilátoru, která v implementaci zahrnuje princip IEF.

Za účelem předpovězení negativních vlivů na výkon systému a optimálních parametrů bloků byly provedeny simulace vysokoúrovňového modelu.

V práci je diskutována implementace jednotlivých bloků a prezentovány výsledky simulace kritických parametrů.

Simulace navrženého oscilátoru prokázaly konzistenci konceptu IEF pro praktickou realizaci. Realizovaný systém však potřebuje další vylepšení.

Klíčová slova: automobilová elektronika, relaxační oscilátor, IEF

# Contents

| 1 | Intro | oduction                                                                 | 1  |

|---|-------|--------------------------------------------------------------------------|----|

|   | 1.1   | Oscillators in general                                                   | 1  |

|   | 1.2   | Design goals                                                             | 2  |

|   | 1.3   | Structure of the thesis                                                  | 2  |

| 2 | The   | oretical prerequisites                                                   | 4  |

|   | 2.1   | First-order oscillator model                                             | 4  |

|   | 2.1.  | 1 One-integrator oscillator                                              | 6  |

|   | 2.1.  | 2 Sawtooth oscillator                                                    | 6  |

|   | 2.1.  | 3 Discussion on the model                                                | 8  |

|   | 2.2   | Noise modeling of the relaxation oscillator                              | 9  |

|   | 2.2.  | 1 Verhoeven's high-level modeling of spectral noise shapes               | 10 |

|   | 2.2.  | 2 Gierkink's jitter                                                      | 17 |

| 3 | Revi  | ew of recent proposals                                                   | 21 |

|   | 3.1   | Relaxation oscillator employing voltage averaging feedback               | 21 |

|   | 3.1.  | 1 The design considerations                                              | 22 |

|   | 3.1.  | 2 Start-up sequence                                                      | 23 |

|   | 3.1.  | Sensitivity to the reference. Noise reduction                            | 24 |

|   | 3.1.  | 4 The performance                                                        | 24 |

|   | 3.2   | Relaxation oscillator employing a feedforward period control scheme      | 25 |

|   | 3.2.  | Comparator and SR-latch delay cancellation                               | 26 |

|   | 3.2.  | The period controller operation                                          | 26 |

|   | 3.2.  | The performance                                                          | 27 |

|   | 3.3   | Relaxation oscillator employing dynamic threshold and switched resistors | 28 |

|   | 3.3.  | 1 Dynamic threshold technique                                            | 28 |

|   | 3.3.  | 2 Switched resistors technique                                           | 29 |

|   | 3.3.  | The performance                                                          | 30 |

|   | 3.4   | Relaxation oscillator employing IEF                                      | 30 |

|   | 3.4.  | 1 IEF application                                                        | 31 |

|   | 3.4.  | The effect of sampling capacitor                                         | 32 |

|   | 3.4.  | The performance                                                          | 32 |

|   | 3.5   | Discussion on the studied proposals                                      | 33 |

|   | 3.5.  | 1 Performance summary                                                    | 33 |

|   | 3.5.  | 2 Comparative analysis                                                   | 34 |

| 4  | Hig    | sh-leve | el modeling                                                 | . 36 |

|----|--------|---------|-------------------------------------------------------------|------|

|    | 4.1    | The     | chosen topology for the implementation                      | . 36 |

|    | 4.1    | 1       | Recommendations on the design                               | . 36 |

|    | 4.2    | Sim     | ulation of HLM                                              | . 37 |

|    | 4.2    | 2.1     | The set-up                                                  | . 37 |

|    | 4.2    | 2       | Verification of the concept                                 | . 40 |

|    | 4.2    | 2.3     | Impact of the switches internal resistance                  | . 41 |

|    | 4.2    | 4       | Impact of the comparators matched and mismatched offsets    | . 43 |

|    | 4.2    | 2.5     | Impact of the mismatch between the operational amplifiers   | . 44 |

|    | 4.2    | .6      | HLM summary                                                 | . 45 |

| 5  | Blo    | ck des  | sign                                                        | . 46 |

|    | 5.1    | Logi    | c devices                                                   | . 46 |

|    | 5.2    | Ope     | rational amplifier                                          | . 48 |

|    | 5.2    | 2.1     | Offset voltage                                              | . 50 |

|    | 5.3    | Com     | nparator                                                    | . 51 |

|    | 5.3    | 3.1     | The topology                                                | . 51 |

|    | 5.3    | 3.2     | The simulation                                              | . 52 |

|    | 5.4    | Cha     | rging current source                                        | . 54 |

|    | 5.4    | .1      | The simulation                                              | . 54 |

|    | 5.5    | The     | IEF block                                                   | . 56 |

|    | 5.5    | 5.1     | Stability of IEF                                            | . 56 |

|    | 5.6    | Swit    | ches                                                        | . 57 |

|    | 5.6    | 5.1     | Discharging switch                                          | . 57 |

|    | 5.6    | 5.2     | Charge transfer switch                                      | . 58 |

| 6  | The    | e com   | olete system                                                | . 60 |

|    | 6.1    | The     | simulation                                                  | . 62 |

|    | 6.1    | 1       | The set-up                                                  | . 62 |

|    | 6.1    | 2       | The results                                                 | . 62 |

|    | 6.1    | 3       | Discussion on the results                                   | . 64 |

| 7  | Co     | nclusio | on                                                          | . 65 |

| Re | eferen | ces     |                                                             | . 66 |

| Αŗ | pend   | ices    |                                                             | . 68 |

|    | A.     | Red     | uction of 1/f noise in MOSFET under switched bias condition | . 68 |

# List of figures

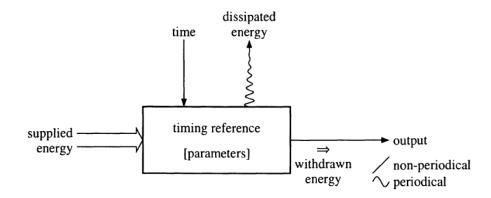

| Figure 1.1 Block diagram representing an oscillator in general. The image is taken from [2] 1                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

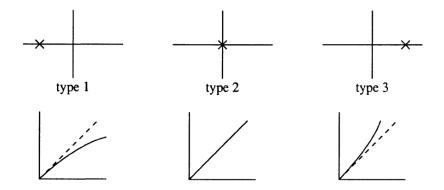

| Figure 2.1 Three types of the first-order systems. Their pole-patterns on top and corresponding impulse responses on bottom. The image is taken from [2]4                                                                                                                      |

| Figure 2.2 Principle of equidistant level discrimination in the first-order oscillator. The image is taken from [5]5                                                                                                                                                           |

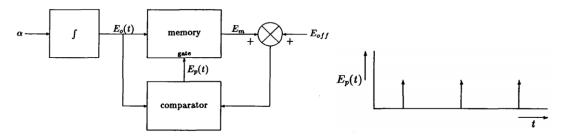

| Figure 2.3 Principle of the first-order oscillator to the left; periodic pulses, generated by the comparator block to the right. The image is taken from [4]5                                                                                                                  |

| Figure 2.4 First-order regenerative oscillator with one integrator and its capacitor voltage waveforms.  The image is taken from [5]6                                                                                                                                          |

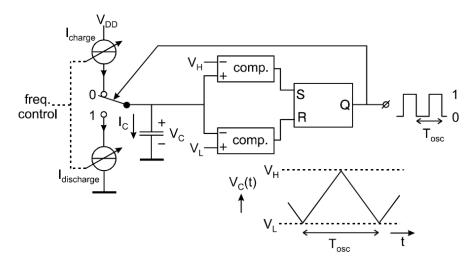

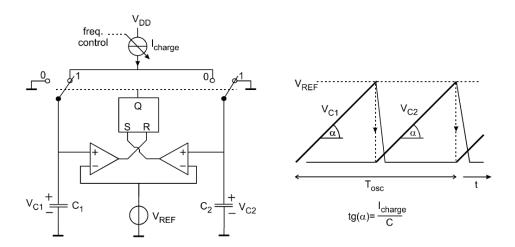

| Figure 2.5 The two-integrator oscillator to the left and its capacitor voltage waveforms to the right The image is taken from [5]7                                                                                                                                             |

| Figure 2.6 Regenerative two-integrator oscillator with memory bypass to the left and its capacitor voltage waveforms to the right. The image is taken from [5]                                                                                                                 |

| Figure 2.7 Dependence of timing error on the integration constant. The image is taken from [5] 8                                                                                                                                                                               |

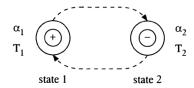

| Figure 2.8 A state machine, describing basic function of the relaxation oscillator. The image is taken from [2]10                                                                                                                                                              |

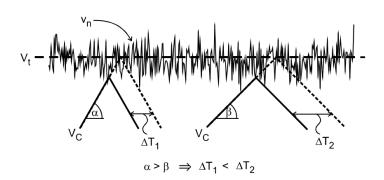

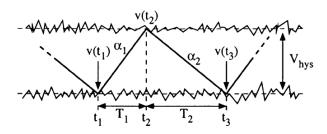

| Figure 2.9 Generalized waveform of the integrator in relaxation oscillator with depicted comparator reference levels fluctuations. The image is taken from [2]10                                                                                                               |

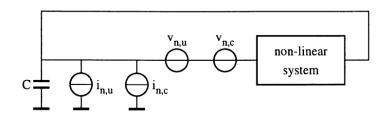

| Figure 2.10 The four basic noise sources in a first-order oscillator by Verhoeven. The image is taken from [2]11                                                                                                                                                               |

| Figure 2.11 An example of the sampling system extracting timing information of the oscillator. The image is taken from [2]11                                                                                                                                                   |

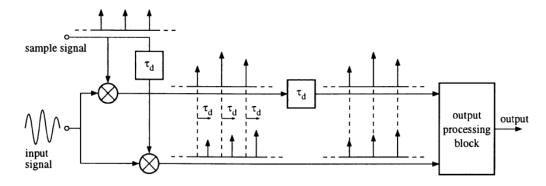

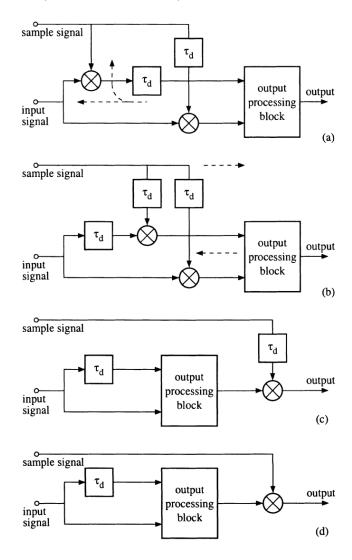

| Figure 2.12 Transformations of the system from Figure 2.11 to enable simpler description of the sampling system. (a) Original system. (b-d) Consecutive transformation steps. The image is taken from [2]                                                                      |

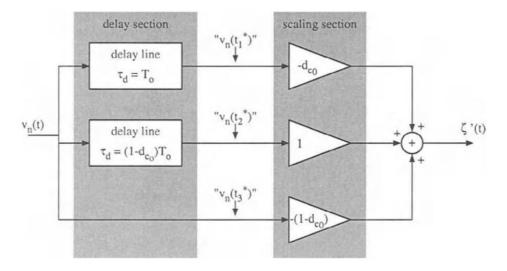

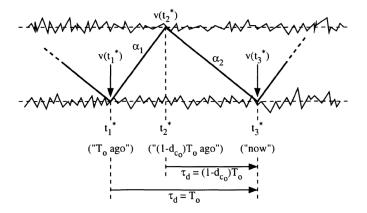

| Figure 2.13 The sampling system to describe equation of the relative variation of the oscillator period in case of uncorrelated noise voltage source. The image is taken from [2].                                                                                             |

| Figure 2.14 Application of the sampling system model to describe the oscillator. The image is taken from [2]14                                                                                                                                                                 |

| Figure 2.15. The filter that corresponds to the relative variation of the oscillator period due to noise in frequency domain. The image is taken from [2]14                                                                                                                    |

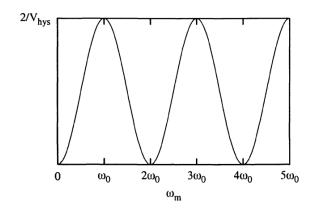

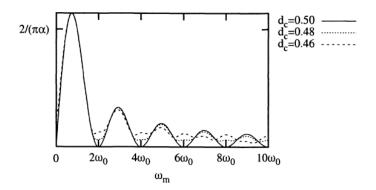

| Figure 2.16 The modulus of the transfer of the filter from Figure 2.15, for the case when duty cycle is equal to 0.5. A DC noise source has no influence, noise components with a frequency close to the carrier frequency have maximal influence. The image is taken from [2] |

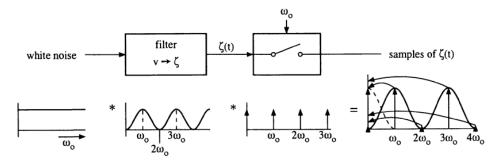

| Figure 2.17 The sampling affecting the noise spectrum of the oscillator. The image is taken from [2]15                                                                                                                                                                         |

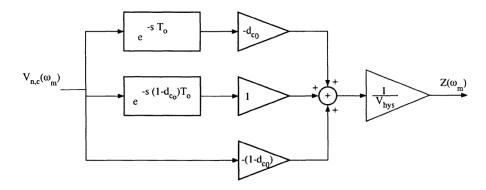

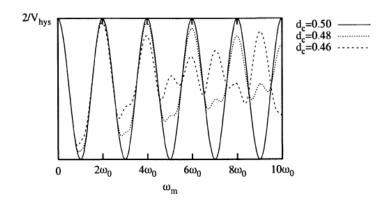

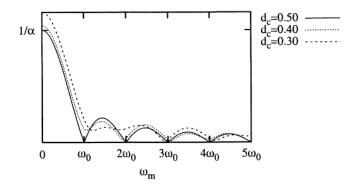

| Figure 2.18 The modulus of the transfer of the filter corresponding to the model of oscillator noise caused by the correlated noise voltage source $(dc0)$ is duty cycle). The image is taken from [2]16                                                                       |

| Figure 2.19 The modulus of the transfer of the filter corresponding to the model of oscillator noise caused by the uncorrelated noise current source ( $dc0$ is duty cycle). The image is taken from [2] 16                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.20 The modulus of the transfer of the filter corresponding to the model of oscillator noise caused by the correlated noise current source ( $dc0$ is duty cycle). The image is taken from [2] 17                                                                             |

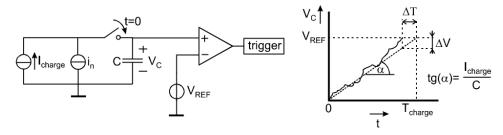

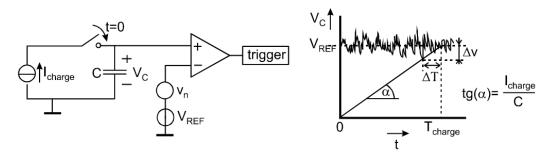

| Figure 2.21 Sawtooth relaxation oscillator with the noise source considered by Gierkink in [5]. The image is taken from [5]                                                                                                                                                           |

| Figure 2.22 Signal model and capacitor voltage waveform in case of a noisy charging current, considered in [5]. The image is taken from [5].                                                                                                                                          |

| Figure 2.23 Signal model and capacitor voltage waveform in case of a noisy reference voltage, considered in [5]. The image is taken from [5]                                                                                                                                          |

| Figure 2.24 The comparator model and the linearized transfer function of its differential pair, used by Gierkink [5] to derive jitter in case in of a noisy reference voltage. The image is taken from [5] 19                                                                         |

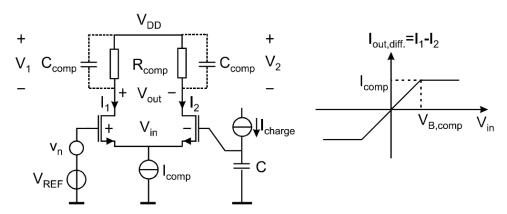

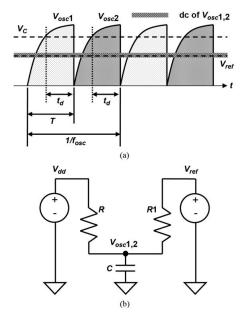

| Figure 3.1 The oscillator structure proposed in [14]. The image is taken from [14]                                                                                                                                                                                                    |

| Figure 3.2 Circuit schematics of (a) feedback amplifier and (b) comparator, that are utilized in [14]. The image is taken from [14].                                                                                                                                                  |

| Figure 3.3 (a) Waveform and (b) modeling of oscillation in [14]. The image is taken from [14] 22                                                                                                                                                                                      |

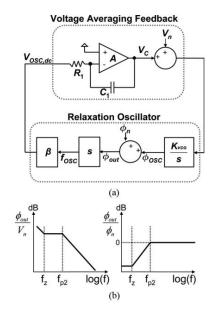

| Figure 3.4 (a) Noise transfer model and (b) noise transfer gains from two dominant noises to phase noise, of the design proposed in [14]. The image is taken from [14].                                                                                                               |

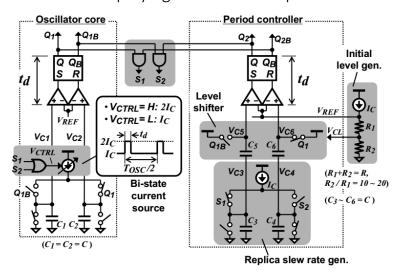

| Figure 3.5 Schematic of the relaxation oscillator with feedforward period control scheme. The image is taken from [17].                                                                                                                                                               |

| Figure 3.6 Waveform of the capacitor voltage in the feedforward period control scheme. The image is taken from [17]                                                                                                                                                                   |

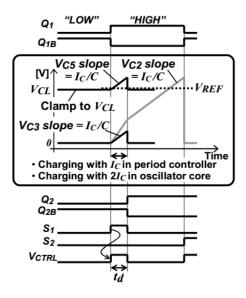

| Figure 3.7 Waveforms of the period controller in the design proposed in [17]. The image is taken from [17]                                                                                                                                                                            |

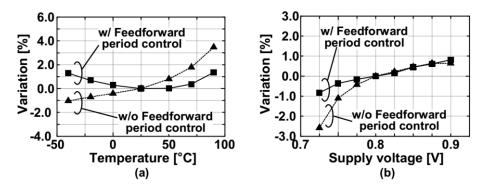

| Figure 3.8 Measured frequency variation of the oscillator in [17] with respect to (a) temperature, (b) supply voltage. The dependencies are shown for the circuits with the enabled and disabled feedforward period control. The image is taken from [17].                            |

| Figure 3.9 Schematic of the relaxation oscillator with dynamic threshold. The image is taken from [18].                                                                                                                                                                               |

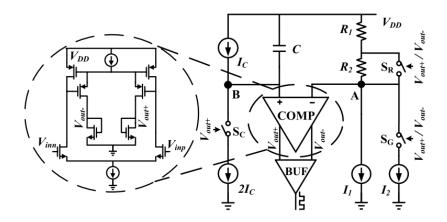

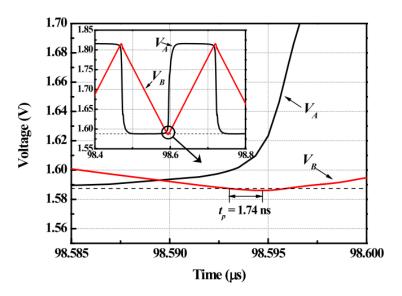

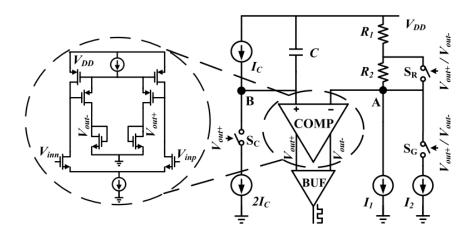

| Figure 3.10 Simulation waveform of the voltages of nodes A and B in Figure 3.9, presented by the authors of [18]. The image is taken from [18]                                                                                                                                        |

| Figure 3.11 Schematic of the relaxation oscillator with dynamic threshold and switches resistors. The image is taken from [18]                                                                                                                                                        |

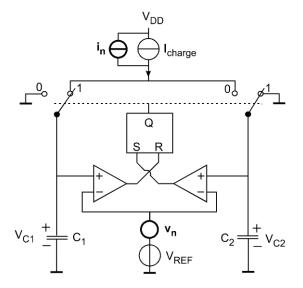

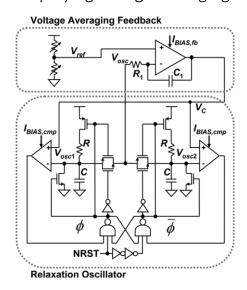

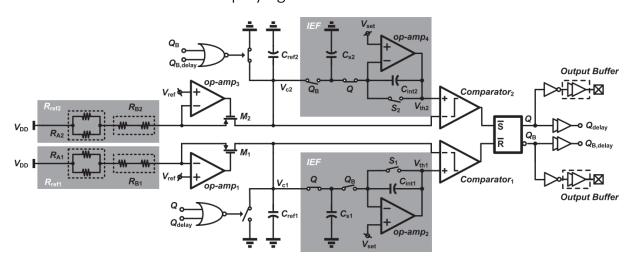

| Figure 3.12 Schematic of the relaxation oscillator with IEF. The image is taken from [19] 30                                                                                                                                                                                          |

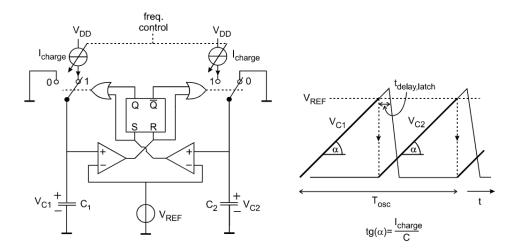

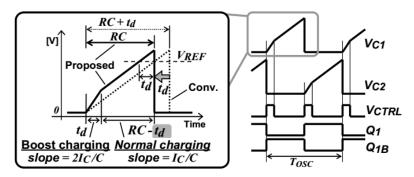

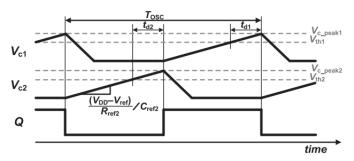

| Figure 3.13 Timing diagrams of relaxation oscillator with a delay $td$ . The image is taken from [19] 31                                                                                                                                                                              |

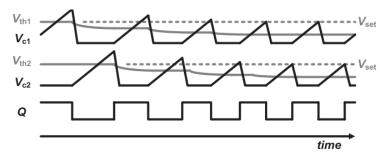

| Figure 3.14 Waveforms of the oscillator with IEF. $Vset$ is the nominal reference level; $Vc1$ and $Vc1$ are the voltages of the reference capacitors; $Vth1$ and $Vth2$ are the output voltages of the IEF blocks; $Q$ is the output of the oscillator. The image is taken from [19] |

| Figure 3.15 Model of IEF. $td$ is the delay of the comparator with the logic circuits; $Cref$ is the reference capacitance; $Cs$ is the sampling capacitance; $Cint$ is the IEF integrator capacitance; $Vset$ is the nominal reference level; $Vc\_peak$ is the peak voltage of the reference capacitor; $Vth$ is the output voltage of the IEF block; $I$ is the charging current. The image is taken from [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.16 The effect of sampling capacitor in the oscillator with IEF. The image is taken from [19].32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

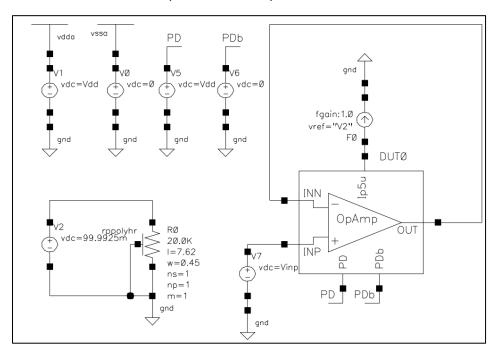

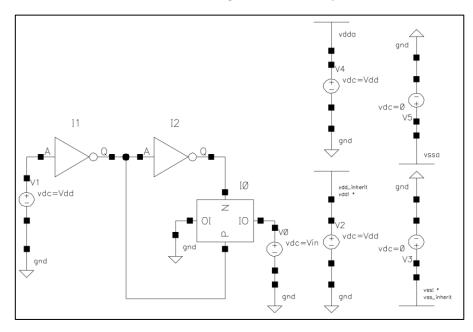

| Figure 4.1 The schematics view of the HLM simulation set-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

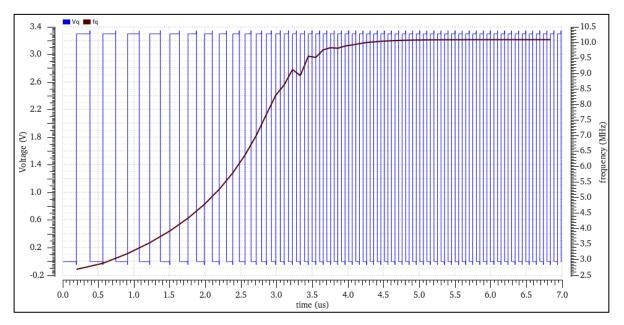

| Figure 4.2 The output waveform of the oscillator (voltage of the Q terminal in Figure 4.1) – blue (Vq), and the frequency waveform of $Vq$ – red (fq). Conditions: tdel = 20 ns, $Vos$ = 0 $V$ for both comparators; $Vos$ = 3 mV for both op-amps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

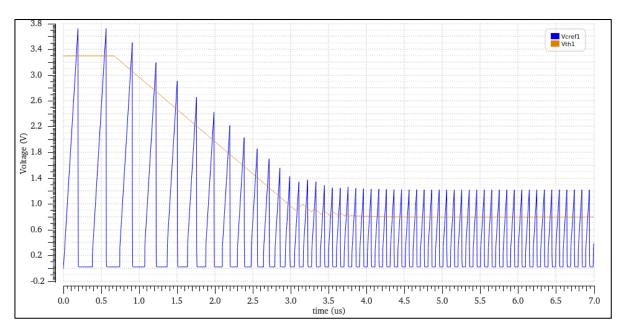

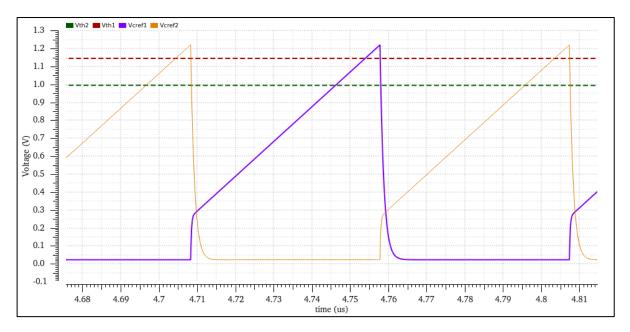

| Figure 4.3 The voltage waveform of the reference capacitor CREF1 (Figure 4.1) – blue (Vcref1), and the output voltage waveform of IEF block connected to CREF1 (node Vth1 in Figure 4.1) – orange (Vth1). Conditions: tdel = $20$ ns, Vos = $0$ V for both comparators; Vos = $3$ mV for both op-amps41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

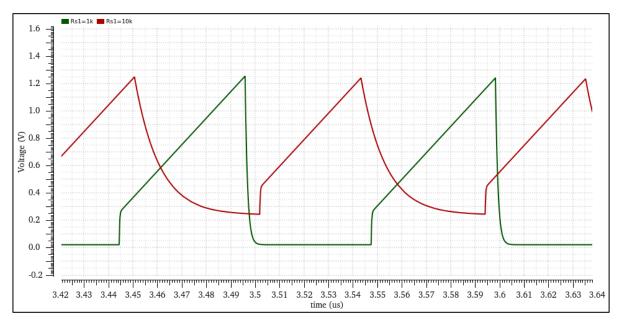

| Figure 4.4 The voltage waveforms of the reference capacitor CREF1 with the resistor R2, at the discharging switch S1, of: 1 kOhm $-$ green (Rs1 = 1k), and 10 kOhm $-$ red (Rs1 = 10k). Conditions: tdel = 2 ns, Vos = 3 mV for both comparators; Vos = 3 mV for both op-amps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

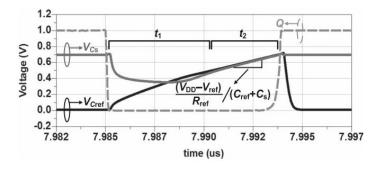

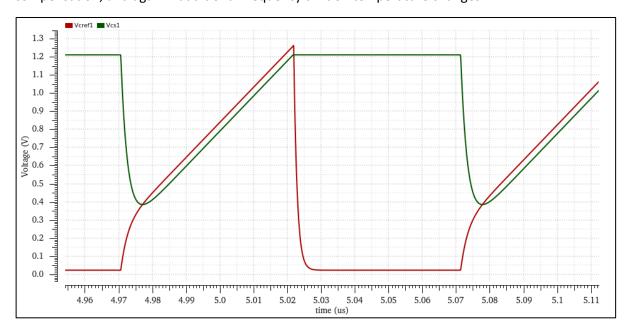

| Figure 4.5 The voltage waveforms of the reference capacitor CREF1 — red (Vcref1), and the sampling capacitor — green (Vcs1), when the internal resistance (R5) of the switch (S2) between these resistors is set to 10 kOhm. Conditions: tdel = 2 ns, Vos = 3 mV for both comparators; Vos = 3 mV for both opamps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

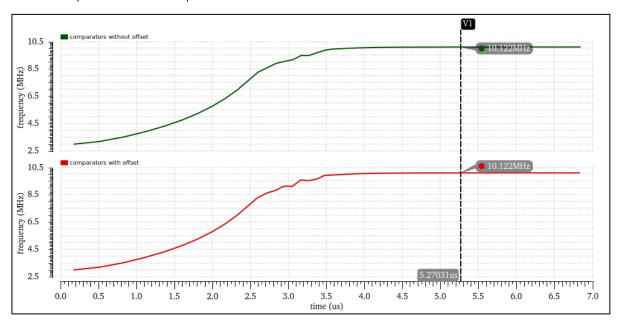

| Figure 4.6 The oscillator frequency over time for the case of comparators without offset – green, and with offset – red. Conditions: $(1^{st} \text{ run})$ – tdel = 1 ns and Vos = 0 V for both comparators, Vos = 0 V for both op-amps; $(2^{nd} \text{ run})$ – tdel = 1 ns and Vos = 10 mV for both comparators, Vos = 0 V for both op-amps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

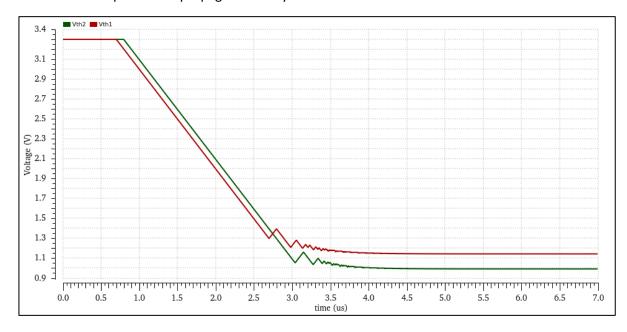

| Figure 4.7 The voltage waveforms (Vth1 $-$ red and Vth2 $-$ green) from the outputs of the IEF blocks of two different branches of the system. Conditions: tdel = 2 ns, Vos = 1 mV for the comparator COM1; tdel = 10 ns, Vos = 5 mV for the comparator COM2; Vos = 3 mV for both op-amps43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 4.8 The voltage waveforms (Vth1 $-$ red and Vth2 $-$ green) from the outputs of the IEF blocks of two different branches of the system, and sampling capacitors CREF1 $-$ purple (Vcref1), CREF2 $-$ orange (Vcref2). Conditions: tdel = 2 ns, Vos = 1 mV for the comparator COM1; tdel = 10 ns, Vos = 5 mV for the comparator COM2; Vos = 3 mV for both op-amps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

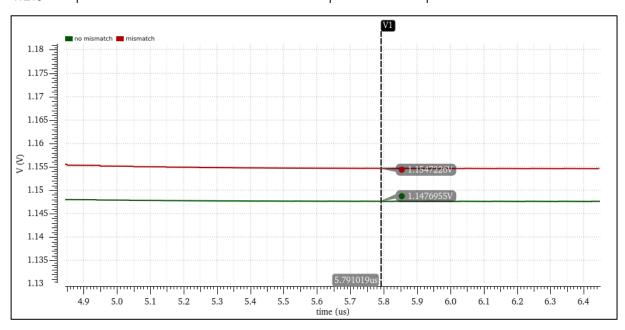

| Figure 4.9 The voltage waveforms of Vth2 when the op-amps are matched – green, and mismatched – red, after the settling. Conditions: $tdel = 2 	ext{ ns}$ , $tdel = 2 	ext{ ns}$                                                                                                                                                                                                                                                                                                                                                                                                                                     |

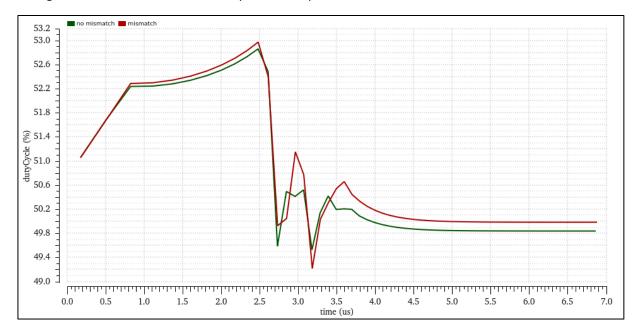

| Figure 4.10 Duty cycle of the oscillator output when the op-amps are matched – green, and mismatched – red. Conditions: $tdel = 2 \text{ ns}$ , $tdel $ |

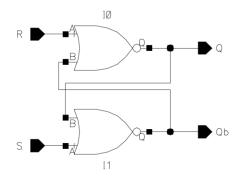

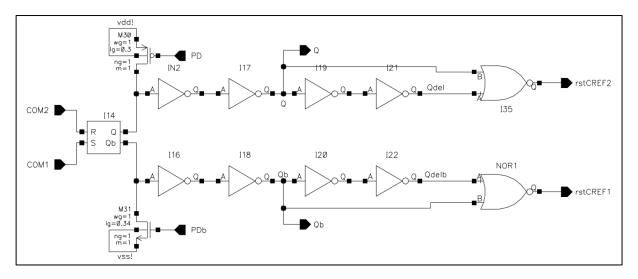

| Figure 5.1. The schematic view of the implemented SR-latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

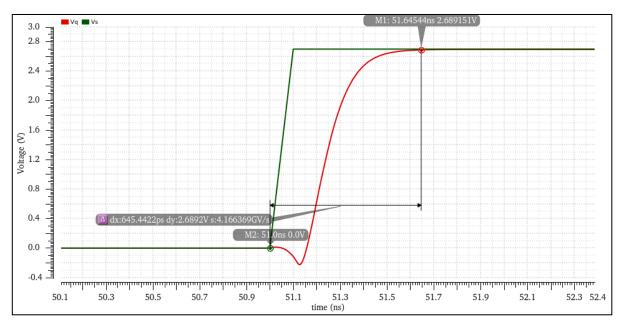

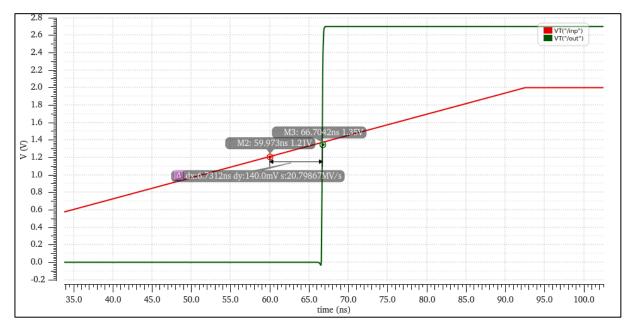

| Figure 5.2. Slew rate of the SR-latch in nominal conditions and power supply voltage of 2.7 V 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 5.3. Logic block of the implemented design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

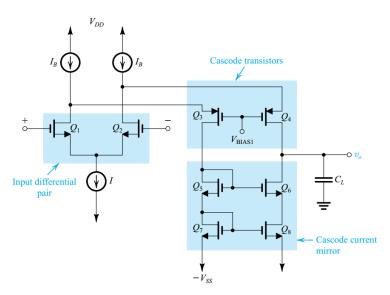

| Figure 5.4. Principle circuit of the folded-cascode op-amp. The image is taken from [20]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

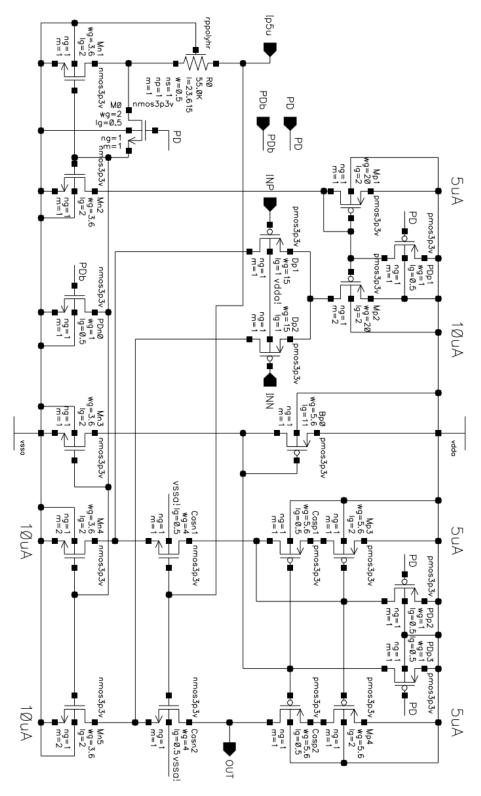

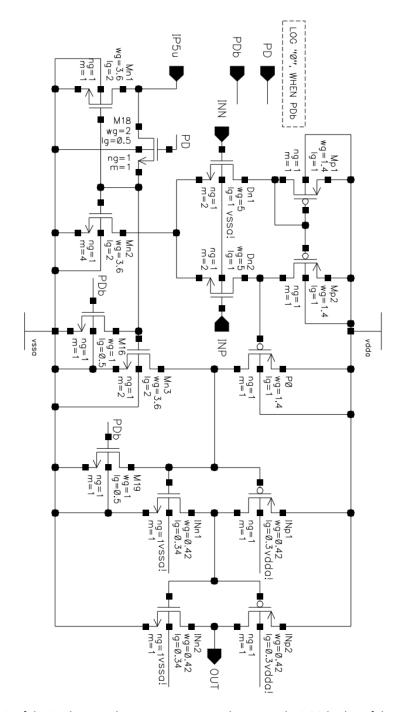

| Figure 5.5 The designed op-amp block. The dimensions of the components are depicted (for NMO and PMOS: wg – channel width, lg – channel length, m – number of transistors in parallel, ng – numbe of gate-fingers)                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.6 Simulation set-up for the op-amp offset estimation                                                                                                                                                                                                                                                                                                                                                                       |

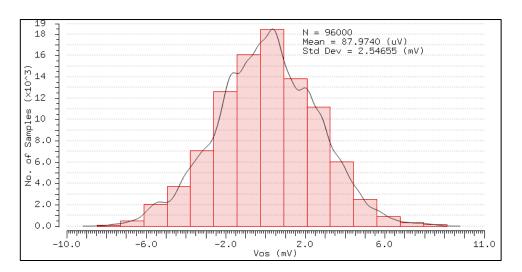

| Figure 5.7 The statistics of the op-amp offset voltage simulated by the Monte Carlo analysis ove process (all the considered corners), temperature (-40°C and 175°C), power supply (2.7 and 3.6 V) and mismatch variations.                                                                                                                                                                                                         |

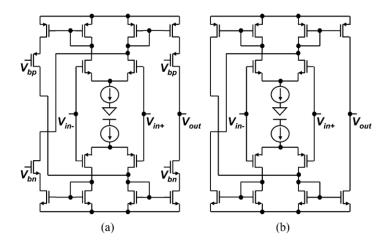

| Figure 5.8. Schematic of the implemented comparator. Power down sets the initial value of the comparator to logical 'low'.                                                                                                                                                                                                                                                                                                          |

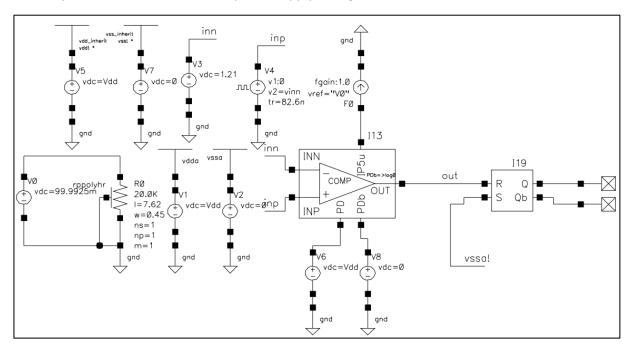

| Figure 5.9. The simulation set-up for the comparator. The input is fed with a voltage ramp of the same slope as expected in the complete system                                                                                                                                                                                                                                                                                     |

| Figure 5.10. Simulation waveform of the comparator for the worst corner. V4 voltage waveform (Figure 5.9) — red; comparator output voltage waveform — green. The resulting propagation delay in approximately 7 ns                                                                                                                                                                                                                  |

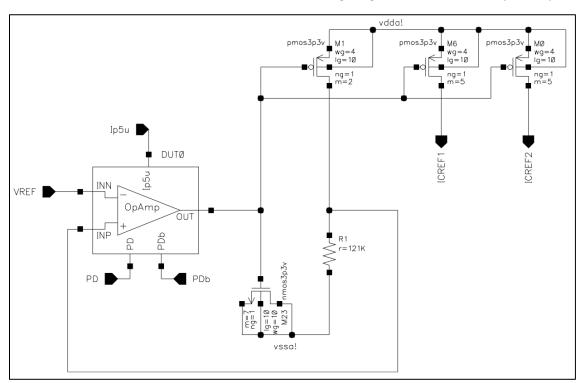

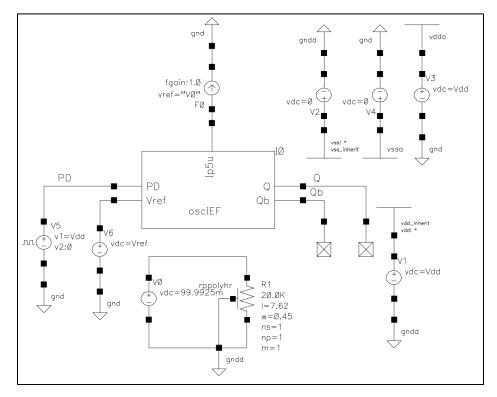

| Figure 5.11 The schematic of the implemented current reference. The NMOS M23 is a compensation capacitor. The resistor R1 is ideal, since trimming is expected.                                                                                                                                                                                                                                                                     |

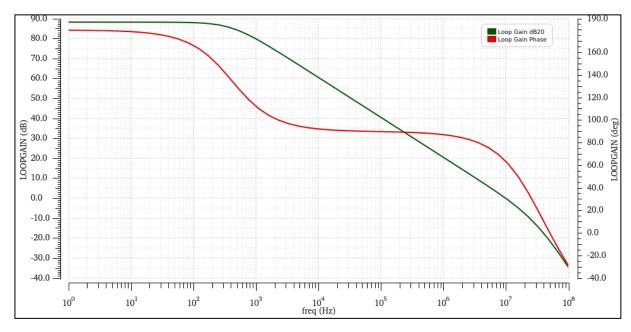

| Figure 5.12 The worst corner simulation result, of the designed current source, with the phase margin of approximately 60°                                                                                                                                                                                                                                                                                                          |

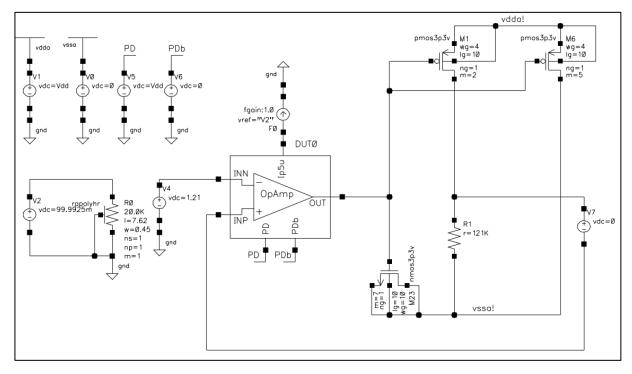

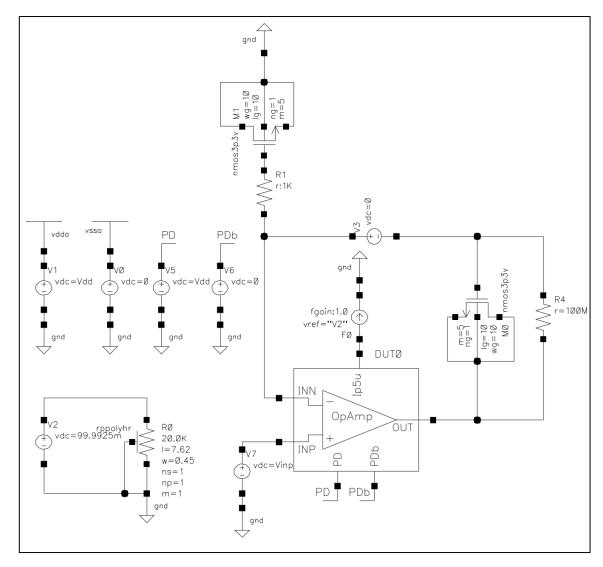

| Figure 5.13 Simulation set-up to estimate frequency stability and precision of the designed curren source                                                                                                                                                                                                                                                                                                                           |

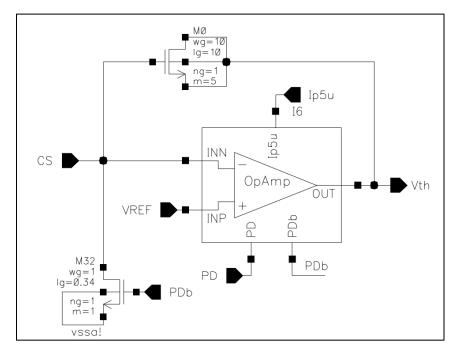

| Figure 5.14 Implemented IEF block. The op-amp is taken from Section 5.2, NMOS M0 is feedbac capacitor, NMOS M32 is a power down switch for the initial state setting. Pin CS is a connection to the sampling capacitor through the switch, pin VREF is a connection to the voltage reference defining the charging capacitors peak voltage, pin Vth is an output of the IEF block defining the reference voltage for the comparator |

| Figure 5.15 Simulation set-up for the IEF block stability analysis.                                                                                                                                                                                                                                                                                                                                                                 |

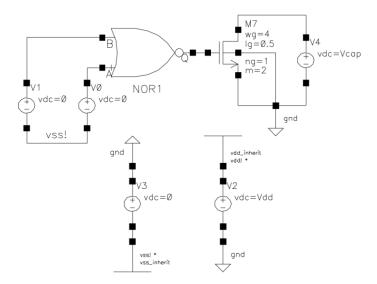

| Figure 5.16 Simulation set-up for the discharging switch NMOS M7. DC voltage source V2 sets the power supply voltage (2.7 V and 3.6 V), V0 and V1 are set to 0 V to trigger the NOR gate to the 'high state (so the switch M7 sees the same voltage on its gate as in the system).                                                                                                                                                  |

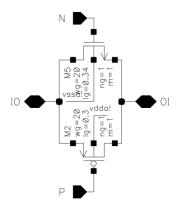

| Figure 5.17 Switch applied between sampling capacitor and the reference one, as well as, IEF block                                                                                                                                                                                                                                                                                                                                  |

| Figure 5.18 The symbolic view of the switch from Figure 5.17 59                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 5.19 The simulation set-up of the charge transfer switch.                                                                                                                                                                                                                                                                                                                                                                    |

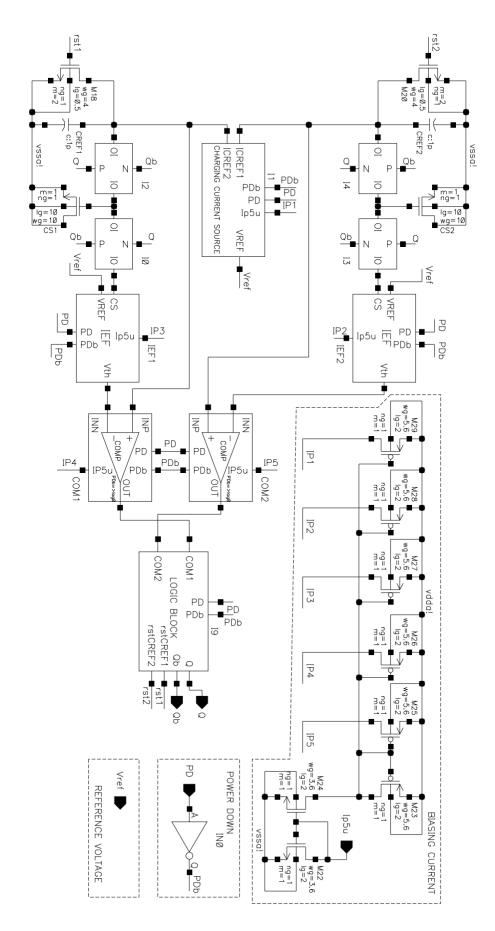

| Figure 6.1 The simulation set-up of the complete system depicted in Figure 6.2                                                                                                                                                                                                                                                                                                                                                      |

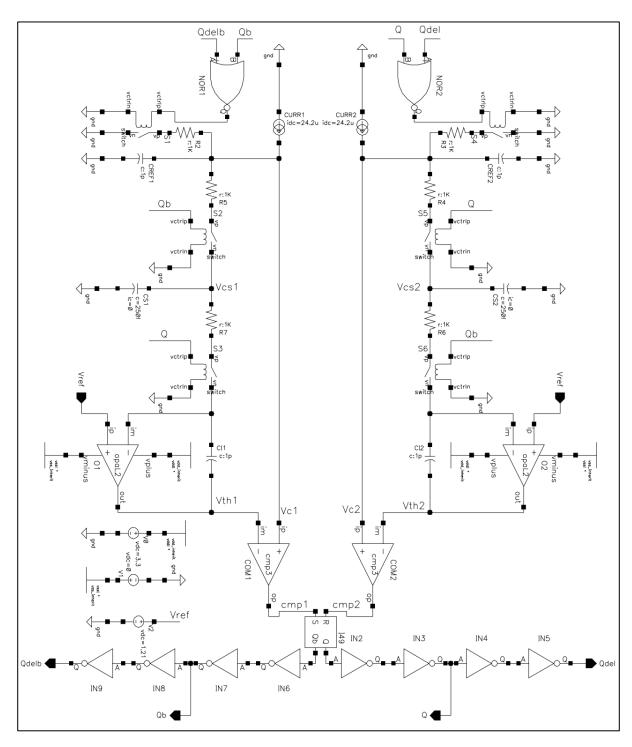

| Figure 6.2 The designed sawtooth relaxation oscillator with IEF                                                                                                                                                                                                                                                                                                                                                                     |

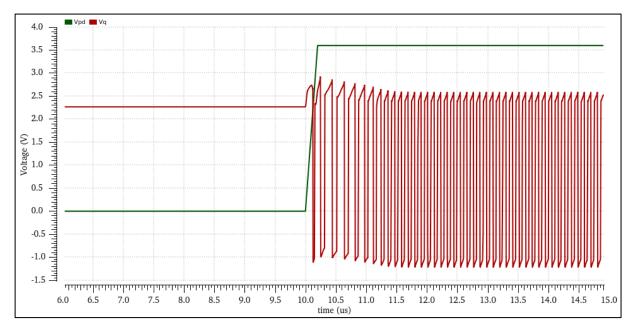

| Figure 6.3 The simulated oscillator output waveform corresponding to the frequency of 9.295 MHz red (Vq), and power-down signal – green (Vpd)                                                                                                                                                                                                                                                                                       |

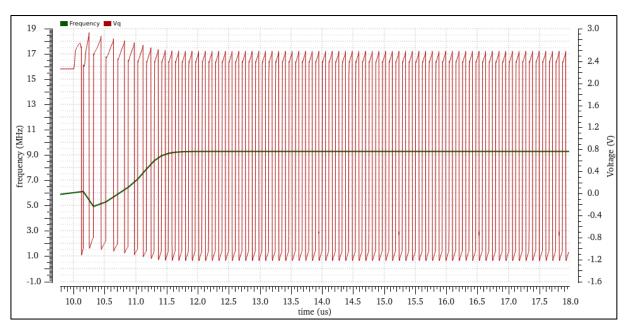

| Figure 6.4 The simulated oscillator output waveform corresponding to the frequency of 9.295 MHz red (Vq), and its frequency over time – green                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                     |

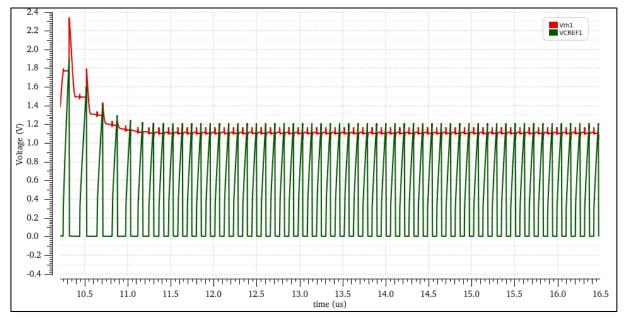

| Figure 6.5 The simulated voltage waveform (corresponding to the corner producing frequency of 9.295 MHz) of the charging capacitor CREF1 (Figure 6.2) – greed (VCREF1), and the dynamic voltage reference for the comparator – red (Vth1)63                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

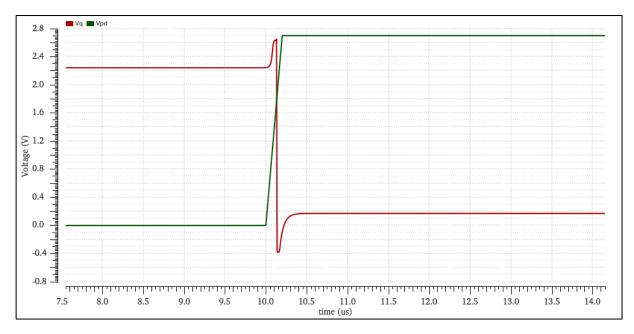

| Figure 6.6 The simulated oscillator output waveform corresponding to the "faulty" corner – red (Vq) and power-down signal – green (Vpd)64                                                                                                                                                  |

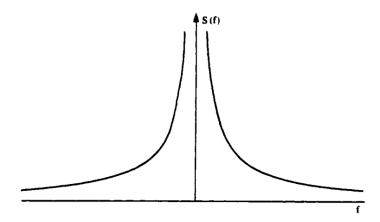

| Figure 0.1 The power spectral density of 1/f noise. The image is taken from [8]                                                                                                                                                                                                            |

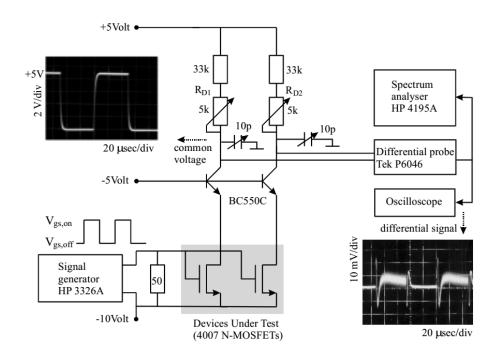

| Figure 0.2 The measurement setup, presented in [5], to measure MOSFET noise under switched bias conditions. The image is taken from [5]69                                                                                                                                                  |

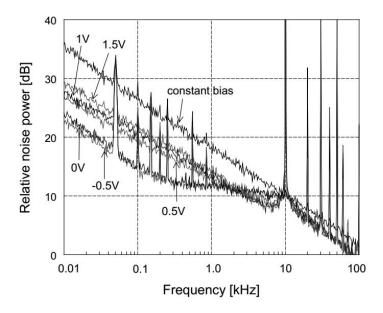

| Figure 0.3 Measured baseband 1/f noise for constant and switched bias conditions, [5]. Measured device: HEF 4007 NMOS; switching parameters: $fswitch = 10 \ kHz$ , 50% duty cycle, $VGS\_on = 2.5 \ VVGS\_off$ is indicated on the plot for different curves. The image is taken from [5] |

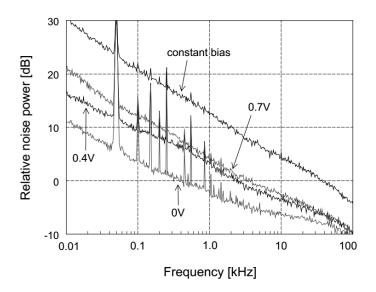

| Figure 0.4 Measured baseband 1/f noise for constant and switched bias conditions, [5]. Measured device: HEF 4007 NMOS; switching parameters: $fswitch = 2 MHz$ , 50% duty cycle, $VGS\_on = 2.5 VVGS\_off$ is indicated on the plot for different curves. The image is taken from [5]      |

## List of tables

| Fable 3.1 Performance summary of the oscillator in [14]                       | . 25 |

|-------------------------------------------------------------------------------|------|

| Table 3.2 Performance summary of the oscillator in [17]                       | . 28 |

| Table 3.3 Performance summary of the oscillator in [18].                      | . 30 |

| Table 3.4 Performance summary of the oscillator in [19]                       | . 33 |

| Table 3.5 Comparative performance summary of the designs from [14], [17]–[19] | . 34 |

| Table 4.1 Parameters of the ideal op-amp block employed in HLM                | . 39 |

| Table 4.2 Parameters of the ideal comparator block employed in HLM            | . 39 |

| Table 5.1 Overview of the process corners employed in the simulations         | . 46 |

### List of acronyms

ADC Analog-to-digital converter

**BER** Bit error rate

**ISO** International Organization for Standardization

**EMC** Electromagnetic compatibility

IC Integrated circuit

**CMOS** Complementary metal-oxide-semiconductor

MIMC Metal-insulator-metal capacitor

MOSFET Metal-oxide-semiconductor field-effect transistor

NMOS N-channel MOSFET

PMOS P-channel MOSFET

**LPF** Low-pass filter

VCO Voltage-controlled oscillator

**FOM** Figure of merit

**DT** Dynamic threshold

**ST** Switched resistor

TC Temperature coefficient

IEF Integrated-error feedback

**Op-amp** Operational amplifier

**HLM** High-level modeling (or "high-level model")

**DC** Direct current

#### 1 Introduction

The share of electronics in the price of a modern automobile has gained almost 15% over the last two decades, and it is expected that the growth will continue and even enhance its rate [1]. It is a good indication of an increase in the amount and complexity of electronic systems in cars.

Therefore, the sensor systems, being a significant part of the modern automotive electronics, expand and are utilized in an increasing number of applications. These systems actively exploit digital signal processing employing ADC units. ADCs require accurate clock signals, since the deviations of the clock frequency cause the rise in bit error rate (BER) of the converters. Taking into account that many of the automotive sensor applications are directly or indirectly related to safety (ISO 26262), design of the precise clock generator is of great importance, what can be a challenging task, because automotive electronic systems are exposed to extreme environmental conditions (e.g. wide temperature range, big variations of the power supply voltage etc.).

Requirements for speeds of operation, electromagnetic compatibility (EMC), low power dissipation, small dimensions have made integrated circuits (ICs) a dominant solution in automotive electronics. Therefore, clock generators gained an additional limitation concerning their architecture, they have to be integrated and occupy little area on the chip to withstand adequate production costs.

This thesis is aimed at designing the integrated clock generator (oscillator) in I4TE technology from the company ON Semiconductor through discussion of the problematics, conduction of the literature research and realization of the chosen architecture by means of the Cadence software.

#### 1.1 Oscillators in general

Oscillator is a system that generates a periodic signal out of a constant one, which is mostly provided, in case of integrated electronics, by a reference voltage or current source. A timing reference is required to be present in the system, since time can be "measured" only through the quantity that varies in time.

Figure 1.1 Block diagram representing an oscillator in general. The image is taken from [2].

Figure 1.1 illustrates a general view [2] on any oscillatory system. In this figure, the energy is supplied to start the system and maintain its operation, since there are no components in electronics that do not dissipate energy. It can also be seen that time modulates the system and, at the output of the system, the influence of time can be measured in the form of either a periodical or a non-periodical time-variant signal. So, it is an indirect time sensor that can be used as a timing reference. Also, we can

understand that transfer of the timing information to the output is dependent upon two things: the parameters of the timing reference, and the energy supplied to it.

There are two major groups of the timing references: linear and non-linear systems. The non-linear timing references are poorly studied and are difficult to model. Moreover, linear systems are supposed to have better performance over the non-linear ones [3].