F3

Faculty of Electrical Engineering

Department of Microelectronics

Verification component implementation - Model of NFC

Bc. Ján Jendrušák

Supervisor: doc. Ing. Jiří Jakovenko, Ph.D.

Field of study: Electronics and Communications

**Subfield: Electronics**

May 2019

# MASTER'S THESIS ASSIGNMENT

### I. Personal and study details

Student's name:

Jendrušák Ján

Personal ID number:

475404

Faculty / Institute:

**Faculty of Electrical Engineering**

Department / Institute: Department of Microelectronics

Study program:

**Electronics and Communications**

Branch of study:

**Electronics**

#### II. Master's thesis details

Master's thesis title in English:

**Verification Component Implementation - Model of NFC**

Master's thesis title in Czech:

Implementace verifikační komponenty - modelu NFC přijímače

#### Guidelines:

- 1. Study NFC (Near Field Communication) Type 2 Tag Platform protocol according to [1] and techniques of verification component (UVC - Universal Verification Component) implementation based on UVM (UV Methodology) framework.

- 2. Implement NFC Forum Device Type 2 UVC supporting NFC protocol according to specification [1](chap.2.1,3,4 and 5) This UVC shall therefore:

- Support the commands from [1] specification: ALL\_REQ, SENS\_REQ, SELL\_REQ, SDD\_REQ, SLP\_REQ, READ, WRITE, SECTOR SELECT

- Identify all possible responses to previously stated commands

- Model the Static Memory Structure and NFC Type 2 Tag Platform State Machine

- Validate the timing between the response of DUT and command from UVC and compare actual response with the expected response

- 3. Write verification plan for NFC Type 2 Tag Platform based on [1] and add coverage points to cover the requirements.

- 4. Demonstrate UVC functionality by writing an example of a constrained-random test. As a DUT use reference NFC Type

- 2 Tag platform design module from ASICentrum.

Bibliography / sources:

[1] NFCForum. Type 2 Tag Operation Specification. Verze 1.1, 2011-05-31.

Name and workplace of master's thesis supervisor:

doc. Ing. Jiří Jakovenko, Ph.D., Department of Microelectronics, FEE

Name and workplace of second master's thesis supervisor or consultant:

Date of master's thesis assignment: 07.02.2019

Deadline for master's thesis submission: 24 052019

Assignment valid until: 20.09.2020

doc. Ing. Jiří Jakovenko, Ph.D.

Supervisor's signature

prof. Ing. Pavel Ripka, CSc.

#### III. Assignment receipt

The student acknowledges that the master's thesis is an individual work. The student must produce his thesis without the assistance of others, with the exception of provided consultations. Within the master's thesis, the author must state the names of consultants and include a list of references.

+.3.2019

Date of assignment receipt

Student's signature

# **Acknowledgements**

I would like to thank my supervisor doc. Ing. Jiří Jakovenko, Ph.D. for his guidance and useful advice everytime I needed one. I would also like to thank ASICentrum company for the great opportunity to work on this master's thesis for their team, especially Ing. Luboš Hradecký for arranging the whole cooperation, Ing. Martin Jäger and Bc. Henrique Hellini for consultations about the testbench development, and Ing. Jan Bičák, Ph.D. and Ing. Tomáš Novák for help with the NFC Type 2 Tag Platform specification and the DUT incorporation into the UVC.

# **Declaration**

I hereby declare that the presented work was carried out independently and that I have listed all information sources used in accordance with the Methodical Guidelines on Maintaining Ethical Principles During the Preparation of Higher Education Theses. Furthermore, I declare that the borrowing and publishing of my thesis or part of it is allowed with the agreement of department.

In Prague, 22. May 2019

# **Abstract**

To design digital circuits is a complex process, which involves verification of design behaviour before it is actually implemented. Universal Verification Methodology (UVM) promises an efficient way of verifying digital designs with any major simulation platform.

Using UVM is demonstrated in this paper to build a verification component for NFC Type 2 Tag Platform, the operational specification for wireless tags in high frequency band. Completely functioning UVC together with prepared verification plan ensures that the Device Under Test (DUT) complies with NFC Type 2 Tag Platform on logical level.

**Keywords:** verification, Universal Verification Methodology, Near Field Communication, SystemVerilog, tag

**Supervisor:** doc. Ing. Jiří Jakovenko, Ph.D.

# **Abstrakt**

Návrh digitálnych obvodov je komplexný proces, ktorý zahŕňa verifikáciu chovania návrhu predtým, ako je na záver implementovaný. Universal Verification Methodology (UVM) je prísľubom efektívneho spôsobu verifikovania digitálnych návrhov s ktoroukoľvek simulačnou platformou.

Použitie UVM je demonštrované v tejto diplomovej práci návrhom verifikačného komponentu pre NFC Type 2 Tag Platform, špecifikácie pre bezdrôtové tagy vo vysokom frekvenčnom pásme. Kompletne funkčný verifikačný komponent spolu s predpripraveným verifikačným plánom by malo zaručiť, že digitálny návrh splňuje požiadavky protokolu na logickej úrovni.

**Kľúčové slová:** verifikácia, Universal Verification Methodology, Near Field Communication, SystemVerilog, tag

**Preklad názvu:** Implementácia verifikačného komponentu – modelu NFC prijímača

| Contents                             |                                                       |

|--------------------------------------|-------------------------------------------------------|

| 0.1 List of Abbreviations 1          | 3.6 SystemVerilog Coverage 19                         |

| 1 Introduction 3                     | Part II<br>Practical Part                             |

| Part I<br>Theoretical Part           | 4 Verification plan 23                                |

| 2 Near Field Communication 7         | 4.1 Requirements                                      |

| 2.1 Type 2 Tag Platform              | 4.1.2 Timing requirements                             |

| 2.1.1 Memory structure 8             | <u> </u>                                              |

| 2.1.2 Sequence schemes 8             | 4.1.3 Tag state requirements 26                       |

| 2.1.3 Bit level coding 10            | 4.1.4 Commands requirements 26                        |

| 2.1.4 Frame format 10                | 4.1.5 Negative scenarios                              |

| 2.1.5 Commands and responses 11      | 4.2 Verification strategy 30                          |

| 2.1.6 Timing requirements 12         | 4.3 Tools                                             |

| 2.1.7 NFC Data exchange format -     | 4.4 Checkers implementation 31                        |

| NDEF                                 | 4.5 Coverage implementation 31                        |

| 2.1.8 Anticollision                  | 4.6 Test cases implementation 32                      |

| 3 Digital design verification and    | 4.7 UVM usage                                         |

| UVM 15                               | 5 Implementation of UVC for NFC                       |

| 3.1 UVM testbench basics 16          | Type 2 Tag 33                                         |

| 3.2 UVM Factory 17                   | 5.1 Command and response items 33                     |

| 3.3 UVM Configuration Database 17    | $5.1.1 \ nfc2\_base\_cmd \ class \ fields \dots \ 34$ |

| 3.4 UVM Phases                       | $5.1.2 \ nfc2\_base\_res \ class \ fields \dots 35$   |

| 3.5 UVM Environment                  | 5.2 System-level design of the                        |

|                                      | testbench                                             |

| 3.5.1 UVM Sequencer and Sequences 18 | 5.2.1 Configuration objects 37                        |

| 3.5.2 UVM Scoreboard 18              | $5.2.2 \ nfc2\_r2t\_agent \ \mathrm{and}$             |

| 3.5.3 UVM Driver 18                  | $nfc2\_sequencer$                                     |

| 3.5.4 UVM Monitor 18                 | $5.2.3 \ nfc2\_driver \dots 38$                       |

| 3.5.5 UVM Agent 19                   | $5.2.4 \ nfc2\_r2t\_monitor \dots 38$                 |

| A Bibliography                                                                                                         | 57 |

|------------------------------------------------------------------------------------------------------------------------|----|

| Appendices                                                                                                             |    |

| 7 Conclusions                                                                                                          | 53 |

| 6.4 DUT error detection                                                                                                | 50 |

| 6.3 Coverage sampling                                                                                                  | 50 |

| 6.2.7 Negative scenarios                                                                                               | 48 |

| $6.2.6 \; SDD\_REQ \; \text{for all valid}$ $NFCID1 \; \text{and} \; SEL\_PAR$ $\text{combinations} \dots \dots \dots$ | 48 |

| 6.2.5 SECTOR SELECT command packets 1 and 2                                                                            | 47 |

| 6.2.4 SLEEP_REQ command execution                                                                                      | 46 |

| 6.2.3 Transition to $ACTIVE\_A$ state and testing lock bits                                                            |    |

| 6.2.2 Transition to $ACTIVE\_A$ state and writing data to Data blocks .                                                |    |

| 6.2.1 Transition to $ACTIVE\_A$ state and reading the whole memory                                                     |    |

| 6.2 Example testcases                                                                                                  | 42 |

| 6.1 Creating and starting sequence .                                                                                   | 41 |

| 6 Implemented UVC<br>demonstration                                                                                     | 41 |

| 5.2.7 nfc2_scoreboard                                                                                                  | 40 |

| 5.2.6 nfc2_tag_model                                                                                                   | 39 |

| nfc2_t2r_monitor                                                                                                       | 39 |

| $5.2.5 \text{ nfc2}\_\text{t2r}\_\text{agent and}$                                                                     |    |

# **Figures**

| 2.1 Modified Miller with 100 % ASK                             |    |

|----------------------------------------------------------------|----|

| [1]                                                            | 9  |

| 2.2 Manchester coding with OOK [1].                            | 9  |

| 4.1 Type 2 Tag Platform State  Machine [1]                     | 27 |

| 5.1 System level of implemented testbench                      | 36 |

| 6.1 Transition to $ACTIVE\_A$ state and first $READ$ command   | 43 |

| 6.2 Issuing <i>READ</i> with higher block number               | 43 |

| 6.3 Captured <i>NACK</i> response                              | 43 |

| 6.4 Predicted <i>NACK</i> response                             | 44 |

| 6.5 Scorebord validation UVM info.                             | 44 |

| 6.6 Successful WRITE command to block 7.                       | 44 |

| 6.7 Validation of the previous $WRITI$ command with the $READ$ |    |

| command                                                        | 45 |

| 6.8 Issuing WRITE with higher block number                     |    |

| 6.9 Issuing WRITE with block numbe 0                           |    |

| 6.10 Issuing WRITE for previously locked block                 | 47 |

| 6.11 Issuing logic 0 for irreversible static lock bit          | 47 |

| 6.12 SLEEP_REQ command verification                            | 47 |

| 6.13 SECTOR SELECT command                                              |    |

|-------------------------------------------------------------------------|----|

| packets verification                                                    | 48 |

| 6.14 SEL_REQ without CRC16                                              | 48 |

| $6.15 \ SEL\_REQ$ with invalid CRC16.                                   | 49 |

| 6.16 SDD_REQ with invalid parity bits                                   | 49 |

| 6.17 $SDD\_REQ$ issued before allowed $FDT_{POLL,A}$ time               |    |

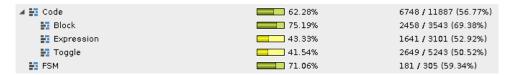

| 6.18 Code coverage report after the current set of the test cases       | 50 |

| 6.19 Functional coverage report after the current set of the test cases | 50 |

| 6.20 DUT error detection in SDD_RES                                     | 51 |

# **Tables**

| 2.1  NFC Type  2  Commands  [1] [2].                         | 11 |

|--------------------------------------------------------------|----|

| 2.2 $FDT_{POLL,A,MAX}$ values for $READ, WRITE$ and $SECTOR$ |    |

| SELECT [1]                                                   | 13 |

| 4.1 Requirements - physical layer                            | 24 |

| 4.2 Requirements - Timing specifications                     | 25 |

| 4.3 Requirements - Commands coverage and scenarios           | 28 |

# 0.1 List of Abbreviations

ACK Acknowledgement

ASIC Application Specific Integrated Circuit

**ASK** Amplitude Shift Keying

**CC** Capability Container

CRC Cyclic Redundancy Check

**CDV** Coverage Driven Verification

**DUT** Device Under Test

**EoF** End of Frame

**FDT** Frame Delay Time

GUI Graphics User Interface

**ISO** International Organization for Standardization

MDV Metric Driven Verification

NACK Negative Acknowledgement

**NDEF** NFC Data Exchange Format

**NFC** Near Field Communication

FPGA Field Programmable Gate Array

OOK On/Off Keying

**RFU** Reserved for Future Use

RTL Register Transfer Level

**SoF** Start of Frame

TB Testbench

**UVC** Universal Verification Component

UVM Universal Verification Methodology

# Chapter 1

# Introduction

Designing digital circuits is a process with many steps on different level of abstraction. In the beginning the whole scope of work must be defined. Project team has to choose a target technology - whether Field Programmable Gate Array (FPGA) or Application Specific Integrated Circuit (ASIC) will be used. Also other aspects of the project are specified, like required features, way of their implementation, supply voltage, design interface and other factors.

After the specification is complete, a team of digital designers creates Register Transfer Level (RTL) code according to the specification, mostly in VHDL or Verilog hardware description language. The correct behaviour of the design should be verified from the beginning of RTL code creation in order to detect as many bugs as possible. To achieve this, RTL design is inserted into testbench environment, where the set of various test cases is performed.

Latest major verification methodology used for digital designs is called Universal Verification Methodology (UVM), which should be suitable for every type of digital circuit. Using UVM promises efficient way of verifying digital designs independently of simulation platform.

This master's thesis describes all important steps during the design of complete verification solution in cooperation with ASICentrum company, design center of EM Microelectronic and part of the Swatch Group. EM Microelectronic focuses on ultra-low power ASICs for industry use, traceability, logictics and wearables. One of the implemented wireless communication protocols is NFC, namely NFC Type 2 Tag Platform specification, and this paper deals with this particular protocol.

The main goal is to develop Universal Verification Component (UVC) for

1. Introduction

NFC Type 2 Tag Platform using UVM library. That way the verification component will be compliant with the latest ASICentrum verification flow and could be inserted into new testbenches to verify new digital designs. Besides that, the understanding of technical documentation together with practical UVC implementation is a great practice for the future verification engineer position.

Created UVC will be evaluated by testing already designed and verified NFC Type 2 Tag logic core from ASICentrum. In order to fullfill this task, all of the necessary information is gathered, therefore the first two chapters cover teoretical background of given task - characteristics of NFC Type 2 Tag Platform and UVM library fundamentals.

The next chapters describe the proposed verification plan for the NFC Type 2 Tag Platform, created verification environment and each UVM component inside the environment. UVC functionality is then demonstrated with ASICentrum logic core with the set of constrained-random written test cases and designed UVC is evaluated.

Part I

**Theoretical Part**

# Chapter 2

# **Near Field Communication**

Wireless comunnication is a major technological trend mainly due to the ability to enable more comfortable connections between electronic devices. One of already well established technologies is Near Field Communication (NFC). NFC is promoted by non-profit association - The NFC Forum, and provides short-range and secure comunnication between NFC Devices, which may operate in 3 modes [3] [4].

The first mode is called Card emulation mode. NFC Device in Card emulation mode acts as a smart card, thus permitting payments for services and goods through communication with an external reader [4]. Another mode is Peer-to-Peer Mode, enabling NFC devices to exchange various data, for example contact information or WiFi passwords. The last mode's name is Reader/Writer Mode, in which one NFC Device's (labeled as reader) role is to read information from the passive NFC Devices - NFC Tags [3].

NFC Forum specifies 5 different types of NFC Tags, each of them is suited for a specific purpose and price range [5]. Main goal of this thesis is to create verification component for Type 2 Tag Platform, therefore only this NFC Forum Platform is described in more detail.

# 2.1 Type 2 Tag Platform

Type 2 Tag uses a particular technology subset of NFC-A Technology including anticollision and it is based on ISO 14443-3 A standard. [6] The device that starts the communication - NFC Forum Device in Poll Mode, transmits electromagnetic field of frequency 13.56 MHz ( $f_c$ ). NFC Tag (also named NFC Forum Device in Listen Mode) detects this field and responds to NFC

Commands according to its own internal state. Both the reader and the tag communicate with each other using the same bitrate  $106 \ kbaud/s$  and the period of one bit is therefore [1]

$$per_{bit} = \frac{128}{f_c} = \frac{128}{13.56 \ MHz} \cong 9.44 \ \mu s.$$

### 2.1.1 Memory structure

Type 2 Tag memory structure depends on the memory size of the tag. If the memory size is equal to 64 bytes, a static memory structure is used. Otherwise, if the memory size is bigger than 64 bytes, a dynamic memory structure is appplied to Tag memory.

Both structures are divided into blocks and each block contains 4 bytes. Static and dynamic structure also share basic memory fields:

- Internal: reserved for manufacturer use

- Lock: static lock bytes, their purpose is to switch between READ/WRITE and READ-ONLY States

- CC: Capability Container, manages the information of the Type 2 Tag Platform

- Data: available area for information storage. TLV blocks may be stored here block of 1 to 3 fields. One byte T field specifies a type of TLV, one or three bytes long L field defines the size in bytes of the value field, and V field may store values. If the L field is equal to 00h or there is no L field, the V field is not present.

Dynamic memory structure also has dynamic lock bytes and reserved bytes, located between or at the end of the data. Complete description of the memory structure can be found in [2].

# 2.1.2 Sequence schemes

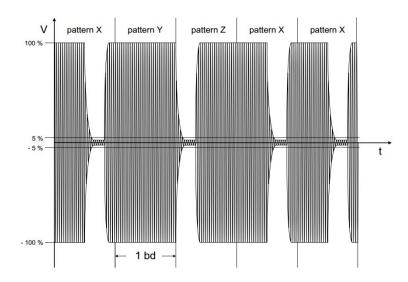

NFC Reader issues a command to NFC Tag by pausing the carrier transmission for a defined time  $t_1 = 2 - 3.4 \mu s$ , also called  $V_2$ . This way 3 particular patterns are created, (see Figure 2.1). Pattern X has  $V_2$  after the half duration of one bit, pattern Y has no modulation throughout the bit duration and in pattern

Z  $V_2$  must occur at the beginning of current bit. This mechanism is known as Modified Miller coding with Amplitude Shift Keying (ASK) 100 % [1] [7].

Figure 2.1: Modified Miller with 100 % ASK [1].

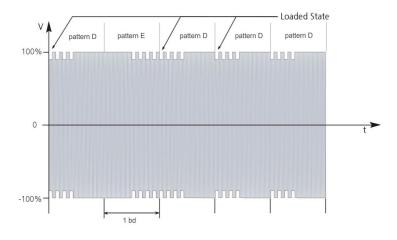

NFC Tag - Device in Listen mode, modulates the analog signal by Manchester coding with On/Off Keying (OOK) subcarrier modulation (see Figure 2.2). With OOK modulating subcarrier (subcarrier frequency  $f_c/16$ ) 3 patterns are defined - D, E and F. In pattern D the subcarrier modulates the carrier for the first half of the bit duration, while in the second half modulation must not occur. Pattern E has a modulated carrier by the subcarrier for the second half of the bit duration and pattern F has no subcarrier modulation during its whole bit duration [1].

Figure 2.2: Manchester coding with OOK [1].

# 2.1.3 Bit level coding

Patterns mentioned in Section 2.1.2 are used to code two logical levels - logic 0 and logic 1. NFC Forum Device uses these patterns as it is stated here

```

pattern X logic 1,

pattern Y logic 0,

```

**pattern Z** during two or more contiguous logic 0, pattern Z is used from the second logic 0, pattern Z is also used as Start of Frame (SoF, see 2.1.4) [1].

NFC Type 2 Tag codes his response as follows:

```

pattern D logic 1, SoFpattern E logic 0 [1].

```

#### 2.1.4 Frame format

Commands and responses of NFC Devices are encapsulated within the frames, which group data bits together with addition of SoF and End of Frame (EoF). NFC-A Technology defines three types of frames - short frame, standard frame, and bit-oriented SDD frame [1] [8].

The short frame is used for initiating the communication. It consists of SoF, maximum of 7 data bits, and EoF. The short frame does not use parity protection [1].

The standard frame sends more than one data bytes and adds odd parity protection at the end of each one. Data bytes are limited from the start with SoF and with EoF at the end [1].

The bit-oriented SDD frame is used for solving collision. It is derived from the standard frame with 7 data bytes split up into 2 parts. Part 1 is sent by NFC Device in Poll Mode and part 2 by NFC device in Listen Mode. Complete description of this frame is located in [1].

### 2.1.5 Commands and responses

Table 2.1 lists all the commands available for NFC Forum Type Tag 2 Platform. For each command additional information are stated - command code and the frame type.

| NFC Type 2 | Command               | Dognanga           | Frame Type         |

|------------|-----------------------|--------------------|--------------------|

| Command    | $\operatorname{code}$ | Response           | $\mathrm{cmd/res}$ |

| SENS_REQ   | 26h                   | SENS_RES           | short/standard     |

| ALL_REQ    | 52h                   | SENS_RES           | short/standard     |

| SEL_REQ    | 9xh                   | SEL_RES            | standard           |

| SDD_REQ    | 9xh                   | SDD_RES            | bit oriented       |

| SLEEP_REQ  | 50h 00h               | -                  | standard           |

| READ       | 30h                   | READ/NACK response | standard           |

| WRITE      | A2h                   | ACK/NACK response  | standard           |

| SECTOR     | C2h                   | ACK/passive        | standard           |

| SELECT     | 0211                  | ACK/NACK           | Standard           |

**Table 2.1:** NFC Type 2 Commands [1] [2]

SENS\_REQ and ALL\_REQ commands are used for detecting NFC Forum Type 2 Devices in Listen Mode. Difference between these commands is Type 2 Tag responds to ALL\_REQ in SLEEP\_A state (see Figure 4.1) [1] [6].

SDD\_REQ is used for resolving the collision (whether more than one device is in Operating Field of NFC Forum Device in Poll Mode). SDD\_REQ also serves for obtaining NFCID1 of an NFC Forum Device in Listen Mode [1] [6].

SEL\_REQ selects the NFC Forum Device in Listen Mode according to sent NFCID1 of length 4 bytes. These 4 bytes are additionally protected with BCC byte - calculated as exclusive-or checksum [1] [6].

Issued *SLEEP\_REQ* command puts NFC Forum Device in Listen Mode to *SLEEP\_A* state. NFC Forum Device in Listen Mode must not respond to this command and NFC Forum Device in Poll mode must always consider this command to be executed properly [1] [6].

READ command consists of the command code 30h and one parameterblock number (BNo). Response from the NFC Type 2 Tag Platform is 16 bytes long payload of data, which means 4 concurrent blocks are returned to NFC Forum Device in Poll Mode. In case of error, Type 2 Tag Platform responds with NACK response [2].

NFC Forum Device in Poll Mode may also write data to Type 2 Tag Platform by issuing WRITE command. Only the whole block is written with one WRITE command,. If the WRITE command is executed successfully, the Acknowledgement (ACK) response is returned to NFC Device in Poll Mode. Otherwise, the Negative Acknowledgement (NACK) response is returned [2].

The last command in command set of this platform is SECTOR SELECT, which is designated for physical memories bigger than 1 KB - is used to switch between 1 KB big sectors. The SECTOR SELECT command is issued with 2 separated packets. The goal of the first packet is to get information whether memory is actually bigger than 1 KB. In that case ACK response is issued by the Type 2 Tag Platform. If the memory is smaller, NACK response is returned. After ACK response the second packet is transmitted with specific sector number and three Reservedf for Future Use (RFU) bytes (00h). If the sector number is inside the available memory, no further response is issued this is called passive ACK Response. If the sector number is outside of the available memory, NACK response is sent back to NFC Forum in Poll Mode [2].

#### 2.1.6 Timing requirements

When it comes to meeting the timing requirements, three important time constants must be fullfilled for NFC Type 2 Tag platform communication. The first one is The Frame Delay Time Poll  $\rightarrow$  Listen, defining the interval in which Listen Frame is allowed to be sent by values  $FDT_{A,LISTEN,MIN}$  and  $FDT_{A,LISTEN,MAX}$  [1].

If sent command is  $ALL\_REQ$ ,  $SENS\_REQ$ ,  $SDD\_REQ$  or  $SEL\_REQ$ ,  $FDT_{A,LISTEN,MIN}$  equals  $FDT_{A,LISTEN,MAX}$  and Listen Frame has to be sent at specific point in time.  $FDT_{A,LISTEN,MIN}$  value depends on the logic value of the last data bit - on the position of the last  $V_2$  pulse.  $FDT_{A,LISTEN}$  then takes values according to:

$$FDT_{A,LISTEN} = n * 128/f_c + x/f_c$$

where x depends on the last logic bit and n depends on the command, which

| Parameter             | Value  |

|-----------------------|--------|

| $FDT_{T2T,READ,MAX}$  | 5  ms  |

| $FDT_{T2T,WRITE,MAX}$ | 10  ms |

| $FDT_{T2T,SL,MAX}$    | 1 ms   |

**Table 2.2:**  $FDT_{POLL,A,MAX}$  values for READ, WRITE and SECTOR SELECT [1]

is being sent - for previously mentioned groups of commands ( $ALL\_REQ$ ,  $SENS\_REQ$ ,  $SDD\_REQ$  and  $SEL\_REQ$ ) its value is 9, for all other commands it is equal or bigger than 9 [1].  $FDT_{A,LISTEN}$  must be respected by Tag with tolerance from  $-1/f_c$  to  $0.4 \ \mu s + 1/f_c$  [1] [6]. READ, WRITE and  $SECTOR\ SELECT$  commands have their own defined  $FDT_{A,LISTEN,MAX}$  values, listed in Table 2.2 [1].

$FDT_{A,LISTEN}$  time also contains two smaller time intervals, both with its own meaning. From the end of the Poll Frame (beginning of the  $FDT_{A,LISTEN}$  time), NFC Forum Device must ignore any response from NFC Device in Listen mode during a time  $FDT_{A,LISTEN,MIN} - 128/f_c$ . Also NFC Device in Listen Mode cannot produce any disturbance before sending a response in time for at least [1]

$$t_{nn,min} = FDT_{A,LISTEN} - (FDT_{A,LISTEN,MIN} - 128/f_c).$$

NFC Forum Device in Poll Mode after the reception of a Listen Frame has to wait certain time, before it sends a new Poll Frame. This time is  $FDT_{A,POLL,MIN}$ , and it depends on the logic value of the last data bit. That means  $FDT_{A,POLL}$  measurement starts from the end of subcarrier's last modulation. This time constant value is not divided into discrete values as  $FDT_{A,LISTEN}$  is, it is limited from one side only and the minimum value is  $1172/f_c$ .

The last requirement is applied to NFC Forum Device in Listen Mode, which must be able to receive initiating commands  $ALL\_REQ$  or  $SENS\_REQ$  after so-called guard time  $GT_A$  of unmodulated carrier. Value of this parameter for NFC-A Technology is 5ms [1].

# 2.1.7 NFC Data exchange format - NDEF

NFC Data Exchange Format (NDEF) is lightweight binary message format for encapsulation of one or more payloads with arbitrary size and type into one message construct. NDEF Message is located in Data Area of Memory Structure, more specifically in NDEF Message TLV block (TLV block with 03h T field value, see Section 2.1.1) [9] [10].

Options of managing NDEF Message are obtained by reading Capability Container (CC). The CC is located in the block 3 of the memory structure (both static and dynamic). The CC can also be written with WRITE command. Using this command the current content of the CC is bit-wise "OR-ed" with 4 data bytes from WRITE command. By this mechanism if a bit is set to logic 1, a change to logic 0 is not possible [2].

Every CC byte has its specific use. Byte 0 should be equal to E1h (so-called magic number), indicating NFC Forum defined data is stored in data area. Byte 1 determines the version number of NFC Type 2 Tag Operation Specification document. Byte 2 specifies memory size in number of 8 bytes and byte 3 indicates read and write access capability of data and CC area [2].

Based on values in the CC and correct presence of NDEF Message TLV in data area (for example L field value is equal to 0), NFC Forum Device might detect the NDEF presence, read the NDEF message using *READ* command or write NDEF message inside NDEF Message TLV with *WRITE* command. If the data to be read or written exceeds the current sector, switch to another sector shall be made with *SECTOR SELECT* command [2].

#### 2.1.8 Anticollision

At first, to be able to handle the situation like the collision, it has to be defined as a phenomenom. Collision happens in case, when more than one NFC Type 2 Tag are responding to  $SDD\_REQ$  command. In that case, the data part of  $SDD\_RES$  response will differ at some point and anticollision loop should be applied. In general concept is simple - sending  $SDD\_REQ$  command with the part of NFCID1 that was already successfully received until the complete NFCID1 is stored in NFC Forum Device. After the whole NFCID1 reception that NFC Type 2 Tag is put to sleep with  $SLEEP\_REQ$  and NFC Forum Device tries to get NFCID1 from another NFC Type 2 Tag in the field [11].

# Chapter 3

# Digital design verification and UVM

In general the goal of verification process is to make sure the simulated device completes its task according to the specification. Digital verification has been evolving very quickly together with digital circuits design and because of rapid design complexity, the growth of digital verification has to keep up. Modern hardware verification language needs to model structures also at higher abstraction levels and more similar approach like software programming can be used, because verification modules do not have to be synthesizable [12] [13].

At around 15 years ago, many languages were used for digital circuits verification, like Vera and e, but currently the most used language is SystemVerilog. SystemVerilog is based upon Verilog with addition of objected-oriented programming constructs and is IEEE standard since 2005 [12].

First of all, to make the job for verification engineers the most intuitive and their results reusable, each main EDA vendor developed their own methodology for customers using their own tools. The first widely used methodology named Verification Methodology Manual (VMM) had been created by Synopsis, later Mentor Graphics and Cadence introduced Open Verification Methodology (OVM) [13] [14].

These standards along with many others had formed a strong foundation of knowledge and experience, which eventually led to the creation of Universal Verification Methodology (UVM). UVM is derived mostly from OVM, but also uses elements from other standards. Its development is in charge of Accelera Systems - a nonprofit independent organization composed of EDA vendors such as Cadence, Mentor, Synopsis etc [15].

Therefore UVM as an open-source library is widely supported by every

major simulation software and is aiming to be the methodology suited for every type of digital design, in regards of size, target technology and design type orientation. However, to reach an efficient level of verifying logic designs, small subset of UVM is really needed. The most important parts are described in the following subsections [16] [13]. At the end of this chapter in Section 3.6 term coverage is defined, so it could be used later in creating complete verification component.

# 3.1 UVM testbench basics

UVM Testbench is constructed in layered, object-oriented way, which empowers division of work to be done. Modular architecture specifies functions each component is responsible for and that also enables easy reusability [13].

The lowest layer is RTL (or gate-level) description of a Device Under Test (DUT), which communicates with transactor layer through pin-level activity on one or more virtual interfaces. Transactor layer contains monitors and drivers and serves as a conversion layer between the pin-level signals and the transactions. These transactions are then passed on to testbench layer above, which controls the flow of the test and generates input stimulus [13].

All the modules are connected between themselves and encapsulated within one UVM Environment, which is configured and built in UVM Test. UVM Test is therefore the starting point for the build process and apart from the building and configuring environment its job is to specify and apply the constrained-random stimulus [13].

UVM Components in UVM Testbench are instances of UVM Classes, which are derived from *uvm\_component class*. These components are part of the testbench hierarchy for the whole duration of the test, while sequences are not (they are extended from *uvm\_sequence class*). UVM also implements a lot of other classes and macros, for example useful UVM messaging system, which displays messages in consistent format inside UVM testbench, and much more (see [17]).

# 3.2 UVM Factory

The UVM Factory creates UVM objects and components and enables to substitute them by derived objects and components without changing the testbench structure. This way the change of sequence behaviour can be changed, or component might be replaced by its newer version [13] [18].

Proper coding must be followed to ensure factory functionality. Firstly, components and object are registrated with corresponding registration macros 'uvm\_component\_utils and 'uvm\_object\_utils. The next step is to use a factory constructor with constructor defaults. Subsequently, components are created during the build phase with create() method [13] [18].

# 3.3 UVM Configuration Database

Components and objects may share resources between themselves (by resource is meant any piece of information), and recommended way do to that is  $uvm\_config\_db$ .  $uvm\_config\_db$  accesses resource database by using two simple methods -  $uvm\_config\_db$ ::set and  $uvm\_config\_db$ ::get. There are no limitations on the type of information, and classic examples of using  $uvm\_config\_db$  are passing virtual interfaces from DUT domain to the test and passing configuration objects through the testbench hierarchy [17] [13].

# 3.4 UVM Phases

UVM uses phases to ensure consistent execution flow, and they can be divided into three main groups. UVM phase execution starts by calling  $run\_test()$  method usually from the inside of the top module block. The job of the first group of phases - build phases, is to construct, configure and connect the testbench component hierarchy.

After build phases follow run time phases, in which stimulus is generated and applied to DUT. There are also parallel run-time phases, which are executed together with run phase and allow to specify task execution in time more precisely. In the end information from scoreboards need to be extracted and evaluated, and this task is reserved for clean up phases. During the clean up phases no simulation time need to be used, therefore they are implemented

as functions [13].

# 3.5 UVM Environment

UVM Environment encapsulates all the verification components targeting the DUT, usually they are configurable through data passed from  $uvm\_config\_db$  [17].

### 3.5.1 UVM Sequencer and Sequences

The UVM Sequencer works at testbench layer and controls the flow of UVM Sequence items generated by one or more UVM Sequences to UVM Driver. Sequences are objects that have necessary information for generating stimulus. Unlike the UVM Sequencer, there are not part of the testbench hierarchy, and can be described as a transient object. This means after sequence execution it can be discarded and testbench moves on to next step of UVM Test [13].

#### 3.5.2 UVM Scoreboard

The UVM Scoreboard collects the input and output sequences of DUT through the UVM Agents analysis ports and checks if the DUT behaviour is correct. The check is done by comparison of DUT response and expected output generated by a reference model implemented in the testbench [17].

#### 3.5.3 UVM Driver

Inputs to DUT are on a pin-level basis, that means the transactions passed from the UVM Sequencer must be converted to be able to communicate with DUT via a virtual interface. Drive can also act as a "responder" - it reacts to pin-level activity in the virtual interface and passes the information to the sequence, which then sends a response transaction back to the driver to complete the communication [17] [13].

#### 3.5.4 UVM Monitor

The UVM Monitor has a reverse task as a driver in the testbench - it converts pin-level activity back to transactions. Homewer, the monitor behaviour

should be passive only and cannot affect the DUT in any way. A monitor just samples the DUT activity and passes the recognized transactions to the other parts of the testbench. To do so, a monitor must implement protocol rules and look for recognizable patterns in the virtual interface [13].

# 3.5.5 **UVM Agent**

All UVM Components dedicated to one logical interface (for example USB) are grouped within one hierarchical component - the UVM Agent. A common UVM Agent consists of an UVM Driver, an UVM Monitor and an UVM Sequencer, but might also contain some other components, for example coverage collector [17].

# 3.6 SystemVerilog Coverage

Coverage should be the part of designed Universal Verification Component (UVC), therefore it is important to explain its purpose. It can be defined as percentage of verification objectives that have been covered. Basically, the coverage measures tested and untested parts of the design [19].

Two types of coverage may be used. The first one is called code coverage, which measures amount of the code in the design (blocks, lines, state machines) that is tested. Code coverage is measured by simulator and the collection needs to be turned on during the configuration of simulation run [19].

Functional coverage is manually implemented by verification engineer and measures the amount of design specification that is already tested. [20] [19]. Functional coverage uses SystemVerilog covergroup construct and can be collected using one common component in the testbench or inside the component where the data are present.

Coverage is used as a central part of CDV - Coverage Driven Methodology. This approach uses test cases only to steer the contrained random sequences toward 100 % coverage. The coverage is therefore the main measure of successful execution of the verification plan, which results in better traceability [21]. CDV approach was later improved by Cadence and labeled by name Metric Driven Verification (MDV). It is based on metrics collections and can be divided into 4 steps executed continuously until the verification is complete [22].

These 4 steps are:

**plan** creation of the verification plan, a document specifying the requierements and way of verifying them,

construct implementation of the verification environment,

execute all the test cases are run and results are checked,

measure and analyze coverage data are mapped to the verification plan and results are analyzed. Cadence has its own tool called vManager, which can fire the regression and directly correlate results with the verification plan [22] [23].

Part II

**Practical Part**

# Chapter 4

# Verification plan

Verification plan proposal is the first step in creating well structured and reliable verification component. In the following sections of this chapter each aspect of UVC preparation will be described. As it was previously stated, verification component is implemented by using SystemVerilog language and Universal Verification Methodology.

# 4.1 Requirements

List of requirements has to include all the rules from the design and standards specifications that should be covered by verification. Well written requirements list is therefore an essential part of verification process. Requirements for covering NFC Type 2 Tag platform are based on all NFC specifications [1] [7] [2] [11] together with original ISO 14443 standards, namely [8] and [6].

Requirements are divided into 5 main groups, each requirement has its own description, origin, priority and method, which is used for covering the requirement. This can be done by checker, test case, coverage points or by their combination.

# 4.1.1 Physical layer requirements

First group of requirements Table 4.1 covers physical aspects of communication, which DUT must follow. This group is solely covered by assertions in  $nfc2\_t2r\_monitor$  component, which decodes the response from DUT. Physical layer has the highest priority to be verified.

4. Verification plan

| Requirement        | Specification     | Priority | Checkers/ Coverage/ Scenario (CH/CV/SC) |

|--------------------|-------------------|----------|-----------------------------------------|

|                    | NFC Digital 4.1.2 |          | СН                                      |

| HF_PHY_T2R_1       | NFC Digital 4.1.4 | 1        |                                         |

| 111 _1 111 _121(_1 | NFC Digital 4.2.2 |          |                                         |

|                    | NFC Digital 4.    |          |                                         |

| HF_PHY_T2R_2       | Digital 4.1.2     | 1        | СН                                      |

|                    | NFC Digital 4.1.4 |          |                                         |

|                    | NFC Digital 4.2.2 |          |                                         |

|                    | NFC Digital 4.    |          |                                         |

| HF_PHY_T2R_3       | NFC Digital 4.1.2 | 1        | СН                                      |

|                    | NFC Digital 4.1.4 |          |                                         |

|                    | NFC Digital 4.2.2 |          |                                         |

|                    | NFC Digital 4.    |          |                                         |

**Table 4.1:** Requirements - physical layer

# HF\_PHY\_T2R\_1

Verify that for each response DUT uses OOK  $f_s$  subcarrier modulation with Manchester coding, with  $f_s = f_c/16 \cong 847.5 kHz$  [1].

# HF\_PHY\_T2R\_2

Verify that each DUT response frame starts with SoF sequence and ends with EoF sequence [1].

# HF\_PHY\_T2R\_3

Verify that standard and bit oriented SDD frames contain correct odd parity and particular responses (SEL\_RES, READ\_RES) have valid end of data field (EoD - CRC16) [1].

### 4.1.2 Timing requirements

Another aspect of DUT behaviour is following timing specifications from Table 4.2. These rules also have the highest priority and each is covered by checkers.

| Requirement  | Specification    | Priority | Checkers/ Coverage/ Scenario CH/CV/SC |

|--------------|------------------|----------|---------------------------------------|

| HF_PHY_T2R_4 | NFC Digital 4.10 | 1        | СН                                    |

| HF_PHY_T2R_5 | NFC Digital 4.10 | 1        | СН                                    |

| HF_PHY_T2R_6 | NFC Digital 9.9  | 1        | СН                                    |

| HF_PHY_T2R_7 | NFC Digital 9.9  | 1        | СН                                    |

| HF_PHY_T2R_8 | NFC Digital 9.9  | 1        | СН                                    |

**Table 4.2:** Requirements - Timing specifications

# HF\_PHY\_T2R\_4

DUT shall not produce any disturbance during at least  $t_n n_m in$  time to  $t_n n$  time before the response start. Value of  $t_n n_m in$  differs for possible last bits [1]. Detectable disturbance is not defined in this standard, but for digital output signal of DUT is no change on output allowed besides DUT response to command. That is why this requirement is covered by  $nfc2\_r2t\_monitor$  structure, which does not allow any unknown patterns and always tries to create a  $nfc2\_base\_res$  item, otherwise it reports ' $uvm\_error$ .

#### HF\_PHY\_T2R\_5

DUT shall send the response at time  $FDT_{A,LISTEN,MIN}$  time or after - this depends on the type of command and last  $V_2$  modulation. For group of commands - ALL\_REQ, SENS\_REQ, SDD\_REQ, SEL\_REQ response must be sent at specific point in time equal to  $FDT_{A,LISTEN,MIN}$  with tolerance of  $-1/f_c to(0.4\mu s + 1/f_c)$ , where

$$FDT_{A,LISTEN,MIN,log,0} = n * (128/f_c) + 20/f_c = 1172/f_c, where n = 9,$$

$FDT_{A,LISTEN,MIN,log,1} = n * (128/f_c) + 84/f_c = 1236/f_c, where n = 9.$

Correct  $FDT_{A,LISTEN}$  time for each command is verified by checkers in

4. Verification plan

$nfc2\_scoreboard.$

# HF\_PHY\_T2R\_6

For READ command response must be sent after  $FDT_{A,LISTEN,MIN}$  from HF\_PHY\_T2R\_5 and at least 5 ms from the last  $V_2$  mod, while n must be integer value equal or higher than 9. This requirement is verified with checker inside  $nfc2\_scoreboard$ .

# HF\_PHY\_T2R\_7

For WRITE command response must be sent after  $FDT_{A,LISTEN,MIN}$  from HF\_PHY\_T2R\_5 and at least 10 ms from the last  $V_2$  mod, while n must be integer value equal or higher than 9. This requirement is verified with checker inside nfc2 scoreboard.

# HF\_PHY\_T2R\_8

SECTOR SELECT response must be sent after  $FDT_{A,LISTEN,MIN}$  from HF\_PHY\_T2R\_5 and at least 1 ms from the last  $V_2$  mod, while n must be integer value equal or higher than 9. This requirement is verified with checker inside nfc2 scoreboard.

# 4.1.3 Tag state requirements

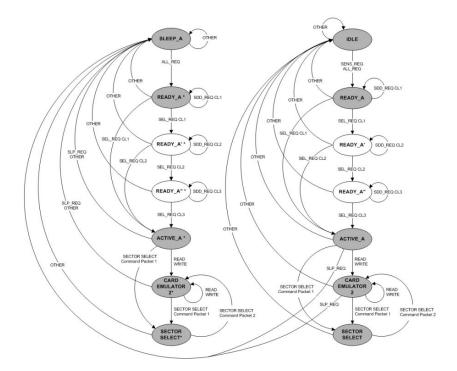

Third group defines DUT behaviour in each state from NFC Type 2 Tag Platform State Machine. For verification of this group combination of cross coverage and directed test cases shall be used. These requirements have priority 2, which means they should be verified, but will be implemented after priority 1 requirements. Due to the larger required space, the table for these requirements is omitted, but all requirements are derived from Figure 4.1 and each Tag state has its own requirement [2].

#### 4.1.4 Commands requirements

Response of DUT for each command needs to be verified from logical standpoint. This is implemented by modeling Tag behaviour and predicting the response according to the current state of the Tag derived from Figure 4.1. This

Figure 4.1: Type 2 Tag Platform State Machine [1].

predicted item is later compared to captured item from  $nfc2\_t2r\_monitor$  in the  $nfc2\_scoreboard$  by using checkers.

Every command has one requirement, in which correct response has to be verified in the proper state. These requirements are not present in Table 4.3. The requirements in Table 4.3 cover command variable fields and special scenarios.

#### HF\_SDD\_REQ\_2

Verify DUT response for each valid combination of  $SEL\_PAR$ , NFCID1 and CL fields in  $SDD\_REQ$  command.

#### HF\_SDD\_REQ\_3

Verify that DUT ignores  $SDD\_REQ$  command with invalid combination of  $SEL\_PAR$  and NFCID1 fields and transitions to  $IDLE/SLEEP\_A$  state.

4. Verification plan • • • •

| Requirement  | Specification                    | Priority | Checkers/ Coverage/ Scenario CH/CV/SC |

|--------------|----------------------------------|----------|---------------------------------------|

| HF_SDD_REQ_2 | NFC Digital 4.7                  | 2        | CV/SC                                 |

| HF_SDD_REQ_3 | NFC Digital 4.7                  | 2        | SC                                    |

| HF_SDD_REQ_4 | NFC Digital 4.7                  | 2        | SC                                    |

| HF_SEL_REQ_2 | NFC Digital 4.8                  | 2        | SC                                    |

| HF_SEL_REQ_3 | NFC Digital 4.8                  | 2        | SC                                    |

| HF_SLP_REQ_1 | NFC Digital 4.9                  | 2        | SC                                    |

| HF_READ_2    | NFC Type 2 Op.<br>Spec. 5.1, 5.4 | 2        | CV/SC                                 |

| HF_WRITE_2   | NFC Type 2 Op.<br>Spec. 5.2, 5.4 | 2        | SC                                    |

| HF_WRITE_3   | NFC Type 2 Op.<br>Spec. 5.2, 5.4 | 2        | SC                                    |

| HF_WRITE_4   | NFC Type 2 Op.<br>Spec. 5.2, 5.4 | 2        | SC                                    |

| HF_SEC_S_1   | NFC Type 2 Op.<br>Spec. 5.3, 5.4 | 2        | СН                                    |

| HF_SEC_S_2   | NFC Type 2 Op.<br>Spec. 5.3, 5.4 | 2        | SC                                    |

**Table 4.3:** Requirements - Commands coverage and scenarios

### HF\_SDD\_REQ\_4

Verify that DUT ignores  $SDD\_REQ$  command with higher CL field than it actually contains and transitions to  $IDLE/SLEEP\_A$  state.

#### HF\_SEL\_REQ\_2

Verify that DUT ignores  $SEL\_REQ$  command with higher CL field than it actually contains and transitions to  $IDLE/SLEEP\_A$  state.

#### HF\_SEL\_REQ\_3

Verify that DUT ignores  $SEL\_REQ$  command with incorrect NFCID1 field for each CL field and transitions to  $IDLE/SLEEP\_A$  state.

#### HF\_SLP\_REQ\_1

Verify successfull  $SLP\_REQ$  command execution by issuing  $SENS\_REQ$  and  $ALL\_REQ$  sequence. DUT shall not respond to  $SENS\_REQ$  but shall respond to  $ALL\_REQ$  and shall transition to  $READY\_A*$  state.

#### HF\_READ\_2

Verify that DUT sends *NACK* response for *READ* command with block number out of memory space and transitions to *IDLE/SLEEP\_A* state.

#### HF\_WRITE\_2

Verify that DUT sends NACK response for WRITE command with block number out of memory space and for blocks 0 and 1 (read-only blocks) and transitions to  $IDLE/SLEEP\_A$  state.

#### HF\_WRITE\_3

Verify that DUT locks correct Data blocks from Static Memory Structure after WRITE command to block 2.

#### HF\_WRITE\_4

Verify that blocks 2 and 3 are irreversible after WRITE command - after the write of logic 1 cannot be changed back to logic 0.

#### HF\_SEC\_S\_1

Verify that DUT issues NACK response after SECTOR SELECT command packet 1 in  $ACTIVE\_A/CARD\_EMULATOR\_A/ACTIVE\_A*/$   $CARD\_EMULATOR\_A*$  states and transitions to  $IDLE/SLEEP\_A$  state.

4. Verification plan

#### HF\_SEC\_S\_2

Verify that DUT ignores  $SECTOR\ SELECT$  command packet 2 and transitions to  $IDLE/SLEEP\_A$  state.

#### 4.1.5 Negative scenarios

Cases labeled as negative scenarios drive the DUT with purposely invalid transactions. Types of invalid injections, which will be verified are sending command before allowed  $FDT_{A,POLL}$  time, invalid parity bits, CRC, or completely missing these fields. These requirements should be implemented with their own directed test cases and have priority 3 - could be verified, if the schedule allows it.

## 4.2 Verification strategy

Verification uses constraint random verification approach and DUT is accessed as a black-box. This way the UVC shall be easily reusable and independent of actual RTL design.

Completeness should be measured by number of requirements implemented and covered. Implemented requirement means that it is linked to all selected items - functional coverage, checker and test cases. Covered requirement has 100~% coverage from all corresponding items.

Test cases should be implemented in two ways - as a constrained random tests with minimum constraints to reach coverage goals faster, or directed approach can be used for specific scenarios. All the test cases are shared for RTL and gate-level simulation.

UVC to be designed should be implemented in the most customizable way. Testbench environment and its components should have their configuration files, where their functions could be turned off.

The goal of verification is to achieve 100 % code coverage and functional coverage with all test cases without any reported error.

**4.3.** Tools

#### 4.3 Tools

Main software used for simulations is Cadence Incisive 15.20-s009 For viewing coverage extracted data Cadence Integrated Metrics Center 15.20-s009 is used.

Cadence Incisive is called by user-written Perl script <code>compile\_script</code>, which has as a parameter <code>-t</code> test case which will be run. This script passes all the necessary arguments (e.g. enables coverage collection, Graphics User Interface - GUI, and specifies UVM message level) to common <code>irun</code> command that parses and executes them.

## 4.4 Checkers implementation

All checkers are implemented as immediate assertions located in passive components, i.e. nfc2\_t2r\_monitor and nfc2\_scoreboard. Assertions shall be exclusively labeled and use this template:

```

assert_<unique_name> :assert(<condition>) begin

//Pass message

'uvm_info(get_type_name(), $sformatf("%m :

Information %d", data), <verbosity>)

end

else begin

'uvm_error("get_type_name()", $sformatf("%m :

Information : %d", data))

end

```

### 4.5 Coverage implementation

Functional coverage is implemented inside relevant components with coverage groups containing cover points and cross coverage. For each covergroup this template is used: 4. Verification plan

```

covergroup cov_grp_<unique_name>;

cov_<unique_name> : coverpoint <item_name> {

//Bins are created automatically or manually

}

cross_<unique_items_name> : cross <item_name_1>,

<item_name_2> {

// If needed, some bins may be ignored

ignore_bins ignore_these_<items> =

binsof(<item_name_1>) intersect {<val_list1>} ||

binsof(<item_name_2>) intersect {<val_list2>};

}

endgroup

```

### 4.6 Test cases implementation

Test cases shall be derived from  $nfc2\_test\_base$  class, which creates the  $nfc2\_env$  verification environment,  $nfc2\_env\_cfg$  environment configuration object instance and initializes it. Derived test case modifies the properties in configuration and starts a sequence.

## 4.7 UVM usage

Designed UVC uses the set of UVM macros and classes described in, namely:

- all UVC components are derived from the most suitable UVM class and use their inherited methods,

- uvm\_config\_db database is used for passing necessary objects between components,

- UVM report macros 'uvm\_info, 'uvm\_warning, 'uvm\_error and 'uvm\_fatal are used most of the time for reporting. Message verbosity is altered by "+UVM\_VERBOSITY=: option and can be set to UVM\_DEBUG, UVM\_FULL, UVM\_HIGH, UVM\_MEDIUM, UVM\_LOW or UVM\_NONE.

## Chapter 5

# Implementation of UVC for NFC Type 2 Tag

Designing UVC for NFC Type 2 Tag Platform is the next task after preparation of verification plan, whom content needed to be taken into consideration. Before starting to write the code, it is better to divide the particular tasks and propose a system-level design of solution.

As it was previously mentioned, the main goal of the UVC is to verify DUT's full functionality according to NFC Type 2 Tag Platform. Required UVC should therefore support all protocol commands and corresponding responses and know how to modulate and demodulate communication channels from DUT interface. In the verification plan there are also requirements, which need invalid sequences or valid command in incorrect time. Thus it is essential not only be able to communicate with DUT using the protocol correctly, but also to inject the protocol errors. This is achieved by properly written command classes and compatible driver.

This chapter will describe UVM components and objects that take care of driving the connected DUT, collecting the functional coverage, and predicting and verifying the DUT responses. Base classes of NFC commands and responses will be described before the UVC analysis on a system level, so one can understand the conception of how they are used in the UVC.

### 5.1 Command and response items

Both NFC command and response classes inherit fields and methods from their respective base classes, and carry all the basic properties. If the command or response is more complex, additional fields or methods are implemented.

#### 5.1.1 nfc2\_base\_cmd class fields

Base item class for commands  $nfc2\_base\_cmd$  extends  $uvm\_sequnce\_item$  class and contains these fields:

```

class nfc2_base_cmd extends uvm_sequence_item;

//fields

rand bit crc_present;

rand bit cmd_len_valid;

rand bit crc_valid;

rand bit parity ok;

rand bit sof present;

rand bit eof_present;

rand nfc2_frame_format_e nfc2_frame_format_i;

rand nfc2_bit_rate_e nfc2_bit_rate_i;

rand bit [6:0] nfc2_pause_a_len;

rand bit [7:0] nfcid1 len;

rand nfc2_wait_after_res_e nfc2_wait_after_res_i;

nfc2_byte_stream_q tx_stream;

nfc2_command_e nfc2_command_i;

int res max wait time;

bit [7:0] cmd_code;

bit [15:0] crc i;

time cmd_end_time;

//...

endclass : nfc2_base_cmd

```

Unusual datatypes from the field declaration are defined in the common SystemVerilog file together with all required constants and datatypes used in the test bench.  $nfc2\_byte\_stream\_q$  is a queue of bytes and holds the payload that driver processes based on the other fields.  $nfc2\_command\_e$  is enumerative type of all supported NFC commands,  $nfc2\_frame\_format\_e$  similarly holds the possible frame formats,  $nfc2\_bit\_rate\_e$  bit rates and  $nfc2\_wait\_after\_res\_e$  options for issuing another command before or after allowed  $FDT_{POLL,MIN}$  or  $GT_A$  time (see Section 2.1.6).

All rand fields are properly constrained by using soft construct, so in case

of negative scenario the constraint might be violated.

nfc2\_base\_cmd class also implements basic functions for randomization, computing CRC16, converting queue to transaction and vice versa and printing functions for reporting in simulators console. Another characteristics are later implemented in classes for specific commands.

#### 5.1.2 nfc2\_base\_res class fields

Base item class for Tag responses  $nfc2\_base\_res$  is also extented from uvm sequence item class and contains these common fields:

```

class nfc2 base res extends uvm sequence item;

//fields

rand bit crc_valid;

rand bit crc_present;

rand bit parity ok;

rand bit res len valid;

rand nfc2_frame_format_e nfc2_frame_format_i;

rand nfc2_bit_rate_e nfc2_bit_rate_i;

rand bit [7:0] nfcid1 len;

time res_start_time;

int unsigned time res;

nfc2_command_e nfc2_command_i;

nfc2_response_e nfc2_response_i;

\mathbf{nfc2\_byte\_stream\_q} \  \, \mathbf{rx\_stream} \, ;

bit [15:0] crc i;

//...

endclass: nfc2\_base\_res

```

These fields are very similar to  $nfc2\_base\_cmd$  fields, but apart from that there is information about the type of response in  $nfc2\_response\_e$  enumerative type and response start time for validating timing.

nfc2\_base\_res class also implements basic functions for randomization, computing CRC16, converting rx\_stream queue to transaction and vice versa, printing functions for reporting in simulator console and checking correct length of response.

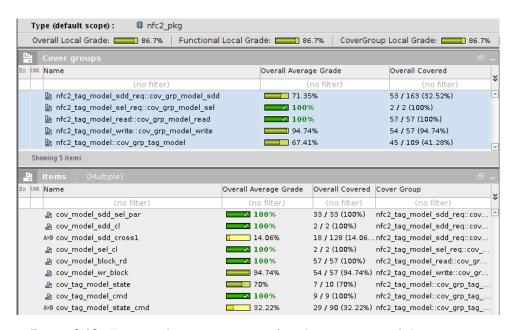

## 5.2 System-level design of the testbench

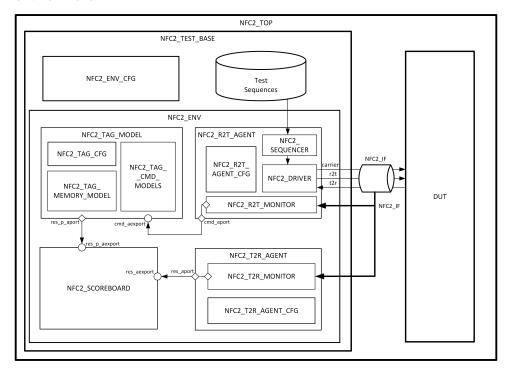

Division of the testbench (TB) to modules is displayed on Figure 5.1. Names of the modules all start with shortcut nfc2. In the  $nfc2\_tb\_top$  module selected testcase together with DUT module are created, also virtual interface connecting DUT to the testbench is created and passed into the  $nfc2\_env$  environment.

Figure 5.1: System level of implemented testbench.

After that the selected test case is launched and build of the  $nfc2\_env$  and  $nfc2\_env\_cfg$  begins. This environment contains 4 components:

- 2 agents designated for transmitting and receiving logic signals from the interface,

- nfc2\_tag\_model modeling DUT NFC Type 2 Tag behaviour and predicting the Tag response,

- nfc2\_scoreboard verifying DUT response by comparing it to nfc2\_tag\_ model predicted item.

Environment  $nfc2\_env$  also has to connect these components during  $connect\_phase$  and for that uses  $uvm\_analysis\_port \#(<item\_name>)$ . In this

instance three analysis ports are needed. Analysis port  $cmd\_aport$  exports captured command from  $nfc2\_r2t\_monitor$  to  $nfc2\_tag\_model$ , analysis port  $res\_aport$  passes captured DUT response from  $nfc2\_t2r\_monitor$  to  $nfc2\_scoreboard$  and the last analysis port  $res\_p\_aport$  transports predicted response from  $nfc2\_tag\_model$  to  $nfc2\_scoreboard$ .

#### 5.2.1 Configuration objects

Object  $nfc2\_env\_cfg$  holds all configurable settings of the UVC. Inside this object another three configuration files are created - one for each agent and one configuring specific DUT parameters for  $nfc2\_tag\_model$ . These objects are passed on to  $uvm\_config\_db$  and relevant components can access them by using get method.

Configuration objects for the agents specify if the checkers inside its monitors are applied and whether the component is active or passive.

Object  $nfc2\_tag\_cfg$  configures all the DUT properties needed for the implemented test bench, which includes:

- number of Data memory blocks,

- response for SENS\_REQ and ALL\_REQ commands,

- maximum cascade level,

- mask for *SEL\_RES* response,

- information about where the NFCID1 is stored in memory,

- coverage enabling bit.

#### 5.2.2 nfc2\_r2t\_agent and nfc2\_sequencer

$nfc2\_r2t\_agent$  encapsulates three components:  $nfc2\_sequencer$ ,  $nfc2\_driver$  and  $nfc2\_r2t\_monitor$ . Its main task is to instantiate, create and connect them in corresponding phases. Besides that it gets the  $virtual\ interface$  from the  $uvm\_config\_db$  and assigns it to  $nfc2\_driver$ .

$nfc2\_sequencer$  code is very simple, it just needs to register itself within the UVM factory, all the other methods are inherited from  $uvm\_sequencer$  class. The sequences for driving are given from the test case and are requested by  $nfc2\_driver$  to process them.

#### 5.2.3 nfc2\_driver

Driver  $nfc2\_driver$  has 2 main roles during the  $run\_phase$ , and that is generating the  $f_c$  clock and processing the items given by  $nfc2\_sequencer$  and driving the DUT with that item after the conversion to logical level according to Modified Miller coding from Section 2.1.2. These tasks are done in parallel by using SystemVerilog fork construct:

```

fork

clock_gen(fc_half_per);

forever begin

seq_item_port.get_next_item(seq_req_inst);

process_item(seq_req_inst);

detect_res_end(seq_req_inst.res_max_wait_time,

seq_req_inst.nfc2_wait_after_res_i);

seq_item_port.item_done();

end

join

```

Implemented  $nfc2\_driver$  uses the relevant item fields (e.g.  $parity\_ok$ ,  $pause\_a\_len$ ) during the whole command processing. It has separate functions for each NFC frame format, and adds parity bits if necessary.  $nfc2\_driver$  component uses set of functions for modulating the DUT input port, which are based on  $f_c$  clock cycles.

Method detect\_res\_end after process\_item() implements basic detection of the DUT response end, and sets time delay according to item field nfc2\_wait\_after\_res\_i. Delay can be smaller than mandatory time FDT\_POLL, MIN, always minimal or randomly generated.

#### 5.2.4 nfc2\_r2t\_monitor

Component monitoring DUT input port was implemented, so each component is independent. That way if now used  $nfc2\_driver$  is disconnected, another module can drive the DUT. Also this  $nfc2\_r2t\_monitor$  checks and validates  $nfc2\_driver$  functionality. Main task of  $nfc2\_r2t\_monitor$  is running in forever loop, where it detects SoF sequence, captures the data bits until the EoF sequence occurs. Command recognition starts after this process,  $nfc2\_r2t\_monitor$  first checks amount of bits captured, and looks for the

command code match. Based on captured command, CRC16 field might be checked, and correct method to validate command length is used. If the frame format is not short,  $nfc2\_r2t\_monitor$  also checks parity bits. For timing validation purposes  $nfc2\_r2t\_monitor$  stores last modulation time to item. In the end  $nfc2\_r2t\_monitor$  writes captured item to analysis port  $cmd\_aport$  and looks for another command SoF.

#### 5.2.5 nfc2\_t2r\_agent and nfc2\_t2r\_monitor

Agent  $nfc2\_t2r\_agent$  incorporates only the Tag monitor  $nfc2\_t2r\_monitor$ , so its duties are to create it, get virtual interface from  $uvm\_config\_db$  and pass it to the  $nfc2\_t2r\_monitor$ .

Tag monitor validates the physical layer of Tag responses alongside the response detection. It works on the same concept as  $nfc2\_r2t\_monitor$ . That means detecting the start of frame, catching and decoding the response until the end of response frame sequence appears.  $nfc2\_t2r\_monitor$  always tries to recognize the response, but sometimes it is not possible, because information about issued NFC command is needed for definite decision. Nevertheless the parity bits are checked in case of standard or bit oriented SDD frame and data validation is left up to  $nfc2\_scoreboard$ .

#### 5.2.6 nfc2\_tag\_model

Predictor model implements NFC Type 2 Tag Platform behaviour like DUT, but in SystemVerilog language. To do that,  $nfc2\_tag\_model$  includes models of behaviour for each supported NFC command and has its own memory model. Memory model is initialized by the same input file as DUT memory, and implements all the features of NFC Type 2 Tag Platform Static Memory Structure. Read and write operations are executed by using  $write\_block()$  and  $read\_blocks()$  functions. At the end of the  $write\_block()$  execution change in static locks settings by  $check\_static\_locks()$  function and particular blocks are locked if necessary. The memory model also supports irreversible bits.

Tag predictor reacts to incoming item from  $nfc2\_r2t\_monitor$ , and proceeds to response prediction according to  $nfc2\_command\_i$  field. At first type of response is predicted by command model.  $nfc2\_tag\_model$  stores its own internal state from Tag State Machine and evaluates whether it shall generate the response or ignore the command. Next tag state is also predicted following

Type 2 Tag Platform State Machine [2]. Afterwards the correct response is generated and written to  $res\_p\_aport$  analysis port. If the command is ignored, no item is sent through analysis port.  $nfc2\_tag\_model$  also in some cases predicts the correct time in which the DUT response has to come. This is done for  $SENS\_REQ$ ,  $ALL\_REQ$ ,  $SDD\_REQ$  and  $SEL\_REQ$  commands, because they shall be sent at particular time slot. For the rest of the NFC commands computation is carried out in  $nfc2\_scoreboard$ .

#### 5.2.7 nfc2\_scoreboard

$nfc2\_scoreboard$  receives captured and predicted  $nfc2\_base\_res$  item and has to compare them. Implemented scoreboard uses simple 1 bit synchronization mechanism, because  $nfc2\_tag\_model$  always predicts Tag response before the DUT issues its own response. In case of two consecutive replies from the same source ' $uvm\_error()$  is executed. If the synchronization is intact,  $nfc2\_scoreboard$  compares frame format, payload and validates the timing. If any mismatch occurs, assertion is raised.

## Chapter 6

## Implemented UVC demonstration

Designed verification component will now be tested with written test case examples. To verify correct functionality of the implemented UVC, already verified and implemented design of HF logic core was provided by ASICentrum company.

### 6.1 Creating and starting sequence

Sequences are essential part of each test and determine course of the test case. Here is  $ALL\_REQ$  command example of how sequence in test case should be created, built, randomized and run:

```

class test_example extends nfc2_test_base;

'uvm_component_utils(test_example)

nfc2_cmd_all_req_seq example_seq;

function new(string name = "test_example",

uvm_component parent = null);

super.new(name, parent);

example_seq = new;

endfunction : new

virtual function void build_phase(uvm_phase phase);

```

```

super.build_phase(phase);

example_seq = nfc2_cmd_all_req_seq::

type_id::create("example_seq", this);

assert(example_seq.randomize() with{

nfc2_wait_after_res_i == RANDOM_E;

});

endfunction : build_phase

virtual task run_phase(uvm_phase phase);

phase.raise_objection(this);

example_seq.start(nfc2_env_inst.

nfc2_r2t_agent_inst.nfc2_sequencer_inst);

phase.drop_objection(this);

endtask

endclass : test example

```

## 6.2 Example testcases

Multiple constrained-random test cases with original scenarios were written and executed to prove UVC correct functionality. Each of these test cases finished with 0 raised assertions and zero 'uvm\_warning, 'uvm\_error and 'uvm\_fatal messages.

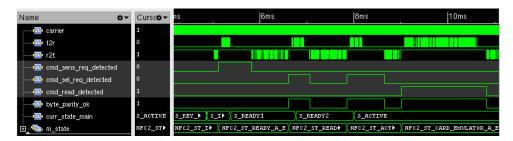

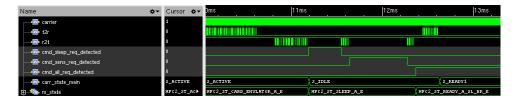

In the following figures from the simulator it can be seen the UVC detection of commands in internal signals  $cmd\_<name>\_detected$  from  $nfc2\_t2r\_monitor$  and the current state of  $nfc2\_tag\_model$  with name  $m\_state$ , while  $curr\_state\_main$  is internal signal from the DUT. The first three waveforms are DUT inputs and outputs - carrier being the  $f_c$  clock, r2t being input commands from the UVC and t2r DUT responses.

## **6.2.1** Transition to *ACTIVE\_A* state and reading the whole memory

First test case and Figure 6.1 illustrates transition to  $ACTIVE\_A$  state by using  $SENS\_REQ$  command and after that  $SEL\_REQ$  command twice, because DUT is configured for 2 cascade levels. Correct NFCID1 is read from the UVC memory model, which is created inside  $nfc2\_test\_base$  class.

Figure 6.1 together with the rest of the simulation waveform also displays the Tag model functionality. After each issued command in r2t signal  $m\_state$  changes exactly in the moment, while the DUT makes the change afterwards.

**Figure 6.1:** Transition to  $ACTIVE\_A$  state and first READ command.

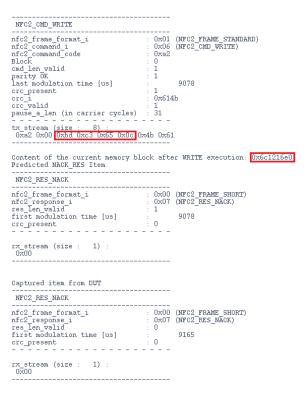

In the end of the test case READ command with block number out of memory space is issued (see Figure 6.2). DUT shall respond with NACK response and test case is complete.

**Figure 6.2:** Issuing READ with higher block number

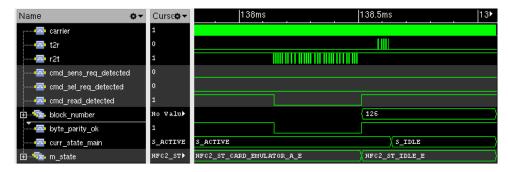

Example of the validation reporting shows item from  $nfc2\_t2r\_monitor$  in Figure 6.3 and item from  $nfc2\_tag\_model$  in Figure 6.4.

```

Captured item from DUT

NFC2_RES_NACK

nfc2_frame_format_i : 0x00 (NFC2_FRAME_SHORT)

nfc2_response_i : 0x07 (NFC2_RES_NACK)

res_len_valid : 0

first modulation time [us] : 139781

crc_present : 0

rx_stream (size : 1) :

0x00

```

Figure 6.3: Captured NACK response

Scoreboard compares the items and reports its results like in Figure 6.5.

**Figure 6.4:** Predicted *NACK* response

```

uvm_test_top.nfc2_env.nfc2_scoreboard_inst [nfc2_scoreboard] Tag response match

uvm_test_top.nfc2_env.nfc2_scoreboard_inst [nfc2_scoreboard] Response frames do match

uvm_test_top.nfc2_env.nfc2_scoreboard_inst [nfc2_scoreboard] FDT Max time is not exceeded

uvm_test_top.nfc2_env.nfc2_scoreboard_inst [nfc2_scoreboard] FDT n value is integer within tolerance

```

Figure 6.5: Scorebord validation UVM info.

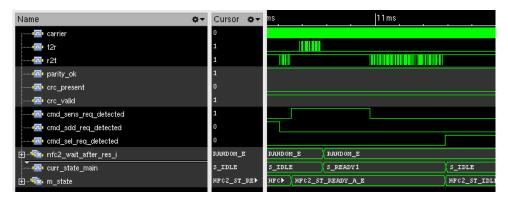

## **6.2.2** Transition to *ACTIVE\_A* state and writing data to Data blocks

In the second test case WRITE command are issued with random data for each Data block. Wheter the data are written correctly is checked by the following READ commands. That way the same run of the memory model and DUT memory is proven. The correct write procedure to the memory model is displayed for one block in Figure 6.6 and match with the DUT memory is shown in responses to READ command in Figure 6.7. It is important to notice that byte order in the command and the output of the memory model is reversed.

Figure 6.6: Successful WRITE command to block 7.

In the end of the test case WRITE command with random block number

**Figure 6.7:** Validation of the previous WRITE command with the READ command.

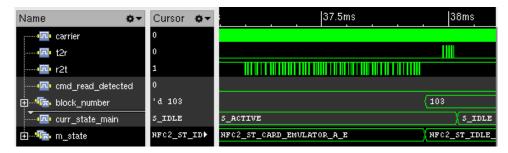

out of memory space is issued (see Figure 6.8). DUT shall respond with NACK response and transition to IDLE state.

Figure 6.8: Issuing WRITE with higher block number

#### **6.2.3** Transition to ACTIVE\_A state and testing lock bits

This test case proves that memory model is compliant with Static Memory Data Structure. First sequence is issuing <code>WRITE</code> command to block 0 with random data in <code>ACTIVE\_A</code> state. Block 0 is reserved for manufacturer use and shall be read-only, therefore Tag shall issue <code>NACK</code> response. The DUT follows this rule and Figure 6.9 shows that the data in memory model are not changed and <code>NACK</code> response is predicted correctly.

The test case continues with locking one block of data by changing one

**Figure 6.9:** Issuing *WRITE* with block number 0.

static lock bit to logic 1. After successful lock the WRITE command to that block is performed. Figure 6.10 demonstrates no change of data in the memory model and correctly predicted NACK response.

Lock bit already set to logic 1 cannot be changed back to logic 0. This property is tested by trying to write logic 0 back to that bit. Output from the console in Figure 6.11 informs that there was an attempt to change irreversible bit and the value of the lock bit stays at logic 1. Again, the byte order for the labeled data is reversed.

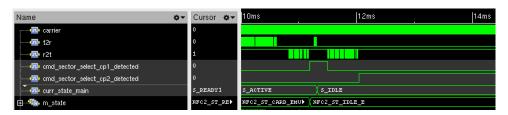

#### 6.2.4 SLEEP\_REQ command execution

At first transition to  $ACTIVE\_A$  has to be made, then  $SLEEP\_REQ$  has to be executed. After that follows  $SLEEP\_REQ$ ,  $SENS\_REQ$  and  $ALL\_REQ$ , and as it is in Figure 6.12, DUT behaves correctly and after  $SLEEP\_REQ$  responds only to  $ALL\_REQ$ .

**Figure 6.10:** Issuing *WRITE* for previously locked block.

**Figure 6.11:** Issuing logic 0 for irreversible static lock bit.

**Figure 6.12:** *SLEEP\_REQ* command verification.

#### **6.2.5 SECTOR SELECT** command packets 1 and 2

SECTOR SELECT switches to another memory sectors, however DUT contains only 1 memory sector. It follows that to SECTOR SELECT command packet 1 DUT shall respond with NACK response and DUT shall ignore the

$SECTOR\ SELECT$  command packet 2 and transition to IDLE state, which Figure 6.13 confirms.

**Figure 6.13:** SECTOR SELECT command packets verification.

## 6.2.6 SDD\_REQ for all valid NFCID1 and SEL\_PAR combinations

The test case shows the usage of  $SDD\_REQ$  command with all the valid combinations of  $SEL\_PAR$  and NFCID1 fields. Bit oriented SDD frame recognition and validation was tested this way and UVC finished the DUT testing with 0 errors.

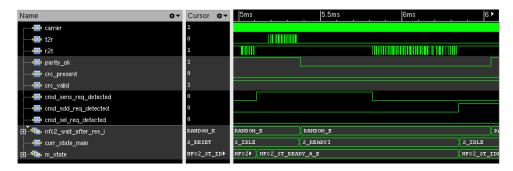

#### 6.2.7 Negative scenarios

In all of these scenarios Tag shall ignore the invalid command and transition to *IDLE* state. First case is Figure 6.14 where *SEL\_REQ* is issued in *READY\_A* state with all valid fields except CRC16. CRC16 is mandatory, but in this sequence it is omitted and Tag together with the UVC ignores this command.

Figure 6.14: SEL\_REQ without CRC16.