#### Master's Thesis

Czech Technical University in Prague

Faculty of Electrical Engineering Department of Measurement

# Migration of an IoT Real-Time System and Reimplementation of Some of Its Functions

Bc. Jan Mrázek

Supervisor: Ing. Milan Kolář Field of study: Computer Engineering May 2019

# **Acknowledgements**

I would like to thank the supervisor of this master's thesis, Ing. Milan Kolář, for providing me with a friendly working environment as well as great guidance throughout my work on this project. I would also like to thank doc. Ing. Jiří Novák, Ph.D. for giving me additional guidance and insights when authoring this text.

Furthermore I want to thank my family, who supported me not only during my work on this thesis, but also throughout my studies.

# **Declaration**

I declare that the presented work was developed independently and I have listed all sources of information used within it in accordance with the methodical instructions for observing the ethical principles in the preparation of university theses.

In Prague, May 20, 2019

# Abstract

This thesis is dedicated to the research and realization of a prototype for migration of a home automation system from an older, MCU-based design to a more modern solution. The older design is a microcontroller-based, low system resource solution incorporating an ARM Cortex-M4 MCU, the FreeRTOS operating system and various memoryconserving implementation approaches. The new proposed solution includes a Texas Instruments Sitara AM3358 chip and a distribution of Debian Linux patched with the PREEMPT RT realtime kernel patch. Development is done using a BeagleBone Black single-board computer.

This thesis provides descriptions and explanations of the concepts and inner workings of real-time operating systems and the Linux device tree system. The process of reimplementing and porting of functionalities from the previous project is described, issues are discussed and their solutions explained. Performance gains are measured and explained for some of the newly implemented functionality.

**Keywords:** home automation, real-time operating system, Linux, device tree, PREEMPT\_RT, Sitara

Supervisor: Ing. Milan Kolář

# Abstrakt

Tato diplomová práce se zabývá rešerší a realizací prototypu pro migraci systému inteligentních domů ze stárnoucí koncepce založené na mikrokontroléru na koncepci modernější. Starší koncepce zahrnuje mikrokontrolér založený na jádře ARM Cortex-M4, operační systém FreeRTOS, relativně nízké systémové prostředky a několik implementačních postupů pro jejich šetření. Navrhované řešení používá čip Texas Instruments Sitara AM3358 a Linuxovou distribuci Debian včetně modifikace jádra PREEMPT\_RT. Vývoj je prováděn za pomoci jednodeskového počítače BeagleBone Black.

Tato práce čtenáři poskytne popis a vysvětlení konceptů a vnitřních procesů operačních systémů reálného času a Linuxového systému device tree. V práci je popsán proces portování a reimplementace několika různých funkcí z původního systému. Problémy zjištěné během tohoto procesu jsou vysvětleny a jsou zde probrána jejich řešení. U některých reimplementací dochází k razantnímu nárůstu výkonnosti oproti předchozímu řešení - tyto změny jsou naměřeny a jejich dopad je detailněji popsán.

Klíčová slova: inteligentní dům, operační systém reálného času, Linux, device tree, PREEMPT\_RT, Sitara

**Překlad názvu:** Migrace a reimplementace funkcí IoT systému reálného času

# Contents

| 1 Introduction                                                | 1  |

|---------------------------------------------------------------|----|

| 1.1 History and Current Trends                                | 2  |

| 1.1.1 External and Paid Software<br>Toolsets                  | 2  |

| 1.1.2 Current Market Situation                                | 3  |

| 1.1.3 Economical Considerations and<br>Initial Cost Tradeoffs | 4  |

| 1.1.4 Embedded vs General-Purpose                             | 5  |

| 1.1.5 Future Outlooks                                         | 5  |

| 2 Hardware                                                    | 7  |

| 2.1 iQtec Home Automation System .                            | 7  |

| 2.2 Existing Solution                                         | 8  |

| 2.2.1 Weak points                                             | 9  |

| 2.3 New Solution                                              | 10 |

| 2.3.1 Hardware Requirements                                   | 10 |

| 2.4 Candidates                                                | 12 |

| 2.4.1 Variscite DART-6UL<br>System-In-Module                  | 12 |

| 2.4.2 STMicroelectronics<br>STM32MP1-Series microprocessor | 13 |

|------------------------------------------------------------|----|

| 2.4.3 Octavo Systems OSD3358<br>System-In-Package          | 14 |

| 2.4.4 BeagleBone Black                                     | 15 |

| 2.4.5 Texas Instruments Sitara<br>AM3358                   | 17 |

| 2.4.6 Lapis Semiconductor<br>MR45V100A                     | 18 |

| 3 Software                                                 | 19 |

| 3.1 Operating System                                       | 20 |

| 3.1.1 Existing Solution - FreeRTOS                         | 20 |

| 3.1.2 RTOS in General                                      | 21 |

| 3.1.3 Combining RTOS and Linux<br>Strengths - PREEMPT_RT   | 21 |

| 3.1.4 Real-Time Thread Scheduling                          | 22 |

| 3.1.5 Effects of the PREEMPT_RT<br>Patch                   | 23 |

| 3.1.6 Cyclictest                                           | 24 |

| 3.1.7 A Custom Threaded<br>Benchmark                       | 25 |

| 3.1.8 Choosing a Particular<br>Operating System            | 28 |

| 3.2 Filesystem                                                                                                                       | 28                          |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 3.2.1 Existing Solution - FatFs                                                                                                      | 28                          |

| 3.2.2 File Access Slowdowns                                                                                                          | 29                          |

| 3.2.3 Quantifying Slowdowns                                                                                                          | 30                          |

| $3.2.4$ Sudden Shutdown Behavior $% \left( {{\left( {{\left( {{\left( {1 \right)} \right)}} \right)}} \right)$ .                     | 31                          |

| 3.2.5 New Solution - ext4                                                                                                            | 31                          |

| $3.3\ {\rm IDE}$ and Other Software Tools $% (1,1,2,2,2,3,3,3,3,3,3,3,3,3,3,3,3,3,3,3,$                                              | 34                          |

| 3.3.1 Code Composer Studio                                                                                                           | 34                          |

| 3.3.2 Microsoft Visual Studio 2017                                                                                                   | 34                          |

| 3.3.3 Cross Compilation                                                                                                              | ~                           |

| 5.5.5 Cross Compliation                                                                                                              | 35                          |

| 3.3.4 Integration of the Cross<br>Compiler                                                                                           |                             |

| 3.3.4 Integration of the Cross                                                                                                       |                             |

| 3.3.4 Integration of the Cross<br>Compiler                                                                                           | 35<br><b>37</b>             |

| <ul><li>3.3.4 Integration of the Cross<br/>Compiler</li><li>4 Implementation Process</li></ul>                                       | 35<br><b>37</b><br>38       |

| <ul> <li>3.3.4 Integration of the Cross<br/>Compiler</li> <li>4 Implementation Process</li> <li>4.1 The Linux Device Tree</li> </ul> | 35<br><b>37</b><br>38<br>39 |

| 4.4.1 FRAM Transactions Over SPI                     | 44 |

|------------------------------------------------------|----|

| 4.4.2 Setting Maximum SPI Speed in Device Tree       |    |

| 4.4.3 Real-World Transfer Speeds<br>Before and After | 47 |

| 4.4.4 SPIDEV Maximum Buffer<br>Sizes                 | 47 |

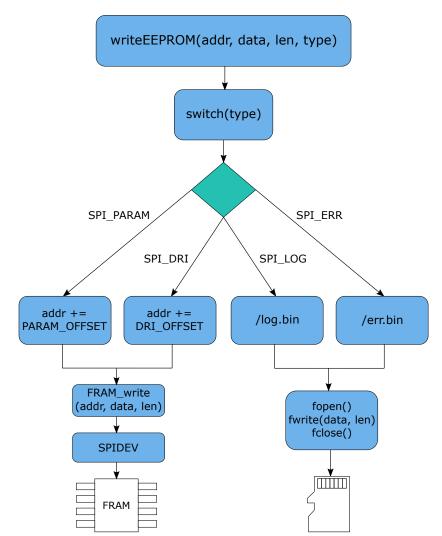

| 4.4.5 EEPROM Redirecting                             | 48 |

| 4.5 Userspace-Based RTC Driver                       | 50 |

| 4.5.1 Setting Hardware Time                          | 51 |

| 4.6 Accurate Software Timers                         | 51 |

| 4.6.1 Proposed Solution: AM3358's<br>PRU             | 52 |

| 4.6.2 Software Approach                              | 52 |

| 4.6.3 Minor Redesign                                 | 53 |

| 4.6.4 Specifics                                      | 53 |

| 4.7 UART Interface Wrapper                           | 55 |

| 4.7.1 Uses                                           | 55 |

| 4.7.2 Implementation Specifics                       | 56 |

| 4.8 Standalone Application<br>Substitutes            | 58 |

| 4.8.1 FTP Server            | 58 |

|-----------------------------|----|

| 4.8.2 FTP's Security Issues | 58 |

| 4.8.3 HTTP Server           | 59 |

| 5 Conclusion                | 61 |

| 5.1 Future Development      | 63 |

| Bibliography                | 65 |

| Project Assignment          | 69 |

# **Figures**

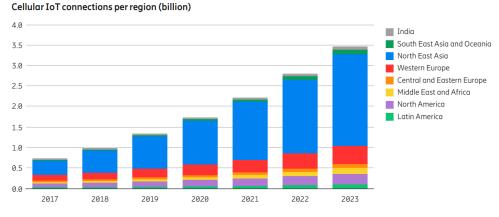

| 1.1 Cellular IoT connections forecast<br>for 2023                           | 6  |

|-----------------------------------------------------------------------------|----|

| 2.1 iQtec PLC                                                               | 8  |

| 2.2 Variscite DART-6UL                                                      | 12 |

| 2.3 STMicroelectronics STM32MP1                                             | 13 |

| 2.4 Octavo Systems OSD3358                                                  | 14 |

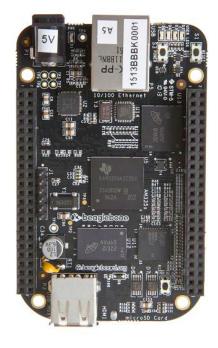

| 2.5 BeagleBone Black                                                        | 16 |

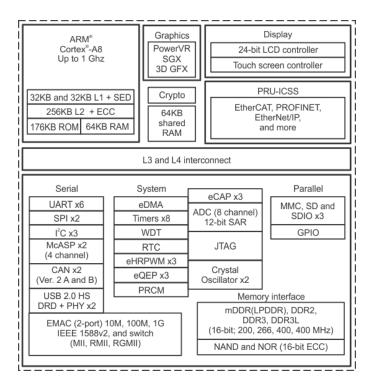

| 2.6 Functional block diagram of the TI<br>AM3358                            |    |

| 2.7 MR45V100A ferroelectric RAM                                             | 18 |

| 3.1 Timer overheads on non-patched kernel                                   | 26 |

| 3.2 Timer overheads on<br>PREEMPT_RT-patched real-time<br>kernel            | 27 |

| 3.3 Random file access times<br>depending on directory population,<br>FatFs | 30 |

| 3.4 Schema of a typical journaling filesystem                               | 32 |

| 3.5 Random file access times<br>depending on directory population,<br>ext4 | 33 |

|----------------------------------------------------------------------------|----|

| 3.6 Code Composer Studio splash screen                                     | 34 |

| 4.1 Simplified diagram of a device tree structure                          |    |

| 4.2 Activity diagram of ported<br>FRAM/EEPROM handler                      | 49 |

| 4.3 Diagram of the implemented software timer structure                    | 54 |

|                                                                            |    |

# **Tables**

| 3.1 Comparison of Cyclictest results |    |

|--------------------------------------|----|

| between unpatched and RT-patched     |    |

| systems                              | 25 |

4.1 A mapping of GPIO pins to interfaces enabled in this project . . 41

# Chapter 1

## Introduction

The market for home automation solutions has been getting bigger and bigger in recent years. To be successful in this specific field of Internet of Things and beat the vast amount of competition, home automation companies strive to create and provide solutions that are very economically (i.e. both in initial price and maintenance costs) friendly and, maybe most importantly, solutions that are intuitive to use and provide a comfortable user experience.

In order to create systems that are inconspicuous and non-invasive (to not disrupt the customer's interior design, for example), home automation developers usually design their electronics to be compact in size. This brings along the downside that a small, microcontroller-based system might not be able to provide the real estate and computing power needed to satisfy all requirements in a timely and responsive manner. When an issue of this nature presents itself to such a developer or company, there are generally multiple ways to get past it. A cost-effective way is to just limit and slow down the responsiveness of the system. While cheap, this approach is far from being correct. They might also try to pursue means of hardware upgrades to take their system back up to par speed-wise.

In some cases, home automation companies will choose to research the options and approaches to hardware upgrades even before the risks of slowdowns and issues tied to them present themselves.

I was tasked with researching such a hardware upgrade by Prague-based smart home company Prologue, s.r.o. Prologue develops and maintains a home automation system called iQtec. The plan was to research the means 1. Introduction

of replacing the iQtec home automation system's main processing unit's CPU with a different, much more modern and faster chip. This project also included researching a switch to a different operating system - a migration from FreeRTOS to a more conventional Linux-based distribution. Another task was the migration and porting of the processing unit's codebase and functionality from the old operating system to the new one.

This master's thesis will describe to the reader in detail the process of designing and executing such a research project. The thesis consists of multiple parts; first, an overview of the the historical, current and future trends in this field of computing are discussed. Next, the existing home automation system is described. After that, some of the current system's weak points are discussed and their solutions are proposed. Then, both the existing and new systems' hardware specifics are introduced and compared. The choice of operating system is explained and some key concepts are introduced. Implementation specifics are described in detail and any issues presenting themselves during the implementation process are discussed and their solutions explained.

#### **1.1** History and Current Trends

In the past, home automation and maybe even IoT systems as a whole used to be mostly based around simple microcontrollers and MCUs (microcontroller units). This situation rose from the fact that these generally simpler processors were typically quite cost-effective to purchase.

Low costs, however, came with a significant penalty; as a result of the relatively low RAM and storage capacity of these devices, a significant portion of the development had to be devoted to making very memory- and CPU-efficient source code. This was often extremely difficult in newly-started companies, as there simply wasn't enough manpower to be dedicated to creating a working product in a reasonable time frame.

#### 1.1.1 External and Paid Software Toolsets

An option in such a situation was to purchase a working pre-implemented source code library or toolset from providers selling such services. There was a clear advantage in doing so, as it enabled developers to divert their attention to implementing actual functionality. A downside of this approach was the fact that a codebase acquired in this manner often came without any sort of guarantee and was not free of bugs.

Even though these solutions were often far from perfect, their monetary costs were not insignificant, especially for a start-up operation.

There however existed paid toolsets which offered such guarantees, but those often had very different target customers - the aerospace industry. This was reflected in the price tag of such solutions, which was so extreme that no startup would elect to use them.

#### 1.1.2 Current Market Situation

The situation in the IoT and microprocessor market nowadays contains three types of big players. First, there are companies who actually manufacture the silicon chips that are used in this type of computing. In today's tech climate, where costs are being pushed down rapidly and the period of moral obsolescence is getting relatively longer (in other words, customers don't seek hardware upgrades as frequently as before), it is very important to offer good customer support in order to sell units. Chip producers therefore put big amounts of effort into providing good documentation, reference and usage manuals and driver support.

Another sort of tech companies who represent a significant portion of the market are businesses that produce software libraries based on those drivers. There is a good amount of collaboration between these two types of tech companies - silicon manufacturers want their hardware to have a good software applicability and a good user experience for developers using it. The result of this that customers will be more likely to choose a product with a good software toolkit, thus bringing more sales to both the hardware and software producers.

These software-creating companies are also getting more and more important on the market as the complexity of the underlying hardware rises. An example - in the past, a typical microcontroller's reference manual would be hundreds of pages long. Nowadays, such reference manuals for bigger, multi-core and high feature chips are often an order of magnitude longer. The amount of information needed to get through when programming drivers and other low-level software for a modern microcontroller is truly vast, which makes software libraries all the more important. 1. Introduction

More and more tech companies have been taking advantage of the seemingly underdeveloped field of services built around maintaining IoT systems. These companies belong to the third type of big players in today's IoT market. The service they usually provide is mainly centered around a means of data storage and manipulation for customers in the form of what is commonly called a cloud service.

Amazon and its AWS (Amazon Web Services) is a good representative of a company offering such a business model. In order to have a good customer uptake, it is very important to provide a high quality of service. This is related more to the application side of the service, such as efficient storage, good realiability and availability, data visualization, database maintenance and so on, and less so the underlying hardware and lower-level software sides. Amazon is also active in lower levels of the software hierarchy, though - since 2017, Amazon has taken stewardship of the FreeRTOS project and now offers a real-time operating system containing libraries and functions which can be integrated into AWS. [1] Other providers of cloud services include Microsoft Azure and Google Cloud.

#### **1.1.3** Economical Considerations and Initial Cost Tradeoffs

A typical IoT or home automation company will put more emphasis on certain hardware and software requirements as its size changes. Smaller companies with less developers and a smaller customer base will generally select hardware from a big silicon manufacturer. This is because such manufacturers typically offer a better developer support.

The unit price for a bigger producer's better-supported chip might be higher, but it is less important for a smaller company's budget, as it might not sell a significant enough number of products for the slightly higher initial costs to matter.

On the other hand, for companies who move a relatively high amount of end products and operate on a bigger scale, the initial unit price might be more important than the manufacturer's product support capability. It might often be cheaper to simply hire more developers to battle issues and problems that present themselves during the development of a big product than to suffer from high initial hardware costs.

#### **1.1.4 Embedded vs General-Purpose**

This approach can also be applied and seen when it comes to developing a design of a particular IoT system. Nowadays, the rate of integration is rising and single-board general purpose computers, such as the Raspberry Pi, its various clones and devices based on a similar concept, are widely commercially available.

There is a lot of competition in this field, which means that prices are relatively low, which is a good trend for IoT companies. Single-board computers of today usually offer a complete solution of a CPU, power module, I/O functionality and peripheral tools that would in the past need to be sourced and assembled from many singular parts besides just the microcontroller.

For a smaller IoT company or start-up, the single-board computer approach offers a tremendous upside; the usual use of a conventional Linux distribution in such a device means that lots of different drivers are continuously being supported and bugs are often quickly patched. This means that using a single-board computer is actually more cost-effective in the long run, as less work needs to be expended to write low-level software.

#### 1.1.5 Future Outlooks

The spread of IoT services has been exponential and has even seen some unexpected acceleration in recent years. In 2018, the number of devices connected to AWS rose by 49% over the preceding 12 months, and Azure grew by an even more staggering 93%. The number of connected devices that are in use exceeded 17 billion in mid-2018, with 7 billion of those being IoT devices, and is projected to exceed 34 billion by 2025 (21 billion of those being IoT). [2]

The development and nearing worldwide deployment of fifth generation networking (5G) communication technology will probably accelerate the growth of the IoT market even more.

#### 1. Introduction

Its promises of high bandwidth and, more importantly, extremely low latencies, will be very important in this field. It is projected that 3.5 billion IoT devices will be connected via cellular networks alone in 2023. [3]

Figure 1.1: Cellular IoT connections forecast for 2023 [3]

As mentioned before, the period of moral obsolescence of today's both IoT and non-IoT devices is lengthening. Another fact is that semiconductor manufacturing technology advancements are slowing down - in 2019, 7 nanometer technology is slowly becoming the standard, with 5nm proposed for 2020 and 3nm for 2024. [4]

It is entirely possible that the market will see a shift with big companies switching to the field of providing services mentioned above - it seems that there is a relatively untapped profit potential, judging from the insane market growth in the recent past, present and near future.

# Chapter 2

## Hardware

In this chapter, first an overview of the iQtec home automation system is provided. Then the details of iQtec's existing hardware are introduced, along with its strong and weak points. In another section, the proposed new hardware gets presented and its specifics are discussed.

### 2.1 iQtec Home Automation System

iQtec is a system used for technological process control and data collection. It is highly modular and can be used in a wide variety of applications, ranging from controlling the environment of a single apartment or house, all the way to gathering data and regulating of large industrial objects. Its main usecases are as follows:

- Temperature regulation

- Heating, ventilation and louver control

- Lighting control, including dimmers and RGB scenes

- Electrical outlet control

- Energy consumption monitoring (electricity, gas, water, etc.)

- Home security camera and intercom functionality

2. Hardware

Each additional sensor or control module connected within this system has its own proprietary software driver, which enables it to get registered, initialized and - most importantly - take part in communication with the main system unit.

#### 2.2 Existing Solution

iQtec's PLC, or programmable logic controller, is comprised of a logic board with an STM32F437ZIT6 microcontroller unit. This MCU is made by STMicroelectronics and is based on an ARM Cortex-M4 core operating at a frequency of 168 MHz. This MCU itself contains 256 kilobytes of RAM, two megabytes of flash memory, and a real-time clock (RTC) module. [5]

Figure 2.1: iQtec PLC [5]

There are also numerous peripherals inside the PLC [5]:

- A Ferroelectric RAM (or FRAM) module with a 128 kilobyte capacity connected on one of the MCU's SPI buses. This FRAM is used to store data that changes frequently, such as outputs from various measurement modules. The main strength of this FRAM module is its extreme read/write endurance it is possible to overwrite every bit up to 10<sup>13</sup> (or ten trillion) times. [6]

- An electrically erasable programmable read-only memory (EEPROM) chip, mainly used to store longer-term data, such as device initialization logs and error messages.

- A microSD card interface, which is primarily used to store service information or update the unit's firmware if needed. An industrial-grade microSD card is used in order for it to sustain temperature fluctuations reliably.

- Transceivers for many different communication protocols, such as RS-422, RS-485, CAN 2.0B, or Ethernet. These are used to communicate with the system's sensors and data collecting devices.

Most of the devices listed above are connected to the MCU via either of  $I^2C$ , SPI or UART-based serial interfaces.

#### 2.2.1 Weak points

The weakest point of this PLC is the microcontroller unit. A massive drawback is its memory size. 256 kB of RAM is not a very comfortable amount to work with as a developer, especially when the code is powering a project which can potentially be quite extensive. There is a significant amount of effort that has been expended into designing the iQtec's software in an efficient way. Lots of time was put into memory optimization in the existing solution to make it run smoothly.

Another drawback is the relatively low computing power of the system's processor. A 168 MHz Cortex-M4 core still offers plenty of power for simpler usecases, but it has been showing signs of running out of breath in this application.

Steps had to be taken when developing the original iQtec codebase to reduce the memory footprint of some of its functions. These steps resulted in some unfavorable behavior of the system, which became apparent as the codebase grew and the system got more complex. Some of these drawbacks will be explained in detail in chapter three.

#### 2.3 New Solution

#### 2.3.1 Hardware Requirements

Research had to be conducted in order to choose a processing unit to act as a basis of the project's hardware. To make sure the correct chip was chosen in the end, a list of system requirements was agreed upon and made up. These requirements took into account the weak points mentioned in the previous section, as well as some parameters of the old solution that should be carried over and executed in a similar or better fashion.

#### Multi-Core Processing

The decision to create this project to use a traditional Linux operating system meant that the new CPU should be able to comfortably switch between lots of threads running concurrently. Therefore, a chip with multiple cores should be chosen.

#### Computing Power

This requirement also stems from the usage of a more complex operating system. To put this requirement into a context of numbers, the DMIPS metric should be explained first. DMIPS stands for Dhrystone Millions of Instructions Per Second, where Dhrystone is the name of a synthetic computing benchmark that quantifies a processor's performance in an accurate manner. A metric of "specific DMIPS" can be defined as the amount of DMIPS achieved for every 1 MHz for a given chip's clock rate.

The old project's processor has a DMIPS value of 210, or a specific DMIPS of 1.25 with a clock rate of 168 MHz [5]. A requirement was defined to provide at least five times the DMIPS of computing power with the new chip. This is quite generous, as it should be possible to beat 1000 DMIPS with almost any chip which already satisfies the first requirement and runs at a reasonable clock speed. For example, if a hypothetical dual-core Cortex-M4 chip existed, it would only have to run at a clock speed of 400 MHz to satisfy this requirement.

#### Memory

As mentioned in the previous section, a low amount of RAM is quite limiting when developing software for embedded systems, and can be downright painful as the project snowballs with more features and an expanding codebase.

To make sure there is enough system memory to satisfy the project's needs even as it gets improved in the future, while at the same time leaving some extra for the operating system itself, it was decided that at least 512 megabytes of memory should be available in the new hardware solution. This amount trumps the original 256 kilobytes by a huge margin, while being more than reasonable in today's state of the art.

#### Interfaces and Storage

The original system's PLC offers a relatively large array of communication interfaces. Five UARTs, three SPI bus interfaces, two I<sup>2</sup>Cs, two USB 2.0 ports, an Ethernet port and more [5]. The new system should provide a comparable amount of these interfaces, with Ethernet and UART being the most important ones. There should also be options available to expand the IO ports with more functionality.

A microSD card slot is also an important requirement, as it stores crucial service information, as mentioned in section 2.1, though this is not necessarily a feature of the processing unit itself. A dedicated storage device (other than the microSD card) would also be welcome - the original design only incorporates a two megabyte flash storage, which is far being optimally sized.

#### 2.4 Candidates

#### 2.4.1 Variscite DART-6UL System-In-Module

The Variscite DART-6UL is one the platforms selected for closer examination. It includes a processor based on NXP's i.MX 6UltraLite family and contains an ARM Cortex-A7 core clocked at up to 900 MHz and 1 gigabyte of RAM. Its features also include two Ethernet connections, dual CAN, I<sup>2</sup>C, SPI, UART and SD/MMC interfaces. The DART-6UL is optimized for low power consumption and is also relatively small in size, with the whole module's dimensions being only 25 by 50 millimeters. The DART-6UL also supports Linux as its operating system of choice. [7]

Figure 2.2: Variscite DART-6UL [7]

The Variscite DART-6UL satisfied demands for available storage devices and communication interfaces. It only uses a single Cortex-A7 core though, which might not be enough to handle the needs of the project when combined with possible future extensions. The lack of multiple cores also hurts its computing power - while its DMIPS value of about 1760 is far higher than the original system's 210, there are multi-core variations of the Cortex-A7 which would help even more.

A big advantage of this system-in-module is the fact that Variscite also produces and sells a 4G LTE modem module, which will be incorporated into the project at some point in the future. Combining these two devices could prove to be favorable, especially when it comes to development support.

#### 2.4.2 STMicroelectronics STM32MP1-Series microprocessor

In February of 2019, STMicroelectronics announced a new series of microprocessors, the STM32MP1. This family of microprocessors uses a single or dual ARM Cortex-A7 core in combination with a Cortex-M4 core, clocked at 650 and 209 MHz, respectively. This enables the STM32MP1 to support multiple and flexible applications and achieve best performance and power figures. Up to 1 gigabyte of DDR3 RAM is available. Communication interface equipment is very good, with six  $I^2C$ , up to 8 UART, six SPI, three SD/MMC and a single Ethernet connection available. As for operating systems, both Linux and Android are supported. [8]

Figure 2.3: STMicroelectronics STM32MP1 [9]

The STM32MP1 satisfied all of the requirements defined in the previous section. It offers two Cortex-A7 cores clocked at 650 MHz, which comply to the computing power requirement with a DMIPS value of 2470. A big plus is the amount of communication interfaces available, as well as the number of storage devices available. A discovery or evaluation kit was not available at the time of this research, so the usage of the STM32MP1 was not pursued further. It is also very new and fresh on the market, which could have negative implications as it is currently relatively unproven, though they are not factual as of writing this thesis.

#### 2.4.3 Octavo Systems OSD3358 System-In-Package

The last candidate that made the short list is Octavo Systems' OSD3358 System-In-Package (SiP). The OSD3358 itself integrates multiple devices in order to make it a system that is completely ready to run.

It integrates a Texas Instruments Sitara AM3358 processor, a TI power management system, up to 1 gigabyte of DDR3 memory and lots of passive components, all while keeping everything inside a single reasonably-sized 27x27 mm package. With this level of integration, the OSD335x Family of SIPs allows designers to focus on the key aspects of their system without spending time on the complicated high-speed design of the processor/DDR3 interface or the PMIC power distribution. It also reduces the overall size and complexity of the design and the supply chain. [10]

Figure 2.4: Octavo Systems OSD3358

The OSD3358 offers an Ethernet connection, two USB 2.0 ports, access to multiple CAN, SPI, UART and I<sup>2</sup>C peripherals, a SD/MMC interface and an optional integrated eMMC storage device. [10] It is capable of running Linux, Android or an RTOS (real-time operating system) as far as operating systems go.

The Octavo OSD3358 also satisfies most of our requirements. It boasts solid computing power - its Cortex-A8 clocked at up to 1 GHz offers a DMIPS value of 2000 with a specific DMIPS of 2 per MHz - a value slightly higher than any of the other candidates. Peripheral interface connections are plentiful and a combination of eMMC and microSD card support is a big plus, as well as its size.

In the end, the OSD3358 was picked as the basis of this thesis's project. The main factors in this decision were its dimensions, its Sitara AM3358 processor, integrated eMMC and good peripheral connection capabilities. Its theoretical performance was also important in the decision, though it does only use a single-core processor.

#### Note on development board used

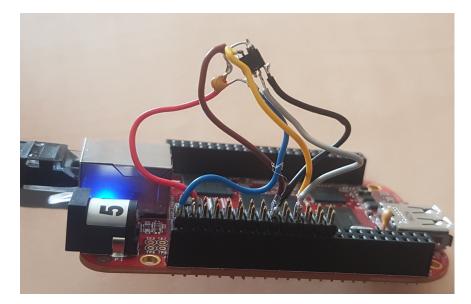

An Octavo OSD335X-SM-RED evaluation board was ordered and acquired in preparations to start the prototyping phase. Issues appeared with Ethernet drivers in the Linux distribution of choice in the early stages of prototyping. The Octavo-supplied evaluation board uses an Atheros AR8035, whose drivers were not functioning properly at the time. This meant that in the end, most of the prototyping was done on a BeagleBone Black board.

In the final product, it is likely that the Octavo SiP will be used, and a different Ethernet adapter will be used instead of the AR8035 located on the Octavo OSD355X-SM-RED.

#### 2.4.4 BeagleBone Black

Due to issues with the Octavo OSD355X-SM-RED evaluation board early on in the development of this project, the decision was made to switch to a BeagleBone Black single board computer. The BeagleBone Black is extremely similar to the Octavo evaluation board, but there are some differences.

The key difference is that this board does not in fact run the Octavo OSD3358 chip - the main CPU of the BeagleBone Black is TI's Sitara AM3358, i.e. the exact same CPU found inside the OSD3358. This has no practical consequences on this project, as these CPU solutions only differ in power delivery circuitry, which does not affect this project in any way. The BeagleBone uses an SMSC LAN8710A Ethernet adapter, which did not exhibit any driver problems during development.

Another notable difference between the Octavo evaluation board and the BeagleBone Black is the amount of RAM, of which the latter only has 512 megabytes.

#### 2. Hardware

The BeagleBone Black is actually a very good board to use for this project. It is widely commercially available and relatively inexpensive (the cost of one unit at the time of writing is about \$55). This means that the BeagleBone Black is very favored among developers and hobbyists alike. There is a big community support for this board, both from users and the manufacturer.

Figure 2.5: BeagleBone Black [11]

The main features of the BeagleBone Black are as follows [11]:

- TI Sitara AM335x 1GHz ARM Cortex-A8 processor

- 512MB DDR3 RAM

- A 3D graphics accelerator and a microHDMI port, which can be utilized to use the BeagleBone Black as a traditional single-board computer

- USB client and host connections

- A microSD card slot, as well as a 4 gigabyte eMMC memory, which allows it to be shipped with a preinstalled OS to provide out of the box usability

- Ethernet, two 46-pin input/output headers

- 4x UART, 2x SPI, 2x I2C, 2x CAN bus peripheral drivers

#### 2.4.5 Texas Instruments Sitara AM3358

The AM335x family of microprocessors, of which the AM3358 is a member, are based on the ARM Cortex-A8 processor core and are enhanced with image, graphics processing, peripheral and industrial interface options. These devices also support high-level operating systems (HLOS). [12]

Figure 2.6: Functional block diagram of the TI AM3358 [12]

The AM335x family chips also contain two additional 32-bit RISC microcontrollers, called the Programmable Realtime Units, located on the SoC in the PRU Subsystem and Industrial Communication Subsystem, or PRU-ICSS. The PRU-ICSS is separate from the ARM core, allowing independent operation and clocking for greater efficiency and flexibility. The PRU-ICSS enables additional peripheral interfaces and real-time protocols. The programmable nature of the PRU-ICSS, along with its access to pins, events and all system-on-chip (SoC) resources, provides flexibility in implementing fast, real-time responses, specialized data handling operations, custom peripheral interfaces, and in offloading tasks from the other processor cores of SoC. [12]

The AM3358 CPU being used here runs at a clock speed of 1 GHz.

#### 2. Hardware

#### 2.4.6 Lapis Semiconductor MR45V100A

The existing PLC uses a 128 kB FRAM chip to store data that changes very frequently and is overwritten constantly, such as temperature or energy consumption measurements, or other information of similar character.

This prototype uses an MR45V100A FRAM chip for this very same purpose. It is a one megabyte unit which should be good for trillions of overwrites per bit. It can be used in temperatures ranging from -40 to +85 degrees Celsius, which will be enough for our use. [6] It is connected to the CPU via a serial peripheral interface (SPI).

A picture of the FRAM chip as installed on the prototype can be seen in figure 2.7.

Figure 2.7: MR45V100A ferroelectric RAM

# Chapter 3

# Software

The software side of this thesis is arguably the part that needed improvement the most.

The iQtec functionality itself and all the system device (i.e. hardware other than the PLC itself) drivers will not need reimplementing or any drastic changes, as the system devices are not a part of this prototype, rather just peripherals connected to it.

The microcontroller-esque nature of the original PLC design is not ideal in today's state of the art, as outlined in 1.1 and 2.2. As the scope of the original project rose, some sub-optimal routes had to be taken in order to ensure proper functionality while staying inside the constraints of the hardware and system resources.

In this chapter, some of these solutions will be explained. New approaches will be discussed and introduced, and a general comparison will be provided between the old and new solutions.

#### 3.1 Operating System

#### **3.1.1** Existing Solution - FreeRTOS

The old PLC uses FreeRTOS as its operating system of choice.

FreeRTOS is a market leading real time operating system, or RTOS for short, from Amazon Web Services that supports more than 35 architectures. It is professionally developed, strictly quality controlled, robust, supported, and free to embed in commercial products without any requirement to expose your proprietary source code. FreeRTOS has become the de facto standard RTOS for microcontrollers by removing common objections to using free software, and in so doing, providing a truly compelling free software model. The FreeRTOS kernel was originally developed by Richard Barry around 2003, and was later developed and maintained by Richard's company, Real Time Engineers Ltd. FreeRTOS was a runaway success, and in 2017 Real Time Engineers Ltd. passed stewardship of the FreeRTOS project to Amazon Web Services (AWS). [1]

FreeRTOS has been used in iQtec's PLC because of its good viability when used in a microcontroller-based system. FreeRTOS is generally designed and created to have a small memory footprint and a small processor overhead. It also supports multi-threading. There are none of the more advanced features typically found in operating systems like Linux or Microsoft Windows, such as device drivers, advanced memory management, user accounts, and networking. The emphasis is on compactness and speed of execution. [13]

The second to last point mentioned in the previous paragraph is one of the bigger downsides of using FreeRTOS here. Networking and device drivers have to generally be "outsourced" to external libraries, or written from scratch. To avoid doing this in this thesis's prototype, it was decided to not use an operating system of this nature, and instead go for a traditional Linux distribution, which offers the "luxury" of having network and device drivers ready to go, as well as a good memory management system.

#### **3.1.2 RTOS** in General

A big strength of using a lightweight operating system such as FreeRTOS can be found in its name - it is a true real time operating system.

A processor core can only run a single thread of execution at a time. To provide multi-tasking, an operating system has what is called a scheduler, which is responsible for deciding which program to run when, and provides the illusion of simultaneous execution by rapidly switching between programs. [14]

The type of an operating system is defined by how the scheduler decides which program to run when. For example, the scheduler used in a multi-user operating system (such as Unix) will ensure each user gets a fair amount of the processing time. Some operating systems prioritize tasks that interact with the user, which helps with user experience and perceived responsiveness. [14]

The task scheduler in a real time operating system provides a deterministic execution pattern. This is very useful in embedded systems, as these systems have real time requirements. A real time requirement is one which specifies that the system must respond to a certain event within an expected and strictly defined time frame. Real time operating systems generally guarantee real time requirements because the system's task scheduler runs in a deterministic manner, and thus its behavior can be predicted. [14] A typical way of providing determinism and predictability is the use of thread priorities. The highest priority task wanting the CPU always gets the CPU within a fixed amount of time after the event waking the task has taken place. On an RTOS, the latency of a task only depends on the tasks running at equal or higher priorities. On a normal operating system, these latencies depend on everything running in the system at a given point in time, which makes it very difficult to meet a task's deadline reliably. [15]

#### 3.1.3 Combining RTOS and Linux Strengths -PREEMPT\_RT

A traditional Linux-type operating system is not an RTOS. Many programs and threads run in parallel and typically, no real time requirements are specified nor guaranteed. If kernel code is executing when some event takes place that requires a high priority thread to start executing, the high priority thread can not preempt the running kernel code, until the kernel code explicitly yields control. In the worst case, the latency could potentially be hundreds of milliseconds or more. [15] There is, however, a way to bring Linux's kernel closer to that of a real time operating system - The PREEMPT\_RT patch.

PREEMPT\_RT is a real-time kernel patch which can transform the Linux kernel into one that is fully preemptive. In addition to faster response times (and maybe more importantly), it removes all unbounded latencies. An unbounded latency means that the amount of delay that can occur is dependent on the situation. [16]

In a normal Linux kernel, a total of four preemption models are implemented which alter the kernel's behavior. These models provide tradeoffs between system throughput and latency, with the "No Forced Preemption" model having the best throughput at the cost of worse latency, while the "Low Latency Desktop" model is at the other end of the perceived spectrum. The PREEMPT\_RT patch adds two more preemption models, one of them dubbed "Fully Preemptible Kernel." This flavor of the patch makes all kernel code preemptible, save for a few selected critical sections. Several substitution mechanisms, such as special real-time mutexes, are implemented to reduce preemption-disabled sections of code to a minimum. This model is the one that truly provides the kernel with real-time behavior. [17]

#### **3.1.4** Real-Time Thread Scheduling

In an ordinary Linux operating system (or any other general purpose OS), tasks need to share CPU time, as there are orders of magnitude more tasks than available CPUs. Waiting tasks are usually dispatched in order of decrasing priority. If two or more tasks' priorities are identical, these kinds of ties are broken according to task scheduler policies. [18] All scheduling is preemptive - if a task with of a higher priority becomes ready to run, the currently running task is preempted and returned to the list of waiting tasks. [19]

The standard task scheduler in Linux is called CFS, or "Completely Fair Scheduler." Internally, this scheduler is called SCHED\_OTHER. It uses an attribute called the *nice value*, which in essence represents a task's priority level. The range of the nice value varies across different Unix systems, but on modern Linux, the range is -20 (high priority) to +19 (low priority). [19] This might seem counterintuitive when thinking about niceness as a priority, but what it actually represents is how "nice" a task is to other waiting tasks. A very nice task will let other tasks skip ahead of it, while a task that is not nice will not.

A Linux kernel patched with PREEMPT\_RT introduces more functionality when it comes to scheduling and priorities. There are two more task scheduling policies, as well as an additional priority system. One of the new policies is called SCHED\_RR. When using this scheduler, tasks of equal priority alternate using a simple round-robin scheme. The other new policy is SCHED\_FIFO. As its name might suggest, tasks with equal priorities are dispatched in the order in which they were enqueued into the task queue. [18]

When using one of these new scheduling policies, threads gain the ability to have a new set of priority values. A static scheduling priority, or sched\_priority, is what the scheduler uses in order to decide which task to dispatch next. sched\_priority is not used in this decision at all when not using any of these two new policies (it is always set to zero for all tasks). Processes scheduled under these policies have a sched\_priority value in the range of 1 (low priority) to 99 (high priority). This means that real-time scheduled threads will always have higher priority than normal tasks. [19]

#### **3.1.5** Effects of the PREEMPT\_RT Patch

To quantify how PREEMPT\_RT actually affects performance in real-time applications, two tests were conducted. The first test's purpose was to measure the difference in latencies between a Linux system where the PREEMPT\_RT patch wasn't applied, and a Linux system that had previously been patched.

In order to prepare the testing environment, an image of Debian 9.8 suited for the BeagleBone Black was sourced and flashed onto a microSD card. This system was then booted up unmodified, and the first batch of tests was run. After that, the system was patched with PREEMPT\_RT, and the same tests were run again. Applying the PREEMPT\_RT patch on the kernel of the BeagleBone Debian distribution is quite simple. The Debian distribution ships with a script that will take care of most of the patching process.

```

root@beaglebone:~# cd /opt/scripts/tools/

root@beaglebone:/opt/scripts/tools/# uname -r #verify kernel version

4.14.71-ti-r80

root@beaglebone:/opt/scripts/tools/# ./update_kernel.sh \

> --ti-rt-channel --lts-4_14

```

3. Software

After the script finishes executing, a reboot is needed for the patch to take effect.

Verification of the model of preemption can be done very quickly - the configuration file /proc/config.gz can be decompressed and displayed with gzip, and all lines containing the word "PREEMPT" can be filtered with grep. A flag will be displayed for each of the preemption models. If the CONFIG\_PREEMPT\_RT\_FULL flag is present and enabled like in the snippet below, the operating system's kernel is fully preemptible.

```

root@beaglebone:~# gzip -cd /proc/config.gz | grep PREEMPT

CONFIG_PREEMPT=y

CONFIG_PREEMPT_RT_BASE=y

CONFIG_HAVE_PREEMPT_LAZY=y

CONFIG_PREEMPT_LAZY=y

# CONFIG_PREEMPT_NONE is not set

# CONFIG_PREEMPT_VOLUNTARY is not set

# CONFIG_PREEMPT_LL is not set

# CONFIG_PREEMPT_LL is not set

CONFIG_PREEMPT_RTB is not set

CONFIG_PREEMPT_RT_FULL=y

CONFIG_PREEMPT_COUNT=y

...

```

#### **3.1.6** Cyclictest

The Cyclictest utility was used to measure the systems' latencies. Cyclictest runs a non real-time master thread which starts a defined number of measuring threads with a defined real-time priority. The measuring threads are woken up periodically with a defined interval by an expiring timer (cyclic alarm). Subsequently, the difference between the programmed and the effective wake-up time is calculated and handed over to the master thread via shared memory. The master thread tracks the latency values and prints the minimum, maximum, and average latencies after each iteration. [20]

In order to put load on the system while Cyclictest was running, the **stress** utility was used. **stress** is a very simple workload generator which can put a configurable amount of load on the CPU, memory, I/O and disk system. [21] It was configured to run 64 load tasks on the CPU and I/O system, as well as 4 tasks on the memory system, each randomly allocating and deallocating 64 megabytes of memory.

Cyclictest was launched and configured to run for 1,000,000 iterations with a thread timer running at a period of 1 ms. Cyclictest's priority was set to 99 (the highest possible priority). The exact same command was used while testing both the unpatched and patched kernels - the priority setting had no effect on the unpatched system. The output of Cyclictest consists of three numbers - the minimum, average and maximum values of thread latency in microseconds. Ideally, these three values should be as close as possible to each other, with the maximum not being very high relative to the average.

A typical output of Cyclictest on a non-RT-patched system looks like the following snippet:

root@beaglebone:~# stress --cpu 64 --io 64 --vm 4 --vm-bytes 64M & root@beaglebone:~# ./cyclictest -t1 -p 99 -n -i 1000 -l 100000 policy: fifo: loadavg: 123.82 77.32 58.20 133/287 1796 T: 0 ( 1796) P:99 I:1000 C: 1000000 Min: 23 Act: 45 Avg: 44 Max: 421

You can see that the maximum latency gets quite wild, at about 10x the value of the average. This would not be acceptable in a real-time system.

The table in 3.1 displays the results of this first test done on a clean installation of BeagleBone Debian, and a PREEMPT\_RT-patched version of the same system. You can see that using a real-time kernel does indeed bring significant improvements in performance and reduces latencies drastically.

|                                | Min. Latency $[\mu s]$ | Avg. Latency $[\mu s]$ | Max. Latency $[\mu s]$ |

|--------------------------------|------------------------|------------------------|------------------------|

| Debian 9.8,<br>unpatched       | 23                     | 44                     | 421                    |

| Debian 9.8,<br>PREEMPT_RT_FULL | 16                     | 24                     | 49                     |

Table 3.1: Comparison of Cyclictest results between unpatched and RT-patched systems

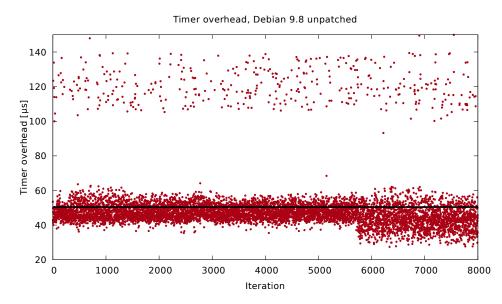

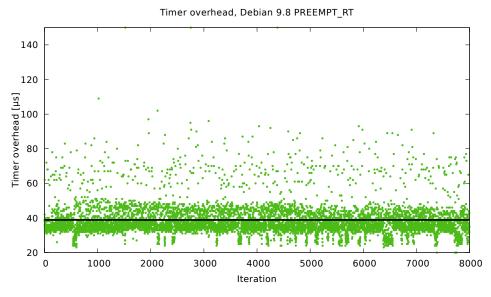

#### **3.1.7** A Custom Threaded Benchmark

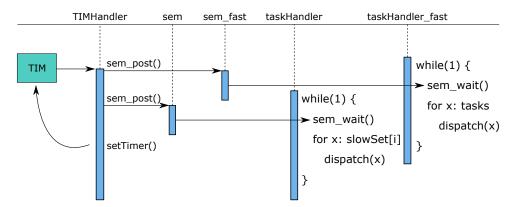

The second test that was executed was in essence quite similar to the first test. A more real-life source code was written (some of which would later be used in the ported code during the implementation phase of the thesis). The purpose of this code was to spawn an independent thread with a high priority, which would keep a timer alive and, when the timer fired, would raise a POSIX semaphore structure so that other threads knew a set amount of time had passed since the last firing. To put it very simply, it is an emulation of a hardware timer running at a configurable period. The actual implementation calls for a 25 millisecond timer, so that value is what was used to benchmark the latencies in this test.

When running on the patched kernel, the thread priority was again set to 99, and the schedule policy was set to SCHED\_FIFO. When running on the unpatched kernel, these settings were not applied as they are not supported.

The only task of the so-called "timer thread" is to wake up after catching a signal, set the timer again, and raise a semaphore. This whole cycle was timed using high-precision clocks in C's time.h library.

During testing, the system was put under load in the same manner as in the first test; using the **stress** utility. Each test was comprised of 8,000 iterations of a 25 millisecond timer, which means that one test instance took about 200 seconds to run.

The results of this test can be seen in figures 3.1 and 3.2. What they represent is, simply put, the overhead (in microseconds) of the implemented timing mechanism. Both figures also include a line representing the mean overhead values.

Figure 3.1: Timer overheads on non-patched kernel

3.1. Operating System

The results are somewhat expected; the unpatched kernel performs worse, its mean overhead value is 50.44  $\mu s$  and 90 % of measurements fall into an interval of (37.375; 62.216). The outliers are rather extreme, and there were three occurrences of overheads larger than 1500  $\mu s$ . Even though microsecond-precision is probably not needed in a 25 ms timer, a 1.5 ms delay is truly unacceptable.

Figure 3.2: Timer overheads on PREEMPT\_RT-patched real-time kernel

The PREEMPT\_RT-patched kernel performed significantly better. Its mean timer overhead was only 38.86  $\mu s$ , and 90 % of values measured fell into an interval of (28.791; 53.085). Outliers were also less frequent and their values were not as high as with the unpatched kernel - just five iterations saw an overhead of more than 100 microseconds (0.0625%), versus a much higher 392 occurrences (4.9%) of the same during benchmarking of the unpatched kernel.

#### 3.1.8 Choosing a Particular Operating System

After running these tests and consulting with the project supervisor, an agreement was reached to use the PREEMPT\_RT-patched version of the official BeagleBone Debian distribution to conduct the rest of this thesis's experiments.

We agreed that while it still might have some performance reserves that could be improved by using a more "lean" operating system, this distribution has a lot to offer to a software developer. Things such as the system's automatically-configured virtual Ethernet connection over its USB port (which allows the user to connect to and transfer data to and from the device without a network), a reasonably well-written documentation and active support forums, as well as the fact that this very operating system is recommended and supported by Texas Instruments, the company making the CPU used in this thesis, were factors that helped make this decision even easier.

## 3.2 Filesystem

As discussed before, iQtec's original PLC uses FreeRTOS as its operating system of choice. Being a bespoke RTOS, its main useful parts are the task scheduling kernel, a means for inter-process communication (IPC), thread synchronization and timers. [22] When used as is, it provides little more functionality. FreeRTOS has to be statically linked with any user-supplied compiled source code to produce a single executable, which is then booted by the system directly (or using a bootloader). Most real-time operating systems including FreeRTOS can not load and unload code dynamically from a file system, just like a regular general-purpose operating system can. Code is usually loaded at start-up and runs until power-down. [23]

#### **3.2.1** Existing Solution - FatFs

Programs running on microcontrollers don't usually have any filesystem capabilities. What these entail is the creation, moving and deletion of files and directories, reading and writing binary data to and from files, and communication with external storage devices, such as SD cards. The existing PLC incorporates all of this functionality, and uses FatFs to do so. 3.2. Filesystem

FatFs is a generic FAT filesystem module for small embedded systems, which is written in C and is very platform-independent. It can be incorporated into small microcontrollers with limited resources, as it boasts a very small memory footprint. [24] Some of FatFs's other features include [25]:

- Windows compatible FAT file system

- Support for multiple volumes (both physical drives and partitions), up to 10

- Long file name support in ANSI/OEM or Unicode

- Volume sizes of up to 2 terabytes (FAT32 specification when using 512 byte sectors)

- Support for RAM disks

#### 3.2.2 File Access Slowdowns

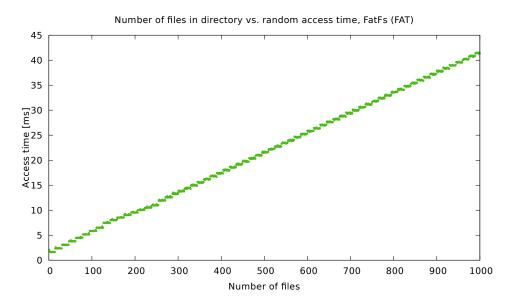

One of FatFs's main uses in iQtec's system is communication with the microSD card. The microSD card's purpose is to store service information, new firmware versions when an update is available, error logs and a partial copy of the system's current program state. There can be up to hundreds of files on the card at a given point in time. The microSD card is usually accessed every 25 milliseconds, so it does see some load almost constantly. One of the drawbacks of using the FAT filesystem is the fact that file operations can get very slow in directories containing more than a few hundred files. This concerns not only write and read operations on files, but simple file accesses are affected, too.

This was reportedly a problem at some point in iQtec's system history file access times would apparently take about 5 milliseconds from start to finish when only about twenty files were present in a given directory, but this access time would rise linearly up to unusable levels. What this means is that the time complexity of searching within a given directory is bounded by O(n), where n is the number of files in the directory. With close to a thousand of files, access times were reaching upwards of 40 milliseconds. This is clearly unacceptable in a case where the filesystem has to be accessed every 25 milliseconds. A workaround was deployed where a larger directory's files were split into subdirectories by the first characters of their filenames. This brought a little bit of extra complexity into the code, but helped mitigate the file access time issue somewhat.

#### 3.2.3 Quantifying Slowdowns

A simple program was created to test this behavior. The application would start with an empty directory and incrementally create files of random sizes. After each file was created, the application would select an existing filename at random and open the corresponding file. The access time was measured and outputted for every iteration. After the completion of this test, the directory would get scrubbed of all created files and the application would quit. The testing would terminate after 1000 files were created, which was more than enough to illustrate the point.

Figure 3.3: Random file access times depending on directory population, FatFs

This test was conducted numerous times and output logs were then analyzed. Typical results can be seen in figure 3.3. The data looks incredibly wellbehaved - as iterations go on, the access times stay almost constant and only rise once every 16 iterations. The output looks almost like a plot of a step function. This is almost certainly caused by a construct inside FatFs that possibly reallocates the directory table in increments of 16 records to save space. A trend line is not included in this graph as it is fairly apparent that file access times rise in a linear manner as the number of files in the tested directory rises. The equation for the trend line is, according to Microsoft Excel,  $f(x) = 0.04 \cdot x + 1.625$ , which indeed corresponds to the theoretical access time complexity of O(n). The test confirmed the existence of one of FAT's weaknesses - directories are merely unsorted arrays of filenames, so a directory searching function simply goes through the entries one at a time, until it finally finds (or doesn't) the correct entry. This is not a problem for directories that are relatively sparse, but gets more apparent as a directory gets populated with many files. [26] The FAT system is not solely to blame, though. FatFs is a very lightweight and simple implementation of a FAT filesystem, which certainly does not help with speed and efficiency. The fact that a 168 MHz-clocked microcontroller is used as the hardware is another factor that surely contributes to the filesystem's slowness.

#### 3.2.4 Sudden Shutdown Behavior

Another weakness of the existing solution is its relatively low tolerance against sudden shutdowns. The FAT filesystem is not inherently power fail safe. This means that if a power loss happens during file or directory updates, incorrect file metadata updates may happen. This produces garbage data, which in turn can cause a filesystem corruption. [27]

In FatFs, the filesystem is only updated once a file that is being updated is closed. Data loss due to sudden shutdown or media removal can be somewhat mitigated by periodically flushing a file that is opened for an extended period of time. The  $f_sync()$  function provides means to do this; only the data since the last synchronisation is lost after a sudden shutdown. After a search through the iQtec codebase, it seems as though this function was not being used at all, which definitely contributed in the system's intolerance to shutdowns.

#### **3.2.5** New Solution - ext4

Since the decision was made to use a traditional general-purpose operating system in the form of a Linux distribution (Debian 9.8 for the BeagleBone Black), there will be no need to use an external filesystem solution. The operating system is installed on a volume using the ext4 filesystem, which is supported by the Linux kernel natively. This brings about numerous advantages over the formerly used FatFs.

One such advantage is the fact that ext4 is a journaling filesystem. This has tremendous implications regarding its sudden shutdown tolerance.

3. Software

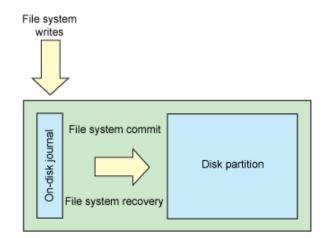

Journaling file systems are fault-resilient file systems that use a journal to log changes before they're committed to the file system to avoid metadata corruption. The journal is a special file that logs the changes destined for the file system. At periodic intervals, the journal is committed to the file system. If a crash occurs, the journal can be used as a checkpoint to recover unsaved information and avoid corrupting file system metadata. Figure 3.4 illustrates how a journaling system works. Ext4 also includes the ability to checksum the contents of the journal to make the journal more reliable. Another interesting fact about ext4 is its date resolution for file attributes down to 1 nanosecond - although this will not be needed in this project. [28]

Figure 3.4: Schema of a typical journaling filesystem [28]

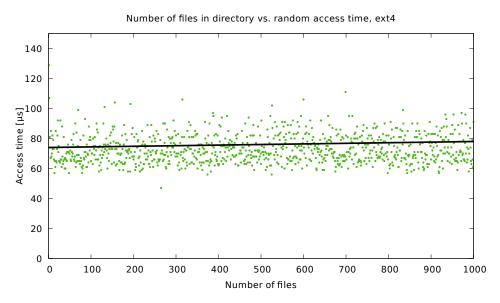

Another advantage that ext4 possesses over FatFs (and FAT in general) is speed. It does not suffer from the issue where file access times in a given directory would go up with the number of files in the directory. This is due to ext4's usage of efficient data structures to store directory entries. Where FAT used simple linear arrays to store such information, ext4 puts those into a special balanced tree. An advantage of balanced trees is that, while their implementation is more complex, they offer a search time complexity of O(log(n)), where n is the number of elements in the tree. [29]

A testing application was written to test the access times of files in an everexpanding directory, very similar to the test executed on the FatFs-equipped old system. The inner workings of this test were identical to the test described in 3.2.3. This test was run on the new hardware and software configuration, i.e. a BeagleBone Black system running an installation of Debian 9.8. The results of this test can be seen in a plot in figure 3.5. Other than the obvious speed-up (or rather lack of slowdown), please take note of the units used. The test showed that the ext4 solution used here was about two to three orders of magnitude faster than the formerly used FAT solution; where FatFs took dozens of milliseconds to access a file, ext4 only needs about 100 microseconds at worst.

The figure also includes a trend line this time, which, as it turns out, correctly reflects the time complexity by rising logarithmically with increasing file counts. According to Excel, the equation for the trend line's curve is  $f(x) = 0.458 \cdot ln(x) + 73.27$ , where ln(x) is the natural logarithm of x.

Figure 3.5: Random file access times depending on directory population, ext4

There is one more explanation for this massive performance gain, other than the usage of a superior, non-lightweight-implemented filesystem. It's also the fact that this test was executed on hardware that is much more powerful - the BeagleBone Black is equipped with a processor based on a very different microarchitecture (Cortex-A8 vs Cortex-M4), as well as having a significantly higher clock-rate (1 GHz vs 168 MHz).

## 3.3 IDE and Other Software Tools

#### 3.3.1 Code Composer Studio

When developing source code for this master's thesis project, the integrated development environment (IDE) of choice was Texas Instruments' Code Composer Studio version 8.3. Code Composer Studio is based on the Eclipse open source software framework. This generally means that a user familiar with Eclipse will find the user experience of CCS to be very similar. The choice to use CCS was made because of its very good integration of various functionalities used in developing applications for Linux-based systems.

Figure 3.6: Code Composer Studio splash screen

#### 3.3.2 Microsoft Visual Studio 2017

Microsoft's Visual Studio was also used for a portion of the development. iQtec's codebase is contained in multiple Visual Studio projects, and plans were made to integrate the Linux-deployed code into the existing projects. The correct platform would then simply be selected in Visual Studio.

Generally, individual functional components of this project were developed and debugged using Code Composer before being integrated into the iQtec codebase in Visual Studio.

#### **3.3.3 Cross Compilation**

During this project, development was done on ordinary desktop computers running the Microsoft Windows operating system. The target device, on the other hand, was an ARM processor running Linux. To bridge the gap between the development and target (or host) environments, a cross compiler is used. A cross compiler is a tool that allows the developer to compile source code on one platform and run it on a different platform.

The cross compiler used in this project was a part of the Linaro Toolchain. What's included in this toolchain, besides the GCC compiler and compiler libraries, is a set of tools that allow the inspection, debugging, and profiling of executables [30]. The Linaro Toolchain is maintained by the Linaro engineering organization and new versions are released periodically.

In order to compile on an x86-64 operating system and deploy onto an ARM system, the 5.5.0-2017.10-i686-mingw32\_arm-linux-gnueabihf package was used. This designation can be broken down into individual parts - i686-mingw32 signifies the host environment, arm signifies the target architecture, linux is the target system, and finally gnueabihf indicates which ABI (application binary interface) is used during compilation (GNU in this case). [31]

#### **3.3.4** Integration of the Cross Compiler

The integration of cross compiler toolchains into Code Composer Studio projects is incredibly easy. Once a toolchain is extracted and installed on the host environment, it is only a matter of adding its path into Code Composer's compiler settings, and finally selecting the desired compiler from a dropdown menu in a project's properties.

When it comes to Visual Studio however, the integration of the Linaro toolchain was a very different experience. As it turns out, it is impossible for Visual Studio 2017 to support third-party cross compilers. Linux targets are supported with a slight workaround, though. It is possible to set up Visual Studio for remote compilation for Linux C/C++ development. Since Windows 10 ships with the option of installing a Linux subsystem (called the Windows Subsystem for Linux, or WSL for short), it is possible to point Visual Studio to target WSL. This means that Visual Studio will compile source code "remotely," with the target system running on the same machine.

3. Software

To take advantage of this workaround, it is then possible to simply obtain a version of Linaro toolchain that runs on x86-64 Linux and targets our ARM system, and finally point WSL to use that compiler instead.

What this means in summary is that Visual Studio will "remotely" copy all source code onto the Windows Subsystem for Linux, compile it using a Linaro cross compiler targeting a system that is completely different from what it thinks, and then return the ready-to-deploy binary file back to the user in Windows.

The particular version of Linaro used for this workaround is 5.5.0-2017.10-x86\_64\_arm-linux-gnueabihf. To verify that the entire cross compilation process works without issues, we can simply run the file command on the resulting binary and check that the target architectures are identical.

**Note**: There is no difference between the terms "executable" and "shared object" in this context.

## Chapter 4

## **Implementation Process**

Chapters 2 and 3 provided an exhaustive description of both the old and new solutions when it comes to the hardware and software used. A consequence of the dramatic hardware and software changes is that a significant part of the codebase needs to be rewritten from scratch.

A portion of the codebase could simply be migrated from the old system to the prototype developed in this thesis. This particular portion consists of peripheral device drivers which are connected to the iQtec PLC via standardized communication protocols, such as SPI or other UART-based protocols. The functionality of these peripherals should remain unchanged provided the handling of communication on the aforementioned buses is implemented correctly.

A lot of the codebase became incompatible with the new system specifications. Some code depended on constructs that are not available or supported in the same way in this thesis's project, such as hardware timers and external real-time clocks. Other parts of the code were simply outdated or depended on technology that has been surpassed, like the filesystem - this issue was described in 3.2.

This chapter will provide to the reader an overview of what tasks needed to be accomplished in order to begin developing new functionality for this project. The process of enabling various peripheral interfaces connected to the CPU of choice, the Texas Instruments Sitara AM3358, will be described. Each system component that needed porting over to the new solution will be introduced in detail and the specifics of its reimplementation will be discussed.

## 4.1 The Linux Device Tree

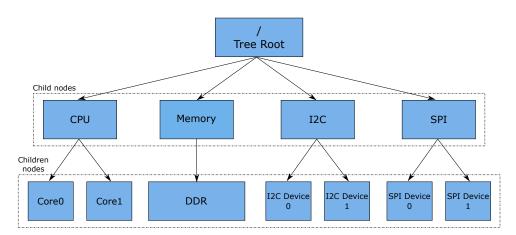

The Linux system, when running on an embedded device, does not have a BIOS. In order to boot and configure the hardware device it is running on, it uses files located on the filesystem that describe the machine's hardware. Every type of embedded Linux device has its own unique set of files to describe its platform hardware. Previously, modifications to the Linux kernel were applied each time Linux was booted from a new unique embedded device. As the popularity of ARM-based microprocessors soared, thousands of such modifications were implemented. Nowadays, ARM-powered embedded devices use *device trees* to describe hardware configurations instead. [32]

The data contained within a device tree describes the type of CPU, memory, input and output pins and other devices connected to it (such as Ethernet, external storage, SPI/I<sup>2</sup>C buses, etc.). [33] Figure 4.1 illustrates a simple device tree structure. [34]

Figure 4.1: Simplified diagram of a device tree structure (adapted from [34])

These files are used as part of the boot process. To modify the hardware that is enabled in the system, it is possible to decompile the full device tree, make changes, then recompile and deploy it, which is a rather tedious process. An alternative way of doing it is by using a device tree overlay. A device tree overlay supplies additional information about the hardware. It is simply merged with the full device tree by the bootloader (typically U-Boot) and then passed to the Linux kernel at boot-up. [32] A device tree overlay's binary form is called a *device tree blob*, or .dtb file. The human-readable format for device trees typically uses the .dts extension. A device tree compiler (DTC) is used to to transform between the two formats.

#### Note on documentation confusion

Previously, it used to be possible to load device tree overlays at runtime. A kernel mechanism called Capemgr (short for cape manager) was used to dynamically load overlays without the need to reboot the system, as long as the device tree blob file was prepared in advance. These overlays were originally used to support custom expansion boards (capes) for various development boards which used device tree-supporting kernels. [35] Though very convenient, this approach is no longer supported due to stability issues and is being phased out to be replaced with U-Boot overlays, which are more stable and well supported, though they do require a reboot. [36] This overhaul started in late 2017 (with kernel version 4.14), more than five years after Capemgr first started being used. This means that lots of documentation sources contain now-obsolete information and troubleshooting device tree-related problems requires a considerable amount of effort.

## 4.2 Enabling Interfaces

The Sitara AM3358 chip contains an abundance of peripheral interfaces. Approximately half of its terminals can multiplex up to eight modes of signal functions. There are many combinations of pin-multiplexing that are possible, but only a certain number of combinations, or IO sets, are permitted due to timing limitations. A table of all possible pin attributes can be found in the AM335x datasheet. [37]

The BeagleBone Black has two 46-pin headers of GPIO pins, 92 in total. Almost every one of these pins (except for ground and power supply pins) can be configured for one of up to 8 possible operating modes. This configuration can be changed by unloading and loading different device trees. The default configuration of the Debian distribution used in this project is unfavorable for our use - a significant number of pins are allocated for multichannel audio, LCD and HDMI output drivers, which means they cannot be used as traditional GPIO (general-purpose input/output) pins. These allocations can be freed by simply not including the HDMI (or other) functionality in the device tree.

As the operating system used here is supported by both Texas Instruments and BeagleBoard.org, it ships with various device tree overlays included, which enable the developer to pick and choose pin multiplexing sets, which in turn defines what interfaces will be available and enabled. 4. Implementation Process

There is no need to recompile device trees, as there are numerous preprepared device tree blobs located in the /lib/firmware/ folder. To enable or disable different device tree blobs, the /boot/uEnv.txt script, which defines the boot configuration, needs to be edited. A sample snippet of what uEnv looks like in default form can be seen below:

```

###U-Boot Overlays###

###Master Enable

enable_uboot_overlays=1

...

###Additional custom capes

#uboot_overlay_addr0=/lib/firmware/<file0>.dtbo

#uboot_overlay_addr1=/lib/firmware/<file1>.dtbo

...

####Disable auto loading of virtual capes (emmc/video/wireless/adc)