#### ASSIGNMENT OF MASTER'S THESIS

Title: Optimization of ASM code for DLX using LLVM system

Student: Bc. Michal Bureš

**Supervisor:** doc. Ing. Ivan Šimeček, Ph.D.

Study Programme: Informatics

Study Branch: System Programming

**Department:** Department of Theoretical Computer Science **Validity:** Until the end of winter semester 2019/20

#### Instructions

DLX is a RISC processor load/store architecture. It is mostly used in universities as a model to study pipelining technique. LLVM is a modular compilerframework.

Tasks:

- 1) Use clang (frontend for C/C++) to generate C code representation in LLVM IR.

- 2) Implement a new backend for LLVM that transfers LLVM intermediate representation (LLVM IR) to DLX-Assembly code.

- 3) Analyze which optimization would be suitable for DLX.

- 4) Implement those optimizations on LLVM IR.

- 5) Evaluate the efficiency of the implemented optimizations.

- 6) Test the backend and optimizations with C code samples.

#### References

- [1] Clang Compiler User's Manual: https://clang.llvm.org/docs/UsersManual.html

- [2] LLVM Design & Overview: http://llvm.org/docs/

- [3] Writing an LLVM Backend: https://llvm.org/docs/WritingAnLLVMBackend.html

- [4] LLVM's Analysis and Transform Passes: https://llvm.org/docs/Passes.html

- [5] John L. Hennessy and David A. Patterson: Computer Architecture: A Quantitative Approach, Second Edition ISBN: 978-7111074397

- [6] Alfred V. Aho, Monica S. Lam, Ravi Sethi, Jeffrey D. Ullman: Compilers Principles Techniques and Tools ISBN: 0-321-48681-1

- [7] Peter M. Kogge: Architecture of Pipelined Computers First Printing Edition ISBN: 978-0070352377

- [8] Patty Sailer, David R. Kaeli, Philip M. Sailer The DLX Instruction Set Architecture Handbook ISBN: 978-1558603714

doc. Ing. Jan Janoušek, Ph.D. Head of Department doc. RNDr. Ing. Marcel Jiřina, Ph.D. Dean

Master's thesis

# Optimization of ASM code for DLX using LLVM system

Bc. Michal Bureš

Department of Theoretical Computer Science Supervisor: doc. Ing. Ivan Šimeček, Ph.D.

January 8, 2019

# **Acknowledgements**

First of all, I would like to thank my supervisor doc. Ing. Ivan Šimeček, Ph.D. for all his advice. I would also like to thank all the people who helped me and supported me during the writing of this thesis with a special thank you to my family.

# **Declaration**

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. In accordance with Article 46(6) of the Act, I hereby grant a nonexclusive authorization (license) to utilize this thesis, including any and all computer programs incorporated therein or attached thereto and all corresponding documentation (hereinafter collectively referred to as the "Work"), to any and all persons that wish to utilize the Work. Such persons are entitled to use the Work for non-profit purposes only, in any way that does not detract from its value. This authorization is not limited in terms of time, location and quantity.

| In Prague on January 8, 2019 |  |

|------------------------------|--|

|------------------------------|--|

Czech Technical University in Prague Faculty of Information Technology © 2019 Michal Bureš. All rights reserved.

This thesis is school work as defined by Copyright Act of the Czech Republic.

It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

#### Citation of this thesis

Bureš, Michal. Optimization of ASM code for DLX using LLVM system. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2019.

# **Abstrakt**

Tato práce popisuje proces vytvoření nového backendu pro architekturu DLX pomocí LLVM kompilátoru. Prochází všemi nezbytnými součástmi tvorby nového backendu pro kompilátory, jako napřílkad výběr instrukcí nebo přiřazení registrů a popisuje je v rámci LLVM. Analyzuje, jak optimalizace fungují v systému LLVM a implementuje několik optimalizací vhodných pro tuto architekturu, například plánování instrukcí. Výsledkem této práce je nový LLVM backend s optimalizacemi pro architekturu DLX, který může být použit pro kompilaci určitých vyšších programovacích jazyků do DLX assembly kódu.

Klíčová slova DLX, kompilátor, backend, LLVM, optimalizace

# **Abstract**

This thesis describes the process of creating a new LLVM compiler system backend for the DLX architecture. It goes through all the necessary parts of creating a new compiler backend such as instruction selection or register allocation and describes them in terms of LLVM. It looks into how optimizations work in the LLVM system and implement several optimizations suitable for the DLX architecture such as instruction scheduling. The result of this thesis is a new working LLVM backend for the DLX architecture with several optimizations in place. This backend can be used to compile several high-level languages to the DLX assembly code.

Keywords DLX, compiler, backend, LLVM, optimizations

# **Contents**

| ln       | trodi | uction                           | 1  |

|----------|-------|----------------------------------|----|

| 1        | DL    | X Architecture                   | 3  |

|          | 1.1   | DLX Registers                    | 3  |

|          | 1.2   | DLX Data Types                   | 4  |

|          | 1.3   | DLX Addressing Modes             | 4  |

|          | 1.4   | DLX Instruction Set              | 5  |

|          | 1.5   | DLX Memory Layout                | 10 |

|          | 1.6   | DLX Calling Convention           | 11 |

|          | 1.7   | DLX Directives                   | 12 |

|          | 1.8   | DLX Simulators                   | 13 |

|          | 1.9   | WinDLX Traps                     | 14 |

|          | 1.10  | DLX Assembly Code Example        | 16 |

| <b>2</b> | Pipe  | elining Technique                | 19 |

|          | 2.1   | DLX Pipeline                     | 20 |

|          | 2.2   | Pipeline Hazards                 | 22 |

|          | 2.3   | Floating-point Operations        | 27 |

|          | 2.4   | Pipeline Configuration in WinDLX | 30 |

| 3        | LLV   | M System                         | 31 |

|          | 3.1   | LLVM IR                          | 32 |

|          | 3.2   | LLVM IR Language                 | 35 |

|          | 3.3   | LLVM IR Instructions             | 38 |

|          | 3.4   | LLVM Tools                       | 44 |

|          | 3.5   | Clang                            | 44 |

| 4        | LLV   | M Backend for DLX                | 47 |

|          | 4.1   | Analysis of Existing Backends    | 47 |

|          | 4.2   | Target Description               | 48 |

|          |       |                                  |    |

|              | 4.3   | Target Machine                       | 49  |

|--------------|-------|--------------------------------------|-----|

|              | 4.4   |                                      | 49  |

|              | 4.5   | Defining Instructions                | 51  |

|              | 4.6   | Defining Calling Conventions         | 53  |

|              | 4.7   | Target Code Generation               | 53  |

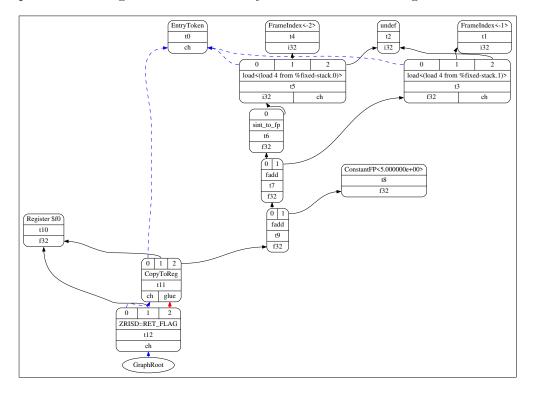

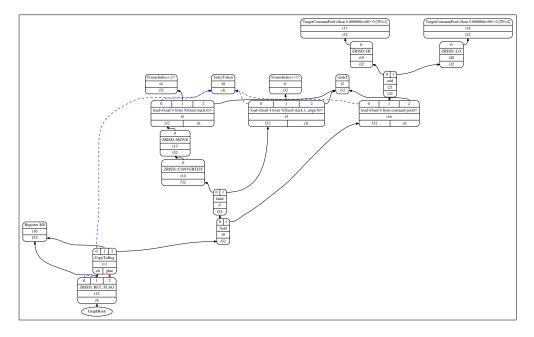

|              | 4.8   | Build Initial SelectionDAG           | 55  |

|              | 4.9   | Legalize SelectionDAG Types          | 57  |

|              | 4.10  | Legalize SelectionDAG Operations     | 57  |

|              | 4.11  |                                      | 61  |

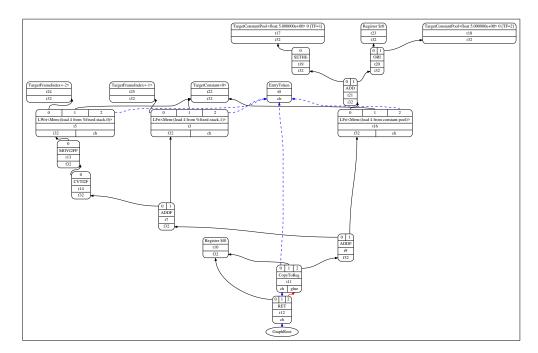

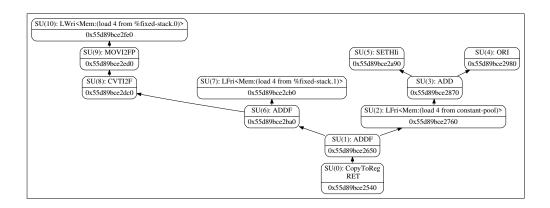

|              | 4.12  | SelectionDAG Scheduling              | 63  |

|              | 4.13  | Build MachineInstr                   | 64  |

|              |       |                                      | 65  |

|              |       |                                      | 67  |

|              |       | - '                                  | 68  |

|              |       | Code Emission                        | 70  |

|              |       | Target Registration                  | 72  |

|              |       | Notes                                | 73  |

|              |       |                                      |     |

| <b>5</b>     | Opt   | imizations                           | 75  |

|              | 5.1   | Analysis of LLVM Optimizations       | 76  |

|              | 5.2   | Instruction Selection                | 80  |

|              | 5.3   | Utilizing Register R0                | 81  |

|              | 5.4   | Instruction Scheduling               | 83  |

|              | 5.5   | Removing Unnecessary Labels          | 89  |

|              | 5.6   | Branch Folding                       | 90  |

|              | 5.7   | Register Rematerialization           | 91  |

|              | 5.8   | Passing Values in Registers          | 92  |

|              | 5.9   |                                      | 93  |

|              | 5.10  |                                      | 96  |

|              | 5.11  |                                      | 96  |

|              |       |                                      |     |

| 6            | Test  | 8                                    | 99  |

|              | 6.1   | 0                                    | 99  |

|              | 6.2   | Testing and Evaluating Optimizations | .02 |

| ~            |       |                                      | ~=  |

| Co           | onclu | sion                                 | .07 |

| Bi           | hliog | raphy 1                              | .09 |

| υ.           | onog  | Tupily                               | .00 |

| $\mathbf{A}$ | Inst  | all 1                                | 15  |

|              | A.1   | Build DLX Backend                    | 15  |

|              |       |                                      | 17  |

|              |       | Tests                                |     |

|              |       |                                      |     |

| $\mathbf{B}$ | Acre  | onyms 1                              | 19  |

# **List of Figures**

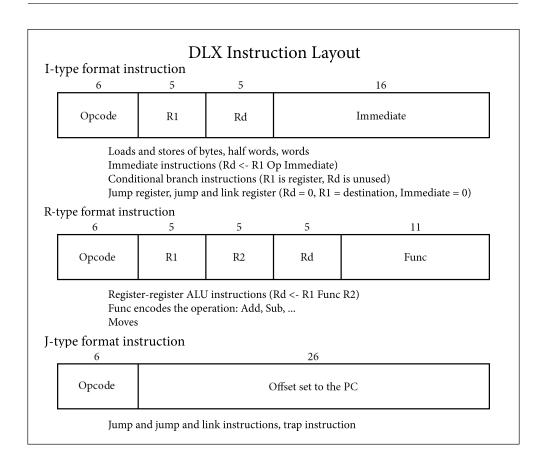

| 1.1  | DLX Instruction Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | DLX Memory Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 |

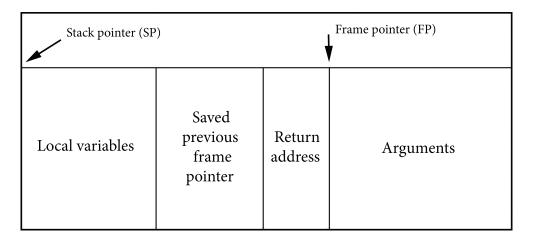

| 1.3  | DLX Stack Frame Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11 |

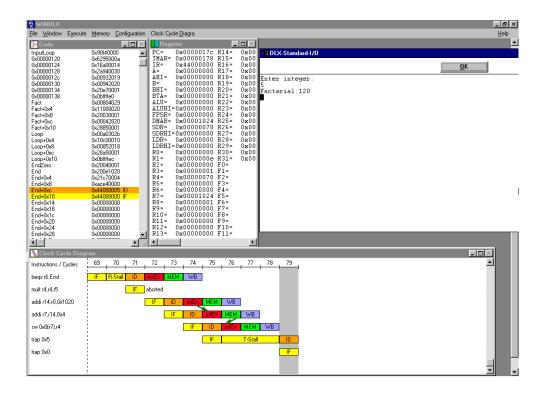

| 1.4  | WinDLX GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15 |

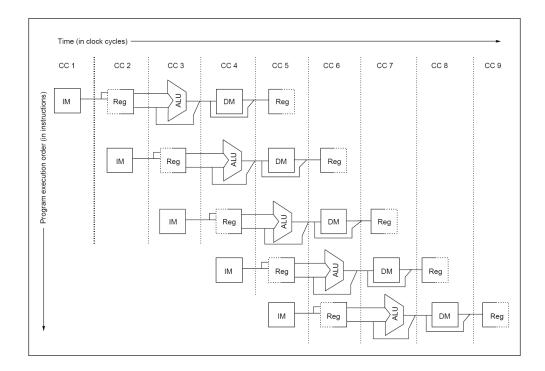

| 2.1  | DLX Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20 |

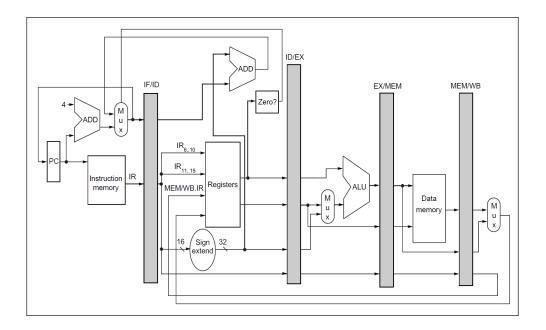

| 2.2  | DLX Pipeline Hardware Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21 |

| 2.3  | DLX Pipeline Datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22 |

| 2.4  | A pipeline stalled for a structural hazard - a load with one memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23 |

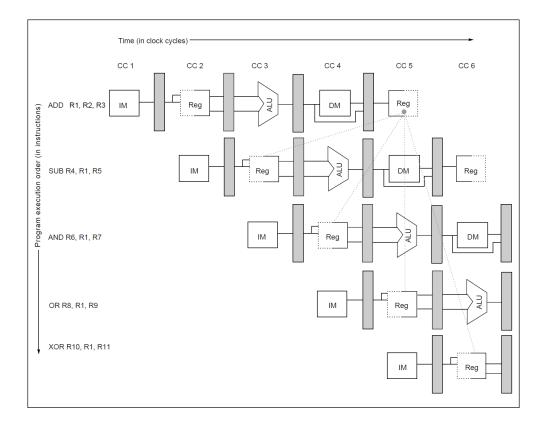

| 2.5  | DLX Pipeline with data hazards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24 |

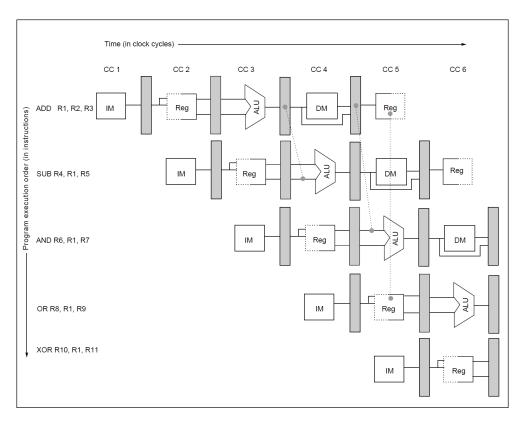

| 2.6  | DLX Pipeline with solved data hazards using forwarding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25 |

| 2.7  | DLX Pipeline using a never-taken scheme when a branch is taken .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27 |

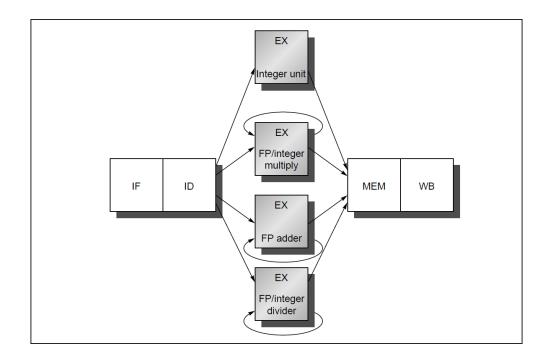

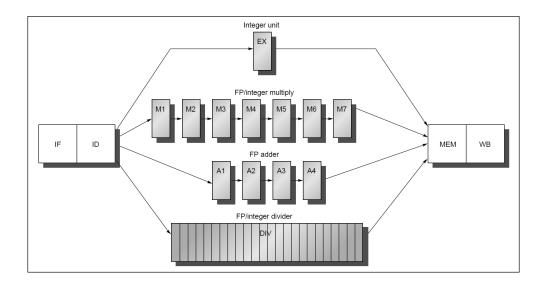

| 2.8  | DLX Pipeline Functional Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28 |