# Czech Technical University in Prague Faculty of Electrical Engineering

# **Doctoral Thesis**

# Czech Technical University in Prague

# Faculty of Electrical Engineering Department of Measurement

# RADIATION TOLERANT POWER ELECTRONICS FOR SPACE APPLICATIONS

**Doctoral Thesis**

Jaroslav Laifr

Prague, November 2018

Ph.D. Programme: P2612, Electrical Engineering and Information Technology Branch of study: 3708V017, Air Traffic Control

Supervisor: *Doc. Ing. Karel Draxler, CSc.* Supervisor-Specialist: *Dr. Pavel M. Trávníček*

| Declaration                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Hereby, I declare, that this Doctoral Thesis is based at all my own work and I have cited all sources I have used in the bibliography. |

| In Prague, November 25 <sup>th</sup> , 2018                                                                                            |

|                                                                                                                                        |

| Prohlašuji, že jsem předloženou disertační práci vypracoval samostatně a že jsem uvedl veškerou použitou literaturu.                   |

| V Praze, 25. 11. 2018                                                                                                                  |

|                                                                                                                                        |

| Jaroslav Laifr                                                                                                                         |

|                                                                                                                                        |

### Acknowledgements

I would like to express my gratitude to my supervisor doc. Ing. Karel Draxler CSc., and my supervisor-specialist Dr. Pavel M. Trávníček, Doc. Ing. Pavel Pačes, Ph.D., next to prof. Ing. Pavel Ripka, CSc., Ing. Vojtěch Petrucha, Ph.D., Ing. Michal Janošek, Ph.D. and Doc. Dr. Ing. Pavel Kovář who gave me once in a lifetime opportunity to work on the space-related topic, one of a kind at the *Czech Technical University in Prague*, for their scientific and university guidance, invaluable comments and patience with my studies.

Secondly, I would like to thank my colleagues at the *Astronomical Institute of the Czech Academy of Sciences*, mainly to Dr. Štěpán Štverák, Ing. Ondřej Šebek and Dr. Petr Hellinger for establishing efficiently working team. Also to the main technical lead of the *Radio and Plasma Waves Investigation consortia* Walter Puccio from the Institute of Space Physics in Uppsala and to Sven Landström from *ESA TEC Directorate* for unique european collaboration and advices, and to all of my Bachelor and Master students for their enthusiastic approach and co-development of scientific goals, namely Antonín Štěpán, Jan Papaj, Lukáš Houštecký, Lukáš Forman, Matej Straka and Radovan Vlach during the CzechTechSat project development.

The work on this thesis was supported by the *Student Grant Competition of CTU* and *Czech PRODEX Committee / Czech Ministry of Education Youth and Sports*.

Finally, yet importantly, I would like to thank my family for their support and patience throughout the study period. My research would not have been possible without them.

#### **Abstract:**

The aim of this thesis is to summarize the state-of-the-art satellite electronics design, find its bottlenecks and propose a novel, scientific-based approaches on the space power systems development addressing rapidly evolving so-called "NewSpace" ecosystem.

The modern consumer-driven electronics with rising computational power and miniaturization demands similar to the *Moore's Law* for computers brings new technological challenges and problems. The *NewSpace community* needs to understand them to successfully conduct its presence in space, both aboard earth-orbiting and interplanetary missions. It is the satellite (manned and unmanned) and aerospace industry, private or government-led institutions which need to follow the technological and scientific progress by faster steps if want to utilize the full potential of the scientific and technological progress in commercially available markets and technological breakthroughs.

Initial studies are the follow-up of the author's Master thesis: Fluxgate Magnetometer for Satellite Attitude Control, carried on within the multi-faculty CubeSat project CzechTechSat led by the author as the Principal Investigator. Students were implementing authors' hypotheses within their bachelor and master thesis terms and supported their research and validation.

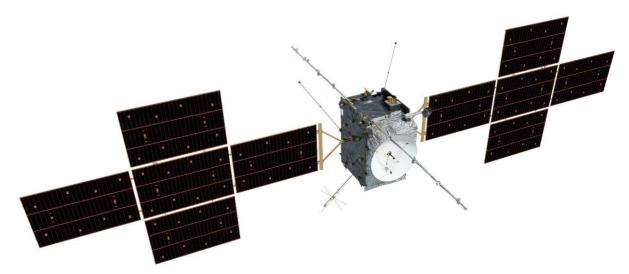

Key findings were implemented as an practical example of the thesis utilization within the Low Voltage Power Supply unit for the Radio and Plasma Waves Investigation instrument selected to be flown aboard the European Space Agency L-Class mission called JUICE (Jupiter Icy Moon Explorer) into the Jovian system in 2023. Also in the project CRREAT by the realization of the ultra low power dosimeter for small satellites.

The thesis is also a base of the spacecraft electronics design E-Book called "*NewSpace Economically*" prepared to be released to the small satellite community in 2019.

Keywords: ESA, RPWI, JUICE, CubeSat, NewSpace, Radiation, Power Supply, Satellite

#### **Abstrakt:**

Cílem výzkumu v předložené disertační práci je shrnout dosud používané návrhy elektroniky vesmírných družic, poukázat na kritické body a rizika s tím spojená a navrhnout postupy založené na vědeckém bázi, beroucí do úvahy konzervativnost spojenou s neochotou ke změnám v uvažování nad návrhem kosmických systémů výkonové elektroniky. Nedílnou součástí nového přístupu je i snížení celkových nákladů (energetických i materiálních) s přihlédnutím k modernímu, tzv. "NewSpace" ekosystému.

Rychle se vyvíjející trh se spotřební elektronikou se svými rostoucími nároky na výkon a miniaturizaci, podobně jako *Moorův zákon* ve vývoji výkonu počítačů, přináší nové poznatky a problémy, které *NewSpace* komunita musí plně pochopit, pokud chce bezpečně působit ve vesmírném prostoru, a to jak na oběžné dráze Země, tak při meziplanetárních misích. Je to převážně kosmický (pilotovaný i nepilotovaný) a letecký průmysl, soukromé i vládní agentury, kteří musí vyvinout veliké úsilí, aby udržely krok s technologickým vývojem a průlomovými výsledky v komerční sféře a využily tak její plný potenciál.

Úvodní studium problematiky vychází z autorovy diplomové práce na téma *Magnetometr pro řízení polohy satelitu*, následované multifakultním projektem nanosatelitu *CzechTechSat* jehož je hlavním řešitelem. Studenti pod vedením autora práce implementovali navrhované hypotézy v rámci svých bakalářských a diplomových prací a pomáhali tak k jejich realizaci a ověření.

Klíčové prvky práce byly poté implementovány jako praktická ukázka využitelnosti v rámci projektu *ESA-Lunar Lander/L-DEPP/LPM* a nízkonapěťového napájecího zdroje přístrojového balíku pro studium radiových a plazmových vln (*RPWI*), vybraného pro let na misi evropské kosmické agentury *ESA* s názvem *JUICE*. V rámci něj byl také vyvinut speciální systém potlačování rozběhových proudů pro vesmírné aplikace. Plánované vypuštění sondy do vesmíru je stanoveno na rok 2023. Dále v projektu *CRREAT* realizací nízkopříkonového širokospektrálního dozimetru pro malé satelity.

Práce je rovněž základem pro připravovanou elektronickou publikaci (*E-Book*) pro vývojáře elektronických systémů malých družic s názvem "*NewSpace ekonomicky*", připravovaná k distribuci v roce 2019.

Klíčová slova: ESA, RPWI, JUICE, CubeSat, NewSpace, radiace, napájecí zdroj, kosmická sonda

# **Table of Contents**

| 1. Inti | roduction                                                         |             |

|---------|-------------------------------------------------------------------|-------------|

| 1.1.    | Ionizing Radiation Impact on Semiconductors                       | 10          |

| 2. Sta  | te of the Art Space-Grade Power Electronics                       | 11          |

|         | Components for Space-Grade Power Supplies                         |             |

| 2       | .1.1. Resistors                                                   |             |

| 2       | .1.2. Capacitors                                                  | 9           |

|         | .1.3. Magnetics                                                   | •           |

|         | .1.4. Rectifiers                                                  |             |

|         | 1.5. Power Switches                                               |             |

|         | 1.6. Voltage References                                           |             |

|         | 1.7. Opto and Photo Elements                                      |             |

|         | .1.8. Electromechanical Elements and SSR                          |             |

|         | .1.9. Integrated Circuits - Analogue                              |             |

|         | .1.10. Integrated Circuits - Digital                              |             |

|         | 1.11. I WM Controllers                                            | 20          |

|         | 1.13. Solar Cells                                                 |             |

|         | 1.1.14. Alternative Power Sources                                 |             |

|         | 1.15. Chemistry for Assembly and Finish                           |             |

|         | Hybrid Space-grade Power Supplies Overview                        |             |

|         | jectives of the Thesis                                            |             |

|         | potheses                                                          |             |

|         |                                                                   |             |

|         | Sults                                                             |             |

|         | Objective A)                                                      |             |

| _       | 2.1. The CzechTechSat Project                                     |             |

| _       | 2.2. ESA / Lunar Lander / L-DEPP Project, LPM PoC                 | 40          |

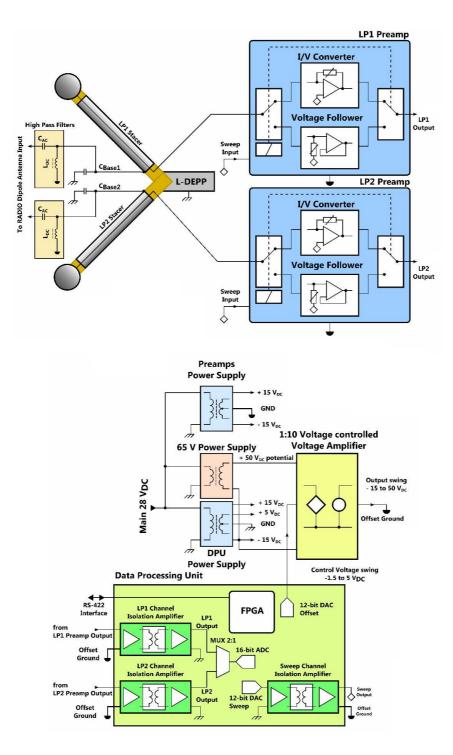

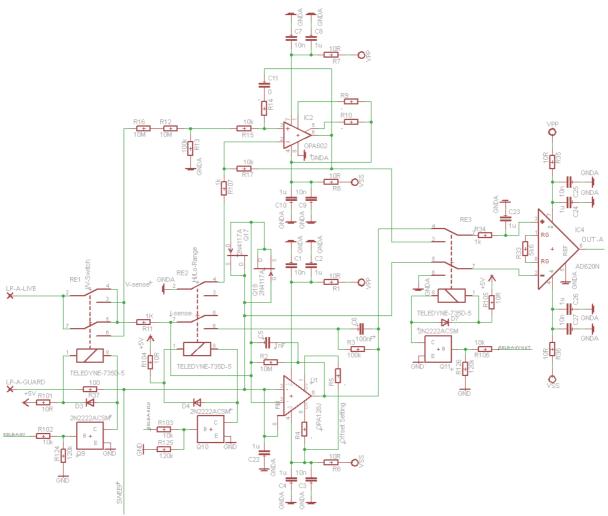

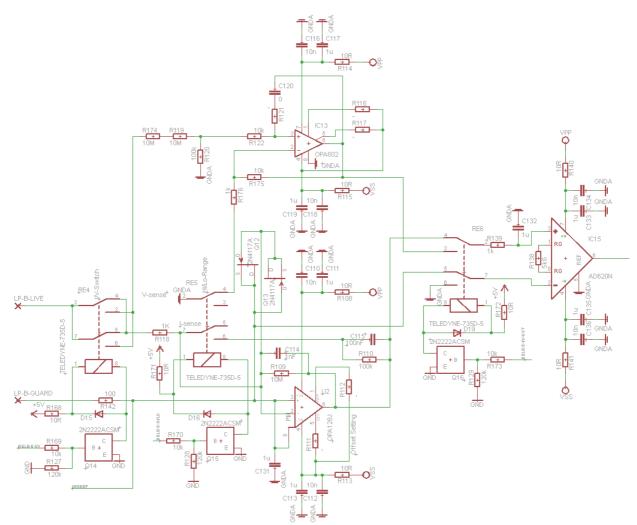

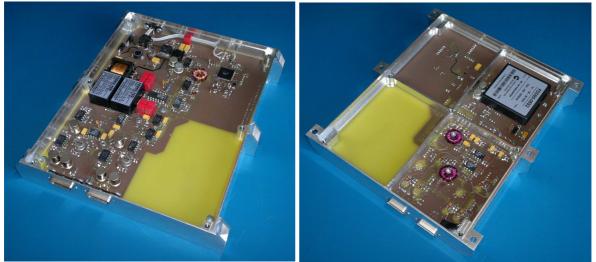

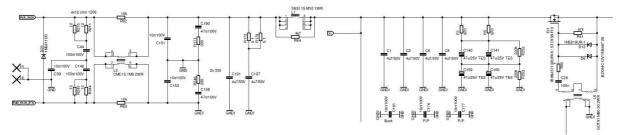

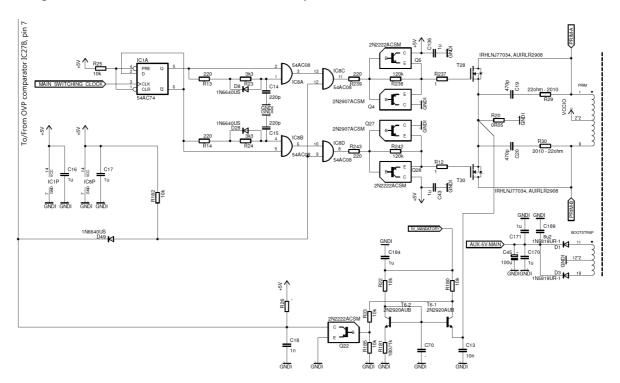

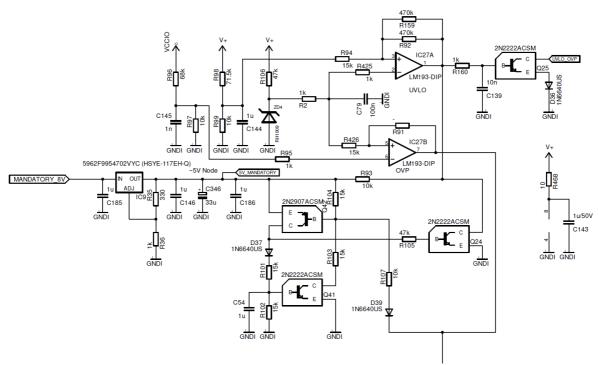

| ·       | 5.2.2.1. LPM PoC Electrical Design                                |             |

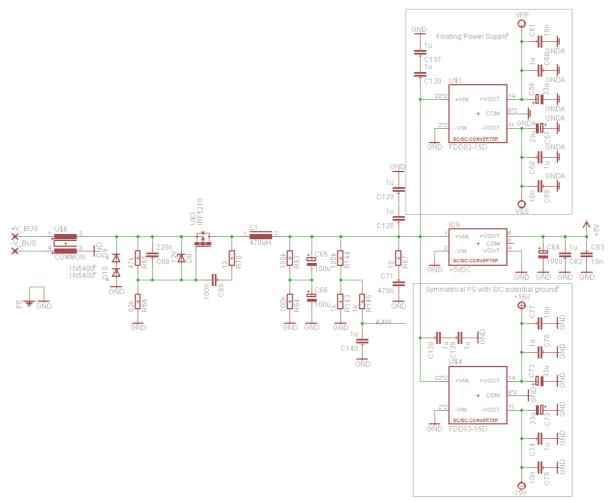

| _       | 5.2.2.2. LPM PoC Low Voltage Power Supply                         |             |

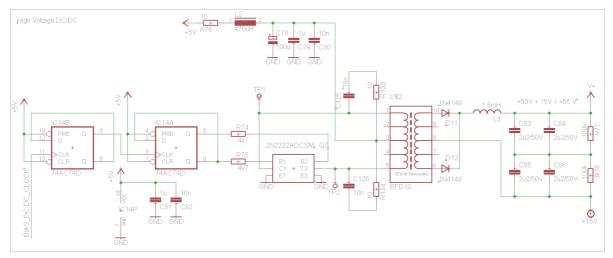

| _       | 5.2.2.3. LPM PoC High Voltage Power Supply                        |             |

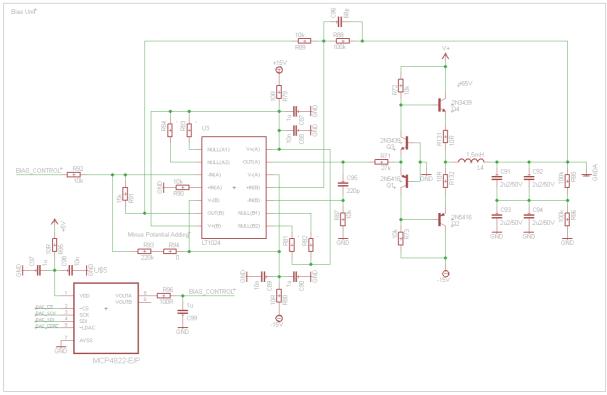

|         | 5.2.2.4. LPM PoC Bias Unit                                        |             |

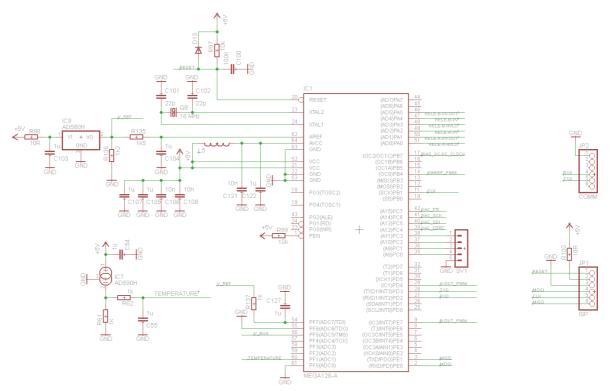

|         | 5.2.2.5. LPM PoC Microcontroller                                  |             |

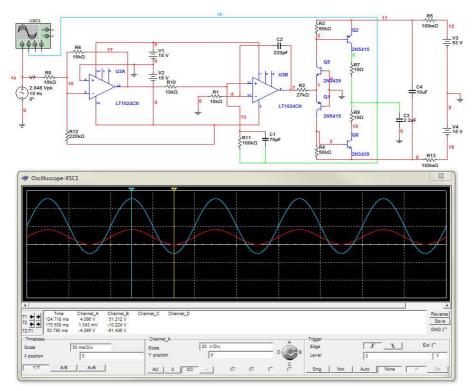

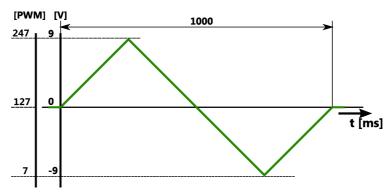

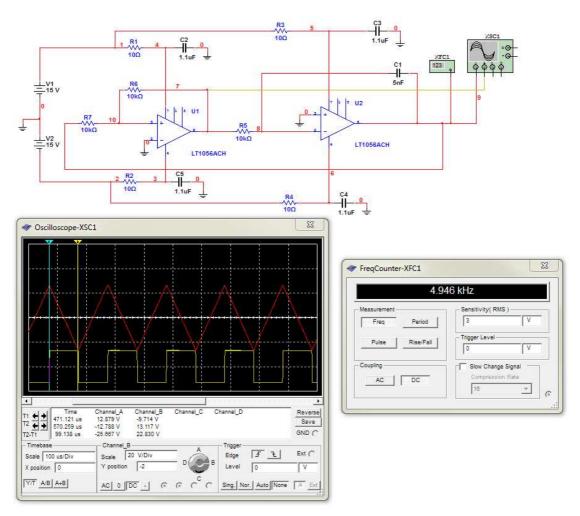

| _       | 5.2.2.6. LPM PoC Voltage Sweep Generator                          |             |

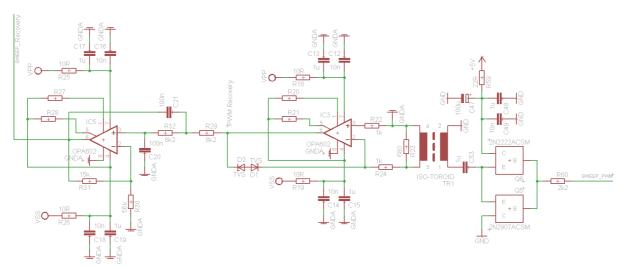

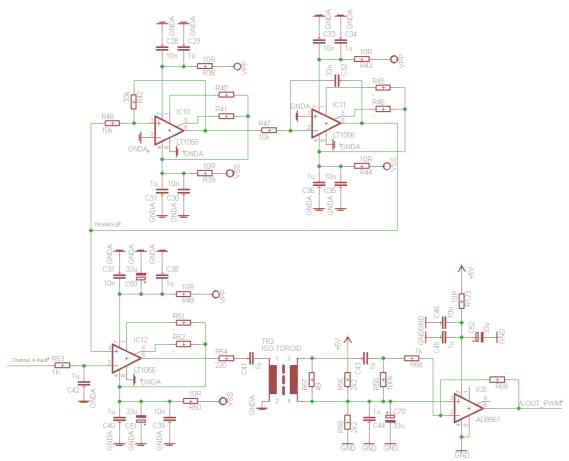

| _       | 5.2.2.7. LPM PoC Preamplifiers 1 & 2                              |             |

| _       | 5.2.2.8. LPM PoC Isolation Amplifiers                             |             |

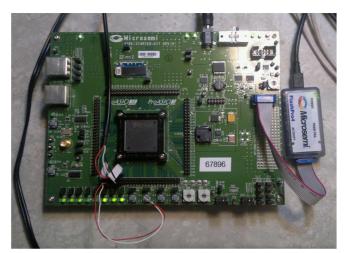

| -       | 5.2.2.9. LPM PoC FPGA Firmware Design and Digital Data Processing |             |

|         | Objective C)                                                      |             |

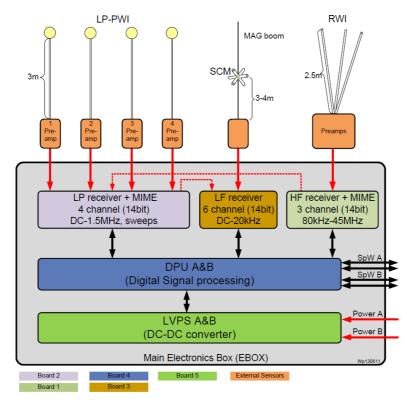

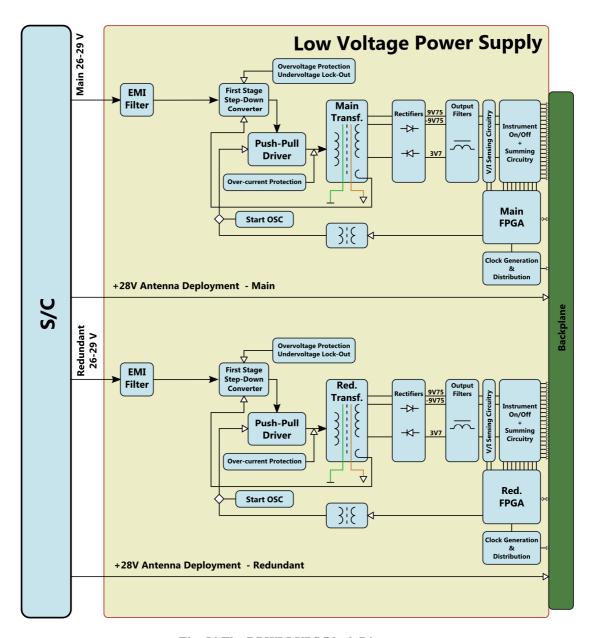

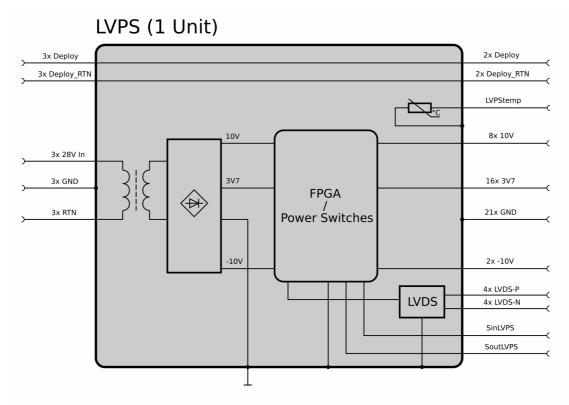

|         | .3.1. RPWI LVPS Topology                                          |             |

| _       | 3.2. RPWI LVPS Thermal Design                                     |             |

|         | .3.3. RPWI LVPS Electrical Interfaces                             |             |

|         | .3.4. RPWI LVPS Grounding Block Diagram                           |             |

|         | .3.5. RPWI LVPS Frequency Plan                                    |             |

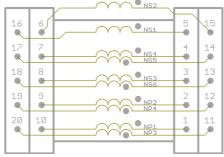

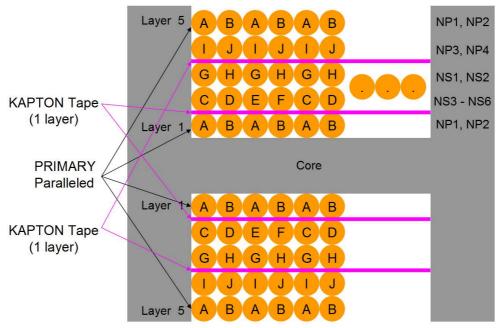

|         | 3.6. RPWI LVPS Magnetics and Main Transformer Design              | 68          |

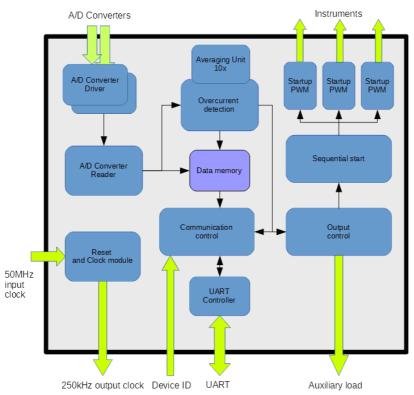

| 5       | .3.7. RPWI LVPS FPGA Firmware Block Diagram and Functionalitie    | <i>s</i> 70 |

| 5       | .3.8. RPWI LVPS FPGA Communication Interface                      |             |

| 5       | .3.9. RPWI LVPS Clock Distribution and Management                 |             |

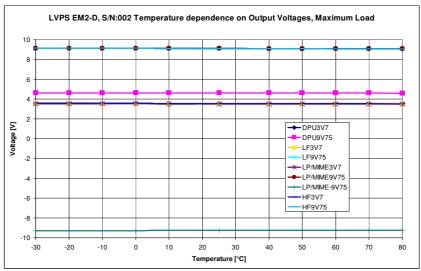

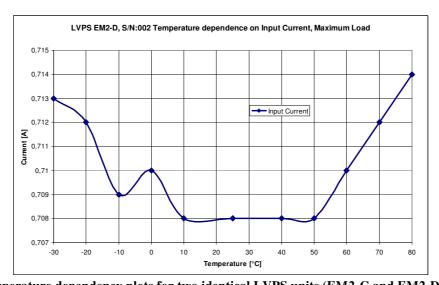

|         | .3.10. RPWI LVPS Thermal Testing                                  |             |

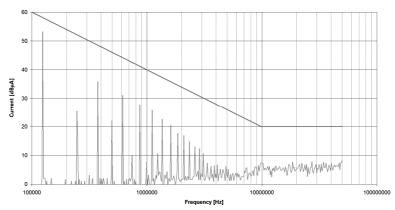

|         | .3.11. RPWI LVPS EMC Measurements                                 |             |

|         | A Novel Digital Inrush Current Limiter                            |             |

| _       | 4.1. RPWI LVPS Power Distribution Unit                            |             |

|         | Objective D)                                                      |             |

|         | nclusions                                                         | ,           |

| 7. List | t of Publications                                                 |             |

| 7.1.    | Published Papers                                                  |             |

| 7.2.    | Submitted Papers                                                  |             |

| 7.3.    | Functional Samples                                                |             |

| 7.4.    | Associated Master Theses                                          |             |

| 7.5.    | Media and Public Relations                                        | 90          |

| Acronym                     | Definition                                                                                    |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------|--|--|

| ADC                         | Analog-to-Digital Converter                                                                   |  |  |

| CBK PAN                     | Centrum Badań Kosmicznych Polskiej Akademii Nauk                                              |  |  |

| CRC Cyclic Redundancy Check |                                                                                               |  |  |

| CRREAT                      | Research Center of Cosmic Rays and Radiation Events in the Atmosphere                         |  |  |

| DPU                         | Data Processing Unit                                                                          |  |  |

| EBOX                        | Electrical Box                                                                                |  |  |

| ESA                         | European Space Agency                                                                         |  |  |

| FPGA                        | Field Programmable Gate Array                                                                 |  |  |

| HDR                         | High Dose Rate                                                                                |  |  |

| HF                          | High Frequency receiver                                                                       |  |  |

| HK                          | Housekeeping                                                                                  |  |  |

| JUICE                       | Jupiter Icy Moon Explorer                                                                     |  |  |

| LCL                         | Latching Current Limiter                                                                      |  |  |

| LDR                         | Low Dose Rate                                                                                 |  |  |

| LF                          | Low Frequency receiver                                                                        |  |  |

| LP/MIME                     | Langmuir Probe / Mutual Impedance Measurement Equipment                                       |  |  |

| LSB                         | Least Significant Bit                                                                         |  |  |

| LVDS                        | Low Voltage Differential Signaling                                                            |  |  |

| LVPS                        | Low Voltage Power Supply                                                                      |  |  |

| MSB                         | Most Significant Bit                                                                          |  |  |

| OCP                         | Overcurrent (Protection)                                                                      |  |  |

| OVP                         | Overvoltage (Protection)                                                                      |  |  |

| PDU                         | Power Distribution Unit                                                                       |  |  |

| PoL                         | Point of Load                                                                                 |  |  |

| RPW                         | Radio and Plasma Waves instrument, LESIA, Meudon, Paris, France                               |  |  |

| RPWI                        | Radio and Plasma Waves Investigation instrument, Institute for Space Physics, Uppsala, Sweden |  |  |

| SCM                         | Search Coil Magnetometer                                                                      |  |  |

| SCR                         | Silicon Controlled Rectifier (Thyristor)                                                      |  |  |

| SEB                         | Singe Event Burnout                                                                           |  |  |

| SEE                         | Single Event Effect                                                                           |  |  |

| SEL                         | Single Event Latchup                                                                          |  |  |

| SPF-Free                    | Single Point of Failure Free Design                                                           |  |  |

| TC                          | Telecommand                                                                                   |  |  |

| TID                         | Total Ionizing Dose                                                                           |  |  |

| TM                          | Telemetry                                                                                     |  |  |

| TM/TC                       | Telemetry/Telecommand                                                                         |  |  |

| UART                        | Universal Asynchronous Receiver/Transmitter                                                   |  |  |

| UVLO                        | Undervoltage Lockout                                                                          |  |  |

| XNOR                        | Negative Exclusive OR                                                                         |  |  |

#### 1. Introduction

In the past decade a dramatic rise of small satellites, *CubeSats*, *PocketQubes* and microsatellites shown that the conservative approach of building space electronics is no longer in line with the technological progress in commercial electronics. Moreover, it turned out, that even commercially available parts are able to withstand the environment of space (vacuum, radiation, thermal cycling) for at least long enough time to fulfill short mission needs, if properly used. The new era of space exploration, such as first CubeSats for deep space flight to Mars (*MarCO-A*, *MarCO-B*, [R-23]) is known as the "*NewSpace*". To maximize the yield of the NewSpace age, this Thesis shall help the designers, mission owners and operators and scientific community to implement techniques to prolong the operational lifetime.

The semiconductor die layout, physical chip properties, materials, mechanical housing, shielding, adhesives or coating are the facts which could determine the electronic system failure rate, reliability and lifetime. The Thesis summarizes ideas, principles and already performed research of circuit design, component selection, software features, data protection, system concepts considerations, practical realization and test results.

Proposed approaches were applied in two *Czech Ministry of Education, Youth, and Sports* grant supported scientific instruments under the *ESA PRODEX* programme and two university and public-funded projects. Namely the *ESA / JUpiter ICy moon Explorer (JUICE)* / Radio and Plasma Waves Investigation (*RPWI*) / Low Voltage Power Supply (*LVPS*), the ESA / Lunar Lander / Lunar Dusty Environment and Plasma Package (*L-DEPP*) – Definition Study / Lunar Plasma Monitor (*LPM*), the *CzechTechSat – The Experimental University Picosatellite Platform* and *CRREAT*. Electrical system topologies and concepts are all focused to be able to withstand the operations within the harsh and condition-critical environments following the initial work developed during the Master Thesis, *Fluxgate Magnetometer for Satellite Attitude Control*.

# 1.1. Ionizing Radiation Impact on Semiconductors

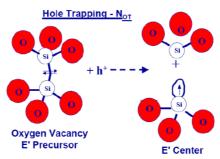

The behavior of discrete semiconductors influenced by the different radiation sources such as particle or photonic irradiation causing ionizing damage, non-ionizing changes or single event effects during the biased operations were studied and summarized in [PP-3]. The paper gives an overview of the key parameters showing most significant changes with respect to accumulated radiation dose in PN junction, *BJT*, *JFET/MESFET*, *MOSFET*, *CMOS*, *IGBT*, *HEMT and SiC* components.

The space radiation influence on electronic systems depends strongly on the orbital altitude and inclination. It is therefore a different task to design a satellite system in the case of the deep space flight.

There are several, scientific community-accepted, software platforms to perform the expected radiation estimations such as the *CREME96 [R-1]*, *SPENVIS [R-2] or SPIS [R-3]*. For the simulation of shielding properties the *GEANT4 [R-4]* or *SHIELDOSE* (part of the *SPENVIS*) tools are often used. To study the particle interaction with matter on semiconductor level, the *SRIM* [R-5] software can be employed. However, in the case of space mission the calculation is often done by payload study team, launch provider or a mission specialist and announced at the project kick-off as a one of the most important design drivers. The ESA convention is to apply a margin of hundred percents on finally identified dose. In the case of *JUICE/LVPS* the targeted Total Ionizing Dose (TID) has been determined to be *50 krads(Si)*, Therefore whole design shall withstand at least *100 krad(Si)*.

# 2. State of the Art Space-Grade Power Electronics

## 2.1. Components for Space-Grade Power Supplies

The radiation hardened portfolio of components intended for current or voltage mode space-grade power supplies and power electronics such as motor controllers or H-bridges is quite broad on the international market, mostly with vendors located in USA, EU, UK and Japan. The offer includes complete discrete components portfolio such as bipolar transistors, BJT arrays, MOSFET transistors, JFETs, rectifiers, Schottky diodes, Zener diodes or voltage references. Integrated circuits such as PWM controllers, voltage references and TTL or CMOS logic families are available as well, however with much variable total ionizing dose (TID) tolerance with respect to discrete parts, due to the high integration complexity.

The following breakdown list of basic electronic parts represents DISCUSSION (*D:*) of typical EEE part categories and their sensitivity to harsh environment of space with author's RECOMMENDATION (*R:*) about its key parameters to observe and pay attention to during the system design phase based on seven years long research period at the CTU FEE.

#### 2.1.1. Resistors

**D:** Surface mounted, through hole or screw "wing" mounted shunt resistors are naturally insensitive to radiation in space. Variations and parametric drifts may be observable at extremely high doses (more than hundreds of MRads) due to physical destruction of the resistive material structure. However, such high doses could be omitted from robustness improvement consideration, as the accompanied semiconductors are typically already fully out of the operational range and shows no functionality.

Conventional ceramic resistor package disintegration or microscopic cracking may arise due to excessive thermal cycling and different thermal expansion coefficients with respect to the PCB. Typical unit temperature cycling during the dusk and dawn cycle when orbiting the Earth, other planet or self tumbling could be expected with reasonably low dT/dt, due to the hardware thermal capacity. Resistor package is then tempered well in line with the temperature of the target system via solder joints and thermal transfer from the PCB or unit frame, in case of wing mounted resistors.

**R:** Mounting the SMD rectangular package with elevated height above the PCB using so-called tin standoff (0.2 - 1 mm) increases the amount of metallic material in series with resistor body to spread the total thermal expansion stress.

Special case is the electronic system immersed directly into space, such as antenna or sensor preamplifier. The active thermal control heating elements in combination with encapsulation under the coverage of the *Multi Layer Insulation (MLI)* are then necessary to consider to stabilize the temperature range and average-out excessive thermal loading range.

Fig. 1 Multilayer Insulation example as a protective layer for spacecraft sensor (left), the composition of temperature insulating layers of the MLI (right), [I-1].

**D:** Much dangerous operational condition from thermal stress and mechanical rupture point of view occurs when the power to dissipate is changing as a step load. Over-dimensioning of the total power loss allowed in package shall be considered at least 200% or more of nominal power. The goal is to maximize the thermal conductivity according to 2.1.1 below

$$\frac{1}{R_{\theta}} = \frac{Q \cdot l_{path}}{A_{surface}(T_{element} - T_{ambient})},$$

(2.1.1)

where  $R_{\theta}$  is thermal resistivity of the conductive surface Q is the amount of heat per unit time,  $l_{path}$  represents the length of the heat transfer path,  $A_{surface}$  is the heat transfer cross-section and T represents temperatures of the heating element and ambient environment respectively. When considering the real environment, a total sum of at least three components have to be taken into account: 1) the thermal resistivity of the resistive element body dissipating heat, 2) thermal resistivity of pins, legs or conductive strap or wire of the component, the mounting material such as tin/lead compound and finally 3) the thermal properties of the PCB itself.

**R:** Where possible, in case of SMD type of component, reverse packaging size with longer pads and shorter sides for better thermal conductivity is recommended to maximize the natural thermal transfer area, thus increasing the thermal conductivity.

Fig. 2 Example of the improved heat dissipation performance using reversed package, [I-2].

Flat thermal filler such as *Mica* or *CHO-THERM*® [R-6] would be used for wing-mounted packages and high power shunts. A droplet of thermally conductive epoxy glue would be utilized for THT/axially leaded resistors to fix them in position and to support the thermal runaway with good galvanic insulation.

Overvoltage stress condition could be encountered in high voltage circuits with excessive voltage peaks, such as in inductive load cases (relays, motors, filter inductor dampers, etc.). It is then necessary to check the voltage strength of the conformal coating to prevent coronal short-circuits. In the place where high voltage, high power resistor is assumed to be placed, the reverse packaging is wise to re-consider to increase the distance between electrodes, or to employ two or more resistors in series with adequately less resistance with respect to their amount to split the power dissipation and voltage stress over bigger/longer area/distance, respectively.

Except the coronal arcing short-circuits, resistors often results in open-circuit state due to fast excessive surge current applied such as from the inductive load. Where necessary such as in case of the feedback loop of the *PID* error amplifier, the ladder of four resistors of the same value would be used in configuration 2-in-parallel in series with 2-in-parallel. Then, when single resistor is opened by failure, the total resistance of the ladder increases by factor of 50 %. In case of short of one of resistors, the total resistance fall by a factor of 50%, which could still maintain the circuit in operational range with no fatal change of behavior as it would result in single component case (opened, or short).

#### 2.1.2. Capacitors

**D:** There are several types of capacitors used in space electronics, with exception of commercial electrolytic and non-hermetic capacitors known mostly from PC power supplies and general electrical appliances for home and office use. The commercial production of *low ESR* capacitors with electrolytic filling has been mastered to deliver components with high surge current capability and very high capacity in limited volume. However, under conditions of vacuum, such components evaporate their dielectrics into open space quickly through their rubber feedthroughs and are unable to work without any hermetization. It is clear, that for the square wave filtering in space-grade rectifiers, the commercial electrolytic capacitor portfolio is not available and have to be replaced by different technology. From reliability point of view, the use of electrolytic capacitor encapsulated in hybrid package is still very risky to use.

The radiation damage again could be omitted from consideration due to the natural radiation insensitivity up to extremely high radiation dose levels destructing the physical properties of the capacitor material.

Mostly multilayer capacitors (*MLCC*) in SMD packages are used for low and medium range of capacitance (pF to µF). Highly stable capacitors known as the *Type-I* could be found in the range of picofarads up to several tens of nanofarads. They are mostly used for timing circuits or very high frequency operations due to their dielectrics thermal and applied voltage stability similar to *NPO* (*negative positive zero*). Multilayer capacitors, mostly known as the *Type-II* with high permittivity dielectrics such as X5R or X7R contains much bigger area of capacitor plates and due to the requirement to fit the same volume of the package as *Type-I*, might be considered as more susceptible to short-circuit failure.

**R:** The ladder configuration would be utilized to compensate one component failure, similarly as in case of resistors. The probability of short circuit failure of ceramic capacitors is generally higher than the probability of open-circuit failure of resistors due to higher amount of parallel layers in the same passive chip package volume. Soldering temperature and stress increases the failure probability, when the package is hand-soldered rather than reflow processed, bent or mechanically stressed. With machine soldering, the temperature profile is better equalized over the whole SMD capacitor body and expands its dimensions homogenously.

When high capacity storage is needed in order of tens to thousands of microfarads, mostly tantalum capacitors are utilized. Due to the physical principle of the tantalum component, the dielectric voltage strength is naturally lower than with respect to ceramic capacitors of the same size. Thus, ladder configuration of four capacitors is often employed when the target voltage is above ~20 V, which is a typical case for 28 V bus. Tantalum capacitors are also typical for their internal discharging leakage current in order of tens to hundreds of microAmps, dispersion of parameters is typical even within the manufactured batch. Thus the compensating resistor divider connected in parallel with capacitor ladder, splitting the leakage current in order of at least similar or one magnitude higher (around 1 mA, typ. across the tantalum capacitor) is recommended, to prevent overvoltage conditions.

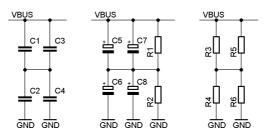

Fig. 3 Fully capacitive (left), Tantalum-Resistor and Resistor-Resistor (right) ladder schematics.

In Fig. 3 the typical configuration of three basic ladders is depicted. The fully capacitive ladder of capacitors of the same capacity C1-C4 and rated to bus voltage is used to prevent short circuit failure in case of ceramic capacitors. Tantalum capacitor bank C5-C8 shall be accompanied with resistive divider R1, R2 to split equally the different leakage current causing voltage imbalance between low and high side of the capacitive chain. With no equalization, the applied voltage per capacitor may easily exceed rated limit. The 4C+2R ladder is recommended also to prevent short circuit failure immunity, at a cost of large footprint area occupied, instead of conventionally utilized single capacitor. The total amount of tantalum capacitors is thus the design trade-off between the available footprint area and risk management.

Maximum power dissipation caused by ripple current and applied AC voltage have to be considered as the internal ESR component ( $m\Omega$  up to  $\Omega$ ) is responsible for the thermal dissipation and may lead to overheating or thermal damage of the tantalum structure. Formula 2.1.2a describes maximum allowable RMS current applied to tantalum capacitors taking into account maximum power dissipation specified by manufacturer and ESR at given working/switching frequency. Similar approach would be studied for applied RMS voltage, where in 2.1.2b the  $Z_f$  is the impedance of the capacitor at given working/switching frequency.

$$I_{RMSMax} = \sqrt{\frac{P_{Max}}{ESR_f}}, \qquad V_{RMSMax} = Z_f \sqrt{\frac{P_{Max}}{ESR_f}},$$

(2.1.2a), (2.1.2b)

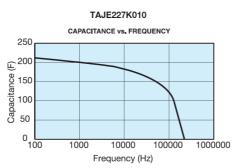

Furthermore, the frequency dependence of tantalum capacitor limits the target use in most of switch mode power supplies or power converter applications. It shall not be used for frequencies above approximately 100 kHz [R-7]. According to the manufacturer, as an example of the capacitors from the *AVX*, the *TAJ* family becomes inductive, when the operating frequency exceeds the resonance point (Fig.4 0.5 - 5 MHz range). Most probably because the granular conductive structure of the electrodes represents the inductive elements, which dominates over the capacitive part in mentioned tens to hundreds kHz frequency range.

Fig. 4 An example of the capacitive drop with respect to high frequency ranges typical for DC-DC converters, [R-7].

Therefore, it is necessary to design the high frequency blocking and filtering power circuits around high capacitance ceramics with paralleling to achieve the desired capacitance or utilize damping resistors or power inductors as low pass filters in series with tantalums. The worst case requirement in terms of the circuit design is the combination of high voltage - high capacity such as input bus filters. The designer have to expect the need for high footprint area on the target PCB, which would be covered by single electrolytic capacitor in commercial electronics design.

#### 2.1.3. Magnetics

D: Inductive components utilized in space-grade power electronics (except special scientific sensors) could be divided into: power inductors, low power pulse transformers, medium and high power transformers and RF coils/RF transformers. Whilst the RF coils are mostly custom-made in terms of size, inductance, material composition and could not be easily categorized, the key parameter is the quality of the wire enamel to prevent evaporation under the vacuum conditions or high power dissipation leading to overheating and/or enamel evaporation. Short circuit of internal turns caused by inappropriate filling chemistry may be a result of the overstressing the component by excessive current ripple or high frequency components of the current, acting as high frequency inductive heating caused by eddy currents. The correct calculation of total inductor power losses is a complex task exceeding the scope of this thesis, when taking into account core material properties such as shape, air gap, etc. However, sufficient order of magnitude precision approach would be found by equations 2.1.3a and 2.1.3b

$$P_{ConductorRMS} = I_{RMS}^2 \cdot R_{Conductor(f)}, \qquad (2.1.3a)$$

where  $I_{RMS}$  represents the passing-through current,  $R_{Conductor(f)}$  represents ohmic resistance of the conductor at given frequency taking into account the skin effect, and approximate estimation of the core losses

$$P_{Core} \propto k \cdot f^{x} \cdot \Delta B^{y} \cdot V_{e}, \qquad (2.1.3b)$$

where k is the constant for core material,  $f^{x}$  is the frequency at frequency exponent, B is the magnetic flux with magnetic flux exponent y and  $V_{e}$  is the effective core volume.

R: During the selection of power inductors, a special care shall be taken on the rated frequency, as manufacturers mostly defines the operating conditions over single frequency only. Then the comparison between the conductor losses  $P_{ConductorRMS}$  and inductive losses in ferrite  $P_{Core}$  have to be calculated and equalized. If the power loss due to high frequency current ripple is bigger than conductor losses, the Curie temperature of the ferrite material limits the component use and bigger package shall be selected.

The equilibrium shall be achieved between both power loss components to define the correct package, as the bigger inductor bobbin requires higher length of the copper wire and vice versa. High volume package also decreases the self resonant frequency, which could be an important design limit in case of low frequency input/output power filters by Tab.: 1.

Tab.: 1 Power magnetics optimization decision flow.

| Calculation Result               | Action                          |

|----------------------------------|---------------------------------|

| $P_{ConductorRMS} > P_{Core}$    | Choose component rated for      |

|                                  | higher current, with wider      |

|                                  | conductor diameter or amount    |

|                                  | of conductors, to wind parallel |

|                                  | windings in transformers.       |

| $P_{ConductorRMS} \sim P_{Core}$ | Less than a magnitude           |

|                                  | difference ~ design is          |

|                                  | optimized.                      |

| $P_{ConductorRMS} < P_{Core}$    | Choose component with bigger    |

|                                  | ferrite/core material/volume.   |

In case of the dimensional constraints, the designer would consider to utilize the temperature heat sinking from the ferrite. Thermal filler shall be used to connect the ferrite and the PCB, if the ferrite is reachable and mounting is possible, in case the physical dimensions limits the designer to pickup bigger inductor body. When the maximum temperature is defined for the inductor, in most cases it represents the core temperature concentrated in the ferrite, not the copper wiring temperature. It is mandatory to understand, that the only efficient way of cooling the standard power inductor ferrite is through the enamel of the copper wire, to the copper wire and finally to mounting pads. The rest of thermal bridging is done via the inductor bobbin (plastic) and via thermal radiation, where both are acting as a thermal heatsink in minority. Such a small thermal bridge is difficult to identify as a potential source of overheating during the breadboarding phase of the development in laboratory, under standard atmospheric pressure acting as cooling medium.

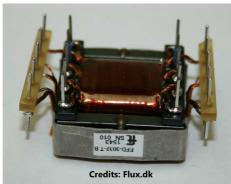

Whilst inductors and power inductors are compact and lightweight devices in low and medium power systems, pulse transformers or power conversion transformers are wound on the bobbin with ferrite or other high permeability material in order of grams up to several tens of grams in most cases. Such highly concentrated mass mounted to the target PCB via through hole pins or SMD pads is critical with respect to rupture or destruction during the vibration and shock tests. Whilst sinusoidal or random vibrations represents the shaking of the satellite launcher, the payload fairing explosive screws represents short-term loads known as shocks. To prevent the damage by the elimination of remaining dilatation between the transformer and the target PCB, the ferrite material is recommended to epoxy glue to the PCB after soldering the wire leads, fix with low outgassing, vacuum-proof string, or fix in combination of both. Except for the wire with vacuum-proof enamel, the use of standard commercial bobbins and ferrite cores is not limited in most cases. Packages such as the EFD are used for their compact height and amount of available pins for wire leads on bobbins.

Fig. 5 An example of the ferrite-based transformer fixture using string and epoxy glue. Credits: ESA SOLAR ORBITER project, Czech Space Research Centre, ASU AVCR.

#### 2.1.4. Rectifiers

The basic semiconductor used in power electronics is *PN* or metal-semiconductor diode, known as rectifier or Schottky diode, respectively. Whilst, standard Si-based diodes are broadly characterized in terms of mass production and use in space for many decades, Silicon-Carbide or Gallium-Nitride diodes offer new spectra of voltage, current and power ratings just recently.

$\boldsymbol{D}$ : As mentioned in [PP-3], the post-irradiation behavior of the diode is observed as increase in the forward voltage  $V_F$  and lower reverse breakdown voltage  $V_{BRR}$ . Induced impurities in the crystalline structure also prolongs the recovery time of the switching diode and increases the leakage current. A proper thermal heat sink is required to keep the rectifying diode reverse leakage current at low levels (below miliAmps). High power Schottky diodes

may show up to several tens of miliamps of the reverse leakage current after irradiation and at elevated temperature, close to operational limit of 125°C. The stabilizing effect of the forward voltage drop inversely proportional to junction temperature could be utilized, during the selection of the rectifier in the target application.

The avalanche effect resulting into permanent short circuit might occur and is known as the Single Event Burn-out [R-8]. When the low-voltage rated Schottky diode is reverse biased and hit by highly energetic particle, its depleted region is ionized and may initiate the avalanche current. Whilst, in low power switching operations such as diode logic, or low power digital signaling, the high capacity bank in rectifier represents sufficient amount of electric charge to thermally destruct the semiconductor during the surge current discharge via transformer winding, limited only by the DC resistance of the Capacitor-Diode-Transformer/Inductor current loop. The 50% or more voltage de-rating is recommended for power rectification / Schottky power diodes.

Following paragraphs are the auto citation of the part of the author's paper [PP-3], describing origins of the particle and photonic radiation damage in PN junction. It shall be considered as the baseline for understanding the radiation damage effects in more complex semiconductor structures (such as *BJTs*, *MOSFETs*, etc.):

#### "Linear Energy Transfer (LET):

The accelerated particles incident to the matter with atomic number  $Z_{Particle}$  and transmits its kinetic energy through the Coulomb interactions to the charged particles. By this process the particle transfers its momentum to the matter and looses its velocity v. Amount of transmitted energy is proportional to the charge of the incident particle and to the time of interaction with atoms in the matter and is therefore inversely proportional to its speed (the slower, the more momentum can be transferred to the matter). The Bethe-Bloch formula given in (2.1.4.1) describes in detail the energy loss (linear energy transfer) of charged particles  $(\alpha, \beta^+, p^+)$  with respect to the penetrating depth x

$$LET = -\frac{dE}{dx} = nZ_{T \, \text{arg} \, et} \, \frac{4\pi e^4 Z_{Particle}^2}{m_0 v^2} \, B \,, \qquad [\text{MeV/}\mu\text{m}]$$

(2.1.4.1)

where: n is the number of particles with atomic number  $Z_{Target}$ , e is a charge of the electron,  $m_0$  is the rest mass of the electron and B is the "stopping number" - factor based on the atomic number of the absorber and the parameters of the incident particles (especially speed). For electrons the Bethe-Bloch formula is changed to given in (2.1.4.2)

$$LET = -\frac{dE}{dx} = nZ_{Target} \frac{4\pi e^4}{m_0 v^2} B$$

, [MeV/\mm] (2.1.4.2)

From (2.1.4.1), (2.1.4.2) follows the LET of the incident particle is not mass-dependent. Energy transfer is proportional to the square of the incident particle charge and inversely proportional to the square of velocity in the material. The result is that the particle passes its energy slowly at first and then reaches its peak with almost quadratic increase (decreased by a factor of factor velocity squared).

Fig. 6 Bragg curves of the LET of carbon ions passing through the silicon target [2], the parameter is the mass of the incident particle.

Once the energy transfer is finished the particle is stopped and the charge neutralized. The LET is then equal to zero. The energy loss plot given in Fig. 6 is so-called Bragg curve with a typical quadratic maximum at the end of the particle path.

When passing through the material the particle dissipate its energy by two most significant processes called electronic and nuclear stopping. The total transferred energy is then given by the sum of both processes given by (2.1.4.3)

$$LET_{Total} = \left(\frac{dE}{dx}\right)_{cores} + \left(\frac{dE}{dx}\right)_{electrons}, \quad [MeV/\mu m]$$

(2.1.4.3)

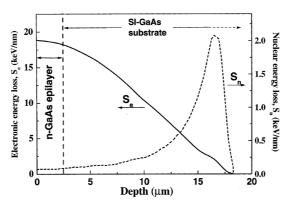

The electronic stopping process dominates at high incident energies (velocities). It is inelastic collision of ion with electron cloud connected with excitation or ionization (electronhole pair generation) of the atoms of the matter. Thus the electrostatic interactions dominate. On the contrary the nuclear stopping dominates at a low energies, ie. low incident velocities or the end of the particle path in the matter. It is an elastic collision of ions with atoms and can be described by the classical kinematics – here the mechanical interactions dominate. Both processes [3] are illustrated .

Fig. 7 Electronic (Se) and Nuclear (Sn) Stopping processes illustration [3] of 200 MeV <sup>107</sup>Ag <sup>14+</sup> ion with respect to depth inside n-GaAs/SI-GaAs epitaxial layer.

By the energy transfer the incident particle can easily dislocate atoms of the semiconductor crystal lattice. As an example the approximate estimation of the number of dislocated nuclei after impact of the proton of energy  $E_{p+}$  into the silicon (covalent bonds of four  $e^-$ ) with elastic collision can be determined from equation (4)

$$N_{Dislocated} = \frac{E_{p+}}{2E_{Dislocating (Si)}}, \qquad [-] \qquad (2.1.4.4)$$

where  $2E_{Dislocating(Si)}$  is determined as an energy needed to dislocate one atom in the Si lattice (~ 15 eV). For illustrating from (4) follows that single p<sup>+</sup> with energy of 10 MeV (typical energy inside of the nuclear reactor) impacting the silicon matter can dislocate approximately  $3,3\cdot10^5$  atoms. It is necessary to point out that during atomic dislocation primary defects occurs. They are interstitials, vacances or combination so-called Frenkel pairs. Lattice periodicity is then strongly affected. Secondary damage arise by interaction of primary defects with a crystal and with dopants in lattice, ie. V-O-H (vacancy-oxygen-hydrogen) complex or V-P (vacancy-phosphor) pair. Then previously neutral impurities become electrically active. Formation of V-O-H complex by impact of hydrogen ion is illustrated schematically in Fig. 3.

Fig. 8 Illustration of oxygen-vacancy complex formation [4].

#### **Interaction between Electromagnetic Radiation and Matter:**

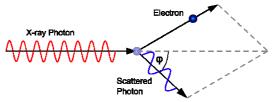

At low energies the Compton scattering process dominates to energy dissipation. Photon colliding with atom transfers its energy to the increase of the kinetic energy of the particle and change also self trajectory. Scattered photon radiates energy quanta at longer wavelength by the equation (5) given below:

$$\Delta \lambda = \lambda' - \lambda = \frac{h}{m_e \cdot c} (1 - \cos \varphi), \qquad (2.1.4.5)$$

where h is Planck constant,  $m_e$  electron mass, c is speed of light and  $\varphi$  is an angle between previous and new velocity vector as is depicted in Fig. 9.

Fig. 9 Compton scattering illustration [5].

With increased energy of photon quanta the effects becomes more complex - from simple  $e^-$  excitation over the photoelectron generation up to electron-hole pair generation at (and higher than) so-called threshold level. Energy needed to produce this pair in Silicon can be determined by the equation (2.1.4.6):

$$E = \frac{2m_e \cdot c^2}{e} = \frac{2 \cdot 9.1 \cdot 10^{-31} \cdot c^2}{1.602 \cdot 10^{-19}} = 1,022 MeV, \qquad (2.1.4.6)$$

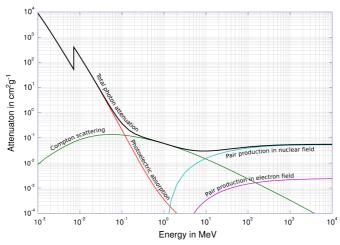

As an example the photon energy absorption processes with respect to the photon energy dissipated in iron is depicted in Fig. 10.

Fig. 10 Processes of proton energy absorption in iron with respect to the photon quanta [1].

#### **Radiation Effects in PN-type Diodes**

In general, the behavior of semiconductors exposed to ionizing radiation depends strongly on dopants, order of doping, particle energy, flux, fluence, type of radiation and electric current or applied voltage. But one common sensitive factor is degradation of carrier lifetime  $\tau$  because of changes in concentration. They are generated or recombined with previously charge-inactive impurities as was mentioned or by ion implantation in case of ion bombardment. These, mainly point defects lying in bandgap, decrease a lifetime of abundant carriers with respect to defects capture cross-section.

During the irradiation of the N-type silicon semiconductor mainly acceptor levels at  $E_C$  - 0.16 eV are created from typical atmospheric impurities. Similarly as phosphor they can form *E-centers* (donor-vacancy complexes) at level of  $E_C$  - ~0.45 eV. Typical impurities in P-type material can create donor levels at  $E_V$  + 0,28 eV and  $E_V$  + 0,05 eV.

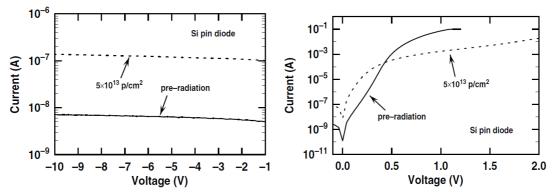

Free electrons and holes then recombine over these centers in forward or are generated in reverse bias. In [6], there are mentioned three types of PN junction diodes with different observed behavior and changes in V/I characteristics with respect to different neutron fluence. First type increase the forward voltage drop  $V_F$  proportionally to fluence. Second type reacts on low fluence by inversely proportional – by decrease of  $V_F$  forward voltage drop and on higher fluence then by the proportional increase of  $V_F$ . Third type of diodes decreases the  $V_F$  proportionally to fluence. Built-in voltage potential is given by (2.1.4.7)

$$V_0 = V_T \ln \left( \frac{N_A \cdot N_D}{n_i^2} \right), [V]$$

(2.1.4.7)

where,

$$V_T = \frac{kT}{q} = 26mV$$

, at 300 K

$N_A$  is the concentration of acceptors,  $N_D$  concentration of donors,  $\underline{n_i}$  is intrinsic concentration, k is Boltzmann constant, T temperature and q represents electron charge. Thus the concentration parameters are responsible for V/I characteristics changes in the term of ion implantation and lattice changes caused by radiation. From mentioned follows that with more intense radiation the carrier mobility is decreased, so the resistivity increase and the V/I characteristics 'lay' down as is mentioned in Fig. 11 (right). Creation of new conductive levels also leads to increase of leakage current in order of ten to hundred times more Fig. 11 (left).

Fig. 11 Illustrative comparison of Si PN-junction V/I characteristics before and after irradiation [6]; reverse bias (left), forward bias (right).

Defects implantation during irradiation shortens the mean free path of carriers. Thus the switching time increases as well as the diode noise. For example at a fluence in order of  $>10^{11}$  cm<sup>2</sup> protons with energy of 1 MeV the  $\tau$  of low power conventional Silicon diode is so high that it loses its semi conductive behavior. Irradiation of the semiconductor by the photon radiation ( $\gamma$ , X, UV, ...) generates primarily the electron-hole pairs. They are distributed in the volume of the junction by applied voltage or according to the concentration of impurities. Photons are thus not the primary source of degradation processes as opposed to corpuscular radiation."

#### Annealing - Self healing mechanism to recovery the PN junction after irradiation

**D:** The thermal annealing is the effect taking into account the fact that all matter with temperature above 0 K is characterized by the movement of its atoms within the crystalline structure. When the mutual movement is stimulated by the heat, the vacancies and impurities tends to release their abnormal positions due to abnormal mechanical stress and thus recover the original structure and shape of the crystal.

**R:** Elevated temperature and excessive power dissipation bias point are thus one of the key ways to improve the radiation tolerance in Silicon based semiconductors as an alternative to radiation hardening process in case the low cost system is desired to be delivered to space.

#### 2.1.5. Power Switches

**D:** From the switch-mode power supplies (SMPS) topology point of view there are two possibilities for choosing the semiconductor switches. One could select between current-driven bipolar or voltage controlled field effect transistors. Bipolar junction transistors (BJT) exhibit with current gain degradation which is decreased in order of tens from a nominal value. However, it is still possible to use it for switching purposes within the same circuit also

at the *End-of-Life (EOL)*. A drawback of BJTs is the high voltage drop between collector and emitter in switch-on state. Thus, from the efficiency point of view, BJTs are well suitable for high voltage power supplies. Whereas the field effect transistors with metal oxide silicon gates suffers from threshold voltage change which can lead to an uncontrollably opened channel and circuit overloading. The biggest advantage is often the extremely low switch-on resistance. The IGBT combine both drawbacks, despite its high power conversion factor. Relatively high V<sub>CE</sub> voltage drop and insulated gate region controlling the collector emitter current makes this component suitable mainly for high power solar cell regulators rated to voltages in order of thousand Volts and tens of Amperes of switched currents.

**R:** The Junction FETs does not contain the insulated gate – the region where the charge deposition change doping level and accelerate recombination, decrease the carrier lifetime and make the channel current control impossible. Moreover, the JFET channel doping level is typically in order of 10<sup>15</sup> to 10<sup>18</sup> n·cm<sup>-3</sup> [PP-3], leading to radiation displacement tolerance in order of Mrads(Si) and more. Similar components to JFETs, i.e. without insulated gate, are the High Electron Mobility Transistors (HEMT) and MESFETs, but suitable only for extra low voltages in order of Volts.

Industry first manufactured *SiC Normally-Off JFET* devices were introduced by US Silicon Carbide pioneering company *SemiSouth*. In [R9], two different transistors, namely *SJDP120R085* and the *SJEP120R100* ( $R_{DSon} = 85$  and  $100 \text{ m}\Omega$ ) were irradiated and tested to high energy gamma radiation. They were both found survived after 7 Mrad TID as a maximum of testing total dose. Unfortunately, the SemiSouth manufacturer announced closure in late 2012 and made these very promising products no longer available. The topic is discussed more in detail in [PP-3].

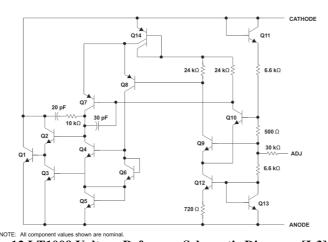

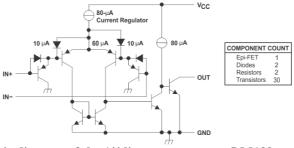

#### 2.1.6. Voltage References

**D:** One of the key analog element in DC/DC converter is the voltage reference integrated circuit as a the thermally-stable precision voltage source. Due to the MOS transistors susceptibility to radiation damage, parametric drifts and ageing faster than in case of the bipolar technology, it is recommended to choose the bipolar junction transistors based chips as for example *LT1009* or its clones in radiation hardened version. The example of the schematic diagram of the *LT1009* is given in Fig. 12 [I-3].

Fig. 12 LT1009 Voltage Reference Schematic Diagram, [I-3].

It is mandatory to highlight, that the high energetic particle hitting the silicon chip is penetrating the structure in various locations, inducing various voltage or charge conditions.

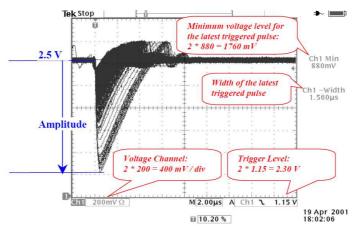

Such behavior is depicted in Fig. 13 [I-4]. The output voltage from steady state 2.5 V drops down by factor of several hundreds of milivolts, with the pulse duration in order of up to 3-7  $\mu$ s.

Fig. 13 The Single Event Effects on LT1009 output captured under heavy ion bombardment, [I-4].

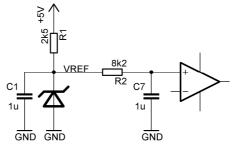

R: The post filtering RC link to suppress and minimize the drop shall be applied such as in Fig. 14. The time constant  $\tau = RC$  is in order of 10  $\mu$ s for most cases and bipolar-based voltage references. As the RC product in fact commutative, the key aspect is the driving current necessary to feed the following stage. In Fig. 14 the example of operational amplifier feeding is represented. The input leakage current shall be then at least two magnitudes lower in the system end-of-life (after irradiation). Thus lower impedance of R2 (and R1) is preferred. Ceramic capacitors in the order of microfarads are good candidates with respect to their miniature size (and the probability of failure of high capacity / small size MLCCs due to its internal high density of electrodes).

Similar *SEE* behavior is extremely important to fix in circuits such as *Undervoltage Lockouts*, *feedback error amplifiers or overload sensing circuits*, where the artificial voltage drop caused by the particle radiation could cause a temporary malfunction or the unit turn-off.

Fig. 14 Proper SEE voltage filtering schematics.

#### 2.1.7. Opto and Photo Elements

**D:** The displacement damage is the root cause of the optical and photo elements degradation such as *LEDs*, *LASERs*, photo transistors or photodiodes. Photo sensors reacts by increased leakage (also known as dark) current which would destabilize the DC operation point of the biased sensor, photoelement preamplifier or the *DC offset* of the pulse shaping circuits. Where possible, the zero bias circuit shall be used to eliminate this phenomena.

Photon emitters, such as *LEDs and LASER* diodes degradation is indicated by the decreased output power and transition frequency, mandatory for digital optical buses. In

combined circuits such as the *OptoFETs* or *optocouplers*, both effects accumulates and lead to the *Current Transfer Ratio (CTR)* degradation.

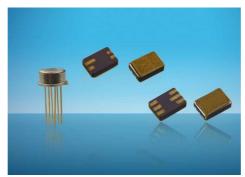

**R:** There are various manufacturers of radiation hardened optocouplers with their portfolio of ruggedized and hermetic ceramic package encapsulated components, but with only limited radiation tests results available. From the metal CANs to Ceramic Leadless Chip Carrier (CLCC) packages, the example is given in Fig. 15 [I-5]. Due to the natural displacement damage degradation, the designer is either recommended to utilize highest available CTR parameter component, choose higher current driving or avoid the use of optocouplers in general.

Fig. 15 Example of various packages of radiation hardened optocouplers by TT Electronics [I-5].

The advantage of the high voltage transient immunity in order of up to  $kV/\mu s$ , galvanic insulation and linear region of current transfer are benefits which are hardly achieved by any other type of galvanic insulation methods, such as transformer based, in given footprint. Above mentioned facts may lead to decision, that the optocoupler is still mandatory to be used. Then the spot-shielding or other physical barrier against the incident radiation (position of the system inside of the satellite body) is crucial to implement and pay attention to.

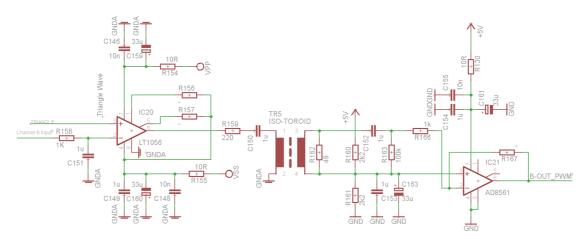

By addressing the Objective C of the Thesis, the opto-coupler feedback free insulated DC/DC converter with multiple outputs is proposed, designed and tested.

#### 2.1.8. Electromechanical Elements and SSR

**D:** Monostable or latching (bistable) relays are often necessary for low power loss routing with limited amount of expected status change cycles such as high current switching, deployment initiators or battery charging/discharging controllers. There are available in various packages, with hermetically sealed cans or boxes, depending on the current, voltage or frequency rating. It is important to assure that no critical elements such as pyros or propulsion is under the control of mechanical contacts, to prevent unexpected reaction due to the launcher vibrations or shocks. To prevent unwanted reed status change, miniature permanent magnets are implemented to keep the mechanical part in stable position. The magnetic dipole is then required to be encountered in case of onboard sensors measuring the magnetic field.

R: An example of the latching relay is given in Fig. 16 [I-6]. It is the TO-5 CAN package with magnetic latching and *Double Pole*, *Double Throw (DPDT)* contact configuration, rated up to 1 A<sub>DC</sub> and frequencies up to 1 GHz signals.

Fig. 16 Teledyne Latching Relay type HR422 in TO-5 CAN package, [I-6].

The electromechanical element is driven by the magnetic force induced by the relay coil, often supported with the force of permanent magnets to assure the shock and vibration tolerance. The driving current in monostable relays would be in order of 20 mA per coil with voltage rating between 5 to 24 Volts, implicating long-term medium power consumption and thermal power dissipation.

In a contrary, the bistable (latching) relay would be driven from the capacitor bank associated to driving elements such as bipolar transistors. The necessary energy is then stored in capacitors for status change events, which are charged via high ohmic charging resistor, assuring low power consumption since the first power up, over the whole mission lifetime and protect the spacecraft power budget in case of the permanent coil short circuit.

The hermetic package assure great radiation tolerance, which is in principle limited only by the disintegration of glass feedthroughs and the radiation susceptibility of the coil wire enamel. The amount of cycles guarantied by the manufacturer is in order of 100 000, per mechanical element.

The *Solid State Relays* based on *opto-FETs* and *LEDs* combines the disadvantages of silicon structures such as blinding of the optical receiver, dimming of the LED brightness, degradation of the CTR, similarly as in case of optocouplers. Their use shall be considered only if no other solution is not found more advantageous or spot shielding is not allowed.

#### 2.1.9. Integrated Circuits - Analogue

**D:** A combination of BJT and JFET technology, with absence of MOS transistors with robust chip/transistor size is a great precursor for long-lasting linear analog circuits such as comparators in Fig. 17 [I-7] or operational amplifiers. Again, similarly as in case of the Voltage references, the circuit mounted on a chip, hit by the high energetic particle will generate the fast SEE voltage output change observable as a fast spike or drop. The accumulative TID damage is expected to create parametric drifts, mostly increased input leakage currents, quiescent currents or change the saturation voltage of output transistor stage. They might change by several magnitudes before the loss of function is encountered.

Fig. 17 Simplified schematic diagram of the 1/4 linear comparator LM139, note the bipolar technology used in critical input, signal processing and output circuits, [I-7].

**R:** The output of the comparator shall be R-C filtered where possible with respect to the time constraints, especially when it is used to trigger latching circuits such as electronic circuit breaker or critical events such as deployment. On the other hand, in fast signals processing chains, single missing pulse or false signal in very rapidly changing pulse trains such as sigma-delta samplers, may not cause a dramatic malfunction.

In case the analog integrated circuit to be used does not contain complementary MOS pairs, it is also understood as *Single Event Latchup Free by design*. Where the designer is not sure about the internal circuit realization or used technology, it shall assume it as SEL sensitive.

#### 2.1.10. Integrated Circuits - Digital

**D:** With advancing the semiconductor development and technology, digital integrated circuits are available mostly based on CMOS transistor pairs, with advantage such as minimal input current required, very low quiescent current and power consumption, high output driving capability or fast frequency response. However, CMOS pairs in standard commercial electronics are one of the most sensitive components, when considered to be implemented in the satellite system. Single Event Latchups may be triggered easily by particles with *LET* as low as 10 MeV·mg<sup>-1</sup>·cm<sup>2</sup>, whilst practical limits for radiation hardened parts starts at around 40 MeV·mg<sup>-1</sup>·cm<sup>2</sup> and more.

**R:** The designer shall utilize CMOS-based digital chips working at low voltages (3.3 V and less), to minimize the probability of avalanche-triggering the SEL, utilize power line protection against the hard (long lasting) short-circuit and integrated circuit burn-out due to excessive current and consider radiation spot shielding or possibility to replace the CMOS commercial chip with radiation hardened or even discrete-based, where feasible by the required complexity. Increased input leakage current, quiescent current, decreased driving capability and frequency response have to be kept in mind during planning the circuit behavior in the system EoL. A practical factor of 100-1000 shall be used as derating correction of working parameters during the BoL with respect to behavior under the EoL.

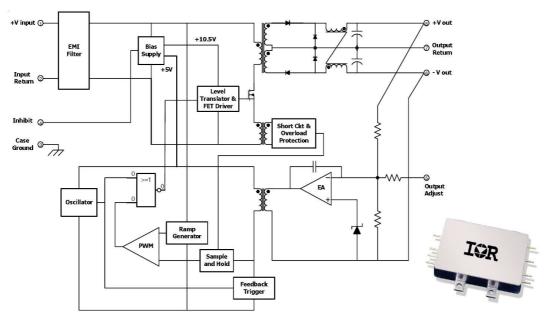

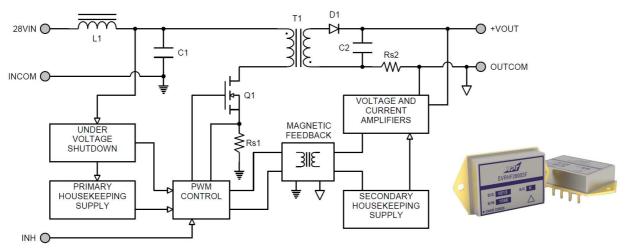

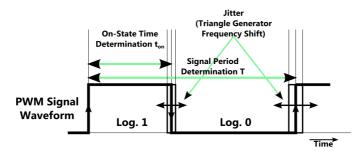

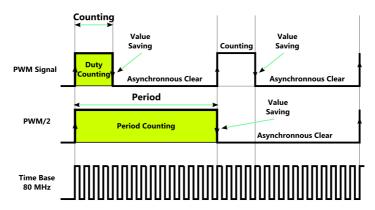

#### 2.1.11. PWM Controllers

**D:** Commercial chips used in consumer electronics were a subject of radiation hardness investigation and improvements like single or double output drive (Flyback or Push-Pull) PWM Voltage-mode controllers x1527 through x1527 or Current-mode x1840, x1841, x1843 or x1845 from several vendors (ST Microelectronics, Texas Instruments, Microsemi, Intersil). The most radiation hardened power supply driver on the space component market is currently the PWM5032 [R-10], double output PWM controller from the Aeroflex/Cobham as a product of the commercial and scientific cooperation between private company and NASA / Mars Technology Program. The chip with quiescent current of 7.1 mA, encapsulated in 24 pin Flat Pack ceramic package can withstand up to 1 Mrad(Si) at a dose rate between 30 – 200 rad/s. It is Single Event Latchup and Single Event Upset immune up to 100 and 20 MeV·cm²·mg⁻¹, respectively.

Integrated standalone primary side PWM drivers have several drawbacks. At first, the galvanically insulated feedback regulation needs to be included, such as optocouplers or magnetic isolators. Unfortunately, neither Rad Hard nor Space-qualified magnetic feedback integrated circuits were currently available on the market. In April 2013, the Intersil company announced its High Rel / Rad Hard Space Product Roadmap, where introduces the *ISL71901SEH* chip as an upgraded version of the *UC1901* Isolated Feedback Generator. It

was announced as an intended concept of radiation hardened development with beginning in 2014. TI offers this product in Hi Rel / Space category; however it is not the ESA-qualified product.

As the next category of DC/DC converters, the Point-of-Load (PoL), single chip regulators are available for local high current voltage supply, such as digital core voltage power source for ADCs, FPGAs or microprocessors. The example of high current capability PoL is for example the *ISL70003ASEH* by Intersil. It incorporates full step-down regulator requiring only external LC filter and several timing and power decoupling passive components. It delivers up to 9A, with maximum input voltage of 13.2 V and TID tolerance of up to 100 kRad(Si) with both LDR and HDR.

**R:** Where possible, use discrete-based solution of the PWM/power stage circuitry, to be able to choose the sensitivity of the system to radiation environment.

#### 2.1.12. Accumulator Cells and Batteries

**D:** Conservatively used and preferred battery cells in aerospace industry, such as commercial airliners are the *Nickel-Cadmium (NiCd)* or *Nickel-Metal Hydride (NiMH)* cell assemblies with exceptionally long flight heritage, good temperature stability and power density, together with great safety during the operations.

In modern aerospace and space industry the *NiCd/NiMH* cells are often replaced with Lithium-based technology, such as *Li-Ion*, *Li-Poly*, or *LiFePO*<sub>4</sub> with the highest available power density. As mentioned in [R-11]: "The power density is 80 W/kg for the NiMH cell and lies between 330 and 3100 W/kg for the lithium-ion cells". As the fire safety is not absolute critical on unmanned spacecraft such as on the passenger carrying aircraft, the satellite power system may be designed to contain cold-redundant / multiple set of batteries, because of the unprecedented Li-cell power density.

R: From performance point of view, the amount of charging/discharging cycles with respect to cell capacity loss may not be necessarily understood as the key chemistry selection driver, as the typical time of the darkness within the orbital period (pure battery discharging) per LEO is generally not be long enough to discharge the cell/battery fully. In such case, the power budget and discharging scenarios shall be reconsidered and over-dimensioned to prevent advance mission loss due to power cycling failure. The most critical parameter to observe is the temperature dependence and discharging current, both limiting the charge accumulation capability. In case of the Li-Ion battery, the critical is charging and discharging below the freezing point [R-12]. The  $LiFePO_4$  cells shows exceptionally good behavior also below the freezing point up to -20°C. The designer shall implement the heating elements to stabilize the temperature of the given chemistry, locate the battery pack in close vicinity to the thermally-dissipative part of the spacecraft or include the potential voltage or battery charge state into the mission power budget according to thermal characterization of the given cell.

#### 2.1.13. Solar Cells

**D:** From solar orbits such as recent mission to the sun, the NASA Parker Solar Probe, european-japanese mission BepiColombo or European mission Solar Orbiter, up to the region of Jupiter, solar cells are the most common sources of electricity aboard spacecrafts.

Following Tab.: 2 summarizes the typical incident solar power densities at distant planets in the Solar system.

| 10 2 Solar Constants at given planets of the Solar Syste |                            |                                             |  |  |

|----------------------------------------------------------|----------------------------|---------------------------------------------|--|--|

| Planet                                                   | Distance from the Sun (AU) | Solar Power<br>Density (W⋅m <sup>-2</sup> ) |  |  |

| Mercury                                                  | 57                         | 9228                                        |  |  |

| Venus                                                    | 108                        | 2586                                        |  |  |

| Earth                                                    | 150                        | 1353                                        |  |  |

| Mars                                                     | 227                        | 586                                         |  |  |

| Jupiter                                                  | 778                        | 50                                          |  |  |

| Saturn                                                   | 1426                       | 15                                          |  |  |

| Uranus                                                   | 2868                       | 4                                           |  |  |

| Neptune                                                  | 4497                       | 2                                           |  |  |

| Pluto                                                    | 5806                       | 1                                           |  |  |

Tab.: 2 Solar Constants at given planets of the Solar System.

A paradox of the insufficient amount of power available at orbits closer to the Sun, than on LEO is caused by the need for excessive cooling of the solar cell array, as the efficiency of the photovoltaic effect in the semiconductor is inverse-proportional to the cell temperature.

The state-of-the-art mass production triple junction solar cells shows 30% efficiency with Air Mass 0, power density  $1367 \text{ Wm}^{-2}$  and  $28^{\circ}\text{C}$  conditions, with maximum power point tracking (MPPT) load [R-13]. The manufacturer claims the drop in the efficiency down to 26.5% at the same optical conditions, when the cell is irradiated by 1 MeV electrons with fluence of  $10^{15}\text{e-cm}^{-2}$ .

Fig. 18 Triple junction solar cell by Azur Space, [R-13].

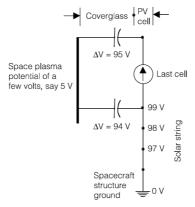

**R:** According to [R-14], the highest practical solar array string voltage shall not be higher than 160 V to prevent short duration arcing between the solar panel conductive substrate and the cell. Thin glue or tape layer necessary to mount the cell into the panel is required to establish the thermal bridge and cool down the cell exposed to the sunlight. The schematic diagram in depicts the string and the situation of the voltage potential on large array.

Fig. 19 High voltage solar cell string diagram with space plasma surroundings, [R-14].

#### 2.1.14. Alternative Power Sources

**D:** There are plans to develop and produce more secure isotope-based types of power sources such as *Radioisotope Thermoelectric Generators (RTGs)*, mostly containing pellets of primarily alpha-decaying *Plutonium Oxide* <sup>238</sup>*PuO*<sub>2</sub>, or <sup>90</sup>*Stroncium* producing heat which is then converted using thermoelectric elements based on Seebeck effect into electricity. Such highly radioactive element aboard the launcher represents significant environmental risk, if the vehicle disintegration during the launch phase below the orbital velocity occurs above the populated territory.

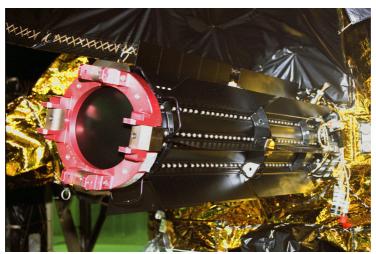

Fig. 20 Radioisotope Thermoelectric Generator power source of the Cassini spacecraft, [I-8].

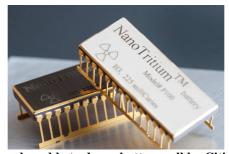

Despite the thermocouple-based electricity generating principle, one of the promising technological breakthrough is the Betavoltaic battery. It represents a new way of long-lasting power generation assemblies development for deep space missions with not available sungenerated power. Several studies were done recently with working examples, using *tritium*  $^3H$ ,  $^{14}Carbon\ or\ ^{63}Nickel$  as beta-radiator isotopes and P-N based charge colleting electrodes. Scientific studies such as [R-15] and [R-16] claims the power yield achieved so far in order of  $\mu$ W, power density of  $3.3\ kWh\cdot kg^{-1}$ , with operational lifetime expected to be between 25 to 100 years.

Fig. 21 Tritium-based beta decay battery cell by Citi Labs, [R-16].

**R:** All above listed isotopes decay as pure beta radiators and thus does not convert to the penetrating gamma ray isotopes over time, such as in case of the <sup>238</sup>Pu-based RTGs. They are suitable to be embedded close to the target electronics, whilst RTGs have to be mounted on external booms to protect the spacecraft itself during the operational lifetime.

#### 2.1.15. Chemistry for Assembly and Finish

**D:** To prevent the disposal and minimize the amount of the lead in the environment by human activity, several countries have agreed and implemented into national legislation a rule proposed by the European Parliament in 2011, known as directive RoHS 2011/65/EU. Since that time, it was adopted by the majority of countries with the dominant market influence, such as USA, China, Switzerland and South Korea. The directive defines the Restriction of the use of certain Hazardous Substances in electrical and electronic equipment. In consumer electronics with two year warranty cycle, the quality of solder joints using pure tin or the alloy of 99.5% tin with 0.5 % of silver is sufficient and does not block the production or reduce the customer comfort. In general, a vast majority of electronic parts manufacturers does not offer their portfolio in other than so-called RoHS-free or lead-free pad finish. Whilst, components for military and aerospace markets are still available with gold or solder pad finish assuming the tin/lead compound.

**R:** Although, the growth of tin whiskers, a crystalline structures similar to cat whisker, growing from the tinned part is not a new phenomenon (first observed in early 1940-1950), there are several spacecraft malfunctions in space considered to have a tin whisker growth as a cause. According to the NASA NEPP program [R-17], there are also other metals broadly used in space electronics sensitive to whisker growth, if the metal is present as pure. According to [R-17] such metals are: zinc, cadmium, indium, antimony or silver. In the electronic assembly, zinc finish could be easily met on some commercially available screw/board standoffs, silver then on connectors.

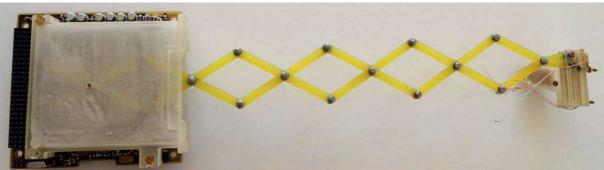

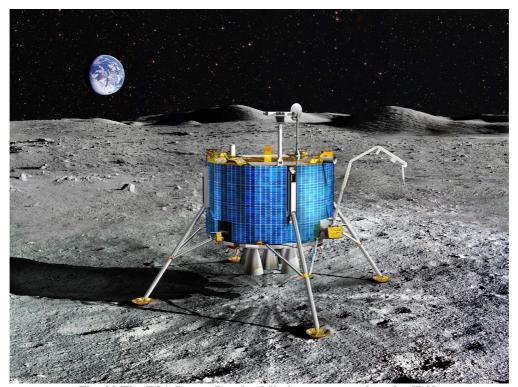

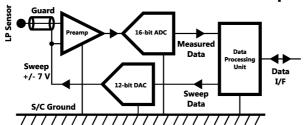

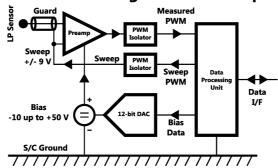

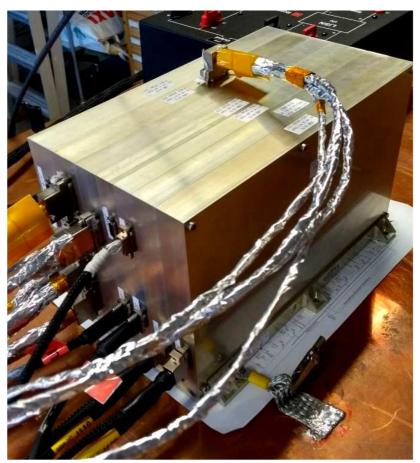

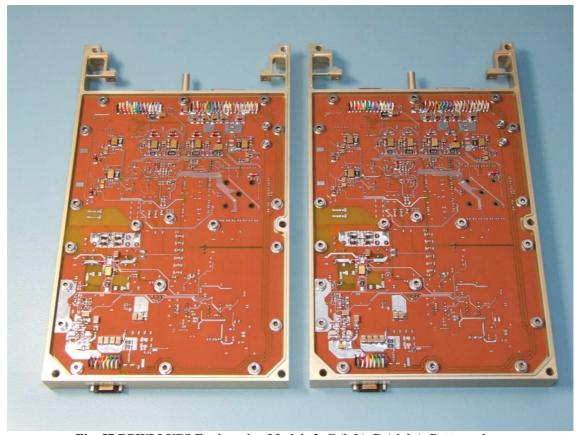

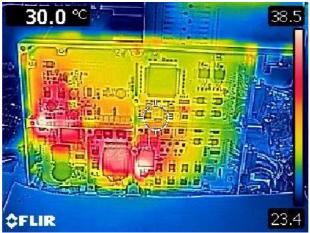

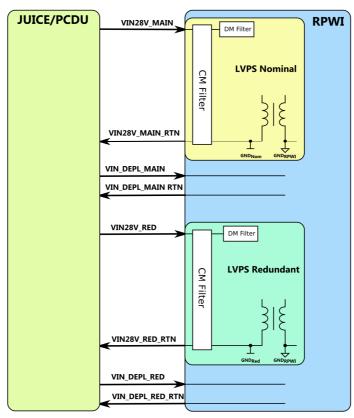

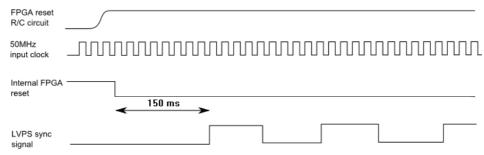

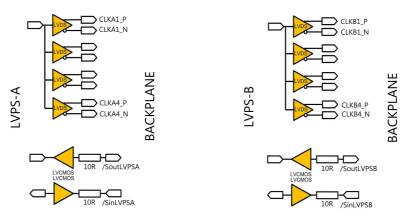

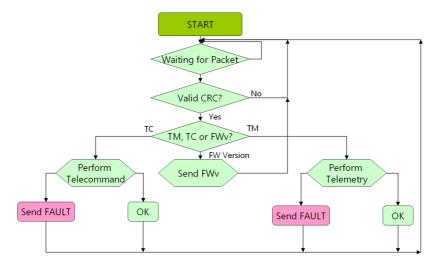

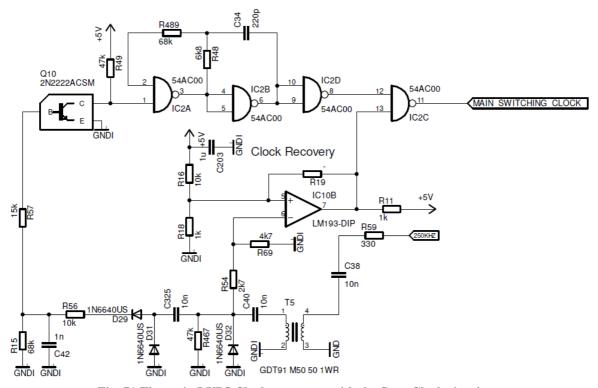

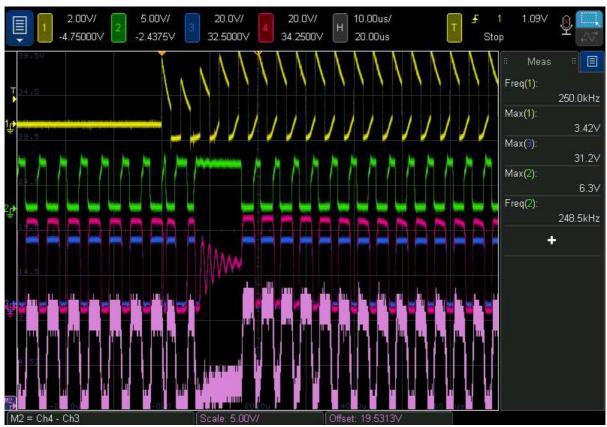

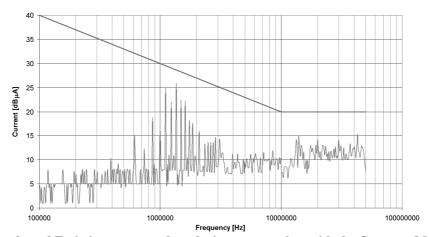

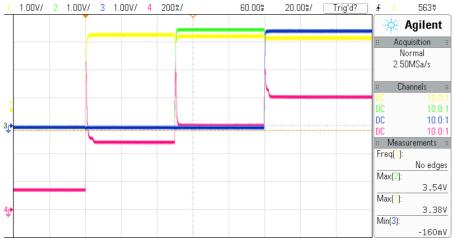

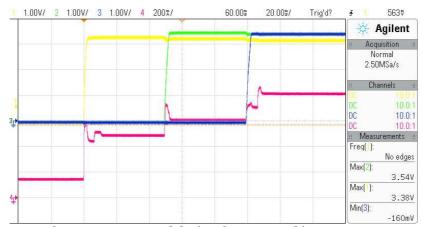

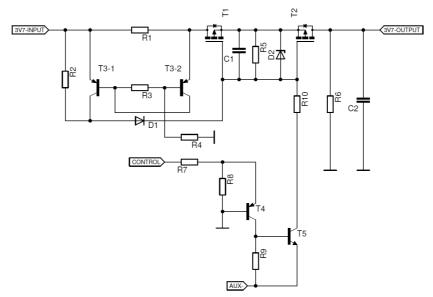

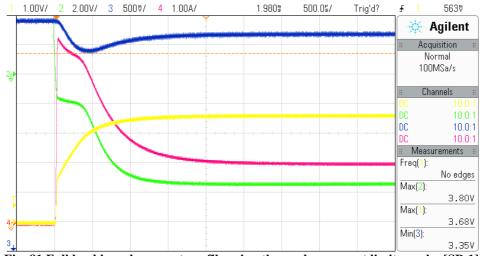

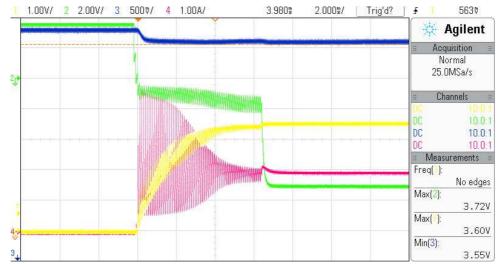

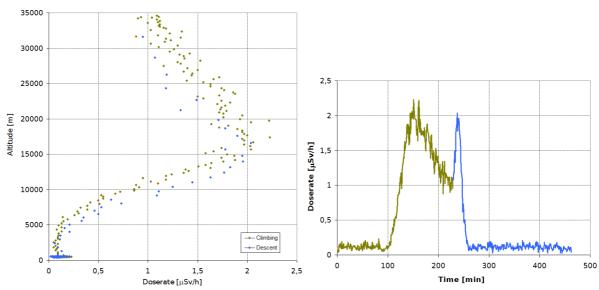

Fig. 22 The example of formed tin whisker, [R-17].