## CZECH TECHNICAL UNIVERSITY IN PRAGUE FACULTY OF ELECTRICAL ENGINEERING

## DOCTORAL THESIS

August 2018

Ing. Vladimír Molata

## CZECH TECHNICAL UNIVERSITY IN PRAGUE FACULTY OF ELECTRICAL ENGINEERING

DEPARTMENT OF MICROELECTRONICS

## Advanced Power Management for Portable Devices

## DOCTORAL THESIS

Ing. Vladimír Molata

Prague, August 2018

Ph.D. Programme: P2612 Electrical Engineering and Information Technology Branch of study: 2612V015 Electronics

Supervisor: doc. Ing. Jiří Jakovenko, Ph.D

#### Declaration

I declare I have completed my doctoral thesis on my own with the contribution of my supervisor and consultants. I used only materials (literature, projects, articles) specified in the attached list.

I agree with the use of the information presented in my doctoral thesis pursuant to Copyright Act 121/2000 Coll., Sec. 60.

In Prague, August the 31st, 2018

Vladimír Molata

#### Acknowledgements

I would like to thank my colleagues from STMicroelectronics and also from CTU in Prague, for their patience and valuable expertise they have provided me with. Special thanks to Ing. Vlastimil Kotě and Ing. Ondřej Tlaskal Ph.D for their ideas, consultations, and great cooperation. It would not be possible to work on this interesting topic without their great support. I also would like to thank my supervisor doc. Ing. Jiří Jakovenko, Ph.D., who has been consulting various parts of my work, for appreciate advises. His comments and suggestions helped me to improve my work.

Finally, I would like to thank my family, friends for overall sustained support during the time of my studies and especially to my wife. She has encouraged me greatly especially in the last years of my Ph.D. work.

#### Abstract

The dissertation thesis deals with the design, verification, optimization, and characterization of basic blocks and sub-blocks that are used in power management for portable devices for which only a limited power supply is available. The reason is that power management is being assigned an ever higher priority by trying to prolong the life of the batteries and hence the whole device powered by this battery.

The work aims to inform readers about issues and possible solutions in the area of power management for portable systems where only a limited power source is available. In particular, it focuses on two basic elements which are most commonly used in power management, linear regulators and switching converters. Each of these elements has certain advantages and disadvantages. Depending on the requirements that are imposed on the supply voltage, we need to choose the optimal configuration.

It also discusses the latest trends in the field of power management, both capacitor-less linear regulators and switching converters. In the case of switching converters, it is divided into parts, namely synchronous converters, which are used for example supplying of the radio frequency power amplifier which is based on Envelope Tracking technique, and then on frequency control for asynchronous converters.

Research in the field of linear regulators for the system on chip applications brings a new solution for the reduction of dedicated capacitors of the regulators and thus the price reduction. Instead of such dedicated capacitors, the capacitor-less regulator is loaded only with capacities (in the range from several hundreds of picofarads to several single nanofarads) of systems it powers. And thanks to this approach, for example, the internal parts of the switching converter or true random number generator can be powered by an uninterrupted power supply, thereby improving its performance.

The work is also focused on the design of switching converters. On one hand, it deals with the synchronous converters, sub-blocks in the PWM controller like ramp generator and also the issue of increasing the efficiency of a three-level switching inverter, where a special sensor is used to determine the orientation of the current in the coil, which is based on the indirect sensing method. And further, stabilization of the switching frequency for asynchronous converters based on the trans linear circuit while preserving their excellent transient properties. The proposed concept avoids the need for a frequency feedback control such as a PLL or DLL.

**Keywords:** Power management unit (PMU), capacitor-less linear regulator, switchingmode power supply (SMPS), current direction sensor, ramp generator, frequency predictor.

### Abstrakt

Předložená disertační práce se zabývá návrhem, verifikací, optimalizací a charakterizací základních bloků a dílčích podbloků, které se využívají ve správě napájení pro přenosná zařízení, u kterých máme k dispozici pouze omezený zdroj energie. Je to z důvodu, že správě napájení se přiřazuje stále vyšší priorita a to je dáno tím, že se snažíme stále více prodlužovat životnost baterie a tím i celého zařízení, které je touto baterií napájené. Zejména se pak zaměřuje na dva základní prvky, a tj. lineární regulátory a spínané konvertory, které jsou pro správu napájení používány nejčastěji. U každého z těchto prvků lze najít jeho výhody či nevýhody, které musíme brát při návrhu systému v potaz.

Práce se věnuje nejnovějším trendům v oblasti správy napájení a to zejména bez-kapa citním lineárním regulátorům a spínacím měničům. U spínacích měničů se pak dělí na dvě části a to na synchronní spínací měniče, které se využívají například pro napájení vysílacích vysokofrekvenčních zesilovačů, kde pro zvýšení účinnosti vysílacích částí se zde využívá například technika zvaná "Envelope Tracking" a dále pak na měniče s proměnnou spínací frekvencí.

Výzkum v oblasti lineárních regulátorů pro SOC přináší nová řešení pro odstranění velkých vnějších (externích) kondenzátorů u těchto regulátorů a tím i snížení ceny. Na místo těchto externích kondenzátorů je výstup bez-kapacitních regulátorů zatížen pouze kapacitou jednotlivých systémů, které napájí. Tato kapacita se pohybuje v rozmezí stovek pikofarad až jednotek nanofarad. Díky tomuto přístupu lze například interní části spínaného měniče nebo generátor náhodných čísel napájet nezarušeným napájením a tím zlepšit jeho vlastnosti.

Další část je zaměřena na problematiku týkající se spínaných napájecích zdrojů. Jednak se věnuje vylepšení podbloku v PWM kontroléru a problematice zvyšování účinnosti tříúrovňového spínaného měniče, kde se využívá speciální senzor pro určení orientace proudu v cívce, který je založen na nepřímé metodě snímání. A dále pak stabilizaci spínací frekvence u měničů s proměnou frekvencí při zachování jejich přechodových vlastností, kde navrhovaný koncept stabilizace spínací frekvence nevyžaduje zpětnou vazbu, oproti systémům pro řízení frekvence pomocí PLL nebo DLL.

Klíčová slova: Správa napájení, bez-kapacitní lineární regulátor, spínaný měnič, senzor pro určení orientace proudu, generátor rampy, frekvenční prediktor.

# Contents

| Ak              | Abstract |                                                                                        | vii |

|-----------------|----------|----------------------------------------------------------------------------------------|-----|

| 1. Introduction |          |                                                                                        | 1   |

|                 | 1.1.     | Organization of this thesis                                                            | 4   |

|                 | 1.2.     | Author's scientific contributions                                                      | 5   |

|                 | 1.3.     | State of the art                                                                       | 6   |

| 2.              | Pow      | ver Management Unit                                                                    | 11  |

|                 | 2.1.     | Regulation principles                                                                  | 11  |

|                 | 2.2.     | Linear regulators                                                                      | 12  |

|                 |          | 2.2.1. LDO regulators                                                                  | 15  |

|                 | 2.3.     | Switching converters                                                                   | 17  |

|                 |          | 2.3.1. Basic DC-DC converter topologies                                                | 17  |

|                 |          | 2.3.2. Switching mode control techniques                                               | 21  |

| 3.              | Сар      | acitor-less Linear Regulators                                                          | 29  |

|                 | 3.1.     | PMOS capacitor-less LDO regulators                                                     | 30  |

|                 |          | 3.1.1. Poles of capacitor-less LDO regulator                                           | 30  |

|                 |          | 3.1.2. Design of a capacitor-less LDO regulator                                        | 31  |

|                 |          | 3.1.3. Achieved results                                                                | 34  |

|                 |          | 3.1.4. Conclusions and future work                                                     | 37  |

|                 | 3.2.     | NMOS capacitor-less linear regulators                                                  | 39  |

|                 |          | 3.2.1. Design of a NMOS capacitor-less linear regulator                                | 40  |

|                 |          | 3.2.2. Comparison of results and future work                                           | 43  |

| 4.              | Cur      | rent direction sensor for three-level flying capacitor converter                       | 47  |

|                 | 4.1.     | Topologies for 4G PA                                                                   | 48  |

|                 | 4.2.     | An apparatus for efficient regulation of the flying capacitance voltage in three-level |     |

|                 |          | FCC                                                                                    | 51  |

|                 |          | 4.2.1. Problems with existing solutions                                                | 54  |

|                 |          | 4.2.2. Detailed description                                                            | 55  |

|                 | 4.3.     | Example of use for a three-level FCC                                                   | 58  |

| 5. | Dua  | I Edge Ramp Generator                                                  | 63 |

|----|------|------------------------------------------------------------------------|----|

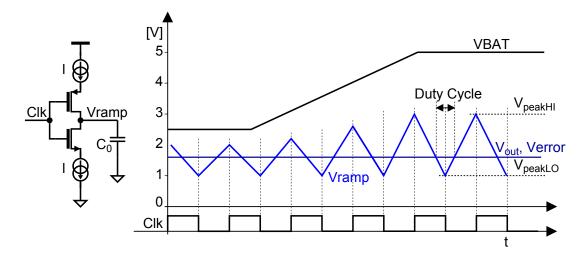

|    | 5.1. | Basic idea of the ramp generation                                      | 64 |

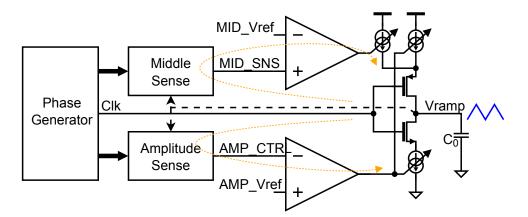

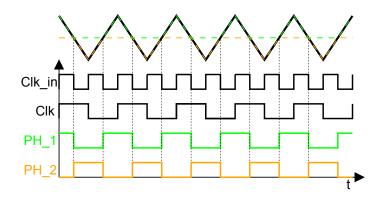

|    | 5.2. | Proposed ramp generator principle                                      | 64 |

|    |      | 5.2.1. Common mode loop                                                | 66 |

|    |      | 5.2.2. Amplitude loop                                                  | 67 |

|    | 5.3. | Achieved results                                                       | 68 |

|    |      | 5.3.1. Measurement                                                     | 70 |

|    | 5.4. | Conclusions                                                            | 71 |

| 6. | Frec | quency control of non-oscillator referenced DC-DC switching converters | 73 |

|    | 6.1. | Theoretical study of feed-forward frequency control                    | 73 |

|    | 6.2. | Practical implementation of a predictor                                | 76 |

|    | 6.3. | Application of a TL predictor to a hysteretic converter                | 81 |

|    | 6.4. | Measurement results                                                    | 86 |

|    | 6.5. | Conclusions and future work                                            | 89 |

|    |      |                                                                        |    |

## Appendices

I

| Α. | List o | of Auth | nor's Publications                          | Ш    |

|----|--------|---------|---------------------------------------------|------|

|    | A.1.   | Publica | tions Related to the Topic of This Work     | III  |

|    |        | A.1.1.  | Publications in Impacted Journals           | III  |

|    |        | A.1.2.  | Publications in Reviewed Journals           | III  |

|    |        | A.1.3.  | Patents                                     | IV   |

|    |        | A.1.4.  | Publications Excerpted by WoS               | V    |

|    |        | A.1.5.  | Other Publications                          | VI   |

|    |        | A.1.6.  | Functional Samples                          | VII  |

|    | A.2.   | Publica | tions Not Related to the Topic of This Work | VIII |

|    |        | A.2.1.  | Publications in Reviewed Journals           | VIII |

|    |        | A.2.2.  | Publications Excerpted by Scopus            | VIII |

|    |        | A.2.3.  | Other Publications                          | VIII |

|    |        | A.2.4.  | Functional Samples                          | IX   |

| в. | Reco   | ognitio | n and Review                                | XI   |

# **List of Figures**

| 1.1.  | Block diagram of a voltage-mode PWM buck regulator                                                | 3  |

|-------|---------------------------------------------------------------------------------------------------|----|

| 1.2.  | Basic types of switching converters                                                               | 4  |

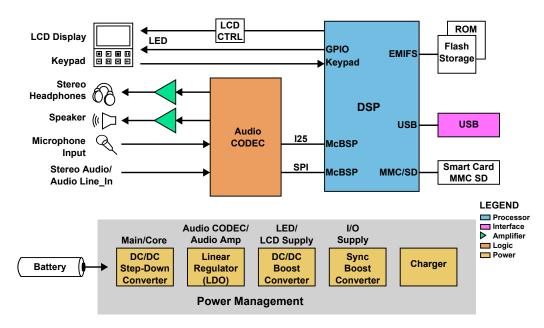

| 2.1.  | Block diagram of MP3 player [36]                                                                  | 12 |

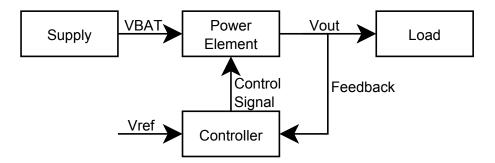

| 2.2.  | Block diagram of a typical electronic power conversion system                                     | 12 |

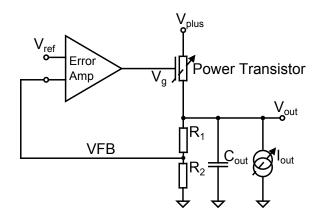

| 2.3.  | Principal block diagram for linear regulator                                                      | 13 |

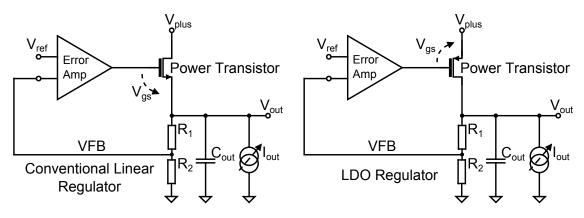

| 2.4.  | Topologies of linear regulators                                                                   | 14 |

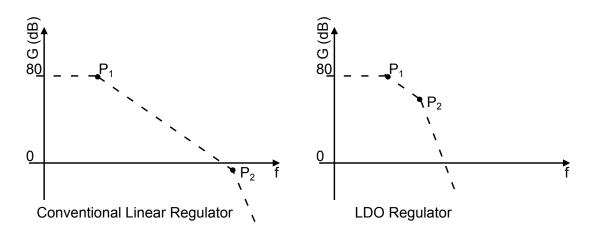

| 2.5.  | Magnitude characteristics with shown poles for both topologies without compensation circuits [55] | 15 |

| 2.6.  | -                                                                                                 |    |

|       | alent circuit diagram for fast load transients [50]                                               | 16 |

| 2.7.  | Block diagram of the switching regulator                                                          | 17 |

| 2.8.  | Schematic of a typical step-down switching converter                                              | 18 |

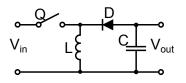

| 2.9.  | Buck converter                                                                                    | 19 |

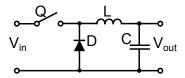

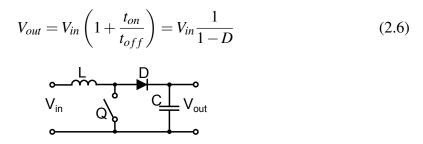

| 2.10. | Boost converter                                                                                   | 20 |

| 2.11. | Buck-Boost converter                                                                              | 21 |

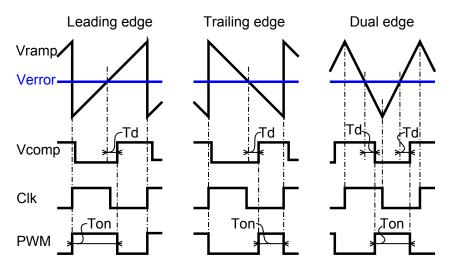

| 2.12. | Steady-state PWM timing diagram of the buck converter shown in Fig. 2.8                           | 22 |

| 2.13. | Schematic of the voltage mode regulation principle                                                | 24 |

| 2.14. | Signal waveforms of the voltage mode regulation principle shown in Fig.                           |    |

|       | 2.13                                                                                              | 24 |

| 2.15. | Schematic of the peak-current mode regulation principle                                           | 25 |

| 2.16. | Signal waveforms of the peak-current mode regulation principle shown in                           |    |

|       | Fig. 2.15                                                                                         | 26 |

| 2.17. | Schematic of the hysteretic voltage mode regulation principle                                     | 27 |

| 3.1.  | Capacitor-less LDO voltage regulator [55]                                                         | 29 |

| 3.2.  | Illustration of pole position for uncompensated capacitor-less LDO regu-                          |    |

|       | lator [55]                                                                                        | 30 |

| 3.3.  | Basic capacitor-less LDO concept [55]                                                             | 32 |

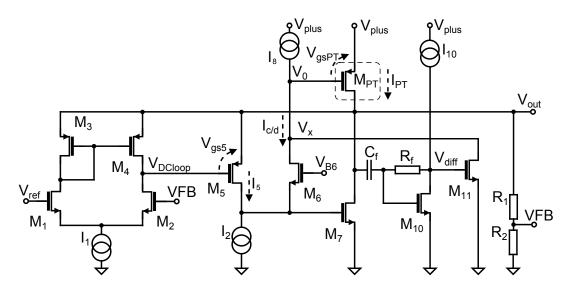

| 3.4.  | The core of the capacitor-less LDO regulator [55]                                                 | 32 |

| 3.5.  | Topology for proposed capacitor-less LDO voltage regulator [58]                                   | 33 |

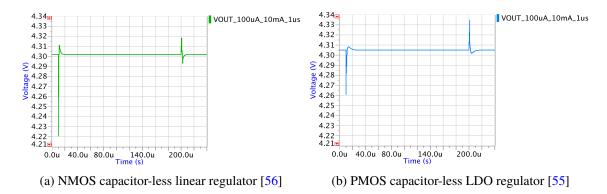

| 3.6.  | Comparison of LDO transient response on the load step from $100 \mu A$ to              |          |

|-------|----------------------------------------------------------------------------------------|----------|

|       | $10 mA$ with $t_{rise}$ resp. $t_{fall} \ 1 \mu s$                                     | 34       |

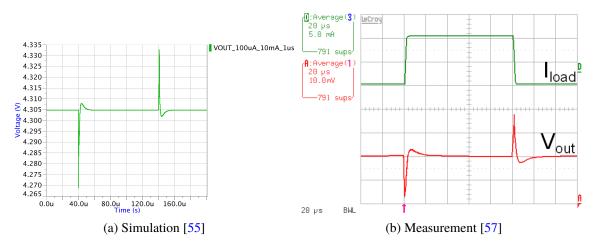

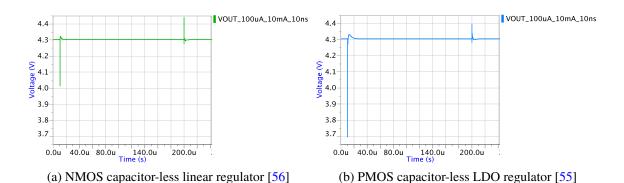

| 3.7.  | Comparison of LDO transient response on the load step from $100 \mu A$ to              |          |

|       | $10 mA$ with $t_{rise}$ resp. $t_{fall}$ $10 ns$                                       | 35       |

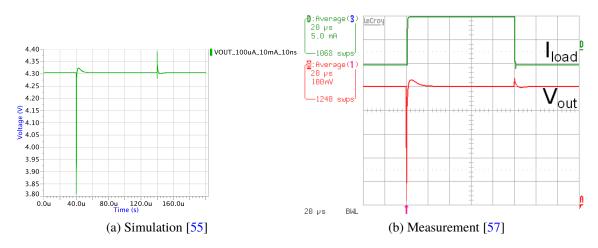

| 3.8.  | Line transient, typical case, $step = 500 mV$ in $1 \mu s$ and in $10 \mu s$ (a). Cur- |          |

|       | rent consumption versus $I_{out}$ , typical case and worst case (b) [55]               | 35       |

| 3.9.  | Layout of capacitor-less LDO regulator [55]                                            | 36       |

| 3.10. | Basic concept of capacitor-less linear regulator with NMOS power tran-                 |          |

|       | sistor [56]                                                                            | 40       |

| 3.11. | The core of the NMOS capacitor-less linear regulator                                   | 41       |

| 3.12. | Circuit implementation of the capacitor-less linear regulator with NMOS                |          |

|       | power transistor [56]                                                                  | 42       |

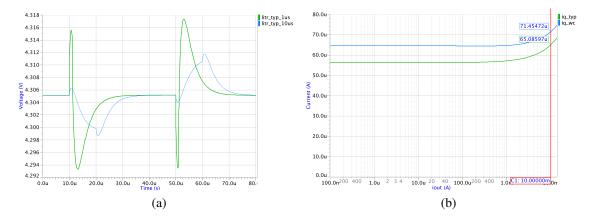

| 3.13. | Comparison of transient response on the load step from $100 \mu A$ to $10 mA$          |          |

|       | with $t_{rise}$ resp. $t_{fall} 1 \mu s$                                               | 43       |

| 3.14. | Comparison of transient response on the load step from $100 \mu A$ to $10 mA$          |          |

|       | with $t_{rise}$ resp. $t_{fall}$ 10 ns                                                 | 44       |

|       |                                                                                        | 40       |

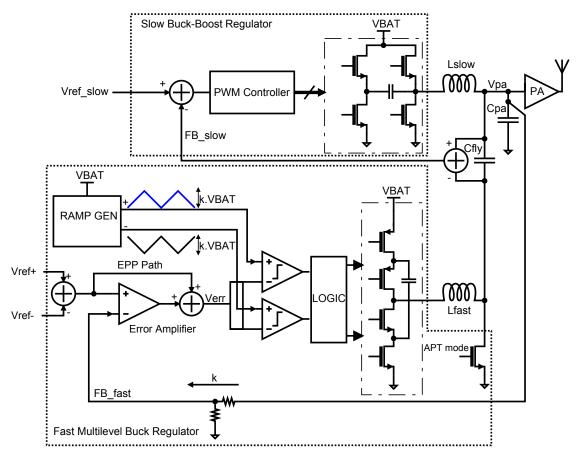

| 4.1.  | Block diagram based on Envelope Tracking technique                                     | 48       |

| 4.2.  | Concept of the switching converter in parallel connection with linear reg-             | 40       |

|       | ulator                                                                                 | 49<br>50 |

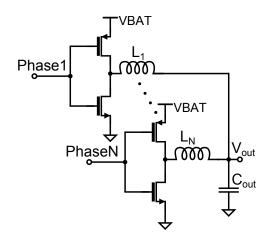

| 4.3.  | Concept of the multiphase buck converter                                               | 50       |

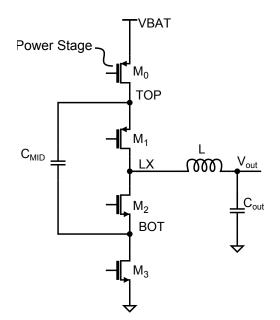

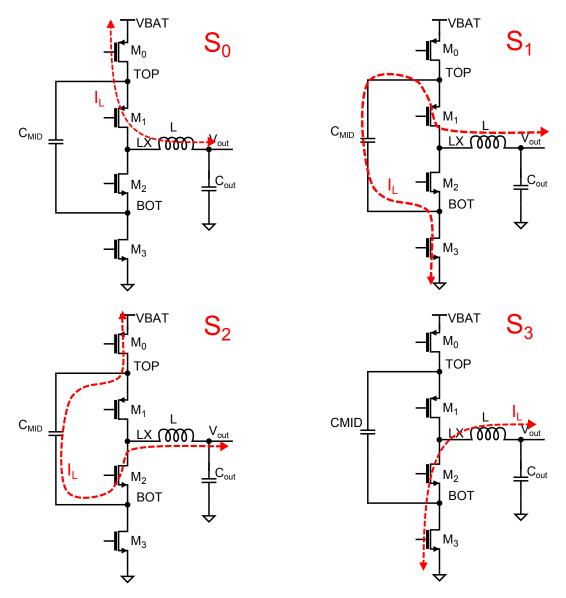

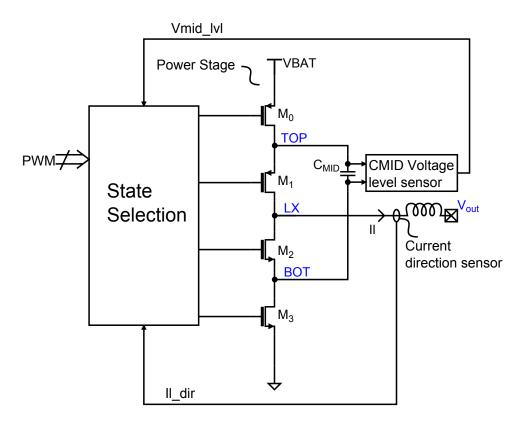

| 4.4.  | Concept of the three-level buck converter                                              | 51       |

| 4.5.  | States of three-level FCC [75]                                                         | 52       |

| 4.6.  | 3-level converter RSS regulation circuit [75]                                          | 54       |

| 4.7.  | RSS algorithm applied to 3-level converter [75]                                        | 55       |

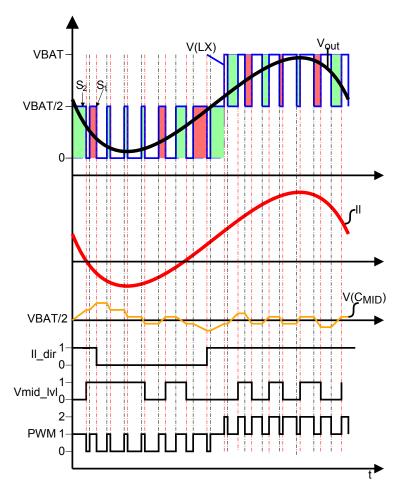

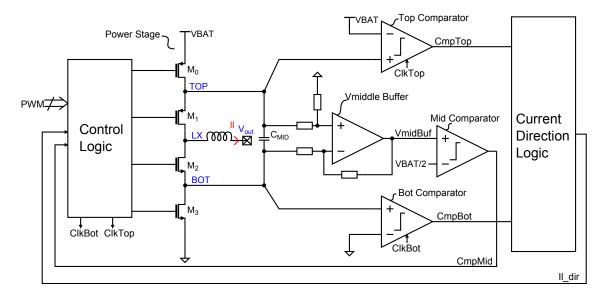

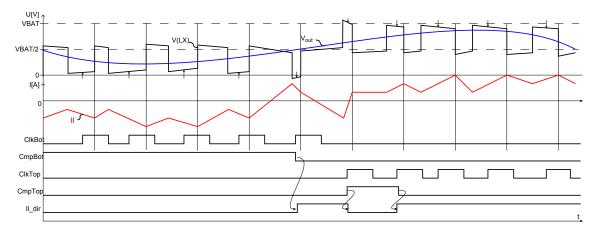

| 4.8.  | Block diagram of the proposed circuit                                                  | 56       |

| 4.9.  | Sensing circuitry operation [75]                                                       | 57       |

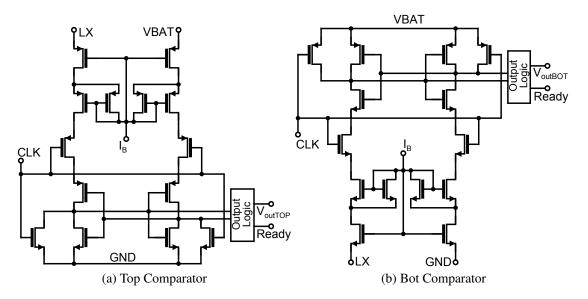

| 4.10. | Simplified schematics of the proposed triggered comparators                            | 58       |

| 4.11. | Envelope Modulator architecture [82]                                                   | 59       |

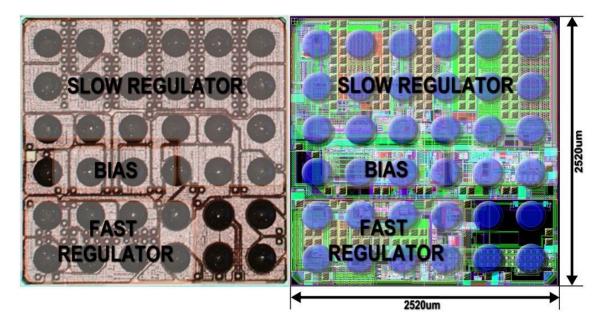

| 4.12. | Micrograph and layout of the EM [82]                                                   | 60       |

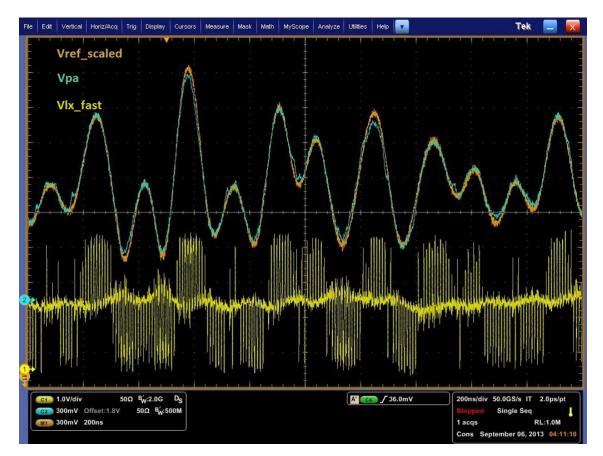

| 4.13. | Tracking performance for LTE10 signal [82]                                             | 61       |

| 5.1.  | Buck converter with voltage-mode PWM controller                                        | 63       |

| 5.2.  | PWM modulation wave                                                                    | 64       |

| 5.3.  | The core of the proposed dual edge ramp generator                                      | 65       |

| 5.4.  | Simplified block diagram of the proposed dual edge ramp generator                      | 66       |

| 5.5.  | Timing diagram of the sampling principle for generating the <i>MID_SNS</i>             | -        |

|       | signal                                                                                 | 67       |

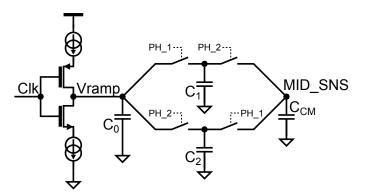

| 5.6.                                                                                                                                                                    | Principal schematic for generation of the <i>MID_SNS</i> signal                                                                                                                                                                                                                                                     | 67                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 5.7.                                                                                                                                                                    | Timing diagram of the sampling principle for generating the <i>AMP_CTRL</i>                                                                                                                                                                                                                                         |                                                                                                                                    |

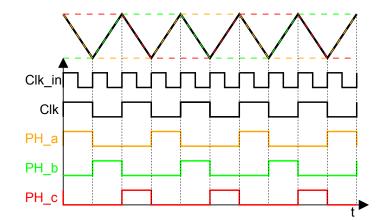

|                                                                                                                                                                         | signal                                                                                                                                                                                                                                                                                                              | 68                                                                                                                                 |

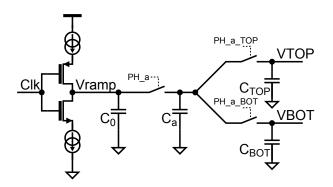

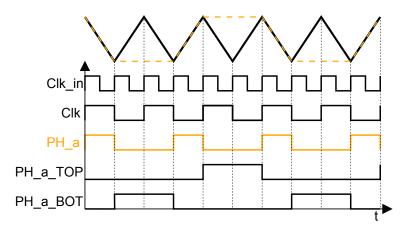

| 5.8.                                                                                                                                                                    | Principal schematic for generation of the AMP_CTRL signal - Phase_a                                                                                                                                                                                                                                                 | 68                                                                                                                                 |

| 5.9.                                                                                                                                                                    | Timing diagram of the sampling principle for generating the AMP_CTRL                                                                                                                                                                                                                                                |                                                                                                                                    |

|                                                                                                                                                                         | for one phase                                                                                                                                                                                                                                                                                                       | 68                                                                                                                                 |

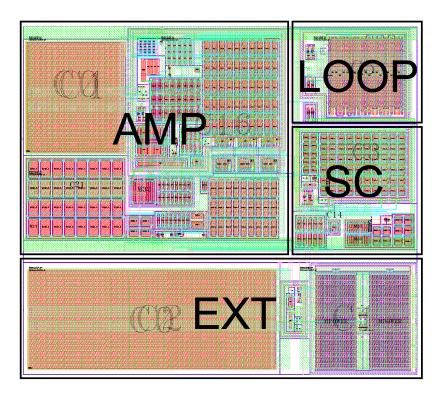

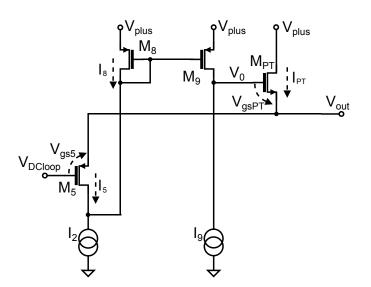

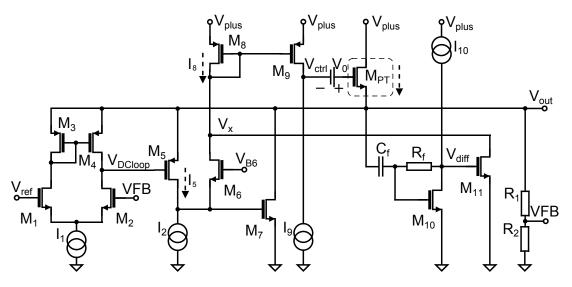

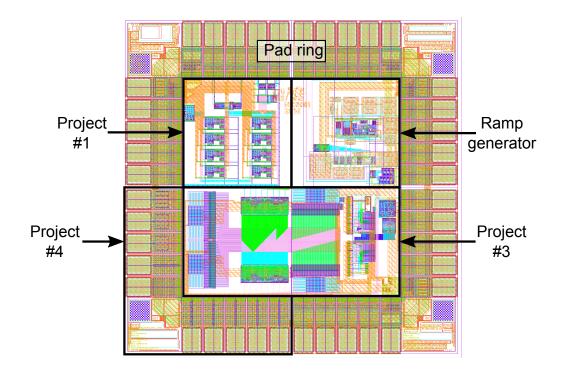

| 5.10.                                                                                                                                                                   | The layout of the multi-project test chip without displayed tiles for better                                                                                                                                                                                                                                        |                                                                                                                                    |

|                                                                                                                                                                         | layer planarization                                                                                                                                                                                                                                                                                                 | 69                                                                                                                                 |

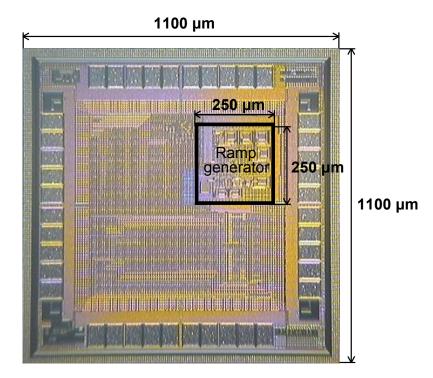

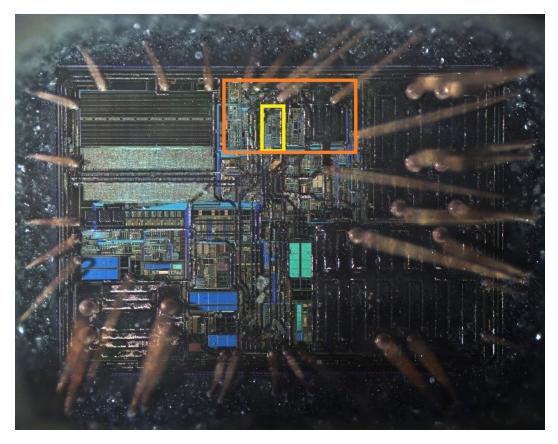

| 5.11.                                                                                                                                                                   | Photo of the fabricated die. The proposed dual edge single ended ramp                                                                                                                                                                                                                                               |                                                                                                                                    |

|                                                                                                                                                                         | generator occupies the marked area                                                                                                                                                                                                                                                                                  | 70                                                                                                                                 |

| 5.12.                                                                                                                                                                   | Emblems of the Czech Technical University in Prague which is located on                                                                                                                                                                                                                                             |                                                                                                                                    |

|                                                                                                                                                                         | the fabricated chip                                                                                                                                                                                                                                                                                                 | 70                                                                                                                                 |

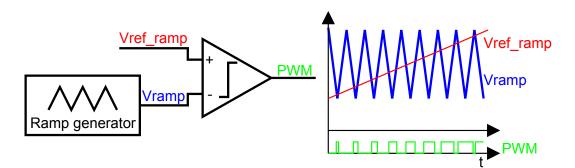

| 5.13.                                                                                                                                                                   | Block diagram and principle of measurement linearity of the proposed                                                                                                                                                                                                                                                |                                                                                                                                    |

|                                                                                                                                                                         | ramp generator                                                                                                                                                                                                                                                                                                      | 71                                                                                                                                 |

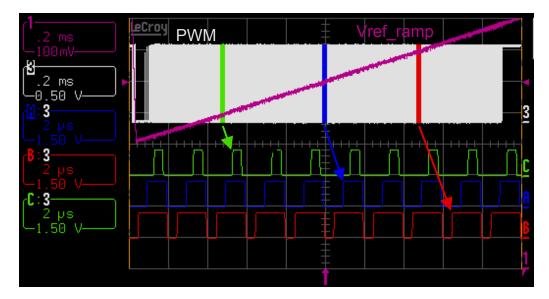

| 5.14.                                                                                                                                                                   | Demonstration of lab results, voltage reference <i>Vref_ramp</i> and <i>PWM</i> sig-                                                                                                                                                                                                                                |                                                                                                                                    |

|                                                                                                                                                                         | nal with zooms                                                                                                                                                                                                                                                                                                      | 71                                                                                                                                 |

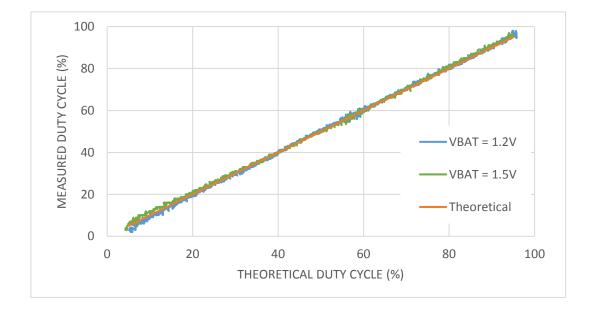

| 5.15.                                                                                                                                                                   | Comparison of ramp linearity for different supply voltage with theoretical                                                                                                                                                                                                                                          |                                                                                                                                    |

|                                                                                                                                                                         | calculation                                                                                                                                                                                                                                                                                                         | 72                                                                                                                                 |

|                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |

|                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                     | 75                                                                                                                                 |

| 6.1.                                                                                                                                                                    | Transfer function of a required ideal predictor                                                                                                                                                                                                                                                                     | 75                                                                                                                                 |

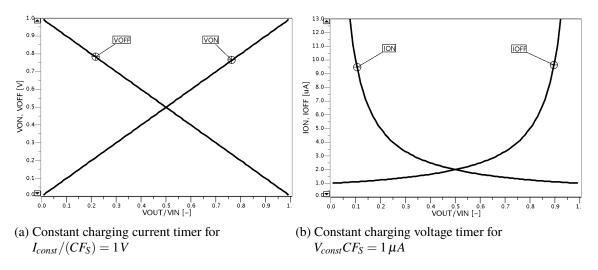

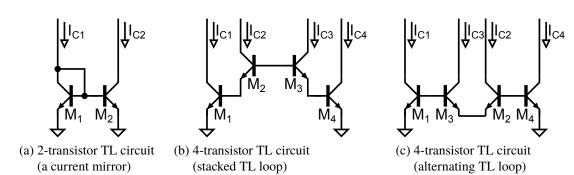

| 6.2.                                                                                                                                                                    | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77                                                                                                                                 |

| 6.2.<br>6.3.                                                                                                                                                            | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77<br>78                                                                                                                           |

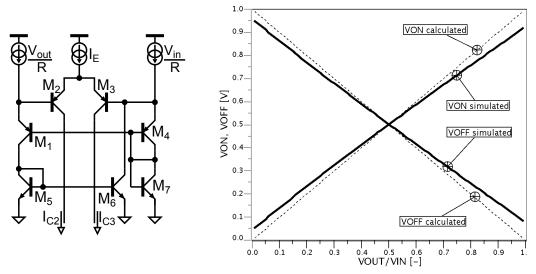

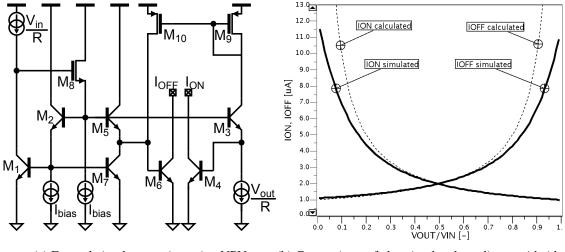

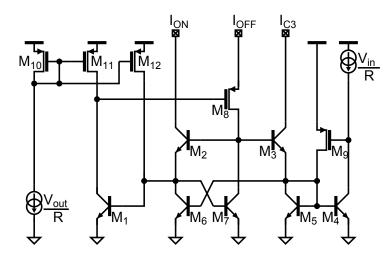

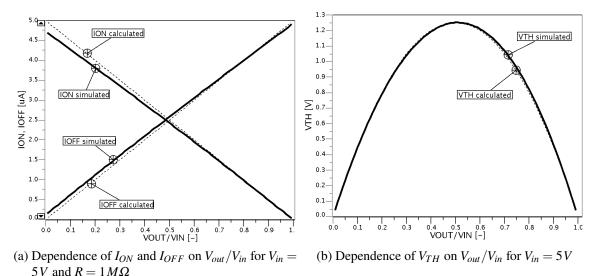

| <ul><li>6.2.</li><li>6.3.</li><li>6.4.</li></ul>                                                                                                                        | Example of trans-linear circuitsTL predictor for constant charging current timerTL predictor for constant threshold voltage timer                                                                                                                                                                                   | 77<br>78<br>80                                                                                                                     |

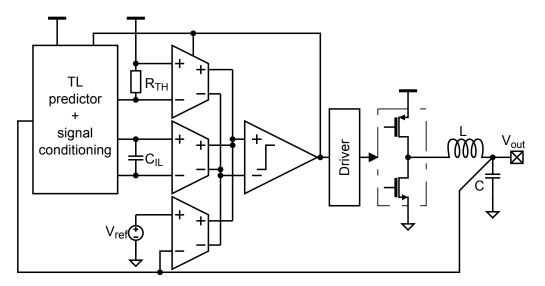

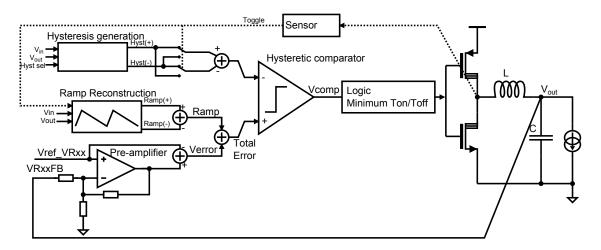

| <ol> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ol>                                                                                                      | Example of trans-linear circuitsTL predictor for constant charging current timerTL predictor for constant threshold voltage timerTL predictor for constant threshold voltage timerExample implementation of a TL predictor for a hysteretic converter                                                               | 77<br>78<br>80<br>82                                                                                                               |

| <ol> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> </ol>                                                                                        | Example of trans-linear circuitsTL predictor for constant charging current timerTL predictor for constant threshold voltage timerTL predictor for constant threshold voltage timerExample implementation of a TL predictor for a hysteretic converterTransfer function of a TL predictor implementation of Fig. 6.5 | 77<br>78<br>80<br>82<br>84                                                                                                         |

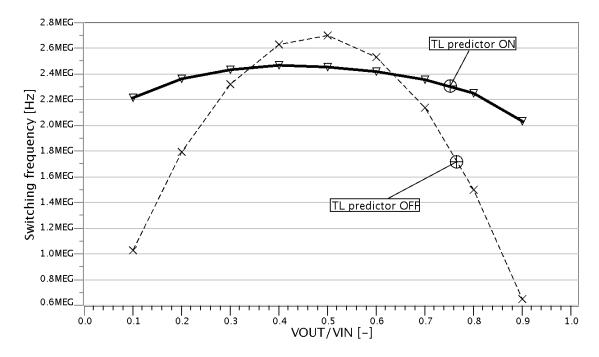

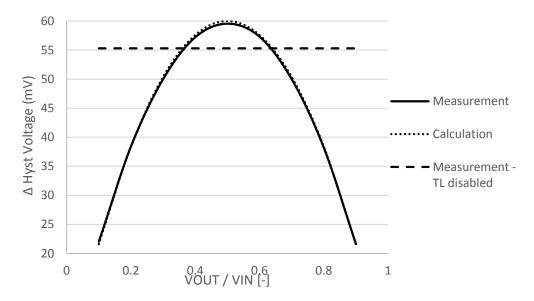

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> </ul>                                                                          | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77<br>78<br>80<br>82                                                                                                               |

| <ol> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> </ol>                                                                                        | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77<br>78<br>80<br>82<br>84<br>84                                                                                                   |

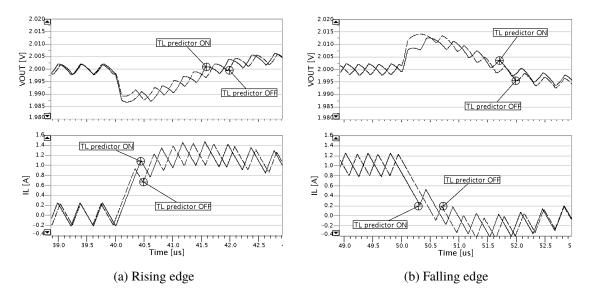

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> </ul>                                                            | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77<br>78<br>80<br>82<br>84                                                                                                         |

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> </ul>                                                            | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77<br>78<br>80<br>82<br>84<br>84<br>84                                                                                             |

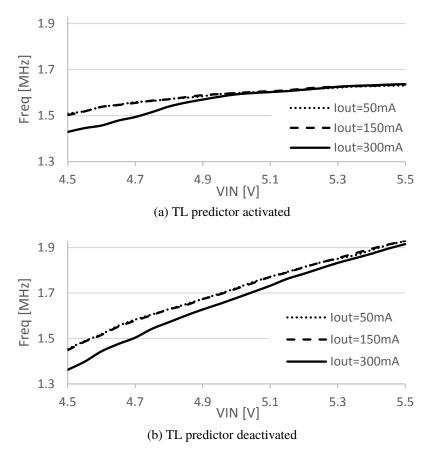

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> <li>6.9.</li> </ul>                                              | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77<br>78<br>80<br>82<br>84<br>84                                                                                                   |

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> <li>6.9.</li> </ul>                                              | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77<br>78<br>80<br>82<br>84<br>84<br>85<br>86                                                                                       |

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> <li>6.9.</li> <li>6.10.</li> </ul>                               | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | <ul> <li>77</li> <li>78</li> <li>80</li> <li>82</li> <li>84</li> <li>84</li> <li>85</li> <li>86</li> <li>86</li> </ul>             |

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> <li>6.9.</li> <li>6.10.</li> <li>6.11.</li> </ul>                | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | 77<br>78<br>80<br>82<br>84<br>84<br>85<br>86                                                                                       |

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> <li>6.9.</li> <li>6.10.</li> <li>6.11.</li> </ul>                | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | <ul> <li>77</li> <li>78</li> <li>80</li> <li>82</li> <li>84</li> <li>84</li> <li>85</li> <li>86</li> <li>86</li> <li>87</li> </ul> |

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> <li>6.9.</li> <li>6.10.</li> <li>6.11.</li> <li>6.12.</li> </ul> | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | <ul> <li>77</li> <li>78</li> <li>80</li> <li>82</li> <li>84</li> <li>84</li> <li>85</li> <li>86</li> <li>86</li> </ul>             |

| <ul> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> <li>6.9.</li> <li>6.10.</li> <li>6.11.</li> <li>6.12.</li> </ul> | Example of trans-linear circuits                                                                                                                                                                                                                                                                                    | <ul> <li>77</li> <li>78</li> <li>80</li> <li>82</li> <li>84</li> <li>84</li> <li>85</li> <li>86</li> <li>86</li> <li>87</li> </ul> |

# **List of Tables**

| 3.1. | Comparison of results from simulation / post layout simulation (PLS) / measure- |    |

|------|---------------------------------------------------------------------------------|----|

|      | ment for proposed PMOS capacitor-less LDO regulator [58]                        | 37 |

| 3.2. | Comparison of simulation results between proposed NMOS capacitor-less linear    |    |

|      | regulator and PMOS capacitor-less LDO regulator [56]                            | 45 |

| 4.1. | Configurations of the power stage [75]                                          | 52 |

| 4.2. | State selection circuit decision table [75]                                     | 53 |

## Nomenclature

- 3G Third Generation

- APT Average power tracking

- BCD Bipolar, CMOS, DMOS

- BW Bandwidths

- CCM Continuous Conduction Mode

- DAC Digital-to-analog converter

- DCM Discontinuous Conduction Mode

- DLL Delay-locked Loop

- DSP Digital signal processor

- EA Envelope Amplifier

- EM Envelope modulator

- EMI Electro-Magnetic Interference

- EPP End point prediction

- ESR Equivalent Series Resistance

- ET Envelope Tracking

- FCC Floatinig Capacitor Converter

- GPS Global Positioning System

- HM Hysteretic Mode

- ICs Integrated Circuits

- LDO Low Dropout

- LQ Low Quiescent

- LTE Long Term Evolution

- LTE-A Long Term Evolution Advanced

- MP3 Digital Audio Format

- NFC Near Field Communication

- OVD Output Voltage Detector

- PA Power Amplifier

- PAPR Peak-to-Average Power Ratio

- PLL Phase-locked Loop

- PMU Power Management Unit

- PWM Pulse-Width Modulation

- RSS Redundant state selection

- SDRAM Synchronous Dynamic Random Access Memory

- SMPS Switching-mode Power Supply

- TL Trans Linear

- TRNG True Random Number Generator

- Tx Transmitter

- ULQ Ultra Low Quiescent

- DC Direct Current

- $C_{diff}$  Error amplifier output capacitance

- $P_x$  Pole

- $R_{diff}$  Error amplifier output resistance

- V<sub>dsat</sub>, V<sub>sat</sub> Saturation voltage

- $V_{ds}$  Drain-source voltage

- *V<sub>out</sub>* Output voltage

- V<sub>plus</sub> Supply voltage

- DC Direct Current

- DC-DC converters Convertor is an electronic device which is supposed to change one DC voltage to another DC voltage level

- ET PA Envelope Tracking Power Amplifier

- FCC Flying Capacitor Converter

- RF Radio Frequency

- SoC System on Chip

- WiMAX Worldwide Interoperability for Microwave Access

# Chapter Introduction

Currently, the portable devices go through rapid development in order to help us in many ways in our daily life. Their main functions contain a GPS and NFC module, a display, a high performance audio/video subsystem, modem for wireless communication or a radio receiver module, a memory subsystem with SDRAM and Flash, an application processor with graphics acceleration, etc. Great emphasis is placed especially on increasing the computing power. However, we need to ensure also adequate lifetime and reliability of these devices. The new processing technologies, especially for the processor and memory, evolve rapidly. Reducing power consumption is still difficult to achieve. On the contrary, power consumption increases, due to increasing operating frequency. The development of battery technology is not improving sufficiently either. The solution of the above can be found in advanced power management, which is the key factor to achieve the required properties.

Increasing priority of optimized power management and consequently prolonging battery life of portable devices is one of key reasons why chip design changes towards system on chip (SoC) solutions. The power consumption of such a system varies extremely over the different use cases; the lowest power consumption of below 50mW is measured for MP3 audio playback to the headphone and over 3W are required for video decoding including the power for color display and the stereo speaker. Many different use cases have to be considered and for each one the overall power consumption must be optimized to guarantee a long battery operation. In addition to the power consumption, the overall size is a key differentiator for a portable device. Of course, lower power consumption enables the usage of smaller batteries, but in addition, the devices get smaller every year with increased functionality which is only possible by higher integration. The main task of power management unit (PMU) is to establish a flow of energy from a battery to a device in the most efficient way and so to contribute to extension of lifetime of such a complex system. PMU deals with a distribution of energy depending on actual power supply demand of particular circuits (active, stand by, sleep and power off). PMU is usually divided into several parts according to voltage levels demanded by particular blocks. The most frequent demands are low noise and constant supply voltage. The blocks that are most commonly used in power management are switching converters and linear regulators.

With the increasing effort to integrate all circuits into a single chip, thereby establishing a SoC solution, the demands for PMU and its integration are growing [1]. Ideally, each block in the SoC should be supplied by independent regulated voltage. This can be achieved for example by using a dedicated on-chip linear voltage regulator for each circuit in the SoC. The main assumptions concerning these regulators in the SoC are small silicon area, low power dissipation, and last but not least the absence of external components that must be connected to the chip, and thus increasing the price of the whole system and occupying pins of the chip. The main objective in this part of research is to develop possible architectures for capacitor-less linear regulators, which can be used in SoC applications. There will be presented two topologies of the capacitor less linear regulators. The first one is based on PMOS power transistor and the other on NMOS power transistor.

Due to the quickly changing nature of the load, which is often determined by the software applications, the supplies are required to have fast dynamic response and high efficiency over the full range of operation. These requirements can be achieved by switching regulators that have been used in ICs for many years.

The power amplifier (PA) is the most power-consuming component in portable devices for wireless communication and its low amplification efficiency leads to a short battery life. Moreover, as new generation of wireless communication systems is developing (such as LTE, LTE-A, and WiMAX) and their information content increases, modulation systems need to have wider bandwidths (BWs) and a higher peak-to-average power ratio (PAPR). To satisfy the linearity specification of the signals, a PA should be operated at a back-off output power region, where the efficiency is low. To improve the low efficiency at the back-off power region, many efficiency enhancement techniques have been proposed.

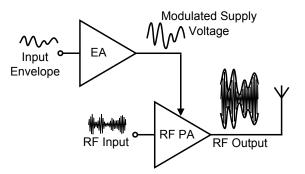

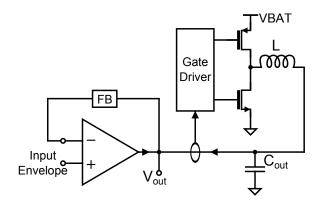

The envelope tracking (ET) technology is a promising approach to achieve both high linearity and high efficiency. Because supply voltage of the PA is modulated by a supply modulator, the efficiency of the envelope tracking power amplifier (ET PA) is proportional to the efficiency of the supply modulator. In an ET PA, a supply modulator tracks the radio frequency (RF) envelope and supplies an instantaneous collector bias voltage to the PA, which is minimized to ensure high efficiency without linearity degradation for a given instantaneous input power. Several topologies for the ET have been proposed such as: fast buck converters, multi-level buck, parallel hybrid structure with a Class-AB amplifier AC-coupled with a buck converter. For an improved efficiency, a feed-forward signal, a dual-switch, a multi-phase PWM control, or multi-level power stage is used. These techniques enable more accurate tracking of the switching converter without increasing of the switching frequency. In this part of the research we will focus on three-level flying capacitor converter (FCC). More precisely, we will engage the issue of efficient regulation of the flying capacitance voltage in the three-level FCC for 4G RF PA.

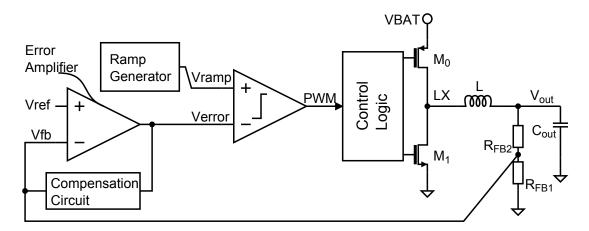

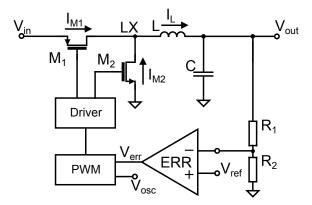

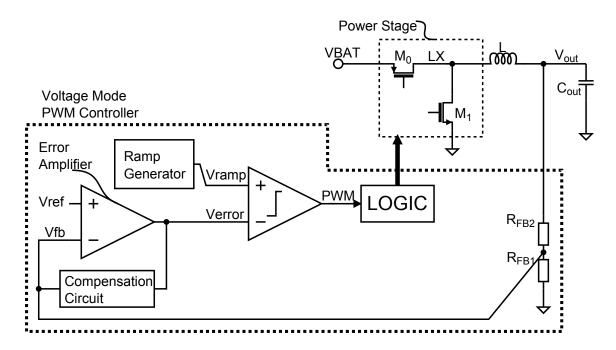

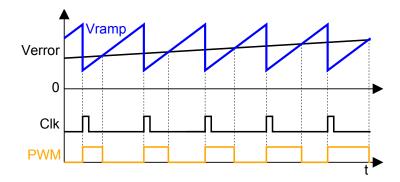

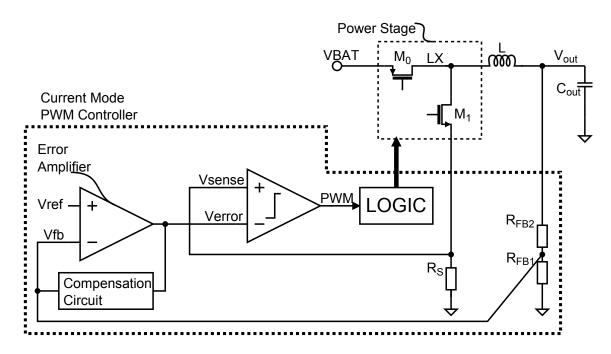

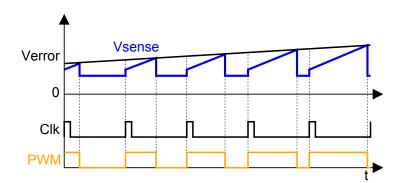

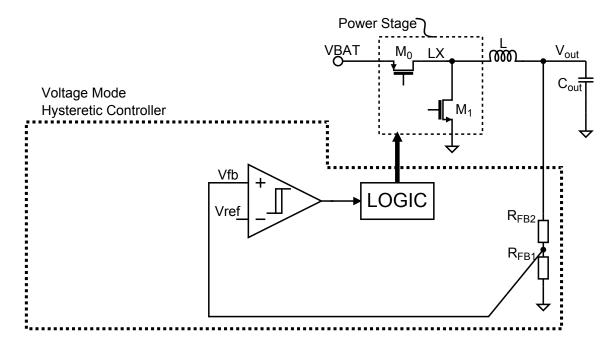

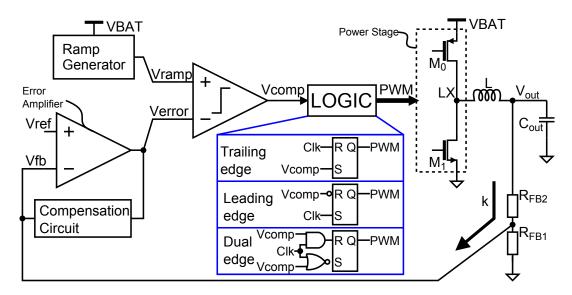

Switching DC-DC converters (e.g. Buck) with voltage-mode PWM controller (Fig. 1.1) are widely used as basic building blocks for portable devices due to their high power efficiency. Due to the increasing demands (e.g. switching frequency, low current consumption and good regulation of these regulators) we need to develop new design approaches, which will bring the required properties. One of the essential blocks in the PWM controller is the ramp generator. We can improve the performance of the whole system by designing a precise ramp, which will be proportional to the input voltage (to generate feedforward effect), to decrease the current consumption (by excluding the comparators from this block) and significantly increase ramp frequency by omitting the comparator's delays.

Figure 1.1.: Block diagram of a voltage-mode PWM buck regulator

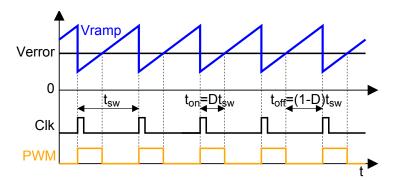

The most essential principle of a switching converter (for example a Buck converter) is that the controller computes  $T_{ON}$  and  $T_{OFF}$  times for the power stage based on the various conditions of the Buck.

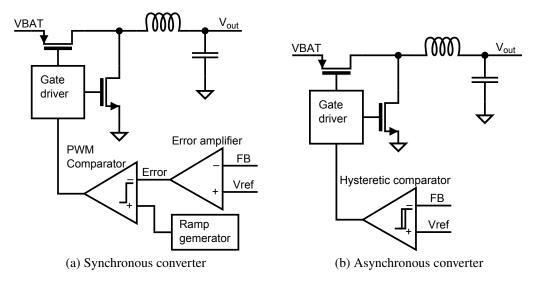

In a synchronous converter such as a PWM one, the period  $T = T_{ON} + T_{OFF}$  is a constant defined by the frequency of the modulation ramp and the ratio  $T_{ON}/(T_{ON} + T_{OFF})$  is determined by a feedback loop set to regulate the output voltage of the converter (Fig. 1.2a). On the opposite, an asynchronous converter such as an Hysteretic Mode (HM) controller (Fig. 1.2b), has no external definition of  $T = T_{ON} + T_{OFF}$ . It is derived as a result of the converter parameters (*L*, *C*, hysteresis for example) and the external parameters (*VBAT*, *V*<sub>out</sub>, *I*<sub>LOAD</sub>...). For specific type of the converter, the relation between *T*, the converter parameters and the external parameters can be analytically derived.

A timing system that controls such a DC-DC converter switching frequency in a feed-

Figure 1.2.: Basic types of switching converters

forward way (i.e. with no direct measurement of the switching frequency), should in consequence implement this analytical derivation based on the measured external parameters. This paper presents the new concept of the feed-forward frequency control for asynchronous converters based on Trans Linear (TL) circuit. Stabilization of the switching frequency is based on modulating of hysteresis for comparator, which guarantees that the switching frequency is as constant as possible, thus avoiding the need for a frequency feedback control such as a PLL or DLL. The proposed solution preserves excellent transient properties of the asynchronous converters.

### 1.1. Organization of this thesis

This thesis is organized as follows. The topic of this work together with descriptions of author's contributions and the state of the art are introduced in chapter 1. The PMU fundamentals and elementary building blocks are summarized in chapter 2. Chapter 3 details the principle, design, implementation and measured results of capacitor-less linear regulators. Chapter 4 deals with the synchronous PWM converter for ET technique especially the sensors for current direction sensor. Chapter 5 describes the principle, design, implementation, and measured results of a new concept of triangular ramp generator. Frequency control technique for asynchronous switching converters is discussed in chapter 6. Finally, in chapter 7 are summarized the achieved results and recommendations for future research.

### 1.2. Author's scientific contributions

The scientific contributions of this research are in the area of power management for portable systems where only a limited power source is available. However, the concepts and techniques used in the proposed linear regulators, the apparatus for current direction detection, triangular ramp generator with single ended output and frequency control for asynchronous converters can be utilized in other general purpose power management systems. The contributions can be categorized into these sections:

- Author has developed new architectures for capacitor-less linear regulators with low current consumption for SoC applications. In order to achieve the research goals, the transient characteristics of capacitor-less regulator was improved by new method which compensates lack of capacity of eliminated dedicated capacitors. This can be achieved by implementing of fast feedback loops, so critical for this type of regulators. Author has developed two new topologies of the capacitor less linear regulators which were designed in 130 nm bulk CMOS technology known as HCMOS9A.

- Author has designed new sensor for current direction detection in the inductor, which

is used in apparatus for efficient regulation of the flying capacitance voltage in the

three-level flying capacitor converter for 4G RF PA (switching frequency

> 80MHz). For the implementation of this control technique special triggered comparators have been developed. With these comparators we can create the sensor

for current direction detection, which is based on indirect measurement of the coil

current through. The basic principle is based on the voltage drop that is generated

at the power switches. The switching convertor with current direction sensor was

designed by the author in the technology known as HCMOS9A.

- Author has developed new concept of dual edge ramp generator with single ended output. This ramp generator can be used in PWM application (e.g. for DCDC converters, D-class inverters or amplifiers). Originality of the design of the saw tooth signal generator consists mainly in the use of new control loops, ensuring a low power consumption in a wide range of operating frequencies. This new solution has been proposed due to the fact that comparators are not used in the proposed generator for detecting threshold levels of the output signal. The device is fully integrated and is manufactured in 130 nm bulk CMOS technology known as HCMOS9GP.

- Author has designed new concept of feed-forward frequency control for asynchronous converters based on TL circuit. Novel architecture and configuration of the feed-forward frequency control circuit for asynchronous DC-DC switching converters has been developed. The proposed solution preserves excellent transient properties

of the asynchronous converters. Proposed feed-forward frequency control method is based on modulating of hysteresis for the comparator, which guarantees that the switching frequency is as constant as possible. The proposed concept avoids the need for a frequency feed-back control such as a PLL or DLL. The implementation techniques are experimentally verified on a prototype chip manufactured in 160 nm BCD technology known as BCD8sP and operates at the switching frequency of up to 2MHz.

All of these technologies have been provided by STMicroelectronics.

### 1.3. State of the art

With each new technology, demands on the power supply of the blocks in the system are growing, especially low noise or high performance [2, 3, 4]. Furthermore, it also increases the number of voltage domains, which occur in the individual systems. With the increase of the voltage domains, it is necessary to develop and upgrade the existing approaches in power management, so that we can meet these requirements. One of the biggest challenges for distribution of the power supply is to create devices that meet the strict requirements and occupy a small area.

In power management, there are three commonly used general circuit topologies [5], which provide DC supply voltage on the chip [6]. The first group includes switching converters, which are employed to regulate high-performance integrated circuits like processor or RF PA due to their high power efficiency [7]. Another possible topology is created by charge pump regulators. These circuits are usually utilized to generate high voltage for lighting or memory units. And finally linear regulators that are used to provide low noise supply voltage with very low ripple for noise sensitive blocks like analog/RF circuits [8, 9]. Typically, these all devices require external components that must be connected to the chip, and thus increase the price of the whole system and occupy pins of the chip. In the last decade, a considerable number of the authors working in the field of power management deal with the problems associated with the elimination of external components, because by removing of external components of power supply devices we bring new possibilities in power management.

For example the limitation of the classical LDO regulators is caused mainly due to the associated single pole-zero cancellation scheme, in which an external capacitor with a high equivalent series resistance (ESR) is required. With help of ESR we are able to create a zero point which can be placed near to the second pole of the system and so we gain the necessary phase shift and the circuit is stable. However, this solution brings difficulties which are associated mainly with the bandwidth limitations and thus short response time

[10, 11, 12]. There are several different principles how to narrow this dependence on ESR. To the most common methods belongs compensation inside the regulator, or creating of inner zero or creating adaptive modulation of dominant pole. Another method is also elimination of a large external capacitor [11]. However, the removal of the external capacitor at the LDO regulator brings disadvantages such as the deterioration of the transient response [10, 13]. Furthermore, there may be problems with stability at low current load due to the fact that output pole is moved significantly with this load.

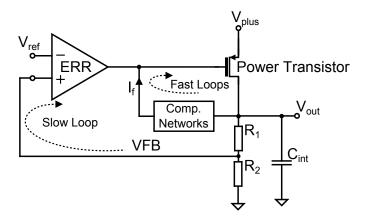

From this reason it is necessary to extend the circuit by fast loops, which will be responsible for fast response of the circuit and which will have greater bandwidth than the bandwidth of the slow regulating loop. At the same time we need to ensure stability of the regulators.

There are several approaches how to deal with these problems, which have been published. The first approach uses direct current feedback to improve line and load regulations [14]. In this structure, symmetrically-matched voltage mirror is employed in sensing the load current. Next solution uses a Dual-Loop for transient improvement [15]. In this concept there are two OTAs, one for slow voltage loop and another for current loop. Voltage-Spoke detection circuit for improving of transient response of capacitor-less LDO is proposed in [16]. The detection circuit is based on capacitive coupling and it makes use of the rapid transient voltage at the LDO output to increase the bias current momentarily. Other authors propose capacitor-less LDO with a low power output voltage detector (OVD) [17]. The OVD is based on an R/C high-pass filter which is able to detect the fastchanging voltage at the LDO output and activate an additional path to control the power transistor. Last but not least paper presents a capacitor-less LDO regulator with a slew-rate enhancement circuit [18]. This proposed slew-rate enhancement circuit senses the transient voltage at the output of the LDO to increase the bias current of the error amplifier for a short duration.

Another important area of power management, which engineers currently investigating, is power supply for RF PA for broadband 3G/4G wireless standards. It is due to the fact that these standards utilize highly spectral-efficient modulation schemes with inherently non-constant-envelope signals having high PAPR. The non-constant envelope signals with high PAPR require the PAs to be backed off from their saturation power to satisfy the stringent linearity specs. This is a major bottleneck for realizing highly efficient mobile 3G/4G transmitters (Txs).

Envelope tracking technique is a dynamic supply modulation scheme, and this technique is among the most effective approach to enhance both high linearity and high efficiency of efficiency of PA. Recent literature has demonstrated several topologies for the envelope amplifier (EA).

The topology of the first approach, which is most common, is based is based on a hybrid modulator [19]. This modulator combining a class-AB buffered linear amplifier and a highly efficient switching-mode buck converter in a master–slave configuration. The linear stage must have large bandwidth to suppress the switching ripples. Next solution uses high-frequency buck PWM converter [20]. This modulator has constant switching frequency, which is equal 130MHz. Other authors propose dual switcher hybrid architecture [21]. The supply modulator has a combined structure of a linear amplifier and two phase switching converter. This parallel combination of switching converters enable more accurate tracking without increase of the switching frequency. Least but not last concept ET modulator is three level buck converter in [22]. This is an improved version of a regular buck converter where are two additional switches and flying capacitor. With this arrangement, the circuit can apply three different voltage levels to the filter and thereby doubling its effective switching frequency. However, there are several practical challenges for designing the ET systems, such as the bandwidth limitation of the envelope modulator, and the precise timing alignment between the envelope and the RF paths.

The PWM voltage-mode converters (e.g. Buck) require a ramp generator to generate the ramp signal. This ramp generator should have as low power consumption as possible in order to achieve high efficiency of the converter, free of the external components for reducing board cost, and at the same time small deviation of the ramp for both amplitude and timing. That is important specially for higher switching frequencies of converters, because this ramp deviation causes a shift of harmonic frequencies at high frequencies. It affects the noise performance of the circuits powered by the PWM voltage converter. The voltage-mode PWM controller and the ramp generator have been proposed and used for years. Typically it contains a capacitor, a charging current branch, a discharging current branch and the comparators [25, 26]. One of the possible solutions to reduce the power consumption is to create more efficient comparator [23] or to exclude it from this block.

For improving the current consumption, the ramp generator with Schmitt trigger was introduced in [24]. This paper proposes a ramp generator with Schmitt trigger circuit replacing the conventional ramp circuit using two comparators and one S-R latch circuit. However, in this case, the ramp is generated in dependence on the hysteresis voltage  $V_{SPH}$  and  $V_{SPL}$  on the Schmitt trigger circuit and therefore no longer guarantees the constant switching frequency of the converter. A similar approach was also chosen in [23], with the difference that a hysteresis comparator is used here. This reduces the consumption but the switching frequency is no longer constant. In [25] 10/30MHz PWM buck converter with an accuracy-improved ramp generator is proposed. To shorten the delay time of the comparator in the ramp generator, a high speed two-stage push pull comparator is used. This is associated with higher generator consumption. The presented proposal in this work

deals with the second option, which is the complete removal of comparators from the ramp generator.

Asynchronous converters (e.g. hysteric control) offers an unsurpassed transient response in comparison with other analog and digital techniques, which makes it advisable to adopt this technique in all cases where wide bandwidth and robustness are required [34]. However, the drawback is that its switching frequency changes with varying input voltage, output voltage or load current, which might result in severe electro-magnetic interference (EMI).

At present, many works have been presented in order to keep the operating frequency of the converters stable, including adaptive hysteresis methods [27, 30, 32, 33] and external signal methods with injection of fixed frequency [31]. The self-adaptive window controller is proposed in [27, 33] to adjust hysteresis window according input voltage, output voltage and load current adaptively. In this system frequency-to-Voltage Converter (FVC) is used to transform the switching frequency  $f_s$  and reference frequency  $f_{ref}$  to its corresponding voltage  $V_s$  and  $V_{ref}$ . Then the error between  $V_s$  and  $V_{ref}$  is used to set the correct hysteresis to achieve constant switching frequency. Although the frequency stabilization is excellent, the disadvantage of this solution is in its complexity, size and overall consumption. The second-order sliding-mode (SOSM) control approach is applied to synchronous buck dc–dc converters, proposed in [28, 29]. Here, the digital state-machine structure is used to stabilize the switching frequency. The novel architecture and configuration of the feed-forward frequency control circuit for asynchronous DC-DC switching converters is presented.

# 2 Chapter Power Management Unit

Every electrical and electronic system needs a power supply to be able to operate. The PMU is especially important in applications requiring high efficiency such as portable electronic systems. This unit can control the charging time, current, and voltage of the battery charger and is responsible for balanced energy distribution according to actual supply-demand of particular circuits and their mode (for example, a device which is in standby mode does not need much energy).

When designing the power supply for the system, consideration needs to be given to the number of supply voltages required, the power handling capabilities of the supplies as well as the ultimate generator of the input. Depending on the power supply requirements of the system, there are several building blocks that could be used to make up the PMU. The combination of the building blocks depends on the input source and output power constraints of the system.

As can be seen from the Fig. 2.1 where is depicted a block diagram for MP3 Player / Recorder, PMU consists of several parts according to requirements of particular blocks in the system. The blocks that belong into PMU are mainly switching converters, charger and linear regulators [35]. Parts of this chapter has been published by the author of this thesis in [55].

### 2.1. Regulation principles

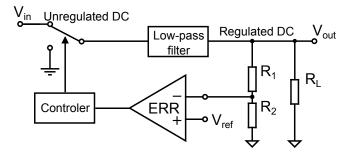

Each electronic power regulator consists of a power element, a controller, and a voltage reference [38], as shown in Fig. 2.2. The input power coming from the supply is converted by the power element and provided to the load. The power conversion can be used a current, a voltage, or a frequency converter (or any combination of these physical quantities). The feedback controller compares the output voltage of the power element with a reference voltage value and acts on the power element so that the error between the two is

Figure 2.1.: Block diagram of MP3 player [36]

minimized. Both linear regulators and switching regulators use this elementary regulation principle.

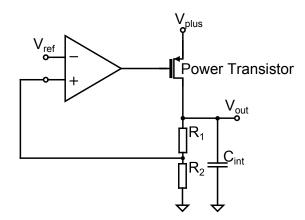

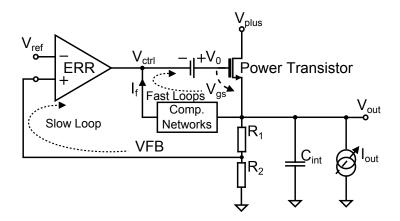

### 2.2. Linear regulators

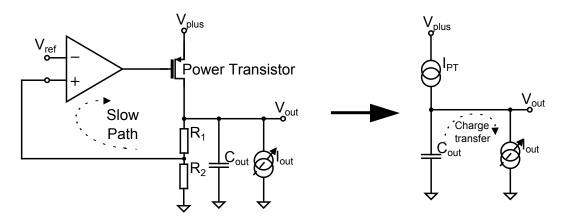

A linear regulator is a circuit that keeps a constant set voltage across its load despite changes in load, temperature, and power supply, among other things. Consequently, such a device has to have the temperature properties of a voltage reference, a good driving capability, and flexibility in output setting. The linear regulator uses a feedback control of sensing the resistive voltage drop to regulate the output voltage as shown in Fig. 2.3. It is constituted of a Power Transistor, a voltage reference ( $V_{ref}$ ) and an error amplifier with a resistive feedback loop composed of R1 and R2. The capacitor  $C_{out}$  is used for adjusting the stability in the loop compensation.

Figure 2.2.: Block diagram of a typical electronic power conversion system

Figure 2.3.: Principal block diagram for linear regulator

The power transistor used in a linear regulator works as an adjustable resistor that reduces the voltage by dissipating the power that is not needed. The error amplifier adjusts the gate voltage  $V_g$  so that the voltage drop across the power transistor gives the desired output voltage value  $V_{out}$ . The regulated voltage value is controlled by the gain of the resistive feedback loop. The error amplifier tends to equalize the voltage at its inputs, and therefore, the load voltage  $V_{out}$  is given by:

$$V_{out} = V_{ref} \frac{R_1 + R_2}{R_2}$$

(2.1)

Linear regulators are very popular due to low electrical noise, the design is less complex and output ripple is smaller in comparison to switching converter, but linear regulators also have some drawbacks. Their efficiency is poor, which means the power dissipated is generally high.

The power loss in the linear regulator mainly comes from the voltage drop across the power transistor. The maximum efficiency of a linear regulator is defined in the formula 2.2 where  $V_{out}$  is the output voltage,  $I_{out}$  is the output current and  $V_{plus}$  is the supply voltage [37].

$$Eff = \frac{V_{out}I_{out}}{V_{out}I_{out} + (V_{plus} - V_{out})I_{out}} \approx \frac{V_{out}}{V_{plus}}$$

(2.2)

Linear regulators can be divided into two basic groups [39]:

- Conventional linear regulators

- LDO regulators

The only difference between these two topologies is in the orientation of a power transistor. Conventional linear regulator utilizes a transistor which is connected in common drain, or this transistor is replaced by BJT transistor or two transistors in Darlington configuration. In contrast, LDO regulator uses configuration with a common source. Both these basic configurations are depicted in the Fig. 2.4. The orientation of a power transistor has a general influence on both working mode and stability of the linear regulator.

Figure 2.4.: Topologies of linear regulators

One of the main drawbacks of the conventional linear regulator is that the gate voltage of power transistor must be at least by  $V_{gssat}$  greater than the output voltage. This is not a problem in itself, but in addition to the ever decreasing supply voltage, this leads to the fact that the supply voltage gets below a possible level of gate voltage. However, this leads to a fact that such a circuit is difficult to use in low voltage applications. In order to use such a regulator for low voltage applications, it is necessary to use a charge pump and this way we can reach required gate voltage level at the gate of a power transistor.

An LDO regulator does not need a charge pump because the power element is in the configuration called common source. Saturation voltage  $V_{ds}$  of such a transistor creates a limit in which a regulator can work. This drop of voltage, or also  $V_{dsat}$ , depends on the maximum output current of the regulator and also on parameters of the power transistor.

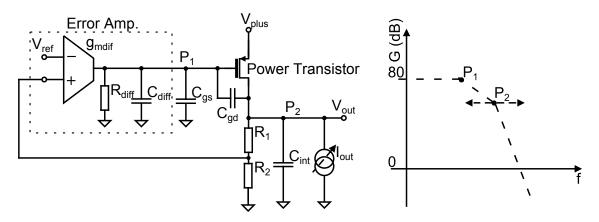

As has been mentioned earlier, the orientation of the power transistor has an influence on the stability of the regulator. Fig. 2.5 depicts typical small signal AC responses for both topologies. As it appears from the figure, the conventional linear regulator is stable thanks to its small output impedance. First pole,  $P_1$ , which is dominant, is created by the output impedance of an error amplifier and input parasitic capacitance of the power transistor. Second pole,  $P_2$ , which is output pole, moves with loading impedance. The position of this pole is on much higher frequencies in comparison to the first pole.

LDO regulator can work in low voltage applications without having to use a charge pump but its disadvantage is that it can become unstable during a change of load. Big loading capacitance together with large output impedance create dominant pole  $P_1$ . However, pole  $P_2$  from an error amplifier is much nearer to the pole  $P_1$  and this can lead to instability of such a system. In order to use this regulator, it is necessary to use internal or external compensation, which ensures the stability of the circuit.

Figure 2.5.: Magnitude characteristics with shown poles for both topologies without compensation circuits [55]

## 2.2.1. LDO regulators

The voltage regulator of the LDO type creates a small family of elements which belong to power management. Its main usage is for supplying blocks where low noise and high accuracy of voltage are necessary. As it is apparent from its name the task of LDO regulator is quite simple - output voltage regulation to keep the output voltage constant, independent of change in load or change of battery voltage. In other words, LDO is a voltage source which keeps the output voltage constant even in the case that battery voltage fluctuates or supply-demand is changing [40].

This regulation of output voltage is the most necessary during fast changes in load current which change depending on the working modes of each particular block. At all portable devices, we try to reduce their consumption and so to prolong their endurance. For this reason, the circuits which are not actually needed are cut off and it decreases the total energy consumption. These kinds of circuits are used for a large group of circuits not only because of low voltage drop but also for its low noise, low price and low internal consumption. As has already been said, linear regulators suffer from low efficiency. The efficiency of such a regulator is inversely proportional to the voltage drop on power transistor ( $V_{plus} - V_{out}$ ). From this reason, in some PMU the LDO regulator is used as a post-regulation element.

#### **Properties of transient responses**