### **Czech Technical University in Prague Faculty of Electrical Engineering**

# **Doctoral Thesis**

August 2018

Ing. Vlastimil Kotě

Czech Technical University in Prague Faculty of Electrical Engineering Department of Microelectronics

# DESIGN OF TRUE RANDOM NUMBER GENERATORS SUITABLE FOR INTEGRATED CIRCUITS

**Doctoral Thesis**

Ing. Vlastimil Kotě

Prague, August 2018

Ph.D. Programme: P 2612 Electrical Engineering and Information Technology Branch of study: 2612V015 Electronics Supervisor: doc. Ing. Jiří Jakovenko, Ph.D.

### Declaration

I declare I have completed my doctoral thesis on my own with the contribution of my supervisor and consultants. I used only materials (literature, projects, articles) specified in the attached list.

I agree with the use of the information presented in my doctoral thesis pursuant to Copyright Act 121/2000 Coll., Sec. 60.

In Prague, August the 31st, 2018

.....

Vlastimil Kotě

### Acknowledgements

I would like to thank my supervisor doc. Ing. Jiří Jakovenko, Ph.D. for the professional guidance, valuable comments and especially for willingness and patience in consultation. I would also like to thank my colleagues from CTU in Prague and company STMicroelectronics for their patience and valuable expertise they have provided me. Special thanks to Ing. Patrik Vacula, Ing. Vladimír Molata, and Ing. Adam Kubačák for their ideas, consultations, and great cooperation. And last but not least, I would like to thank my wife Michaela, my daughter Anastázie, my son Vlastimil, and the whole family for their over-all sustained support during the time of my work.

### Abstract

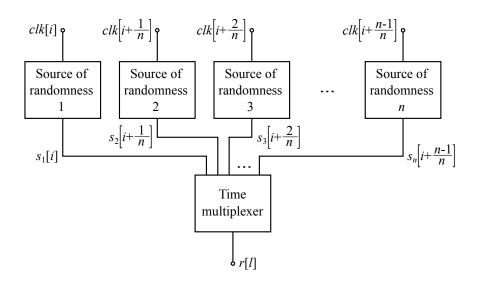

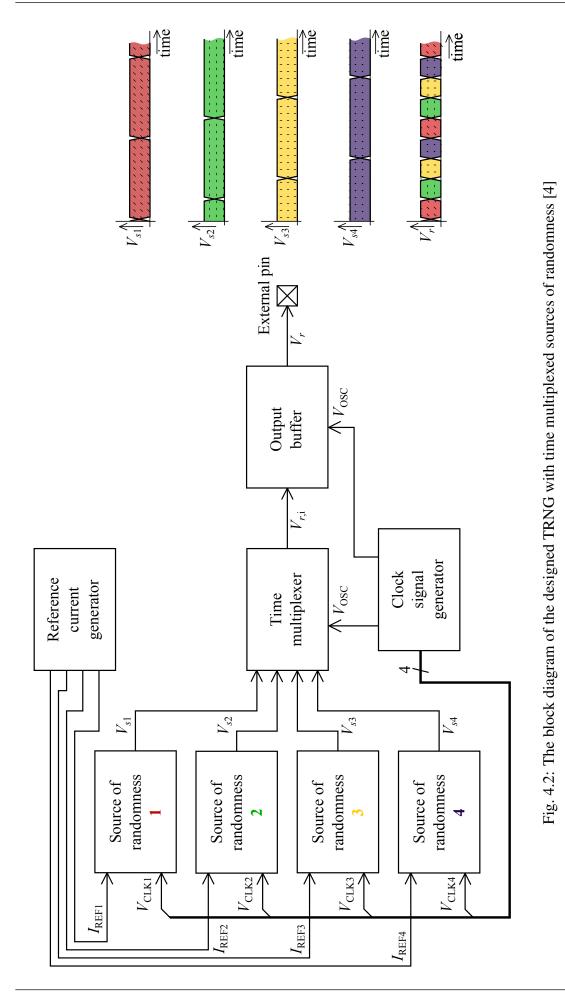

This doctoral thesis deals with the design of true random number generators (TRNGs) suitable for integrated circuits (ICs). These devices exploit randomness of physical phenomena, in this case, noises in semiconductors structures. The first proposal is a TRNG with time multiplexed metastability-based sources of randomness using the principle of pipelining. Digitized random signals coming from sources of randomness are interleaved in a time multiplexer, which allows increasing output data rate. This TRNG has been fabricated in a 130 nm HCMOS9GP bulk CMOS technology from STMicroelectronics, occupies an area of 0.029 mm<sup>2</sup>, and can operate in changing environmental conditions. Random bit sequences can be generated up to the data rate of 20 Mb/s without any corrective mechanisms while its power consumption is 72.48  $\mu$ W at temperature of 25 °C.

Another proposal is enhanced generic architecture of TRNGs, which can detect attempts of attackers trying to manipulate with properties of random number sequences. Protective mechanisms detecting sudden changes in sequence properties are based on features of the von Neumann corrector and an approximately entropy estimation. A presented reconfigurable noise source can produce random sequences in two settings between which is switched when entropy decreases. These circuits have been designed in a 130 nm HCMOS9A bulk CMOS technology also from STMicroelectronics.

Simulations of the presented TRNGs are very time-consuming. Therefore, for verification of systems containing these generators, their behavioral models have been created in the Verilog-A HDL. They approximate properties of the TRNGs and are able to shorten duration of the simulations to allow revealing possible errors of systems.

The developed TRNGs are analog and mixed-signal (AMS) circuits containing very sensitive parts. Their precise handmade physical design is very time-consuming. Hence new methodology steps of the physical design have been proposed. Introduced functions can automatically sort electrical devices according to their topological, structural and electrical properties, control layout objects without filling forms, or search an IC design database based on similarity of object properties. They speed up the physical design, help to prevent errors and make the design more robust.

**Keywords:** True random number generator, integrated circuit, source of randomness, behavioral model, physical design of analog and mixed-signal circuits.

### Abstrakt

Tato doktorská práce se zabývá návrhem generátorů pravých náhodných čísel (TRNG) vhodných pro integrované obvody (IC). Tato zařízení využívají náhodnost fyzikálních jevů, v tomto případě šumů v polovodičových strukturách. Prvním návrhem je TRNG s časově multiplexovanými metastabilními zdroji náhodnosti využívající tzv. princip řetězení. Digitalizované náhodné signály produkované zdrojem náhodnosti jsou prokládány v časovém multiplexoru, který umožňuje zvýšení výstupní datové rychlosti. Tento TRNG byl vyroben ve 130nm CMOS technologii nazvané HCMOS9GP od společnosti STMicroelectronics na ploše 0,029 mm<sup>2</sup> a je schopen pracovat v proměnných podmínkách. Sekvence náhodných bitů mohou být generovány až do datové rychlosti 20 Mb/s bez použití opravných mechanizmů při výkonové spotřebě 72,48 μW a teplotě 25 °C.

Dalším návrhem je rozšířená obecná architektura TRNG, jenž je schopná detekovat pokusy útočníků snažících se manipulovat s vlastnostmi sekvencí náhodných čísel. Ochranné mechanismy detekující náhlé změny vlastností těchto sekvencí jsou založeny na charakteristikách von Neumannova korektoru a na přibližném odhadu entropie. Uvedený rekonfigurovatelný zdroj šumu je schopen produkovat náhodné sekvence ve dvou nastaveních, mezi nimiž je přepínán při poklesu entropie. Tyto obvody byly navrženy ve 130nm CMOS technologii nazvané HCMOS9A od společnosti STMicroelectronics.

Simulace prezentovaných TRNG jsou velmi časově náročné. Proto pro verifikace systémů obsahujících tyto generátory byly vytvořeny v jazyce Verilog-A HDL jejich behaviorální modely. Napodobují vlastnosti TRNG a jsou schopné zkrátit dobu trvání simulací, aby bylo možné odhalit případné chyby systému.

Vyvinuté TRNG jsou analogové a smíšené (AMS) obvody obsahující velmi citlivé části. Jejich precizní ručně vytvářený fyzický návrh je velmi časově náročný. Proto byly navrženy nové metodologické kroky fyzického návrhu. Zavedené funkce umí automaticky třídit elektronické součástky podle jejich topologických, strukturních a elektrických vlastností, ovládat databázové objekty bez vyplňování formulářů nebo prohledávat databáze na základě podobnosti databázových objektů. Tyto funkce zrychlují fyzický návrh, pomáhají předcházet chybám a dělat design robustnější.

**Klíčová slova:** Generátor pravých náhodných čísel, integrovaný obvod, zdroj náhodnosti, behaviorální model, fyzický návrh analogových a smíšených obvodů.

### Contents

| Li | ist of Acronyms X |               |                                                          |      | V |

|----|-------------------|---------------|----------------------------------------------------------|------|---|

| Li | st of S           | Symbols       | 5                                                        | XVI  | I |

| Li | st of l           | Figures       |                                                          | XX   | I |

| Li | st of [           | <b>Fables</b> |                                                          | XXV  | V |

| 1  | Intr              | oductio       | n                                                        | -    | 1 |

|    | 1.1               | Organ         | ization of This Thesis                                   | •    | 3 |

|    | 1.2               | Autho         | r's Scientific Contributions                             | •    | 3 |

|    | 1.3               | State of      | of the Art                                               |      | 5 |

|    | 1.4               | Solutio       | on Methods of the Work                                   | . 12 | 2 |

| 2  | TRN               | NG Fun        | damentals                                                | 1    | 5 |

|    | 2.1               | Gener         | ic Architecture                                          | . 10 | 6 |

|    |                   | 2.1.1         | Noise Source                                             | . 1′ | 7 |

|    |                   | 2.1.2         | Digitizer                                                | . 1′ | 7 |

|    |                   | 2.1.3         | Post-processing Block                                    | . 19 | 9 |

|    |                   | 2.1.4         | Output Interface                                         | . 25 | 5 |

|    | 2.2               | TRNG          | s with Direct Noise Amplification                        | . 25 | 5 |

|    |                   | 2.2.1         | Source of Randomness Based on Thermal Noise of Resistors | . 20 | 6 |

|    |                   | 2.2.2         | Direct Amplification of Noise in Semiconductor Junction  | . 2  | 7 |

|    | 2.3               | TRNG          | Based on Ring Oscillators                                | . 29 | 9 |

|    | 2.4               | Metas         | tability-Based TRNG                                      | . 3  | 1 |

|   | 2.5  | TRNG     | Based on Chaos                              | 34 |

|---|------|----------|---------------------------------------------|----|

|   | 2.6  | Noises   | Occurring in Electronic Circuits            | 37 |

|   |      | 2.6.1    | Thermal Noise                               | 38 |

|   |      | 2.6.2    | Flicker Noise                               | 39 |

|   |      | 2.6.3    | Shot Noise                                  | 40 |

|   |      | 2.6.4    | Generation-Recombination Noise              | 41 |

|   |      | 2.6.5    | Random Telegraph Signal Noise               | 41 |

|   |      | 2.6.6    | Avalanche Noise                             | 42 |

| 3 | Eval | uation o | of Random Number Sequences                  | 43 |

|   | 3.1  | NIST 7   | Test Suite                                  | 44 |

|   |      | 3.1.1    | Monobit Test                                | 45 |

|   |      | 3.1.2    | Frequency Test within a Block               | 46 |

|   |      | 3.1.3    | Runs Test                                   | 46 |

|   |      | 3.1.4    | Test for the Longest Run of Ones in a Block | 46 |

|   |      | 3.1.5    | Binary Matrix Rank Test                     | 46 |

|   |      | 3.1.6    | Discrete Fourier Transform Test             | 47 |

|   |      | 3.1.7    | Non-overlapping Template Matching Test      | 47 |

|   |      | 3.1.8    | Overlapping Template Matching Test          | 47 |

|   |      | 3.1.9    | Maurer's "Universal Statistical" Test       | 47 |

|   |      | 3.1.10   | Linear Complexity Test                      | 48 |

|   |      | 3.1.11   | Serial Test                                 | 48 |

|   |      | 3.1.12   | Approximate Entropy Test                    | 48 |

|   |      | 3.1.13   | Cumulative Sums Test                        | 48 |

|   |      | 3.1.14   | Random Excursions Test                      | 49 |

|   |      | 3.1.15   | Random Excursions Variant Test              | 49 |

|   | 3.2  | FIPS T   | est Suite                                   | 49 |

|   |      | 3.2.1    | Monobit Test                                | 50 |

|   |      | 3.2.2    | Poker Test                                  | 50 |

|   |      | 3.2.3    | Runs Test                                   | 50 |

|   |      | 3.2.4    | Long Runs Test                              | 51 |

|   | 3.3  | Shanno   | on Entropy                                  | 51 |

| 4 | TRN  | NG with  | Time Multiplexed Sources of Randomness          | 53  |

|---|------|----------|-------------------------------------------------|-----|

|   | 4.1  | Princip  | ple of Time Multiplexed TRNG                    | 54  |

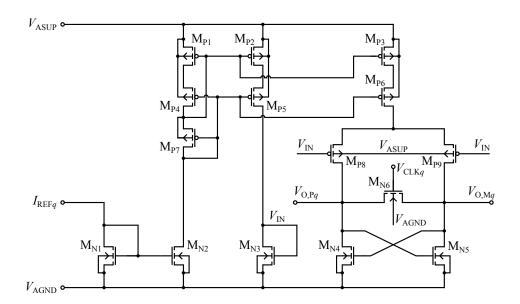

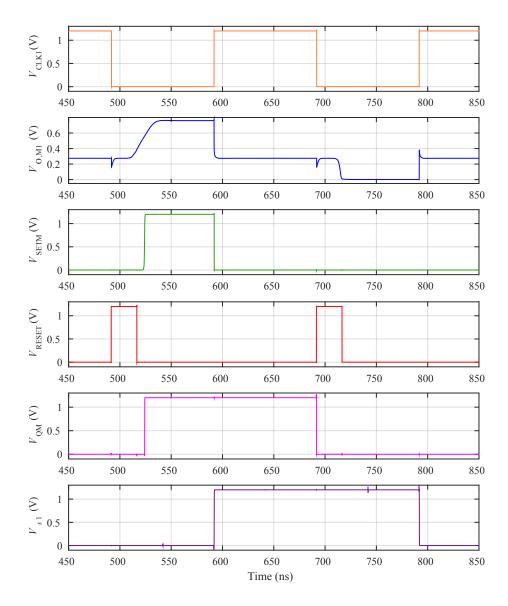

|   | 4.2  | Circuit  | t Implementation                                | 56  |

|   |      | 4.2.1    | Noise source                                    | 58  |

|   |      | 4.2.2    | Digitizer                                       | 72  |

|   |      | 4.2.3    | Time Multiplexer                                | 73  |

|   | 4.3  | Measu    | rement Results                                  | 77  |

|   |      | 4.3.1    | Arrangement of Measuring Instruments            | 77  |

|   |      | 4.3.2    | Evaluation of Generated Random Number Sequences | 78  |

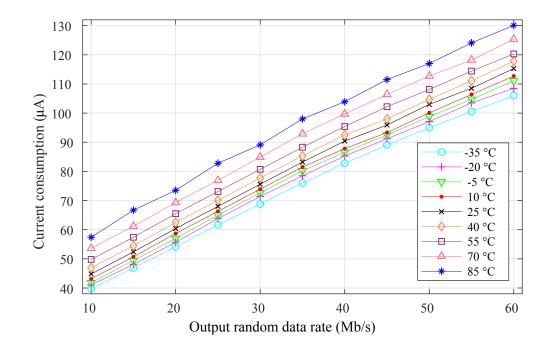

|   |      | 4.3.3    | Current Consumption                             | 84  |

|   |      | 4.3.4    | Required Energy per Random Bit                  | 85  |

|   | 4.4  | Compa    | arison                                          | 87  |

| 5 | Prot | ective N | Mechanisms for TRNGs                            | 89  |

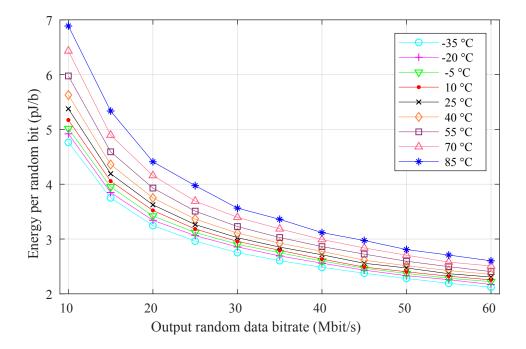

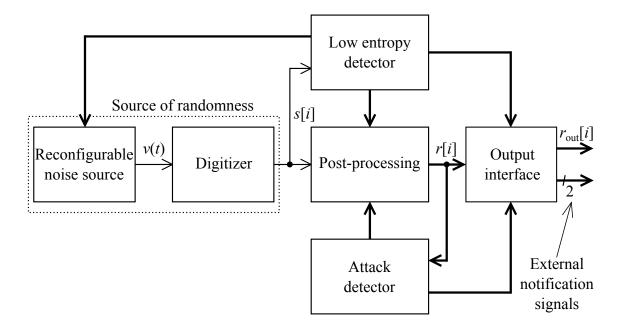

|   | 5.1  | Enhan    | ced Generic Architecture                        | 90  |

|   | 5.2  | Protec   | tive Mechanisms                                 | 92  |

|   |      | 5.2.1    | Attack Detector                                 | 92  |

|   |      | 5.2.2    | Low Entropy Detector                            | 96  |

|   | 5.3  | Recon    | figurable Source of Randomness                  | 99  |

|   |      | 5.3.1    | Reconfigurable Noise Source                     | 100 |

|   |      | 5.3.2    | Differential Digitizer                          | 105 |

|   |      | 5.3.3    | Power Supply                                    | 108 |

|   | 5.4  | Achiev   | ved Results                                     | 109 |

|   | 5.5  | Future   | Work on Development of TRNGs                    | 112 |

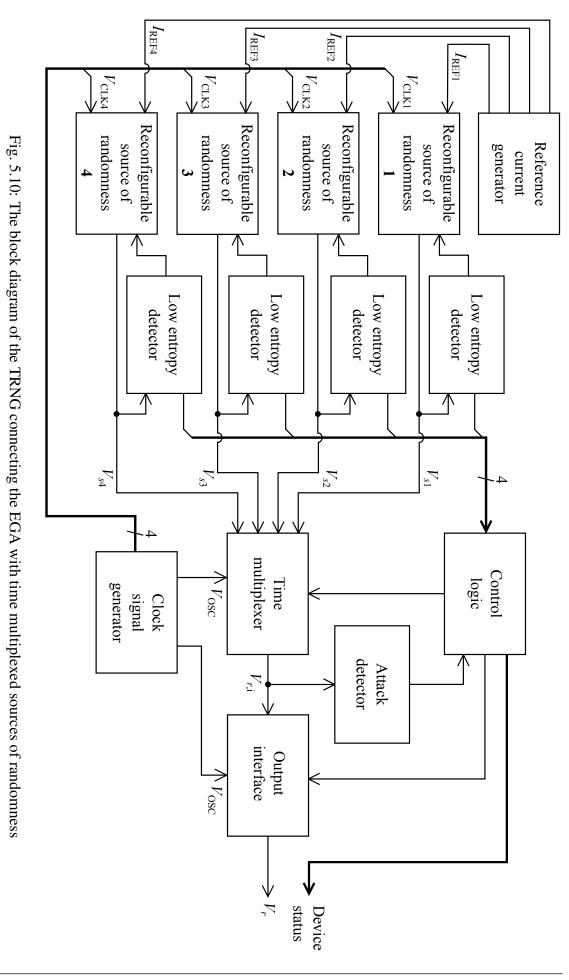

|   |      | 5.5.1    | EGA with Time Multiplexed Sources of Randomness | 113 |

|   |      | 5.5.2    | Noise source with Automatic Zeroing             | 113 |

| 6 | Beh  | avioral  | Models of TRNGs                                 | 117 |

|   | 6.1  | Behav    | ioral Model of TRNG with Time Multiplexer       | 118 |

|   |      | 6.1.1    | Description of Model                            | 119 |

|   |      | 6.1.2    | Properties of Model                             | 122 |

|   | 6.2  | Behav    | ioral Model of EGA                              | 124 |

|   |      | 6.2.1    | Structure of Model                              | 124 |

|    |         | 6.2.2          | Evaluation of Model                          | 126 |

|----|---------|----------------|----------------------------------------------|-----|

| 7  | New     | metho          | dology steps of physical design of AMS ICs   | 129 |

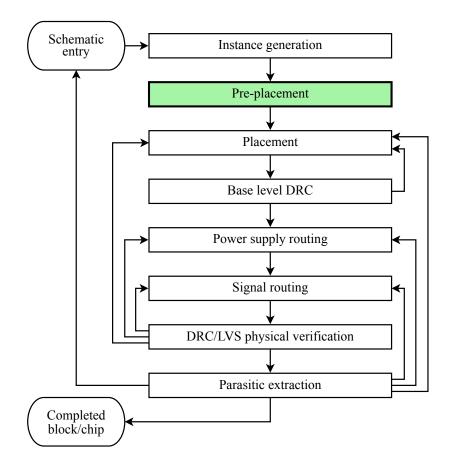

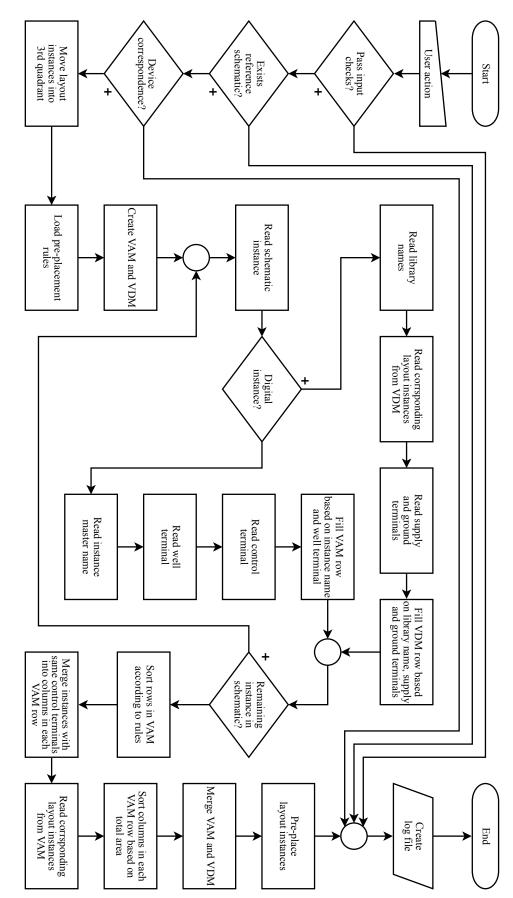

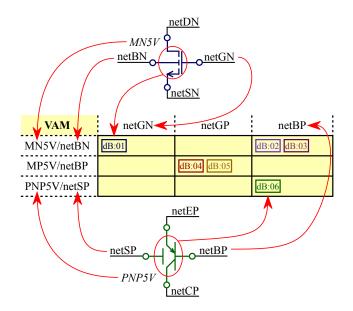

|    | 7.1     | Autom          | nated Pre-placement Phase                    | 130 |

|    |         | 7.1.1          | Definition of Rules                          | 131 |

|    |         | 7.1.2          | Algorithm Implementation                     | 137 |

|    |         | 7.1.3          | Productivity Improvement                     | 141 |

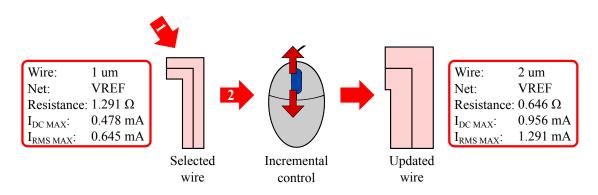

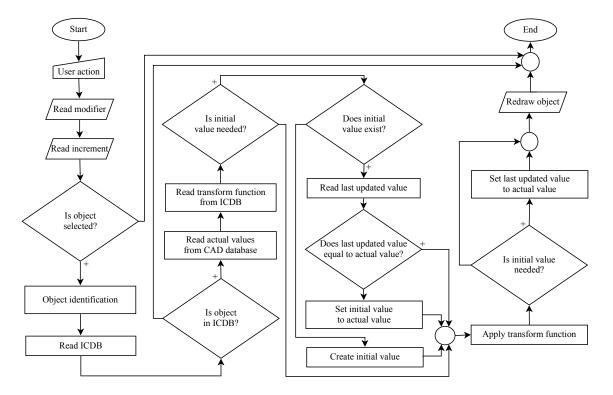

|    | 7.2     | Increm         | nental Control of Layout Objects             | 145 |

|    |         | 7.2.1          | Implementation in CAD Environment            | 146 |

|    |         | 7.2.2          | Productivity Gain                            | 147 |

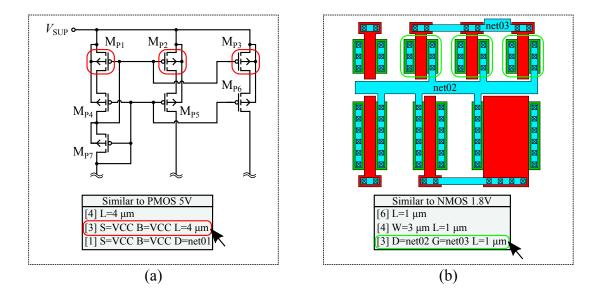

|    | 7.3     | Search         | for Objects based on Their Similarities      | 148 |

|    | 7.4     | Classif        | fication of Matched Structures               | 150 |

|    | 7.5     | Future         | Work on Physical Design Methodology          | 150 |

| 8  | Con     | clusions       | 8                                            | 151 |

| Re | eferen  | ces            |                                              | 155 |

| Aŗ | pend    | ix             |                                              | i   |

| Li | st of A | Author's       | s Publications                               | iii |

|    | A.1     | Public         | ations Related to the Topic of This Work     | iii |

|    |         | A.1.1          | Publications in Impacted Journals            | iii |

|    |         | A.1.2          | Publications in Reviewed Journals            | iii |

|    |         | A.1.3          | Publications Excerpted by WoS                | iv  |

|    |         | A.1.4          | Other Publications                           | iv  |

|    |         | A.1.5          | Functional Samples                           | v   |

|    | A.2     | Public         | ations Not Related to the Topic of This Work | v   |

|    |         | A.2.1          | Patents                                      | v   |

|    |         | A.2.2          | Publications Excerpted by Scopus             | vi  |

|    |         |                |                                              |     |

|    |         | A.2.3          | Other Publications                           | vi  |

|    |         | A.2.3<br>A.2.4 | Other Publications                           | vi  |

## List of Acronyms

| AMS    | Analog and Mixed-Signal                  |

|--------|------------------------------------------|

| ApEn   | Approximate Entropy                      |

| ASIC   | Application Specific Integrated Circuit  |

| BCD    | Bipolar-CMOS-Double Diffused MOS         |

| BJT    | Bipolar Junction Transistor              |

| CAD    | Computer-Aided Design                    |

| CMOS   | Complementary Metal-Oxide-Semiconductor  |

| DC     | Direct Current                           |

| DRC    | Design Rule Check                        |

| DRM    | Design Rule Manual                       |

| EGA    | Enhanced Generic Architecture            |

| ESD    | Electrostatic Discharge                  |

| FIB    | Focused Ion Beam                         |

| FinFET | Fin Field Effect Transistor              |

| FIPS   | Federal Information Processing Standards |

| FPGA   | Field Programmable Gate Array            |

| FPPM   | Final Pre-Placement Matrix               |

| GR     | Generation-recombination                 |

| HDL    | Hardware Description Language            |

| IC     | Integrated Circuit                                      |

|--------|---------------------------------------------------------|

| ICDB   | Incremental Control Database                            |

| ІоТ    | Internet of Things                                      |

| LDO    | Low Dropout Voltage Regulator                           |

| LFSR   | Linear Feedback Shift Register                          |

| LVS    | Layout Versus Schematic                                 |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor       |

| NBTI   | Negative Bias Temperature Instability                   |

| NIST   | National Institute of Standards and Technologies        |

| PBTI   | Positive Bias Temperature Instability                   |

| PC     | Personal Computer                                       |

| PDF    | Probability Density Function                            |

| PRNG   | Pseudo-Random Number Generator                          |

| PSD    | Power Spectral Density                                  |

| RMS    | Root Mean Square                                        |

| RNG    | Random Number Generator                                 |

| RO     | Ring Oscillator                                         |

| RTS    | Random Telegraph Signal                                 |

| SCR    | Silicon Controlled Rectifier                            |

| SoC    | System on Chip                                          |

| SOI    | Silicon On Insulator                                    |

| TRNG   | True Random Number Generator                            |

| VAM    | Virtual Analog Matrix                                   |

| VCO    | Voltage Controlled Oscillator                           |

| VDM    | Virtual Digital Matrix                                  |

| VHDL   | Very-High-Speed Integrated Circuit Hardware Description |

| XOR    | Exclusive Or                                            |

|        |                                                         |

Language

## List of Symbols

| <i>a</i> <sub>a</sub> | Offensive signal (V)                                                        |

|-----------------------|-----------------------------------------------------------------------------|

| b                     | Bias of random number generation (-)                                        |

| е                     | Coefficient of resilient function (-)                                       |

| d                     | Binary derivative (b)                                                       |

| $d_{ m A,B}$          | Relative difference between $t_A$ and $t_B$ (%)                             |

| f                     | Frequency (Hz)                                                              |

| g                     | Random number sub-sequence (V)                                              |

| $g_{ m ds}$           | Output conductance of the MOSFET small signal model (S)                     |

| $g_m$                 | Transconductance (AV <sup>-1</sup> )                                        |

| h                     | Coordinate of resilient function (-)                                        |

| i                     | Normalized period (-)                                                       |

| j                     | Order of ring oscillator (-)                                                |

| $k_{ m B}$            | Boltzmann constant (1.38064852 $\cdot$ 10 <sup>-23</sup> JK <sup>-1</sup> ) |

| l                     | Normalized period (-)                                                       |

| т                     | Length of bit sequence (b)                                                  |

| n                     | Number of source of randomness (-)                                          |

| 0                     | Occurrences                                                                 |

| р                     | Probability                                                                 |

| q                     | Identifier of source of randomness (-)                                      |

| $q_e$                   | Elementary charge ( $q = 1.60217662 \cdot 10^{-19} \text{ C}$ )                  |

|-------------------------|----------------------------------------------------------------------------------|

| r                       | Internal random numbers (V)                                                      |

| r <sub>ds</sub>         | Output resistance of the MOSFET small signal model ( $\Omega$ )                  |

| <i>r</i> <sub>out</sub> | External random numbers (V)                                                      |

| S                       | Digitized noise signal (V)                                                       |

| t                       | Time (s)                                                                         |

| x <sub>t</sub>          | Sample test statistic value                                                      |

| Z.                      | Constant of resilient function (-)                                               |

| Z <sub>t</sub>          | Test statistic                                                                   |

| Α                       | Amplification (-)                                                                |

| В                       | Random data rate (bit/s)                                                         |

| С                       | Capacitance (F)                                                                  |

| Ε                       | Energy (J)                                                                       |

| F                       | Resilient function                                                               |

| G                       | Conductance (S)                                                                  |

| Н                       | Entropy (b)                                                                      |

| Ι                       | Current (A)                                                                      |

| $K_{\mathrm{f}}$        | Coefficient of flicker noise for MOSFETs ( $C^2/m^2$ )                           |

| $K_{\mathrm{f},R}$      | Material-dependent coefficient of flicker noise for resistors (Sm <sup>2</sup> ) |

| K <sub>rts</sub>        | Coefficient of random telegraph signal noise (-)                                 |

| L                       | Length (m)                                                                       |

| M                       | Input parameter of the NIST test suite (b)                                       |

| Ν                       | Quantity (-)                                                                     |

| 0                       | Order of binary derivative (-)                                                   |

| Р                       | Power (W)                                                                        |

| Q                       | Input parameter of the NIST test suite (b)                                       |

| R                       | Resistance ( $\Omega$ )                                                          |

|                         |                                                                                  |

| S            | Spectral density (W/Hz)                               |

|--------------|-------------------------------------------------------|

| Т            | Temperature (K)                                       |

| V            | Voltage (V)                                           |

| W            | Width (m)                                             |

| X            | Random bit                                            |

| Y            | Random bit                                            |

| Ζ            | Random bit                                            |

| α            | Significance level (-)                                |

| γ            | Technology dependent coefficient of thermal noise (-) |

| ζ            | Skew tent map coefficient (-)                         |

| η            | Coefficient of flicker noise (-)                      |

| ι            | Number of bits (-)                                    |

| К            | Constant of metastable circuit (-)                    |

| $\mu$        | Mean value                                            |

| $\mu_{ m m}$ | Mobility $(m^2 V^{-1} s^{-1})$                        |

| ν            | Analog noise signal (V)                               |

| ξ            | Number of logic gates (-)                             |

| ρ            | Relative ratio (-)                                    |

| $\sigma^2$   | Variance                                              |

| τ            | Delay (s)                                             |

| υ            | Base of logarithm (-)                                 |

| Θ            | Period (s)                                            |

| Ψ            | Periodic square waveform signal (V)                   |

## List of Figures

| 2.1  | The generic architecture of a TRNG [97]                                     | 16 |

|------|-----------------------------------------------------------------------------|----|

| 2.2  | The digitization model with the clocked comparator                          | 18 |

| 2.3  | The digitization model composed of digital circuits                         | 18 |

| 2.4  | The block diagram of the TRNG exploiting thermal noise of resistors [15]    | 26 |

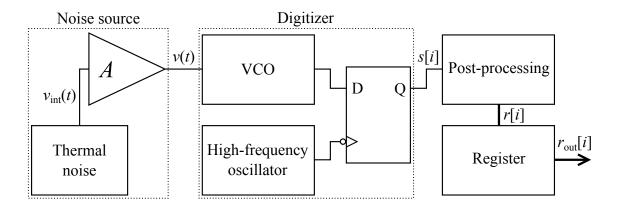

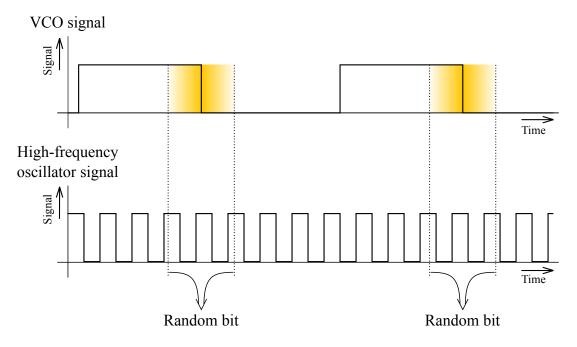

| 2.5  | The principle of VCO controlled sampling [15]                               | 27 |

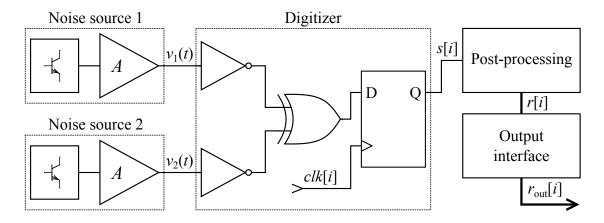

| 2.6  | The block diagram of the TRNG with two independent noise sources [25]       | 28 |

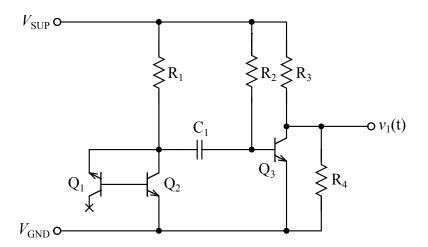

| 2.7  | The noise source based on noise occurring in the reverse polarized P-N      |    |

|      | junction [25]                                                               | 28 |

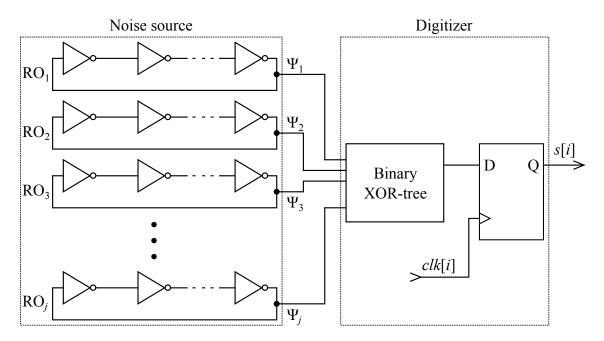

| 2.8  | The source of randomness based on a architecture with ring oscillators [27] | 29 |

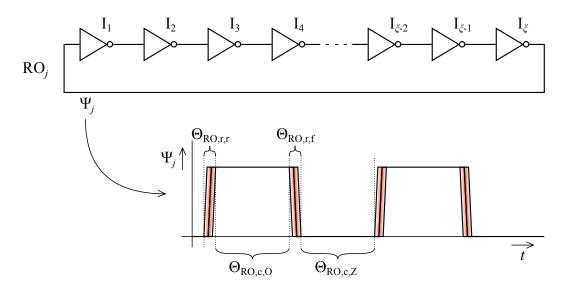

| 2.9  | The RO output signal $\Psi_j(t)$ with the jitter displayed                  | 30 |

| 2.10 | The mechanical analogy of metastable systems                                | 32 |

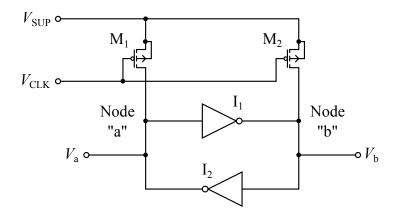

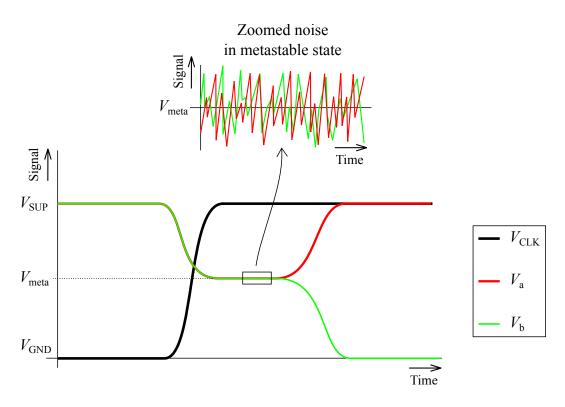

| 2.11 | Waveforms of signals in the metastability based noise source [41]           | 33 |

| 2.12 | The noise source exhibiting the metastable behavior [98]                    | 34 |

| 2.13 | The source of randomness based on the discrete time non-linear dynami-      |    |

|      | cal system [58]                                                             | 35 |

| 2.14 | The noise source as the CMOS compatible current mode circuit published      |    |

|      | in [58]                                                                     | 36 |

| 2.15 | The transient simulation of the noise source published in [58]              | 37 |

| 2.16 | The phase portrait plot of the noise source published in [58]               | 37 |

| 4.1  | Principle illustration of the proposed TRNG [4]                             | 55 |

| 4.2  | The block diagram of the designed TRNG with time multiplexed sources        |    |

|      | of randomness [4]                                                           | 57 |

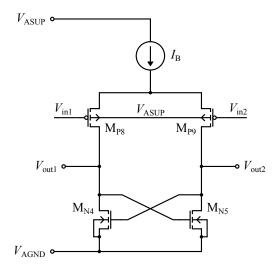

| 4.3  | The schematic diagram of the metastability-based noise source [4]                                               | 58 |

|------|-----------------------------------------------------------------------------------------------------------------|----|

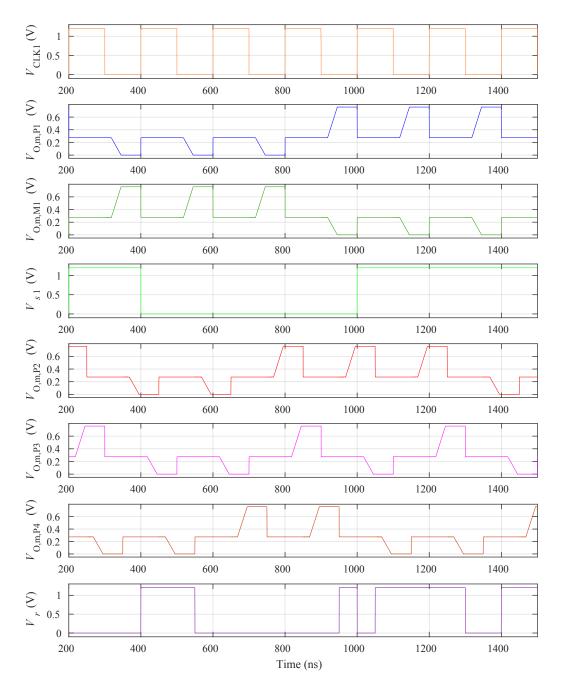

| 4.4  | Waveforms of signals inside the designed TRNG simulated by the Mentor                                           |    |

|      | Eldo simulator at the transistor level [4]                                                                      | 59 |

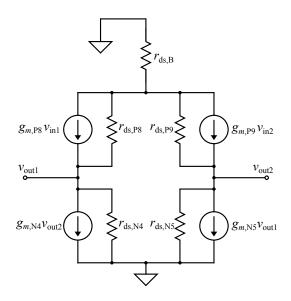

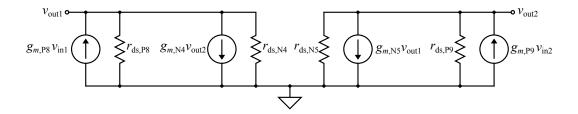

| 4.5  | The schematic diagram of the proposed metastable element used for offset                                        |    |

|      | analysis                                                                                                        | 60 |

| 4.6  | The small signal model of the metastable element                                                                | 61 |

| 4.7  | The simplified small signal model of the metastable element used for gain                                       |    |

|      | calculation                                                                                                     | 61 |

| 4.8  | The schematic diagram of the designed digitizer [4]                                                             | 72 |

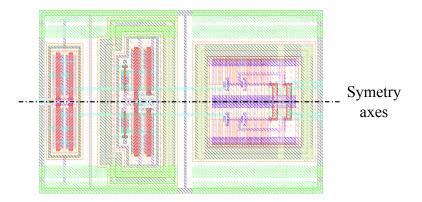

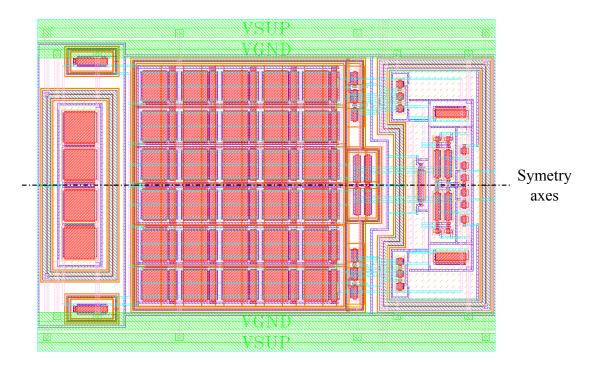

| 4.9  | The layout of the metastable element connected to input parts of the digi-                                      |    |

|      | tizers with a drawn symmetry axis                                                                               | 73 |

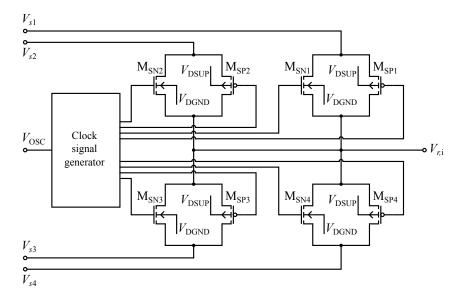

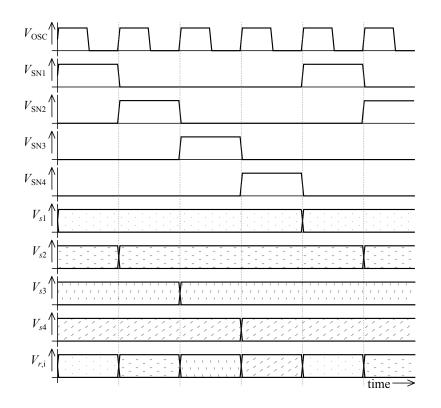

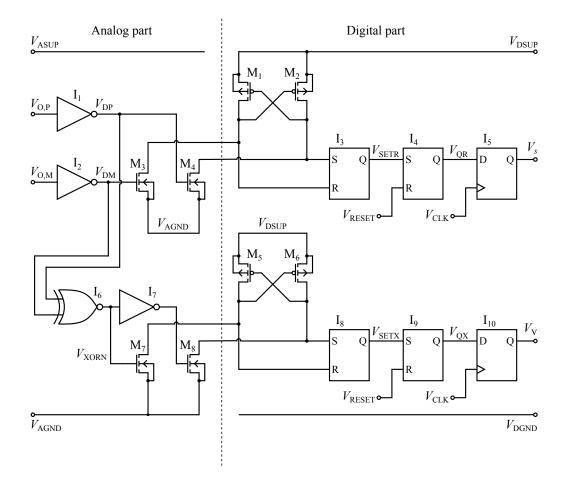

| 4.10 | The schematic diagram of the time multiplexer [4]                                                               | 74 |

| 4.11 | Waveforms illustrating the function of the time multiplexer [4]                                                 | 74 |

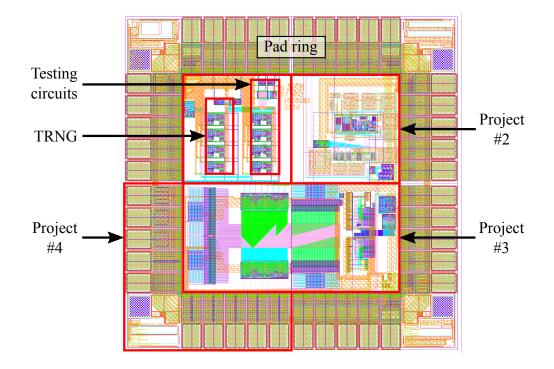

| 4.12 | The layout of the multi-project test chip without displayed tiles for better                                    |    |

|      | layer planarization                                                                                             | 75 |

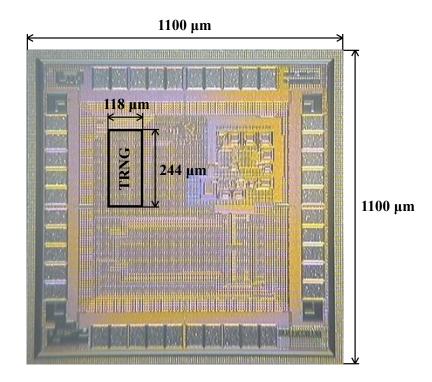

| 4.13 | Photo of the fabricated die. The proposed TRNG containing all described                                         |    |

|      | parts – the noise sources, the digitizer, the time multiplexer, and the output                                  |    |

|      | buffer – occupies the marked area [4]                                                                           | 76 |

| 4.14 | One of the smallest emblems of the Czech Technical University in Prague                                         |    |

|      | with the width of $59.55\mu m$ and the heigth of $44.85\mu m$ is present on the                                 |    |

|      | fabricated chip                                                                                                 | 76 |

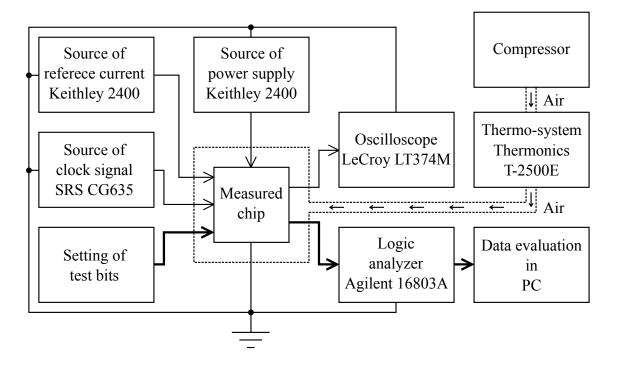

| 4.15 | Diagram of the measuring instrument arrangement                                                                 | 77 |

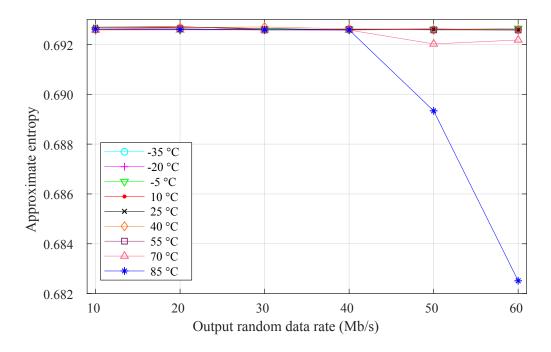

| 4.16 | The approximate entropy of output random number sequences generated                                             |    |

|      | in the temperature range of $-35 ^{\circ}$ C to $85 ^{\circ}$ C [4]                                             | 84 |

| 4.17 | The current consumption of the designed circuit measured in the temper-                                         |    |

|      | ature range of $-35 \degree C$ to $85 \degree C$ [4]                                                            | 85 |

| 4.18 | The energy per random bit of the designed TRNG calculated in the tem-                                           |    |

|      | perature range of $-35 ^{\circ}$ C to $85 ^{\circ}$ C $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 87 |

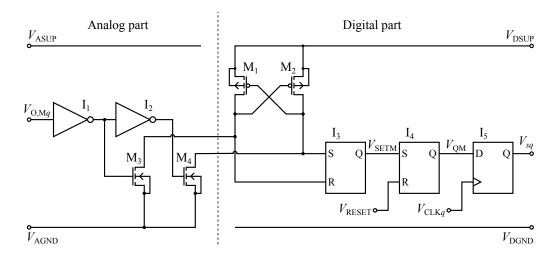

| 5.1  | The block diagram of the proposed EGA                                                                           | 91 |

| 5.2  | The model of the side channel attack aimed at the noise source                                                  | 93 |

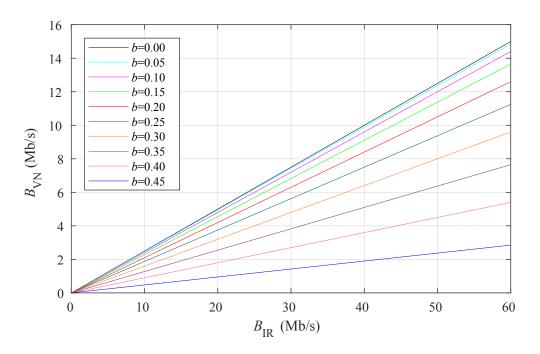

| 5.3  | Relation between $B_{\rm VN}$ and $B_{\rm IR}$ depending on the bias $b$                                        | 94 |

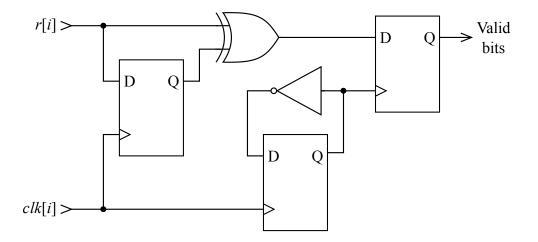

| 5.4  | The principle schematic diagram of the valid bit generator without buffers |     |

|------|----------------------------------------------------------------------------|-----|

|      | for proper timing                                                          | 95  |

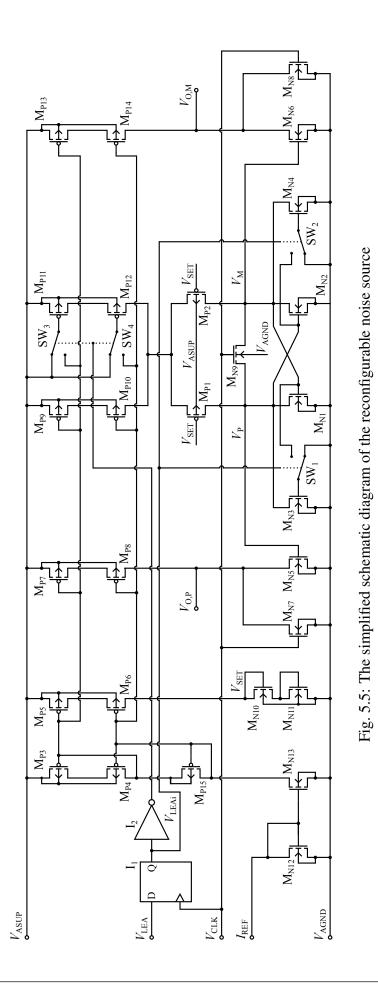

| 5.5  | The simplified schematic diagram of the reconfigurable noise source        | 101 |

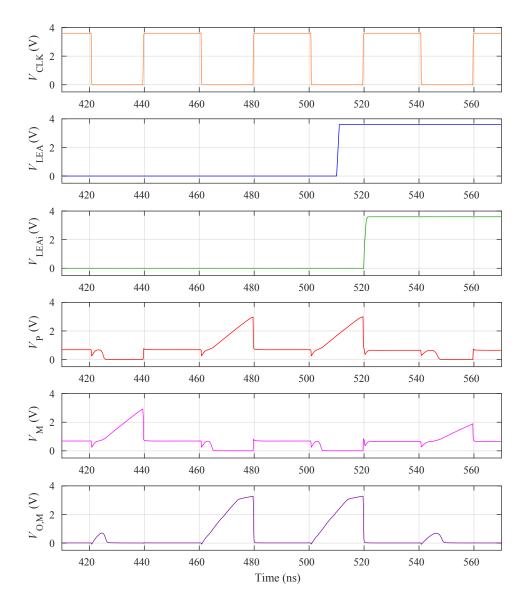

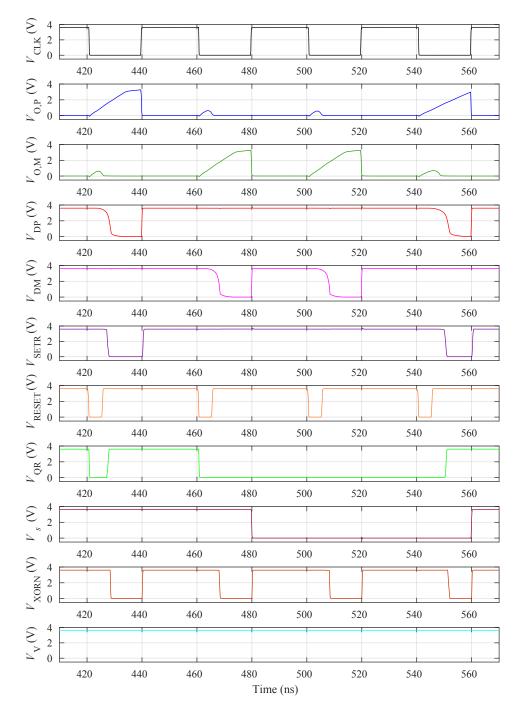

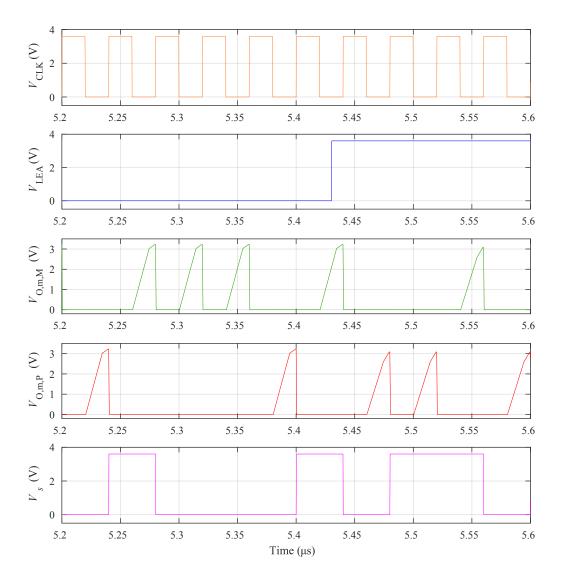

| 5.6  | Waveforms of signals inside the reconfigurable noise source simulated by   |     |

|      | the Mentor Eldo simulator at the transistor level                          | 102 |

| 5.7  | The layout of the reconfigurable noise source with a drawn symmetry axis   | 103 |

| 5.8  | The schematic diagram of the differential digitizer with the check of com- |     |

|      | plementarity                                                               | 106 |

| 5.9  | Waveforms of signals inside the differential digitizer simulated by the    |     |

|      | Mentor Eldo simulator at the transistor level                              | 107 |

| 5.10 | The block diagram of the TRNG connecting the EGA with time multi-          |     |

|      | plexed sources of randomness                                               | 114 |

| 6.1  | Structure of the model of the source of randomness                         | 119 |

| 6.2  | Waveforms of signals generated by the behavioral model of the TRNG         |     |

|      | with time multiplexed sources of randomness simulated by transient anal-   |     |

|      | ysis of the Mentor Eldo simulator                                          | 120 |

| 6.3  | Waveforms of signals generated by the behavioral model of the TRNG         |     |

|      | based on the EGA simulated by the Mentor Eldo simulator                    | 125 |

| 7.1  | Physical design flow enhanced by the pre-placement phase [8]               | 131 |

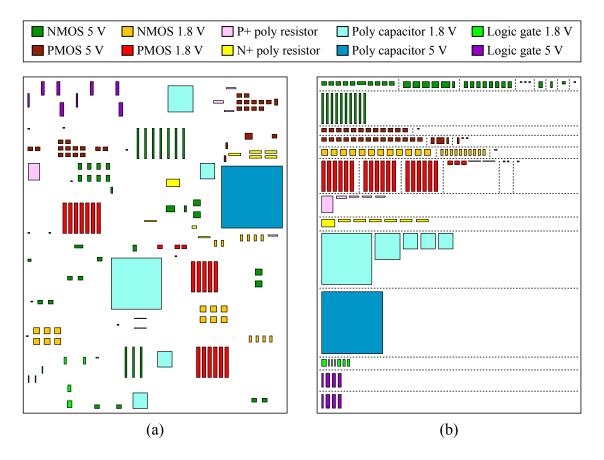

| 7.2  | Symbolic view of layout instances before (a) and after (b) the automated   |     |

|      | pre-placement phase [8]                                                    | 132 |

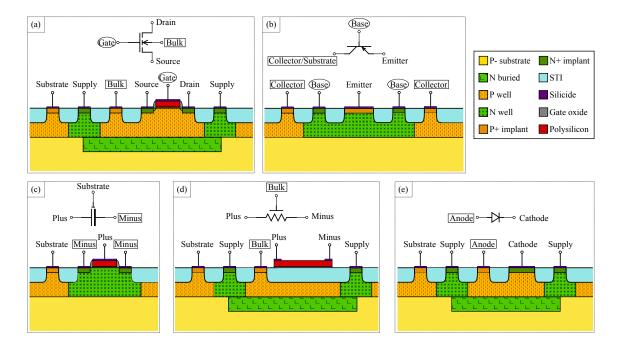

| 7.3  | Cross sections of usually used devices in CMOS and BCD designs: (a)        |     |

|      | Junction insulated N-channel MOSFET. (b) PNP BJT. (c) Polysilicon -        |     |

|      | N-well capacitor. (d) Polysilicon resistor with a junction insulated bulk  |     |

|      | terminal. (e) Junction insulated N+ – P-well diode [8]                     | 133 |

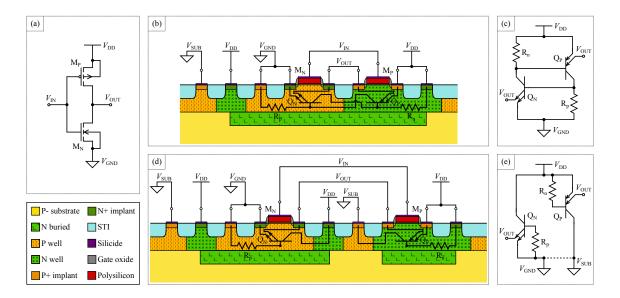

| 7.4  | Parasitic thyristor structures in CMOS or BCD designs: (a) Example of      |     |

|      | a frequently used circuit - an inverter. (b) Cross section with depicted   |     |

|      | parasitic components. (c) Schematic diagram of the parasitic thyristor     |     |

|      | structure. (d) Solution eliminating the parasitic thyristor structure. (e) |     |

|      | Schematic diagram of the parasitic structure without thyristor configura-  |     |

|      | tion [8]                                                                   | 135 |

| 7.5 | The flow chart of the automated pre-placement phase [8]                           |

|-----|-----------------------------------------------------------------------------------|

| 7.6 | VAM filling with outlined way of indexing [8]                                     |

| 7.7 | The process of the wire width modification with the shown status bar 145          |

| 7.8 | The flow chart of the incremental control of layout objects [9] 147               |

| 7.9 | Use of the similar search in the schematic editor (a) and layout editor (b) . 149 |

### List of Tables

| 2.1 | The truth-table of the XOR operation                                                    | 21  |

|-----|-----------------------------------------------------------------------------------------|-----|

| 2.2 | Examples of the mean value calculated using the formula 2.16                            | 22  |

| 2.3 | The table describing the basic function of the von Neumann corrector                    | 23  |

| 3.1 | The required ranges for runs with different lengths of the Runs test                    | 50  |

| 4.1 | Summary of found recommendations for the noise source proposal [4]                      | 70  |

| 4.2 | Results of the FIPS tests (P – Passed; F – Failed) $\ldots \ldots \ldots \ldots \ldots$ | 80  |

| 4.3 | Results of the NIST tests at the output random data rates 10 Mb/s and                   |     |

|     | 20 Mb/s                                                                                 | 81  |

| 4.4 | Results of the NIST tests at the output random data rates 30 Mb/s and                   |     |

|     | 40 Mb/s                                                                                 | 82  |

| 4.5 | Results of the NIST tests at the output random data rates 50 Mb/s and                   |     |

|     | 60 Mb/s                                                                                 | 83  |

| 4.6 | Parameters including required energy per random bit of published TRNGs                  | 86  |

| 5.1 | The 4-bit sub-sequences with the low values of the approximate entropy                  |     |

|     | estimation                                                                              | 98  |

| 5.2 | The 8-bit sub-sequences with the low values of the approximate entropy                  |     |

|     | estimation                                                                              | 99  |

| 5.3 | Dimensions and numbers of elements of MOSFETs used in the reconfig-                     |     |

|     | urable noise source                                                                     | 104 |

| 5.4 | Results of the NIST tests for both settings of the reconfigurable noise    |

|-----|----------------------------------------------------------------------------|

|     | source which have been generated directly (Directly), using the XOR cor-   |

|     | rector (XOR), or using the Von Neumann corrector (VN)                      |

| 5.5 | Results of the FIPS tests for both settings of the reconfigurable noise    |

|     | source which have been generated directly (Directly), using the XOR cor-   |

|     | rector (XOR), or using the Von Neumann corrector (VN)                      |

| 5.6 | Used settings of the proposed low entropy detector                         |

| 6.1 | Results of the FIPS tests of the behavioral model of the TRNG with time    |

|     | multiplexed sources of randomness. The sequences were generated di-        |

|     | rectly (Directly), using the XOR corrector (XOR), or using the Von Neu-    |

|     | mann corrector (VN)                                                        |

| 6.2 | Results of the NIST tests of the behavioral model of the TRNG with time    |

|     | multiplexed sources of randomness                                          |

| 6.3 | Results of the FIPS tests for both settings of the behavioral model of the |

|     | TRNG based on the EGA                                                      |

| 6.4 | Results of the NIST tests for both settings of the behavioral model of the |

|     | TRNG based on the EGA                                                      |

| 7.1 | Results of productivity improvement based on design time measurement       |

|     | for different type of AMS circuits [8]                                     |

| 7.2 | The results demonstrating productivity gain created by the incremental     |

|     | control [9]                                                                |

| 7.3 | The results demonstrating productivity increase created by the similar     |

|     | search [12]                                                                |

#### l Chapter

### Introduction

Can we imagine our lives without modern communication systems? Internet and modern hand-held devices are used every day. These modern communication systems connect people and allow us to reduce geographical distances between different places in the world. Almost immediately through these systems, we can transmit or receive the latest information about development of the newest events and things. Important transactions in business, negotiations with offices, and sending of sensitive information can be also made by these communication systems. To make it all possible, one condition must be met. Security of transfers made by the modern communication systems has to be ensured. For this purpose, different session keys for authentication and encryption are created. Therefore parts of these systems are devices that are able to generate unpredictable and nonrecurring numbers – random numbers [1]. These very important devices – random number generators (RNGs) – generate random numbers with specific features, for example, uniform distribution and high entropy.

Random numbers are usually generated by mathematical computational algorithms known as pseudo-random number generators (PRNGs). Number sequences generated by PRNGs only approximate to properties of true random number sequences and are not appropriate for use in cryptographic devices and communication systems because they are generated by the computational algorithm using present and past values. The initial state usually called seed is set externally. Thus, under certain conditions, future values could be theoretically predictable [2].

For higher security level, devices based on a physical source of randomness can be incorporated into structures of modern communication or cryptographic systems instead of PRNGs. These generators are commonly called true random number generators (TRNGs) and are based on physical phenomena exhibiting a random behavior. However, magnitudes of these sources of randomness are very small. Therefore TRNGs are very sensitive to disturbance. The basic function of these generators can be affected by sources of undesired deterministic noise such as temperature variations or power supply noise. In an extreme case, this weakness allows deliberate attacks that are executed by malicious noise. Hence, the TRNGs described in this work contain structures that are able to suppress temperature and process variation or are able to react to states caused by deterministic noises. Another fundamental parameter of the TRNGs usable in the systems above-mentioned is sufficient output random data rate. Therefore the presented TRNGs are proposed to generate high-quality random numbers with high output random data rate.

It is not possible to prove that an arbitrarily long sequence of random numbers is really random. Therefore the quality of generated output random number sequences is evaluated using well-known statistical test suites, which are composed of certain amount of exactly defined tests and are able to find any undesirable hidden dependencies or unbalanced distribution.

In order to be possible to put the proposed TRNGs on the market, it is necessary to come up with a functional product on time. This can be achieved by shortening design time because fabrication time is usually fixed. However, shorter design time must not adversely affect the quality and reliability of fabricated devices. Therefore, during development of described TRNGs, new design methodology steps have been proposed and used. For correct function of TRNGs, the high quality of physical design is essential because any inaccuracy in physical design can cause an undesirable distortion of output random data or even generator failure. Hence the introduced methodology steps are also focused on physical design of integrated circuits (ICs).

The development of TRNGs is an actual topic. The main goals of this thesis are following:

- Development of a new TRNG architecture allowing an increase of output random data rate.

- Proposal of mechanisms detecting a significant decrease of the quality of random number sequences.

- Development of behavioral models of TRNGs allowing acceleration of system simulations.

- Development of extensions of physical design methodology speeding up the design process and making designs more robust.

### **1.1 Organization of This Thesis**

This thesis is organized as follows. The topic of this work together with descriptions of author's contributions and the state of the art are introduced in chapter 1 followed by summary of TRNG fundamentals in chapter 2. Methods of random number sequence evaluation are presented in chapter 3.

Principle and design of the improved TRNG structure with time multiplexed sources of randomness are shown and discussed in chapter 4. Chapter 5 deals with the TRNG completed by protective mechanisms detecting deliberate malicious attacks.

Simulations of systems on chip (SoCs) containing TRNGs are very time-consuming. Therefore behavioral models of TRNGs, which are able to shorten simulation time, are presented in chapter 6. Physical design time of TRNGs can be reduced by new analog and mixed-signal (AMS) methodology steps described in chapter 7. Finally, the work is concluded in chapter 8.

### **1.2** Author's Scientific Contributions

This work is aimed at the development of improved structures of true random number generators that produce high-quality random number sequences and can be integrated into modern communication and cryptographic systems quickly and easily. The presented TRNGs are proposed as parts of complex SoCs, which can be fabricated in standard complementary metal-oxide-semiconductor (CMOS) or bipolar-CMOS-double diffused MOS (BCD) [3] processes on silicon substrates. In other words, they are designed both from the perspective of the generated random number sequences quality and from the perspective of system integration. More specifically, this work brings the following contributions:

• Development of the TRNG with time multiplexed sources of randomness to get higher output random data rate.

In the proposed TRNG presented in chapter 4, the random data rate is increased by a transition from a serial approach to the parallel use of more independent sources of randomness. The so-called principle of pipelining has been implemented. This new architecture together with obtained results has been published in the impacted journal Radioengineering [4].

#### • Implementation of protective mechanisms into TRNG structure.

The new enhanced generic architecture introduced in chapter 5 includes mechanisms, which can detect a bias in sequences of random numbers caused by deliberate malicious attacks and can reveal a significant decrease in the entropy of sources of randomness. This idea has been published in the reviewed journal ElectroScope [5] and presented at an international conference [6].

• Development of behavioral models of designed TRNGs allowing faster simulations and verifications at a system level.

Simulations of SoCs containing TRNGs at the transistor level are enormously timeconsuming. This work presents behavioral models of the developed TRNGs, which approximate their properties, speed up the simulations, and allow revealing system errors. The behavioral models of TRNGs have been presented at an international conference [7].

## • Development of methodology steps of AMS IC physical design allowing faster and more robust design of the TRNGs.

This thesis introduces new features suitable for the physical design of the developed TRNGs. A tool automatically sorting electrical devices according to their topological, structural and electrical properties has been published in the impacted journal named Integration, the VLSI Journal [8]. Other functions controlling layout objects without filling forms, searching an IC design database based on similarity of object properties, or classifying matched structures regarding systematic mismatch have been published in the reviewed journal named Advances in Science, Technology and Engineering Systems Journal [9] and presented at international conferences [10], [11], [12], and [13].

#### **1.3** State of the Art

Cryptographic devices and secure communication systems use random numbers for their operations [1]. In other words, RNGs help to ensure the security. Random number generators can be also used for other purposes. They are commonly used to model and simulate various natural phenomena or physical processes. Random numbers are the basis for simulations of electrical circuits and elements, semiconductor structures or simulators of physical fields. Specifically, the Monte Carlo simulation method is based on generating random number sequences [14]. In statistics, random numbers are used, among other things, for selection of random samples from larger data sets. Very often for measurements in acoustics, noises with different spectral characteristics are generated by random number generators. Sequences of random numbers are used not only for scientific purposes but they appear in art or in commercial applications such as various lottery games and gambling slot machines.

Functions of many electronic devices and systems depend on generating of highquality random number sequences with sufficient output random data rate. Any failure of the RNG leads to total failure of the whole system. Therefore it is essential to use random number sequences generated by any TRNG. In the past, different variations of TRNGs were only presented in specialized cryptographic devices such as hardware security modules, cryptographic accelerators, or smart cards. With the advent of modern compact fast computers and more sophisticated programs, the need for available highquality random number sequences has increased. TRNGs have been incorporated into more complex systems such as motherboard chipsets [15], platforms or processors [16]. Today, TRNGs are individual blocks of SoCs [17].

True random number sequences can be extracted from the chaos, which occurs in semiconductor lasers [18], from randomness occurring in Josephson junctions in superconductive integrated circuits [19]. Other TRNGs are based on radioactive decay [20] and [21] or magnetic tunnel junctions [22]. However, these principles are not suitable for TRNGs, which are parts of SoCs, usually fabricated in standard CMOS processes on silicon substrates.

Thus TRNGs integrable into these SoCs are based on more principles appropriate such as amplification of electrical noise, oscillator jitter, metastable states of electronic circuits, or chaotic based non-linear dynamical systems. The amplification of electrical noise is pure analog technique. In this case in a part called a noise source, a type of analog noise is extracted and amplified directly. In 1997, Holman et al. described the technique of direct noise amplification in [23]. This technique was also used by Intel in the design of the RNG, which was described by Jun and Kocher in 1999 [15]. Eberlein and Bakar proposed a TRNG based on CMOS channel noise, which is suitable for smart card applications in 2007 [24]. The new structure based on random current spikes appearing in a reverse polarized p-n junction and influencing a circuit with an unstabilized operating point was proposed by Kotě et al. in 2012 [25].

The phenomenon called the jitter is the basis for TRNGs, which are composed of standard digital cells without any analog parts. This phenomenon arises in all digital clocked circuits and can be described as an uncertainty in the exact timing of the rising edge or the falling edge in a square wave signal. Thus basic parts of these TRNGs are ring oscillators. This type of TRNGs is usually designed in Field Programmable Gate Arrays (FPGAs) or in ICs. In 2004, Kohlbrenner and Gaj proposed a TRNG using a FPGA [26], which do not contain any phase-locked loops and only uses configurable logic blocks. A detailed description of the behavior of TRNGs based on a large number of ring oscillators with the same ring length and a post-processing based on resilient functions was developed by Sunar et al. [27]. In 2006, this proposal was implemented into a FPGA by Schellekens et al. [28]. This TRNG needed minimally 110 ring oscillators of three inverters.

Fischer et al. analyzed the jitter generated in ring oscillators [29]. They used a simple physical model of jitter sources to show that the random jitter accumulates slower than the global and manipulable deterministic jitter. In 2009, Bochard et al. continued with the analysis of a improved TRNG structure based on ring oscillators and showed that the proportion of the pseudo-randomness compared to the true-randomness in the generated random raw signal is much bigger than expected [30]. In 2010, Güler and Ergün presented a high speed RNG based on the jitter, which was design and fabricated as the first known application specific integrated circuit (ASIC) [31]. For better extraction of randomness from an oscillator based TRNG, Amaki et al. proposed a jitter amplifier [32], which was fabricated in a 65 nm CMOS process in 2013. A classical ring oscillator in TRNGs was replaced by self-timed rings. A new self-timed based TRNG was presented by Cherkaoui et al. [33] where self-timed rings allowed to adjust the time lapse between two successive events propagating around the ring.

Effect of flicker noise on a CMOS ring oscillator based TRNG was described by Güler et al. in 2014, which showed that flicker noise has a positive effect on increasing the entropy [34]. Then in 2017, Coustans et al. exploited subthreshold properties of jitter of events propagating in a self-timed ring oscillator and in an inverter based ring oscillator for a design of a TRNG in a 180 nm CMOS process [35]. A concept of capacitive coupling between two ring oscillators amplifying jitter and a dual-edge sampling scheme increasing the output random data rate was used by Do and Liu for a design of a low-power TRNG fabricated in a 65 nm CMOS process [36]. In 2018, Saxl et al. published an ultra-low power TRNG based on ring oscillators composed of current-starved inverter design [37], which is intended for passive radio frequency identification tags and fabricated in a 55 nm semiconductor process.

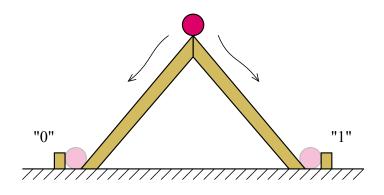

In integrated circuits, metastable states appear and have the random behavior caused by the presence of noises. Therefore this phenomenon is especially suitable for ICs and is the basis for modern TRNGs. A TRNG based on metastable behavior was published by Kinniment and Chester in 2002 [38] and fabricated in an AMS 0.6 µm process. This solution uses a feedback loop to set the ratio between output ones and zeros. In 2008, Tokunaga et al. proposed a metastability based TRNG fabricated in a 130 nm CMOS process [39], which grades the probability of randomness regardless of the output bit value by measuring the metastable resolution time. The proposed system determines the original random noise level at the time of metastability and tunes itself to achieve a high probability of randomness. TRNGs based on metastability of digital latches and fabricated in a 350 nm CMOS process were presented by Holleman et al. [40]. Used floating-gate memory cells allow compensating offsets causing any nonrandom behavior.

A pure digital TRNG was designed by Srinivasan et al. [41] in 2009. In this TRNG, programmable cross-coupled inverters and programmable delay components reducing parasitic deterministic influences were implemented. For this design, a 45 nm CMOS technology was used. In 2010, Suresh and Burleson used this design for comparison of the digital post-processing effectiveness of using the XOR corrector and the von Neumann corrector [42], which are the most used correctors for direct post-processing in TRNGs. Then in 2015, Suresh and Burleson followed up on this work with an article [43] that described a stochastic model for metastability based TRNG and an impact of intra-die variations. Using this model, they compared three basic post-processing tech-

niques the XOR corrector, the von Neumann corrector, and the PRESENT cipher corrector. Meanwhile, in 2012, they proposed a sub-vdd pre-charge technique [44], which improve the tolerance of the used metastability based TRNG to device mismatch. Mathew et al. designed TRNGs based on the above-mentioned unstable cross-coupled inverter pair architecture in a 45 nm CMOS process [45] and in a 14 nm fin field effect transistor (FinFET) CMOS process [46]. Another TRNG linked a jitter generator as a noise pre-amplification and a metastable latch as jitter edge detector [47]. This solution was developed by Kuan et al. in 2014 and was fabricated in a 40 nm CMOS technology. In 2017, Tao and Dubrova presented a TRNG fabricated in a 65 nm CMOS process [48], in which randomness was extracted from a circuit formed by latch comparators and a metastable detector allowing ternary valued outputs. Kotě et al. developed a TRNG with time multiplexed metastability-based sources of randomness in 2018 [4]. This generator fabricated in a 130 nm CMOS technology is suitable for ICs used in modern hand-held devices and is resistant to changing environmental conditions.

Metastability based TRNGs have been mostly implemented into ICs. However, in 2012, Hata and Ichikawa proposed a pure digital metastability based solution of TRNGs [49] that can be implemented in any FPGAs. The RS latch was implemented as a source of randomness. The XOR tree was applied on the outputs of the 256 RS latches for improving the quality of output random sequences. Then in 2013, Wieczorek presented another solution [50] and [51], which is based on a response time difference of a pair of nearly metastable D flip-flops and can also be implemented in any FPGAs. Another TRNG developed by Li et al. in 2017 uses cross-coupled NAND gates and manual routing [52]. The proposed TRNG was implemented in a FPGA and contained self-calibration and post-processing circuits.

Another type of TRNGs also suitable for ICs uses chaotic based non-linear dynamic systems and their high sensitivity to initial condition changes. A TRNG developed by Petrie and Connelly [53] combined direct noise amplification, oscillator sampling, and discrete-time chaotic system based on the Bernoulli shift map and was fabricated in 2  $\mu$ m CMOS technology in 1998. A TRNG architecture based on a circuit called a double-scroll attractor was published by Yalcin et al. in 2004 [54]. This generator was realized by current feedback operational amplifiers and is appropriate for integration on a chip. Drutarovsky and Galajda proposed a TRNG extracting randomness from a chaotic

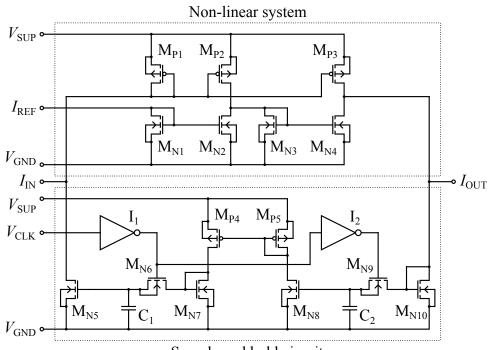

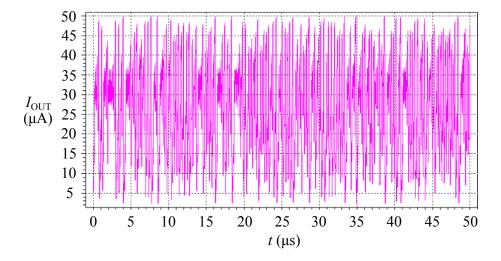

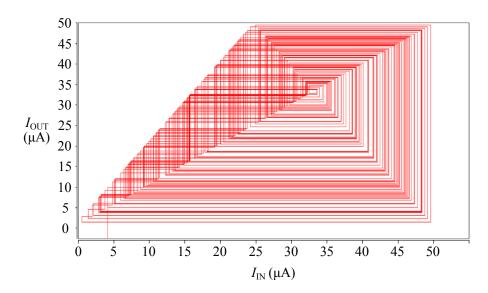

switched-capacitor circuit in 2007 [55]. This proposal is embedded into a mixed-signal reconfigurable device without any external components. In 2010, Pareschi et al. designed two TRNG prototypes [56] developed from a pipeline analog-to-digital converter (ADC) design, which was modified to operate as a set of piecewise-linear chaotic maps. The prototypes were fabricated in a 350 nm respectively in a 180 nm CMOS processes. In 2014, Cicek et al. developed two chaos based TRNGs. The first [57] used the dual Bernoulli map as a source of randomness and was implemented in a field programmable analog array IC. The second [58] operated with a current mode skew tent map circuit and was designed in a 250 nm CMOS technology.

A compact discrete-time chaotic oscillator is proposed to approximate a V-shape map and is a core of a TRNG [59], which was designed in a 180 nm CMOS process and presented by Jiteurtragool et al. in 2015. In the same year, Park et al. proposed a TRNG using a discrete Boolean chaotic oscillator [60] fabricated in a 350 nm CMOS technology. Also, the chaotic based TRNGs can be implemented in a FPGA. In 2017, Koyuncu and Ozcerit published a solution suitable for FPGAs [61] that used the Sundarapandian-Pehlivan chaotic system. Next year, Wieczorek and Golofit introduced a new concept of a TRNG combining metastability based source of randomness and a chaotic circuit using a time-continuous random variable in a feedback loop [62]. This concept was verified in a FPGA and is also appropriate for gate level on-chip implementations.

Safety of contemporary systems is dependent on the unpredictability of random number sequences. Safety of these systems can be violated if there is a possibility that the values of generated random numbers can be detected or affected by a deliberate attack. Therefore the random number sequences are generated by TRNGs, which are tested and qualified by statistical tests. For testing of the majority of TRNGs, two well-known statistical test suites are usually used. The first test suite – FIPS PUB 140-2, Security Requirements for Cryptographic Modules [63] (the FIPS test suite) – was published by the National Institute of Standards and Technology in 2001. The second test suite – A Statistical Test Suite for Random and Pseudorandom Number Generators for Cryptographic Applications [64] (the NIST test suite) – was published by the National Institute of Standards and Technology in 2010. This strict test suite is suitable for applications where the strongest requirements are needed. In some publications, the third statistical test suite – The Diehard Battery of Tests of Randomness [65] – developed by Marsaglia in 1995 appears. A necessary condition for implementation of a TRNG into modern systems is positive results of these test suites.

Simulations of proposed circuits are an integral part of IC design. As described above, TRNGs can be parts of SoCs. Simulations of these complex systems at a transistor level is becoming unrealistic due to enormous time demands [66]. Therefore researchers and designers develop behavioral models of individual parts of SoCs, which allow to simulate and verify the whole system in an acceptable time. Petrie and Connelly presented a model of the proposed TRNG in [53]. Properties of output random data were evaluated by statistical tests. The TRNG structure published by Kotě et al. in [25] was verified by a developed behavioral model, which was created in analog hardware description language Verilog-A. Then, they described an enhanced architecture of TRNGs [5], which was also modeled in Verilog-A and can detect deliberate malicious attacks. For evaluation of well-known post-processing techniques, Suresh and Burleson developed a model of the metastability-based TRNG [43]. Behavioral models of TRNGs developed on the base of usually used architectures were presented by Kotě et al. in [7]. These types of generators are suitable for implementation in SoCs.

Another integral part of IC design is physical design. TRNGs are sensitive circuits, whose physical design has to be created with the utmost care because any error can cause generator failure. Moreover, TRNGs are often not only composed of digital cells. They are a typical representative of AMS circuits. This part of state of the art can also be found in the author's publication [8].

In the early years of IC design and production, a lot of time was spent on an inspection of the semiconductor structures drawn on tracing paper as all geometrical parameters were checked manually by rulers and protractors. As time passed, this inefficient technique was replaced by computer-aided design (CAD) applications, which are beneficial for both design and inspection of the semiconductor structures. Development of CAD applications for IC physical design began in the second half of the 20th century [67], [68]. Today's CAD systems [69], [70], [71] allow modifications of physical design flow and implementation of new algorithms. Unlike digital synthesis and implementation tools, AMS physical design still remains handwork. Several automated tools for analog layout were presented [72]. Some of them are capable of good quality routing, some of them help with generation of devices, unfortunately still there is no tool widely commercially used for analog placement. There are two main reasons for this situation. At first, placement of AMS circuits requires much more constraints compared to digital ones. As described by Scheible and Lienig in [73], these constraints can be implicit or explicit, and in AMS physical design flow it is very difficult to express all of them explicitly to be then accessible for algorithmic processing.

The second obstacle in AMS physical design flow, well-stated in [74], is somehow a reluctance of analog designers to use a complete automated analog flow. They are missing some kind of "aesthetics" in an automatically proceeded layout. Aesthetics which enables human beings to verify with a naked eye if electrical and matching requirements are met. Instead, analog designers prefer small automated steps, using so-called in-design assistants [73] that design environments from different vendors such as [69], [70], [71] are full of. Moreover, in-design assistants are not only developed by the vendors, but they are also developed by researchers. Vacula et al. developed an incremental control of layout objects [10], which removes form filling based on incremental approach. They also introduced a way of search in IC design database [12], which is based on similarity of object properties. Systematic mismatch arising in matched structures can be minimized by a method of matched structure classification presented in [13]. Designers can use indesign assistants for time-consuming tasks, but they keep the control of the whole layout.

In the final phase of physical design, lithographic design shapes are transformed into text or vector files and their geometrical and electrical parameters are checked by automatic algorithms [75]. The principle of these checks has remained similar up to now, of course, modern and more efficient algorithms [76], [77] are used in the contemporary CAD environments. Unfortunately, this saves time only during the inspection at the end of design.

However, another amount of time can be saved by anticipating human failure in early stages of layout. Again, automatic algorithms implemented in some CAD environment can do a part of the job. They are able to lay out simple integrated circuits [78], typical circuit structures [79], [80], basic analog building blocks [81] or to optimize floorplan using multi-objective optimization algorithm based on topological benchmark [82]. They can replace lengthy and complex manual work, in which humans are most likely to make a mistake. Moreover, if they keep respecting particular stages of IC layout, these algo-

rithms can be appropriately combined, so results of one algorithm can be used as an input for another one. The analog layout flow is then becoming partially automated.

Numerous works describing almost fully autonomous physical design synthesis have been published. The approach [83] introduced by Eick et al. describes automatically generated constraints used for an automatic placer and then for an automatic router. Another automatic physical design flow [84] developed by Habal and Graeb takes into account influence of each device reshaping and is focused on finding an optimal layout by applying a non-slicing placement algorithm and numerical simulation to evaluate device sizing procedure and effect of layout parasitics.

Automated methods [83], [84] look very promising, but there are several drawbacks which limit their usage in practice. The core of these methods is an extraction of matched structures such as current mirrors, cascaded current mirrors, and differential pairs. High precise designs use trimmed structures which contain a number of pass-gates and switches to be able to configure required circuit parameters. Also in low power designs used in mobile applications and the Internet of Things (IoT), the power consumption is very optimized. Due to this need, AMS circuits contain switches disconnecting dedicated parts. In high reliable design, the negative bias temperature instability (NBTI) [85] and the positive bias temperature instability (PBTI) phenomena [86] are taken into account. Therefore inputs of differential amplifiers are usually reconfigurable. The additional switches do not allow simple detection of basic analog structures. It is another reason why until today there is no universal tool for automated AMS physical design synthesis and AMS physical designs are still made manually. Therefore Kotě et al. introduced a pre-placement phase of IC AMS physical design flow [8], which automatically sorts electrical devices used in planar IC technologies according to their topological, structural and electrical properties. The automated pre-placement phase is able to prevent a creation of hardly detectable errors occurring during physical design and speeds up the entire design process.

## **1.4** Solution Methods of the Work

Known and world-wide spread environment Cadence Virtuoso has been used to development TRNGs suitable for ICs. As described above, proposed TRNGs are the representative of AMS electronic circuits. For proposal implementation, the Analog-on-Top approach has been applied. Thus schematic diagrams have been created in Cadence Virtuoso Schematic Editors [87], [88]. Functions of proposed circuits have been simulated by known tools such as Mentor Eldo [14] or Virtuoso Spectre Circuit Simuator [89]. The TRNGs have been developed in 130 nm bulk CMOS technologies known as HCMOS9GP and HCMOS9A and in 160 nm BCD technologies known as BCD8sP and SOIBCD8S. All of these technologies have been provided by STMicroelectronics. To be possible to simulate SoCs containing TRNGs in an acceptable time, behavioral models of these generators have been created in the Verilog-A hardware description language (HDL) [90]. The models have been simulated in the simulators above-mentioned.

Physical design of proposed TRNGs has been created in Cadence Virtuoso Layout Editors [91], [69]. New methodology steps of physical design flow have been developed in the Cadence SKILL programming language [92] and in the Cadence SKILL IDE environment [93]. Before pattern generation tape-out, the proposed topologies were checked by Calibre DRC and LVS [94] whether they were compatible with design rule manual (DRM) respectively with the proposed schematic diagrams. Parasitic capacitors and resistors have been extracted from completed physical designs by Synopsys Star-RCXT [95]. A fabricated TRNG has been characterized and validated by standard laboratory equipment such as precise voltage and current sources, oscilloscopes, logic analyzers, etc. All generated and measured data have been processed by MATLAB [96].

# Chapter 2

## **TRNG** Fundamentals

Development of true random number generators progresses dynamically, as it is mentioned in state of the art description in section 1.3. Modern communication and cryptographic systems still have higher requirements on safety. In this regard, random number sequences generated by PRNGs have insufficient properties such as periodicity of the generated sequences. Therefore it is necessary to develop new and more sophisticated TRNGs. Although the development of TRNGs is advanced, it is essential to describe fundamentals of the TRNGs as first.

Before the description of basic structures of TRNGs, random numbers are defined. The random numbers can only be considered in the case when the number is a part of a sequence of several other numbers, which were generated independently within each other of a defined set or an interval with a probability distribution. Moreover, future values of random numbers are not possible to predict based on knowledge of present or past values of the number sequence. Cores of the TRNGs usually generate digital values in the form of logic bits, which can be processed in additional blocks creating any more complex format of numbers. Therefore, in this case, sequences of logic zeros and logic ones are assumed.

In this chapter, a generic architecture of TRNGs is introduced. The basic principles of TRNGs suitable for utilization in ICs are thermal noise generated by resistors, oscillator jitter, metastable states of electronic circuits, or chaotic behavior of non-linear dynamic systems. Description of these principles is followed by explanations of basic physical phenomena with the random behavior, which serve as a source of randomness.

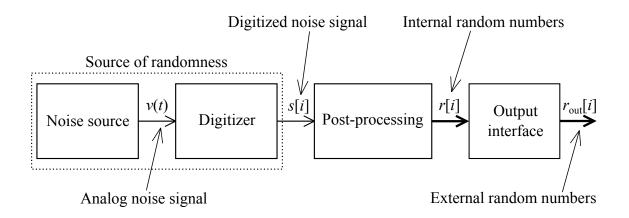

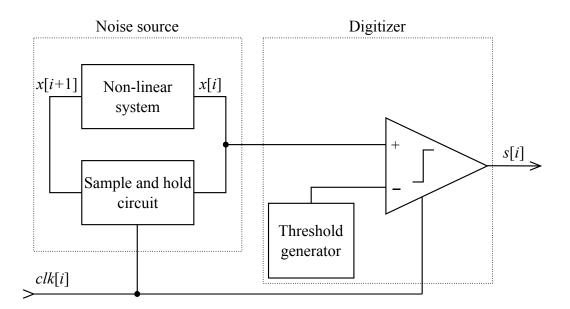

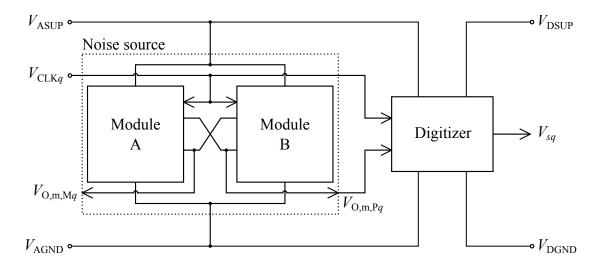

## 2.1 Generic Architecture

True random number generators are devices, whose output digital signals exhibit nondeterministic properties. Cores of these devices are able to generate random bits, and by their processing, random numbers can be formed. The generated sequences of logic zeros and logic ones are divided into frames with a fixed length. These created numbers are written in the frames in the binary form and can be marked as the random numbers. For modifications of some of their properties, a post-processing algorithm can be incorporated into a TRNG architecture. Majority of TRNGs follows a generic architecture that was also presented in [97], [28] and [98]. The generic architecture consists of several blocks. A noise source and a digitizer form a source of randomness. Into the generic architecture, a post-processing block and an output interface are also incorporated. The arrangement of these blocks is shown in figure 2.1.

Fig. 2.1: The generic architecture of a TRNG [97]

A noise source produces a signal with non-deterministic features commonly called an analog noise signal v(t), which is a continuous signal in the time t. This signal v(t) is digitized in the next block – a digitizer – that creates a digitized noise signal s[i] where i is a normalized period,  $i = t/\Theta_c$ , and  $\Theta_c$  is a period of a clock signal. Occurring imperfections of the digitized noise signal s[i] such as a bias, hidden dependencies, or unbalanced distribution can be solved in the post-processing block, which produces internal random numbers r[i]. The format of the internal random numbers must be adapted to the required output data format. This is a function of an output interface that produces an external random numbers  $r_{out}[i]$  compatible with system requirements.

### 2.1.1 Noise Source

The noise source is a unit creating the analog noise signal v(t) based on a physical phenomenon. If this phenomenon has the random behavior, the output analog noise signal v(t) can also have random features. An ideal noise source generates the analog noise signal v(t) with the uniform probability distribution. However, it is tough to develop such a source of randomness. Therefore some correction data techniques are usually used in combination with an appropriate source of randomness, whose properties are closer to the properties of the ideal source of randomness.

Physical phenomena such as radioactive decay, chaos occurring in lasers, or randomness occurring in superconductive circuits can be used as noise sources for TRNGs. However, the TRNGs are usually implemented in SoCs. For these purposes, it is essential to use the noise source, which can be integrated into a chip. In real integrated TRNGs, electrical noises generated in semiconductor structures, jitter arising in ring oscillators, metastable states appearing in ICs, or chaos emerging in non-linear dynamic systems can be used.

## 2.1.2 Digitizer

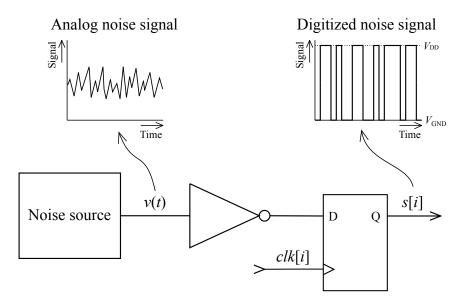

The contemporary SoCs works with digital signals. For this reason, TRNGs generate a random signal in digital form. To be possible to produce the digitized random signal, the generic architecture of TRNGs contains the digitizer. For demonstration in this part, there are shown basic models of analog noise signal digitization.

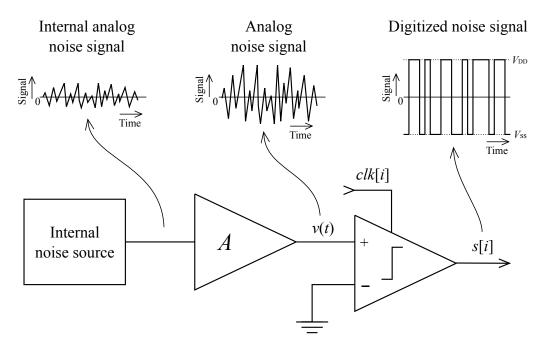

The main component of the first model of digitization is a clocked comparator. Structure of this model is shown in figure 2.2. The internal analog noise signal is amplified to have sufficient amplitude to be able to drive the input of the clocked comparator. The analog noise signal v(t) is compared with a reference in each clock period. Thus the signal v(t) is converted to a signal with discrete levels, which is synchronized with the system clock. The output signal can be marked as the digitized noise signal s[i] and processed in next blocks. The topology containing comparator was described in [23].

Fig. 2.2: The digitization model with the clocked comparator