Ph.D. Thesis

Czech Technical University in Prague

Faculty of Electrical Engineering Department of Measurement

# Methods for Verification and Validation of Automotive Distributed Systems

### Ing. Jan Sobotka

Electrical Engineering and Information Technology Branch of study: Measurement and Instrumentation

August 2017 Supervisor: doc. Ing. Jiří Novák, Ph.D.

## Acknowledgement / Declaration

Many people helped me during a long time of writing of this thesis. I would like to thank all of them. Some of them are my supervisor for the guidance, our lab crew for fruitful discussions, and a number of great students which helped me a lot with the implementation part of this work. Also, I would like to thank my girlfriend Radka for the patience and my family for the support, since the time of my studies was quite longer than expected.

The thesis is dedicated to my grandmother Anna, because she always said, that I will be a great doctor. (smile)

I declare that I carried out this doctoral thesis independently, and only with the cited sources, literature and other professional sources.

In Prague 30. 8. 2017.

## Abstrakt

Stále narůstající složitost automobilových elektronických systémů vytváří poptávku po vhodných validačních a testovacích metodách. Směrování automobilového průmvslu k plně autonomním vozidlům tento trend dále podporuje. Cílem práce je rozšířit množinu dostupných testovacích metod v několika oblastech. První takovou oblastí jsou měřicí metody pro komunikační sběrnici FlexRay. V porovnání se staršími standardy CAN a LIN je řadič této sběrnice konfigurován mnohem větším množstvím parametrů. Pro zajištění správné funkce systému je nutné ověřit, že aktuální hodnoty těchto parametrů odpovídají hodnotám požadovaným. Tento úkol vyžaduje návrh měřicích metod schopných identifikovat skutečné hodnotv pa-Další oblastí vyžadující rametrů. doplnění stávajících testovací možností je integrační testování automobilové elektroniky. S rostoucím počtem elektronických řídicích jednotek začíná být stávající způsob testování pomocí ručně navržených a implementovaných testovacích sekvencí nedostatečný.

Práce se zabývá automatizací generování těchto testovacích sekvencí využitím principů Model-based  $\mathbf{S}$ testování. Testovací sekvence isou generovány z modelů specifikovaných časovanými automaty. Součástí práce je návrh tohoto inovativních testovacího konceptu. Řešení je následně implementováno ve formě testovacího nástroje Taster a také je představena nová HIL testovací platforma založená na modulárním hardwaru firmy National Instruments. Ověření této metody je provedeno formou dvou případových studií. První demonstruje metodu problému testováním systému na bezklíčového zapalování, druhá potom testuje reálný systém otvírání pátých dveří automobilu.

**Klíčová slova:** Testování, FlexRay, Parametry, Autobilová, Elektronika

## Abstract /

The growth of complexity together with the severity of the potential failure of electronic systems in modern vehicles create pressure on development of powerful validation and testing techniques. This thesis is trying to fill few identified gaps in this field. One of the gaps is the absence of suitable measurement methods for relatively new automotive communication system called FlexRay. In comparison with older communication standards CAN and LIN, each FlexRav communication controller is parametrized by almost hundred of parameters. From the validation point of view, it is necessary evaluate that the parameters to programmed communication into controller are in conformance with the specified parameters values. Such evaluation is not possible without suitable methods capable of measuring the actual parameters values. Another blank space which this thesis is trying to fill is related to the Integration of automotive electronics testing systems. Due to increasing number of electronic control units and number of implemented functions, traditional approach incorporates, the manual test case design is reaching its limits.

This thesis proposes several improvements for this specific domain. Namely it is testbed platform based on National Instruments products, a novel approach based on the Model Based Testing techniques using the Timed Automata specification, several test generation algorithms, and implementation of the proposed concept. The presented solutions were experimentally evaluated. The FlexRay measurement methods were validated on the real communication network. Moreover, in the case of Integration testing, the implemented concept was proved by two case studies. The objective of the first one was the car keyless access system. The second study validated the described solution on the automatic trunk opening system.

**Keywords:** Automotive, Model, Based, Testing, FlexRay, Parameter, Evaluation

## Contents /

| 1 Int | roduc  | <b>tion</b> 1             |

|-------|--------|---------------------------|

| 2 St  | ate of | the Art                   |

| 2.1   | FlexR  | lay2                      |

|       | 2.1.1  | Of the Shelf Avail-       |

|       |        | able Solutions 3          |

|       | 2.1.2  | Related Work 4            |

|       | 2.1.3  | Risk of Incorrect Pa-     |

|       |        | rameterization5           |

| 2.2   | Integr | cation Testing and MBT6   |

|       |        | Weaknesses of Tra-        |

|       |        | ditional Approach7        |

|       | 2.2.2  | Terminology7              |

|       |        | Taxonomy                  |

|       |        | Embedded System           |

|       | 2.2.1  | Modeling                  |

|       | 225    | Test Selection Criteria12 |

|       |        | Test Generation           |

|       |        | Existing Tools13          |

|       | 2.2.8  | -                         |

|       | 2.2.0  | Loop14                    |

|       | 2.2.9  |                           |

| 23    | -      | nary                      |

|       |        | <b>bjectives</b> 17       |

|       |        | tay Objectives17          |

|       |        | ation Testing Objec-      |

| 0.2   |        |                           |

| 4 FI  |        |                           |

| 4.1   |        | view of FlexRay Com-      |

| 4.1   |        | cation System             |

| 19    |        | neter Set Analysys21      |

|       |        | up Parameters             |

| 4.0   |        | pWakeupChannel23          |

|       | 4.3.1  |                           |

|       | 4.0.2  | gdWakeupTxActive,         |

|       |        | pWakeupPattern24          |

|       | 4.3.3  |                           |

|       | 4.0.0  | gdWakeupRxIdle,           |

|       |        | gdWakeupRxWindow24        |

| 4 4   | Ctonto |                           |

| 4.4   |        | ip Parameters             |

|       | 4.4.1  | 01                        |

|       | 4.4.2  | 0                         |

|       | 4.4.3  | Collision Avoidance       |

|       | 1 1 1  | Symbol                    |

|       | 4.4.4  | pdListenTimeout26         |

| 4.5                                                       | Evalu                                                                                                                                                   | ation of Clock Syn-                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           | chron                                                                                                                                                   | ization Parameters26                                                                                                                                                                                                                                                               |

|                                                           | 4.5.1                                                                                                                                                   | Cycle Length Influ-                                                                                                                                                                                                                                                                |

|                                                           |                                                                                                                                                         | encing and Measure-                                                                                                                                                                                                                                                                |

|                                                           |                                                                                                                                                         | ment                                                                                                                                                                                                                                                                               |

|                                                           | 4.5.2                                                                                                                                                   | Offset Correction                                                                                                                                                                                                                                                                  |

|                                                           |                                                                                                                                                         | Measurement27                                                                                                                                                                                                                                                                      |

|                                                           | 4.5.3                                                                                                                                                   | pdMicrotick27                                                                                                                                                                                                                                                                      |

|                                                           |                                                                                                                                                         | pClusterDrift-                                                                                                                                                                                                                                                                     |

|                                                           |                                                                                                                                                         | Damping28                                                                                                                                                                                                                                                                          |

|                                                           | 4.5.5                                                                                                                                                   | pRateCorrectionOut28                                                                                                                                                                                                                                                               |

|                                                           |                                                                                                                                                         | pOffsetCorrectionOut29                                                                                                                                                                                                                                                             |

| 4.6                                                       |                                                                                                                                                         | ation on Real                                                                                                                                                                                                                                                                      |

|                                                           |                                                                                                                                                         | Ray Network                                                                                                                                                                                                                                                                        |

|                                                           |                                                                                                                                                         | FPGA FlexRay                                                                                                                                                                                                                                                                       |

|                                                           |                                                                                                                                                         | Controller                                                                                                                                                                                                                                                                         |

|                                                           | 4.6.2                                                                                                                                                   | FlexRay Hardware –                                                                                                                                                                                                                                                                 |

|                                                           |                                                                                                                                                         | EUT                                                                                                                                                                                                                                                                                |

|                                                           | 4.6.3                                                                                                                                                   | Experiments32                                                                                                                                                                                                                                                                      |

| 4.7                                                       |                                                                                                                                                         | urement Accuracy                                                                                                                                                                                                                                                                   |

|                                                           |                                                                                                                                                         | peed                                                                                                                                                                                                                                                                               |

| 4.8                                                       |                                                                                                                                                         | nary35                                                                                                                                                                                                                                                                             |

|                                                           |                                                                                                                                                         |                                                                                                                                                                                                                                                                                    |

| 5 In1                                                     | tegrat                                                                                                                                                  | ion resting                                                                                                                                                                                                                                                                        |

|                                                           |                                                                                                                                                         | ion Testing                                                                                                                                                                                                                                                                        |

|                                                           | Select                                                                                                                                                  |                                                                                                                                                                                                                                                                                    |

|                                                           | Select                                                                                                                                                  | tion of Formal Model36                                                                                                                                                                                                                                                             |

| 5.1                                                       | Select<br>5.1.1<br>Time                                                                                                                                 | ion of Formal Model36<br>Passenger Car Inner<br>Light Model                                                                                                                                                                                                                        |

| 5.1                                                       | Select<br>5.1.1<br>Time                                                                                                                                 | ion of Formal Model36<br>Passenger Car Inner<br>Light Model                                                                                                                                                                                                                        |

| 5.1                                                       | Select<br>5.1.1<br>Time<br>5.2.1                                                                                                                        | ion of Formal Model36<br>Passenger Car Inner<br>Light Model                                                                                                                                                                                                                        |

| 5.1                                                       | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2                                                                                                               | tion of Formal Model36<br>Passenger Car Inner<br>Light Model                                                                                                                                                                                                                       |

| 5.1                                                       | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3                                                                                                      | tion of Formal Model36<br>Passenger Car Inner<br>Light Model38<br>d Automata Theory40<br>Finite–State Machine40<br>Automata for Infi-<br>nite Input40<br>Büchi Automaton41                                                                                                         |

| 5.1<br>5.2                                                | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                                                                                             | ion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite–State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41                                                                              |

| 5.1<br>5.2<br>5.3                                         | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin                                                                                   | ion of Formal Model36<br>Passenger Car Inner<br>Light Model                                                                                                                                                                                                                        |

| 5.1<br>5.2                                                | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin                                                                                   | ion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite–State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41                                                                              |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.                                                                 | tion of Formal Model36<br>Passenger Car Inner<br>Light Model                                                                                                                                                                                                                       |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                           | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>System                                                       | tion of Formal Model36<br>Passenger Car Inner<br>Light Model                                                                                                                                                                                                                       |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>Syste<br>Test (                                              | tion of Formal Model36<br>Passenger Car Inner<br>Light Model                                                                                                                                                                                                                       |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                           | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>System<br>Test 0<br>5.6.1                                    | ion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite-State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41<br>ng Workflow Proposal 42<br>ed for Comfort Sys-<br>                        |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                           | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>System<br>Test 0<br>5.6.1                                    | tion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite-State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41<br>ng Workflow Proposal 42<br>ed for Comfort Sys-<br>                       |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                           | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>Syste<br>Test 0<br>5.6.1<br>5.6.2                            | tion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite-State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41<br>ng Workflow Proposal 42<br>ed for Comfort Sys-<br>                       |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                           | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>System<br>Test 0<br>5.6.1                                    | tion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite-State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41<br>rimed Automaton 41<br>g Workflow Proposal 42<br>ed for Comfort Sys-<br>  |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                    | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>Syste<br>Test 0<br>5.6.1<br>5.6.2<br>5.6.3                   | tion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite-State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41<br>rimed Automaton 41<br>mg Workflow Proposal 42<br>ed for Comfort Sys-<br> |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7             | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>Syste<br>Test 0<br>5.6.1<br>5.6.2<br>5.6.3<br>Algor          | tion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite-State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41<br>Timed Automaton 41<br>ag Workflow Proposal 42<br>ed for Comfort Sys-<br> |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8      | Select<br>5.1.1<br>Time<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Testin<br>Testb<br>tems.<br>Syste<br>Test 0<br>5.6.1<br>5.6.2<br>5.6.3<br>Algor<br>Evalu | tion of Formal Model 36<br>Passenger Car Inner<br>Light Model 38<br>d Automata Theory 40<br>Finite-State Machine 40<br>Automata for Infi-<br>nite Input 40<br>Büchi Automaton 41<br>Timed Automaton 41<br>rimed Automaton 41<br>mg Workflow Proposal 42<br>ed for Comfort Sys-<br> |

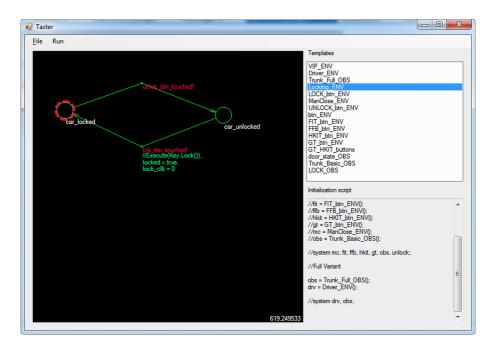

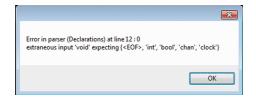

| 5.9.1 Taster Architecture $\dots 52$  |

|---------------------------------------|

| 5.9.2 Model Parser                    |

| 5.9.3 Model Execution53               |

| 5.9.4 Test Adapter                    |

| 5.9.5 Trace Logger $\dots 54$         |

| 5.9.6 Implementation                  |

| 5.9.7 User Interface $\dots 54$       |

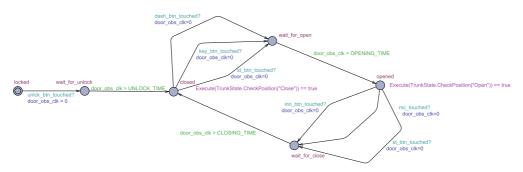

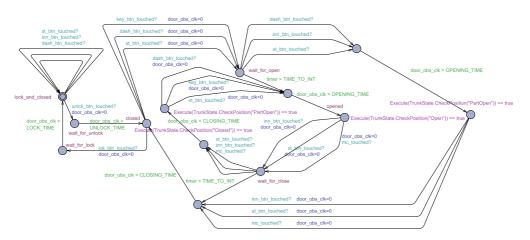

| 5.10 Case Study – KESSY $\dots 56$    |

| $5.10.1$ Specification $\ldots 57$    |

| 5.10.2 Models                         |

| 5.10.3 SUT Implementation $\dots 59$  |

| 5.10.4 Results                        |

| 5.11 Case Study – Trunk               |

| $5.11.1$ Specification $\dots 62$     |

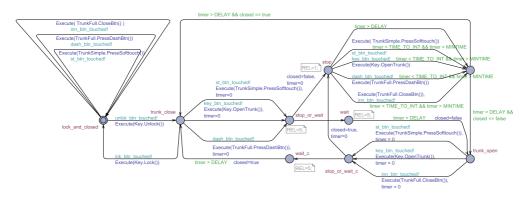

| 5.11.2 Experiment Plan64              |

| 5.11.3 Models                         |

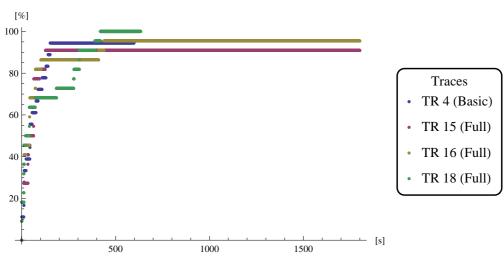

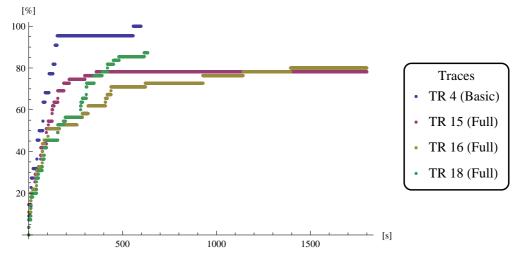

| 5.11.4 Original Test Suite $\dots 69$ |

| 5.11.5 Results70                      |

| 5.11.6 Conclusion71                   |

| 5.12 Summary74                        |

| <b>6</b> Future Work                  |

| <b>7</b> Conclusion                   |

| <b>References</b>                     |

| A Author's Publications and           |

| <b>Grants</b>                         |

| A.1 Publications Related to the       |

| Thesis                                |

| A.1.1 Publications in Jour-           |

| nals with Impact                      |

| Factor                                |

| A.1.2 International Con-              |

| ference Proceedings87                 |

| A.2 Selected Grants Related to        |

| the Thesis                            |

| B Abbreviations                       |

| C Taster User Guide91                 |

## Tables / Figures

| 41    | Parameter set summary22              |

|-------|--------------------------------------|

|       |                                      |

| 4.2.  | An example of real param-            |

|       | eterization23                        |

| 4.3.  | Wakeup parameters sum-               |

|       | mary24                               |

| 4.4.  | Startup parameters sum-              |

|       | mary25                               |

| 4.5.  | List of measured parameters 26       |

| 4.6.  | Test Network Configuration32         |

| 4.7.  | 0                                    |

| 4.8.  | pOffsetCorrectionOut mea-            |

|       | surement (all values in $\mu T$ ) 34 |

| 4.9.  | Overview of measurement              |

|       | duration                             |

| 5.1.  | Selection of modeling envi-          |

|       | ronment                              |

| 5.2.  |                                      |

|       | PAAL modelling language45            |

| 5.3.  | 0 0 0                                |

| 5.4.  |                                      |

| 5.5.  | Kessy – fault injection re-          |

|       | sults                                |

| 5.6.  |                                      |

|       | Trunk ECU Inputs63                   |

|       | Trunk ECU Outputs63                  |

|       | Trunk model summary69                |

| 5.10. |                                      |

|       |                                      |

| 5.11. |                                      |

|       | Test runs – SUT int. 172             |

| 5.13. | Test runs – SUT int. 273             |

| 2.1.          | Wrong pdListenTimeout               |

|---------------|-------------------------------------|

|               | value                               |

| 2.2.          | Possible taxonomy of MBT 7          |

|               | Possible taxonomy of MBT $\dots 10$ |

| 2.4.          | PN example - Button model11         |

| 3.1.          | FlexRay objectives                  |

| 3.2.          | Integration testing objec-          |

|               | tives                               |

| 4.1.          |                                     |

| 4.2.          | 1 1                                 |

|               | wakeup window                       |

| 4.3.          | pdListenTimeout measure-            |

|               | ment                                |

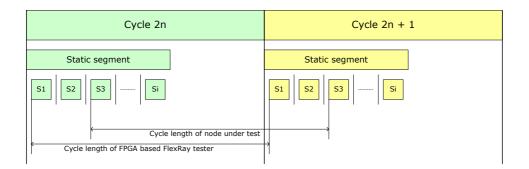

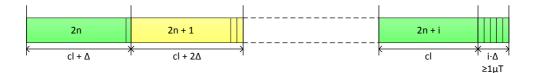

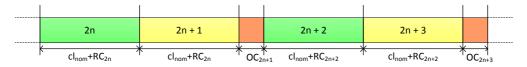

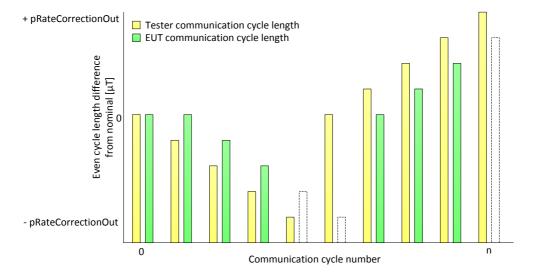

| 4.4.          | Cycle length measurement $\dots 27$ |

| 4.5.          |                                     |

|               | tion                                |

| 4.6.          | Offset correction affected          |

|               | by $pClusterDriftDamping \dots 28$  |

| 4.7.          | Offset correction affected          |

|               | by $pClusterDriftDamping \dots 29$  |

| 4.8.          | Offset correction measure-          |

|               | ment limitation                     |

| 4.9.          |                                     |

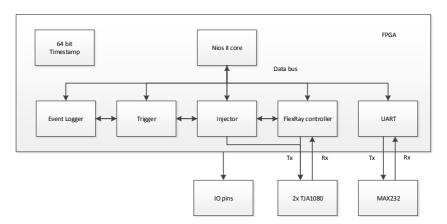

|               | Structure of FlexRay SoC31          |

|               | Inner Light Controller              |

| 5.2.          |                                     |

| 5.3.          | 1 0                                 |

|               | tion testing                        |

| 5.4.          | MBT Workflow in details43           |

| 5.5.          | NI HIL platform                     |

| 5.6.          |                                     |

| 5.7.          |                                     |

| 5.8.          |                                     |

| 5.9.          |                                     |

| 5.10.         |                                     |

| 5.11.         |                                     |

| 5.12.         |                                     |

| 5.13.         |                                     |

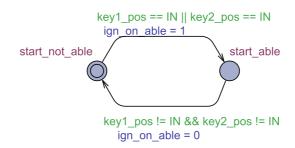

|               | Key position model                  |

| 5.15.         |                                     |

| E 16          | System                              |

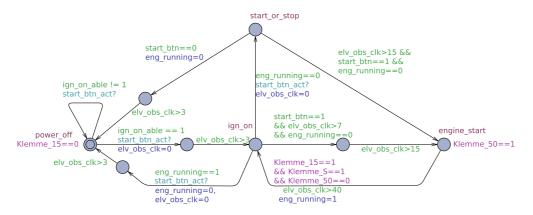

| 5.16.         | Observer model – Ignition           |

| E 17          | System                              |

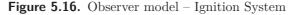

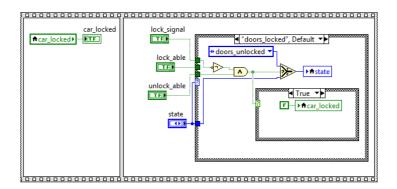

|               | Lock able signal                    |

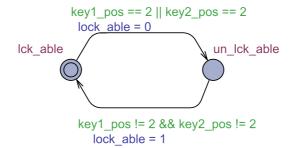

| <b>J.1</b> Ö. | Unlock able signal60                |

| 5.19.        | Start able signal60         |

|--------------|-----------------------------|

| 5.20.        | A part of SUT implemen-     |

|              | tation model61              |

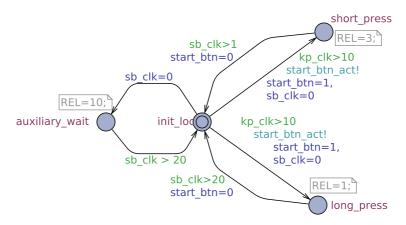

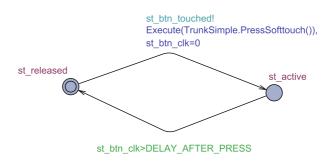

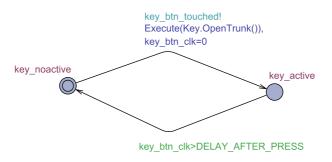

| 5.21.        | Input – SoftTouch button 65 |

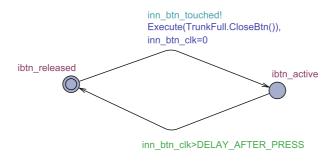

| 5.22.        | Input – Button on inner     |

|              | door's side65               |

| 5.23.        | Input – Button on Key66     |

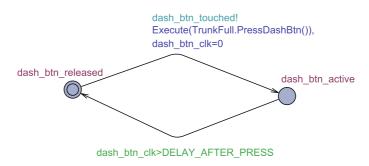

| 5.24.        | Input – Button on Dash66    |

| 5.25.        | Input – Close by hand67     |

| 5.26.        | Input – Virtual Pedal67     |

| 5.27.        | Input – Unlock button67     |

| 5.28.        | Environment - A Driver      |

|              | Model                       |

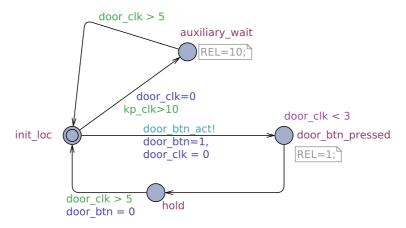

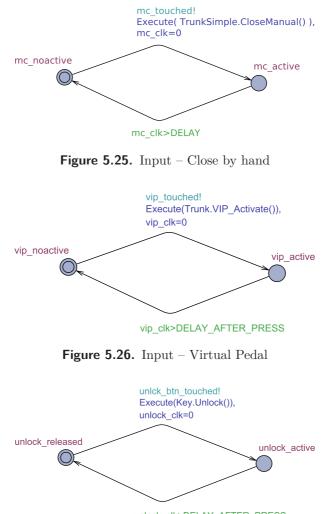

| 5.29.        | Trunk Observer – Basic68    |

| 5.30.        | Trunk Observer – Full69     |

| 5.31.        | Trunk Node Coverage71       |

| 5.32.        | Trunk Edge Coverage72       |

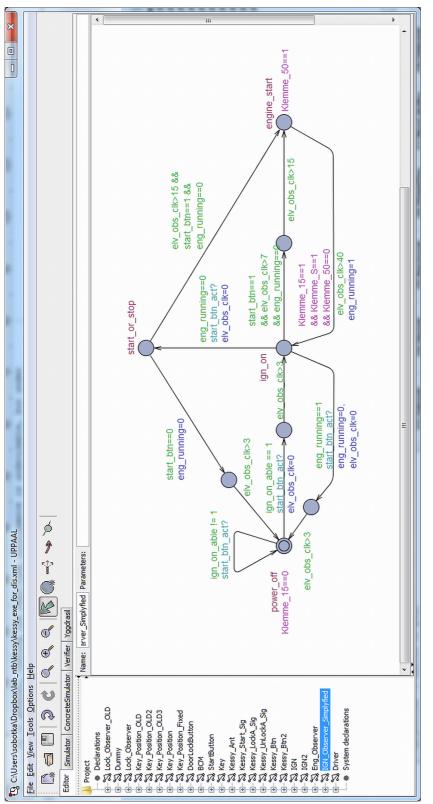

| <b>C</b> .1. | Input Model93               |

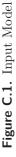

| C.2.         | Model Viewer94              |

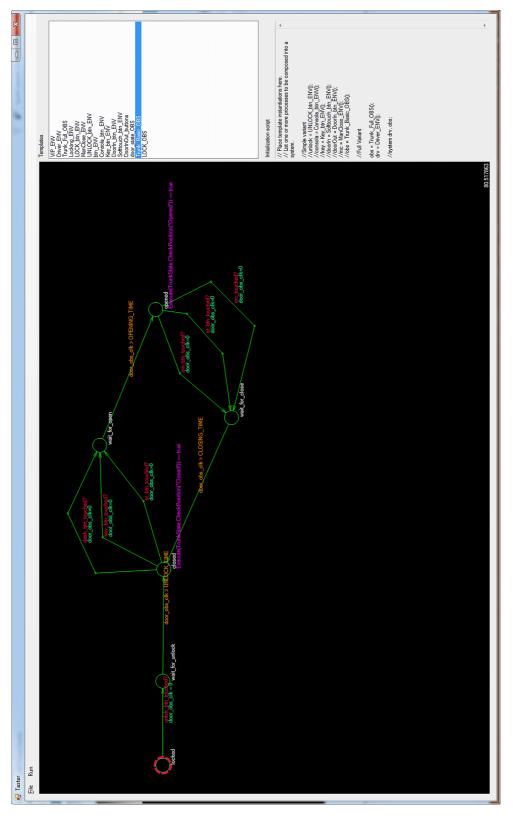

| C.3.         | Taster Runtime Screen95     |

| C.4          | Trace Viewer 96             |

## Chapter 1 Introduction

The length of a development cycle of new car models is continually decreasing. Aside of question if it is meaningful or not. Such situation makes a lot of pressure for research and development of appropriate validation, verification and testing methods, which would ensure the quality of final products (i.e. cars). The trend is noticeable for several decades and still it has not reached the peak. Rather, then it accelerates together with the expansion of a number of electronics systems equipped in vehicles [1].

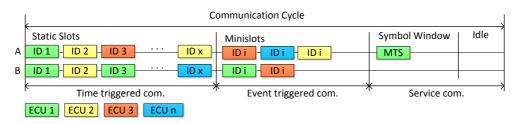

In modern vehicles, multiple communication buses are involved. Most common ones are Controller Area Network (CAN) and Local Interconnect Network (LIN). Due to theirs limitations, newer communication standards find more and more applications and are slowly replacing the old ones. One of those newer communication systems is called FlexRay [2]. The FlexRay communication system is intended for reliable data transfer with speed up to 10 Mb/s. Its intended application is x-by-wire systems (e.g. steer or brake by wire). More common real-world application is drive train and chassis stability control in high-class Audi, BMW, and Mercedes-Benz vehicles. The focus on reliability makes FlexRay much more complicated in comparison to other automotive communication systems. For example, FlexRay configuration set contains tens of parameters in comparison with several for CAN. The difference between intended and actual parameters can significantly affect system reliability. Some of the configuration parameters are easy to measure. For example, incorrect setup of communication cycle length will not allow integration into running communication or, in the case of cold start node, the initialization of communication. A different situation occurs in the case of incorrect values of clock synchronization parameters. Under common conditions, the FlexRay communication can operate without any observable variance.

In connection with the area mentioned above, there is highly actual and exciting area of Model–Based Testing. Term Model–Based Testing (MBT) covers large research area, and its meaning can differ across disciplines. In this thesis, the MBT will be denoted a testing method based on an executable model. Much work was done on this field in past few decades [3]. Despite this, a significant number of challenges await for a solution. MBT technologies are not sufficiently widespread in automotive development. To help to MBT dissemination, it is necessary to continue with inventing new and adapting existing methods in a form meeting specific car industry requirements Deployment of an MBT oriented processes can solve multiple challenges in automotive electronics testing.

An integral part of the testing of an automotive electronics system is the Integration testing. It is a high–level function oriented examination. The purpose of this testing is to examine if newly developed Electronic Control Units (ECU) can work in a group as a distributed system. Moreover, many functions are not implemented only in single ECU. The Integration testing is essential for a tryout of such features. The MBT approach can address challenges such as the needful amount of human work, increase the test coverage or decrease time to test.

## Chapter 2 State of the Art

Passenger car manufacturers play a role of a system integrator today, as a substantial part of vehicle subsystems is supplied by their contractors. This is especially true for vehicle electronics, where particular ECUs are supplied by different manufacturers. Nevertheless, the ECUs have to seamlessly collaborate together. The ECUs collaboration utilizes vehicle communication network technologies like CAN, LIN or FlexRay, thus expected network functionality is vital for reliable and safe vehicle operation.

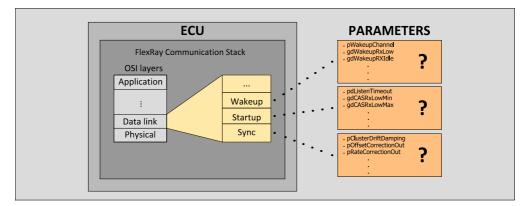

In the case of FlexRay ECU, communication behavior is affected by tens of parameters that must be set according to the vehicle manufacturer specification to ensure FlexRay cluster robustness and reliability. The vehicle manufacturer may not rely on ECU manufacturer declaration of conformity (in terms of correct parameter values) and has to measure the actual parametrization instead. This approach is common for CAN and LIN networks, where the number of critical parameters is lower, and measurement methods and instruments are widely available. As far as I know, such measurement methods are not available for the FlexRay technology at all.

## 2.1 FlexRay

Deployment of a communication system starts with a bus (technology) selection. In general, it requires the availability of proper testing and analysis tools and methods. A project continues with fundamental network design such as network topology, communication speed, and selection of basic parameters. Network design results in a complete parameter set (parameterization) for each network controller. The complexity of this parameterization depends on chosen communication technology. In the case of researched FlexRay, it is tens of parameters. This section maps work related to FlexRay configuration parameters evaluation.

Conformance of a FlexRay communication controller – part of System on a Chip with FlexRay protocol specification [2] is ensured by conformance testing specified by [4]. This document provides exact instructions for chip manufacturers how to test their newly implemented FlexRay devices. From the parameterization point of view, it defines couple of tests for each parameter. The objective of the tests is to examine if parameters influence communication controller behavior as it is defined in the standard.

A car manufacturer (system integrator) starts at best with tested FlexRay silicon chips. Verification of everything else is its own business. One of these responsibilities is validation if the parameters specified by a network designer conform with parameters programmed into registers of communication controllers. This task is usually done by some network analyzer connected to a communication bus. For well–adopted communication protocols these devices are commonly available on the market as development support tools.

#### 2.1.1 Of the Shelf Available Solutions

The section provides an overview of analysis tools and devices available on the market and their features. The list is not comprehensive due to the limited information provided on companies websites. The intention of this section is an outline of production solution capabilities.

The first representatives are Digital Oscilloscopes. Producers, such as Agilent Technologies, Tektronix or Teledyne LeCroy offer oscilloscopes with a frame decoding capability. Teledyne LeCroy probably provides the most advanced solution with its product called Trigger, Decode, Measure/Graph and Physical Layer (TDMP), which is capable of measuring some physical layer characteristics as propagation delay or jitter. No one can extract data link layer parameters.

The second group of representatives contains Specialized FlexRay Interfaces. For instance supplier of modular hardware for rapid prototyping, National Instruments offers two types of FlexRay interface card. As the label suggests, NI PXI-8517/2 designed for PCI eXtensions for Instrumentation (PXI) platforms and NI PCI-8517/2 is for conventional PCI. Programming resources are unified in NI-XNET driver. Application development is possible in LabView or ANCI C/C++ environment. The simple FIBEX editor is also included under the name Database Editor. The platform provides a flexible environment for high-level tests implementation. Low-level features necessary for parameter evaluation are not accessible.

From the list of specialized bus tools manufacturers for the automotive Industry, Eberspächer, and Vector were selected. Eberspächer Electronics portfolio contains hardware interfaces e.g. FlexCard USB and FlexCard PMC II. The difference is in a number of physical interfaces and its combination – FlexRay, CAN/CAN FD, Ethernet. There is no difference in analysys capabilities related to this work. Hardware is based on Bosch E–Ray IP core. The analysis is possible by Caromee software. In product manual is stated capability to display of unspecified synchronization information. The benefit of Eberspächer software is multivendor hardware support including Vector or National Instruments.

Vector Informatik GmbH is state of the Art company in automotive communication systems development support tools. Vector offers several FlexRay network interfaces which differ on a number of channels and PC connection type. One of the highest spec options, VN8900 is available in our department, and it can be used for the thesis purposes. Vector interfaces are based on same Bosch E–Ray IP core as Eberspächer products. Available analysis software is CANoe. Vector also provides FIBEX editor with some useful advanced functionality like parameters constraints check. The CANoe can show some parameters such as an actual value of rate and offset correction. Features can be extended by CAPL scripting.

Of the shelf available solutions can be summarized in following way. Large variety of FlexRay development support tools products is available on the market. Many of them support active bus transmission to provide synchronization node ability. Tools are usually connected with complex software environment. Bundled features are frequently extensible by scripting or programming. Nevertheless, capabilities are oriented to the application layer of International Organization for Standardization (ISO) / Open Systems Interconnection (OSI). Configuration parameters evaluation is data link layer problem. It requires ability to influencing of frame transmission e.g. transmit time variation. This kind of features no one of available devices can offer.

#### 2.1.2 Related Work

The growing complexity of automotive embedded systems requires new measurement and validation techniques [5]. The similar research focused on other vehicle distributed systems (mostly the CAN) was conducted in the past, e.g. in [6]. The CAN interface configuration is much simpler than for the FlexRay, since only a few parameters are used, such as time quantum, a length of particular bit segments and synchronization jump width. One parameter, in particular, is critical for the ECU with CAN interface deployment – the sample point position within the bit time. The risk of incorrect setting and the measurement method was described in [6].

Book [7] is an overview of Time-Triggered Communication Systems. It is not only focused on FlexRay, but also other Time-Triggered procools are discussed with their pros and cons. An example might be Time-Triggered variants of CAN (TTCAN) and Ethernet (TTEthernet). Remarkable is the description of core Time-Triggered Communication principles. In the context of this work clock synchronization study in section [8] can be helpful. Some general verification recommendations are also mentioned in [9].

Authors of [10] have focused on the extraction of FlexRay cluster global parameters. Their primary goal was to develop an FPGA device with the capability of automated parameters identification from ongoing FlexRay communication. The solution is based on passive bus monitoring. A subset of Global parameters marked with g prefix in FlexRay standard is investigated. Analysys start with bitrate detection for proper sampling frequency selection. Consequently, duration of communication segments is extracted. Direct measurements, as well as calculations using protocol constraint, are performed. The work can be viewed as automation of Time Division Multiple Access (TDMA) constraints identification using an oscilloscope. Clock synchronization related parameters are not investigated under this work.

Paper [11] is also focused on global cluster communication parameters. The motivation for configuration parameters evaluation is discussed in details. Also, it is discussed in context of intended application – automotive safety–critical control systems. The parameter set is analyzed and divided into three classes according to its scope. Similar to paper described in the previous paragraph, the approach is based on passive bus observation. Experimental results using five different network setups are shown. Implementation of a health–monitoring node used for measurement is not covered in many details. The impact of bus traffic density to parameter identification is presented. Clock synchronization related parameters are categorized in parameter set analysis, but no experimental results are included.

In summary works [10] and [11] targets to extraction of FlexRay cluster global parameters. They rely on the passive bus communication monitoring approach only. The limitation of this approach is its inability to reveal the values of all parameters, especially the local node–specific parameters that define node–specific behavior within the wakeup, startup and synchronization. These parameters apply to boundary conditions that are not usually reached during normal operation.

Work [12] studies the behaviour of local oscillators used as a clock source in individual FlexRay nodes. FlexRay specification allows usage of the ordinary crystal oscillator with deviation from nominal frequency up to 1500 *ppm*. Autors present the interesting method for local clock frequency measurement. The method works remotely using the connection to a FlexRay bus. In comparison with the above–mentioned works, it

requires active bus transmission to influence clock synchronization algorithm. Despite the paper is not focused directly on configuration parameters measurement, it shows the interesting method for revealing actual value of offset correction in a FlexRay node. Knowledge of actual offset correction is basis for evaluation of pOffsetCorrectionOut parameter – offset correction limit.

#### 2.1.3 Risk of Incorrect Parameterization

A significant FlexRay node parameter is *pRateCorrectionOut*, which determines the maximal possible rate correction value the node is allowed to apply. Let's consider the following situation: the desired value of *pRateCorrectionOut* parameter in ECU specification is 601  $\mu$ T (unit Microtick defined in FlexRay standard and abbreviated  $\mu$ T ), which is the maximal value for communication speed 10 Mb/s and communication cycle length 5 ms. This value allows the communication controller to correct maximal permitted oscillator deviation, which is defined by standard [2] as 1500 ppm of oscillator's nominal frequency.

Let us assume that in the supplier delivered ECU the configured *pRateCorrectionOut* value is not 601, but only 300  $\mu$ T instead. Such a violation of node parameter specification would not influence the ECU's behaviour under most conditions, unless the local oscillator's frequency reaches a deviation higher than 750 ppm from the nominal value (more precisely from the cluster average value). At this moment the ECU ends communication and goes to the halt state, while it would continue operating with correct parametrization. Considering a crystal oscillator natural behaviour [13], this probably happens after a long time (several years) due to crystal aging in combination with high or low temperatures [14]. To detect this kind of specification breach special testing methods are needed, allowing the car manufacturer to ask the ECU supplier to fix the parametrization during the pre–production phase.

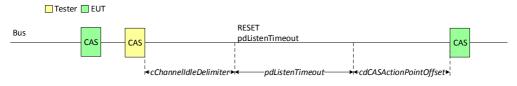

A wrong value of pdListenTimout is another example of a manufacturer specification breach. The pdListenTimeout value specifies the time spent in a coldstart listen phase. According to specification [2] the pdListenTimeout value has to be calculated according equation (2.1):

$pdListenTimeout[\mu T] = 2*(pMicroPerCycle[\mu T] + pRateCorrectionOut[\mu T]) (2.1)$

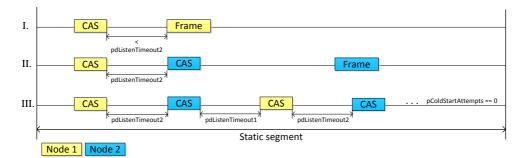

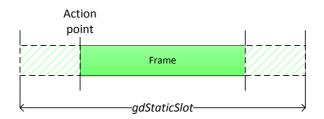

Depending on the communication cycle schedule, lower as well as higher parameter values can cause problems with FlexRay cluster startup (e.g. leading coldstart node change or startup phase extension). Three possible scenarios are shown in Figure 2.1. All cases consider two coldstart nodes in a communication network.

The first case labelled I. shows a situation when the gap between Collision Avoidance Symbol (CAS) and the startup frame in a static slot (actual pdListenTimeout of node 2) is shorter than the required pdListenTimeout. In this case the startup behaviour of the cluster is not seriously affected. The second scenario shows the change of leading coldstart node. The pdListenTimeout timer of node 2 expires before node 1 sends its first startup frame (assigned key slot is later in static segment of communication cycle) and cluster startup is thus delayed. Case III. means that pdListenTimeout parameters in both nodes are too small; the nodes are alternating in coldstart leading and the

Figure 2.1. Effects of wrong pdListenTimeout value

startup delay is significant. To prevent all these problems, an evaluation of the actual value of the pdListenTimeout parameter is necessary.

The examples presented above show that the problems originating from incorrect ECU parametrization may occur later (caused by components ageing), under specific operating conditions (e.g. extreme temperature), under the spare part change or under the simultaneous influence of aforementioned effects. This kind of problem is hard to detect because of its sporadic nature. Evaluation of configuration parameters can dramatically increase confidence in the fault–free operation of FlexRay networks during the car life cycle.

### 2.2 Integration Testing and MBT

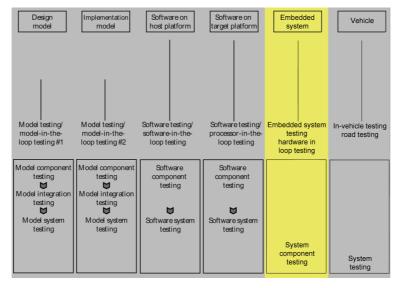

Integration testing is widely used term covering various methods and processes in testing of software or electronic systems. In general, Integration testing denotes a phase after some parts (modules, components, code fragments, etc.) are joined. Further in this work by name Integration testing is denoted Automotive Integration testing as described below. Integration testing phase is placed close to the end of a new car electronic system development. An example of a development process with corresponding testing methods is depicted in the Figure 2.2. Application area of this work is marked by a yellow background. By nature it is a high level, function oriented testing of almost finished car electronics system or part of that system (a network of ECUs). The objective of the testing is to examine whether the whole system is able to operate in synergy and functions distributed over multiple ECUs work as expected. Automotive Integration testing is being performed on Hardware–in–the–Loop basis on a testbed. An industrial experience says that implementation of test sequences is usually done by test engineers. In general, this area has great potential for research and real word application of MBT solutions.

Test management, development, and execution are usually performed by some software tool. For the purpose of this work EXAM is considered. It is complex testing tool co-developed and used by Volkswagen AG. Graphical user interface provides the environment for individual test cases development. A test case is implemented as sequences or activity diagrams. These test cases are organized in test suites and test campaigns. The test suite is executed by test runner in a sequence of test cases. Finally test results are stored in the database for various assessments.

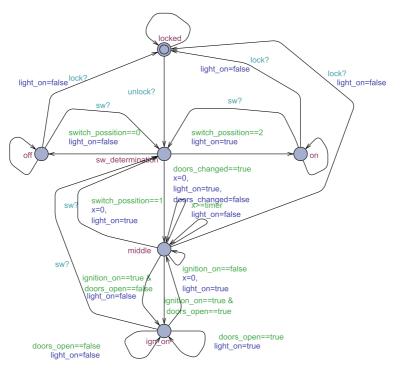

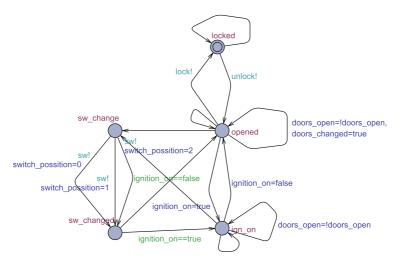

Current test suites are mostly implemented using typical driver use cases. Time to test of complex systems is limited and thus number of uncovered situations in test suites is significant. Considered systems have multiple inputs and outputs and particular function behavior is typically constrained by other distributed system parts. I.e. behavior of car inner light depends on the state of doors locking, ignition state, switch position, etc. Frequently basic and low-end functionality test cases are preferred in test suites from high-end variants.

Figure 2.2. An automotive distributed system development process [15]

#### 2.2.1 Weaknesses of Traditional Approach

Manual design and implementation of test cases is very laborious and demanding task. The quality of this approach strongly depends on the quality of test engineers work. Like every human activity, it is prone to errors. Good test rule policy and its enforcement can be beneficial. Weaknesses of manual test case design and implementation can be viewed in a similar way as problems in ordinary coding. Produced code can be great, but there is no guarantee. There are numerous coding as well as software projects management recommendation which can help to ensure the desired level of quality. However, the result is in hands of coding/testing team.

Specifically, in intended Integration testing, supplementary cons are identifiable. One of them is fixation to the behavior of an average driver. It means that test cases mostly acts like the average driver and some less common, but still, valid scenarios remain uncovered. Another con example – a Modern car is offered in various trim levels. Some optional extras can be selected across defined trim levels. It creates a significant number of combinations. The manual combination of test cases covering particular features is practically impossible. Last but not least during a vehicle life cycle, electronics system is often changed. Every change requires an update to a test suite to fit exact system specification. Maintenance of test suites is also very demanding and error prone task.

#### 2.2.2 Terminology

Terminology in fields related to this thesis – Integration testing (defined in 2.2) and Model–Based testing might be confusing. Differences in the meaning of individual

terms are caused by various aspects. One of these aspects is liveliness of the scientific areas. Especially the domain of MBT is only a few tens of years old, and research is still active. Another reason is in different conventions in target application area. An example is testing in software development and testing in the automotive industry. To make the work clearly understandable, used terminology is briefly described.

**Model–based testing (MBT)** covers very extensive research area. The reason of area extensiveness is that in general, it is possible to classify as Model–Based every test method, which using some model (including non–executable or mental model). For the purpose of this work, a testing method is denoted as Model–Based if the method directly uses some executable model to performing a testing.

**System under Test (SUT)** is a system which is the object of a Testing. In this thesis primarily a car electronics system or its part.

**Testing** is an interaction with some system. The purpose of the testing activity is to achieve some level of confidence that behavior of the system under test meets the defined objectives. A reasonable definition of test objective is essential for successful test implementation. Demonstration of general test objective is conformance testing. The goal is to find out if the behavior of the system under test is in compliance with system specification.

**Hardware-in-the-Loop (HIL)** is the testing method with roots in aircraft industry suitable for testing complex electronic control systems like an electronic control unit or whole electronics system. The object of testing is an embedded system, but sensors and actuators are simulated or stimulated by testbed facilities. SUT works identically as in its final deployment, but interaction with the environment is controlled by some test equipment.

**Reactive system** is a system which reacts to inputs from environment by producing some outputs. Reactive system are usually non-terminating. Behavior of this kind of systems can be non-deterministic and it is usually based on internal system state. For this reason, testing of reactive systems is more challenging in comparison to transformative systems. Transformative systems deterministically produce output after input and some portion of time.

Real-Time Systems is system with responds to an event within defined time window.

**Test Objective** or test purpose is definition what a test case should test. Test objective can be very different from a formal property, e.g. system does not contain deadlock, to some performance or durability criterion of an SUT.

**Test Case** is sequence of steps to examine some SUT property or properties. It can be viewed as implementation of one or more test objectives.

Test Suite is a collection of test cases.

**Test Campaign** denotes higher level entity containing an arbitrary number of test suites. It is used by some test tools to improve test management options.

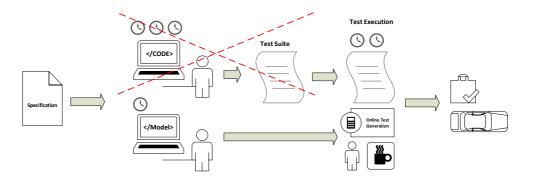

**Offline Testing** means the test case or whole test suite is generated before it is executed. Test generation and test execution are strictly separated. The process is similar to manual test case development when tester designs and implements test case. Afterward, test case is executed on a target platform.

**Online Testing** In opposite to offline testing the border between test generation and test execution is not sharp. Online testing tool interacts with SUT in command and

response way. This approach allows reacting to SUT non–deterministic behavior. The technique is especially suitable for slowly interacting system, e.g. car and driver.

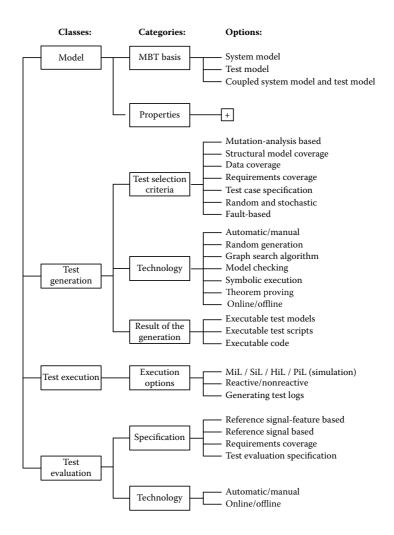

### 2.2.3 Taxonomy

World of MBT can be categorized in different ways. A possible taxonomy suitable to thesis goals is depicted in Figure 2.3. Firstly it divides MBT into four classes which correspond with consequent steps during testing. Each class is subdivided into multiple categories and options. Titles used for options designate specific methods and technologies. Only this last column refers to specific technology. Classes and categories have a general meaning.

Class models are distinguished on the basis of model purpose and its relation to SUT. Model directly related to the SUT is considered as System Model. An abstract model for deriving test cases only is classified as Test Model. As usual the most common in practice is a combined approach.

With some model, three consequent steps (classes) can be performed. Performing testing in MBT way does not necessarily contain all depicted phases. Test generation class covers test selection (objective). The second part of the class is technology cappable to achieve desired test objective. Moreover, final step is rank test generation by a format of obtained results.

Third class categorizes MBT according to execution options. It differentiates what is tested – Model, Software, Hardware or Processor. The ordinary testing process can start with testing of SUT model and continues until it is possible to test final hardware with software. Systems related to this thesis are tested after hardware and software are available. No model or processor in the loop simulation is performed.

Test evaluation refers different approaches to the test result processing. In the simplest way it can be done manually – only test input is generated. In presented case, a model providing test oracle capability is supposed.

#### 2.2.4 Embedded System Modeling

There are numerous options for modeling of automotive embedded systems. The researched system class has two specific features. It is Real–Time and Reactive behavior. Selected model language should be able to capture these attributes. These requirements limit the number of applicable formalisms, but the list of possible languages still contains at least hundreds of options. E.g. paper [17] present a survey on Timed Automaton (TA), and it contains almost eighty variants. The problem is not lack of suitable formalism, rather the opposite – too many options. Enumeration can begin with process algebras like Communicating Sequential Processes (CSP). As the name suggest, the systems are represented by process and interaction between them. Properties can be specified by some modal temporal logic. A known example is Linear Temporal Logic (LTL). The problem of this theoretical description possibilities is that they are not well accepted by practitioners. Graphical representation based on an Finite–state machine (FSM) is much better adopted to a wider audience. Some of them significant in the field of interest are outlined in rest of the section.

#### Petri net

The first example of an embedded system representation is Petri net. The net consists of places, arcs, and transitions. Arcs can be coupled with weights. There is a huge number of Petri net variants. One of the Petri net definition given by [18], is:

Figure 2.3. Overview of the taxonomy for Model–Based Testing[16]

- Petri net is quintuple  $(S, T, F, M_0, W)$  where

- S is a finite set of places.

- $\bullet$  T is a finite set of transitions.

- F is a finite set of arcs  $F \subseteq (S \times T) \cup (T \times S)$ .

- $M_0: S \to \mathbb{N}$  is initial marking, where a place  $s \in S$  contains  $n \in \mathbb{N}$  dots.

- $W : F \to \mathbb{N}^+$  is set of arc weights, where for every  $f \in F$  weight is  $n \in \mathbb{N}^+$ . Weight denotes how many dots are consumed by a transition, or it is a count of dots produced in output places.

Petri net according to the definition can also be viewed as weighted bipartite graph. Execution is nondeterministic and depends on marking. Firstly it is necessary to fulfill a minimal number of dots(tokens) on some transition. The enabled transition can be consequently fired. According to weights, tokens are consumed by a transition, and an

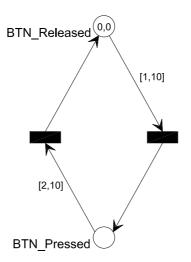

Figure 2.4. PN example – Button model

arbitrary number of tokens is inserted into output place. A timed–arc Petri net button model is depicted in Figure 2.4.

#### **Timed Automata**

Theory of timed automata was originally published by Alur and Dill [19]. Actually the term timed automata usually means slightly modified version called Timed Safety Automata [20] which uses local invariant conditions to ensure automaton progress. Formal definition of a single timed automaton, given by [21], is:

- A timed automaton A is a tuple  $A = (N, l_0, E, I)$  where

- N is a finite set of locations (or nodes),

- $l_0 \in N$  is an initial location,

- $E \in N \times \mathcal{B}(\mathcal{C}) \times \Sigma \times 2^{\mathcal{C}} \times N$  is the set of edges and

- $I: N \longrightarrow \mathcal{B}(\mathcal{C})$  assigns invariants to locations

- We shall write  $l \xrightarrow{g,a,r} l'$  when  $\langle l, g, a, r, l' \rangle \in E$

Local invariant is constraint in form  $x < n, x \le n$  where n is natural number.

Informally, the timed automaton is an oriented graph which contains states and transitions. One of the states is called initial. Transitions are labeled by guards which enable relevant transition. One of the key concepts of timed automata theory is parallel composition of individual automatons to the network of timed automata. The theoretical background for this operation provides parallel composition operator know from CSP. Timed Safely Automata are implemented e.g. in UPPAAL [22] tool. Comparison of TA and Petri net (PN) is provided by [23].

#### UML

In comparison to formalisms presented above, Unified Modeling Language (UML) is a bit more complex. TA and PN are compact modeling systems with strong mathematical background. UML was born for practice. UML application is not limited to model a

system behavior, but it is capable of capturing most of the aspects of a software system including business processes. MBT tools usually implement a subset of UML. I.e. system structure is expressed by UML block diagram, and system behavior is modeled by FSM. With the presumption of usage of an FSM variant for behavior modeling, it is UML as MBT basis very similar to TA.

#### 2.2.5 Test Selection Criteria

An integral part of a test generation are test selection criteria. It is specification what the generated cases should or should not contain. Definition of reasonable test criteria is work for a test engineer. It is similar to manual test case design, just in the more general way. Unfortunately it is not possible to select single best test selection criteria for any SUT. Based on the work [24] test selection criteria suitable for transition based models is overviewed. Also, test generation can be directly influenced by form of an environment model.

#### Structural Model Coverage Criteria

They use model structure to expresses test objectives. In case of FSM based models criteria are in form which nodes and edges should be incorporated in test case. Obviously, full node or full edge coverage are very commons criteria. Another criterion is a coverage of all automaton cycles. Instead of full/all entities a certain level of coverage can be chosen. E.g. test case has to cover at least 70% of edges. As not so straightforward options the isomorphism–checking methods [25] can be mentioned. Similarly to code testing, Modified condition/decision coverage (MC/DC) can be applied to an FSM.

#### Data Coverage Criteria

Industrial strength formalism works with variables as well as complex data structures. It makes case structural coverage criteria hardly applicable. Due to state space magnitude, it is necessary to pick significant variable values. Data coverage criteria are based on some partition of value space into classes or intervals of boundary values. As a representative Classification Tree Method [26] is listed.

#### Fault-based Criteria

Evaluation of test cases or entire suites bases on effectiveness to reveal pre–defined bugs in SUT. Instead of model oriented metrics – e.g. node coverage is Fault–based criteria expressed as a count of revealed injected bugs to an SUT. A well–known member of this group is Mutation Testing [27]. The key idea is to test a test suite by small variation (a mutant) of SUT implementation. A mutation example is replacing operator such as < to <=. Same tests are executed over original and mutated SUT. The significant disadvantage of Mutation Testing is a required access to an SUT code, which is not possible in many cases.

#### 2.2.6 Test Generation

This is a first phase of the testing process automation. After the model development and specification of test selection criteria is time to release the power of MBT. With all necessary information in machine–readable form, rest of testing process can be completely automated. Suitable algorithms run over the model and generate test cases which fulfill given criteria.

#### Graph search techniques

Taking into account graph nature of many modeling formalisms, application of graph search algorithms act naturally. Graph traversing is possible in various ways. Some suitable for MBT are for instance random search, Breadth-first search (BFS), and Depth-first search (DFS) respectively its modified versions according to the used modeling formalism. Model semantics bring some constraint into the exploration. For example, it is not possible to pick any edge if some enabling condition (guard) is not fulfilled. Optimized test generation using shortest path algorithms is also widely used.

#### Symbolic execution

Instead of specific (single) variable values, a model is executed with a valuation of variables by a set of values (intervals). Alternatively, another analogy with fixed-step discrete simulation, symbolic execution is like a discrete simulation for multiple steps at one time. Model is executed using constraints instead actual values. The result of execution are symbolic test cases. One symbolic test case can represent a group of real test cases. Symbolic as well as real test cases have to fulfill test selection criteria. Instantiation of symbolic to real test cases is done by a sampling of given intervals. The examples of this approach from TA world are Region and Zone graphs [17][20].

#### Model Checking

MC or property checking is decision making if a system meets given property (deadlock-free, all states are reachable). As a side effect, model checkers can work as test generators. In this case, the test selection criterion is expressed as reachability property. The idea of usage of a model checker to produce test cases for a real system seems very logical as there are a lot of high-level Model Checker (MC) tools and methods [28]. Also, a synergy of model formal analysis with testing of its implementation can be beneficial [29]. Deployment of UPPAAL MC engine for test case generation was objective of the dissertation theses [30][31].

#### 2.2.7 Existing Tools

#### TRON

Uppaal TRON (UPPAAL for Testing Realtime systems ONline) is MBT tool developed as a part of Marius Mikucionis Ph.D. project [31]. The tool is available from webpage [32]. TRON is intended to online conformance testing of system specified by timed automata network. The modeling language is the same for both SUT and environment models. Models are explored using UPPAAL model checking engine. Inputs for testing are choosen randomly. Test objective is specified by environment model – fully permissive model performs full conformance test. For real SUT connection multiple examples how to implement test adapter are provided. Presentation [33] provides further information.

#### CoVer

Uppaal CoVer is a command line extension [34] for offline test generation based on UPPAAL model checking engine. Test suite generation is controlable by Observer and Property files. Syntax is described in Backus–Naur Form. Format of abstract test cases can be modified by Extensible Markup Language (XML) config file. Model coverage criteria are specified by observer automata [35]. Tool generates abstract test suite which has to be converted to an executable form. Detailed CoVer description can be found in Anders Hessel Ph.D. thesis [30].

#### Yggdrasil

Simple offline test–case generation tool integrated in UPPAAL since version 4.1.19. Yggdrasil derives traces with edge coverage criteria. It is necessary to fulfill some conditions (deterministic, deadlock free models ...), otherwise tests might not be generated. To make generated traces executable it is possible to add a test code into the model. Test code can be added to nodes and edges of the model.

Features:

- Offline test generation

- Depth or Breadth search order selection

- Load a trace into UPPAAL simulator

- Export of outputs to a file

#### 2.2.8 Hardware-in-the-Loop

Testing can be performed from a very beginning stage of the development as it is shown in Figure 2.2. Whichever is available it can be distinguished as Model–in–the– loop, Software–in–the–loop, Processor–in–the–loop and finally Hardware–in–the–loop. Integration testing works with pre–production versions of an electronic car system. The intelligent part of this system is usually implemented as electronic units called an ECU. ECU is Microcontroller Unit (MCU) controlled module with various input and output types. Individual ECUs are interconnected by a communication link.

The main purpose of Hardware–in–the–loop (HIL) facilities is to handle SUT inputs and monitor its outputs. It creates the interface between real hardware and software testing tools. The method serves inputs to an SUT and observes its reaction by observing outputs. Identically as testing of a computer program, but Inputs/Outputs (I/O) are physical. In–the–loop postfix indicates cyclic nature of the process. Input values generation, as well as the evaluation between right and wrong outputs, is the task of test generator.

Working in desired time window is required since investigated systems have Real-time properties. It means that a new input has to be served within specified time and similarly output is valid only within a given time interval. Handling time constraints is also dedicated to an HIL platform. Simulation of complex subsystems such as sensors, actuators, and communication interfaces is frequently necessary. To conclude the HIL method allows performing MBT with real hardware.

HIL test execution has its specifics [36]. The mapping between abstract test cases to the real ones have to be solved. For instance in a step of an abstract test case is input value specified by equivalence class. However, in execution time is necessary to choose the certain value. In a simplified example, it can be done by selecting a random value from given interval. Instantiation of test sequences is usually done by a software module called test adapter. The extensiveness of the adapter depends on input and output formats compatibility.

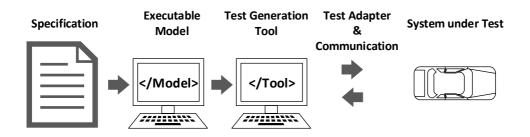

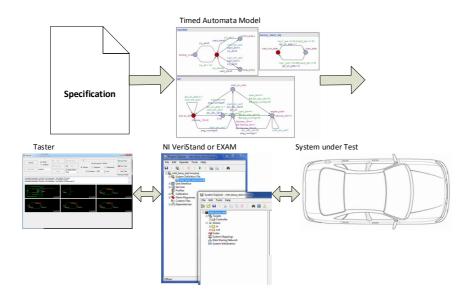

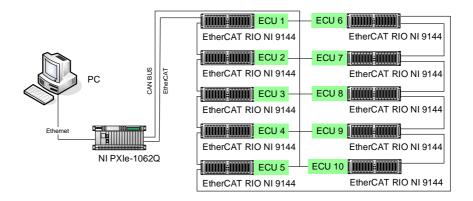

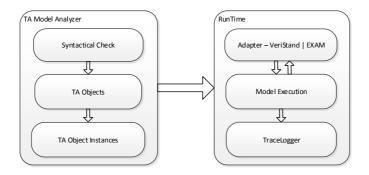

#### 2.2.9 Related Work