# Czech Technical University in Prague Faculty of Electrical Engineering

# **Doctoral Thesis**

## Czech Technical University in Prague

# Faculty of Electrical Engineering Department of Electric Power Engineering

# HVDC circuit breakers modeling in multiterminal grids

**Doctoral Thesis**

# Alexander Yanushkevich

Prague, May 2017

Ph.D. Programme: Electrical Engineering and Information Technology Branch of study: Electric Power Engineering (3907V001)

Supervisor: Prof. Ing. Josef Tlustý, CSc.

# Acknowledgement

I would like to thank my supervisor Prof. Ing. Josef Tlustý, CSc. for guidance during my studies and in personal development. Additionally, like to show my appreciation to my university colleagues Jan Švec, RadekProcházka, Petr Mareček, Jan Kyncl and work ex-colleagues Rene Smeets, Theo Bosma, NadewBelda and Rick Scharrenberg for help and cooperation in research activities. My biggest appreciation is to my family for support in all the activities and challenges that I've taken in my life.

# **Declaration**

Hereby I declare that the thesis is the result of my own work done independently and all the references in the work are appropriately cited and listed in the list of references.

In Prague, 31.5.2017

Alexander Yanushkevich

# **Abstract**

Transition towards sustainable energy systems lead to transformation of the existing electrical power grids. One of the key enabling technologies for this transformation is high voltage direct current (HVDC) technology that has range of advantages comparing to today's AC systems. One of the main obstacles for HVDC grids implementation is lack of robust and reliable protection systems for DC fault clearing. HVDC circuit breaker is a crucial component for DC fault clearing, however, performance of this new technology in multiterminal HVDC grids is not fully understood. Discussed nowadays innovative hybrid circuit breaker solution, that combines mechanical switches and power electronic components, is very different from AC circuit breaker technology. Application of power electronic components for DC fault clearing puts higher requirements on protection system where approach used in AC systems may not be optimal. Alternative multifeeder protection solution is proposed and investigated in the thesis. This solution brings benefitofthe protection system cost reduction and high speed fault clearing capability. In this thesis methods for HVDC components, including converter and circuit breakers, modelling are explained. Developed models are crucial for further protection systems development and optimisation. These models are used for performance investigation of the HVDC circuit breakers in multiterminal HVDC grids, radial and meshed. Results of the simulations performed in the thesis conclude into requirements for protection system and HVDC circuit breakers design.

# **Anotace**

Přechod směrem k udržitelným energetickým systémům vede k transformaci stávajících elektrických rozvodných sítí. Jednou z klíčových technologií pro tuto transformaci je stejnosměrný přenos vysokého napětí (HVDC). Tato technologie má řadu výhod v porovnání s dnešními AC systémy. Jednou z hlavních překážek při realizaci HVDC sítí je neexistencedostatečně robustního a spolehlivého systémuchráněníproti DC poruchám. Jedním ze základních prvků ochrany proti DC poruchám je HVDC vypínač. Chování této nové technologie však není v sítích s více terminály (Multiterminal) dosud plně objasněno. V dnešní době často diskutované inovativní hybridní řešení HVDC vypínačů, které kombinuje mechanické spínače a výkonové elektronické součástky, je velmi odlišné od technologií AC vypínačů. Aplikace výkonových elektronických součástek pro odstranění DC poruch klade vyšší nároky na systém ochrany, kde nemusí být přístup používaný v AC systémech optimální. V rámci této práce bylo navrženo a prozkoumáno alternativní řešení vícevodičové ochrany. Toto řešení přináší výhodu nákladů na systém chránění proti DC poruchámpři podobě snížení V práci zachovánívysoké rychlostijejich odstranění. isou vysvětlenymetodymodelováníHVDC komponent, včetně měničů a vypínačů. Vyvinuté modely jsou rozhodující pro další vývoj a optimalizaci systémů chránění. Vypracované modely jsou použitypři vyšetřováníchování HVDC vypínačův radiálních a mřížových víceterminálových sítích. Na základě výsledků provedených simulací jsou doporučeny požadavky použitelné pro návrh systému chránění a HVDC vypínačů.

# **Table of Contents**

| 1. | Introduction3                           |                                               |                                                |    |  |  |

|----|-----------------------------------------|-----------------------------------------------|------------------------------------------------|----|--|--|

|    | 1.1                                     | Drivers                                       | s towards HVDC grid                            | ∠  |  |  |

|    | 1.2                                     | HVDC                                          | Converter technology                           | 8  |  |  |

|    |                                         | 1.2.1                                         | VSC system design                              | 10 |  |  |

|    |                                         | 1.2.2                                         | VSC modules design                             | 10 |  |  |

|    |                                         | 1.2.3                                         | VSC converter design                           | 12 |  |  |

|    |                                         | 1.2.4                                         | VSC control                                    | 13 |  |  |

|    |                                         | 1.2.5                                         | Configurations of HVDC systems                 | 14 |  |  |

| 2. | Current status and aims of the thesis   |                                               |                                                |    |  |  |

|    | 2.1 DC fault transients in HVDC systems |                                               |                                                |    |  |  |

|    | 2.2                                     | DC fau                                        | ılt protection systems                         | 19 |  |  |

|    | 2.3                                     | HVDC                                          | circuit breakers                               | 20 |  |  |

|    | 2.4                                     | Aims c                                        | of the thesis                                  | 24 |  |  |

| 3. | Wor                                     | king me                                       | thods                                          | 25 |  |  |

|    | 3.1                                     | HVDC                                          | systems modelling                              | 25 |  |  |

|    |                                         | 3.1.1                                         | Converter model for DC fault studies           | 25 |  |  |

|    |                                         | 3.1.2                                         | Model verification                             | 26 |  |  |

|    | 3.2                                     | HVDC                                          | HVDC circuit breaker modelling                 |    |  |  |

|    |                                         | 3.2.1                                         | Hybrid circuit breaker                         | 28 |  |  |

|    |                                         | 3.2.2                                         | Current commutation                            | 29 |  |  |

|    |                                         | 3.2.3                                         | Energy absorption                              | 30 |  |  |

|    | 3.3                                     | Hybrid                                        | Power Electronic HVDC Circuit Breaker type I   | 32 |  |  |

|    | 3.4                                     | Hybrid                                        | Power Electronic HVDC Circuit Breaker type II  | 34 |  |  |

|    | 3.5                                     | Hybrid                                        | Power Electronic HVDC Circuit Breaker type III | 37 |  |  |

|    | 3.6                                     | Hybrid                                        | Power Electronic HVDC Circuit Breaker type IV  | 39 |  |  |

|    | 3.7                                     | Active Oscillation HVDC Circuit Breaker model |                                                |    |  |  |

|    | 3.8 Multifeeder circuit breaker         |                                               |                                                |    |  |  |

|    |                                         | 3.8.1                                         | Auxiliary switch                               | 46 |  |  |

|    |                                         | 3.8.2                                         | Protection system                              | 48 |  |  |

| 4.                        | Results |                                                     |                                                      |    |  |  |

|---------------------------|---------|-----------------------------------------------------|------------------------------------------------------|----|--|--|

|                           | 4.1     | DC fa                                               | ult conditions                                       | 51 |  |  |

|                           |         | 4.1.1                                               | Effect of VSC type                                   | 52 |  |  |

|                           |         | 4.1.2                                               | Effect of the transmission media                     | 53 |  |  |

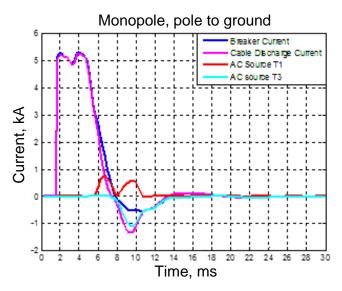

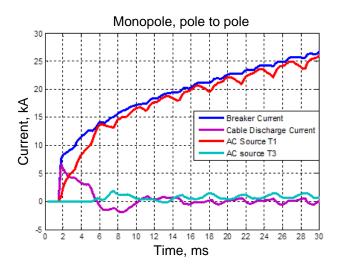

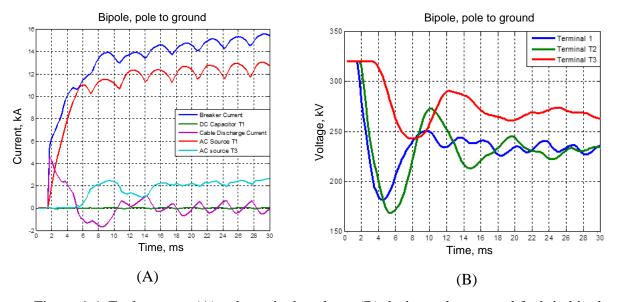

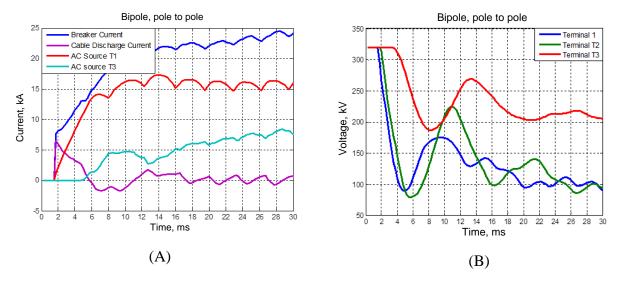

|                           |         | 4.1.3                                               | Effect of the system configuration.                  | 53 |  |  |

|                           | 4.2     | Circui                                              | t breaker performance in a radial grid               | 57 |  |  |

|                           |         | 4.2.1                                               | Hybrid Power Electronic Type I (HPE I)               | 57 |  |  |

|                           |         | 4.2.2                                               | Hybrid Power Electronic Type II (HPE II)             | 60 |  |  |

|                           |         | 4.2.3                                               | Hybrid Power Electronic Type III (HPE III)           | 62 |  |  |

|                           |         | 4.2.4                                               | Hybrid Power Electronic Type IV (HPE IV)             | 65 |  |  |

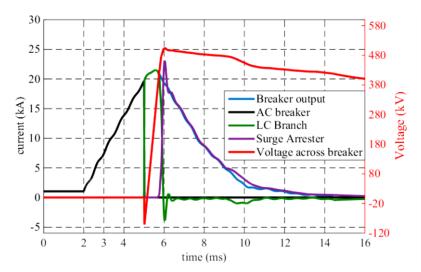

|                           |         | 4.2.5                                               | Active Oscillation HVDC Circuit Breaker              | 67 |  |  |

|                           |         | 4.2.6                                               | Results of performance                               | 69 |  |  |

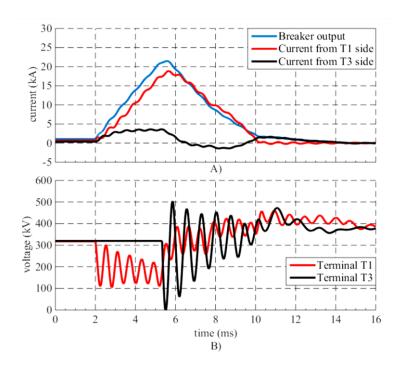

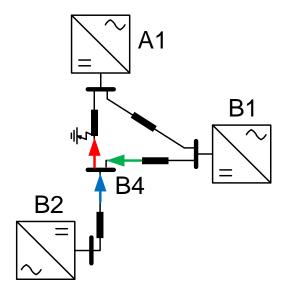

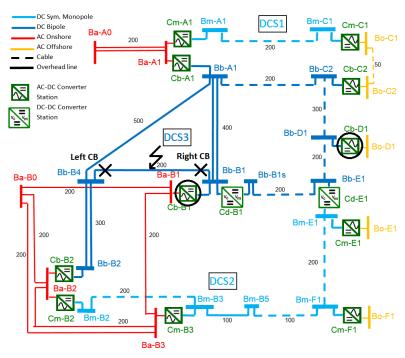

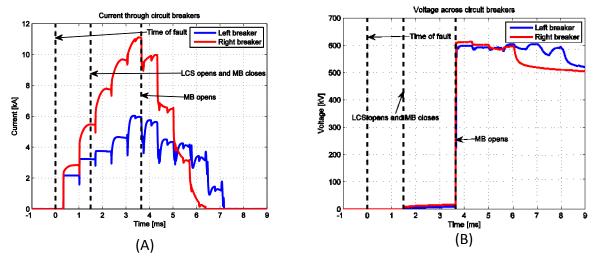

|                           | 4.3     | Multifeeder circuit breaker performance             |                                                      |    |  |  |

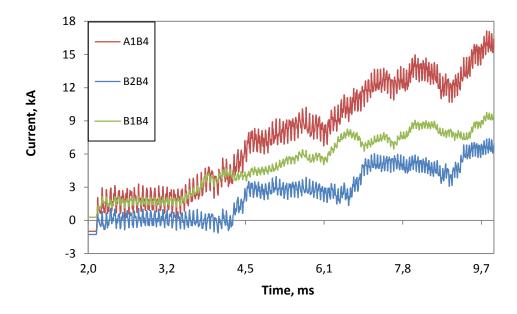

|                           |         | 4.3.1                                               | Fault current                                        | 71 |  |  |

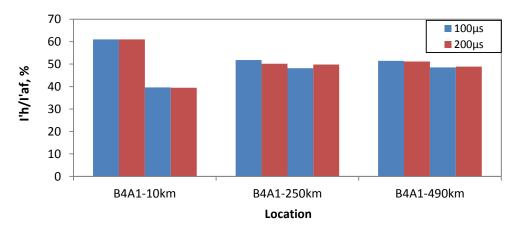

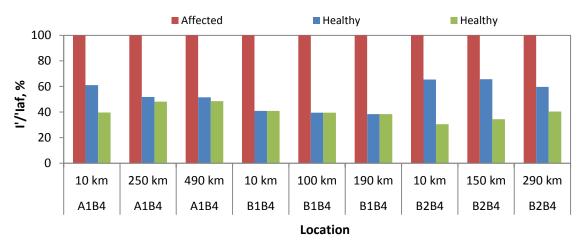

|                           |         | 4.3.2                                               | Protection system                                    | 71 |  |  |

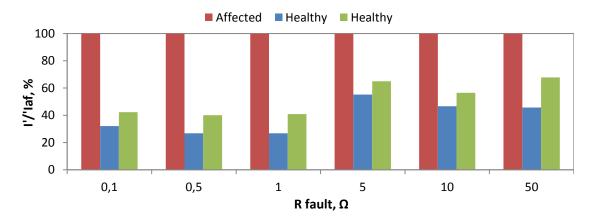

|                           |         | 4.3.3                                               | Circuit breaker design                               | 73 |  |  |

|                           | 4.4     | Circuit breaker performance in CIGRE Benchmark grid |                                                      |    |  |  |

|                           |         | 4.4.1                                               | Hybrid Power Electronic Type I (HPE I)               | 75 |  |  |

|                           |         | 4.4.2                                               | Hybrid Power Electronic Type II (HPE II)             | 77 |  |  |

|                           |         | 4.4.3                                               | Hybrid Power Electronic Type IV (HPE IV)             | 78 |  |  |

|                           |         | 4.4.4                                               | Comparison Performance of Different Circuit Breakers | 79 |  |  |

|                           | 4.5     | 4.5 Requirements for HVDC circuit breakers          |                                                      |    |  |  |

| Co                        | nclusi  | on and                                              | future work                                          | 83 |  |  |

| Ref                       | ferenc  | es                                                  |                                                      | 85 |  |  |

| Lis                       | t of pu | ublicatio                                           | ons                                                  | 88 |  |  |

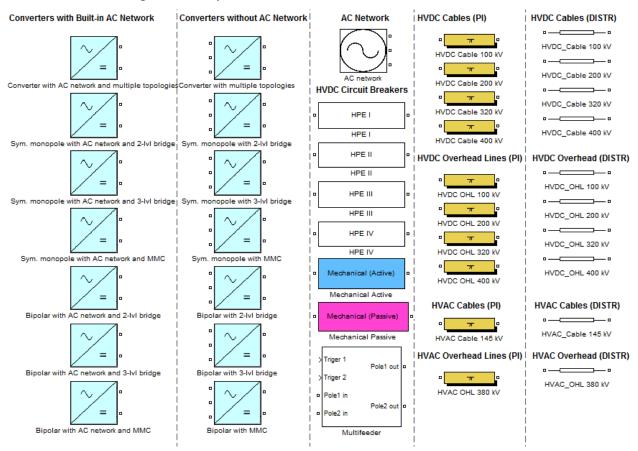

| Annex A – Models database |         |                                                     |                                                      |    |  |  |

| An                        | nex B   | – Arres                                             | ster model                                           | 90 |  |  |

| An                        | nex C   | - Ciore                                             | e benchmark HVDC grid                                | 91 |  |  |

# 1. Introduction

Transmission of bulk power over long and inter country lines has been seriously limited by system stability. Moreover, due to deregulated power market and large amount of decentralized generation in a meshed AC grid, an existing power system is becoming more complex. These limitations are triggering all sorts of problems and reliability issues in power systems. However, the recent advancement in power electronics has been pushing the boundary limit. As a result, the use of FACTS and HVDC devices has become growing in recent years. High voltage direct current (HVDC) technology has been considered as a viable alternative to AC systems for long distance power transmission and interconnection of power systems with different frequencies or networks which may not be synchronized. Besides, using fast DC power modulation implemented in a HVDC link's control system, the power oscillation in related AC power grids can be restrained timely, which is helpful to enhance the transient stability of the power system.

Moreover, the penetration of variable renewable energy sources in power systems around the globe has been increasing at an impressive rate in recent years. The EU aims at the 20-20-20 goals according to Energy and Climate Package one of which is the 20% share of renewable generations in the EU total consumption by 2020 and up to 30% in 2030. To deliver this energy to European consumers, it will require the development of a high capacity transmission system capable of delivering this energy to Europe's load centres.

The German transmission system, where implementation of renewable generation has been growing at the fastest rate, is facing challenges to maintain operation of the grid. At the same time as European grid is interconnected, problems in the German system affect grids in the neighbouring countries, like Czech Republic, Poland and the Netherlands, due to uncontrolled power flows.Implementation of the HVDC systems that have higher than HVAC transmission capacity in the same corridors and full power controllability can help to solve many problems existing today and upcoming in the future.

Plans for HVDC grids have been discussed in Europe and around the globe. Even first steps have been taken already by implementing small multiterminal systems. However, protection of an HVDC grid is considered as one of the main technical challenges for big system deployment. Protection system algorithms and prototypes of HVDC circuit breakers have been proposed. Effects of circuit breakers operation on the grid as well as methods for modelling of these devices are under investigation still.

## 1.1 Drivers towards HVDC grid

There are several drivers and challenges that need to be looked into while discussing the implantation of HVDC grids. The high-voltage high-power grid today is based on high-voltage alternating current (HVAC) technology. The large conventional generators connected to this grid are responsible for supplying power, keeping the frequency within the limits, and maintaining the voltage balanced throughout the nodes in the grid. The power flow has been predominantly unidirectional, i.e. from the generators to the consumers through the transmission and distribution systems. The power flow and voltage control in these grids has been relatively simple mainly because of the availability and predictability of the generators. In addition, transmission systems have been monopolies where the system security has been the main objective for control purposes. This has, however, changed in the recent past and the need for fast power flow control has emerged. Highvoltage direct current (HVDC) transmission system, whether it is conventional line-commutated converter (LCC) based or the modern voltage source converter (VSC) based, offers this functionality in addition to other benefits, such as lower losses and smaller transmission line corridor needed to transmit the same amount of power.

The past two decades have seen tremendous growth in renewable technologies such as wind and solar. The introduction of the renewables promises to mitigate the climate change and pollution problems through the replacement of fossil fuel powered electricity generating plants. The intermittency and unpredictability associated with renewables is proven to be a challenge for the transmission system operators (TSOs). Frequency is a measure of the balance between demand and supply of energy and has shown greater excursions around the nominal value. HVDC is an excellent solution for fast frequency control due to its characteristic fast power control functionality. In addition, offshore wind power plants (OWPP) are being built further offshore and AC transmission is technically not viable due to high charging currents that take up the entire thermal capacity of the cable connecting the OWPP to the grid system onshore. HVDC transmission does not produce steady-state charging currents and hence can be utilized for power flow over large distances.

Until recently, the electricity consumption was predicted in advance with a fairly degree of accuracy that enabled the amount of conventional generation to be adjusted to match this. As renewable generation cannot be changed easily (dispatched) due to its intermittent nature, the load has to be matched to maintain the power balance. The growth of the renewable share creates more, bigger and faster fluctuations of generation and leads to a paradigm shift from "generation matches load" to "load matches generation". Variable generation from wind farms or solar installations have a rate of change much faster than the ramp rate of conventional generating

units and the present system for voltage control. This implies new challenges for power system operations, as well as the need for accurate forecasting.

The transmission grids are not evolving as quickly as the generation and consumption. The generation has become more dispersed and diversified and in the case of renewables, needs support from the grid rather than providing it. The growth in transmission capacity has not been in line with the growth of value and direction of power flows. This means the factors of safety are being encroached into and available stability margins are thin. The consumers are now more active and the trend is that of more active consumers as the smart grid technologies and business models are rolled out. In order for the grids to facilitate the power flows associated with these changes, grids have to be adequately equipped with fast power-flow control capability and voltage control functions.

CAVE-thinking (Citizens Against Virtually Everything) leads to public pressure to put more of the transmission system lines underground in the form of cables. This undergrounding trend will increase the investment level, as high voltage cable systems are more expensive than overhead lines. This trend might also speed up the development of an HVDC grids as HVDC cable systems become an attractive alternative to high voltage AC cables.

The liberalization and deregulation of electricity markets is resulting into increased transactions between neighbouring countries. Firstly, it is easier to control the flow of power over HVDC lines, which is ideal for power trade from one country to the other. Secondly, transmission grids of countries do not operate in synchronism in general and may have different grid control strategies. The only way to transfer power between such grids is through HVDC lines. That is why a vast number of country interconnectors have been built using HVDC.

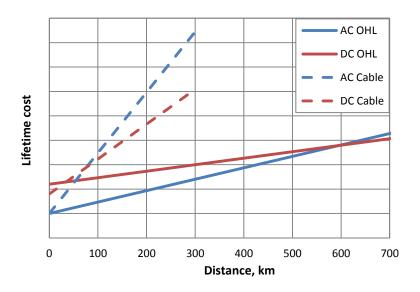

In terms of capital expenditure, the substation costs for HVAC transmission is lesser than that of HVDC converter station; the reason being the elaborate AC/DC converter equipment and allied accessories for HVDC against a simple configuration of transformers and switchgear for HVAC operation. On the other hand, the cost of transmission line for HVDC is lower than that for HVAC. The reason is the need for smaller transmission towers and smaller number of conductors for HVDC transmission than HVAC technology. Therefore, above a certain length HVDC becomes the cheaper option. The cost summary is illustrated in Figure 1.1. The variable costs include the costs of losses which are lower for HVDC. The break-even distance is between 600 and 800 km for overhead lines (OHL) and between 80 and 100 km for cable transmission due to even higher AC losses and the need for reactive compensation along the transmission route[1].

Figure 1.1: Comparison system lifetime costs as a function of transmission distance

Wind resource, even onshore, may be located further from the load centre. In the case of offshore wind, HVDC becomes the preferred option at very short distances as mentioned in the preceding section. The presence of an HVDC link between a wind farm and a grid system prevents the faults in one network from disrupting safe operation in the other. The fast power controllability associated with HVDC is another plus when integrating intermittent wind resource. In brief, HVDC makes integration of wind power with reduced costs, reduced losses, and higher security.

Offshore oil & gas production facilities have to employ fully-redundant gas turbines for their power demand. These take up valuable space on the platform that could otherwise be used for other purposes adding to the capacity of the facility. This solution entails high cost of production due to full-throttle operation of the standby generating unit. The CO<sub>2</sub> produced during use of these turbines is another cause for concern in certain countries. Norwegian authorities, for example, may ask offshore field developers to provide an economic comparison between offshore power production and powering from the shore solutions and employ the latter if it is comparatively economical. Due to this, few offshore oil & gas facilities on the Norwegian continental shelf have been powered from the shore; the first one being the Troll platform operated by Statoil [2].

In Europe the evolution of the HVDC Grid will be taken in steps. During next 10 years more than 60 HVDC projects are planned to be built. The first main development step foreseen to take place, in parallel to a few first regional multiterminal projects, is that the authorities planning a grid will require gridenabled pointtopoint systems that should be prepared for a future extension to a threeor more multiterminal system.

Until recently, majority of HVDC systems worldwide were point to point connection type. Point to point connections are very vulnerable to failure. Breakdown of any component can cause the failure of the complete HVDC connection leading to, generally, lower reliability of the system comparing to AC grids. In the past attempts were made to benefit from the same transmission corridor building radial multiterminal systems. Nevertheless, conventional LCC technology did not allow flexibility of the system operation and multiterminal systems were no developed further till recent years. Introduction of new flexible VSC based HVDC technology allows relatively easy implement multiterminal systems opening opportunity to increase reliability of the systems.

Development of multiterminal systems is seen to be crucial for wind energy integration and small island grids connection where is difficult to apply AC transmission. Offshore wind energy integration is strong component of EU targets towards low carbon future. While offshore wind share is becoming more significant in the European energy demand reliability of supply is getting more essential leading towards utilization of multiterminal HVDC systems.

Combining activities in offshore and onshore HVDC systems could lead towards overlaying continental SuperGrid [3], as shown in Figure 1.2, allowing integration of renewable resources and free energy trading. Long term plans for development of Continental SuperGrids have been discussed in Europe, Asia and North America. Nevertheless, it could take tens of years, same way it took 100 years to build European continental AC grid. On the way towards SuperGrid many challenges have to be overcome, as such as technical, economical and not the least political since it will involve international cooperation.

Figure 1.2: Concept of the future HVDC SuperGrid

## 1.2 HVDC converter technology

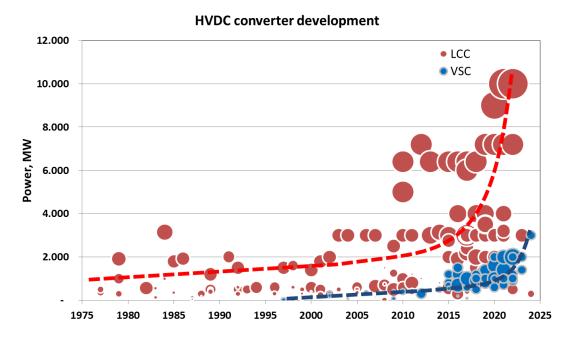

Line commutated converter (LCC) is a thyristor based technology that has been in operation for more than 40 years and used both for overhead and submarine transmission lines. In the past ten years, there have been a boom of development and deployment of LCC HVDC systems, mainly caused by construction growth in China. There HVDC is used for bulk power transmission from west part of the country, rich of hydro and wind resources, to the east part where the demand is mainly concentrated. Existing technology allows to transmit up to 6400 MW of power for bipolar line using voltage of ±800 kV. In the near future, upcoming technology for 7200 MW using  $\pm 1000$  kV is expected. Development is going further to  $\pm 1200$ kV HVDC transmission lines with 10000 MW of power rating. Due to use of thyristors application of LCC is possible only in strong AC systems with high short-circuit power. Except for China and India, development of LCC technology that has been going rapidly during last 15 years reached technical and feasible limits. Further increase in voltage level and transmitting power is limited byvulnerability of the power system due to loss of the HVDC line. Development of this technology in the range of 400-500 kV will be connected with decreasing costs and losses as well as compact design. LCC technology is not considered for multiterminal systems nowadays, mainly due to need of polarity reversal for power flow change and difficult control in a parallel multiterminal configuration [4]. However, two 3-terminal systems exist nowadays, in Canada [5] and Italy [6].

Voltage source converter (VSC) is an IGBT based converter technology. First VSC commercial application was presented in 1999 in Sweden [7]. VSC has an advantage over LCC due ability to connect systems with low short-circuit power like wind parks, offshore platforms or isolated power islands. Compared to LCC VSC technology has the following additional advantages [8,9]:

- 1) Simultaneous control of both active and reactive power. The AC voltage can be controlled at both stations.

- 2) Does not require any support from the AC grid it is connected to, and it can even be used for energizing an AC grid (black start capability).

- 3) VSC converters can operate without communication between the stations. It does not experience commutation failures and can support the AC grid by fast voltage control, thus minimizing the risk of commutation failures on nearby LCC links in case of a voltage drop.

- 4) In a LCC link the DC current always flows in the same direction, and the DC voltage polarity must change depending on the direction of power flow. A VSC converter always has the same voltage polarity but different current direction depending on the power

- direction. VSC converters therefore can control the power flow continuously, which makes it easier to build multiterminal schemes.

- 5) VSC technology is more suitable for connecting decentralized onshore or offshore wind farms where robust and economical extruded cables could be used.

- 6) Smaller converter stations that reduce the space requirements.

However, VSC suffers from higher power losses and supplementary control complexity. Due to lower power capacity of IGBT compared to thyristor, the highest ratings of VSC are much lower than that of LCC systems. Nowadays, bipolar systems technology for power transmission up to 1200 MW using ±500 kV overhead lines or XLPE cables for land or submarine connections are available. Up to now, main applications of VSC systems are offshore wind park connection to the land and submarine cables interconnections. Since the technology is relatively immature, comparing to LCC, the high potential in development is expected, especially application of new semiconducting materials like SiC or GaN. These new materials have better electrical characteristics, less power losses and higher working temperatures. In the next 20 years rating of ±800kV and 4000MW for bipolar system could be available. Technology costs are expected to decrease in the future and that could lead to the move from LCC to VSC in high power transmission applications.

In Figure 1.3 ratings of LCC and VSC systems are presented, including systems proposed until 2025. It clearly can be observed that increase of the ratings for both LCC and VSC systems in upcoming years is expected.

Figure 1.3: HVDC system ratings for LCC (red) and VSC (blue), size of bubble represents operational voltage, dash lines are trends

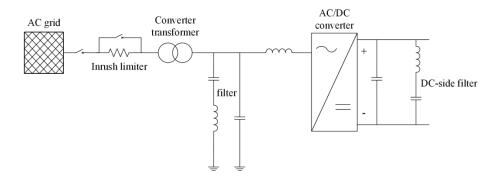

#### 1.2.1 VSC system design

Further discussion is limited to VSC technologies, as itrepresents the best potential solution for multi-terminal HVDC transmission systems. The major components of a point-to-point HVDC connection are shown in Figure 1.4. The converter stations at ends of the DC line provide the interface between the AC and DC systems where power is extracted from the AC system (rectifier mode) or transfer power to it (inverter mode). As it is possible to transmit power both ways over a transmission corridor, these converter stations have the ability to switch from rectifier to inverter mode. Converter stations are equipped with AC/DC converter valves made up of power electronic modules, switchgear, converter transformers, and AC & DC filters (if required). The other major component is the transmission medium that can be either an overhead line or a cable. The materials employed are similar to those used in AC lines. The major difference is that HVDC lines can operate with two conducting paths in the line compared to three for AC transmission. In certain cases a metallic return is used to enable monopolar operation in case of a fault on one of the poles. In that case, 50% of the rated power can be transmitted.

Figure 1.4: Schematic arrangement of major components in a VSC HVDC converter station

#### 1.2.2 VSC modules design

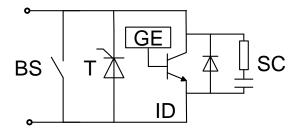

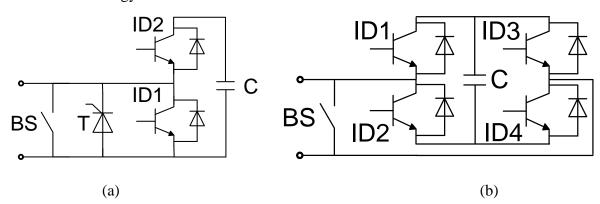

For VSC two main approaches are used: pulse width modulation (PWM), often presented by 2 or 3 level converters, and modular multilevel converter (MMC). The pulse width modulated voltage source converter employs line of modules, depicted in Figure 1.5, in the valves for AC/DC conversion where the main components are:

- 1. A single self-commutating switch IGBT with antiparallel diode (ID)

- 2. The associated gate electronics (GE)

- 3. The snubber circuit (SC)

- 4. The antiparallel thyristor for protecting the anti-parallel diodes in case of AC fault (T)

- 5. The bypass switch (BS)

- 6. Busbars for connection to adjacent modules

- 7. Casing and cooling (surrounds the module)

The modules may be connected in series and/or parallel to enhance the voltage and/or current ratings respectively. The modules in this topology switch simultaneously requiring a single gate pulse. As the switches are self-commutating, they have to interrupt the rated current and high rate-of-change of current can produce high voltages across the modules due to their inherent inductances. Therefore, the snubber circuit has to be designed to protect the power electronics from voltage surges. This is the main reason which limits the voltage scalability of this technology.

Figure 1.5: Schematic layout of the PWM VSC module

Inmodular multilevel converter (MMC) based VSC modules have similar design but arranged in a different configuration, half or full bridge, presented in Figure 1.6. When in PWD solution capacitor is connected in parallel to entire converter, in MMC each module has its own capacitor that allows achieving required operational voltage. The modules may be connected in series and/or parallel to enhance the voltage and/or current ratings respectively. The modules do not switch simultaneously and the control system for generation of firing pulses is fairly complex. Due to its design, this technology is more scalable in terms of voltage rating than the PWM VSC technology.

Figure 1.6: An example schematic layout of a half bridge (a) and full-bridge (b)MMC modules

#### 1.2.3 VSC converter design

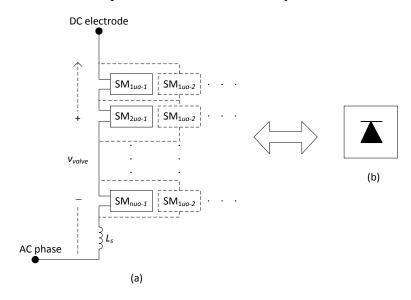

Switching modules (SM) are collected into a valve connecting the AC line with one of the DC electrodes. All valves are housed in enclosures that perform the tasks of insulation and connection to other valves and equipment in the HVDC converter terminal. The valve cooling system is an auxiliary system that keeps the powerelectronic modules within specified temperature limits, and must be considered a critical sub-system for the operation of the HVDC station. A representation of a valve is given in Figure 1.7. The inductance  $L_s$  is often present to reduce the di/dt stresses on the power-electronic switches. The first subscript in the module numbering represents module number in the valve. The second signifies the position of the valve in the phase leg, "u" for upper and "l" for lower. The third subscript identifies the phase to which the specific phase leg is connected (a, b, or c). Finally, the last subscript refers to the shunt path for additional current capacity. The shunt connection of modules is possible in the PWM VSC converters only. In a three-phase system, three phase legs, each containing two valves, connect to three AC lines to form a three-phase AC/DC conversion system.

Figure 1.7: Multilevel converter valve arrangement (a) Schematically (b) Symbol.

The individual valves discussed above are connected to form a complete converter. The converter topology to be used in further discussion is the MMC VSC based solution, since this topology:

- offers modularity,

- lower losses as compared to other VSC topologies due to lower switching frequencies,

- lower harmonics distortion, no filters required, and

- is being supported more and more by the manufacturers and utilities.

The construction of a converter is shown in Figure 1.8, where six valves are configured in three phase legs to form a three-phase converter. The arm connecting a specific phase to the positive DC bus is known as the upper arm (indicated by the subscript 'u') and the one connecting the negative DC bus to a specific phase is called the lower arm (indicated by the subscript '1'). Each valve has a series inductor between the AC connection and the DC electrode.

Figure 1.8: The three-phase MMC VSC (a) Schematic (b) Symbol.

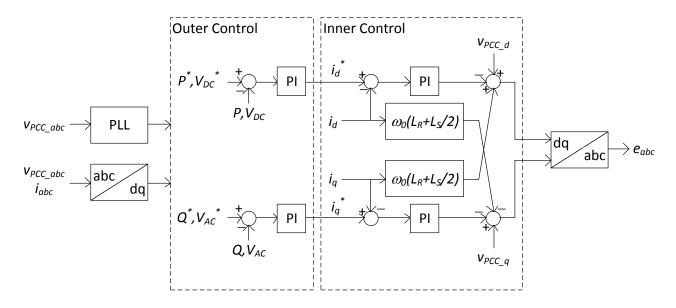

#### 1.2.4 VSCcontrol

The converter is supposed to behave like a synchronous generator, which controls its AC voltage magnitude and phase in response to certain control commands. The active and reactivepower exchange between the converter and the AC system follows the same set of rules and equations as in the case of exchange between a generator and an infinite bus.

The control of the converters is divided into the outer and inner control loops as shown in Figure 1.9. The first of the two outer control loops compares the active power and the converter DC-link voltage to their respective reference values and fed into a proportional-integral (PI) controller. The output of the PI controller is the reference d-axis current  $(I_d^*)$ . Similarly another PI controller outputs the q-axis reference current  $(I_q^*)$  by processing the error between the reference and actual reactive power and AC voltage. These reference currents are then processed to form reference voltages for the converter. The switch-modulation control (not shown here) takes care of individual switching in the modules in the converter arms. The switch modulation in PWM VSC is simple in the sense that all the switches in a valve change their state simultaneously on a single gate command. The output voltage is, therefore, a train of high-frequency rectangular pulses, which has to be filtered by the switching-harmonic filter in order to get a sinusoidal voltage. In contrast, the switches in MMC VSC valve are given individual firing commands at different points in the cycle to synthesize a nearperfect sinusoid without the help of switching harmonic filters.

Figure 1.9: Major loops in the converter control system

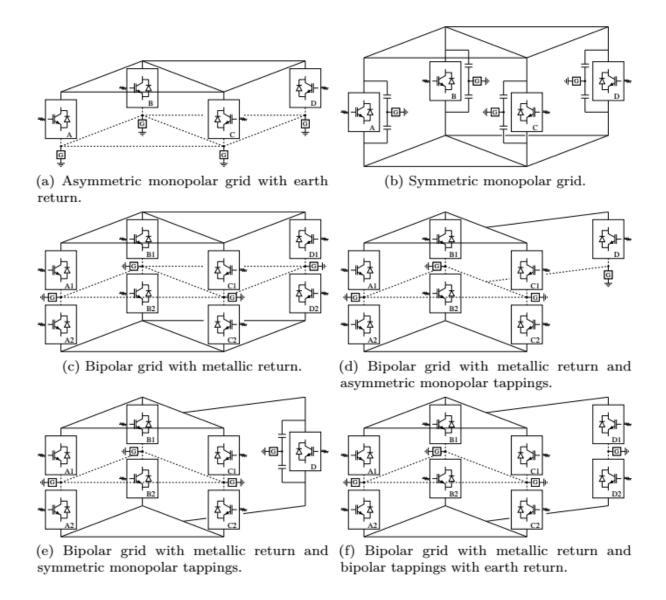

#### 1.2.5 Configurations of HVDC systems

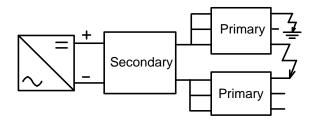

In general, a point-to-point HVDC transmission system consists of a rectifier station, inverter station and a transmission line. There are mainly five kinds of point-to-point HVDC transmission schemes: monopolar earth return system, monopolar metallic return system, bipolar system with neutral point of one terminal earthing, bipolar system with neutral point of both terminals earthing and bipolar system with neutral line earthing. For earth return system, electric corrosion of DC earthing electrode and influence of DC currents on DC magnetic bias of neutral earthing transformers should be taken into consideration. Therefore, a monopolar earth return system is usually adopted by cross-sea power transmission projects or instalment-constructed bipolar system with one pole operating first. Topologies of multiterminal systems can have different configurations of monopolar, bipolar or combined type with metallic return or without. Examples of possible configurations are presented in Figure 1.10.

Figure 1.10: Possible HVDC grid configurations

# 2. Current status and aims of the thesis

Deployment of HVDC grids is limited by several areas such as components development, converter and DC system controls and grid protection against DC faults.HVDC components and system control have been developing in the past 20 years from the beginning of VSC technology. Protection of the grid, on the other side, is a relatively new topic as there are only few multiterminal systems deployed so far. In order to boost implementation of multiterminal HVDC grids, robust and reliable protection system against DC faults should be developed. A range of fault detection methods and HVDC circuit breakers designs have been proposed and studied. Number of developed prototypes has been studied in laboratory environment. Further chapters explain the state of the art in DC fault transient studies, fault detection methods and circuit breaker technologies.

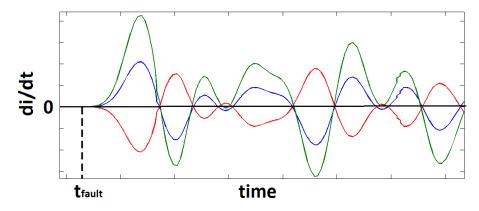

## 2.1 DC fault transients in HVDC systems

The aim of this section is to introduce the transient behaviour of HVDC networks under DC fault conditions. Understanding of a short circuit phenomenon in HVDC systems is essential for development of protection systems and circuit breakers in particular. Due to relatively low impedance in HVDC systems rate of rise of short circuit current is much higher than in AC systems [10]. Resulting high short circuit current could damage components of the system leading to prolong outages. This chapter describes the method for calculation of short circuit phenomenon in VSC HVDC systems. Moreover, the influence of the main parameters of the HVDC and associated AC systems on the short-circuit conditions are discussed.

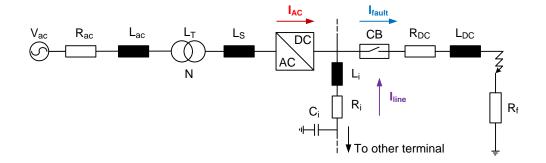

Simplified HVDC systems could be represented by a number of component blocks and parameters, see Figure 2.1. The HVDC converter divides a system into its AC and DC parts. The AC part is represented by AC source and AC system parameters, transformer and line inductance. The DC part, for point to point and multiterminal systems, includes DC system parameters, namely line resistance, inductance and capacitance. In case of a multiterminal system, potential circuit breaker current I<sub>fault</sub> consists of two components: AC side current contribution I<sub>AC</sub>from the nearest terminal and other terminals contribution I<sub>line</sub> that consists of system capacitance discharge current and other terminal AC side contribution.

Figure 2.1: Single line diagram of HVDC system in case of DC fault

Generally DC fault current can be defined as follows:

$$i(t) = \frac{U}{R} \left( 1 - \exp\left(-\frac{t}{\tau}\right) \right) + I_0 \exp\left(-\frac{t}{\tau}\right)$$

(2.1)

where  $\tau = L/R$  is the time constant of the system, U is DC system voltage and I<sub>0</sub> is current prior the fault. From the equation (1) can be observed that if the current is not interrupted it reaches the value of U/R.

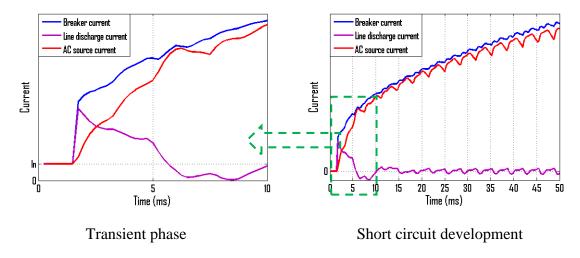

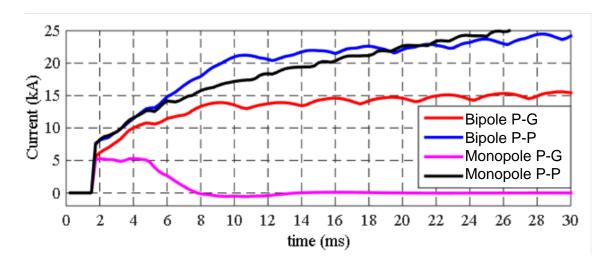

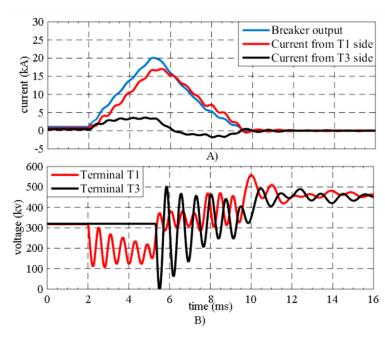

The detailed transient development of the short circuit current in HVDC systems is a complex phenomenon and depends on the value of many system and fault parameters. A representative example of the DC fault current development is shown in Figure 2.2.

Figure 2.2: Example of the representative fault current development

During the initial transient phase of the short circuit current development (i.e. typically within the first 5-10ms after occurrence of the fault), the following parameters are most important since they influence the discharging of associated capacitances:

- a) The size of the capacitance in concentrated filter elements [11] or cables (solid insulated cables or overhead power lines) [12],

- b) The length of the faulted line between the fault location and the circuit breaker [13],

- c) The length and number of lines connected to the same busbar as the faulted line [14],

- d) The size of a DC inductor (if used) [11] or the distributed line inductance (cable or overhead power line) [12],

- e) The resistance of the fault [15] and the method of the system earthing [16],

- f) The topology of the system and location of the fault [14].

The detailed quantitative influence of all these parameters has to be calculated for each and every situation individually, but a qualitative influence can be described and is universally valid. The amplitude of the initial transient capacitive discharge current increases with increasing capacitance such as that of DC filter elements or a number of lines connected. The larger the resistance in the short-circuit loop, the lower the amplitude of this transient peak. The resistance is slightly influenced by the length of the line between the fault location and the breaker, but mainly by the earthing scheme selected and the fault arc resistance. Any inductance introduced in a short circuit current loop decreases the rate-of-rise of short-circuit current but not the peak value. Thus, the rate-of-rise for overhead power line systems is lower than for cable systems since inductances are an effective means to reduce the short-circuit current.

The fault current waveform just after the fault occurrence is strongly dependent on the value of any fault limiting reactor installed in the system. This is because the main current component contribution comes from the discharge of the DC line capacitance and capacitors inside the converter flowing through the current limiting reactor. Consequently, a larger current limiting reactor value can limit the fault current rate-of-rise. This effectively reduces the DCCB interruption current requirement, assuming that it can operate fast enough, i.e. during the initial transient phase where the fault current has still not reached its steady state value. In order to reduce fault current rate of rise the use of fuses and superconductive coils was proposed and studied as well [17, 18].

The transient discharge of the DC-side capacitances results in a voltage drop in the DC system. This leads to an overcurrent through the converter valves, which are consequently blocked by theinternal protection system. In half-bridge VSC converters (PWM and MMC) when IGBTs are blocked, the bypass diodes or thyristors, protecting the IGBTs, bring the converter into an uncontrolled rectifier state providing a path for the fault current from the AC-side being injected into the fault. This leads to a further increase in the short-circuit current. If no measures to achieve interruption are taken, the short circuit current reaches a steady-state level within 10-100ms. In this steady-state phase the main parameters influencing the amplitude of the short circuit current are:

- a) Topology of the system and location of the fault [14,19],

- b) Converter technology [20-22],

- c) SCR of AC systems [11],

- d) Method of earthing [16, 20],

- e) Fault clearing options such as partial system disconnection and circuit breakers action [20, 23, 24].

Again, an increase of the total resistance in the system between the converters and earth decreases the amplitude of the steady-state short-circuit current. The fault resistance, the earthing of the system and also the topology (weakly or densely meshed) all contribute to the total resistance. For symmetric monopoles in particular, there is no current loop established during a pole-to-earth fault and no steady-state contribution from the AC can occur. Obviously, weak AC systems (with a low SCR) contribute less to the fault-current amplitude than strong AC systems connected to the DC network.

## 2.2 DC fault protection systems

Due to lower impedance compared to AC in HVDC systems a DC fault propagates extremely fast and in few milliseconds it causes voltage drop in all the terminals leading to converters control capability loss [25]. Additionally, growing fault current increases the risk of damaging sensitive power electronics components.

Several methods of DC fault detection and protection have been investigated and implemented [26]. Nowadays, frequently used method is opening of AC circuit breakers on the AC side and, when DC system is disconnected, identifying the faulted feeder and isolating it from the rest of the DC system. After that DC system can restart its operation. This solution is very time consuming and may require more than 100 ms for full system restoration. This approach is acceptable in cable systems where DC faults are mostly permanent and no reclosing operation is required. Another option could be, in case if full bridge converters are used, to block converters and isolate faulted feeder by disconnecting it from the rest of the DC system [27, 28]. This solution is faster than the first one since there is no time delay caused by AC breakers opening and system restoration can be done in tens of milliseconds. However, it requires significant increase of IGBTs in the VSC converters, up to doubling comparing to half bridge solution, and therefore, increases cost of the system. The fastest solution is to apply DC circuit breakers that can isolate the faulted feeder in several milliseconds. Several concepts of HVDC circuit breakers have been proposed [29]. However, the optimal solution that allows fast fault clearing capability with acceptable losses during steady-state operation is the hybrid circuit breaker concept [30].

Reliable protection system for HVDC meshed grids is still under development and no universal approach has been proposed so far. Due to fast fault propagation and information processing and communication delay central fault protection is very challenging [31, 32]. Thus

local measurement is a preferable solution in order to identify the faulted feeder and trigger the circuit breaker in the shortest period of time [33, 34]. Detection of the fault based on the threshold values of voltage or current are not fast enough and do not provide high level of selectivity [35-37]. Another option could be measurement of the rate of change of voltage [38]. However, it should be taken into account that voltage fluctuations are very sensitive to changes in the system as well as external effects and, therefore, achieving reliable protection based on this approach could be very challenging. In certain cases when the fault is far away from the circuit breaker it can be difficult to distinguish if the fault is within the protected feeder. In this case higher level protection system based on more advanced algorithms and measurements may be applied to accurately identify the affected feeder.

#### 2.3 HVDC circuit breakers

One of the key components limiting the deployment of multiterminal HVDC grid is absence of suitable DC breakers capable of interrupting DC fault current. This is due to strict practical challenges that these devices are required to satisfy. One of these challenges is the requirement that the DC switchgear must isolate the faulty section of the network in a very short time before the fault current reaches dangerous levels.

The breaking of DC current is technically demanding and consequently true DC breakers are considerably larger and more expensive than their AC counterparts. DC circuit breakers which exist today, mainly in medium voltage applications, normally consist of an AC circuit breaker plus an auxiliary circuit which creates a high frequency oscillatory current, allowing the arc to be interrupted when the current passes through zero. Alternatively DC breakers can be made out of semiconductor devices such as IGBT's, for example one half phase or the full-bridge circuit, is the equivalent of a single pole breaker whilst much faster than their mechanical counterparts, they would be considerably larger and more expensive, which will add to the costs of operating the DC breaker.

Development of HVDC circuit breakers has been started recently. The main reason is multiterminal systems construction planning. Nowadays, there is no standard design for HVDC breakers and, therefore, a lot of development is going on and opportunities for different design are available. Most of development is focused on research of breakers for VSC technology. One of the reasons for that is development of multiterminal systems using VSC technology where breakers are necessary. Another is lower ratings of VSC systems comparing with LCC.

Several technological areas where research and development is needed in order to improve or enable HVDC circuit breakers were identified and discussed [29]. These areas are summarized in the list below:

- Optimization of existing HVDC circuit breaker scheme by optimizing the size of elements like capacitors, inductors, varistors, or charging units. Main goal is a reduction in size, interruption time, and costs.

- Optimization of switching arcs with respect to growth of oscillation and capability to interrupt by detailed investigation of arc characteristics under many different conditions for gas and vacuum circuit breakers. Derivation and verification of the parameters in mathematical arc models.

- Multi-physics simulation of HVDC arcs for high current (growing current oscillation) and interruption phase.

- Extension of medium voltage circuit breakers to higher voltage levels. Either by improving the technology, by series connection, or by applying breakers across medium voltage levels in multilevel converter topologies.

- Fast mechanical switches or disconnectors with high recovery voltage withstand and low on-state-losses. Ideally, these switches have sufficient arcing voltage for fast commutation. Use of such a switch in a hybrid circuit breaker.

- Pure semiconductor switch with minimal on-state-losses. Use of new wide band-gap power semiconductor devices, e.g. SiC or GaN.

- Fault current limiters for medium and high voltage applications.

- Combined optimization of the whole system: breaker-control-protection.

- New testing methods for HVDC circuit breakers or its individual components. Due to the strong breaker-network interaction, power hardware in the loop techniques would be advantageous.

- Standards and norms for multiterminal HVDC.

In common with AC transmission systems, a breaker failure scenario would need to be considered. This could be another series connected DC breaker, the converter itself, if it were of the full-bridge design, or the AC circuit breaker.

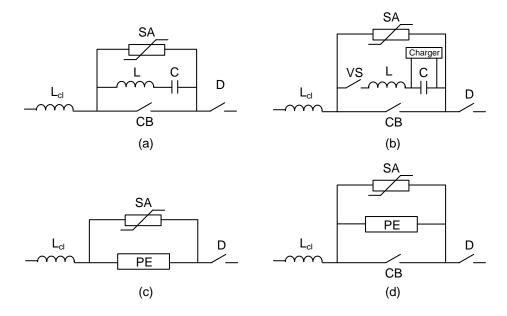

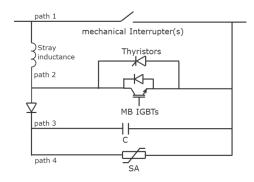

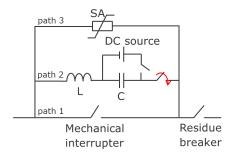

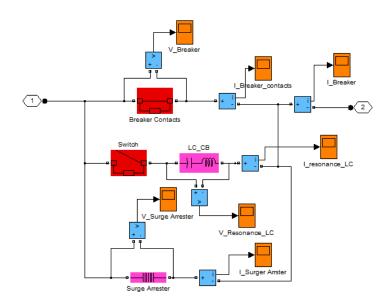

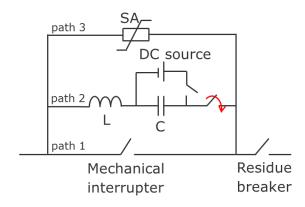

There are four main topologies for HVDC circuit breakers considered nowadays presented in Figure 2.3. Two topologies are based on breaking of the current in the mechanical switch and therefore they are called a mechanical type. In another topology fault current is interrupted by power electronic branch and it is called electronic type circuit breaker. The last one is a combination of both where fault current is commutated into power electronic branch by which is interrupted. Hybrid type has an advantage of lower on-state losses than an electronic type and faster fault blocking capability than a mechanical type. All topologies utilise surge arresters (SA) to dissipate inductive energy stored in the system when the fault current is interrupted. Often

circuit breakers have a current limiting reactor  $L_{cl}$  to reduce rate of rise of current and disconnector (D) to isolate the circuit breaker from the rest of the grid and eliminate leakage losses through the surge arresters. More detailed explanation of the operating principle can be found in Chapter 3.

Figure 2.3: Example of HVDC circuit breaker topologies: (a) passive oscillation, (b) active oscillation, (c) electronic, (d) hybrid types

Depending on the demands and topologies of the multiterminal HVDC grids, converters and connected AC systems it may be appropriate to implement a variety of HVDC circuit breaker topologies. The parameters specified in the Table 2.1 represent proposed and hardware demonstrated results that are the state of the art at the time of writing. Regarding maturity of technology, whilst in some cases there may be significant work required to bring a topology to the full scale application, majority of the discussed designs have been proven in a laboratory environment and none are thought to be beyond a full scale prototype.

Several prototypes of HVDC circuit breaker have been discussed for future applications in multiterminal HVDC transmission systems. The choice of the breaker topology is likely to depend heavily on numerous network parameters; therefore, the decision is highly system dependent. With regards to the selection of specific circuit breaker topologies, extensive project specific investigation is likely to occur for each planned system, however some general observations based upon apparent trends can be discussed. It is expected that, besides current and voltage capabilities, the on-state losses and the current interruption time would be the critical factors. Based on this consideration further investigation is focused on modelling and analysis of performance of active oscillation type and several topologies of hybrid type circuit breakers.

Table 2.1: Summary of HVDC circuit breaker prototypes

| Туре               | Breaking<br>branch | Current<br>breakingtime<br>(ms) | Breaking<br>current<br>(kA) | Voltage<br>(kV) | On-state<br>Losses | di/dt<br>(A/μs) | Installation<br>Costs | References |

|--------------------|--------------------|---------------------------------|-----------------------------|-----------------|--------------------|-----------------|-----------------------|------------|

| Passive            | Air Blast          | 12                              | 4.0                         | 500             | Negligible         | -               | lower                 | [39]       |

| oscillation        | SF6 CB             | 14                              | 2.2                         | 500             |                    | -               |                       | [40]       |

|                    | VI                 | < 5                             | 2.0                         | 400             |                    | -               | lower                 | [41]       |

|                    | SF6 CB             | 20                              | 1.2                         | 250             |                    | 1               |                       | [42]       |

| Active oscillation | SF6 CB             | 30 -40                          | 8.0                         | 250             | Negligible         | ole -           |                       | [43]       |

| oscillation        | VI                 | 5                               | 10.0                        | 80              |                    | 2.0             |                       | [44]       |

|                    | VI                 | < 8                             | 16.0                        | 72              |                    | 1.7             |                       | [45]       |

| Electronic         | PE                 | 0.4                             | 19.1                        | 13.5            | higher             | 47.8            | higher                | [46]       |

|                    | PE                 | 2.4                             | 16.0                        | 80              | lower              | 6.7             | higher                | [47]       |

| IIhi.d             | PE                 | 2                               | 7.5                         | 120             |                    | 2.9             |                       | [48]       |

| Hybrid             | PE                 | 3                               | 15.0                        | 200             |                    | 5.0             |                       | [49]       |

|                    | VI                 | 2                               | 15.0                        | 450             |                    | -               |                       | [50]       |

Note: VI – vacuum interrupter, PE – power electronics

#### 2.4 Aims of the thesis

In order to further implement HVDC grid, protection system against DC faults should be developed. To deliver reliable DC protection system future research should be focused on interoperability investigation of the protection algorithms and circuit breakers as well as how DC fault clearing effects operation of the HVDC grid. As discussed earlier a range of DC fault detection methods and HVDC circuit breakers designs been proposed and studied. Performance of HVDC circuit breakers in multiterminal system has not been studied extensively so far. This thesis is aiming to fill this gap and investigate operation of different circuit breakers topologies in multiterminal HVDC grids.

The work is divided in several steps:

- Create a model of HVDC converter that can be used for DC fault studies

- Create models of HVDC circuit breaker topologies

- Investigate DC fault conditions and influence of the grid parameters such as transmission media, converter type and topology

- Investigate performance of different types of circuit breakers in multiterminal systems: radial and meshed topologies

- Conclude requirements for HVDC circuit breakers based on the results of simulations

- Propose cost effective solution for multiterminal grid protection

# 3. Working methods

In this chapter methods to design models for DC fault transient studies are described. The developed models are compiled to develop a database that is presented in Annex A. The database allows designing required topology of the grid with implemented HVDC circuit breakers to investigate performance of the HVDC grid and its elements during DC faults.

## 3.1 HVDC systems modelling

In this chapter, a replacement model for acomplex converter station modelshown in Figure 1.4in Chapter 1.2.1 is explained. This replacement model is developed in order to decrease the computation time of the simulation and eliminate the complex control parameters of the system. With a decreased computation time and no active control in the model, simulations of multiterminal systems become more feasible. Furthermore, the model only has to be valid during fault conditions as the behaviour of the circuit breakers during DC faults is investigated.

#### 3.1.1 Converter model for DC fault studies

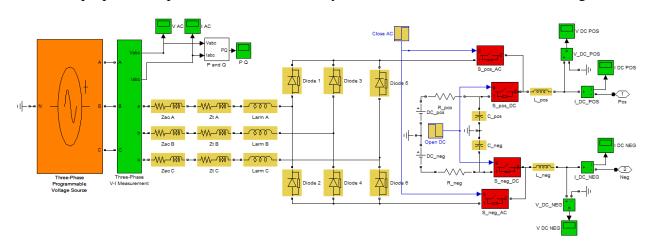

The proposed simplified model for an AC system and the converter is shown in Figure 3.1.

Figure 3.1: Simplified model converter station and AC system

The AC system showed in Figure 3.1contained a three-phase AC voltage source, output impedances of AC system that defined by AC system short circuit power ( $S_{AC}$ ) and reactance to resistance ratio:

$$L_{AC} = \frac{U_{AC}^2}{S_{AC}} \cdot \sin(\arctan\left(\frac{X_{AC}}{R_{AC}}\right)) \cdot \frac{1}{2\pi f}$$

(3.1)

$$R_{AC} = \frac{U_{AC}^2}{S_{AC}} \cdot \cos(\arctan\left(\frac{X_{AC}}{R_{AC}}\right))$$

(3.2)

The transformer modelled by the impedance of the transformer that is defined by short circuit impedance, nominal power and active losses.

$$R_t = \frac{\Delta P_k}{S_T} \cdot \frac{U_{AC}^2}{S_T} \tag{3.3}$$

$$L_t = \sqrt{(\frac{u_k}{100})^2 - (\frac{\Delta P_k}{S_T})^2} \cdot \frac{U_{AC}^2}{S_T} \cdot \frac{1}{2\pi f}$$

(3.4)

The controlled MMC IGBT bridge has been replaced by an uncontrolled three-phase diode rectifier. This diode rectifier simulates the blocking mode of the IGBTs during fault conditions. Parameters of the diodes and capacitance of the converter are derived from the topology of the converter and depend on the number of modules/levels in the arm and resistance of the single diode/thyristor.

$$R_{armdiode} = N_{arm} \cdot R_{diode} \tag{3.5}$$

$$C_{pos} = C_{neg} = \frac{3 \cdot C_{module}}{N_{arm}} \tag{3.6}$$

Inductance of the arm reactor can be defined using

$$L_{arm} = L_{pu} \cdot \frac{U_{AC}^2}{S_T} \cdot \frac{1}{2\pi f} \tag{3.7}$$

Inductance of the current limiting reactors L\_pos and L\_neg, that limit the rise of current from converter, is defined by the system design. Value of the inductance is limited by the effect on HVDC system stability as affect rate of current control [51]. Values between 50 and 100 mH could be considered acceptable.

Finally, the model is designed to set the initial conditions of the system and to connect the rectified voltage of the AC system when the fault is detected. Prior the fault is initiated, two DC sources (DC\_pos and DC\_neg) are connected to the output circuit to set the initial conditions and represent steady state operation of the converter. When the fault is detected, the switches S\_pos\_DC and S\_neg\_DCare opened to disconnect the DC sources and converter capacitors; at the same instance the switches S\_pos\_AC and S\_neg\_ACare closed. Changing of the converter state is done with consideration of the converter protection system delay.

#### 3.1.2 Model verification

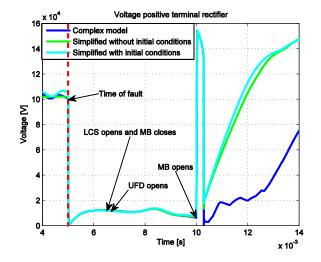

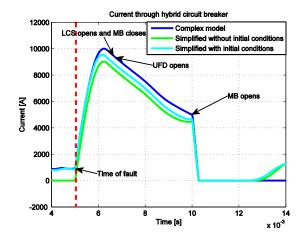

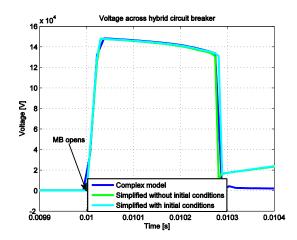

To verify that the simplified model is working correctly, three different simulations are compared: simulations of the complex model, simulations of the simplified model with and without setting initial conditions. In all three cases symmetrical monopole point to point system is considered; a fault at the rectifier side is simulated. Different system configurations and faults at other locations give comparable results, but those are not explained here. The hybrid circuit

breaker is implemented at the rectifier end in order to investigate stresses on the device. The results of the simulations are shown in Figure 3.2-3.5.

Voltage positive terminal inverter

Complex model

Simplified without initial conditions

Simplified with initial conditions

Simplified with initial conditions

LCSlopens and MB closes

LCSlopens and MB closes

Time of fault

Time [s]

X 10<sup>-3</sup>

Figure 3.2: Rectifier positive terminal voltage

Figure 3.3: Inverter positive terminal voltage

Figure 3.4: Current through hybrid circuit breaker

Figure 3.5: Voltage across hybrid circuit breaker

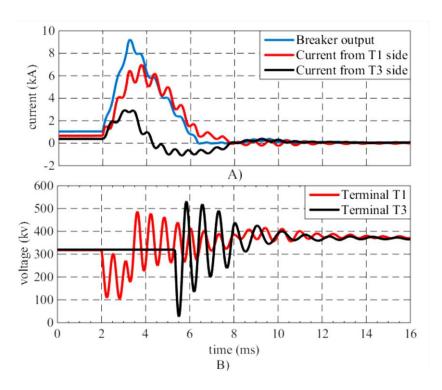

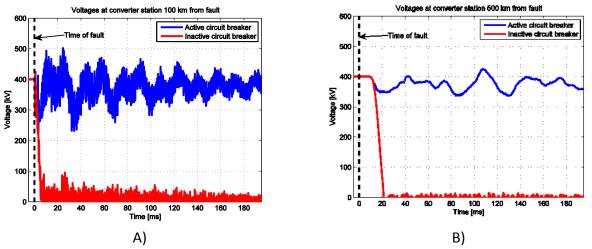

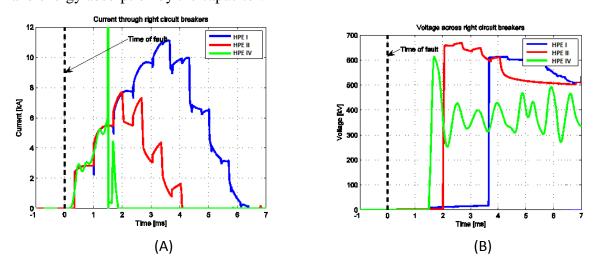

The simulation with the complex model takes almost two minutes, while the calculation time for the simplified circuit is below 10 seconds. This is a speedup of more than ten times which has even higher effect in a multiterminal system. Additionally, it avoids risk of control systems interaction between converters that can have negative effect on the results if not considered fully. Figure 3.2 shows that the voltage at the positive terminal of the rectifier is almost the same for all three simulations, only the voltage recovery after fault clearance is different due to action of the control system inside the converters. Although it plays a role when continues grid operation is studied, in this work, where just circuit breaker operation is considered, these discrepancies are acceptable.

Figure 3.3shows that the voltage at the positive terminal of the inverter is almost the same for the complex model and the simplified model without initial conditions, whereas the

simplifiedmodel with initial conditions differs slightly. Figure 3.4shows that the current for all three simulations has the same behaviour, only some small differences in the values can be seen. Next, Figure 3.5 shows that the voltage across the breaker is almost identical during the fault. Because the results show little variations between the complex and simplified model, it has been concluded that the replacement model is working with acceptable accuracy for further investigations.

#### 3.2 HVDC circuit breaker modelling

One of the key components limiting the deployment of a multiterminal HVDC grid is absence of suitable HVDC circuit breakers capable of interrupting DC fault current. This is due to strict practical challenges that these devices are required to satisfy. One of these challenges is the requirement that the DC switchgear must isolate the faulty section of the network in a very short time before the fault current can damage components of the network. It is also equivalently important to verify whether, upon their integration into HVDC grids, these HVDC circuit breakers meet the requirements demanded by multiterminal HVDC networks. There are two important aspects worth considering prior implementation of theHVDC breakers. The first is a clear understanding of the transient phenomena that the breakers are subjected to during switching operations, for instance, at time of fault clearing. The other is proper knowledge of the design and working principle of the circuit breakers themselves.

For these reasons in this further section a mechanical and four hybrid type circuit breakers are investigated in details and modelling principles are explained. Investigated circuit breakers contain several components that are similar and in the following sections these general elements and phenomena are described. Models of the investigated circuit breakers have been verified by comparison with results of the tested prototypes presented in the literature.

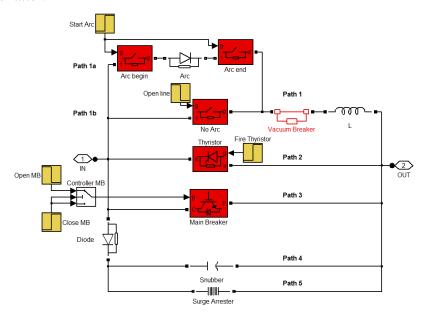

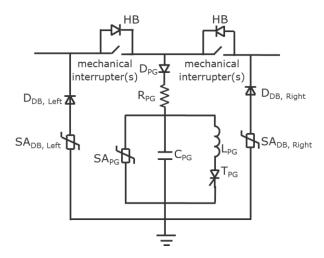

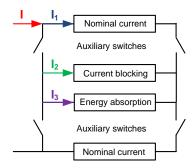

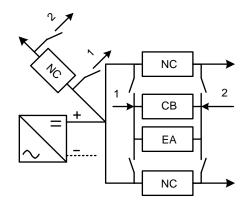

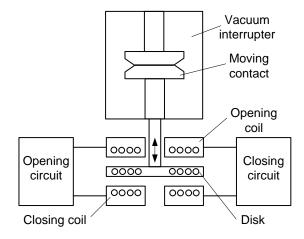

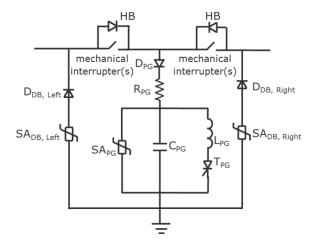

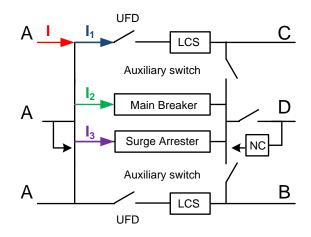

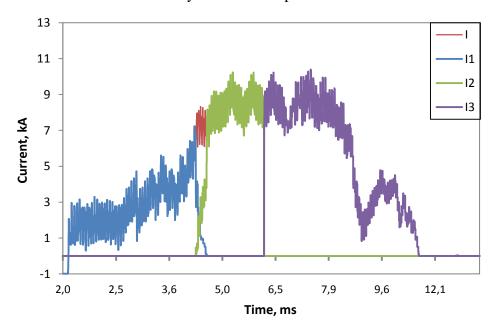

#### 3.2.1 Hybrid circuit breaker

A hybrid circuit breaker generally consists of several branches: nominal current, current blocking and energy absorbing branches as presented in Figure 3.6. Nominal current branch has low steady-state power losses and consists of a mechanical switch and, in some topologies, additional power electronic devices for current commutation. Current blocking branch consists of power electronic devices and passive components in order to block the fault current. Speed and process of current blocking depends on the design of the nominal current branch due to mechanical switch opening delay. Energy absorbing branch is required in order to dissipate inductive energy stored in the system when fault current is blocked. Generally, metal oxide

varistor (MOV) is applied as energy absorbing element. It has similar design to a surge arrester used for overvoltage protection.

Figure 3.6: General design of a hybrid DC breaker

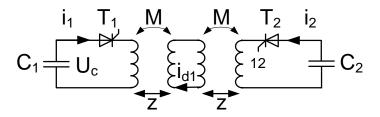

#### 3.2.2 Current commutation

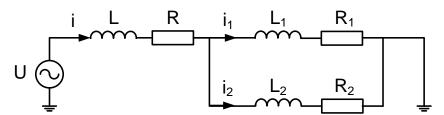

In order to divert fault current from the nominal current branch to the current blocking branch commutation circuit should be designed. In Figure 3.7 simplified electrical circuit for commutation during a pole to ground fault is presented, where L is inductance and R is resistance of the path between the voltage source and the fault location. Parameters L and R include AC system and AC transformer impedance, DC transmission line (OHL or cable) impedance and fault resistance. Nominal current branch consists of impedance  $L_1$  and resistance  $R_1$  that represent arc voltage in the mechanical switch or resistance of power electronic components installed. Current blocking branch consists of impedance  $L_2$  and resistance  $R_2$  of power electronic components.

Figure 3.7: Electric equivalent of the hybrid DC breaker commutation circuit

In HVDC systems  $R >> R_1$  and  $L >> L_1$ , hence solution for the fault current is

$$i(t) = \frac{U}{R} \left( 1 - \exp\left(-\frac{t}{\tau}\right) \right) + I_0 \exp\left(-\frac{t}{\tau}\right)$$

(3.8)

where  $\tau = L/R$  is the time constant of the system and  $I_0$  is current prior the fault. From the equation (3.8) can be observed that if the current is not interrupted it reaches the value of U/R.

Current commutation process could be described by solving equations (3.9) and (3.10) for currents in nominal current and current blocking branches as defined in Figure 3.7.

$$L_2 \frac{di}{dt} + R_2 i = (L_1 + L_2) \frac{di_1}{dt} + (R_1 + R_2) i_1$$

(3.9)

$$L_1 \frac{di}{dt} + R_1 i = (L_1 + L_2) \frac{di_2}{dt} + (R_1 + R_2) i_2$$

(3.10)

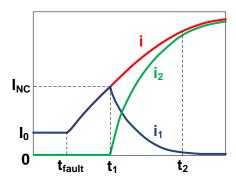

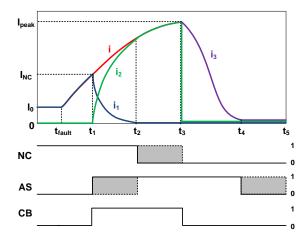

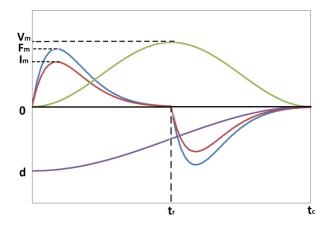

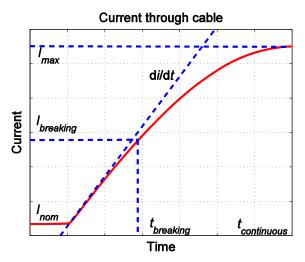

In Figure 3.8 current commutation process is presented where  $t_{fault}$  is the time of the fault inception and  $t_1$  is the time of the commutation process beginning that can be triggered by the action of the protection relay, and  $t_2$  is the end of the commutation process when the current is fully commutated into the current blocking branch. Current  $I_0$  is the steady-state current prior the fault and  $I_{NC}$  is the maximum current in the nominal current branch. Maximum value of  $I_{NC}$  can be limited by the capabilities of the power electronic components, installed in the nominal current branch, as they are dimensioned for current commutation only and not for the fault current blocking.

Figure 3.8: Illustration of the current commutation process

In order to commutate significant part of the current, resistance of the nominal current branch should be much higher than resistance of the current blocking branch in the end of the commutation process. For this reason switches with high arc voltage can be used in the nominal current branch. High pressure gas filled type switches have high arc voltage, however, they have lower contacts moving speed due to gas resistance. As alternative to reach high contact separation speed vacuum switch could be used [52], however, vacuum arc has relatively low resistance and thus could be supported by the power electronic switch [53].

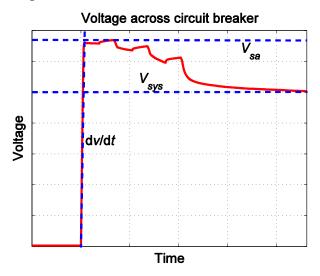

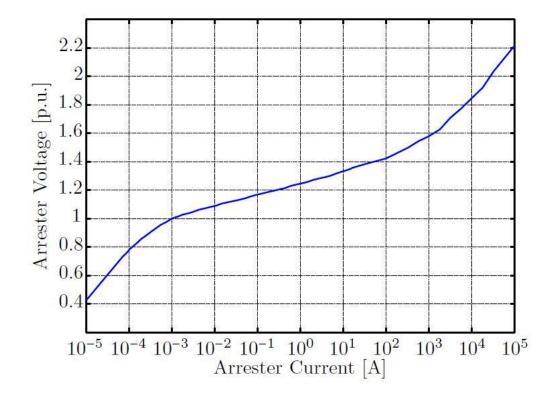

#### 3.2.3 Energy absorption

Energy absorption branch consists of surge arresters [54]. Number and parameters of surge arresters depend on the amount of energy that should be dissipated and limiting voltage. Limiting voltage is defined by the system design and voltage withstand capability of the protected devices [55]. Generally, considering typical surge arrester U=f(I) characteristics, the counter voltage amplitude must be set significantly higher than the maximum system voltage to prevent high leakage current through the breaker once the bulk of the energy has been dissipated. At the same time, the recommendation for basic insulation level for long term voltage exposure for DC equipment defines the upper limit for the DC breaker counter voltage. Considering that in hybrid breaker designs arrester's protection voltage value is set between 1.5 and 1.6 of the system

voltage. In the proposed circuit breaker design the surge arresters are disconnected from the grid during steady-state operation leaving more room for defining the surge arrester protective voltage in order to reduce stress on the components.

Development of the current through surge arrester can be defined using (3.11), where  $U_{sa}$  is limiting voltage of the surge arrester, U is nominal voltage of the system and  $I_{peak}$  is the fault current at the moment of current blocking, and  $\tau = L/R$  from the circuit in Figure 3.7.

$$i_{sa} = I_{peak} \exp^{-\frac{t}{\tau}} + \frac{U_{sa} - U}{R} \left( \exp^{-\frac{t}{\tau}} - 1 \right)$$

(3.11)

The duration of the current flow in the surge arrester  $t_{sa}$ , can be deduced by equalling to 0 the equation (3.11) and solving it for t. Energy dissipation time is important for concluding the fault clearing process preceding opening of the auxiliary switches.

$$t_{sa} = \tau \ln(1 + \frac{RI_{peak}}{U_{sa} - U}) \tag{3.12}$$

If the surge arrester voltage characteristics  $U_{sa}=f(I)$  is replaced by the real characteristics it comes that the steady state current is never really interrupted. A "small" current flows through the surge arrester as long as a voltage difference appears across the circuit breaker. An expression for the energy that is dissipated in the surge arrester  $E_{sa}$  is now derived using equation (3.11) and (3.12) as follows:

$$E_{sa} = U_{sa} \int_0^{t_{sa}} i_{sa}(t) dt = U_{sa} (I_{peak} \tau - \frac{U_{sa} - U}{R} t_{sa})$$

(3.13)

Characteristics of a surge arrester are unstable after reaching maximum operational temperature, generally 120°C, and energy absorption capabilities are limited by thermal stability limit that is between 190°C and 220°C [56, 57]. The cool-down time typically lies between 45 and 60 minutes depending on the arrester type and the ambient conditions.

To define number of surge arresters required for the breaker equation (9) can be used, where k is a safety coefficient and  $n_{op}$  is the number of operations during cool down time. Number  $n_{op}$  can include reclosing operation as well as probability of the fault occurrence in the protected feeders during cooling time. During reclosing operation  $E_{sa}$  could be lower since only activation of the current blocking branch is required in order to define if fault was temporary. Energy absorption of a single surge arrester E' is limited by thermal stability limit of a MOV element in the surge arrester and defined in a datasheet as an energy value per kV of limiting voltage level.

$$N_{sa} = \frac{\sum^{n_{op}} E_{sa}}{E'U_{sa}} k \tag{3.14}$$

# 3.3 Hybrid Power Electronic HVDC Circuit Breaker type I

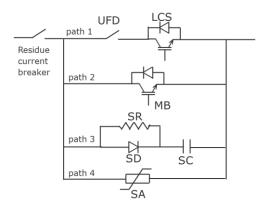

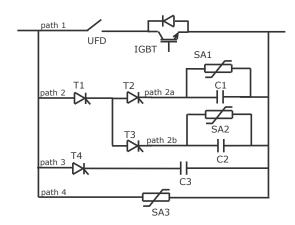

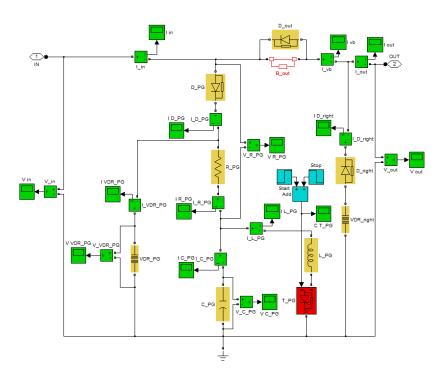

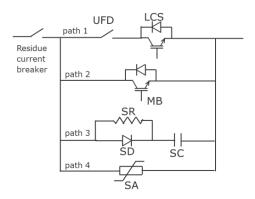

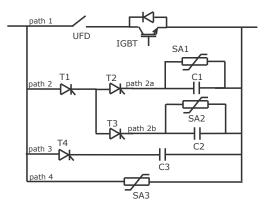

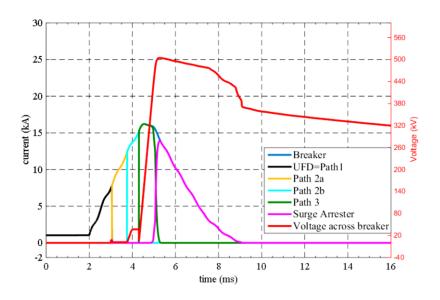

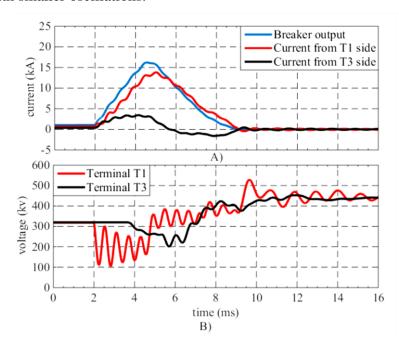

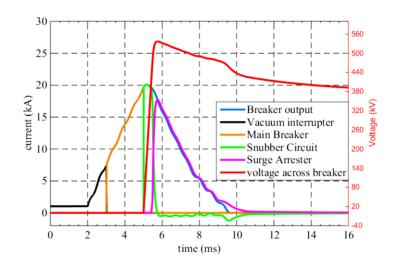

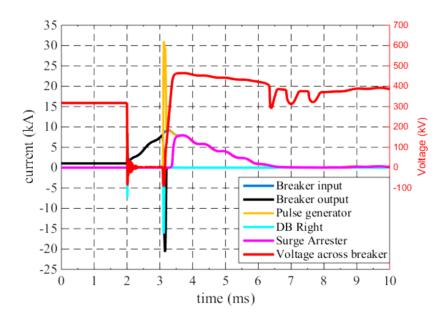

The electrical model of type I hybrid power electronic (HPE I) HVDC breaker based on the concept proposed in [47, 58] is shown in Figure 3.9. It can be seen from the model that this scheme consists of four parallel paths.

Figure 3.9: Electrical diagram of the HPE I HVDC circuit breaker

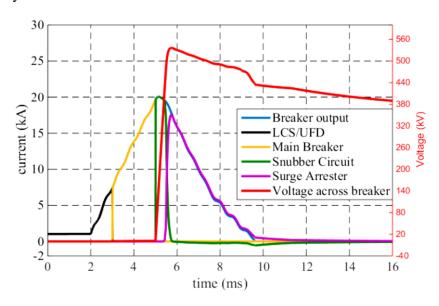

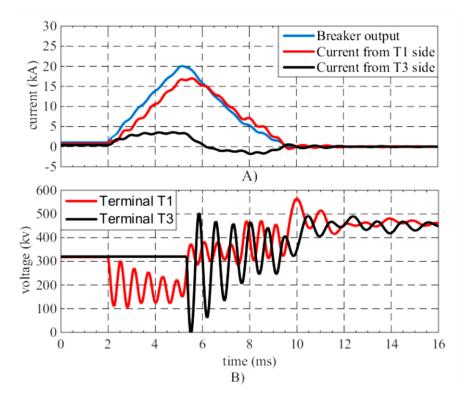

Under normal load operation, current flows through the branch consisting of the load commutation switch (LCS) and ultrafast disconnector (UFD). The load commutation switch is a power electronic switch that is able to carry the load current with low losses and it contains only a few modules of IGBTs required to commutate the current into the main breaker when ordered to interrupt.

When a fault is detected, the load commutation switch turns into blocking state while at the same time the main breaker switches on. The main breaker has several modules of IGBTs that can withstand higher voltage stresses compared to the load commutation switch. However, this branch has higher on-state losses and hence, this is the reason why it is used only during switching operations. The fault current is now commutated to the main breaker (path2). After the fault is fully commutated to the main breaker, the ultra-fast disconnector is opened to protect the load commutation switch against transient recovery overvoltage (TRV) at later stage. By the time the contacts of ultra-fast disconnector reach the position where it can withstand the TRV, the main breaker is switched off. The rise of TRV immediately follows the opening of the main breaker and soon it reaches the surge arrester protection level. By this time the surge arrester will be turned into conducting mode (path 4) and finally this branch will dissipate the magnetic energy in the system. Consequently, the fault current is interrupted. The snubber circuit (path 3) is included to control the rate of rise of TRV (du/dt) after the main breaker is switched off.

A disconnecting circuit breaker (residual current DC breaker) interrupts the residual current and isolates the faulty line from the HVDC grid to protect the arrester banks of the hybrid HVDC breaker from thermal overload.

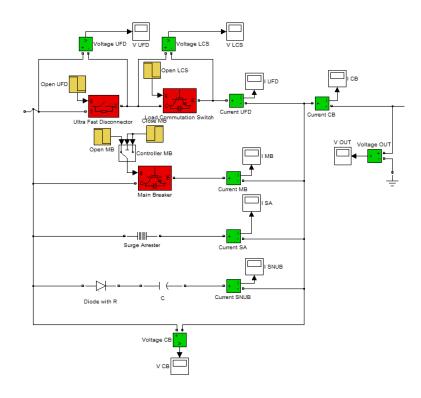

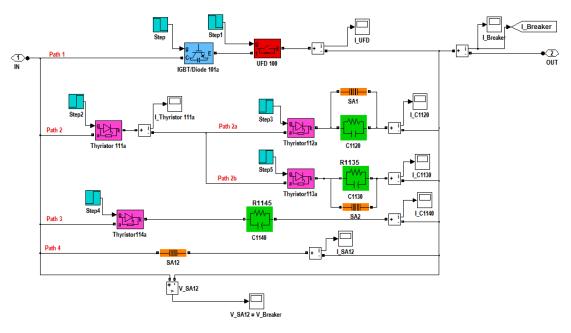

Figure 3.10:MatLab model of the HPE I HVDC circuit breaker

The MatLab model of the HPE I circuit breaker is presented in Figure 3.10. Dimensioning of the components are explained as following.

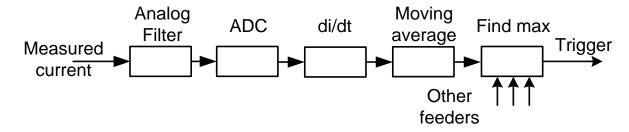

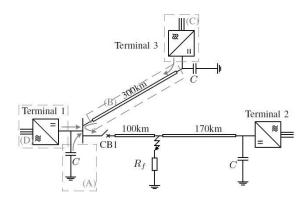

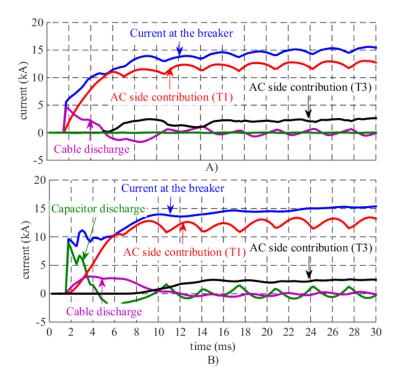

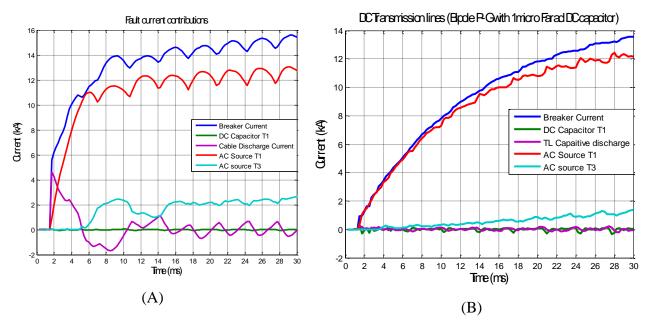

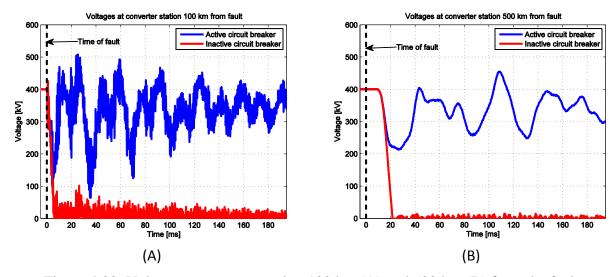

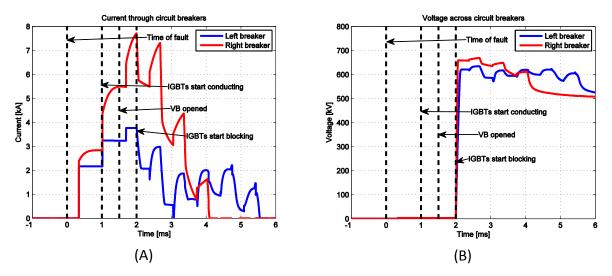

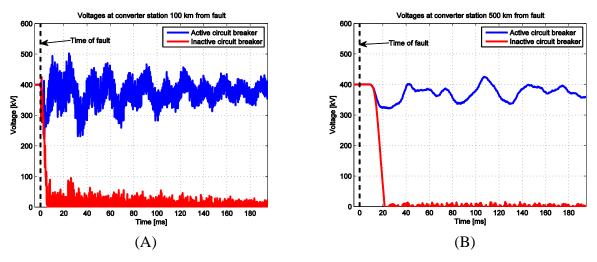

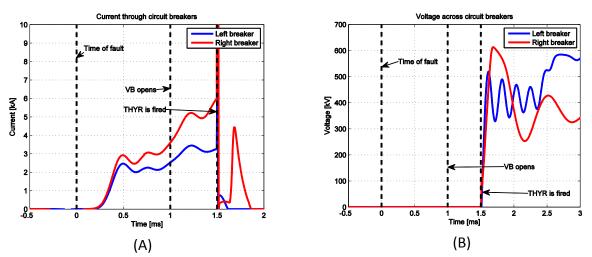

**Ultra-Fast Disconnector (UFD)**. UFD isolates the LCS from the voltage stress built up across the main breaker during current blocking. It is modelled as an ideal switch that can operate only at zero current.