F3

Faculty of Electrical Engineering Department of Measurement

Implementation of a PCIe Encryption Module for Ip-over-Satellite Modem with support of Open-Encryption Interface

Bc. Ondrej Ille

Supervisor: Doc. Ing. Jiří Novák

Field of study: Cybernetics and robotics Subfield: Sensors and Instrumentation

May 2017

# ZADÁNÍ DIPLOMOVÉ PRÁCE

#### I. OSOBNÍ A STUDIJNÍ ÚDAJE

Příjmení: Ille Jméno: Ondrej Osobní číslo: 393186

Fakulta/ústav: **Fakulta elektrotechnická**Zadávající katedra/ústav: **Katedra měření**Studijní program: **Kybernetika a robotika**

Studijní obor: Senzory a přístrojová technika

#### II. ÚDAJE K DIPLOMOVÉ PRÁCI

Název diplomové práce:

Implementace PCIe šifrovacího modulu pro satelitní IP modem s podporou rozhraní Open-encryption

Název diplomové práce anglicky:

Implementation of a PCIe Encryption Module for Ip-over-Satellite Modem with Support of Open-Encryption Interface

Pokyny pro vypracování:

- 1. Navrhněte a implementujte PCle modul pro HW akcelerované šifrování.

- 2. Zabezpečte výrobu prototypu, oživte jej spolu se základní deskou a ověřte funkčnost komunikačních rozhraní.

- 3. Upravte existující ovladače OS Linux pro platformu Cavium MIPS a pokud to bude nezbytné, rozšiřte jejich funkcionalitu.

- 4. Navrhněte otevřené rozhraní a protokol pro správu klíčů a integrujte jej do protokolového zásobníku.

| Seznam doporucene literatur | y | 1 |

|-----------------------------|---|---|

|-----------------------------|---|---|

- [1] Johnson H., Graham, M.: High-Speed Digital Design, Prentice Hall 1993

- [2] Corbet, J., Rubini, A., Kroah-Hartman, G.: Linux Device Drivers, O'Reily 2005

- [3] Schroder, C.: Linux Networking Cookbook, O'Reily 2008

Jméno a pracoviště vedoucí(ho) diplomové práce:

doc. Ing. Jiří Novák Ph.D., K 13138 - katedra měření

Jméno a pracoviště druhé(ho) vedoucí(ho) nebo konzultanta(ky) diplomové práce:

Datum zadání diplomové práce: 21.12.2016 Termín odevzdání diplomové práce: 26.05.2017

Platnost zadání diplomové práce: 30.09.2018

Podpis vedoucí(ho) práce Podpis vedoucí(ho) ústavu/katedry Podpis děkana(ky)

#### III. PŘEVZETÍ ZADÁNÍ

Diplomant bere na vědomí, že je povinen vypracovat diplomovou práci samostatně, bez cizí pomoci, s výjimkou poskytnutých konzultací. Seznam použité literatury, jiných pramenů a jmen konzultantů je třeba uvést v diplomové práci.

Datum převzetí zadání Podpis studenta

# **Acknowledgements**

I would like to thank all my colleagues from Research and Development Department of ND Satcom for cooperation during the development of this thesis. Namely Artur Hauger and Werner Staerk for hardware development, Bernd Jungbludt for supervision and mental support, Bruno Schrade for advice on Linux drivers and discussions about real-time operating systems and Philipp Schönberger for help with the SW integration. I would also like to thank my supervisor Doc. Ing. Jiří Novák who provided useful consultations during the development of this thesis. I also would like to thank Ing. Vít Záhlava Csc. for precious consultations about PCB layout. Last but not least, I would like to thank my family for support during whole studies.

# **Declaration**

This thesis is an intellectual property of ND SatCom GmbH, Graf-von-Soden-Strasse, D-88090 Immenstaad am Bodensee, Germany. All possible commercial applications are prohibited without agreement of ND Satcom. The redistribution of this thesis is allowed without confidential information stated in Appendix, according to Czech law, 111/1998 §47b. The full version is available only to the closed circle of employees of Czech Technical University who are required to see the thesis for the purpose of its submission and defense. All design materials and source code are confidential to ND Satcom.

I declare that the presented work was developed independently and that I have listed all sources of information used within it in accordance with the methodical instructions for observing the ethical principles in the preparation of university theses.

Prague, 20 May 2017

### **Abstract**

Master thesis deals with the design and implementation of the encryption system for satellite router to the state of functional prototype. The encryption itself is implemented in dedicated CPU with hardware accelerator. The system contains hardware part concerning with design and manufacturing of PCIe module and software part implementing and integrating necessary software modules. The whole design is connected to IP stack of satellite router Skywan 5G and it is ready for promising commercial applications.

**Keywords:** encryption, PCIe, COMe, Linux, Satelite communications, Skywan 5G

**Supervisor:** Doc. Ing. Jiří Novák

## **Abstrakt**

Diplomová práca sa zaoberá návrhom a implementáciou šifrovacieho systému pre satelitný router až do stavu fungujúceho prototypu. Šifrovanie samotné je riešené pomocou dedikovaného CPU s hardwarovým akcelerátorom. Systém je realizovaný na úrovni hardware v podobe návrhu a výroby PCIe modulu a tiež na úrovni software v podobe implementácie a integrácie potrebných modulov. Celý návrh je zapojený do protokolového zásobníku IP satelitného routra Skywan 5G a je pripravený na sľubné komerčné použitie.

**Klíčová slova:** šifrovanie, PCIe, COMe, Linux, Satelitná komunikácia, Skywan 5G

**Překlad názvu:** Implementace PCIe šifrovacího modulu pro satelitní IP modem s podporou rozhraní Open-encryption

# **Contents**

| Abbreviations                     | 1  |

|-----------------------------------|----|

| 1 Introduction                    | 5  |

| 1.1 Skywan 5G                     | 5  |

| 1.2 Encryption requirements       | 6  |

| 1.3 Possible realization          | 7  |

| 1.3.1 Internal module             | 8  |

| 1.3.2 External module             | 8  |

| 1.4 Background of Cryptology      | 9  |

| Symmetric vs. asymmetric key      |    |

| ciphers                           | 9  |

| Block vs. stream ciphers          | 9  |

| 1.4.1 Cryptoanalysis              | 10 |

| 1.4.2 Algorithms of interest      | 10 |

| 2 Hardware design                 | 17 |

| 2.1 System level design           | 19 |

| 2.1.1 CPU selection               | 19 |

| 2.1.2 System configuration and    |    |

| status                            | 23 |

| 2.1.3 Power supply design         | 24 |

| 2.1.4 Thermal design              | 25 |

| 2.1.5 Clock design                | 26 |

| 2.2 Tool selection                | 26 |

| 2.3 Schematic design              | 29 |

| 2.3.1 Power supply                | 30 |

| 2.3.2 Power sequencing            | 34 |

| 2.3.3 Ethernet transceiver        | 35 |

| 2.3.4 Clock circuits              | 37 |

| 2.3.5 DDR3                        | 37 |

| 2.3.6 PCIe                        | 37 |

| 2.3.7 Termination resistors       | 38 |

| Other parts of the schematic      | 39 |

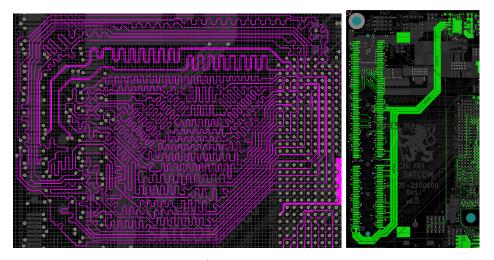

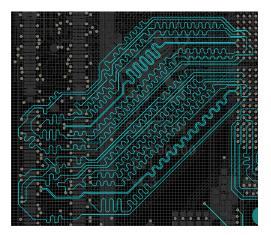

| 2.4 Board layout                  | 40 |

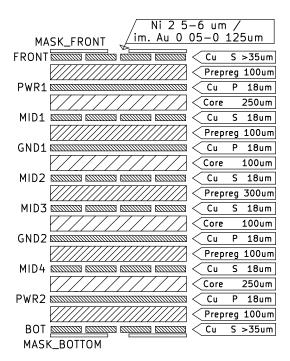

| 2.4.1 Board stack-up              | 40 |

| 2.4.2 Component placement         | 41 |

| 2.4.3 Transmission line impedance | 42 |

| 2.4.4 Routing                     | 43 |

| 2.5 Board manufacturing           | 46 |

| 2.6 EMC consideration             | 48 |

| 3 HW/SW Interface                 | 51 |

| 3.1 Power sequencing              | 52 |

| 3.2 POR configuration             | 56 |

| 3.3 Initialization sequence       | 59 |

| 4 SW integration                  | 61 |

| 4.1 Host driver                   | 62 |

| 4.2 Device firmware               | 63 |

| Bibliography                      | 85         |

|-----------------------------------|------------|

| Appendix B - Component placement  | 83         |

| Appendix A - Schematic            | 81         |

| 5.5 Conclusion                    | 79         |

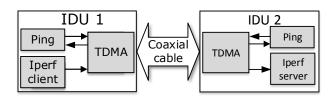

| TDMA                              | 76         |

| 5.4 Packet forwarding test over   |            |

| 5.3 Response time                 | 76         |

| consumption                       | 74<br>74   |

| 5.1 Thermal performance and power | _          |

| 5 Testing and conclusion          | <b>7</b> 3 |

| engine                            | 70         |

| framework to Linux networking     |            |

| 4.7 Connection of encryption      | •          |

| 4.6.4 Real-time kernel            | 70         |

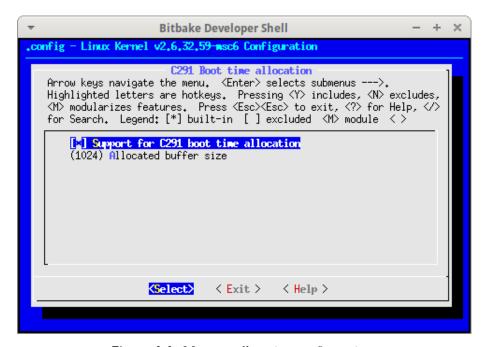

| 4.6.2 Memory allocation           | 68<br>69   |

| 4.6.1 Per-CPU variables           | 67         |

| 4.6 Porting of the C291 driver    | 67         |

| 4.5 Configuration of the SW       | 66         |

| 4.4 C291 CLI                      | 66         |

| 4.3 Encryption sequence           | 65         |

# **Figures**

| 1.1 Skywan 5G                                                                                                             |                 |

|---------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.2 Internal architecture of Skywan 50                                                                                    | G 7             |

| 2.1 High-level diagram of a Encryption                                                                                    | n               |

| board interfaces                                                                                                          | 18              |

| 2.2 C29x Block diagram(from [14])                                                                                         | 21              |

| 2.3 C29x modes of operation(from                                                                                          |                 |

| [14])                                                                                                                     | 22              |

| 2.4 C29x reference design                                                                                                 | 23              |

| 2.5 Power supply chain                                                                                                    | $\frac{25}{25}$ |

| 2.6 ISL95870B internal circuits(from                                                                                      | 20              |

| `                                                                                                                         | 31              |

| [17])                                                                                                                     | $\frac{31}{32}$ |

| $2.7 \ V_{CORE} $ simulation                                                                                              |                 |

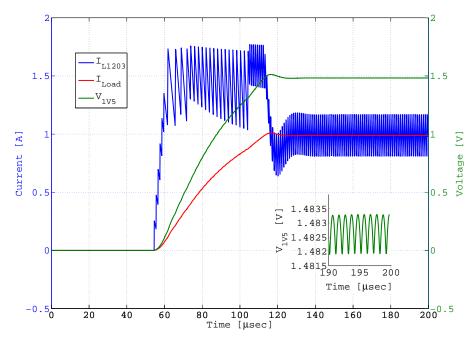

| $2.8 V_{1V5}$ simulation                                                                                                  | 34              |

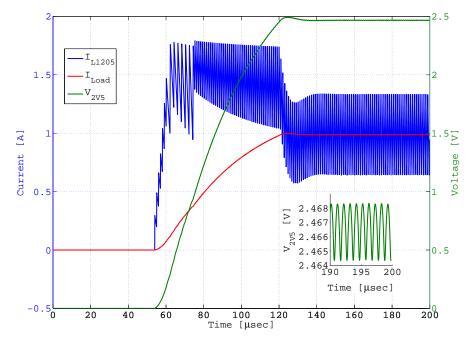

| $2.9 V_{2V5}$ simulation                                                                                                  | $\frac{35}{26}$ |

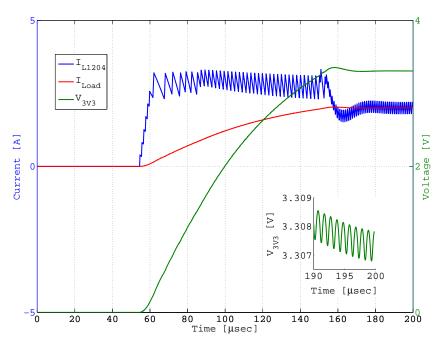

| 2.10 $V_{3V3}$ simulation                                                                                                 | 36              |

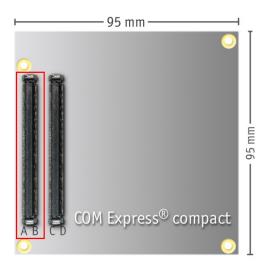

| 2.11 COMe module dimensions                                                                                               | 40              |

| 2.12 Board stack-up                                                                                                       | 41              |

| 2.13 Routing of local signals (IO power                                                                                   |                 |

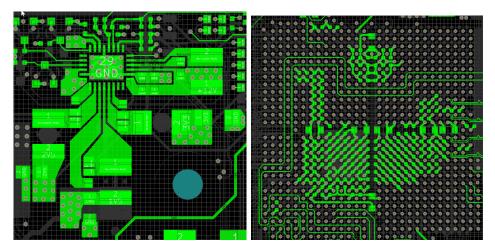

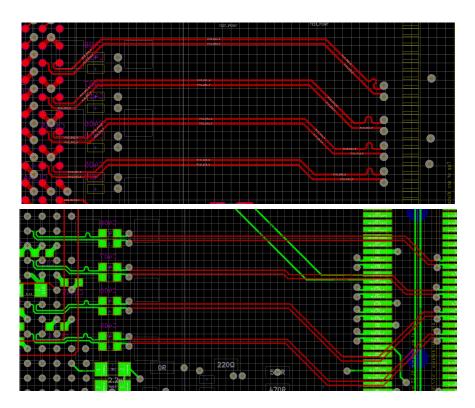

| - left, decoupling capacitors - right)                                                                                    | 45              |

| 2.14 Routing of DDR3 (adress signals                                                                                      |                 |

| left, reference voltage - right)                                                                                          | 45              |

| 2.15 Routing of DDR3 data bytes and                                                                                       | d               |

| strobes                                                                                                                   | 46              |

| $2.16~\mathrm{Routing}$ of PCIe (RX pairs - up,                                                                           |                 |

| TX pairs - down)                                                                                                          | 47              |

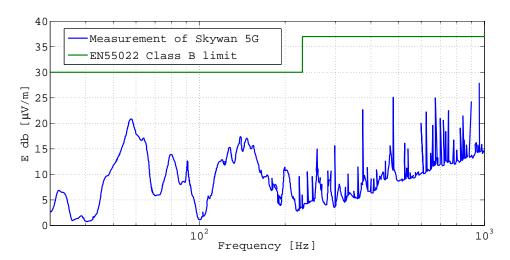

| 2.17 EMC measurement of Skywan                                                                                            |                 |

| 5G                                                                                                                        | 48              |

| 2.18 Board prototype                                                                                                      | 49              |

| 2.19 Board plugged into the                                                                                               |                 |

| motherboard                                                                                                               | 50              |

|                                                                                                                           |                 |

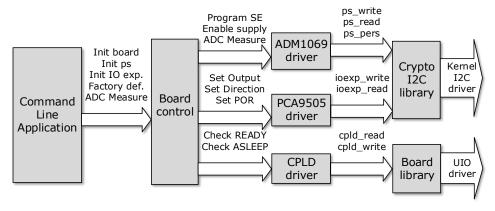

| 3.1 Structure of initialization SW                                                                                        | 51              |

| 3.2 Commands in Command line                                                                                              |                 |

| application                                                                                                               | 53              |

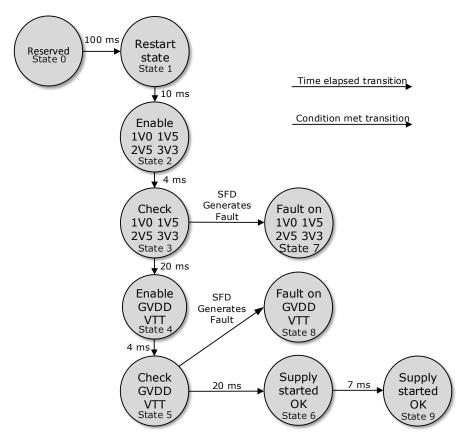

| 3.3 SE state machine                                                                                                      | 54              |

| 3.4 Measurement of power supplies vi                                                                                      | a               |

| ADM1069                                                                                                                   | 55              |

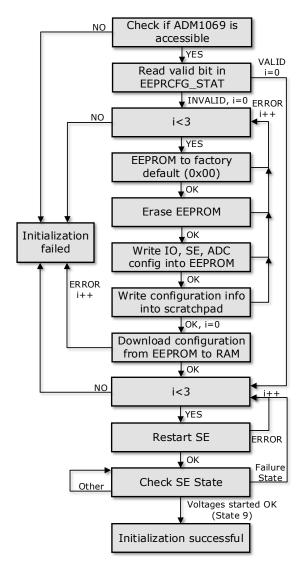

| 3.5 Power sequencer initialization                                                                                        |                 |

| sequence                                                                                                                  | 56              |

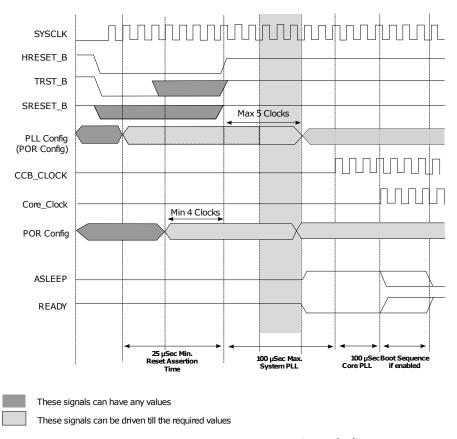

| 3.6 Power-on reset sequence (from                                                                                         |                 |

| $[31]) \dots \dots$ | 59              |

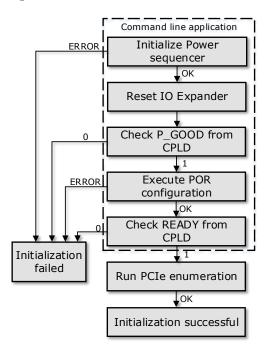

| 3.7 HW initialization sequence                                                                                            | 60              |

| 3.8 C291 detected on PCIe                                                                                                 | 60              |

|                                                                                                                           |                 |

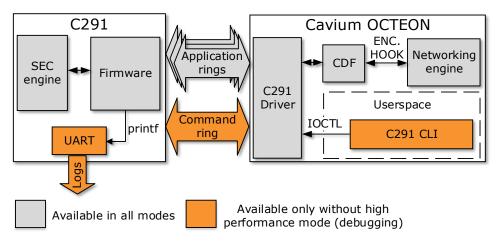

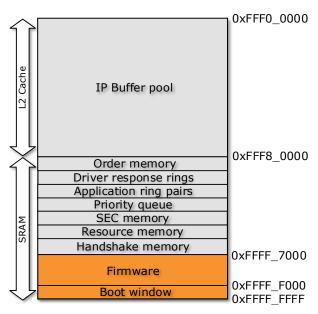

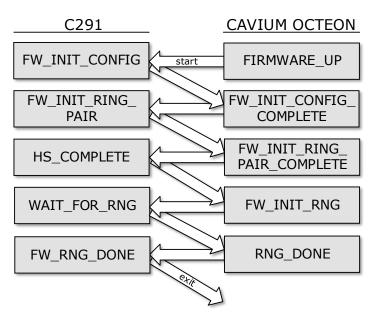

| 4.1 SW overview                                                                                                           | 61              |

| 1.2 Physical memory layout in C201                                                                                        | 63              |

| 4.3 Handshake between the driver and firmware                   | 64<br>69       |

|-----------------------------------------------------------------|----------------|

| 5.1 Thermal performance (no air flow-left, with air flow-right) | 75<br>75<br>77 |

|                                                                 |                |

# **Tables**

| 2.1 C29x family parameters(from                |    |

|------------------------------------------------|----|

| [14])                                          | 21 |

| 2.2 Power supply consideration                 | 24 |

| 2.3 Details of C291 power                      |    |

| consumption                                    | 26 |

| 2.4 C291 clock requirements                    | 27 |

| 2.5 DDR3 bytes connection                      | 38 |

| 2.6 PCIe lanes connection                      | 38 |

| 2.7 Impedance results                          | 43 |

| 2.8 Impedance equations                        | 44 |

| 3.1 EEPROM scratchpad registers .              | 55 |

| 3.3 POR configuration                          | 57 |

| $3.5~\mathrm{POR}$ configuration (continued) . | 58 |

| 4.1 Driver/Firmware pre-build                  |    |

| configuration                                  | 67 |

| 4.2 Pre-run configuration                      | 68 |

| 4.3 Functions implemented by                   |    |

| encryption hook                                | 71 |

| 5.1 Power consumption of the                   |    |

| Encryption board                               | 74 |

| 5.2 Response time of AES encryption            | 77 |

- **ADC** Analog to Digital converter.

- **BAR** Base address register. A register in PCI/PCIe for configuration of memory accesses.

- **BGA** Ball Grid Array. A type of Integrated circuit package with ball-shaped pins placed on a bottom side.

- **BGP** Border Gateway Protocol. A routing protocol.

- **BOM** Bill of Materials. A list of all used components on printed circuit board.

- CBC Cyclic block chaining

- **CLI** Command Line Interpreter/Interface.

- **COMe** Computer-on-Module. A standard for embedded boards.

- **CPLD** Complex Programmable Logic Device. A non-volatile programmable logic circuit.

- **CPU** Central Processing Unit.

- **DCR** Direct Current Resistance. A parasitic parameter of a real inductor.

- **DDR** Double Data Rate. An interface between a processor and memory chips/modules.

- **DFM** Design for manufacturability.

- **DMA** Direct Memory Access. A method for transferring the data in a system without putting a load on the processor.

- **DPA** Differential Power Analysis. A side channel attack on encryption system.

- **DRC** Design Rule Check.

- **DVB-S2** Digital Video Broadcasting Satellite. A protocol for high-bandwidth transfer over satellite.

**ECC** Error Correction Code. An approach of adding redundant information to memory to increase error immunity.

- **EP** Endpoint. A type of node in PCI Express terminology. More endpoints are allowed on one bus.

- **FEM** Finite Element Method. A numerical method for solving partial differential equations

- **FIPS** Federal Information Processing Standards. Set of standards by US government.

- FPGA Field Programmable Gate Array.

- **FSM** Finite state machine.

- **FW** Firmware

- **HW** Hardware

- **I2C** Inter-integrated circuit. A protocol for communication of processor and other chips inside a computer.

- IC Integrated Circuit

- IO Input/Output

- IP Internet Protocol

- **IP-Core** Intelectual Property Core. A reusable hardware design for digital integrated circuits.

- **LAW** Local Access Window. A memory window used to configure physical address map of a C291 processor.

- **LUT** Look-up-Table. Basic building block in Field programmable gate array circuits.

- MAC Medium Access Control.

- **MF-TDMA** Multi-frequency Time Division Multiple Access. A method for accessing physical layer by link layer.

- **MIPS** Mega Instructions per Second. Unit for measuring the performance of a processor.

- **MMU** Memory Managment Unit. A unit inside processor for translation of virtual addresses to physical addresses.

- **NDA** Non-disclosure Agreement.

- **NIST** National Institute of Standards and Technology.

**NMS** Network Management Service. Skywan 5G application for network configuration.

**OS** Operating System

**OSPF** Open Shortest Path First. A routing protocol.

**PCB** Printed Circuit Board.

**PDE** Partial Differential Equation.

**PCIe** Peripheral Computer Interconnect Express. A standard for connection of peripherals to a processor.

PKCAL Public key calculator mode. A mode of a C29x processor.

**POR** Power-on-Reset. A type of reset which always has to be executed after power-up of a processor.

**PWM** Pulse-width Modulation.

**QoS** Quality of Service. A feature of Skywan 5G allowing traffic prioritization.

**RC** Root Complex. A type of node in PCI Express terminology. Only one Root complex is allowed on one bus.

**RF** Radio Frequency

**RNG** Random Number Generator.

RT Real Time

**SEC** Security engine from Freescale/NXP

**SFD** Supply Fault Detector. A circuit inside ADM1069 used for detecting over/under voltage on input pins.

**SKMM** Secure key management mode. A mode of a C29x processor.

SMBus System Managment Bus

SoC System-on-Chip

**SO-DIMM** Small Outline Dual Inline Memory Module. A type of memory module used in notebooks and embedded systems.

SW Software

**TBD** To be defined. This feature is open for future modifications.

**TLB** Transaction Lookaside Buffer. A fast memory inside processor used for storing page tables by the operating system.

**TSEC** Tripple Speed Ethernet controller.

**UART** Universal Asynchronous Receiver Transceiver.

**USB** Universal Serial Bus. A communication protocol for connection of external peripherals.

# Chapter 1

## Introduction

Security is an important feature in today's world. Every area has a demand for secure handling of data. In communication industry, this demand is extraordinarily high. Secure communication provides a chance for services such as internet banking. Encryption has a rich mathematical background, often difficult to comprehend without deep knowledge of algebra. Engineers insight into this problem can be found in [1] and it is briefly discussed further in this chapter. From engineers point of view, the realization of encryption systems is especially interesting. During the implementation of an encryption system, many aspects have to be considered such as Performance, Security, Power requirements, Cooling, Scalability, Genericity or Level of realization.

The system whose encryption is implemented in this thesis is a satellite router used in traffic control, aviation, border control or military applications. The product can be categorized as "High reliability" device and thus guarantee proper operation is more important than short time to market. Reliability is directly proportional to design time spent. This thesis does cope with the design of prototype (keeping in mind manufacturability) and does not intend to develop the product into the state where it would be ready for market.

# 1.1 Skywan 5G

The fifth generation of Skywan satellite router is compact communication system providing satellite connectivity with custom MF-TDMA based protocol. An additional DVB-S2 demodulator is integrated within a unit. Each unit offers up to 16 frequency channels. The IP traffic data rates over TDMA are in the range 12-20 Mb/s. The IP level is handled by Linux networking engine with a strong connection to user-space IP stack. Modern routing protocols such as OSPF and BGP are used for route distribution. An extensive QoS system can prioritize the IP traffic.

The whole system is configurable by the database which is accessible via Web-based engine or NetConf protocol. From external interfaces, the device features 4 Ethernet ports, RS232 and coaxial cable for connection of satellite antenna. The mechanical format is intended for installation into a server rack. One unit is shown in Figure 1.1. The exact mechanical specification is not

1. Introduction

important for the purpose of this thesis. The main function of the device can be summed up as follow: provide reliable IP-over-Satellite connectivity.

Figure 1.1: Skywan 5G

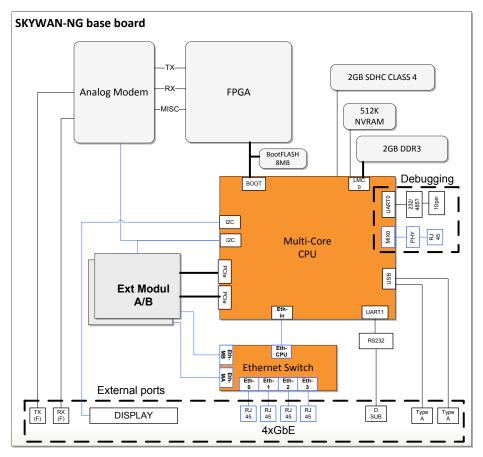

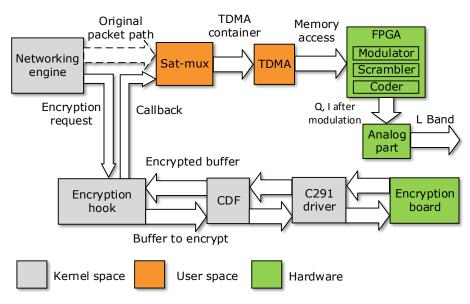

An internal architecture of Skywan 5G is shown in Figure 1.2. The IP traffic is handled by four core MIPS CPU (Cavium OCTEON CN6130). The device has a six-port Ethernet switch which can be programmed from the CPU. Satellite connectivity is achieved via connection of an external antenna to the Analog Modem which transmits/receives modulated signal at frequencies from 800 MHz up to 2,4 GHz (known as L-Band). The low level part of MF-TDMA protocol is implemented inside the FPGA. The device is equipped with two extension slots in the COMe format[10]. MIPS CPU is running Realtime Linux, kernel version 2.6.

The device is accessible over a set of buttons and display. The primary configuration interface is a Web browser application which provides full configuration features. The whole network can be configured from one node (after setting up default TDMA connectivity) over NMS application. These details are sufficient for the reader of the thesis. Further details about the device are stated in [2, 3].

## 1.2 Encryption requirements

Up to now, the encryption of the IP packets was left to the customer. The customer was responsible for using the encryption on the application level before the IP traffic entered the Skywan 5G. The main goal of this thesis is to design a simple extension of Skywan 5G, which would encrypt the IP traffic. The encryption has following requirements:

- Encryption throughput capable of encrypting all the IP traffic which is forwarded by the device. The maximal ethernet-ethernet forwarding performance is approximately 65 000 packet per second. Considering the ethernet jumbo frames (whose support is now being developed), it leads up to approx. 560 MB/s. This estimate assumes that packets forwarded from Ethernet to Ethernet would be encrypted. In the first step, only packets forwarded over satellite will be encrypted.

- Choose components which are suitable for FIPS certification of the system. This mainly concerns RNG engines.

- Have a possibility to remove the encryption from the system. Some markets are barely reachable with FIPS certified encryption. FIPS is

Figure 1.2: Internal architecture of Skywan 5G

not trusted all over the world due to suspicion of predictable (and thus prone to be hacked or spied on) RNG generators. Simply said: Politics play an important role within encryption and cyber security, thus being flexible and neutral is beneficial.

- Have a support of common encryption algorithms and protocols such as AES, RSA, Diffie-Helman, Elliptic curves, Hash functions and others.

- Low power consumption (5-10 W).

# 1.3 Possible realization

Any form of encryption is computationally demanding operation. Using software which would perform the encryption on the main CPU on Skywan 5G Motherboard is the easiest approach to implement. This solution is unacceptable since the CPU on the motherboard is already handling the IP traffic. The basic load (without IP traffic) of the CPU depends on the configuration of TDMA and QoS software modules. With increasing traffic, the CPU is loaded more up to the point where it is not able to handle all

1. Introduction

IP packets, and traffic drops occur. Encryption on the Cavium CPU would necessarily lead to lowering the packet forwarding performance (in packets-per-second) due to high computational requirements (and thus high CPU time). This effect is undesirable, and this kind of realization is not considered.

Another possibility is to use the FPGA on Skywan 5G motherboard and extend the design (which is handling the low-level part of TDMA protocol) with a set of encryption IP cores. The FPGA has a limited amount of LUTs (215 360), and the actual design uses more than half. Future extensions are planned for the FPGA design. These extensions require LUTs which would be used by encryption IP cores, which does not make the FPGA perspective for implementation of encryption.

CPU and FPGA are the only possible computational resources on the Skywan 5G motherboard and both are not suitable for the implementation of encryption. Extension of original Skywan 5G hardware must be considered. As can be seen from Figure 1.2 the Skywan 5G is equipped with two extension slots. One of the extension slots is intended for implementation of custom functionality such as encryption. This solution will be referred to as "internal module" solution. Another approach is to use some of the external interfaces to connect local module which would handle the encryption. This solution will be referred to as "external module" solution.

#### 1.3.1 Internal module

The internal module solution is extension board entirely hidden within Skywan 5G chassis plugged into COMe slot. The SW running on the board would use encryption resources on the extension board to perform the encryption operations. The extension module connector features PCIe interface, which can be used for connection of encryption module to the motherboard. This solution is easy to implement, but it has a limited potential. The whole device is strictly defined, and there is no space for third party additions into the implementation. From the business perspective, it is sometimes important to have flexibility for customers who do not trust the actual implementation of encryption.

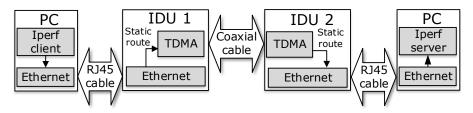

#### 1.3.2 External module

The external module can be connected to Skywan 5G by Ethernet. A custom Ethernet-based protocol would be used to communicate with the device. The encryption requests would be sent to the device via this protocol. The encrypted/decrypted data would be sent back by the external module again by Ethernet. This form of implementation is more difficult and time demanding since it requires not only the HW design but also the design of the Encryption protocol. Such a protocol is being developed by ND Satcom and it is intended to be used in combination with Internal module solution, thus creating a hybrid solution (having benefits of both solutions).

The protocol is named Open Encryption Interface (OEI) and it is described in [42]. Once the OEI is designed and supported by Skywan 5G it is possible

to give its details to third party customer who can design private encryption system. The system will be usable with Skywan 5G since all the communication would be according to the OEI. The implementation of this protocol (and its connection to configuration database) is a logical continuation of this thesis.

# 1.4 Background of Cryptology

Cryptology is a scientific discipline, part of Mathematics, which attempts to hide the content of data or messages. Cryptology can be divided into several disciplines. Two most important are: Cryptography and Cryptoanalysis. Cryptography develops algorithms which are transforming data so that only certain people can find out the original content. The original data are known as plaintext. The transformed data are known as ciphertext. Encryption is the process of changing a plaintext to a ciphertext. Decryption is the process of changing a ciphertext back into a plaintext. Cryptoanalysis is examining possible errors in cryptographic algorithms and it is trying to penetrate the encryption systems. An important part of encryption algorithm is a key which is a secret information (usually known only to a private group of communicants). A key is an additional input (apart from data) into encryption algorithm.

### Symmetric vs. asymmetric key ciphers

One of the criteria of the division is by the handling of a key. Symmetric key ciphers refer to set of algorithms which share the same key for encryption, decryption. To keep the encryption secure, this key must be secret known only to the participants of the communication. On the other hand, asymmetric ciphers distinguish between private and public keys. A private key is a secret kept between the participants of the communication. A public key is a key which is available to third parties which can monitor the communication process.

The disadvantage of symmetric key ciphers is that both communicants need to have common secret before the communication. To achieve this, another secure channel must be existing (in the old times a courier distributing highly guarded book, e.g. with keys for each day of the year). This is a weak spot of the whole process. If this private information leaked, anyone could decrypt the ciphertext and obtain the plaintext. The asymmetric key cryptography has algorithms with no prior common secret (the most common is explained below). It is common practice to use asymmetric protocol for private key exchange and use the private key subsequently for symmetric encryption.

#### Block vs. stream ciphers

Next criteria of the division is by the size of data chunk processed by an encryption algorithm. Since most of the data sizes are variable (e.g. each IP

1. Introduction

packet might have a different length), the size of the data only exceptionally matches the required size of input into encryption algorithm. The data need to be partitioned. The block ciphers divide the input data into blocks of fixed size and calculate the output of the same size. The encryption of each block is independent of the previous calculation (exceptions exist). This property makes the block ciphers good candidate for parallelization. The other type of cipher is a stream cipher which is processing each bit of the input data separately.

#### 1.4.1 Cryptoanalysis

As mentioned earlier, cryptoanalysis is a discipline which attempts to break (attack) the cipher algorithms. The easiest way how to break a cipher from observed ciphertext is to try all possible key combinations and execute decryption with each one of them. This process is known as brute-force attack. If the key has sufficient length, it is impossible to be execute such an attack in reasonable time even with all the computational resources available on Earth. When designing the encryption engine, one also has to consider future development of computation, such as Neural Networks, GPU development, the performance of supercomputers or special HW accelerators. Some of the key lengths which are secure today might be insecure in 10 years (e.g. DES was secure at the time when it was designed, but it was broken in 1997 [43]). A big question in the development of encryption algorithms is the progress in the quantum computing, which might cause a total breakdown of existing encryption systems as we know them today.

A successful attack on a cipher is any approach which requires fewer operations than brute force attack. Such an attack might still be implausible with the existing computational resources. Such attacks were executed on ciphers which are widely used today (e.g. AES). However, these algorithms remain secure since there are not enough computational resources to break them. Such an attack can be called "mathematical attack". It operates on the cipher as on a black box.

Next type of the attack is considering additional effects which are involuntarily given out by the implementation of the encryption system. It is known as a side-channel attack. The side channel attack operates rather on the implementation of the cipher than on the algorithm itself. A common approach of side channel attack is to measure secondary outputs of encryption system (CPU, FPGA or dedicated IC). Parameters of interest are power consumption, timing information (cache latencies) or electromagnetic radiation. These parameters are correlated with the key and plain text. One well-known side channel attack is DPA (Differential power analysis), where derivative of power consumption is the secondary output.

#### 1.4.2 Algorithms of interest

In the following subsections, the algorithms which are going to be used in Skywan 5G encryption system are described. A next step in the realization

of this system is to offer support for more encryption algorithms, achieve integration with embedded database and configuration engine and implement OEI as embedded SW module. These topics are beyond the scope of this thesis.

An important fact when choosing an encryption algorithm is public availability and openness. If the implementation is open, many people already attempted to break it and thus more secure it is (if it is still unbroken). A paraphrased motto from [1] says: Cryptography is not about hiding a necklace in a big city and saying: find the necklace without having any other details about the necklace. Cryptography is about locking a necklace in a box, providing all the construction information about the box and being calm that the necklace will stay inside the box!

#### Advanced encryption standard

Advanced encryption standard (shortly AES), originated in Rijndael algorithm, is a symmetric key block cipher. The algorithm was result of public competition from NIST. The winning proposal was submitted by Joan Daemen and Vincent Rijmen in [4]. These days it is one of the most used symmetric encryption algorithms. AES is operating on 128 bits (16 bytes) block size and using key sizes of 128, 192 or 256 bits. The number of iterations (rounds) for one AES calculation is key dependent (10,12 or 14 rounds). AES calculation is matrix based and input block is ordered into 4\*4 state matrix:

$$\begin{bmatrix} d_0 & d_1 & d_2 & d_3 \\ d_4 & d_5 & d_6 & d_7 \\ d_8 & d_9 & d_{10} & d_{11} \\ d_{12} & d_{13} & d_{14} & d_{15} \end{bmatrix}$$

$$(1.1)$$

The algorithm is described by following steps:

- 1. Execute key expansion according to key schedule algorithm. The algorithm description is omitted due to its complexity. The important outcome is that each round operates on a different key which is the output of key scheduling algorithm. Such a key is called round key.

- 2. Calculate initial round by bitwise XOR of the round key with the respective input byte.

- 3. Perform calculation of n-2 rounds, where n is the total number of rounds with following steps:

- a. Byte substitution: Each byte of the state matrix is replaced by another byte from Look-up-Table known as Rijndael S-box (the calculation of the S-box is omitted).

- b. Shift the matrix rows: Each byte element of the row k is shifted left k-1 times.

1. Introduction

c. Perform multiplication of each column by fixed matrix:

$$\begin{bmatrix}

2 & 3 & 1 & 1 \\

1 & 2 & 3 & 1 \\

1 & 1 & 2 & 3 \\

3 & 1 & 1 & 2

\end{bmatrix}$$

(1.2)

Since the elements of the state matrix are 8 bit wide, they are not treated as a decimal number, but as coefficients of a polynomial of order 7. Thus the multiplication of the column (vector) consists of polynomial multiplication and addition. Since the multiplication of polynomials of order 7 and 3 can result to a polynomial of order 10, the modulo of the multiplication result by polynomial  $x^8 + x^4 + x^3 + x + 1$  is executed and the coefficients of the polynomial remain one byte wide.

- d. Perform the XOR operation with current round key.

- 4. Calculate the last round which is the same as rounds in step 3 with leaving out the sub-step (c).

Detailed mathematical background of AES is beyond the scope of this thesis. AES algorithm is standardized by the NIST and it is adapted by the US government for the encryption of classified data. Successful side channel attacks on the implementations of AES exist (using cache timing attack on SW implementation as in [5]), but the cipher is still considered to be safe. The HW implementations use various methods of transforming the data before the encryption to avoid correlation between power consumption, key and plain-text as in [6]. A successful DPA attacks still exist [7].

#### Diffie-Hellman

Diffie-Hellman refers to asymmetric key encryption algorithm introduced in [8] which provides a mechanism for sharing a secret with no prior common secret. Development of this cipher was considered as the huge step in the field of cryptography. The high-level overview of the algorithm is following:

- 1. Let's assume two communicants A and B who have no prior common secret. They establish a common integers p and g, where g is primitive root modulo of p. They share these integers over a public channel.

- 2. Communicant A chooses a secret integer m and calculates  $M = g^m \, mod \, p$  and sends the M to communicant B.

- 3. Communicant B chooses a secret integer n and calculates  $N = g^n \mod p$  and sends the N to communicant A.

- 4. Communicant A calculates:  $k = N^m \mod p$ .

- 5. Communicant B calculates:  $k = M^n \mod p$ .

6. Now both communicants share common secret integer k. This integer can be used as a key to symmetric key encryption.

By definition modulo operation can be rewritten by adding (substracting) integer multiple of the divisor:

$$N = g^n \bmod p = g^n + pK \tag{1.3}$$

If we use the equation (3), substitute it into the equation from step 4 and apply binomic formula we get:

$$k = (g^{n} + pK)^{m} = \sum_{k=0}^{m} {m \choose k} (g^{n})^{m-k} (pK)^{k} =$$

$$g^{nm} + \sum_{k=1}^{m} {m \choose k} (g^{n})^{m-k} (pK)^{k}$$

(1.4)

Note that since all the members of binomic series are multiple of p it is clear that:

$$\left(\sum_{k=1}^{m} {m \choose k} (g^n)^{m-k} (pK)^k \right) \mod p = 0$$

$$(1.5)$$

which gives us:

$$k = (g^{n} + pK)^{m} = \left(g^{nm} + \sum_{k=1}^{m} {m \choose k} (g^{n})^{m-k} (pK)^{k}\right) \mod p =$$

$$(g^{nm} \mod p)$$

(1.6)

If the other communicant performs the same operation as in step 5 he obtains:

$$M = g^m \bmod p = g^m + pK \tag{1.7}$$

$$k = (g^{m} + pK)^{n} = \sum_{k=0}^{n} {n \choose k} (g^{m})^{n-k} (pK)^{k} =$$

$$g^{nm} + \sum_{k=1}^{n} {n \choose k} (g^{m})^{n-k} (pK)^{k}$$

(1.8)

1. Introduction

$$(g^{m} + pK)^{n} =$$

$$\left(g^{nm} + \sum_{k=1}^{n} \binom{n}{k} (g^{m})^{n-k} (pK)^{k}\right) \mod p =$$

$$(g^{nm} \mod p) + \left[\left(\sum_{k=1}^{n} \binom{n}{k} (g^{m})^{n-k} (pK)^{k}\right) \mod p\right] =$$

$$g^{nm} \mod p = k$$

$$(1.9)$$

which proves that both communicants reach the same shared secret k. Note that since the third person in the communication knows M, N, g, p he would need to solve following equations:

$$M = g^m \, mod \, p \tag{1.10}$$

$$M = g^m \bmod p \tag{1.11}$$

to be able to calculate k. This problem is known as discrete logarithm problem and there is no known algorithm for its calculation (other than brute-force). If g and p have sufficient length, it is impossible to iterate over all possible options with existing computational resources. It is recommended that p should have approximately 1000 bits and  $q \approx \frac{p}{2}$ .

#### Hash message authentication code

Hash message authentication code (shortly HMAC) which is used for verification of data integrity and authentication of a message. A hash function creates a small sequence from a bigger sequence, which logically implies that many inputs map to equal outputs. A typical requirement for a hash function is that minor change (e.g. one bit) in the input sequence causes a big change in the output sequence. Typically many bits need to be altered in the message to achieve the same output of hash function from original and altered data. The minimal amount of bits which must be altered in any of inputs (the whole input state space must be considered) to obtain equal output is known as Hamming distance. If fewer bit flips than Hamming distance occurs during the communication, the received hash and the calculated hash will not match and the error is detected. If the hash function is executed on private data (which are exchanged with symmetric encryption), any person in the middle can not produce the same output of the hash function. A match between received and calculated hash thus not only guarantees the data integrity but also the authenticity of the message.

Many hash functions exist, the most known are: SHA1, SHA2, SHA3 or MD5. The HMAC is a combination of such a hash function and secret cryptography key which was standardized in [9]. The main formula for calculation of HMAC function is:

$$HMAC = H(K' \oplus op, H(K' \oplus ip, m))$$

(1.12)

Where H is the hash function, K is the hash key, K' is derived hash key and m is the input message. The security of HMAC always depends on the underlying hash function. Today MD5 and SHA1 are not considered to be secure enough as standalone hash functions. However, the usage of SHA1 in the HMAC format remains in practical use for message authentication.

# Chapter 2

# Hardware design

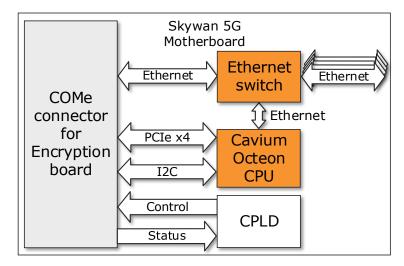

As mentioned in 1.3 there are two possible options of encryption system realization. An external module connected over Ethernet or internal PCIe extension module to the motherboard system. PCIe extension module solution was chosen. Two extension slots, A and B, in the format of COMe (Computer-On-Module) standard are available on Skywan 5G motherboard. The COMe standard is described in [10] and it has 220 signal and power pins. The exact pinout is omitted and can be found in the specification. Slot A is used for the implementation of Encryption module. Following interfaces of Skywan 5G Motherboard CPU are routed to the Slot A of COMe connector:

- PCIe Generation 2 with four lanes

- 1Gb Ethernet

- I2C

- UART

- Control and status signals

PCIe is used as the main communication interface between Motherboard and system running on Encryption module. The high-level diagram of all the connected interfaces to the COMe connector is shown in the Figure 2.1.

An important topic when designing an embedded system is the level at which the main features (encryption algorithms) are implemented. As it is common in engineering practice, different aspects are in mutual conflict. Due to this reason, it is important to lay out hardware realization requirements:

- Low power consumption of the system. 5-8 W is required, while the system should not at any case consume more than 10W.

- Encryption throughput of more than 560 MBs. The number is estimated from maximum packet forwarding rate of Skywan 5G (ethernet to ethernet) when considering ethernet jumbo frames.

- Component availability. It is important to use components which are not outdated, and their production is guaranteed for the whole lifetime of the project (5 to 10 years).

Figure 2.1: High-level diagram of a Encryption board interfaces

- A manufacturing prize per 1000 pieces. If the system is too expensive, it is not rentable for series manufacturing. Intended manufacturing prize of the whole system (board and components) is approximately 200 Euros per board when manufacturing 1000 boards.

- A level of commercial support and availability of integration tools for chosen components.

- A degree of realization difficulty. The products with good support (e.g. drivers, reference designs) are easier to implement.

With these points outlined there are several options available:

- SW realization Put CPU on the board and execute the encryption operations either in a firmware of the CPU or as a software module under an operating system. The advantage of this solution is a variety of suitable CPUs and availability of open source encryption libraries in C (e.g. in [11] or [12]). The disadvantage of this approach is the power consumption of such a CPU. CPUs with enough MIPS to calculate the encryption in SW can have higher power consumption than required.

- **HW** realization with custom chip There is an option to use a chip which only implements encryption. One such a chip is [13]. Since this chip is not available anymore and no similar chips were found it was decided not to use this option.

- FPGA implementation The idea of implementing the encryption operations in FPGA with either SoC or set of open source IP cores is the most optimal from the power vs. performance point of view. However, HW design would involve not only PCB design but also the design of SoC and its integration with PCIe interface. This additional design effort makes this task implausible within the time dedicated for this thesis.

CPU with HW Acceleration Using a CPU with dedicated HW block for encryption acceleration. Since encryption is HW accelerated this solution has low power consumption and simple usage since there is no need to design own SoC. The disadvantage of this approach is usually the price. Application specific CPUs are commonly more expensive than general purpose CPUs since the target market is smaller.

Based on these points it was decided to use a CPU with HW accelerated encryption.

# 2.1 System level design

Before drawing the schematic and designing the layout, it is important to design the product on a system level. System level design includes connection of interfaces, power supply design, and clock tree design. It is important to think about system initialization, proper reset, and configuration. Particular components must be selected to realize all the features. The outcome of this step is a group of block diagrams and tables which are introduced in each of the following sub-sections. The overall block diagram of the board is shown in Appendix A, Page 2. Following rules mainly drive this part of the design:

- Maximize the components re-usage from the motherboard of Skywan 5G. If some functionality is required, it is better to choose component which is already used on Motherboard, rather than using new component. This design rule minimizes the number of entries in Bill of Materials (BOM). With fewer entries in the BOM, the manufacturing is cheaper. With a higher amount of pieces from the same component the price per piece drops.

- Use reference materials and designs. It is not probable to make an error when using a component exactly as in reference design. It is common to rely on reference designs in engineering practice today.

- Avoid using deprecated and discontinued components. Once a finite supply of these components is sourced out, the device will not be manufacturable anymore!

- Use generic approach. It is better to implement a functionality available within a component and not use it during operation (not populate the component, resistor, etc.) than not implement it at all. This namely concerns the interfaces which are available in CPUs such as DDR3 or Ethernet. With this approach, there is a room for future development and extension of features without HW re-design.

#### 2.1.1 CPU selection

As mentioned above, CPU with HW accelerated encryption will be used. After research of available components in the CPU market, following options were considered:

- CAVIUM Nitrox PX family. This CPU family fits by encryption parameters, but after communication with the manufacturer, it was decided not to use this CPU since it is outdated and it is not recommended for new designs.

- CAVIUM Nitrox III family. This CPU family is intended for a high-end server application. CNN3510–C5 is the cheapest CPU from this family. This CPU costs approx. 300 USD/piece when bought 1000 pieces. A single piece of the CPU costs over 500 USD. The reference design of this CPU costs 25 000 USD. The power consumption of this CPU is no less than 13 W which is beyond the required maximum. Due to these reasons, it was decided not to use this CPU.

- Intel CPUs with a support of AES Instruction set. An appropriate CPU here is Intel Atom which is intended for low power applications. The usage of CPU from Intel requires NDA, acquiring one is a long-run process in case of Intel. A design of Intel-based system was considered infeasible within the duration of this thesis.

- C29x CPU family from Freescale Semiconductors (acquired by NXP Semiconductors). It is intended for server applications, and it has a wide selection of products. The overall prize/performance/power ratio of this CPU family is very lucrative. Furthermore, NXP Semiconductors offer reference design materials for free.

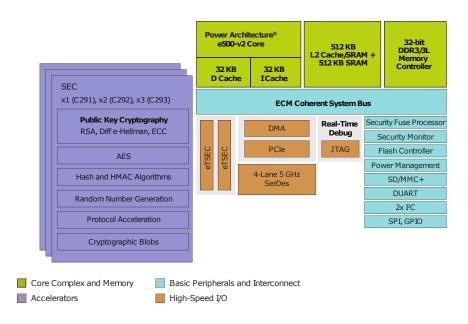

A C29x family of CPUs was chosen. This family of CPUs contains three products: C291, C292, C293. The last digit in the name of the CPU indicates the number of SEC engines (encryption accelerator from Freescale). The CPU has Power Architecture e500-v2 from IBM. The basic parameters of the CPU family are displayed in Table 2.1. Based on the encryption throughput and power consumption it was decided to use C291. The prize per one CPU within 1000 pieces batch is 112 USD. The block diagram of the CPU and the encryption algorithms supported by SEC are shown in Figure 2.2. More details are in [14]. The CPU contains true random number generator based on thermal noise which is NIST certified. This feature is important due to possible FIPS certification of the whole system. Furthermore, AES accelerator claims to be DPA resistant. C291 is available in convenient BGA package with 783 pins. The core frequency of C291 does not reach GHz region, which is also a critical aspect. Faster CPUs would generate EMI at L-Band frequencies, and it might disturb the satellite connectivity of the whole system.

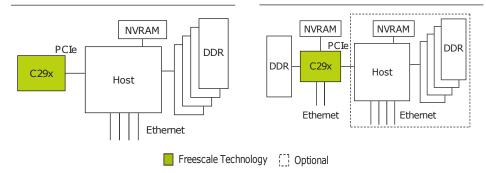

The CPU can operate in two modes: Public key calculator (PKCAL) and Secure Key Management Module (SKMM). In PKCAL the CPU works as a remote endpoint to a standalone system for encryption offload. In this mode most of the peripherals are disabled, and there is only small firmware running in the core of the CPU. There is no OS running on the CPU. In the SKMM the device should be running Linux OS, and it can be used for receiving Ethernet traffic and performing encryption operations on it. CPU makes use

|                                 | C291 | C292  | C293  |

|---------------------------------|------|-------|-------|

| CPU frequency [MHz]             | 667  | 1000  | 1200  |

| SEC frequency [MHz]             | 267  | 333   | 400   |

| DDR frequency[MHz]              | 800  | 1067  | 1200  |

| Typical power (65 °C) [W]       | 5    | 9     | 18    |

| 2048 bit private key operations | 8461 | 17587 | 31689 |

| Bulk encryption (AES-HMAC       | 6    | 9     | 12    |

| SHA-1 for SSL or Ipsec) [Gb/s]  |      |       |       |

**Table 2.1:** C29x family parameters(from [14])

Figure 2.2: C29x Block diagram(from [14])

of external DDR memory in this mode. The comparison of applications in both modes is shown in Figure 2.3. It is intended to use the CPU in PKCAL mode. To keep SKMM for future, all the interfaces must be implemented on the PCB! If used in PKCAL, it is possible not to populate several components to reduce the manufacturing costs.

C291 is equipped with following peripherals/interfaces:

- PCIe MAC controller. It is intended to use this controller as the main communication interface with the Cavium CPU on Skywan 5G Motherboard.

- 5 Ghz, 4 Lane SerDes (Serialize-deserialize) engine which can be used as physical layer transceiver for PCIe.

- DMA controller with external signals. This controller will be unused in the design. DMA operations are well supported by PCIe bus without a

## **Public Key Calculator**

# Secure Key Management Module

Figure 2.3: C29x modes of operation(from [14])

need of an external DMA engine. The C291 features bus mastering, so it can copy the data to/from motherboard without burdening Cavium CPU.

- eTSEC (Enhanced Tripple speed Ethernet Controller) offering 10 Mb/100Mb/1Gb Ethernet versions.

- 32-bit DDR3 memory controller with ECC. It is used only in SKMM module. This interface is the most difficult from the design point of view, but it was decided to implement it. Running the CPU in SKMM (booting Linux) is impossible without external memory.

- I2C. There are two I2C controllers each can be Master or Slave on I2C bus.

- SDHC controller. During operation in SKMM, CPU needs non-volatile storage for booting an OS. Flash card in MicroSD slot can be used for this purpose.

- Two UART interfaces. First UART interface will be routed to COMe connector. The second one can be used as debugging interface, and it will be routed to an external connector.

- SPI interface is unused. The original intention was to connect an external RNG based on the thermal noise of resistor. Since designing an analog RNG is a complex topic it was decided not to implement it.

- IFC (Integrated flash controller) interface is dedicated for connecting external flash memory. Flash memory can be used as Linux boot location when running in SKMM mode. To reduce the board costs, it was decided not to implement this interface. In the case of running SKMM microSD slot will be used as a boot location. Though microSD throughput is lower than IFC throughput, it is sufficient for booting Linux.

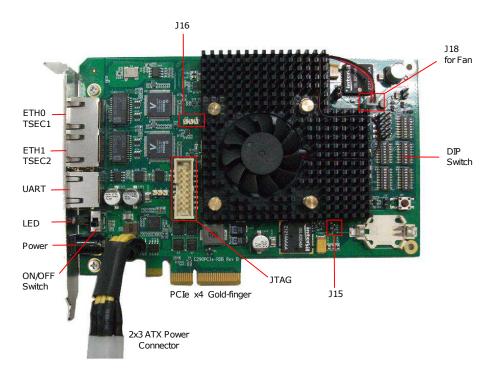

This CPU is well prepared for integration into commercial systems. The manufacturer offers reference design in the format of PCIe card (with C293). The schematic of this design can be downloaded from NXP website. The device can be bought for 990 USD which makes it cheap in comparison with CAVIUM reference designs. One such card was obtained, and it is shown in Figure 2.4. Software drivers, Linux ported to C291, host drivers for PKCAL mode, hardware layout, and other design documents are provided on CD.

Figure 2.4: C29x reference design

#### 2.1.2 System configuration and status

Digital boards often have non-volatile CPLD with design loaded during manufacturing. It provides board initialization, configuration, and test functions. A CPLD is on the motherboard of Skywan 5G and it has dedicated control and status signals for connecting the Extension slot. Due to this reason, there is no CPLD on the Encryption board. However, C291 CPU still needs to be configured. This configuration is called POR (Power-on-Reset) configuration. During the hard reset of CPU (pulling H\_RESET\_N input low) the CPU latches logical level at several pins. Based on these values, CPU is configured. At the time of Hard reset, all output pins are in a state of high-impedance. Connecting a weak pull-up or weak pull-down resistor then determines the logical level at reset. This approach is used in the reference design where pull-up or pull-down is selected via DIP switch. On the encryption board it is necessary to have the CPU reconfigurable from SW of Skywan 5G. Due to this reason, 40 bit IO expander is used. Serial resistor between the output of IO

expander and configuration pin is used to realize weak pull-up or pull-down function. If a pin is later driven to a different voltage by CPU, the device will not be damaged. IO Expander circuit is a slave device on the I2C bus, and it is connected to COMe connector. This way the CPU on the motherboard (I2C master) can configure the C291. The whole process is further described in Chapter 3.

#### 2.1.3 Power supply design

Since the C291 is the main component on the encryption board, the design of the power supply chain is driven by its requirements. It is important to realize that the board contains only digital components, there is no analog part on the board (except temperature sensor). This fact simplifies the design of power supply chain. In analog design, it is necessary to be careful about noise and use linear voltage controllers instead of DC-DC converters or switched controllers. The main attempt when designing the power supply chain is to the follow reference design and design of the motherboard. The reusability of components makes the design more flexible for future "mass" production.

| Name       | Voltage<br>[V] | C291<br>consumpti | Other<br>on consump-                                       | Overall consump-                                         |

|------------|----------------|-------------------|------------------------------------------------------------|----------------------------------------------------------|

|            |                | $[\mathbf{W}]$    | $egin{aligned} \mathbf{tion} \ [\mathbf{W}] \end{aligned}$ | $egin{aligned} 	extbf{tion} \ [	extbf{W}] \end{aligned}$ |

| $V_{CORE}$ | 1,0            | 8,194             | 0                                                          | 8,194                                                    |

| $V_{GVDD}$ | 1,5            | 0,81              | 2                                                          | 2,81                                                     |

| $V_{VTT}$  | 0,75           | -                 | -                                                          | -                                                        |

| $V_{3V3}$  | 3,3            | $0,\!15$          | approx. 1                                                  | $1,\!15$                                                 |

| $V_{2V5}$  | $^{2,5}$       | -                 | 0,5                                                        | 0,5                                                      |

| $V_{1V5}$  | 1,5            | $0,\!24$          | -                                                          | $0,\!24$                                                 |

**Table 2.2:** Power supply consideration

The 12V power supply available from COMe connector from a motherboard powers the whole Encryption board. No other power supply (like external connectors) will be used! The COMe specification states the maximal power consumption of the module to be 121W. This is far above the design goal, and there is no need to worry about the current capacity of COMe connector.

The first step of power supply design is to list all the supply voltages which will be used in the design and estimate maximal power consumption. Although the C291 is the main component, the consumption of other ICs is not negligible! The Table 2.2 shows the estimate of power consumption of each power supply.

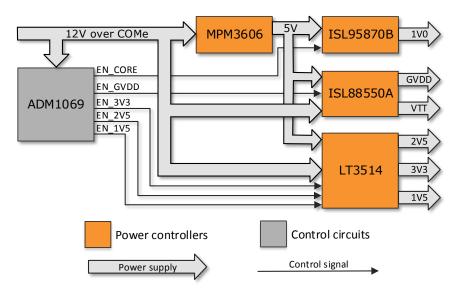

The second step is to create a voltage chain and define how are the voltages going to be generated. The designed supply chain is displayed in Figure 2.5. Most important ICs are further discussed in 2.3. As mentioned above it is common to use switching controllers in digital boards. Switching controllers have higher efficiency than linear controllers, but produce more

noise. Since all voltages listed in Table 2.2 are lower than the 12V supply voltage from the motherboard, step-down converters are used. Supply voltages for CPU core and DDR memory have the highest current consumption. This leads to controllers with external switching transistors connected in a bridge configuration.

Figure 2.5: Power supply chain

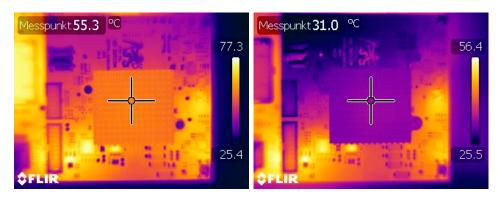

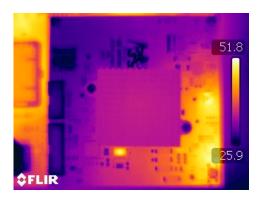

### 2.1.4 Thermal design

The datasheets of ICs usually state quiescent power, which is power consumed by a circuit just to maintain its state without performing any operations (no gates switching). Thus it is good to consider this information as required minimum and keep a reserve in the thermal design. Luckily the C291 documentation provides more accurate information about power consumption. The power is measured with Dhrystone algorithm running on the core, DMA engine in operation, and the SEC engine executing encryption. The average power is measured with 90% activity. The maximal power is measured with 100% activity.

The design must fulfill the requirements for SKMM although it will be used in the PKCAL mode. Furthermore, power consumption at highest temperature must be considered. The power consumption details are shown in Table 2.3. It is intuitively clear that the BGA package can not dissipate this amount of power without a heatsink. The maximal thermal resistance of a heatsink can be calculated:

$$P_{DIS} = \frac{T_j - T_A}{R} = \frac{105 - 45}{12} = 5W \tag{2.1}$$

$$P_{DIFF} = P_{MAX} - P_{DIS} = 9,54 - 5 = 4,54W$$

(2.2)

$$R_{HSMAX} = \frac{T_J - T_A}{P_{DIFF}} = 13, 2\frac{{}^{o}C}{W}$$

(2.3)

2. Hardware design

where R is a Thermal resistance of BGA package,  $P_{DIS}$  is Maximal power dissipated by BGA package,  $T_j$  is Maximal junction temperature,  $T_A$  is Ambient temperature,  $P_{MAX}$  is Maximal overall power consumption. The calculation was performed with the assumption of 4 layer PCB and no air flow! Since the final board has ten layers and the air flow above Extension Slot A in the Skywan 5G is not negligible, this calculation was taken only as guideline and heatsink with 16 °C/W was selected. Available heatsinks with lower thermal resistance were too expensive.

| Part of C291                                   | Power consumption [W] |

|------------------------------------------------|-----------------------|

| Average core power at 65 °C                    | 5,206                 |

| Maximal core power at 105 $^{\circ}\mathrm{C}$ | 8,194                 |

| DDR3 power at 800 Mhz                          | 0,81                  |

| PCIe power at x4 5GT/s                         | $0,\!24$              |

| m eTSEC power at $3.3V$                        | $0,\!07$              |

| Power of other peripherias                     | 0,08                  |

| Maximal overall power consumption              | 9,54                  |

**Table 2.3:** Details of C291 power consumption

## 2.1.5 Clock design

The clocking in the design can be divided into two parts: clocking of C291 and clocking of PCIe. The C291 clocking requires three separate clocks: System clock, DDR clock, and TSEC clock.

The second part of the clock design is the design of PCIe reference clock. In the terminology of PCIe standard, one of the devices always has to provide PCIe reference clock (100 or 125 Mhz). The clock is usually generated by a device which is Root-Complex (RC) in the PCIe system. It is not a rule, but a general habit. It is not the case in our system. Extension slot Ext A, used for Encryption board does not have the reference clock provided from the motherboard. Thus PCIe clock generator must be placed on the Encryption board. This architecture is used since the Extension slot A should be used for connection to stand-alone systems which would provide the reference clocks. All the clock signals and clocking requirements are listed in Table 2.4.

# 2.2 Tool selection

Schematic design and design of PCB is challenging task which requires complex software tools. Before selecting the particular tool it is important to lay down tool requirements:

The Design of multilayer boards with at least ten copper layers. The motherboard is designed with ten copper layers.

| Clock signal       | Required<br>fre-<br>quency<br>[MHz] | l Duty<br>cycle<br>[%] | Slew<br>rate<br>[V/ns] | Peak<br>period<br>jitter<br>[ps] |

|--------------------|-------------------------------------|------------------------|------------------------|----------------------------------|

| System clock       | 66-100                              | 40-60                  | 1-4                    | +-150                            |

| $(SYS\_REFCLK)$    |                                     |                        |                        |                                  |

| DDR clock          | 66-100                              | 40-60                  | 1-4                    | +-150                            |

| $(DDR\_REFCLK)$    |                                     |                        |                        |                                  |

| TSEC clock         | 125                                 | 47 - 53                | 3.33                   | +-150                            |

| $(TSEC1\_REFCLK)$  |                                     |                        |                        |                                  |

| PCIe clock         | 100  or                             | 45-55                  | -                      | 60                               |

| (PCIE_CLK_CPU_P/N) | 125                                 |                        |                        |                                  |

**Table 2.4:** C291 clock requirements

- Support for routing of differential pairs. This feature is important for routing of PCIe and Ethernet interfaces. Maintaining single-ended and differential impedance of differential pair is critical. The differential impedance depends on the distance of conductors. A slight mismatch in the distance between conductors within a pair can lead to catastrophic signal integrity.

- Length matching of single ended traces, differential pairs and deskewing of differential pairs. These features are most crucial for routing of parallel interfaces where all signal lines must have same electrical length. Designing DDR3 memory interface without the length matching feature is practically impossible.

- Generation of BOM (Bill of materials) and proper manufacturing data (Gen-Cad, Gerber, and drilling data).

Many tools are available from open-source, up to professional tools. The motherboard of Skywan 5G is designed with Orcad Cadence. It would be the best to design it with the same tool. However, license to this software is expensive (approximately 5000 EUR) and it was decided not to use it. A similar situation is with Altium Designer from Mentor Graphics. Since the board layout of Skywan 5G was outsourced, whole license would have to be bought. Possibly the tool would remain unused for a long time after finishing the Encryption board. Thus the regular support fee is the main reason why neither Altium nor Orcad was used.

An open source tool, KiCad [15], was chosen. It is a rapidly developing tool, and it supports all above-listed features. At the time of the design, version 4.0.4 was available. This tool supports scripting in Python which is a benefit in comparison to other programs. Each design file is stored in a structured text file which makes the design easily understandable. KiCad is multiplatform software so the same design can be used in many operating systems. A disadvantage of this tool is a lack of schematic and footprint

libraries. The online database does offer only basic footprints. Since the time scope of this project is relatively long, all schematic components and footprints were designed from scratch. The tool offers following subprograms:

- Electronic schematic editor Design of schematic.

- Schematic library editor Design of components in the schematic.

- Printed circuit board editor Design of boards layout and generation of manufacturing data.

- PCB footprint editor Design of IC footprints and mechanical objects.

- Gerber viewer Review of generated manufacturing data in Gerber format.

- Bitmap to Component Generator of decoration images in non-copper layers from Bitmaps.

- PCB Calculator Tool for impedance calculations of transmission lines.

- Worksheet layout editor Editor of page outline patterns that can be used across the design.

After design and manufacturing of the board, the tool was evaluated and compared with professional tools. The tool fulfilled the expectations and did not put any significant obstacles into the design process. However, the tool has many bugs causing freeze or crash of the program.

The performance of OpenGL implementation of routing tool is weak. When the design is complex, and it contains many components, it often freezes (mostly for actions like select and move track). Sometimes it is even more beneficial to delete the track and route it again since the tool is able to do it more fluently.

Several features are missing in the tool (in Comparison to Altium and Orcad), which makes the design process obscure and unnecessarily long. The estimate is that the design process was prolonged by at least by 50 hours due to all these flaws. Following notes were reported to KiCad community in online bug-tracker:

- Missing zone DRC. It is not possible to override global DRC rules with zone specific rules which make it difficult to route the signals out from a BGA package. This was especially problematic in case of DDR3 interface! The global design rules must be temporarily changed for the initial phase of routing and then modified for routing outside of BGA. Furthermore, the "Shove track" tool does not perform well as long as two tracks already corrupt actual DRC rules at some point (typically under the BGA).

- The length matching tool offers only one-time meander creation. Once the meander was created its length can not be tuned anymore. It consists of tiny lines which are not grouped into some "meander object". If one

wants to change the meander size, the whole meander must be erased (segment by segment), the line must be re-routed and length-matched again, which is very impractical.

- The management of differential pairs is catastrophic. The tool does not provide a way how to drag the differential pair together. One can either erase the pair (or its segment) and route it again, or drag each track individually, risk changing the distance between the pair members and violate the differential impedance! Additionally, the DRC check of differential pairs reports thousands of errors if the distance within a pair is the same as minimal track clearance. Luckily, the last problem can be fixed by lowering the minimal track clearance by 0.001 mm, since the problem exists only due to incorrect operation with floating point arithmetic in the tool.

- The layout designer can not design custom via stack-pad. This option makes it impossible to route high-speed boards operating at frequencies above 10 GHz.

- Missing FEM simulation. Design guidelines recommend performing FEM simulations after finishing the layout.

# 2.3 Schematic design

The design of schematic for digital boards is a simple task these days. After the specification of requirements on System level (discussed in the previous sub-chapter), the functionality must be implemented with either ICs or discrete components. Although the CPU is chosen at this point, the selection of the remaining components is not negligible. Choosing a wrong component can cause failure of the whole project. It is unusual to use discrete components for realization of some functionality (e.g. discrete power supply) since it is too expensive to manufacture the device with discrete components. Most of the functionality is thus realized with dedicated integrated circuits. The connection of the ICs is simple due to recommended applications which are available in the datasheets. However one must keep many issues and design approaches in mind. Following list names only a few of them:

- Be careful about recommended and limiting values of each input and output pin of every IC. Although exceeding the recommended values is not often critical, it is not good to use circuit permanently beyond the recommended values. Exceeding the maximal ratings is often critical and leads to damaging the circuit.

- Always check the thresholds of digital logic levels when connecting two digital ICs together. The minimum voltage for detection of logic 1 and the maximal output voltage of logic 0 must be fairly distant. This situation is getting even worse with noise! Noise between digital circuits

can cause wrong interpretation of logic level. This problem is in detail explained in [16].

- Beware of live-insertion effects. These include connection of IO pins of un-powered ICs to signals in logic one. If this effect occurs, the clamping diode in IO pin of unpowered IC will open, and the logic pin will be loaded with the power consumption of the whole chip. In the worst case, it can damage the circuit. This fact is especially important at I2C bus since it is the main method of accessing the Encryption board during its initialization.

- Use generic approach as much as possible. If a chip can be configured by pull-up or pull-down resistor, then it is good to implement both options and populate only one of the resistors. Leaving the board configurable without a need of redesign is practical. The only change needed, is a population of a different component.

- Use plenty of 0 Ohm resistors as switches. Sometimes it is convenient to have an option to disconnect certain functionality, and the best way to do it is not to populate 0 Ohm resistor, instead of cutting a wire if the resistor is not there.

## 2.3.1 Power supply

### Core power supply

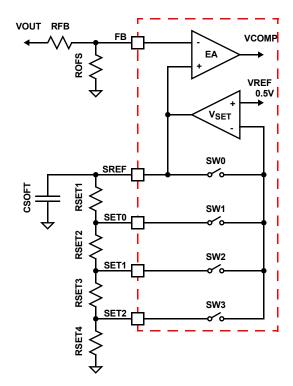

The core power supply is used to power the core of C291, system bus, SEC engines and main logic of peripherals. Its implementation is displayed in Appendix A - page 10. The used voltage controller is ISL95870B from Intersil. It is step-down buck PWM regulator intended for Mobile GPUs and Mobile memories. The output stage is driving two transistor half-bridge. SI4420BDY and SI4116DY transistors are used in the output stage, due to low channel resistance in turned on state. It is important to select an inductor with low DC resistance, due to high current flowing trough it. A nice feature of this circuit is available at RTN pin. This pin is used to balance the voltage offset of the ground plane. Feedback from the output voltage is connected via the voltage divider (feedback attenuator). Part of the ISL95870B circuitry is shown in Figure 2.6. The voltage controller regulates the voltage on the FB pin to be equal to the reference voltage. The reference voltage is set to 0.5 V via pull-up resistors on VD0/VD1 pins.

Following voltage divider is used to set the output voltage:

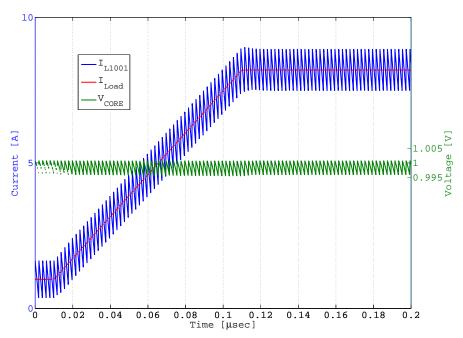

$$V_{FB} = V_{CORE} \frac{R_{1011}}{R_{1011} + R_{1013}} = 0,5$$

(2.4)

where  $V_{FB}$  is the voltage at feedback pin,  $V_{CORE} \approx 1V$  is the output voltage and  $R_{1011}$ ,  $R_{1013}$  are resistors in the voltage divider (marked as in Appendix A). The overcurrent protection is set with resistors  $R_{1018}$  and  $R_{1019}$

Figure 2.6: ISL95870B internal circuits(from [17])

it is calculated according to the datasheet [17]:

$$R_{1018} = \frac{I_{OC}.DCR}{I_{OCSET}} = 12,353K\Omega \to 12,1K\Omega$$

(2.5)