Faculty of Electrical Engineering

13137 Department of Radioelectronics

## Modeling of Spiral Polysilicon Divider in High Voltage MOSFET Transistor and Leakage

Ing. Václav Paňko

Ph.D. Programme: P2612 Electrical Engineering and Information Technology

Branch of study: Radioelectronics

February 2015

Supervisor: Doc. Ing. Josef Dobeš, CSc.

### Acknowledgement

I would like to thank my supervisor doc. Ing. Josef Dobeš, CSc. for his effective, methodical and technical support in my study. I very appreciate his help and his very useful advices and recommendation.

Many thanks belong to my colleagues from ON Semiconductor company especially to Ing. Stanislav Banáš and RNDr. Jiří Slezák, Ph.D. for their great help and support.

I would also like to thank my wife Ilona Paňková for her patience, motivation and understanding during my study.

#### **Declaration**

I declare that my doctoral dissertation thesis was prepared personally and bibliography used duly cited. This thesis and the results presented were created without any violation of copyright of third parties.

Prohlašuji, že jsem předloženou práci vypracoval samostatně a že jsem uvedl veškeré použité informační zdroje v souladu s Metodickým pokynem o dodržování etických principů při přípravě vysokoškolských závěrečných prací.

| V Praze dne 26. 2. 2015 |  |

|-------------------------|--|

|                         |  |

|                         |  |

|                         |  |

#### **Abstract**

The power consumption is one of the most important integrated circuit parameters. It is crucial to know the circuit's estimated leakage power since such a bound will enable the designers to ensure that the circuit meets the standby power constraints which impacts battery life in portable devices. It means that the leakage of MOSFET devices have to be modeled accurately. The first fundamental thesis aim is the accurate gate dimension dependent drain and source leakage modeling. The second fundamental thesis aim is the enhanced model of high voltage spiral divider that allows designing of circuits that can actively control the power consumption.

The leakage current in standard MOSFET models (BSIM3/BSIM4) is typically modeled by drain-bulk and source-bulk diodes. This modeling method does not consider the impact of several parasitic bipolar devices. For the accurate modeling the impact of the following bipolar transistors has to be considered: a lateral bipolar transistor drain-bulk-source, a vertical bipolar transistor drain-bulk-substrate (only in isolated structures), and a vertical bipolar transistor source-bulk-substrate (only in isolated structures). For example, the drain or source leakage as a function of gate length cannot be modeled without the scalable parasitic bipolar devices. This thesis demonstrates the structure of a proposed macro model, implemented scalability (in most cases nonlinear), developed scaling equations, and physical explanation of this scaling.

The splitting of the scaling equations to the area, perimeter and constant segments makes the higher geometry accuracy than the using a conventional area factor scaling. The parasitic BJTs are not active when MOSFET operates in the standard regime in ON state and take part only in drain and source leakage in OFF state or in non-standard operation where drain-bulk or source-bulk junction is in forward regime.

Finally, the comparison of measured data vs. simulation is presented in order to confirm the model validity. This model improvement solves not only leakage current scaling, but it also accounts for additional parasitic bipolar effects, such as current injection to the substrate.

Next chapters deal with the enhanced accurate DC and RF model of nonlinear spiral polysilicon voltage divider. The high resistance polysilicon divider is a sensing part of the high voltage start-up MOSFET transistor that can operate up to 700 V. The strong electric field in low doped drain drift area located under the low doped polysilicon spiral divider causes a lot of parasitic effects that have a significant influence on DC and RF device characteristics and makes divider ratio voltage and frequency dependent.

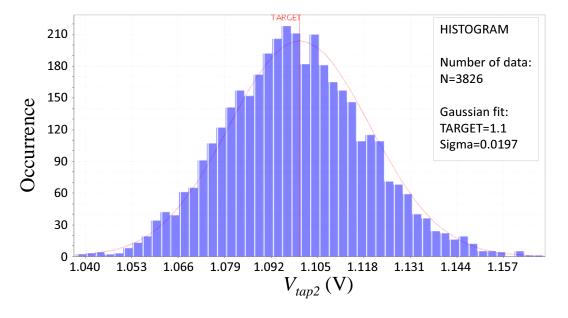

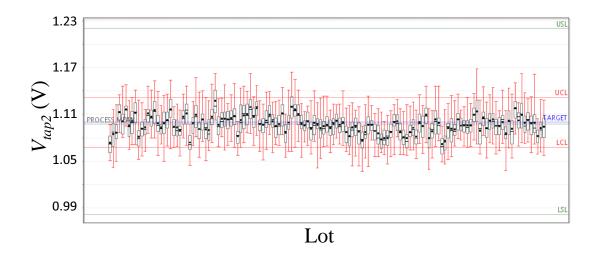

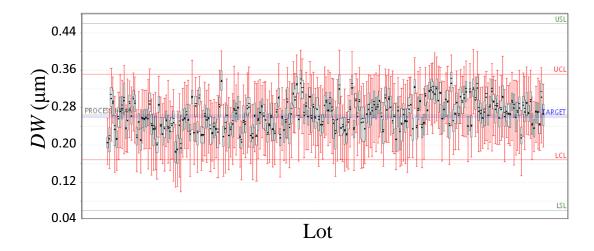

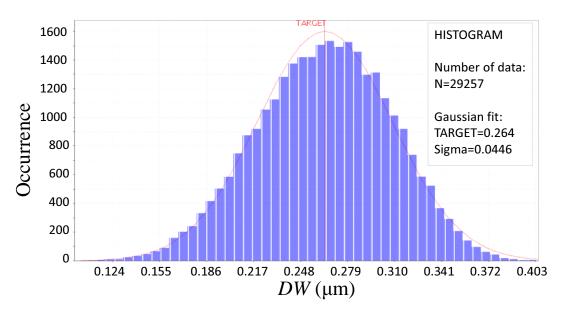

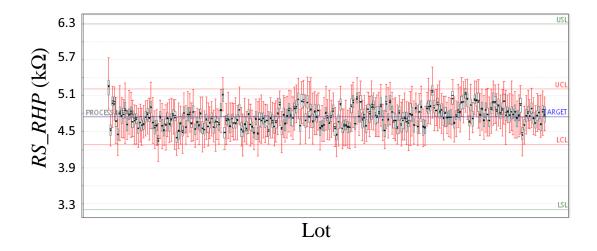

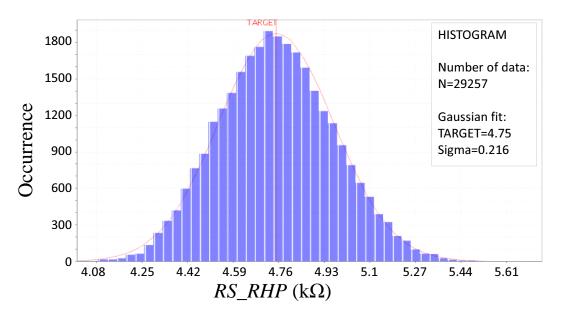

This thesis presents the structure of a proposed model, implemented voltage, frequency and temperature dependency, and scalability. A special attention is paid to the ability of the created model to cover the mismatch and influence of a variation of process parameters on the device characteristics. The statistical process variation model is created based on measurement about 30000 devices and mismatch model is based on measurement about 3000 devices.

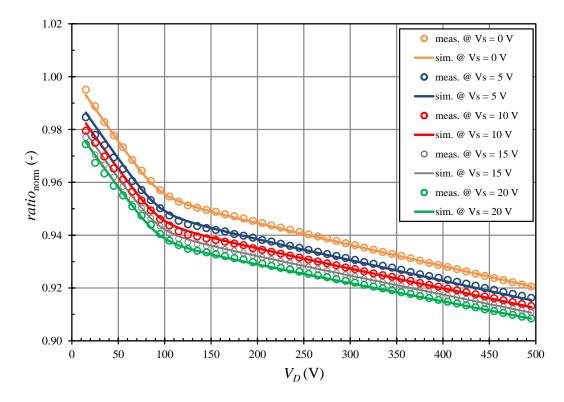

The modeling results are compared with measured data and the maximal relative model error of the divider ratio is less then 1.1~% and a typical application is also demonstrated.

**Keywords**: High voltage start-up MOSFET, pinch-off, high voltage spiral divider, leakage current, MOS, LDMOS, modeling, characterization, parameter extraction, statistical modeling.

#### **Abstrakt**

Spotřeba energie je jedním z nejdůležitějších parametrů integrovaných obvodů. Je velmi důležité znát odhadovanou velikost svodového proudu, což návrhářům umožní zajistit, aby obvod splňoval požadavky na pohotovostní režim, který má vliv na výdrž baterie v přenosných zařízeních. To znamená, že svodový proud v MOS tranzistorech musí být modelován přesně. Prvním zásadním cílem práce je přesné modelování svodového proudu drainu a source závislého na rozměrech hradla. Druhým zásadním cílem práce je vylepšený model vysokonapěťového spirálového děliče, umožňující navrhování obvodů, který může aktivně řídit spotřebu energie.

Svodový proud ve standardních MOSFET modelech (BSIM3/BSIM4) je typicky modelován diodami drain-bulk a source-bulk. Tato metoda nebere v úvahu vliv několika parazitních bipolárních tranzistorů. Pro přesné modelování vliv následujích bipolárních tranzistorů musí být vzat v úvahu: laterální bipolární tranzistor drain-bulk-source, vertikální tranzistor drain-bulk-substrát (v i izolovaných strukturách) a vertikální tranzistor source-bulk-substrát (v i izolovaných strukturách). Například svodový proud drainu a source jako funkce délky hradla nemůže být modelován bez parazitních bipolárních tranzistorů závislých na rozměru hradla. Tato práce demonstruje strukturu navrženého makro modelu, implementovanou rozměrovou závislost (ve většině případů nelineární), vyvinuté rozměrově závislé rovnice a fyzikální vysvětlení.

Rozdělení rozměrově závislých rovnic na složku plošnou, obvodovou a konstantní způsobuje větší přesnost modelu než použítí konvenční závislosti přes faktor plochy. Parazitní BJT nejsou aktivní, když MOSFET pracuje ve standardním režimu v ON stavu, ale mají vliv na svodový proud, pokud je MOSFET v OFF stavu nebo v nestandardním zapojení, kdy je drain-bulk nebo source-bulk přechod v propustném stavu.

Nakonec je prezentováno porovnání měřených a simulovaných dat, aby se potvrdila platnost modelu. Toto vylepšení modelu řeší nejen závislost svodového proudu na rozměru hradla, ale bere v úvahu také další bipolární efekty, například injekci nosičů do substrátu.

Další kapitoly se zabývají vylepšeným přesným DC a RF modelem nelinárního spirálového polykřemíkového napětového děliče. Vysoce rezistivní polykřemíkový dělič je snímací částí vysokonapětového start-up MOSFET tranzistoru, který může pracovat až do 700 V. Vysoké elektrické pole v nízko dotovaném polykřemíkovém spirálovém děliči způsobuje mnoho parazitních efektů, které mají významný vliv na DC a RF charakteristiky součástky a způsobuje napěťově a frekvenčně závislý poměr děliče.

Práce prezentuje strukturu navrženého modelu, implementovanou napěťovou, frekvenční, teplotní a rozměrovou závislost. Speciální pozornost je věnována schopnosti vytvořeného modelu pokrýt mismatch a vliv variace procesních parametrů na charakteristiky součástky. Model statistické variace procesu je vytvořen na základě měření asi 3000 součástek a mismatch model je založen na měření asi 3000 součástek.

Výsledky modelování jsou porovnány s měřenými daty a maximální relativní chyba modelu poměru děliče je menší než 1.1 % a typická aplikace je také demonstrována.

**Klíčová slova**: Vysokonapětový start-up MOSFET, prahové napětí, vysokonapětový spirálový dělič, svodový proud, MOS LDMOS, modelování, charakterizace, extrakce parametrů, statistické modelování

**Překlad titulu**: Modelování spirálového polykřemíkového děliče ve vysokonapěťovém MOSFET tranzistoru a svodového proudu

### **Contents**

| 1 In         | troductiontroduction                                        | 1  |

|--------------|-------------------------------------------------------------|----|

| 1.1          | Current Situation of the Studied Problem (State-of-the-Art) | 2  |

| 1.2          | Aims of the Thesis                                          | 5  |

| 1.3          | Used Modeling Methodology                                   | 6  |

| 2 <b>G</b> a | ate Dimension Dependent Drain and Source Leakage            | 10 |

|              | Introduction                                                |    |

| 2.2          | P-channel MOSFET                                            |    |

|              | 2.2.1 Crossection and modeling                              |    |

|              | 2.2.2 Substrate vertical parasitic BJTs                     |    |

|              | 2.2.3 Lateral parasitic BJT                                 |    |

| 2.3          | N-channel LDMOS                                             |    |

|              | 2.3.1 Crossection and modeling                              |    |

|              | 2.3.2 Substrate vertical parasitic BJTs                     |    |

|              | Chapter Summary                                             |    |

|              | V Start-up MOSFET Description                               |    |

|              | Structure Description                                       |    |

|              | HV MOSFET Applications                                      |    |

| -            | piral Divider Modeling                                      |    |

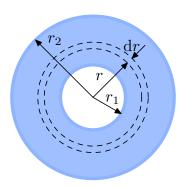

|              | Spiral Element Length                                       |    |

|              | Divider Ratio Modeling                                      |    |

| 4.3          | Divider Dynamical Modeling                                  |    |

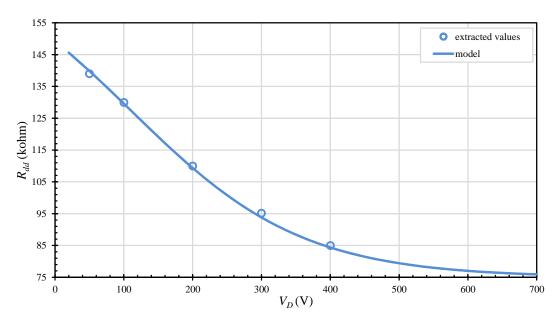

|              | 4.3.1 Spiral segments resistance                            |    |

|              | 4.3.2 Spiral to silicon capacitance                         |    |

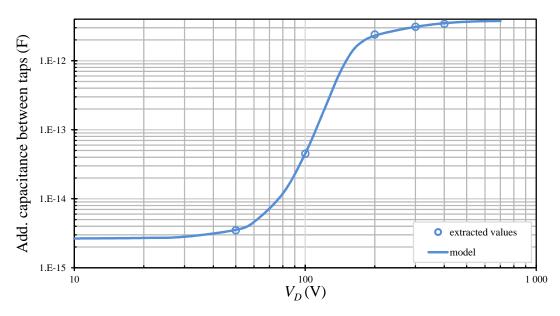

|              | 4.3.3 Additional capacitance between taps                   |    |

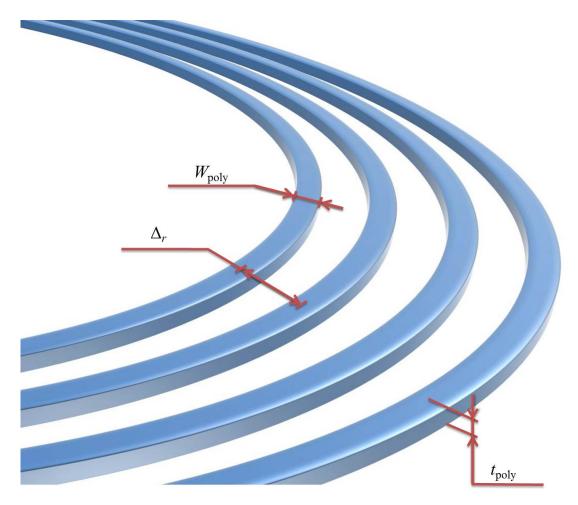

|              | 4.3.4 Turn-to-turn polysilicon capacitance                  |    |

| 4.4          | 4.3.5 Ptop resistance                                       |    |

|              | Chapter Summary                                             |    |

|              | ivider Statistical Modeling                                 |    |

|              | Mismatch Variation Modeling                                 |    |

|              | onclusion                                                   |    |

|              | eferences                                                   |    |

|              | st of Candidate's Works                                     |    |

| LI           | List of Candidate's Works Relating to the Doctoral Thesis   |    |

|              | List of Candidate's Works  List of Other Candidate's Works  |    |

|              | Response and Reviews                                        |    |

| Δ ΔΙ         | bbreviations and Symbols                                    |    |

|              | sed Equipments and Software                                 |    |

| <i>-</i> 0.  | Equipments Used for Measurement                             |    |

|              | Used Software                                               |    |

| C C:         | andidate's Short Curriculum Vitae                           |    |

|              | andidate's Short Curriculum Vitae                           | 60 |

### **List of Tables**

| 2.1. | Extracted parameters of the parasitic vertical BJTs (for MOSFET) | 16 |

|------|------------------------------------------------------------------|----|

| 2.2. | Extracted parameters of the parasitic lateral BJT (for MOSFET)   | 20 |

| 2.3. | Extracted parameters of the parasitic vertical BJT (for LDMOS)   | 27 |

| 4.1. | Calculated spiral parameters                                     | 36 |

| 4.2. | Calculated parameters of the spiral segments                     | 37 |

| 4.3. | Extracted ratio model parameters                                 | 39 |

| 4.4. | Extracted resistance temperature model parameters                | 41 |

| 4.5. | Extracted spiral capacitance model parameters                    | 44 |

| 4.6. | Extracted tap capacitance model parameters                       | 48 |

| 4.7. | Extracted $R_{\rm dd}$ resistance model parameters               | 51 |

## **List of Figures**

| 1.1. | World electricity consumption                                                 | 1  |

|------|-------------------------------------------------------------------------------|----|

| 1.2. | Total chip dynamic and static power dissipation trends                        | 2  |

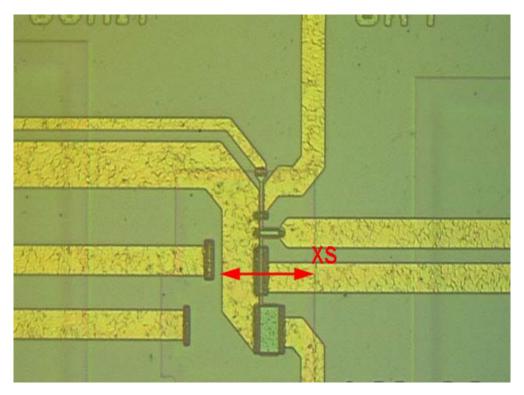

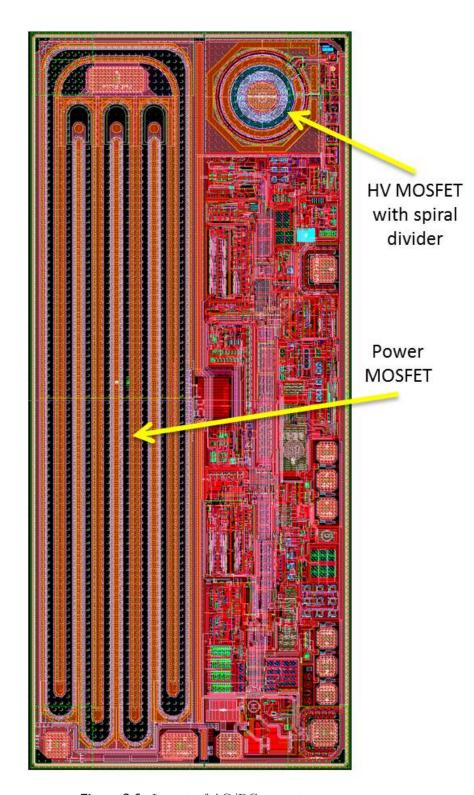

| 1.3. | Layout of HV start-up MOSFET                                                  | 4  |

| 1.4. | Characterization test chip                                                    | 6  |

| 1.5. | Process control monitoring test chip                                          | 7  |

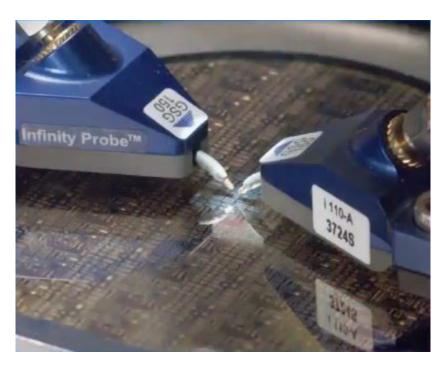

| 1.6. | On-wafer S-parameters measurement                                             | 7  |

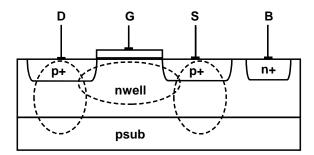

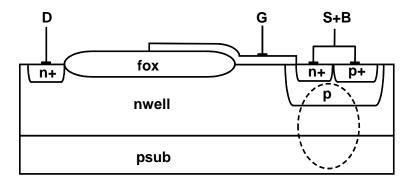

| 2.1. | Crossection of P-channel MOSFET                                               | 11 |

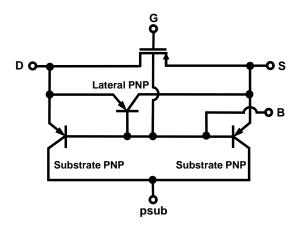

| 2.2. | Updated MOSFET model with parasitic BJTs                                      | 11 |

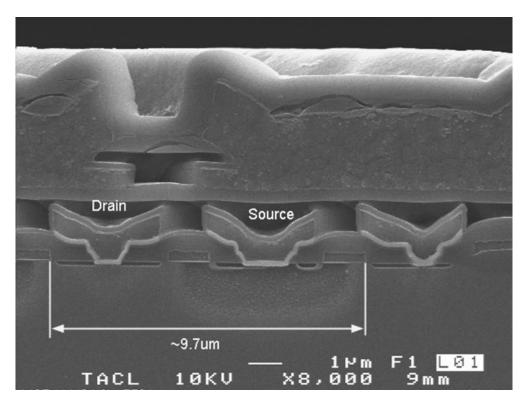

| 2.3. | Photo of the chip for construction analysis                                   | 12 |

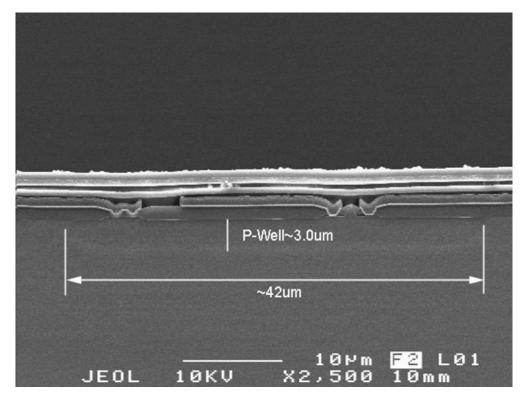

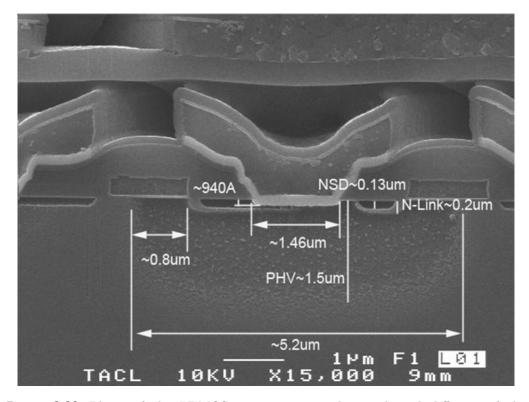

| 2.4. | Photo of the MOSFET construction analysis - bulk                              | 12 |

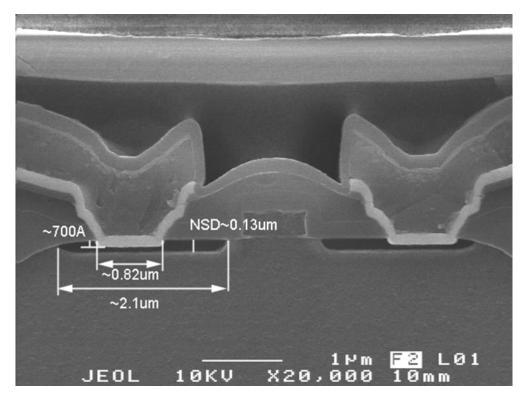

|      | Photo of the MOSFET construction analysis - drain, source and gate            |    |

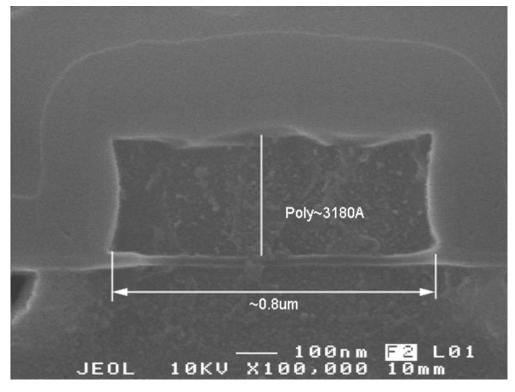

| 2.6. | Photo of the MOSFET construction analysis - gate                              | 13 |

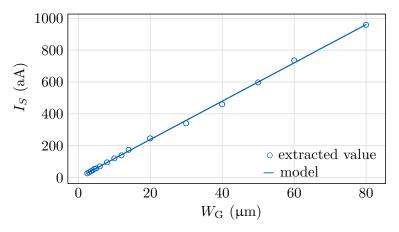

| 2.7. | Vert. BJT: $I_S$ vs $W_G$ .                                                   | 14 |

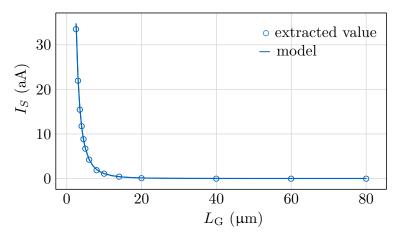

| 2.8. | Vert. BJT: $I_S$ vs $L_G$ .                                                   | 14 |

| 2.9. | Vert. BJT: $I_S$ vs $W_G/L_G$                                                 | 15 |

|      | Vert. BJT: $B_F$ vs $W_G$ .                                                   |    |

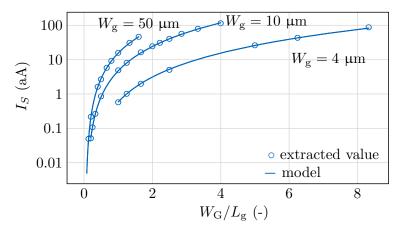

|      | Lat. BJT: $I_S$ vs $W_G$ .                                                    |    |

|      | Lat. BJT: $I_S$ vs $L_G$                                                      |    |

|      | Lat. BJT: $I_S$ vs $W_G/L_G$                                                  |    |

|      | The leakage current redistribution in MOSFET with $L_{\rm G}=2.5~\mu{\rm m}$  |    |

|      | The leakage current redistribution in MOSFET with $L_{\rm G}=10.5~\mu{\rm m}$ |    |

|      | Lat. $B_F$ vs $W_G$                                                           |    |

|      | $I_{\rm D}V_{\rm G}$ characteristics of MOSFET without parasitic BJTs         |    |

|      | $I_{\rm D}V_{\rm G}$ characteristics of MOSFET with parasitic BJTs            |    |

|      | Crossection of N-channel LDMOS with indication of parasitic BJT               |    |

|      | Updated LDMOS model with parasitic BJT                                        |    |

|      | Photo of the LDMOS construction analysis - drain, source and gate             |    |

|      | Photo of the LDMOS construction analysis - gate                               |    |

|      | Vertical parasitic BJT: $I_S$ vs $W_G$                                        |    |

|      | Vertical parasitic BJT: $B_F$ vs $W_G$                                        |    |

|      | $I_{\rm D}V_{\rm G}$ characteristics of LDMOS without parasitic BJT           |    |

|      | $I_{\rm D}V_{\rm G}$ characteristics of LDMOS with added parasitic BJT        |    |

|      | The simplified 3D structure of HV start-up MOSFET transistor                  |    |

|      | Acceptor, donor and total doping concentration                                |    |

|      | Schematic symbol of HV start-up MOSFET                                        |    |

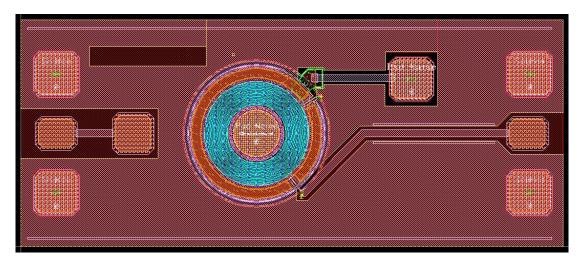

|      | Layout of HV start-up MOSFET                                                  |    |

|      | The simplified circuit of AC/DC convertor                                     |    |

|      | Layout of AC/DC convertor                                                     |    |

|      | Equivalent lumped 3D circuit                                                  |    |

|      | Equivalent lumped 2D circuit                                                  |    |

|      | Drain and source voltage dependency of normalized ratio                       |    |

|      | Measurement setup for divider AC measurement                                  |    |

|      | Layout of HV MOSFET for divider AC measurement                                |    |

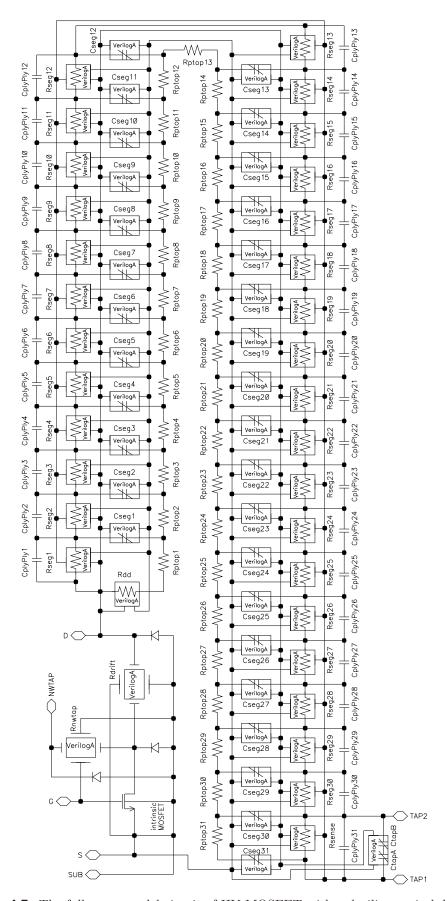

|      | The full macromodel circuit of HV start-up MOSFET with polysilicon            | 41 |

| 7.1. | spiral divider                                                                | 42 |

## List of Figures cont.

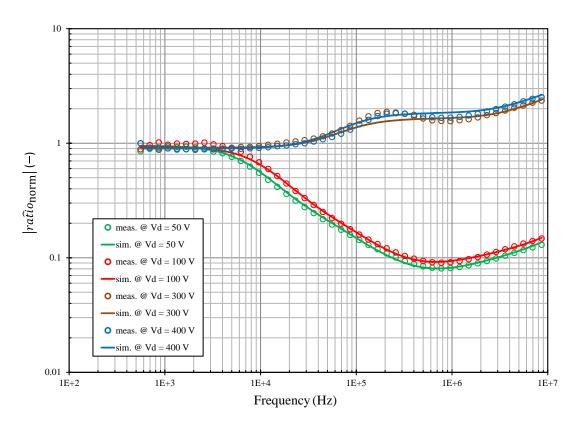

| 4.8.  | Magnitude of normalized complex divider ratio                                    | 43 |

|-------|----------------------------------------------------------------------------------|----|

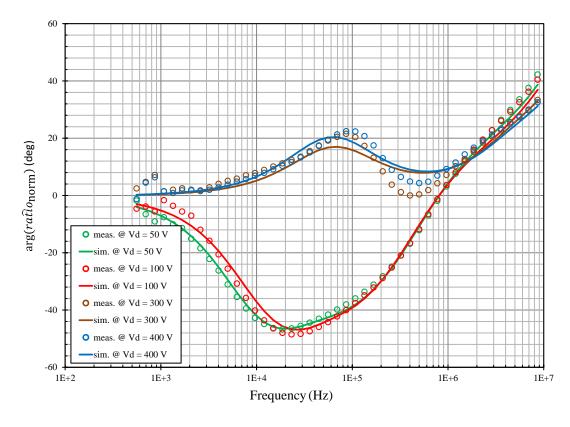

| 4.9.  | Phase of normalized complex divider ratio                                        | 43 |

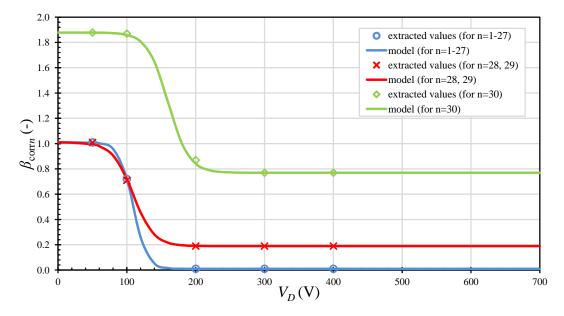

| 4.10. | Voltage dependency correction coefficient $\beta_{corn}$                         | 44 |

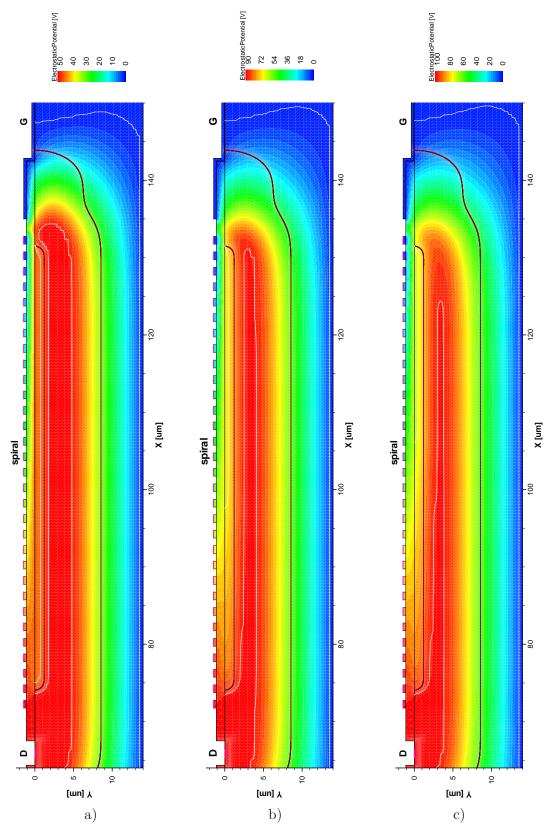

| 4.11. | TCAD simulation of electrostatic potential for $V_D$ =50, 90, 150 V              | 45 |

| 4.12. | TCAD simulation of electrostatic potential for $V_D$ =150, 200, 400 V            | 46 |

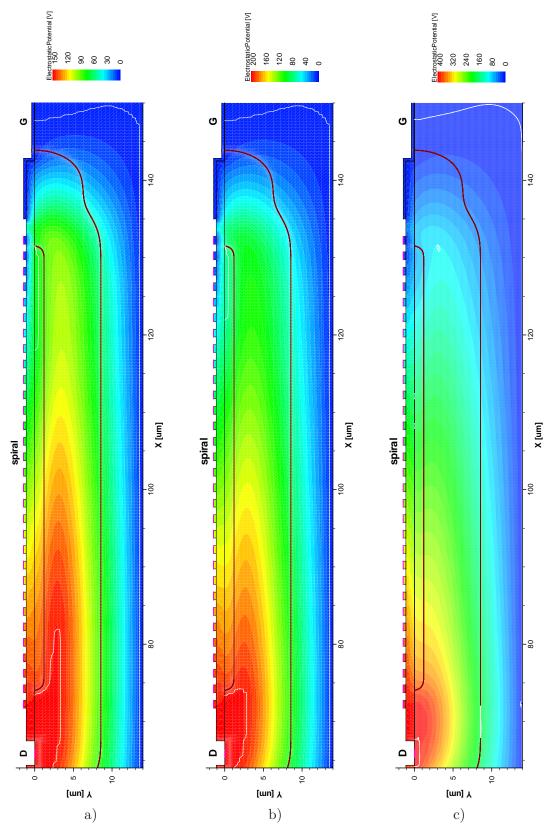

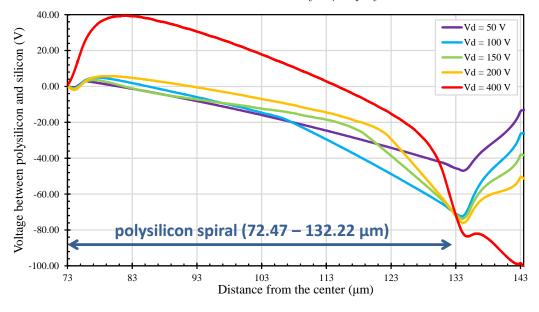

| 4.13. | Electrostatic potential distribution                                             | 47 |

| 4.14. | Voltage between polysilicon and silicon                                          | 47 |

| 4.15. | Additional capacitance between taps                                              | 48 |

| 4.16. | Turn-to-turn polysilicon capacitance parameters                                  | 49 |

| 4.17. | Calculation of annulus resistance                                                | 50 |

| 4.18. | Voltage dependent resistor $R_{\rm dd}$                                          | 51 |

| 5.1.  | The histogram of measured and simulated electrical parameter $V_{\mathrm{tap2}}$ | 52 |

| 5.2.  | The boxplot of measured electrical parameter $V_{tap2}$                          | 53 |

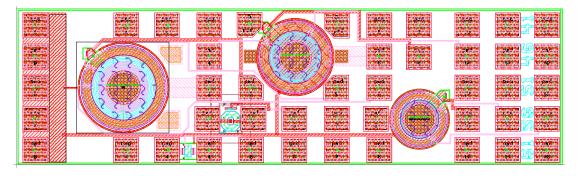

| 5.3.  | Layout of HV MOSFET placed on the SGPCM test chip                                | 53 |

| 5.5.  | The boxplot of measured electrical process parameter DW                          | 54 |

| 5.4.  | The histogram of measured and simulated electrical process parameter DW .        | 54 |

| 5.7.  | The boxplot of meas. el. process parameter RSRHP                                 | 55 |

| 5.6.  | The histogram of meas. and sim. el. process parameter RSRHP                      | 55 |

# Chapter 1 Introduction

Nowadays, the power consumption is one of the most important integrated circuit parameters. Almost all semiconductor devices manufacturers make an effort to design products with the lowest power consumption as reasonably achievable.

As an example, how important the power consumption is, are the following independent statistics and analysis from U.S. Energy Information Administration and analysis from ON Semiconductor company<sup>1</sup>). Every year more than 160 billion kWh are consumed in residential homes in the United States. 3–4 % of electricity consumed in the United States each year is lost inside inefficient power supplies of products like

- desktop computers,

- notebook computers,

- televisions,

- game consoles,

- DVD players, etc.

Employing energy efficient solutions can increase the efficiency of home electronic products by 20 %, which means reducing the energy consumption by more than 32 billion kWh per year, reducing Carbon ( $\rm CO_2$ ) emissions by 43.5 billion pounds, eliminating 1 million kilotons of  $\rm CO_2$  emissions over 10 years, and eliminating 100 new coal fired power plants.

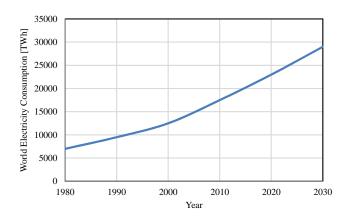

Increasing the efficiency of these products by 20 % could mean more than \$3.2 billion in energy savings per years in the United States alone. Or enough power to supply Alaska, Delaware, Hawaii, Idaho, and Maine combined. It is interesting to imagine the impact globally. Increasing of the world electricity consumption is expected as is shown in Fig 1.1. Considering this facts, minimizing the power consumption becomes inevitable.

Figure 1.1. World electricity consumption

<sup>&</sup>lt;sup>1</sup>) Adopted from Rory Gonzalez, *ON Semiconductor*, available at https://www.youtube.com/watch?v=3NUSMlilQdw. © Semiconductor Components Industries, LLC, 2011. See App. D.

## 1.1 Current Situation of the Studied Problem (State-of-the-Art)

The power consumption can be divided into the two main categories [1]:

- Active (dynamic) power: arises from the repeated capacitance charge and discharge through parasitics on the output of the gates.

- **Static power**: caused by currents that leaks through transistors even when they are turned off.

There are five main leakage current sources (causing static power consumption) in a CMOS circuits [2]:

- **Subthreshold leakage** in the channel of an OFF transistor between the source and drain terminals.

- **Source/drain junction leakage** (reverse-biased).

- **Gate leakage** (tunneling current through the gate oxide insulation).

- **Gate induced drain leakage** GIDL (due to the high electric field effect in the drain junction, can be minimized by the doping profile in the drain).

- **Punchthrough** (occurs in short channel devices, can be controlled by using implants at the bottom or the edges of the source and drain junction boundaries).

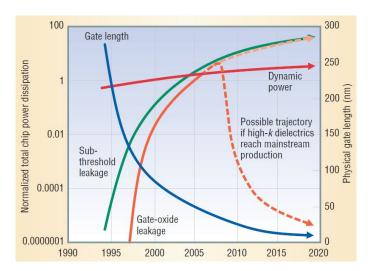

Exponential increases projected for the two principal components of static power consumption: subthreshold leakage and gate leakage shows Fig. 1.2.

Figure 1.2. Total chip dynamic and static power dissipation trends based on the International Technology Roadmap for Semiconductors. The two power plots for static power represent the 2002 ITRS projections normalized to those for 2001. The dynamic power increase assumes a doubling of on-chip devices every two years. Reprinted from "Leakage Current: Moore's Law Meets Static Power," by N. S. Kim, et al., 2003, *Computer*, 36(12), p. 69. © 2003 by the IEEE. Reprinted with permission, see App. D.

Reducing the supply voltage decreases the power consumption but also reduces the circuit's maximum operating frequency.

Here are other more sophisticated techniques for minimizing the power consumption[3].

- Active (dynamic) power: The following techniques are used to minimize active power consumption:

- Clock gating.

- **Voltage islands** (Lower operating voltages reduces active power in a quadratic way. Using voltage islands in areas of a chip where performance and speed of that functional unit is non-critical saves the power).

- Dynamic voltage and frequency scaling (DVFS) (The active operating voltage and frequency are changed based on demand of the load. High load = nominal voltage and frequency, low load = the voltage or the frequency is scaled down to perform at a lower speed but provides the benefit of low active power consumption).

- On-die voltage regulators (On-die voltage regulators are specifically designed to meet the demands of various active and static power requirements).

- **3D-IC** (Stacking ICs that communicate with one another to minimize the signal interconnect, e.g. using Through Silicon Vias TSV).

- **Static power**: The following techniques are used to minimize static power consumption:

- **Power-gating** (Provides the leakage power savings for a device in standby).

- Multi-threshold voltage transistor usage [4] (Swapping of nominal threshold voltage gates with higher threshold voltage gates. The sub-threshold leakage is inversely proportional to the threshold voltage in CMOS).

- Active back-bias (Increasing the bias voltage of the substrate nodes in CMOS reduces the leakage current but essentially increases the threshold voltage).

Other interesting techniques for minimizing the power consumption are summarized in the following text.

A Novel Adaptive Design Methodology for Minimum Leakage Power Considering PVT Variations on Nanoscale VLSI Systems is described in [5].

An Energy-Saving Rate-Harmonized Scheduler guarantees that every idle duration can be used to switch into sleep mode [6]. Energy-Saving Rate-Harmonized Scheduling saves 16.8~% energy compared to conventional Rate-Monotonic Scheduling.

An intelligent energy optimization approach for MPI based applications in HPC systems is described in [7].

The paper [8] focuses on cache leakage reduction and proposes the first Timing-Aware Cache Leakage Control (TACLC) mechanism. TACLC exploits system slack to turn cache lines into low-leakage states provided that the timing constraint is met. The experimental results demonstrate that TACLC effectively utilizes system slack to reduce cache leakage.

Scheduling and interconnection design to minimize the interconnection's energy consumption without performance degradation is described in [9].

In the paper [10], a novel technique for optimizing electronic circuits by resizing transistor parameters using single perceptron neural network is proposed.

Off-state leakage current is one of two principal sources of power dissipation in today's microprocessors. Intel chairman Andrew Grove cited off-state current leakage in particular as a limiting factor in future microprocessor integration [11] in comments on power consumption problem at the 2002 International Electron Devices Meeting.

It is crucial to know the circuit's estimated leakage power since such a bound will enable the designers to ensure that the circuit meets the standby power constraints which impacts battery life in portable devices [2]. It means that the leakage of MOSFET devices have to be modeled accurately.

The leakage current in standard MOSFET models (BSIM3/BSIM4) is typically modeled by drain-bulk and source-bulk diodes. This modeling method does not consider the impact of several parasitic bipolar devices. For the accurate modeling the impact of the following bipolar transistors has to be considered: a lateral bipolar transistor drain-bulk-source, a vertical bipolar transistor drain-bulk-substrate (only in isolated structures), and a vertical bipolar transistor source-bulk-substrate (only in isolated structures). For example, the drain or source leakage as a function of gate length cannot be modeled without the scalable parasitic bipolar devices. The first part of this thesis deals with accurate gate dimension dependent drain and source leakage modeling.

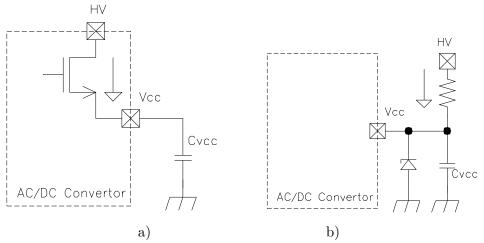

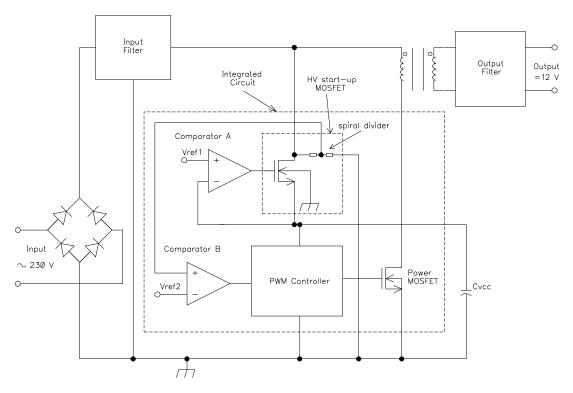

Another possibility of minimizing the power consumptions provides the circuits with sophisticated integrated features that dynamically adapts the power consumption to actual loads or power supply. Such a circuit includes the control circuit that is sensing the input/output voltage in order to dynamically adapts the power consumption. In case of AC/DC convertor the input voltage can be up to 400 V. For sensing this high input voltage a HV divider is commonly used. If the external HV divider is connected to the convertor then resistor is a source of a power consumption (see Fig 1.3b). If the convertor uses integrated HV sensing divider (see Fig 1.3a) then charging of the external capacitor  $C_{\rm VCC}$  can be controlled by the circuit based on HV supply and can be switched off. The second part of this thesis deals with accurate modeling of this integrated high voltage divider.

**Figure 1.3.** Comparison of the a) circuit with integrated HV sensing divider and b) circuit with external HV sensing divider

In the third part of this thesis a special attention is paid to the ability of the created model to cover the mismatch and influence of a variation of process parameters on the device characteristics. Introduction

#### 1.2 Aims of the Thesis

The thesis is organized as follows:

- **Chapter 1** gives a brief overview of the current situation of the studied problems, literature overview and aims of the thesis.

- Chapter 2 deals with the accurate gate dimension dependent drain and source leakage modeling and demonstrates the structure of a proposed macro models, implemented scalability (in most cases nonlinear), developed scaling equations, and physical explanation of this scaling. Finally, the comparison of measured data vs. simulation is presented in order to confirm the model validity. This model improvement solves not only leakage current scaling, but it also accounts for additional parasitic bipolar effects, such as current injection to the substrate.

- **Chapter 3** describes the structure and applications of the high voltage MOSFET with integrated nonlinear spiral high voltage polysilicon divider.

- **Chapter 4** deals with the proposed and implemented DC and AC model of the nonlinear spiral high voltage polysilicon divider.

- **Chapter 5** describes proposed and implemented high voltage divider statistical modeling.

- **Chapter 6** contains conclusions and final remarks.

#### The thesis aims can be summarized as follows

- Designing the characterization test chip containing required devices with sufficient number of various dimensions.

- Extracting the parasitic bipolar transistors for various MOSFET and LDMOS gate dimensions.

- Proposing new models of the MOSFET and LDMOS drain and source leakage that are dependent on the gate dimensions and implementing them into the commercial simulators.

- Extracting, developing and implementing new model of the nonlinear high voltage spiral polysilicon divider in HV start-up MOSFET.

- Evaluating statistical data and making new HV divider model responsive to the statistical process variation.

- Comparing new developed models with measured data and identifying changes of the simulation times.

The fundamental results (new scientific findings) of this thesis are described in Chapters 2, 4 and 5.

This thesis was prepared based on the plainTEX template – officially recommended design style CTUstyle for doctoral (Ph.D.) theses at the Czech Technical University in Prague.

#### 1.3 Used Modeling Methodology

The following list of steps describes model development flow used for this thesis:

1. Characterization test chip design - At first characterization test chip was designed in software Cadence Virtuoso Layout. For leakage modeling a lot of MOSFET and LDMOS devices were placed on this test chip in different dimensions and configurations. Test chip contains all structures necessary for characterization of the process and making predictive SPICE models. Therefore it's typically very large chip – full reticle. HV MOSFET was placed into several layout structures allowing various type of measurement (eg. DC, AC, mismatch, etc.).

Figure 1.4. Characterization test chip.

2. Process control monitoring (PCM) test chip design - PCM test chip was designed in software Cadence Virtuoso Layout and added into all following production masks (each fabricated standard production wafer then contains PCM test chip with required devices for statistical modeling). PCM has defined testplan measured in each wafer before testing production device. Measurement must pass the defined criteria. PCM is used for monitoring distribution of main process parameters and generation of corner models and statistical models.

Figure 1.5. Process control monitoring test chip.

- 3. Test chip manufacturing Test chips were manufactured in analog 1 μm CMOS technology and wafers best matching process means were selected for measurement. Also three experimental process split lots were fabricated (high resistance implant dose 85 %, 100 % and 115 %) for extraction of temperature coefficients dependency on polysilicon sheet resistance.

- **4. Measurement methods definition** The measurement methods had to be selected, set, adjusted and tested, especially AC methods (it was experimented with external loads, finally the load  $C_{\text{load}} = 330 \text{ nF}$  was selected).

- 5. Measurements for the leakage modeling:

- S-parameters measurements for resistances and some other BJTs' parameters extraction.

**Figure 1.6.** On-wafer S-parameters measurement. <sup>1</sup>)

<sup>1)</sup> Retrieved from video 15 February, 2015, from IC-CAP Device Modeling Software - Measurement Control and Parameter Extraction, Keysight Technologies, Visible http://www.keysight.com/en/pc-1297149/ic-cap-device-modeling-software-measurement-control-and-parameter-extraction

- DC measurements at various temperatures -40, -20, 0, 27, 60, 90, 125, and 150 °C ( $I_DV_G$  and  $I_DV_D$ , parasitic BJTs measurement: forward and reverse Gummel characteristics  $I_CV_{BE}$ ,  $I_BV_{BE}$ , and  $I_EV_{BC}$ ,  $I_BV_{BC}$ , forward and reverse output characteristics  $I_CV_{CE}$  and  $I_EV_{EC}$ , resistances  $R_E$ ,  $R_B$ ,  $R_C$  measurements).

- CV measurements  $(C_{BE}, C_{BC})$ .

#### • 6. Measurements for the HV divider modeling:

- Ratio DC measurement (for various  $V_S$  at temperatures -40, -20, 0, 27, 60, 90, 125, and 150 °C).

- Ratio AC measurement (for various  $V_D$ )

- High resistance implant dose process split temperature coefficients measurement (for temperatures -40, -20, 0, 27, 60, 90, 125, and 150 °C).

- 7. Export/import data Measured data were exported from measurement database DAM (ON Semiconductor internal measurement and data management system, thesis author is employee) in .mdm file format and then imported into IC-CAP (Integrated Circuit Characterization and Analysis Program, Keysight Technologies)

- 8. Measurement data quality verification The quality of measured data was verified (e.g. comparing same bias points from different measurement methods, verifying measured data trends, physical data scaling, etc.)

- 9. TCAD simulations Many TCAD simulations were done in Synopsys Sentaurus Workbench (simulations of leakages for various device dimensions at various temperatures, simulations of electrostatic potential distribution in HV MOSFET for various biases).

- 10. Model development and parameter extraction Models were developed in IC-CAP together with parameter extraction. For leakage modeling, the separate models for each device dimension were extracted. Finally, the scaling equations for each model parameter was developed to fit extracted models for all device dimensions. The dependency of temperature coefficients on polysilicon sheet resistance was extracted from the experimental process split lots (the high resistance implant dose 85 %, 100 %, and 115 %).

- 11. Model implementation The all new developed models were implemented into the commercial simulators HSPICE (Synopsys), ELDO (Mentor) and SPECTRE (Cadence).

- 12. Simulated and measured data comparison All measured data were compared with simulated data and all discrepancies were eliminated by model or equation corrections.

- 13. Model testing The all new developed models were verified in their defined operation areas at temperatures from −50 to 200 °C. The important requirement was that the new developed models had smooth derivatives of simulated characteristics.

- 14. Statistical data export The big amount of statistical data measured on PCM chip was exported from the factory (almost 30000 measured devices).

- 15. Statistical data evaluation Statistical data were evaluated and electrical process variation parameters were calculated.

- 16. Statistical parameters implementation The statistical model parameters were implemented in to the new developed models. The mapping equations between model parameters and statistical electrical process parameters were also implemented by using master variables.

- 17. Statistical parameters extraction The statistical model parameters were extracted by using Forward or Backward propagation of variances.

- 18. Corner models extraction The corner libraries (worst case corner models) were also implemented.

- 19. Monte Carlo verification All the new developed models were verified by comparison of Monte Carlo simulations and process variation.

- 20. Final application verification The simulation speeds were measured and compared with conventional models and are acceptable. Any convergency issue was not observed during the verification realized on several real designs.

# Chapter 2 Gate Dimension Dependent Drain and Source Leakage

In this chapter the first fundamental thesis result is descibed. This chapter deals with the accurate gate dimension dependent drain and source leakage modeling and demonstrates the structure of a proposed macro models, implemented scalability (in most cases nonlinear), developed scaling equations, and physical explanation of this scaling.

#### 2.1 Introduction

The BSIM3v3 or BSIM4 model [12] is very often used for the MOSFET transistors modeling. These models provide very good accuracy and the BSIM4 model is also used in this chapter. The leakage current is modeled by drain-bulk and source-bulk diodes in this model (e.g. by parameters  $J_{SS}$ ,  $J_{SD}$ ,  $J_{SWS}$ ,  $J_{SWD}$ , etc.), and the diodes are scaled with the area and perimeter of the drain and source by component parameters  $a_d$ ,  $p_d$ ,  $a_s$  and  $p_s$ ). This method is described in detail in [13–15]. The leakage modeling for four-terminal MOSFET was also published in [16].

However, there exist the operation areas where these methods are not sufficient. Especially, the real current redistribution in OFF state is not taken into account, which means that the lateral drain to source injection is not modeled. Moreover, in the case of an isolated MOSFET the injection to the substrate is not also modeled. The correct modeling of above mentioned effects, that is introduced in this chapter, makes the model more precise not only in OFF state (the drain leakage current, the source leakage current), but also in the case of an nonstandard biasing (open drain-bulk or source-bulk junction).

In order to demonstrate these phenomena, an isolated P-channel MOSFET and an N-channel lateral DMOS were selected as a testcases. In the following sections the improved modeling methods are described for these two testcases.

#### 2.2 P-channel MOSFET

#### 2.2.1 Crossection and modeling

An example of more general isolated MOSFET, in this case the P-channel MOSFET, is shown in Fig. 2.1. The source and drain are formed from P<sup>+</sup> layer and the bulk from nwell. This configuration forms two parasitic vertical substrate transistors and one parasitic lateral transistor. An emitter of the first substrate transistor is formed from the drain, a base from the bulk, and a collector from the substrate. The same applies for the second substrate transistor, however an emitter is formed from the source. The parasitic lateral transistor occurs between source and drain where the source is an emitter, the bulk is a base and the source is a collector.

Figure 2.1. Crossection of P-channel MOSFET with indication of parasitic BJTs

These three parasitic bipolar transistors are scaled with the gate length and width and have significant impact on the leakage characteristics. If the standard BSIM4 model with the parasitic diodes is used for the modeling of this P-channel MOSFET, the leakage modeling is not accurate. This standard model does not consider the impact of the parasitics bipolar transistors, e.g. an injection to the substrate or lateral channel injection. The possible solution by using the SPICE models [17] is shown in Fig. 2.2 where all three parasitic bipolar devices are added without the necessity of adding the new circuit nodes. In this case the source-bulk and the drain-bulk parasitic diode parameters of the BSIM4 model have to be suppressed. The dependency of the model parameters of the parasitic bipolar transistors on the gate length and gate width are described in next two sections. The standard Gummel-Poon model [18] is used for modeling of these BJTs.

Figure 2.2. Updated MOSFET model with parasitic BJTs

The component parameters are given by

$$a_d = W_G L_D$$

$$a_s = W_G L_S$$

$$p_d = 2(W_G + L_D)$$

$$p_s = 2(W_G + L_S)$$

(1)

where  $W_{\rm G}$  is the gate width of MOSFET,  $a_d$  and  $p_d$  are an area and a perimeter of the drain,  $a_s$  and  $p_s$  are an area and a perimeter of the source, and  $L_{\rm D}$  and  $L_{\rm S}$  are the lengths of the drain and source.

Figure 2.3. Photo of the chip for construction analysis (the red arrows indicates the cat).

**Figure 2.4.** Photo from the MOSFET construction analysis - bulk (pwell). The whole MOSFET structure is shown.

**Figure 2.5.** Photo of the MOSFET construction analysis - drain, source and gate are shown in detail.

Figure 2.6. Photo of the MOSFET construction analysis - gate is shown in more detail.

#### 2.2.2 Substrate vertical parasitic BJTs

The model parameters of the substrate vertical parasitic BJTs reflect the dependency on gate dimensions and also the impact of the current redistribution between vertical and lateral parasitic BJTs. The values of the model parameters are replaced by equations with scaling parameters.

The model parameter  $I_S$  (transport saturation current) is defined as

$$I_S = \left(j_{sa} \ln \frac{L_G}{L_0} + j_{sb}\right) a_d + j_{sp} p_d + j_{sc}$$

$$\tag{2}$$

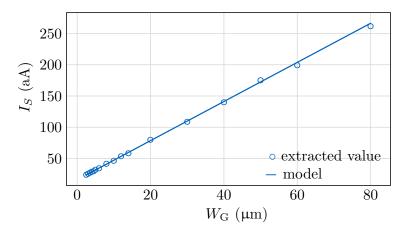

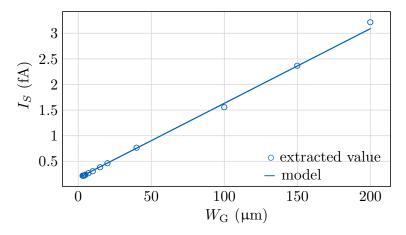

where  $j_{sa}$ ,  $j_{sb}$ ,  $j_{sp}$ , and  $j_{sc}$  are the extracted scaling parameters and  $L_0 = 1 \mu m$  is the reference gate length. This equation implies that the parameter  $I_S$  is linearly dependent on gate width  $W_G$  which is shown in Fig. 2.7.

The logarithmic dependency of the parameter  $I_S$  on the gate length  $L_G$  that also comes from (2) is shown in Fig. 2.8. This gate length dependency controls the current redistribution between the substrate vertical and the lateral BJT. The lateral injection from the drain to the source is more significant than the injection to the substrate for the short gate lengths. Therefore, the parameter  $I_S$  of the vertical BJT is logarithmically decreased for the short gate lengths. The dependency of  $I_S$  on  $W_G/L_G$  is shown in Fig. 2.9.

Figure 2.7. Vertical parasitic BJT:  $I_S$  vs  $W_G$ .

**Figure 2.8.** Vertical parasitic BJT:  $I_S$  vs  $L_G$ .

Figure 2.9. Vertical parasitic BJT:  $I_S$  vs  $W_G/L_G$ .

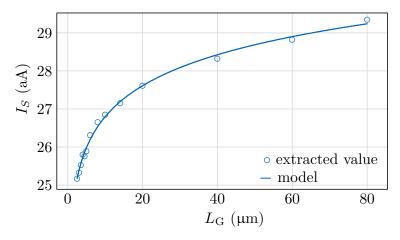

Figure 2.10. Vertical parasitic BJT:  $B_F$  vs  $W_G$ .

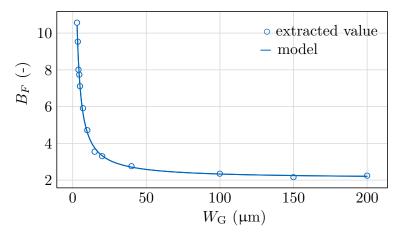

The model parameter  $B_F$  (ideal forward maximum beta) is not dependent on the gate length  $L_{\rm G}$  and is a constant for a whole range of  $L_{\rm G}$ . On the other hand there exists a strong nonlinear dependency of the parameter  $B_F$  on the gate width  $W_{\rm G}$  (gate width is included in the component parameters  $a_d$  and  $p_d$ ). This dependency is shown in Fig. 2.10 and is expressed as

$$B_F = \frac{j_{sat}a_d + j_{sp}p_d + j_{sc}}{j_{ba}a_d + j_{bp}p_d + j_{bc}}$$

(3)

where  $j_{sat}$  is a scaling saturation current parameter,  $j_{ba}$ ,  $j_{bp}$ , and  $j_{bc}$  are the extracted scaling parameters. The saturation current parameter  $j_{sat}$  in the  $B_F$  numerator in (3) assures the correlation between parameters  $B_F$  and  $I_S$  [19]:  $B_F \sim I_S/(I_B@V_{BE} = 0 \text{ V})$ .

The model parameter  $I_{KF}$  (forward beta high current roll-off) is independent on the gate length  $L_{\rm G}$  and linearly dependent on the gate width  $W_{\rm G}$

$$I_{KF} = j_{ka}a_d + j_{kp}p_d + j_{kc} \tag{4}$$

where  $j_{ka}$ ,  $j_{kp}$ , and  $j_{kc}$  are the extracted scaling parameters.

The model parameters  $R_E$  (emitter resistance),  $R_C$  (collector resistance) and  $R_B$  (base resistance) are inversely proportional to the gate width  $W_G$  and are not dependent on the gate length  $L_G$

$$R_E = \frac{1}{g_{ea}a_d + g_{ep}p_d + g_{ec}} \tag{5}$$

$$R_C = \frac{1}{g_{ca}a_d + g_{cp}p_d + g_{cc}} \tag{6}$$

$$R_{C} = \frac{1}{g_{ca}a_{d} + g_{cp}p_{d} + g_{cc}}$$

$$R_{B} = \frac{1}{g_{ba}a_{d} + g_{bp}p_{d} + g_{bc}}$$

(6)

where  $g_{ea}$ ,  $g_{ep}$ ,  $g_{ec}$ ,  $g_{ca}$ ,  $g_{cp}$ ,  $g_{cc}$ ,  $g_{ba}$ ,  $g_{bp}$ , and  $g_{bc}$  are the extracted scaling parameters.

The parasitic capacitance is modeled by the vertical BJTs. Therefore, the capacitance parameters of the lateral BJT  $(C_{JE}, C_{JC})$  and source/drain junction diode parameters of MOSFET [12]  $(C_{JS}, C_{JD}, C_{JSWS}, C_{JSWD}, C_{JSWGS}, C_{JSWGD}, J_{SS}, J_{SD}, J_{SWS},$  $J_{SWD}$ ,  $J_{SWGS}$ ,  $J_{SWGD}$ ) are suppressed (set to zero or very low value, e.g.  $10^{-30}$ ). The dependency of the model parameters  $C_{JE}$  and  $C_{JC}$  of the vertical BJTs on the gate width is linear

$$C_{JE} = c_{jea}a_d + c_{jep}p_d + c_{jec} \tag{8}$$

$$C_{JC} = c_{jca}a_b + c_{jcp}p_b + c_{jcc} (9)$$

where  $c_{jea}$ ,  $c_{jep}$ ,  $c_{jec}$ ,  $c_{jca}$ ,  $c_{jcp}$ , and  $c_{jcc}$  are the extracted scaling parameters and  $a_b$ ,  $p_b$ is the area and perimeter of the bulk.

The Early voltage effect was not observed due to the deep nwell that means the big base width, so the model parameter VAF was set to the large number.

| Scaling parameter | Unit                         | Value                  |

|-------------------|------------------------------|------------------------|

| $j_{sa}$          | $\mathrm{Am^{-2}}$           | $3 \times 10^{-19}$    |

| $j_{sb}$          | $\mathrm{Am^{-2}}$           | $9 \times 10^{-19}$    |

| $j_{sp}$          | $\mathrm{Am^{-1}}$           | $1.2 \times 10^{-19}$  |

| $j_{sc}$          | A                            | $1.6 \times 10^{-17}$  |

| $j_{sat}$         | $\mathrm{Am^{-2}}$           | $2.1\times10^{-18}$    |

| $j_{ba}$          | $\mathrm{Am^{-2}}$           | $2.2\times10^{-20}$    |

| $j_{bp}$          | $\mathrm{Am^{-1}}$           | $5.2 \times 10^{-22}$  |

| $j_{bc}$          | A                            | $4 \times 10^{-21}$    |

| $j_{ka}$          | $\mathrm{Am^{-2}}$           | $1 \times 10^{-6}$     |

| $j_{kp}$          | $\mathrm{Am^{-1}}$           | $2.9\times10^{-7}$     |

| $j_{kc}$          | A                            | $5 \times 10^{-5}$     |

| $g_{ea}$          | $\Omega^{-1}\mathrm{m}^{-2}$ | $2 \times 10^{-4}$     |

| $g_{ep}$          | $\Omega^{-1}\mathrm{m}^{-1}$ | $5 \times 10^{-5}$     |

| $g_{ec}$          | $\Omega^{-1}$                | $1 \times 10^{-2}$     |

| $g_{ca}$          | $\Omega^{-1}\mathrm{m}^{-2}$ | $2 \times 10^{-1}$     |

| $g_{cp}$          | $\Omega^{-1}\mathrm{m}^{-1}$ | $8 \times 10^{-3}$     |

| $g_{cc}$          | $\Omega^{-1}$                | $5 \times 10^{-2}$     |

| $g_{ba}$          | $\Omega^{-1}\mathrm{m}^{-2}$ | $1 \times 10^{-4}$     |

| $g_{bp}$          | $\Omega^{-1}\mathrm{m}^{-1}$ | $3.7 \times 10^{-6}$   |

| $g_{bc}$          | $\Omega^{-1}$                | $2.1 \times 10^{-5}$   |

| $c_{jea}$         | $\mathrm{Fm}^{-2}$           | $2.45 \times 10^{-16}$ |

| $c_{jep}$         | $\mathrm{Fm}^{-1}$           | $3.09 \times 10^{-16}$ |

| $c_{jec}$         | F                            | $2.9 \times 10^{-16}$  |

| $c_{jca}$         | $\mathrm{Fm}^{-2}$           | $2.95 \times 10^{-17}$ |

| $c_{jcp}$         | $\mathrm{Fm}^{-1}$           | $6.02 \times 10^{-16}$ |

| $c_{jcc}$         | F                            | $2.1\times10^{-17}$    |

|                   |                              |                        |

**Table 2.1.** Extracted parameters of the parasitic vertical BJTs

Both parasitic vertical BJTs were measured and also their parameters were extracted based on the standard methodology described in [18]. Extracted parameters (computed by the Levenberg-Marquardt algorithm [20]) are summarized in Tab. 2.1.

#### 2.2.3 Lateral parasitic BJT

The model parameters of the lateral parasitic BJT reflect the dependency on gate dimensions and also the impact of the current redistribution between vertical and lateral parasitic BJTs. The values of the model parameters are replaced by equations with scaling parameters.

The model parameter  $I_S$  (transport saturation current) is defined as

$$I_S = \frac{i_{slw} W_G}{\left(L_G/L_0\right)^{\left(\alpha_{sla} + \frac{L_G}{W_G}\alpha_{slb}\right)}} + i_{slc}$$

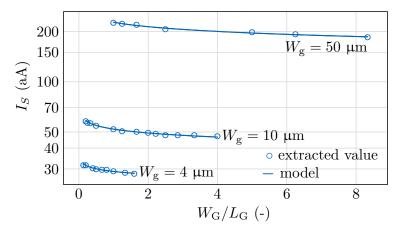

(10)

where  $i_{slw}$ ,  $\alpha_{sla}$ ,  $\alpha_{slb}$ , and  $i_{slc}$  are the extracted scaling parameters. The parameter  $i_{slw}$  expresses the almost linear dependency of the transport saturation current  $I_S$  on the gate width  $W_G$  that is shown in Fig. 2.11. Increasing the gate width  $W_G$  of MOSFET causes the increasing of the effective emitter size of the lateral BJT and this leads to increasing of the saturation current  $I_S$ .

Figure 2.11. Lateral parasitic BJT:  $I_S$  vs  $W_G$ .

Figure 2.12. Lateral parasitic BJT:  $I_S$  vs  $L_{\rm G}$

The strong nonlinear dependency on the gate length  $L_{\rm G}$  is depicted in Fig. 2.12 and is determined by the parameters  $\alpha_{sla}$  and  $\alpha_{slb}$ . Increasing the gate length  $L_{\rm G}$  of MOSFET means increasing the distance between emitter and collector (base width) that causes decreasing of the saturation current  $I_S$ . The dependency of  $I_S$  on  $W_{\rm G}/L_{\rm G}$  is shown in Fig. 2.13.

Figure 2.13. Lateral parasitic BJT:  $I_S$  vs  $W_G/L_G$ .

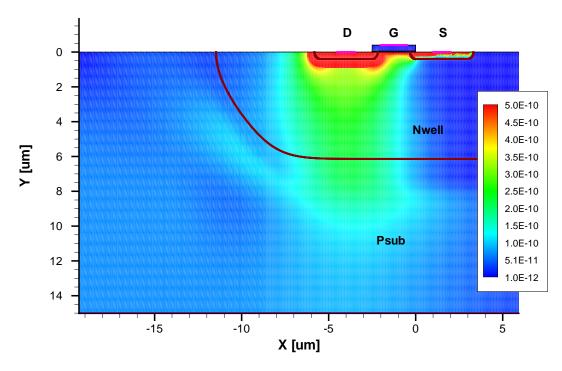

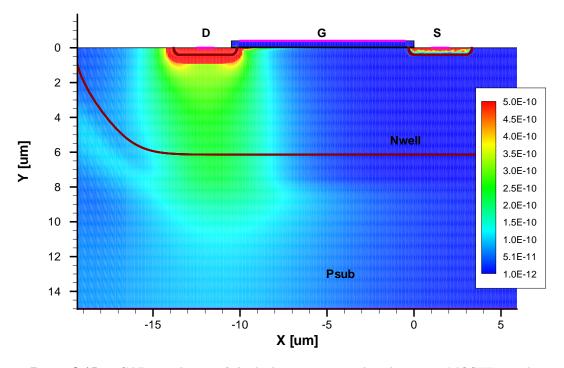

The dependency of the current redistribution between vertical and lateral parasitic BJTs on the gate length is demonstrated in TCAD simulation graphs for two selected gate lengths. The hole current density of MOSFET with the gate length 2.5  $\mu$ m is depicted in Fig. 2.14 that shows the leakage current flowing from the drain to the source (lateral BJT) and also to the substrate (vertical BJT). However, MOSFET with the gate length 10.5  $\mu$ m, depicted in Fig. 2.15, shows the leakage current flowing predominantly to the substrate. The current density in Figs. 2.14 and 2.15 is modeled at nominal temperature 300.15 K, and is exponentially temperature dependent as is demonstrated in Figs. 2.17 and 2.18. The difference between the current densities at 300.15 K and 423.15 K is about six orders, so the leakage at the higher temperatures, where devices often operate, becomes significant for practical designs and should not be neglected.

The model parameter  $I_{KF}$  is independent on the gate length  $L_{\rm G}$  and is linearly dependent on the gate width  $W_{\rm G}$

$$I_{KF} = j_{klp}W_{G} + j_{klc} \tag{11}$$

where  $j_{klp}$  and  $j_{klc}$  are the extracted scaling parameters.

The model parameters  $R_E$ ,  $R_C$ , and  $R_B$  are inversely proportional to the gate width  $W_G$  and are not dependent on the gate length  $L_G$

$$R_E = \frac{1}{g_{elp}W_{\rm G} + g_{elc}} \tag{12}$$

$$R_C = \frac{1}{g_{clp}W_{\rm G} + g_{clc}} \tag{13}$$

$$R_B = \frac{1}{g_{blp}W_{\rm G} + g_{blc}} \tag{14}$$

where  $g_{elp}$ ,  $g_{elc}$ ,  $g_{clp}$ ,  $g_{clc}$ ,  $g_{blp}$ , and  $g_{blc}$  are the extracted scaling parameters.

Figure 2.14. TCAD simulation of the leakage current redistribution in MOSFET with  $L_{\rm G}=2.5~\mu{\rm m}$  at nominal temperature 300.15 K. Graph represents the hole current density in Am $^{-2}$ .

Figure 2.15. TCAD simulation of the leakage current redistribution in MOSFET with  $L_{\rm G}=10.5~\mu{\rm m}$  at nominal temperature 300.15 K. Graph represents the hole current density in Am<sup>-2</sup>.

The Early voltage dependency on the gate length  $L_{\rm G}$ , that is actually the base width of parasitic lateral transistor, was negligible in comparison with very high dependency of saturation current  $I_S$  on the gate length. This is the reason why the Early voltage parameter was fixed to the constant value  $V_{AF} = 50$  V.

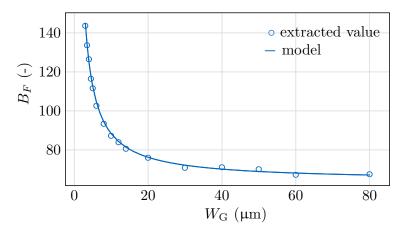

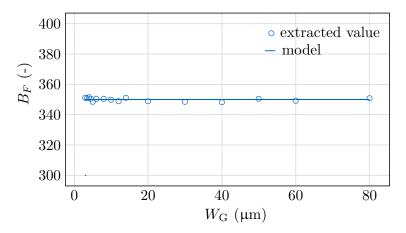

The model parameter  $B_F$  (ideal forward maximum beta) is dependent neither on the gate length  $L_{\rm G}$  nor the gate width  $W_{\rm G}$  and is a constant for a whole range of  $L_{\rm G}$  and  $W_{\rm G}$  (see Fig. 2.16).

Figure 2.16. Lateral parasitic BJT:  $B_F$  vs  $W_G$ .

The parasitic lateral BJT was measured and also its parameters were extracted based on standard methodology described in [18]. Extracted parameters are summarised in Tab. 2.2.

| Scaling parameter | Unit                         | Value                  |

|-------------------|------------------------------|------------------------|

| $i_{slw}$         | $\mathrm{Am^{-1}}$           | $9.54 \times 10^{-17}$ |

| $\alpha_{sla}$    | _                            | 2.25                   |

| $lpha_{slb}$      | _                            | 0.127                  |

| $i_{slc}$         | A                            | $3 \times 10^{-23}$    |

| $j_{klp}$         | ${ m Am^{-1}}$               | $5 \times 10^{-7}$     |

| $j_{klc}$         | A                            | $7.5\times10^{-8}$     |

| $g_{elp}$         | $\Omega^{-1}\mathrm{m}^{-1}$ | $1 \times 10^{-4}$     |

| $g_{elc}$         | $\Omega^{-1}$                | $1.5\times10^{-5}$     |

| $g_{clp}$         | $\Omega^{-1}\mathrm{m}^{-1}$ | $1 \times 10^{-4}$     |

| $g_{clc}$         | $\Omega^{-1}$                | $1.5\times10^{-5}$     |

| $g_{blp}$         | $\Omega^{-1}\mathrm{m}^{-1}$ | $1 \times 10^{-4}$     |

| $g_{blc}$         | $\Omega^{-1}$                | $1.5\times10^{-5}$     |

|                   |                              |                        |

**Table 2.2.** Extracted parameters of the parasitic lateral BJT

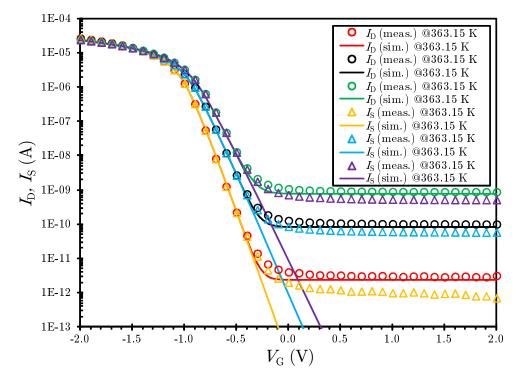

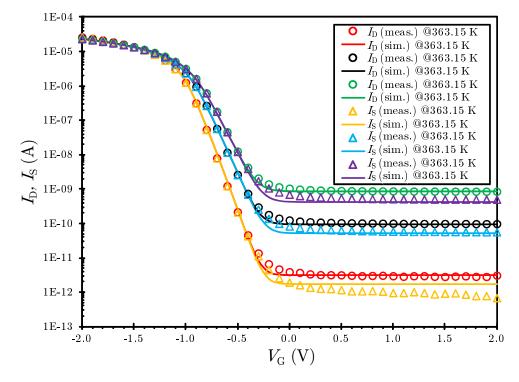

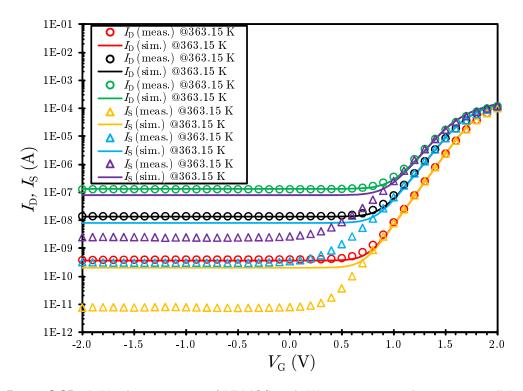

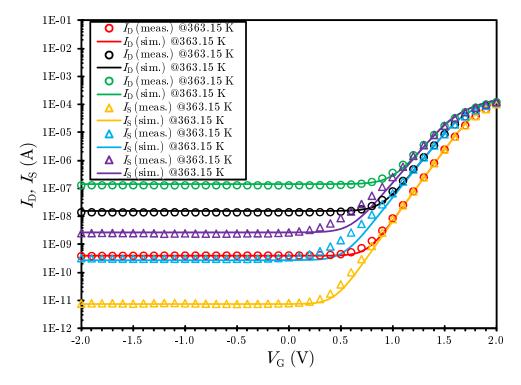

The comparison of the  $I_{\rm D}V_{\rm G}$  characteristics between the standard BSIM4 model and MOSFET with parasitic BJTs is shown in Fig. 2.17 and 2.18. The leakage current in the standard BSIM4 model flows from the drain only to the bulk. To the contrary the model with parasitic BJTs takes into account injection from the drain to the substrate and also to the source (see source current in Fig. 2.17 and 2.18).

Figure 2.17.  $I_{\rm D}V_{\rm G}$  characteristics of MOSFET with  $L_{\rm G}=2.5~\mu{\rm m}$  and  $W_{\rm G}=50~\mu{\rm m}$  without parasitic BJTs (standard BSIM4).

Figure 2.18.  $I_{\rm D}V_{\rm G}$  characteristics of MOSFET with  $L_{\rm G}=2.5~\mu{\rm m}$  and  $W_{\rm G}=50~\mu{\rm m}$  with parasitic BJTs.

The similar modeling approach, but without implemented scalability, is used in [21], where MOSFET and two substrate BJTs are parasitic devices and the main device is lateral BJT.

#### 2.3 N-channel LDMOS

#### 2.3.1 Crossection and modeling

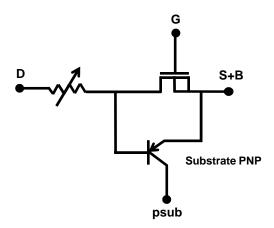

The second selected testcase is the N-channel LDMOS scaled with the gate width only. A crossection of this device is depicted in Fig. 2.19. The drain is formed from nwell layer (contacted by N<sup>+</sup>), the source from N<sup>+</sup> layer and the bulk from P layer. This configuration forms a different parasitic components than MOSFET in previous chapters. The substrate vertical parasitic BJT has a major influence on the leakage current. An emitter is formed from the bulk, a base from the drain and a collector from the substrate. This parasitic BJT is scaled with the gate width and the accuracy of the leakage current is significantly increased by adding this BJT to the standard BSIM model as is denoted in Fig. 2.20.

The LDMOS transistor is predominantly used in forward bias regime where the source is connected with the bulk. Hence the potential influence of the lateral parasitic BJT (nwell as an emitter, the bulk as a base and the source as a collector) is negligible.

Figure 2.19. Crossection of N-channel LDMOS with indication of parasitic BJT.

Figure 2.20. Updated LDMOS model with parasitic BJT.

Figure 2.21. Photo of the LDMOS construction analysis - drain, source and gate are shown in detail.

Figure 2.22. Photo of the LDMOS construction analysis - lateral diffusion of the bulk (PHV) defining gate length is shown in more detail.

#### **2.3.2** Substrate vertical parasitic BJTs

Because the emitter of the parasitic BJT is formed from the bulk, the emitter area and perimeter depends only on the gate width

$$a_b = W_{\rm G} L_{\rm B}$$

$$p_b = 2(W_{\rm G} + L_{\rm B})$$

(15)

where  $W_{\rm G}$  is the gate width of LDMOS,  $a_b$  and  $p_b$  are area and perimeter of the bulk (emitter) and  $L_{\rm B}$  is the lengths of the bulk.

The model parameters of the parasitic BJTs reflect the dependency on gate width. The values of the model parameters are replaced by equations with scaling parameters.

The model parameter  $I_S$  is defined as

$$I_S = j_{sa}a_b + j_{sp}p_b + j_{sc} (16)$$

where  $j_{sa}$ ,  $j_{sp}$ , and  $j_{sc}$  are the extracted scaling parameters. This equation implies that the parameter  $I_S$  is linearly dependent on gate width  $W_G$  which is shown in Fig. 2.23.

Figure 2.23. Vertical parasitic BJT:  $I_S$  vs  $W_G$ .

Figure 2.24. Vertical parasitic BJT:  $B_F$  vs  $W_G$ .

The model parameter  $B_F$  is nonlinear dependent on the gate width  $W_G$  and is expressed as

$$B_F = \frac{j_{sa}a_b + j_{sp}p_b + j_{sc}}{j_{ba}a_d + j_{bp}p_d + j_{bc}}$$

(17)

where  $j_{ba}$ ,  $j_{bp}$ , and  $j_{bc}$  are the extracted scaling parameters. This dependency is shown in Fig. 2.24.

The model parameter  $I_{KF}$  (forward beta high current roll-off) is independent on the gate length  $L_{G}$  and linearly dependent on the gate width  $W_{G}$

$$I_{KF} = j_{ka}a_b + j_{kp}p_b + j_{kc} (18)$$

where  $j_{ka}$ ,  $j_{kp}$ , and  $j_{kc}$  are the extracted scaling parameters.

The model parameters  $R_E$  (emitter resistance),  $R_C$  (collector resistance) and  $R_B$  (base resistance) are inversely proportional to the gate width  $W_G$  and are not dependent on the gate length  $L_G$

$$R_E = \frac{1}{g_{ea}a_b + g_{ep}p_b + g_{ec}} \tag{19}$$

$$R_C = \frac{1}{g_{ca}a_b + g_{cp}p_b + g_{cc}} \tag{20}$$

$$R_B = \frac{1}{g_{ba}a_b + g_{bv}p_b + g_{bc}} \tag{21}$$

where  $g_{ea}$ ,  $g_{ep}$ ,  $g_{ec}$ ,  $g_{ca}$ ,  $g_{cp}$ ,  $g_{cc}$ ,  $g_{ba}$ ,  $g_{bp}$ , and  $g_{bc}$  are the extracted scaling parameters.

The parasitic capacitance is modeled by the vertical BJTs. Therefore, the capacitance parameters of the lateral BJT ( $C_{JE}$ ,  $C_{JC}$ ) and source/drain junction diode parameters of MOSFET [12] ( $C_{JS}$ ,  $C_{JD}$ ,  $C_{JSWS}$ ,  $C_{JSWD}$ ,  $C_{JSWGS}$ ,  $C_{JSWGD}$ ,  $J_{SS}$ ,  $J_{SD}$ ,  $J_{SWS}$ ,  $J_{SWD}$ ,  $J_{SWGS}$ ,  $J_{SWGD}$ ) are suppressed (set to zero or very low value, e.g.  $10^{-30}$ ). The dependency of the model parameters  $C_{JE}$  and  $C_{JC}$  of the vertical BJTs on the gate width is linear

$$C_{JE} = c_{jea}a_b + c_{jep}p_b + c_{jec} (22)$$

$$C_{JC} = c_{jca}a_d + c_{jcp}p_d + c_{jcc} (23)$$

where  $c_{jea}$ ,  $c_{jep}$ ,  $c_{jec}$ ,  $c_{jca}$ ,  $c_{jcp}$ , and  $c_{jcc}$  are the extracted scaling parameters and  $a_d$ ,  $p_d$  is the area and perimeter of the drain (nwell).

The parasitic vertical BJTs was measured and also its parameters were extracted based on the standard methodology described in [18]. Extracted parameters are summarized in Tab. 2.3.

Figure 2.25.  $I_DV_G$  characteristics of LDMOS with  $W_G = 150 \ \mu m$  without parasitic BJT.

Figure 2.26.  $I_{\rm D}V_{\rm G}$  characteristics of LDMOS with  $W_{\rm G}=150~\mu{\rm m}$  with added parasitic BJT.

| Scaling parameter                                         | Unit                                                               | Value                                                                                       |

|-----------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| $j_{sa}$ $j_{sp}$ $j_{sc}$                                | $\begin{array}{c} \rm Am^{-2} \\ \rm Am^{-1} \\ \rm A \end{array}$ | $3.6 \times 10^{-18}$ $9 \times 10^{-20}$ $1.5 \times 10^{-16}$                             |

| $j_{ba}\ j_{bp}\ j_{bc}$                                  | $ m Am^{-2}$ $ m Am^{-1}$ $ m A$                                   | $7 \times 10^{-18}  2 \times 10^{-20}  5 \times 10^{-21}$                                   |

| $j_{ka}\ j_{kp}\ j_{kc}$                                  | $ m Am^{-2}$ $ m Am^{-1}$ $ m A$                                   | $3.85 \times 10^{-6}$<br>$2.22 \times 10^{-19}$<br>$7.75 \times 10^{-5}$                    |

| $egin{aligned} g_{ea} \ g_{ec} \end{aligned}$             | $\Omega^{-1} m^{-2}$ $\Omega^{-1} m^{-1}$ $\Omega^{-1}$            | $6.6 \times 10^{-5}  2 \times 10^{-6}  5 \times 10^{-5}$                                    |

| $egin{aligned} g_{ca} \ g_{cp} \ g_{cc} \end{aligned}$    | $\Omega^{-1} m^{-2}$ $\Omega^{-1} m^{-1}$ $\Omega^{-1}$            | $ 2 \times 10^{-1} \\ 8 \times 10^{-3} \\ 5 \times 10^{-2} $                                |

| $egin{aligned} g_{ba} \ g_{bc} \end{aligned}$             | $\Omega^{-1} m^{-2}$ $\Omega^{-1} m^{-1}$ $\Omega^{-1}$            | $\begin{array}{c} 1 \times 10^{-4} \\ 3.7 \times 10^{-6} \\ 2.1 \times 10^{-5} \end{array}$ |

| $egin{aligned} c_{jea} \ c_{jec} \end{aligned}$           | $\mathrm{Fm^{-2}}$ $\mathrm{Fm^{-1}}$ $\mathrm{F}$                 | $1.44 \times 10^{-16}$ $1.3 \times 10^{-15}$ $2 \times 10^{-16}$                            |

| $egin{aligned} c_{jca} \ c_{jcp} \ c_{jcc} \end{aligned}$ | $Fm^{-2}$ $Fm^{-1}$ $F$                                            | $2.95 \times 10^{-17}$ $6.02 \times 10^{-16}$ $2.1 \times 10^{-17}$                         |

**Table 2.3.** Extracted parameters of the parasitic vertical BJT

The comparison of the  $I_{\rm D}V_{\rm G}$  characteristics between standard LDMOS model and LDMOS with parasitic BJT is shown in Figs. 2.25 and 2.26. The source/bulk leakage current fitting of the LDMOS is improved by adding parasitic BJT. The gate leakage current (tunneling) modeling has been already presented in many publications, e.g. [22–25], but phenomena described in this chapter were mostly neglected.

### 2.4 Chapter Summary

In this chapter the accurate gate dimension dependent drain and source leakage modeling was presented (the structure of a proposed macro models, implemented scalability, developed scaling equations, and physical explanation of this scaling). Finally, the comparison of measured data vs. simulation is presented in order to confirm the model validity. This model improvement solves not only leakage current scaling, but it also accounts for additional parasitic bipolar effects, such as current injection to the substrate.

# Chapter 3 HV Start-up MOSFET Description

This chapter describes the structure and applications of the high voltage power start-up MOSFET with integrated nonlinear spiral high voltage polysilicon divider. This start-up MOSFET transistor is used to minimizing the power consumption (structure and application patented by ON Semiconductor [26–27]). It is designed to provide initial current directly from the high voltage source. This MOSFET transistor charges up the regulator voltage on an external capacitor to about 14 V. The main goal is to minimize power consumption of the circuit that is directly connected to the rectified DC high voltage source. This high voltage can be up to 400 V for a 230 V AC supply and 700 V for switcher applications using power factor correction.

### 3.1 Structure Description

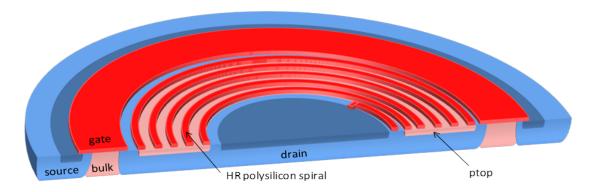

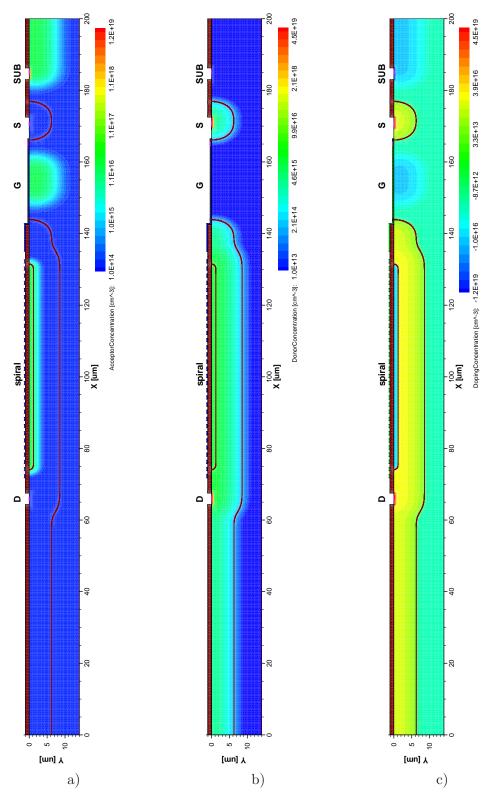

The HV start-up MOSFET is fabricated in an analog 1  $\mu$ m CMOS technology. The simplified structure of this MOSFET is depicted in Fig. 3.1. The source and drain are formed from a low-doped Nwell1 and are contacted by N+ diffusion. The drain drift area is doped by Nwell2 that is deeper and more doped than Nwell1. Furthermore, the drain drift area contains a floating P doped resurf diffusion (ptop) fabricated before field oxide. The final doping concentration of the ptop is the same as of Nwell2 (but with different type of dopant) after all process steps. The concentration profiles are shown in Fig. 3.2 where is acceptor concentration (Fig. 3.2a), donor concentration (Fig. 3.2b) and total doping concentration (Fig. 3.2c). For abbreviations explanation see Appendix A.

The MOSFET bulk is created from Pwell not isolated from the P-substrate and it is covered by polysilicon gate. This drain-gate-source structure is rotary symmetrical around vertical axis in the center of the drain. It means that the drain is created in the shape of a circle and the gate and the source in the shape of an annulus.

Figure 3.1. The simplified 3D structure of HV start-up MOSFET transistor.

The drain is located in the center of the device and contains a rounded bonding pad. A drain bonding wire is connected directly to this bonding pad and this is only one

Figure 3.2. Concentration profiles: a) acceptor concentration, b) do nor concentration and c) total doping concentration. Each figure has different contour range. The axial symmetry is in X=0.

possible way how the drain can be connected. The oxide breakdown is much lower (about 100 V) than the maximum allowed drain voltage. The drain can be biased up to 700 V and this makes integrated direct sensing of the high drain voltage impossible. Hence, the high resistance polysilicon spiral voltage divider is used for the sensing of high drain voltage.

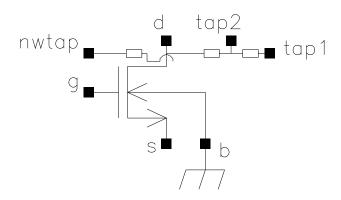

The spiral is connected to the drain and continues spirally toward the gate. How the polysilicon spiral divider is connected to other device components is depicted in the schematic symbol of HV MOSFET in the Fig. 3.3 (terminals d, tap1, tap2).

Figure 3.3. Schematic symbol of HV start-up MOSFET.

The spiral divider is designed to have the electric field distribution as much similar as possible as the drain drift area under it. This ensures the voltage between divider and silicon does not exceed oxide breakdown voltage. The polysilicon spiral divider has a big impact on a distribution of the electric field in the low doped drain drift area. And on the contrary, the strong electric field in the low doped drain drift area causes a lot of parasitic effects that have a big influence on DC and RF device characteristics. These effects can be observed later in modeling chapters were the results of TCAD simulations are shown.

These attributes make the modeling of this start-up MOSFET complicated, especially the divider ratio voltage and frequency dependency. The divider is usually modeled by the simple RC network, but there exist the operation areas where such simple model is not sufficient.

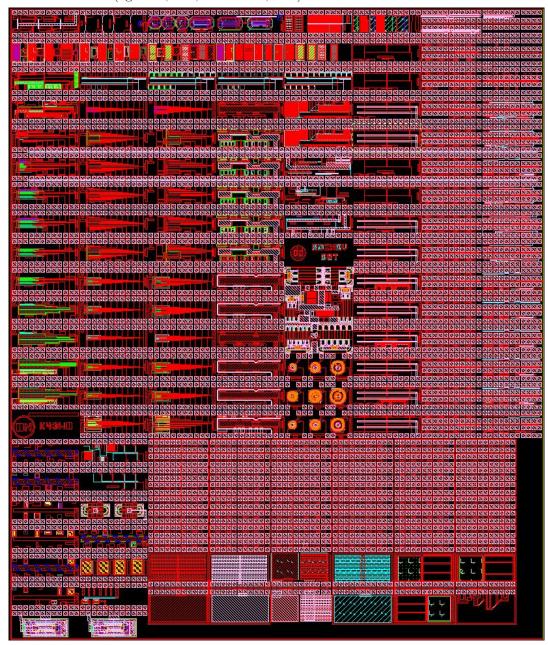

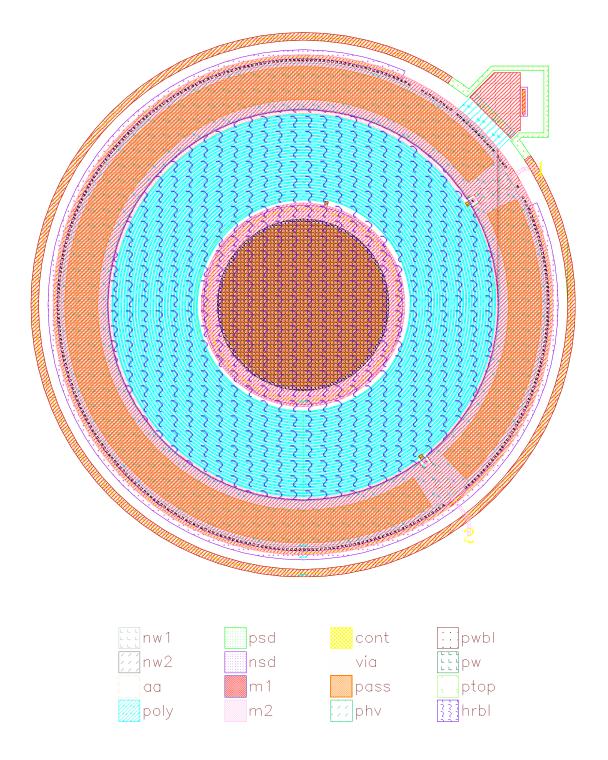

The layout of HV start-up MOSFET device as is seen by design engineers in layout editors (Cadence Virtuoso Layout Editor or Mentor Pyxis Layout) is depicted in Fig. 3.4.

Figure 3.4. Layout of HV start-up MOSFET.

### 3.2 HV MOSFET Applications

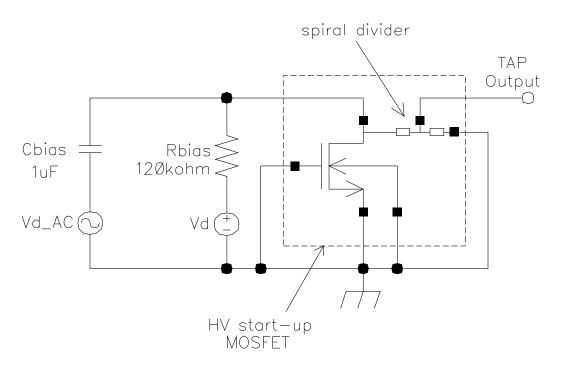

The AC/DC convertor [28] has been selected as an example of a typical application of HV start-up MOSFET with the polysilicon spiral divider. The simplified AC/DC convertor circuit is depicted in Fig. 3.5. The HV start-up MOSFET subblock is modeled by the circuit in Fig. 4.7 and by the equations introduced in this thesis.

The voltage reference  $V_{\rm ref1}$  determines the voltage (in Comparator A) to which the external capacitor  $C_{\rm vcc}$  is charged up and basically determines the voltage at which the HV start-up MOSFET is switched off. This solution decreases the power consumption in comparison with older solution where the external capacitor  $C_{\rm vcc}$  was permanently charged through an external resistor. The solution with HV spiral divider enables to switch off the charging in case the external capacitor  $C_{\rm vcc}$  is charged up enough. The voltage reference  $V_{\rm ref2}$  determines when the whole AC/DC convertor is switched on based on the direct sensing of high voltage by the spiral divider described in this thesis. The high input voltage is divided by the spiral divider and compared in Comparator B with the voltage reference  $V_{\rm ref2}$ . It means that the AC/DC convertor is turned off if the input high voltage is lower than defined value (depends on product specification, e.g. 112 V). For more applications see [29] for design of a 65 W adapter, [30] for 32 W, 32 V universal input AC-DC printer adapter, and [31] for designing converters with the NCP101X family.

**Figure 3.5.** The simplified circuit of AC/DC convertor. The HV start-up MOSFET subblock is modeled by the circuit in Fig. 4.7.

The circuits that use HV start-up MOSFET with spiral divider allow designing applications with many features such as:

- The Dynamic Self-Supply

- No need of auxiliary winding [31]

- Low Standby-Power

- High Voltage Sensing

- Brown-out Protection [29]

- Line Overvoltage Protection [29].

**Figure 3.6.** Layout of AC/DC convertor.

# **Chapter 4 Spiral Divider Modeling**

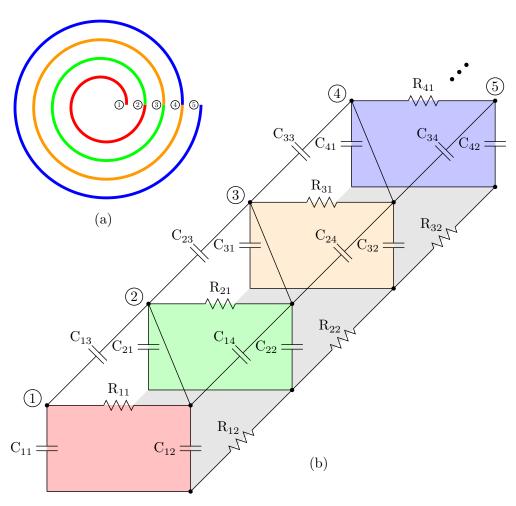

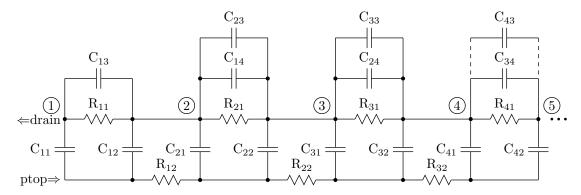

This chapter deals with the proposed and implemented DC and AC model of the nonlinear spiral high voltage polysilicon divider which is one of the fundamental results (new scientific findings) of this thesis. For the purpose of the equivalent lumped element circuit creation the polysilicon spiral is divided into several separate spiral elements. This division is shown in Fig. 4.1(a) where each spiral element has a different color. For better lucidity only the first four turns are depicted in this figure. The equivalent 3D circuit in Fig. 4.1(b) is obtained if these spiral elements are uncoiled to parallel plains. The 3D equivalent circuit in Fig. 4.1(b) can be redrawn for better lucidity to the 2D equivalent circuit, which is depicted in Fig. 4.2.

**Figure 4.1.** Equivalent lumped 3D circuit of first four spiral poly subsegments and ptop: (a) colored spiral subsegment, (b) equivalent circuit. Colors from (a) match (b).

Figure 4.2. Equivalent lumped 2D circuit of first four spiral poly subsegments and ptop.

### 4.1 Spiral Element Length

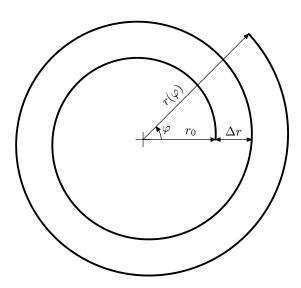

In this section the length L of a spiral is determined. The spiral divider of the HV MOSFET transistor is a special case of the Archimedes spiral. The radius r of the spiral is increased in one turn by a radius increment  $\Delta r$ . The basic equation defined in polar coordinates for the radius is

$$r = r_0 + \varphi \frac{\Delta r}{2\pi} \tag{24}$$

where  $r_0$  is an initial radius of the spiral and  $\varphi$  is an actual angle circumscribed by the spiral. The parameters of the spiral are depicted in Figure 4.3.

The curve length can be calculated in the following way. If  $f(\varphi)$  is the function of the curve in polar coordinates then the length L of the curve is defined as

$$L = \int_{\psi}^{\phi} \sqrt{[f(\varphi)]^2 + \left(\frac{\mathrm{d}f(\varphi)}{\mathrm{d}\varphi}\right)^2} \mathrm{d}\varphi$$

(25)

Figure 4.3. Schematic drawing of the spiral parameters.

For the spiral defined in polar coordinates by (24) the spiral length L is obtained by substituting the equation (24) into (25):

$$L = \int_{\psi}^{\phi} \sqrt{\left(r_0 + \varphi \frac{\Delta r}{2\pi}\right)^2 + \left(\frac{\Delta r}{2\pi}\right)^2} d\varphi \tag{26}$$

where  $\phi$  is an angle circumscribed by a whole spiral. The beginning of the spiral is given by initial radius  $r_0$  and therefore it is assumed the starting angle  $\psi = 0$ . The solution of the integral yields the following expression

$$L = \frac{\Delta r}{4\pi} \ln \left( \frac{r_0 + \phi \frac{\Delta r}{2\pi} + \sqrt{\left(r_0 + \phi \frac{\Delta r}{2\pi}\right)^2 + \frac{\Delta r^2}{4\pi^2}}}{r_0 + \sqrt{r_0^2 + \frac{\Delta r^2}{4\pi^2}}} \right) + \left( \frac{r_0 \pi}{\Delta r} + \frac{\phi}{2} \right) \sqrt{\left(r_0 + \phi \frac{\Delta r}{2\pi}\right)^2 + \frac{\Delta r^2}{4\pi^2}} - \frac{r_0 \pi}{\Delta r} \sqrt{r_0^2 + \frac{\Delta r^2}{4\pi^2}}$$

(27)

The logarithmic term in (27) can be neglected. The difference caused by neglecting this logarithm therm is below 0.05 % for initial radiuses bigger than 10  $\mu$ m. The equation for the length L of the spiral after neglecting logarithmic term reduces to

$$L = \left(\frac{r_0 \pi}{\Delta r} + \frac{\phi}{2}\right) \sqrt{\left(r_0 + \phi \frac{\Delta r}{2\pi}\right)^2 + \frac{\Delta r^2}{4\pi^2}} - \frac{r_0 \pi}{\Delta r} \sqrt{r_0^2 + \frac{\Delta r^2}{4\pi^2}}$$

(28)

When  $\Delta r \ll r_0$  then the equation (28) can be simplified to

$$L = r_0 \phi + \frac{\Delta r}{4\pi} \phi^2 \tag{29}$$

and the length of the spiral segment between angles  $\varphi_1$  and  $\varphi_2$  can be calculated based on (29) as

$$L_{\varphi_1,\varphi_2} = r_0(\varphi_2 - \varphi_1) + \frac{\Delta r}{4\pi}(\varphi_2^2 - \varphi_1^2)$$

(30)

The calculated and process parameters of the spiral are summarized in Table 4.1 and calculated parameters of each spiral segment are summarized in Table 4.2.

| Parameter       | Value  | Unit                 | Note                            |

|-----------------|--------|----------------------|---------------------------------|

| $r_0$           | 72.47  | $\mu \mathrm{m}$     | initial radius of the spiral    |

| $\Delta r$      | 2      | μm                   | radius increment                |

| $L_{ m tot}$    | 19208  | μm                   | whole spirale length            |

| $L_2$           | 192.69 | $\mu \mathrm{m}$     | sense spiral segment length     |

| $R_{ m SHpoly}$ | 5000   | $\Omega/\mathrm{sq}$ | HR polysilicon sheet resistance |

| $R_{ m tot}$    | 96.041 | $\mathrm{M}\Omega$   | whole spirale resistance        |

| $R_2$           | 963.5  | $\mathrm{k}\Omega$   | sense spiral segment resistance |

| $t_{ m poly}$   | 350    | nm                   | polysilicon thickness           |

| $t_{ m FOX}$    | 1.1    | $\mu \mathrm{m}$     | field oxide thickness           |

| $W_{ m poly}$   | 1      | $\mu \mathrm{m}$     | polysilicon width               |

**Table 4.1.** Calculated and process parameters of the spiral (for  $V_D \to 0$ ).

| Spiral segment | $arphi_1$ | $arphi_2$ | Length             | Calc. resistance         |

|----------------|-----------|-----------|--------------------|--------------------------|

| order          | [rad]     | [rad]     | $[\mu \mathrm{m}]$ | $(@V_D \to 0) [M\Omega]$ |

| 1              | $0\pi$    | $2\pi$    | 461.63             | 2.308                    |

| 2              | $2\pi$    | $4\pi$    | 474.19             | 2.371                    |

| 3              | $4\pi$    | $6\pi$    | 486.76             | 2.434                    |

| 4              | $6\pi$    | $8\pi$    | 499.32             | 2.497                    |

| 5              | $8\pi$    | $10\pi$   | 511.89             | 2.559                    |

| 6              | $10\pi$   | $12\pi$   | 524.46             | 2.622                    |

| 7              | $12\pi$   | $14\pi$   | 537.02             | 2.685                    |

| 8              | $14\pi$   | $16\pi$   | 549.59             | 2.748                    |

| 9              | $16\pi$   | $18\pi$   | 562.16             | 2.811                    |

| 10             | $18\pi$   | $20\pi$   | 574.72             | 2.874                    |

| 11             | $20\pi$   | $22\pi$   | 587.29             | 2.936                    |

| 12             | $22\pi$   | $24\pi$   | 599.86             | 2.999                    |

| 13             | $24\pi$   | $26\pi$   | 612.42             | 3.062                    |

| 14             | $26\pi$   | $28\pi$   | 624.99             | 3.125                    |

| 15             | $28\pi$   | $30\pi$   | 637.55             | 3.188                    |

| 16             | $30\pi$   | $32\pi$   | 650.12             | 3.251                    |

| 17             | $32\pi$   | $34\pi$   | 662.69             | 3.313                    |

| 18             | $34\pi$   | $36\pi$   | 675.25             | 3.376                    |

| 19             | $36\pi$   | $38\pi$   | 687.82             | 3.439                    |

| 20             | $38\pi$   | $40\pi$   | 700.39             | 3.502                    |

| 21             | $40\pi$   | $42\pi$   | 712.95             | 3.565                    |

| 22             | $42\pi$   | $44\pi$   | 725.52             | 3.628                    |

| 23             | $44\pi$   | $46\pi$   | 738.09             | 3.690                    |

| 24             | $46\pi$   | $48\pi$   | 750.65             | 3.753                    |

| 25             | $48\pi$   | $50\pi$   | 763.22             | 3.816                    |

| 26             | $50\pi$   | $52\pi$   | 775.78             | 3.879                    |

| 27             | $52\pi$   | $54\pi$   | 788.35             | 3.942                    |

| 28             | $54\pi$   | $56\pi$   | 800.92             | 4.005                    |

| 29             | $56\pi$   | $58\pi$   | 813.48             | 4.067                    |

| 30             | $58\pi$   | 186.227   | 526.35             | 2.632                    |

| 31             | 186.227   | 187.687   | 192.69             | 0.963                    |

**Table 4.2.** Calculated parameters of the spiral segments

The resistances for  $V_D \to 0$  are calculated as