Master's thesis

Faculty of Electrical Engineering Department of Measurement

# FPGA Based Robotic Motion Control System

Bc. Martin Meloun

June 2014 Supervisor: Ing. Pavel Píša Ph.D.

ČESKÉ VYSOKÉ UČENÍ TECHNICKÉ V PRAZE

Fakulta elektrotechnická Katedra měření

Akademický rok 2012-2013

# ZADÁNÍ DIPLOMOVÉ PRÁCE

Student:

Bc. Martin Meloun

Studijní program: Obor: Kybernetika a robotika Senzory a přístrojová technika

Název tématu česky:

Systém pro řízení pohybu robota využívající FPGA

Název tématu anglicky:

FPGA Based Robotic Motion Control System

#### Pokyny pro vypracování:

Seznamte se s již řešenými projekty systémů pro řízení polohy na bázi knihovny PXMC a proveďte jejich rozšíření, integraci a portaci na perspektivní kombinace FPGA a CPU (jak diskrétní, tak implementované na FPGA).

- a) Zpracujte přehled použitelných kombinací FPGA a CPU pro danou aplikaci, zaměřte se i na výkonnost a cenovou dostupnost jednotlivých řešení s diskrétními a syntetizovanými CPU.

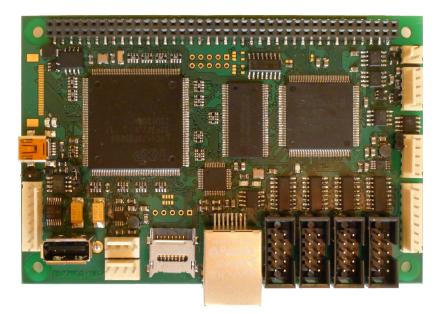

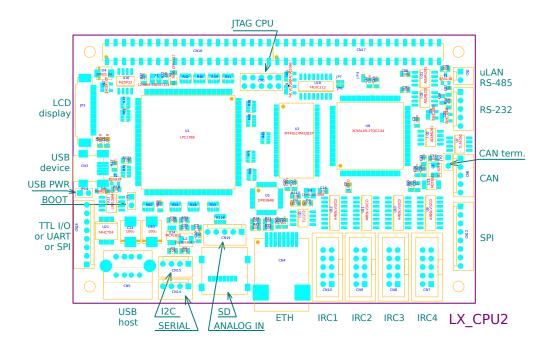

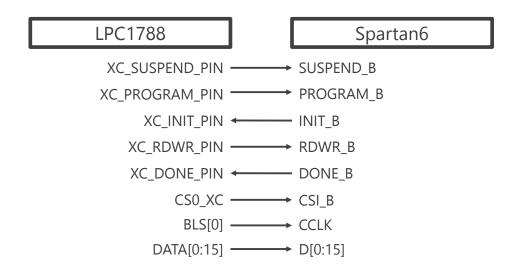

- b) Implementujte ve VHDL rozhraní pro přístup k syntetizovaným periferiím v FPGA Spartan 6 připojeném k mikrokontroléru LPC1788 na desce LX\_CPU1 a navrhněte potřebné periferie pro řízení 4 až 6 stejnosměrných motorů. K otestování funkce lze využít mechaniku robota BlueBot.

- c) Navrhněte rozšíření periferií pro řízení bezkartáčových motorů.

- d) Podle možností navrhněte další možná (budoucí) rozšíření systému, například portaci do prostředí operačního systému reálného času, využití sběrnice CAN nebo komunikace ETHERNET pro řízení robota atd.

#### Seznam odborné literatury:

- [1] Volnei A. Pedroni: Digital Electronics and Design with VHDL, MORGAN KAUFMANN 2008, ISBN: 0123742706

- [2] Enoch O. Hwang: Digital Logic and Microprocessor Design with VHDL, Thomson 2006, ISBN: 0-534-46593-5

- [3] Skup Konrad R.: Motion Control for Mobile Robots: Basics and Concepts of PXMC Library for Brushless DC Motors, 2008, ISBN: 978-3639086140

- [4] Burian V.: Využití programovatelného pole pro řízení bezkartáčových motorů, bakalářská práce ČVUT FEL

2011

- [5] LPC17xx User manual, Rev. 2, NXP Semiconductors, 19 August 2010

- [6] Knihovna PXMC, http://pxmc.org/, GIT http://www.pikron.com/pxmc/git/pxmc.git, 2001 2012, PiKRON s.r.o.

Vedoucí diplomové práce: Datum zadání diplomové práce: Platnost zadání do<sup>1</sup>:

Hagh

Prof. Ing. Vladimír Haasz, CSc. vedoucí katedry

Ing. Pavel Píša, Ph.D. (K13135) 14. prosince 2012 30. června 2014

L.S.

Mr

Prof. Ing. Pavel Ripka, CSc. děkan

V Praze dne 14.12.2012

<sup>&</sup>lt;sup>1</sup> Platnost zadání je omezena na dobu tří následujících semestrů.

## Acknowledgement

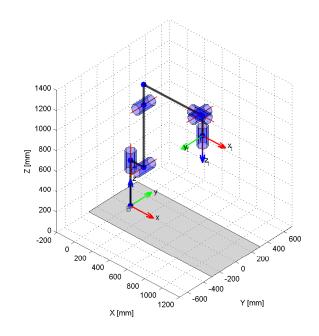

I would like to express my gratitude to Ing. Pavel Píša Ph.D. for supervision, useful comments, remarks and support for this master thesis. Furthermore I would like to thank Ing. Tomáš Pajdla Ph.D. for permission to publish my research report supervised by him as an appendix of this thesis.

#### **Declaration**

I declare that I worked out the presented thesis independently and I quoted all used sources of information in accord with methodical instructions about ethical principles for writing academic thesis.

### Abstrakt

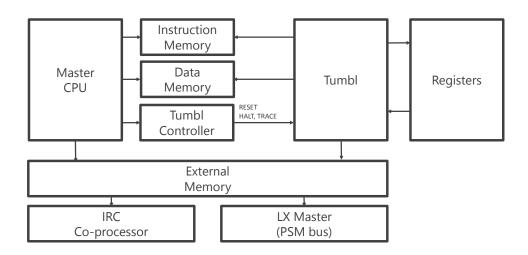

Diplomová práce se zabývá zpracováním přehledu použitelných kombinací CPU a FPGA pro centralizované řízení až 4 PMSM motorů a dále návrhem samotných periferií v FPGA pro samotné řízení. Prvně je zpracován přehled možných kombinací CPU a FPGA, i s možností použití jenom FPGA a v něm syntetizovaný procesor, a to vzhledem k výkonu a ceně. Dále je popsáno oživení FPGA na zvolené platformě a komunikace mezi CPU a FPGA. Poté pokračuje odvozením periferií pro řízení PMSM motorů. Samotné motory pak řídí výkonový modul, který je propojen s řídícím modulem přes vlastní typ sběrnice, pro kterou byla navržena odpovídající periferie. Diplomová práce využívá předchozích projektů systémů pro řízení motorů, konkrétně PXMC knihovny a sysless frameworku jako podklad pro embedded aplikaci na CPU, oboje od firmy PiKRON . Cílem práce je připravit platformu k produktizaci.

#### Klíčová slova

CPU, FPGA, LPC1788, Spartan6, LX\_CPU1, PMSM motor, syntetizovatelný procesor, robot, řízení polohy, Tumbl, PXMC, sysless

### Abstract

This master thesis presents a platform research about possible CPU and FPGA combinations for centralized control system for up to 4 PMSM motors, alongside with design of the FPGA peripherals needed for the actual controller. At the beginning a platform overview is presented, including the option to use a synthesized controller inside FPGA, with performance and cost of each platform in mind. Then there is a description on how to configure FPGA on the chosen platform and how to communicate between CPU and FPGA. Then peripherals for PMSM motor controller are derived. The motors themselves are controlled by power stage module, which is connected with the control module using a custom bus, for which a relevant peripheral was designed. This thesis bases on previous PMSM motor control systems, namely PXMC library and sysless framework as a base for an embedded application on CPU, both developed by PiKRON. The goal of this thesis is to ready the platform for productization.

#### **Keywords**

CPU, FPGA, LPC1788, Spartan6, LX\_CPU1, PMSM motor, synthesized controller, robot, motion control, Tumbl, PXMC, sysless

# Contents

| 1. | Intro | oduction 1                                                                         |

|----|-------|------------------------------------------------------------------------------------|

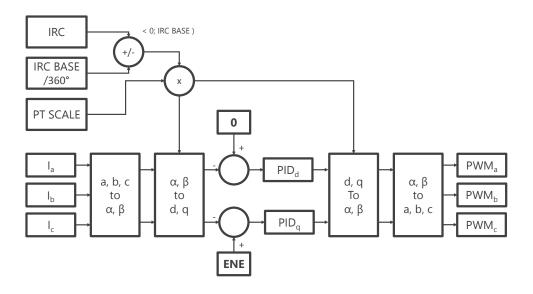

|    | 1.1.  | PMSM Motor Controller                                                              |

|    | 1.2.  | Planning                                                                           |

| _  |       |                                                                                    |

| 2. | Plat  |                                                                                    |

|    | 2.1.  | 0                                                                                  |

|    | 2.2.  | Sysless Framework                                                                  |

|    | 2.3.  | Synthesized CPU Cores                                                              |

|    | 2.4.  | The Platform                                                                       |

|    | 2.5.  | Spartan-6 Wiring And Configuration                                                 |

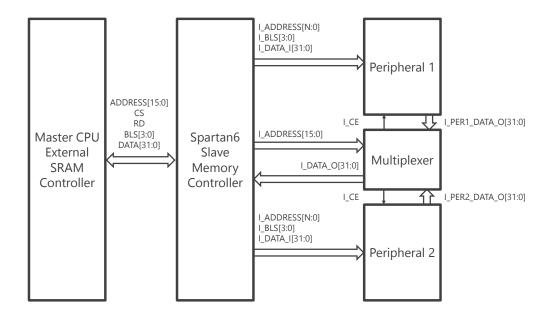

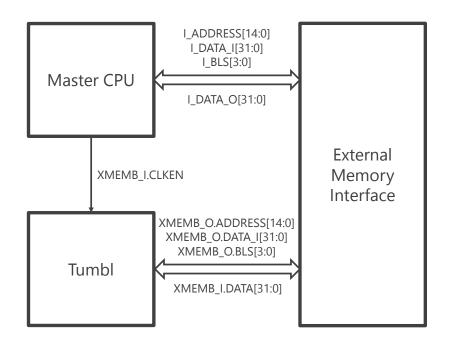

|    | 2.6.  | Slave Memory Controller                                                            |

|    | 2.7.  | Power Stage Module                                                                 |

| 2  | EDC   | A Peripherals Analysis 15                                                          |

| з. |       |                                                                                    |

|    |       |                                                                                    |

|    | 3.2.  |                                                                                    |

|    |       | IRC Peripheral                                                                     |

|    | 3.4.  | Power Stage Module Communication                                                   |

| 4. | Tum   | bl Co-processor Core 21                                                            |

|    |       | Overview                                                                           |

|    | 4.2   | Minimalization Of The Core                                                         |

|    | 4.3.  | Co-processor Modifications                                                         |

|    | 4.4.  |                                                                                    |

|    |       | 4.4.1. Conditional Execution                                                       |

|    |       | 4.4.2.         Branching With Link         26                                      |

|    |       | 4.4.3. Count Leading Zeroes                                                        |

|    |       | 4.4.4. Instruction Binary Encoding Changes                                         |

|    |       | 4.4.5. Assembler Changes                                                           |

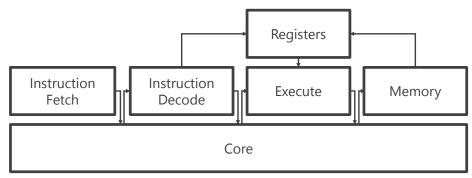

|    | 4.5.  | Processor Pipeline                                                                 |

|    | 4.9.  |                                                                                    |

|    |       |                                                                                    |

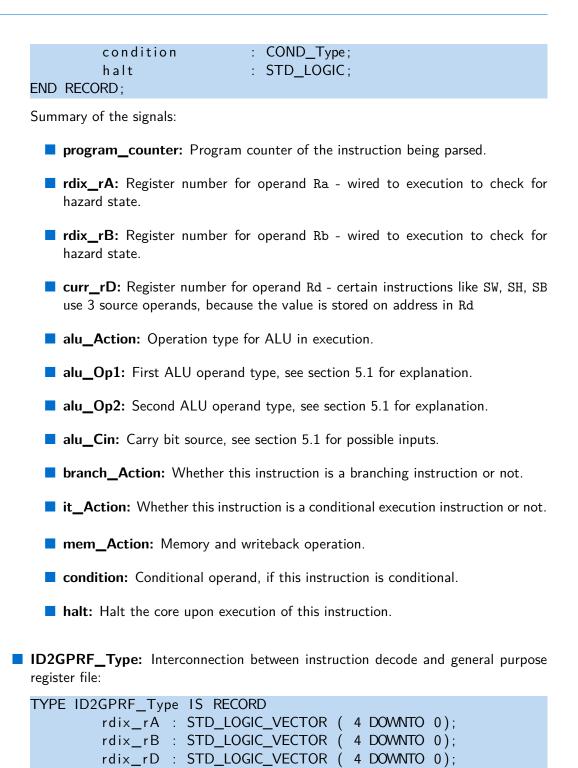

|    |       | 4.5.2. Instruction Decode                                                          |

|    |       | 4.5.3. Execution                                                                   |

|    |       | 4.5.4. Memory And Writeback                                                        |

|    |       | 4.5.5. General Purpose Register File                                               |

|    |       | 4.5.6. Core Component                                                              |

|    |       | 4.5.7. Top Module                                                                  |

|    | 4.6.  | Division                                                                           |

|    | 4.7.  | External Memory Interface                                                          |

|    | 4.8.  | C lanugage support                                                                 |

|    | 4.9.  | Pipeline Balance                                                                   |

| 5  | Tum   | bl Co-processor Implementation 34                                                  |

| 5. |       | Enumerations                                                                       |

|    | 5.2.  | Records                                                                            |

|    | 5.3.  | Entities                                                                           |

|    | 5.5.  | 5.3.1. Instruction Fetch                                                           |

|    |       | 5.3.1. Instruction Fetch         42           5.3.2. Instruction Decode         43 |

|    |       | $3.3.2. $ modululi Decode $\ldots$ 43                                              |

|    |                                                             | 5.3.3.         Execution         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                             |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 43<br>44                                                                                                                                      |

|----|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------|----------------------------------------------------------------------|---------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|    | 5.4.                                                        | 5.3.5. Core Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 44<br>45                                                                                                                                      |

|    |                                                             | 5.4.1. General Purpose Registers File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 46                                                                                                                                            |

|    | 5.5.                                                        | Top Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •           |                                                                                                 | •                                         | •                                       |                                                                      |                                       |                         | 46                                                                                                                                            |

| 6. |                                                             | er FPGA Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 48                                                                                                                                            |

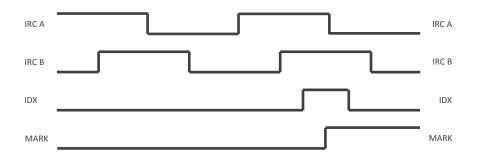

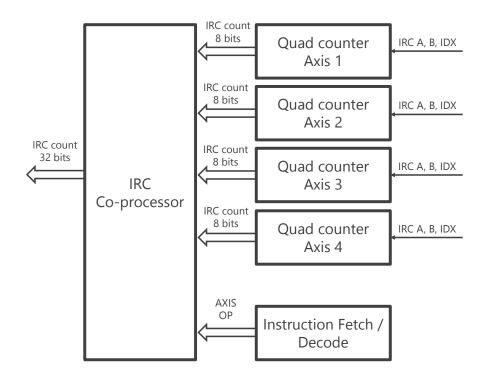

|    | 6.1.                                                        | IRC Co-processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 48                                                                                                                                            |

|    | 6.0                                                         | 6.1.1. Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 48                                                                                                                                            |

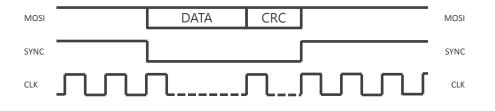

|    | 0.2.                                                        | LX Master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 49<br>50                                                                                                                                      |

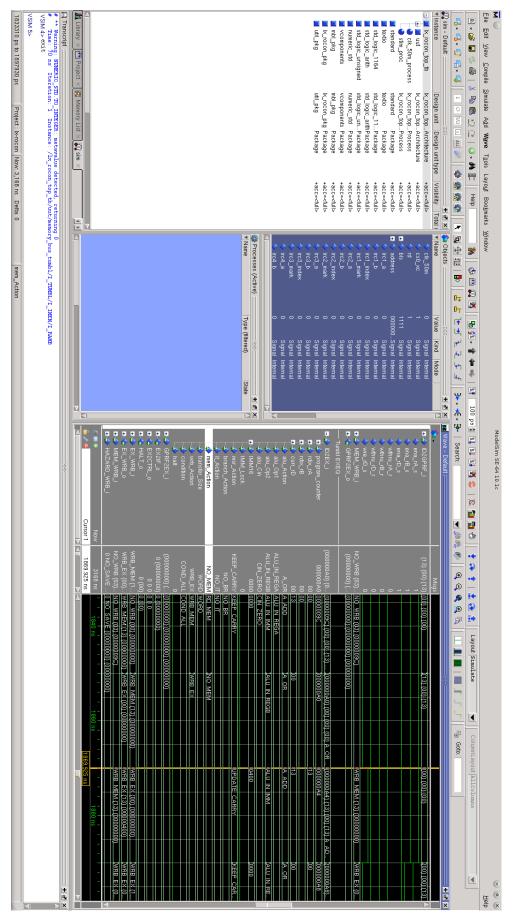

| 7. | FPG                                                         | GA Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 52                                                                                                                                            |

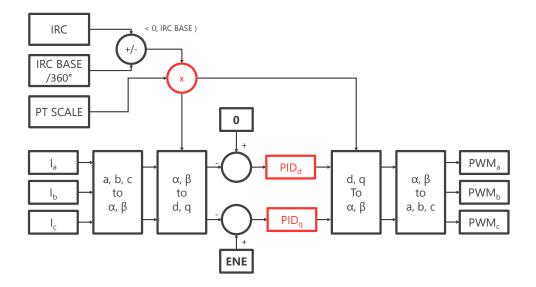

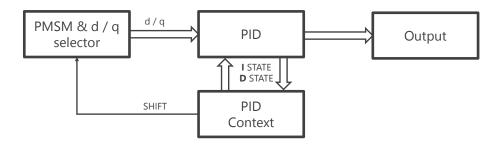

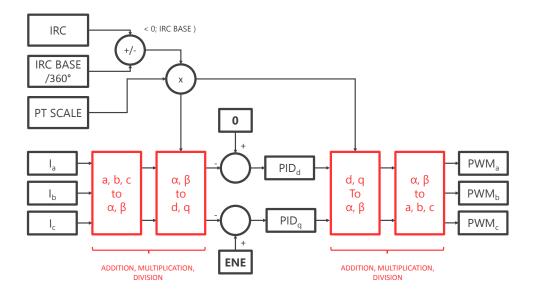

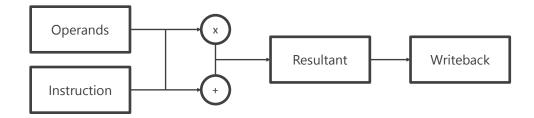

|    | 7.1.                                                        | ModelSIM Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                 |                                           |                                         |                                                                      |                                       |                         | 52                                                                                                                                            |