Czech Technical University in Prague Faculty of Electrical Engineering Department of Computer Science and Engineering

# System for Solving Linear Equation Systems

by

Luboš Vondra

A thesis submitted to the Faculty of Electrical Engineering, Czech Technical University in Prague, in partial fulfilment of the requirements for the degree of Doctor.

PhD programme: Electrical Engineering and Information Technology Specialization: Computer Science and Engineering

December 2013

# Thesis Supervisor:

prof. Ing. Róbert Lórencz, CSc. Department of Computer Systems Faculty of Information Technology Czech Technical University in Prague Thákurova 9 160 00 Praha 6 Czech Republic

Copyright  $\bigodot$  2013 by Luboš Vondra

# Abstract and contributions

A huge number of problems in various fields of science leads to System of linear equations (SLE) representation. The problems that also lead to a differential equation set should be included here because their solution is obviously obtained by solving a corresponding linear equation system. Due to these facts it is very important to be able to solve SLE accurately and quickly.

The thesis presents a system for solving huge SLEs quickly, numerically stable and indeed accurately to eliminate the problem of generating rounding errors and their propagation through the rest of the computation. This problem is eliminated by solving the SLE by means of Residual Number System (RNS) and Gaussian elimination in modular arithmetic.

The main contributions of the thesis are as follows:

- 1. System optimizations of operation multiplication with reduction. The special case for many multiplications with one common factor (multiplication of vector by scalar value).

- 2. System optimizations of solving a SLE by means of RNS, including application of the first mentioned contribution.

- 3. A new mixed radix conversion algorithm suitable for parallel implementation including the possibility of balancing and sufficient precision determination.

### Keywords:

Set of Linear Equations, System Optimizations, Residual Arithmetic, Residual Number System, Set of Linear Congruencies, Floating Point Arithmetic, Exact Arithmetic, Mixed Radix Conversion, Parallel Computing, Single Instruction Multiple Data

# Acknowledgements

First of all, I would like to express my gratitude to prof. Ing. Róbert Lórencz, CSc., my thesis supervisor. He has been a constant source of encouragement and insight during my research and provided me with numerous opportunities for professional advancements. His continuous support is gratefully acknowledged. His efforts as thesis supervisor contributed substantially to the quality and completeness of the thesis. I have learned a great deal from them. I have been fortunate to carry out the research for this dissertation under the supervision of prof. Ing. Róbert Lórencz, CSc.

I would like to express my special appreciation to my colleagues from the Applied Numerical Mathematics and Cryptography group, namely Ing. Tomáš Zahradnický, Ph.D., Ing. Jiří Buček and others.

The staff of our department has provided me with a pleasant and flexible environment for my research. Especially, I would like to thank doc. Ing. Miroslav Šnorek, CSc., the head of the department, and the former head of the department, prof. Ing. Pavel Tvrdík, CSc for taking care of my financial support. My work has been partially supported by the Ministry of Education, Youth, and Sport of the Czech Republic under research program MSM 6840770014.

Many other people influenced my work. I wish to thank my colleagues from the Seznam.cz a.s., namely Ing. Michal Bukovský, Mgr. Jan Klesnil, Filip Volejník and others whose encouragement has always been a valuable source of support.

Finally, my greatest thanks go to my family and friends whose support was of great importance during the times of writing this thesis.

Dedication

To my wife Eliška, my sons Martin and Filip, my parents and the rest of my family.

# Contents

| 1        | Intr | oducti   | on 1                                                                                                                                                           |

|----------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | Motiva   | 1 ation                                                                                                                                                        |

|          | 1.2  | Proble   | $em statement \dots \dots$                               |

|          | 1.3  | Contri   | butions of the thesis $\ldots \ldots 2$                                           |

|          | 1.4  | Organ    | ization of the thesis                                                                                                                                          |

| <b>2</b> | Stat | ce-of-tl | ne-Art 4                                                                                                                                                       |

| 3        | Our  | Appr     | oach 6                                                                                                                                                         |

|          | 3.1  | Theor    | y                                                                                                                                                              |

|          |      | 3.1.1    | Outline                                                                                                                                                        |

|          |      | 3.1.2    | Transformation to integer numbers                                                                                                                              |

|          |      | 3.1.3    | Transformation into $\mathcal{Z}_n \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $                                                            |

|          |      | 3.1.4    | Gaussian elimination with non-zero pivoting                                                                                                                    |

|          |      | 3.1.5    | RNS and mixed radix representation                                                                                                                             |

|          | 3.2  | Impler   | $nentation \dots \dots$                                  |

|          |      | 3.2.1    | Transformation into integer number space $\mathcal{Z}$                                                                                                         |

|          |      | 3.2.2    | Transformation into $Z_n \ldots \ldots$ |

|          |      | 3.2.3    | Set of linear congruencies                                                                                                                                     |

|          |      | 3.2.4    | The calculation of Final results                                                                                                                               |

|          |      | 3.2.5    | Final result verification                                                                                                                                      |

|          |      | 3.2.6    | System Architecture                                                                                                                                            |

|          | 3.3  | Comp     | lexity                                                                                                                                                         |

|          |      | 3.3.1    | Time complexity                                                                                                                                                |

|          |      |          | 3.3.1.1 Transformation to integer numbers                                                                                                                      |

|          |      |          | 3.3.1.2 SLC                                                                                                                                                    |

|          |      |          | 3.3.1.3 Transformation to real numbers                                                                                                                         |

|          |      |          | 3.3.1.4 Overall complexity $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 21$                                                                 |

|          |      | 3.3.2    | Memory consumption                                                                                                                                             |

|          |      |          | 3.3.2.1 Transformation to integer numbers                                                                                                                      |

|          |                |             | 3.3.2.2 SLC                                                                                     | 24 |

|----------|----------------|-------------|-------------------------------------------------------------------------------------------------|----|

|          |                |             | 3.3.2.3 Transformation to real numbers                                                          | 25 |

|          |                |             | 3.3.2.4 Total memory consumption                                                                | 26 |

|          |                | 3.3.3       | Communication complexity                                                                        | 26 |

| 4        | $\mathbf{Sys}$ | $tem O_{1}$ | ptimizations 2                                                                                  | 28 |

|          | 4.1            | Motiva      | ation $\ldots$ | 28 |

|          |                | 4.1.1       | Assumptions                                                                                     | 28 |

|          | 4.2            | Result      | 58                                                                                              | 29 |

|          |                | 4.2.1       | Multiplication with reduction                                                                   | 30 |

|          |                |             | 4.2.1.1 Integer Approach                                                                        | 30 |

|          |                |             | 4.2.1.2 Floating Point Approach with <b>fmod/remainder</b> Functions 3                          | 30 |

|          |                |             | 4.2.1.3 Optimized Floating Point Approach                                                       | 31 |

|          |                |             | 4.2.1.4 Floating Point Approach with $MMX^{TM}$ and $SSE2 \dots $                               | 32 |

|          |                |             | 4.2.1.5 Floating Point Approach with SSE2 by Intel Intrinsics                                   | 35 |

|          |                | 4.2.2       | Gaussian elimination                                                                            | 36 |

|          |                |             | 4.2.2.1 Using SSE2 for Gaussian elimination                                                     | 36 |

|          |                |             | 4.2.2.2 Montgomery domain                                                                       | 37 |

|          |                |             | 4.2.2.3 Optimizations for sparse matrices                                                       | 38 |

|          |                | 4.2.3       | Memory demands                                                                                  | 39 |

|          |                |             | 4.2.3.1 Auxiliary data structures                                                               | 39 |

|          |                |             | 4.2.3.2 Shared memory                                                                           | 40 |

|          | 4.3            | Exper       | iments and Evaluation                                                                           | 42 |

|          |                | 4.3.1       | Multiplication with reduction and Gaussian elimination                                          | 42 |

|          |                |             | 4.3.1.1 Rationale                                                                               | 46 |

|          |                | 4.3.2       | Memory demands                                                                                  | 47 |

|          |                |             | 4.3.2.1 Auxiliary data structures                                                               | 47 |

|          |                |             | 4.3.2.2 Shared memory                                                                           | 48 |

|          | 4.4            | Summ        | ary                                                                                             | 50 |

| <b>5</b> | Dec            | entrali     | ization 5                                                                                       | 52 |

|          | 5.1            | Motiva      | ation                                                                                           | 52 |

|    | 5.2 Results $\ldots$ |          |                                                                                                                                                                  |           |  |

|----|-------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|

|    |                                                                                                       | 5.2.1    | Prime number generation                                                                                                                                          | 52        |  |

|    |                                                                                                       | 5.2.2    | Mixed Radix Conversion                                                                                                                                           | 53        |  |

|    |                                                                                                       |          | 5.2.2.1 Total distributed ordering $\ldots \ldots $                                 | 54        |  |

|    |                                                                                                       |          | 5.2.2.2 Precision Resolving – Round Robin                                                                                                                        | 57        |  |

|    | 5.3                                                                                                   | Experi   | ments and Evaluation                                                                                                                                             | 58        |  |

|    |                                                                                                       | 5.3.1    | Prime number generation                                                                                                                                          | 59        |  |

|    |                                                                                                       | 5.3.2    | Mixed Radix Conversion $\ldots \ldots \ldots$    | 60        |  |

|    |                                                                                                       | 5.3.3    | System Architecture                                                                                                                                              | 62        |  |

|    |                                                                                                       | 5.3.4    | Process architecture                                                                                                                                             | 62        |  |

|    |                                                                                                       |          | 5.3.4.1 SLC solver thread $\ldots \ldots \ldots$ | 63        |  |

|    |                                                                                                       |          | 5.3.4.2 MRC thread $\ldots \ldots \ldots$        | 65        |  |

|    |                                                                                                       |          | 5.3.4.3 Message processor                                                                                                                                        | 65        |  |

|    |                                                                                                       |          | 5.3.4.4 Process architecture summary                                                                                                                             | 66        |  |

|    |                                                                                                       | 5.3.5    | Complexity                                                                                                                                                       | 67        |  |

|    |                                                                                                       |          | 5.3.5.1 Time complexity $\ldots \ldots \ldots$   | 67        |  |

|    |                                                                                                       |          | 5.3.5.2 Memory consumption                                                                                                                                       | 68        |  |

|    |                                                                                                       |          | 5.3.5.3 Communication complexity                                                                                                                                 | 68        |  |

|    |                                                                                                       | 5.3.6    | Architecture impact                                                                                                                                              | 70        |  |

|    |                                                                                                       | 5.3.7    | Scalability                                                                                                                                                      | 71        |  |

|    | 5.4                                                                                                   | Summ     | ary                                                                                                                                                              | 72        |  |

| 6  | App                                                                                                   | olicatio | n 7                                                                                                                                                              | 73        |  |

| 7  | Con                                                                                                   | clusior  | 15 7                                                                                                                                                             | 75        |  |

| 0  | <b>D</b> 4-                                                                                           |          |                                                                                                                                                                  | 70        |  |

| 8  | Futi                                                                                                  | ıre Wo   | ſĸ (                                                                                                                                                             | 76        |  |

| 9  | Bibl                                                                                                  | iograp   | hy 7                                                                                                                                                             | 77        |  |

| 10 | Refe                                                                                                  | ereed I  | Publications of the Author 8                                                                                                                                     | <b>30</b> |  |

| 11 | Unr                                                                                                   | efereed  | l Publications of the Author 8                                                                                                                                   | 81        |  |

| Α | $\operatorname{List}$ | of Abbreviations         | 82 |

|---|-----------------------|--------------------------|----|

| в | Mor                   | ntgomery domain          | 83 |

|   | B.1                   | Introduction             | 83 |

|   | B.2                   | Formal statement         | 83 |

|   | B.3                   | Rationale                | 84 |

|   | B.4                   | Description of Algorithm | 85 |

# List of Figures

| 3.1 | Linsolve architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

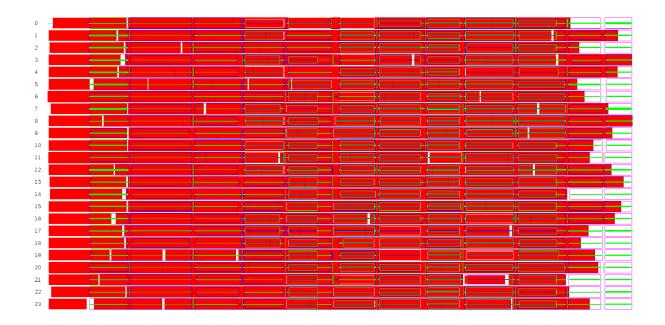

| 3.2 | An example of the Node workload $(n = 500, p = 5)$ - The graph of different<br>processes utilization. The blue colour represents the master process and the<br>red colour represents slave processes. The master process is idle almost all<br>the time, while the slave processes are busy.                                                                                                                                                                                                                                                          | 22 |

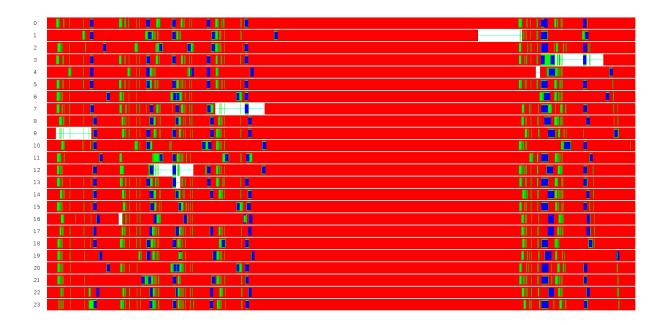

| 3.3 | An example of the Node workload $(n = 500, p = 24)$ where starvation is<br>obvious - The meaning of colours remains the same as in 3.2. Master process<br>is busy at later stage of computation and the slave processes starve (the gaps                                                                                                                                                                                                                                                                                                              |    |

|     | in red bars).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23 |

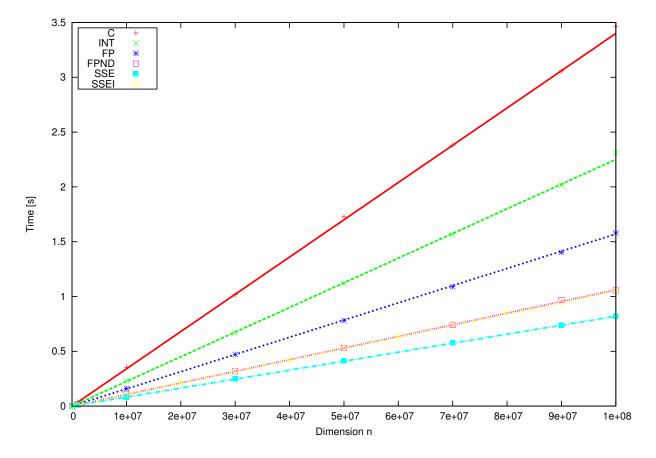

| 4.1 | Vector multiplication with reduction timings - The meaning of lines is as<br>follows. C - pure C implementation; INT - integer assembler implementa-<br>tion; FP - floating point implementation; FPND - floating point without<br>division; SSE - floating point without division by means of SSE; SSEI - SSE<br>implemented by means of Intel intrinsics                                                                                                                                                                                            | 43 |

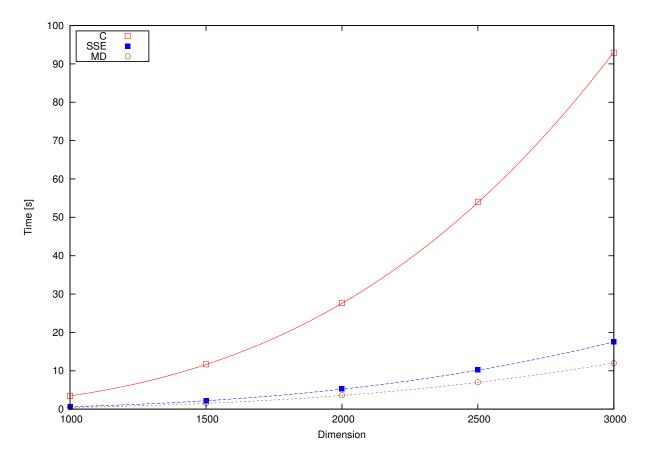

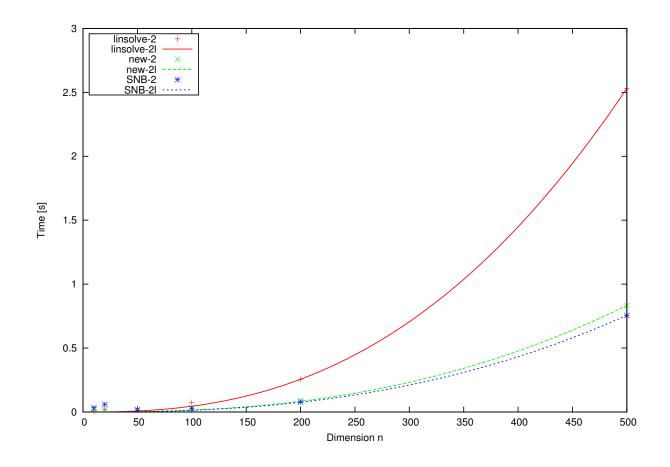

| 4.2 | Gaussian elimination timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45 |

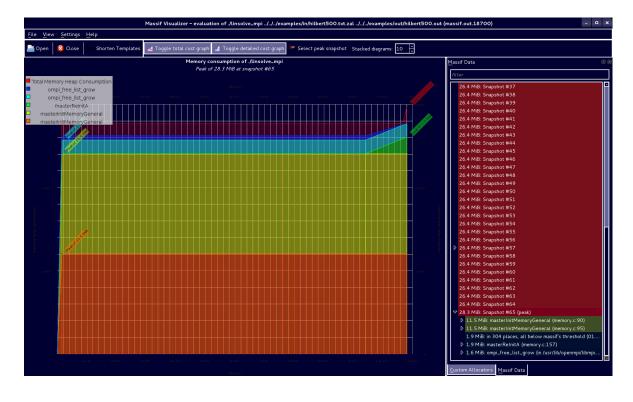

| 4.3 | Memory demands with a bad index order $(n = 500, m = 3000)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47 |

| 4.4 | Memory demands with a good index order $(n = 500, m = 3000)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48 |

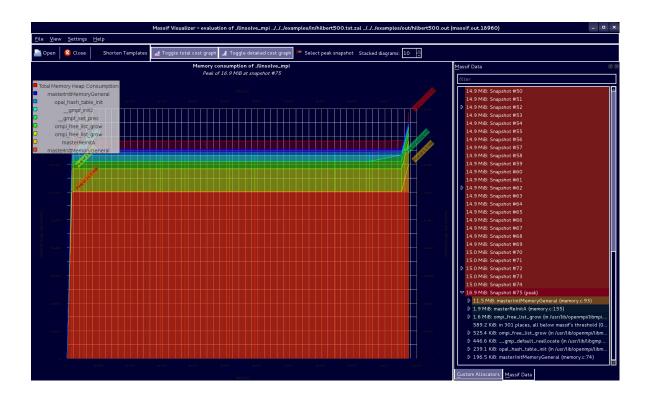

| 4.5 | Memory demands without shared memory<br>( $n = 500$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 |

| 4.6 | Memory demands with shared memory used<br>( $n = 500$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49 |

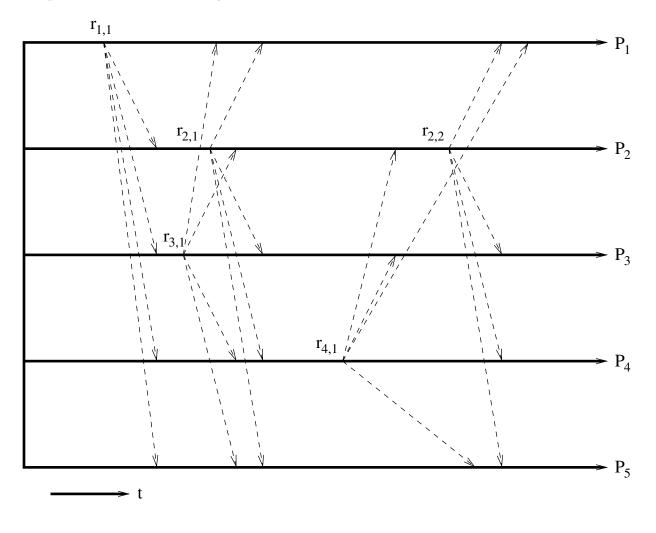

| 5.1 | Example of results ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55 |

| 5.2 | MRC conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61 |

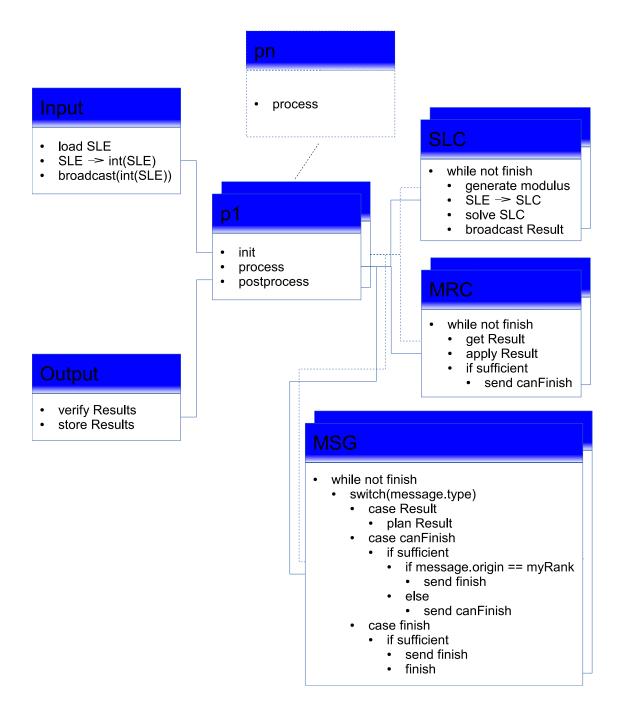

| 5.3 | The process architecture - The system consists of <i>n</i> processes. Only one process performs the input (loading and initial transformation of SLE) and output (verification and storing the results). All the processes includes SLC solver, MRC thread and message processing thread (MSG). The SLC solver performs the solution of single SLCs. The MRC thread performs the mixed radix conversion for the appropriate part of the result vector. The message processing thread handles all the received messages and takes appropriate actions. | 64 |

| 5.4 | An example of the node workload for new architecture $(n = 500, p = 24)$ -                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 01 |

| J.1 | The meaning of colours remains the same as in 3.2. Message processing is marked with green colour. $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                             | 71 |

| 5.5 | An example of the node workload for new architecture ( $n = 500, p = 24$ ) - A detail close to the end. The meaning of colours remains the same as in 5.4. Even in the detailed view the nodes are busy almost all the time | 72 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

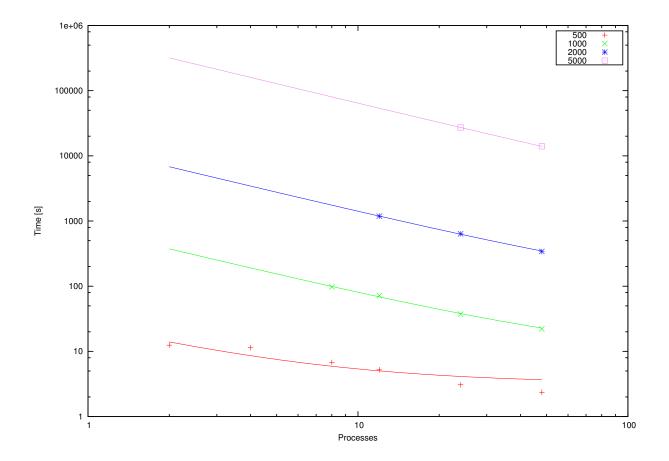

| 5.6 | The linsolve parallel run timings in dependency on process count for different dimensions of SLE                                                                                                                            | 74 |

# List of Tables

| 3.1 | Example transformation (RNS to MR)                                                                                 | 15 |

|-----|--------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Vector multiplication with reduction timings                                                                       | 42 |

| 4.2 | Vector multiplication timings                                                                                      | 44 |

| 4.3 | Gaussian elimination timings                                                                                       | 44 |

| 4.4 | Gaussian elimination timings for sparse matrices                                                                   | 45 |

| 4.5 | Latency FP versus Montgomery domain                                                                                | 46 |

| 5.1 | Moduli of results of example 5.2.1                                                                                 | 56 |

| 5.2 | Results ordering of example $5.2.1$                                                                                | 56 |

| 5.3 | MRC conversion timings                                                                                             | 60 |

| 5.4 | $\operatorname{SLC}$ and result vector sizes and timings for different bandwidth networks $% \operatorname{SLC}$ . | 69 |

| 5.5 | Timings for parallel run SLE solution $T[s]$                                                                       | 73 |

# List of Algorithms

| 1 | Modular multiplication in Montgomery domain         | 38 |

|---|-----------------------------------------------------|----|

| 2 | Problem distribution for shared memory use (master) | 41 |

| 3 | Problem distribution for shared memory use (slave)  | 41 |

| 4 | SLC solver thread                                   | 63 |

| 5 | Mixed Radix Conversion thread                       | 65 |

| 6 | Montgomery reduction                                | 85 |

# 1 Introduction

## 1.1 Motivation

Finding a solution a set of linear equations (SLE) is one of the most common mathematical problems. There are many well known and defined approaches such as various elimination and iteration methods for their solution.

Nevertheless, some SLEs cause considerable problems when one attempts to solve them using the currently easily accessible computational technology. These problems rise from the principle of how numbers are represented in digital devices.

One of the properties of the floating point representation is that it is not able to represent every real number. Moreover, the floating point representation cannot give the full range of rational numbers, but only a small subset of them. Thus, the usage of real numbers and their floating point representation is doubtful and it is complicated to recognize that a loss of accuracy has occurred.

On the other hand, the usage of integer numbers is transparent and computations using integer numbers are easily controlled. Using integer arithmetic is precise and if there is a problem, a flag indicating overflow of the integer range is set.

The most common standard for floating point representation is the IEEE organization standard [18]. When using this standard, the number of bits used for fraction representation is strictly specified. The number of bits is 23 or 52 bits for single or double precision. Knowing these fraction ranges clearly states the rounding errors of computation in such standards.

The range limitations are clear and it is straightforward that it is impossible to break them in hardware. There always has to be a limit in hardware implementation. According to the fraction and exponent limits the range of expressible numbers is given. This range could be extended on software level using a library for multiple precision computing. Such libraries cause a reasonable slowdown of the whole computation. In addition to using these libraries it is still necessary to determine the precision needed for the appropriate problem.

Due to the given problems, it is obvious that floating point arithmetic computations are burdened with plenty of rounding errors. These errors are generated and propagated through the computation, so the result can be frequently inaccurate. Maybe it seems that those rounding errors are not important but clearly they are propagated through the whole computation. Thus the consequent step of the computation does not have the precise input data and so it is not possible to produce the right result. Moreover, each of the consequent computational steps generate their own rounding errors and these are also propagated through the rest of the computation.

Another way of solving the problem of rounding errors and their propagation is to use another mathematical model for finding a solution. Such a model should be a residual number system (RNS). This model provides the possibility of creating arbitrary large computer word, which leads to preserving all the information from the input data, and generates no rounding errors, because the computations are processed in residual arithmetic, where accuracy is guaranteed. There is also a problem of setting the needed precision but for RNS there is a mechanism for its estimation. This estimation is optimal in comparison with some others which are typically very pessimistic. Another advantage of the RNS is the natural degree of parallelism.

## **1.2** Problem statement

Our aim is to design a distributed system for solving SLEs capable of solving sets with dense coefficient matrices of large dimensions. This system is meant to be usable for clusters of workstations as well as for High Performance Computing (HPC) clusters. The solution process itself is to be error free which means no errors during the computation nor rounding errors.

## **1.3** Contributions of the thesis

There are two main contributions expressed in this thesis.

- 1. System optimizations of multiplication with reduction, especially the vector form of this operation. This also includes an overall optimization of the whole Gaussian elimination process. Some minor memory demand improvement.

- 2. The new Mixed Radix Conversion algorithm for distributed environment with possible dynamic weighting and recognition of sufficient precision. This also allows a

completely homogeneous design of application where all the nodes have exactly the same role.

## 1.4 Organization of the thesis

The thesis consists of the seven following chapters.

- 1. *Introduction*: Describes the motivation for our work and our goals. There is also a list of main contributions of the thesis.

- 2. *State-of-the-Art*: This chapter maps the current state-of-the-art in solving general dense SLEs exactly.

- 3. *Our Approach*: Describes the theoretical background of solving a SLE by means of RNS and Gaussian elimination. Presents initial design of the system this thesis is based on. Also presents a complexity analysis of the initial design.

- 4. *System Optimizations*: Describes the system optimizations performed during the development of the new system, especially multiplication with reduction operation.

- 5. *Decentralization*: Presents the design of a new decentralized version of the system including partial results on the design of parallel algorithms, such as mixed radix conversion and prime number generation.

- 6. Conclusions: Summarizes the results of our work and concludes the thesis.

- 7. Future Work: Suggests possible topics for further interests.

# 2 State-of-the-Art

The problem of linear equation systems is common in different fields of science. Thus it is not surprising that there are plenty of publications dealing with it.

Some publications focus on different pivoting strategies for different elimination methods. The choice of the pivoting strategy has a direct impact on the result and its accuracy. This is due to the fact that if the elements in the elimination process are well chosen, then there is no need for such a great precision. Numerous pivoting strategies are described in article [9]. Also, paper [29] introduced a new pivoting strategy for Gaussian elimination. But there is no guarantee for the solution to be exact just for a well chosen pivoting strategy. Nevertheless, none of the pivoting strategies should be marked as best for the general linear equation system.

Another often used technique for an ill-conditioned SLE solution is based on various regularization procedures. This technique tries to find a meaningful approximate solution to the problems with an ill-conditioned coefficient matrix. Paper [28] gives a comprehensive description of various regularization techniques. Other methods dealing with regularization of the matrix are expressed in [3, 4, 31].

Paper [30] describes a package for iterative solving of linear equation-systems which are ill-conditioned and have large dimensions. This package contains various iterative methods of SLE solution.

The basics of the method we use are presented in paper [27]. This article describes a system for solving linear equation systems exactly using the residual number system and it gives emphasis on the hardware implementation of the described algorithms.

The hardware implementation of the algorithms described in [27] is expressed in article [25] where the design of this system is presented.

The system described in this thesis is based on facts published in these articles.

There is also a software implementation of this algorithm. It is introduced in paper [16]. The article describes a software implementation of the procedure that solves SLEs by means of RNS. For this implementation, the FORTRAN language was used. The downside of this implementation is its simplicity. It has no support for parallel processing, therefore, it is not suitable for problems of large dimensions. Paper [17] is just a remark to this algorithm.

Another implementation of similar algorithms is described in papers [5–8], where a parallel

system for SLE solution is proposed using the RNS and distribution of individual Set of Linear Congruencies (SLC) solution to separate processors.

The SLE solution algorithm in [5–8] is basically divided into two parts. The first part of the processing is a simultaneous solution of separate SLCs, whereas the other is the mixed radix conversion algorithm itself. The parallel solution of SLCs is algorithmically almost identical to our approach. There is a difference in the knowledge of moduli count used. Doctor Koç presents algorithms where the count of moduli used is predefined. Our system, on the other hand, does not know the moduli count at the beginning of the computation. This count is determined by particular results of the Mixed Radix Conversion (MRC) algorithm which then has to be performed simultaneously with the SLCs solutions. The count of moduli used strictly corresponds with the accuracy of the computation. The more moduli we use the more accuracy we get. Thus we are determining whether the results have a sufficient accuracy and then the computation is finalized. So the algorithm cannot be strictly divided similarly to [5–8].

Articles [5–8] present different approaches to the parallel solution of the mixed radix conversion algorithm. There are some algorithms based on systolic arrays in [5,8]. And the algorithm suitable for Symmetric multiprocessor architecture with distributed memory are presented in [6,7]. Those parallel algorithms for the MRC are not suitable for usage in our system, due to the presented necessity of the MRC processed simultaneously with SLCs solution. The algorithm used for moduli count control is described in 3.1.5.

Works [A.7] and [10] deal with primary design of the system. These works describe the basic implementation of the system for SLE solution.

# 3 Our Approach

### 3.1 Theory

#### 3.1.1 Outline

The standard approach to solving the SLE in modular arithmetic consists of 4 steps [23,27]. These steps are scaling transformation, SLE reduction into many SLCs, SLCs solving process, and finally a backward transformation.

- 1. Scaling transformation. This transformation takes the input SLE and performs scaling of its matrix and right-hand side (RHS) by a constant. The scaling procedure is necessary to ensure that the input SLE is representable within an integer set. Scaling can be performed for each row of the input matrix independently or globally for the entire SLE.

- SLE reduction into SLCs. A number of prime number moduli q is chosen and modular reduction is performed for the entire SLE producing as many SLCs as the number of moduli. A proper choice of moduli is important as modular reduction will often be needed.

- 3. *Solving SLCs.* SLCs obtained from the previous step are solved in this step. As they have nothing in common, they can be solved independently.

- 4. *Backward transformation*. After we have solved SLCs, we obtain up to so many partial solutions that we recombine back into the floating point set yielding an SLE solution. This is done with a backward transformation using a mixed radix conversion (MRC) [12, 14, 27].

#### 3.1.2 Transformation to integer numbers

Let us presume that in this section the number called the smallest element means the number with the smallest absolute value. To correspond with this, the function *min* also returns the number with the smallest absolute value.

The whole computation is implemented in residual arithmetic, so the first step is transformation into  $\mathcal{Z}$ . The early implementation used for such a transformation formulae 3.1.

$$a_{ij} = \frac{2^{m+1}}{\min(a_{i1}, a_{i2}, \dots, a_{in}, y_i)} a_{ij} \qquad 1 \le i, j \le n \qquad (3.1a)$$

$$y_i = \frac{2^{m+1}}{\min(a_{i1}, a_{i2}, \dots, a_{in}, y_i)} y_i \qquad 1 \le i \le n \qquad (3.1b)$$

The first formula in 3.1a fits for elements of coefficient matrix **A**. The other 3.1b fits for right-hand side vector **y**. The identifier m represents the mantissa size,  $a_{ij}$  represents the elements of the coefficients matrix and  $y_i$  represents the RHS vector elements.

The terms 3.1 should be described in a few sentences. Each row is adjusted separately, so the smallest element of the whole row (including the appropriate element of the right-hand side vector) has to be found. Then the whole row is divided by that element. After the division, the smallest element of the row has the value of 1. Finally, all the elements of the row are shifted to the left by the size of fraction (m) bits. Now all the elements are integer numbers.

During the experiments we discovered a problem with this part of computation. The division operation is a generator of certain numerical errors that are propagated down the whole computation. Consequently, results are obtained for a different set of linear equations.

This problem is easily solved by using the shift operation instead of a division operation. Numbers are not divided by the smallest element but they are shifted to the right by the number corresponding to the exponent of the smallest element. After this operation the value of the smallest element is in the range (1, 2) and all the other elements in the row are greater than 1. Then these numbers are shifted to the left just in the same way as they were in 3.1. The final formulae are presented in form 3.2.

$$min_i = min_{0 \le k \le n}(a_{ik}, y_i) \tag{3.2a}$$

$$a_{ij} = \frac{2^{m+1}}{2^{exp(min_i)}} a_{ij} \qquad 1 \le i, j \le n \qquad (3.2b)$$

$$y_i = \frac{2^{m+1}}{2^{exp(min_i)}} y_i \qquad 1 \le i \le n, \qquad (3.2c)$$

In formulae 3.2 the identifier exp(x) represents the exponent of the x value. The  $min_i$

represents the element with the smallest absolute value in the i-th row. When using formulae 3.2 for the transformation into integer numbers, numerical errors caused by the division operation are avoided.

Using formulae 3.2 for the transformation into integer numbers causes a limitation of the available input range. If there is a need to use the whole original input range, then the range used for the transformation has to have different parameters. The following paragraphs discuss the required ranges.

We should express the relationship for the input range. Let the desired input range has m bits of mantissa, the least acceptable exponent is  $e_{min}$  and the largest exponent is  $e_{max}$ . Then it is necessary to find out the parameters of the range needed for the transformation which are marked as  $m_1$ ,  $e_{min1}$ ,  $e_{max1}$ . These parameters should be set to allow the transformation of every representable number of the original input range.

$$e_{max1} = e_{max} - e_{min} + m \tag{3.3a}$$

$$e_{min1} = \min(0, e_{min}) \tag{3.3b}$$

$$m_1 = m \tag{3.3c}$$

The relation of the original input range parameters and the parameters of the range needed for an errorless conversion is gathered in formulae 3.3. The relevance of 3.3c is straightforward because during the conversion there are no other operations but a shift operation and there is no need for fraction enlargement.

Formula 3.3b states the relation of the least exponent of the original and the new ranges. The least exponent from the new range is set to minimum of 0 and the original  $e_{min}$ . This fact rises from the shifting process where numbers are shifted, so they have the exponent equal to 0 and then they are shifted to the left by the size of the fraction.

Finally the greatest exponent which can arise from formulae 3.2 has the value according to 3.3a. This is the case when one row contains both: the element with the smallest possible exponent  $e_{min}$  and the greatest one  $e_{max}$ .

#### **3.1.3** Transformation into $\mathcal{Z}_n$

This transformation is performed by **fmod** function, which returns the remainder after division, in floating point representation. This function and its characteristics are described in 3.2.2

#### 3.1.4 Gaussian elimination with non-zero pivoting

Gaussian elimination algorithm is commonly used and well understood, so it is described only very briefly. In addition, it is supplied with non-zero pivoting. At the beginning, the form of the expanded coefficient matrix corresponds to formula 3.4.

$$(\mathbf{A}|\mathbf{y}) = \begin{pmatrix} a_{11} & a_{12} & a_{13} & \dots & a_{1n} & y_1 \\ a_{21} & a_{22} & a_{23} & \dots & a_{2n} & y_2 \\ a_{31} & a_{32} & a_{33} & \dots & a_{3n} & y_3 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ a_{n1} & a_{n2} & a_{n3} & \dots & a_{nn} & y_n \end{pmatrix}$$

(3.4)

The Gaussian elimination is split into two phases. The first one is modification to eliminate some variables in the right equations. More accurately, the first phase consists of transformation of the matrix 3.4 into upper triangular matrix expressed in formula 3.5.

$$\begin{pmatrix} a_{11} & a_{12} & a_{13} & \dots & a_{1n} & y_1 \\ 0 & a_{22}^{(1)} & a_{23}^{(1)} & \dots & a_{2n}^{(1)} & y_2^{(1)} \\ 0 & 0 & a_{33}^{(2)} & \dots & a_{3n}^{(2)} & y_3^{(2)} \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \dots & a_{nn}^{(n-1)} & y_n^{(n-1)} \end{pmatrix}$$

(3.5)

The algorithm can be written in a symbolic way by formulae 3.6 and 3.7.

$$a_{ij}^{(0)} = a_{ij}$$

$i = 1, \dots, n$   $j = 1, \dots, n+1$  (3.6)

$$a_{ij}^{(k)} = a_{ij}^{(k-1)} - \frac{a_{ik}^{(k-1)}}{a_{kk}^{(k-1)}} a_{kj}^{(k-1)} \quad k = 1, \dots, n-1 \quad i = k+1, \dots, n \quad j = k+1, \dots, n+1$$

$$(3.7)$$

Adjusting the expanded coefficient matrix may result into the element  $a_{k+1k+1}^{(k)}$  in the kth step of the elimination being equal to zero. And such an element should not be used for the k + 1-st step of elimination, so it is necessary to modify the matrix. One and the easiest way is non-zero pivoting from [25] where such an element is exchanged with another non-zero element of the matrix. More precisely, row k is swapped with row l where  $l > k \land a_{lk} \neq 0$  holds. This row swapping implies the change of the determinant sign which is also calculated during the first phase.

Some other pivoting strategies are mentioned in [9] and [29].

Determinant is then the result of the product of elements on the main diagonal. Finally, its sign is set according to the number of row swaps during the elimination. Formula 3.8 expresses the determinant value. Identifier l is the number of row swaps.

$$D = \prod_{i=1}^{\dim} a_{ii}^{(i-1)} \cdot (-1)^l \tag{3.8}$$

The second phase of the algorithm just calculates the variables. The value of the variable corresponding to the last column of the expanded coefficient matrix is determined directly by the last row of 3.5. This value is used to gain the value of the variable corresponding to the last but one column. And so the process continues until having values of all variables.

#### 3.1.5 RNS and mixed radix representation

The transformation from the RNS back into the integer numbers can be solved by Chinese remainder theorem (CRT). Instead of this classical way, the system uses another method which is based on the relation between RNS representation and mixed radix representation. The reason for the usage of another algorithm is the complexity of the CRT transformation. The following description of the conversion process was taken from [22]. The extension for signed numbers is formed in [27].

We have an n-tuple  $\rho = [r_1, r_2, \ldots, r_n]$ , where the components are *radices*. Let R is a

product of these radices so  $R = \prod_{i=1}^{n} r_i$  holds.

It is straightforward that every number s from the range  $0 \le s < R$  can be expressed in the form corresponding to formula 3.9.

$$s = d_0 + d_1(r_1) + d_2(r_1r_2) + \ldots + d_{n-1}(r_1r_2\ldots r_{n-1})$$

(3.9)

Identifiers  $d_0, d_1, \ldots, d_{n-1}$  in equation 3.9 are standard mixed radix digits which have to conform to relation 3.10.

$$0 \le d_i < r_{i+1} \quad i = 0, 1, \dots, n-1.$$

(3.10)

The mixed radix representation are numbers  $d_0, d_1, \ldots, d_{n-1}$  which can be written down in form 3.11.

$$\langle s \rangle_{\rho} = \langle d_0, d_1, \dots, d_{n-1} \rangle \tag{3.11}$$

The special case of the mixed radix representation is a fixed radix representation with all radices having the same value  $(r_1 = r_2 = \cdots = r_n)$ . For example, when having all radices  $r_i = 10$  then, such a representation is the common decimal number system. But a more interesting and relevant case is when radices are equal to moduli of RNS, thus  $r_i = m_i$  for  $i = 1, 2, \ldots, n$ . Then the range of the multi-modulus residual arithmetic and mixed radix representation are equal.

It is necessary to find the relations for the integer number s and its representations in residual number system  $|s|_{\beta}$  and mixed radix representation  $\langle s \rangle_{\beta}$  now.

The representation  $|s|_{\beta}$  in the RNS and its relation to the number s is described in section 3.1.2.

If the number s is known, the process to determine the mixed radix representation  $\langle s \rangle_{\beta}$  follows. Let  $s = t_1$  and the relation for  $d_0$  is expressed in formula 3.12.

$$t_{1} = s$$

=  $d_{0} + m_{1} [d_{1} + d_{2}(m_{2}) + \ldots + d_{n-1}(m_{2} \ldots m_{n-1})]$  (3.12)

=  $d_{0} + m_{1}t_{2}$

The relation 3.13 can be written down as

$$\begin{aligned} |t_1|_{m_1} &= |d_0 + m_1 t_2|_{m_1} \\ &= d_0 \\ &= |s|_{m_1}. \end{aligned}$$

(3.13)

From the relations 3.13 and 3.12 it should be clear that there is no need to perform any processing to determine the value of  $d_0$  because it is equal to the first residue in RNS representation. Then the relations for  $t_2$  and  $d_1$  are expressed in formulae 3.14 and 3.15.

$$t_2 = d_1 + m_2 [d_2 + d_3(m_3) + \ldots + d_{n-1}(m_3 \ldots m_{n-1})] = d_1 + m_2 t_3.$$

(3.14)

$$\begin{aligned} |t_2|_{m_2} &= |d_1 + m_2 t_3|_{m_2} \\ &= d_1 \end{aligned}$$

(3.15)

It is easy to extract the recursive form for  $d_i$  elements of the mixed radix representation from formulae 3.12, 3.13, 3.14 and 3.15. The initial value is  $t_1 = s$ . This recursive formula is expressed in 3.16.

$$d_{0} = |t_{1}|_{m_{1}}$$

$$t_{1} = s$$

$$t_{i+1} = \frac{t_{i} - d_{i-1}}{m_{i}}$$

$$d_{i} = |t_{i+1}|_{m_{i+1}}$$

$$i = 1, 2, \dots, n-1.$$

(3.16)

Those relations are only prerequisites for conversion from residual representation to mixed radix representation. This process is based on recursive formula 3.16 for  $t_{i+1}$ . If the residual representation is known, the following relations hold:

$$|t_1|_{\beta} = [d_0, |t_1|_{m_2}, \dots, |t_1|_{m_n}]$$

#### SECTION 3. OUR APPROACH

$$|d_0|_{\beta} = [|d_0|_{m_1}, |d_0|_{m_2}, \dots, |d_0|_{m_n}].$$

Combining these two relations, we get the following notation:

$$|t_1 - d_0|_{\beta} = \left[0, \left|z_2^{(1)}\right|_{m_2}, \left|z_3^{(1)}\right|_{m_3}, \dots, \left|z_n^{(1)}\right|_{m_n}\right],$$

where

$$z_i^{(1)} = |t_1|_{m_i} - |d_0|_{m_i}$$

$i = 2, 3, \dots, n_i$

Now we can establish the reduced base vector  $\beta_1$ .

$$\beta_1 = [m_2, m_3, \ldots, m_n].$$

And the value of  $t_1 - d_0$  with base vector  $\beta_1$  is

$$|t_1 - d_0|_{\beta_1} = \left[ \left| z_2^{(1)} \right|_{m_2}, \left| z_3^{(1)} \right|_{m_3}, \dots \left| z_n^{(1)} \right|_{m_n} \right].$$

In order to be able to compute the value of  $t_2$ , a multiplicative inverse  $m_1^{-1}(\beta_1)$  has to exist and has to be known. Those inverses exist because all the elements of  $\beta_1$  are prime numbers. And the condition for existence of multiplicative inversion  $|x^{-1}|_m$  of x is that x and m are relatively prime. Then the inversions can be expressed as:

$$m_1^{-1}(\beta_1) = \left[m_1^{-1}(m_2), m_1^{-1}(m_3), \dots, m_1^{-1}(m_n)\right].$$

Then the  $t_2$  can be expressed in the form:

$$|t_{2}|_{\beta_{1}} = \left| \frac{t_{1} - d_{0}}{m_{1}} \right|_{\beta_{1}} \\ = \left[ \left| w_{2}^{(1)} \right|_{m_{2}}, \left| w_{3}^{(1)} \right|_{m_{3}}, \dots, \left| w_{n}^{(1)} \right|_{m_{n}} \right], \qquad (3.17)$$

where

$$w_i^{(1)} = \left| z_i^{(1)} \right|_{m_i} m_1^{-1}(m_i) \quad i = 2, 3, \dots, n.$$

When using formula 3.16, we get the second element of the mixed radix representation  $d_1$ .

$$\left| w_2^{(1)} \right|_{m_2} = |t_2|_{m_2} = d_1$$

We can use it in equation 3.17 and then we can write:

$$|t_2|_{\beta_1} = [d_1, |t_2|_{m_3}, \dots, |t_2|_{m_n}]$$

(3.18)

$$|d_1|_{\beta_1} = [|d_1|_{m_2}, |d_1|_{m_3}, \dots, |d_1|_{m_n}].$$

(3.19)

These relations are similar to relations for  $d_1$ . Repeating the process for the rest, we will get  $d_2, d_3, \ldots, d_{n-1}$ .

This algorithm can be easily written in a table where the principle can be understood much more easily. Table 3.1 shows the steps of the algorithm, for example, where  $\beta = [13, 11, 7, 5, 17]$  and  $|s|_{\beta} = [4, 2, 4, 2, 5]$ . The elements of mixed radix representation corresponding with relation 3.16 are marked out in **bold**.

The above algorithm has to be extended for signed numbers because when used in this fashion, it works only with positive numbers. The extension is based on double conversion, one for the number (residue) itself and the other for its negative value. There, the negative value means the number (residue) subtracted from the corresponding modulus  $m_i$ . Afterwards it is necessary to determine which of the two results will be used. If the positive result is less than M/2, then it is the actual final value, otherwise, if the result gained with negative partial results fulfills the condition of being less than M/2, then the negative value of this result is the final value.

Finally, all the elements of the result vector are divided by the determinant to obtain rational number results according to section 3.1.4.

The transformation algorithm is very important for the termination of the whole computation. The process terminates when elements of the mixed radix representation marked in table 3.1 are zero for all the elements of the result vector. This condition has to be fulfilled for at least one of the representations (positive/negative). When it is satisfied, there is no need to extend the range and this means that no other SLCs have to be solved.

This method of process termination does not guarantee the achievement of a sufficient range (M) to solve the SLE exactly without any rounding errors. But the probability of

| β                                                     | $m_1 = 13$ | $m_2 = 11$ | $m_3 = 7$ | $m_4 = 5$ | $m_5 = 17$ | op. |

|-------------------------------------------------------|------------|------------|-----------|-----------|------------|-----|

| $ t_1 _{\beta}$                                       | 4          | 2          | 4         | 2         | 5          |     |

| $ d_0 _{eta}$                                         | 4          | 4          | 4         | 4         | 4          | —   |

| $ t_1 - d_0 _{\beta}$                                 | 0          | 9          | 0         | 3         | 1          |     |

| $m_1^{-1}(\beta_1)$                                   |            | 6          | 6         | 2         | 4          | •   |

| $ t_2 _{\beta_1} =  \frac{t_1 - d_0}{m_1} _{\beta_1}$ |            | 10         | 0         | 1         | 4          |     |

| $ d_1 _{\beta_1}$                                     |            | 10         | 3         | 0         | 10         | —   |

| $ t_2 - d_1 _{\beta_1}$                               |            | 0          | 4         | 1         | 11         |     |

| $m_2^{-1}(\beta_2)$                                   |            |            | 2         | 1         | 14         | •   |

| $ t_3 _{\beta_2} =  \frac{t_2 - d_1}{m_2} _{\beta_2}$ |            |            | 1         | 1         | 1          |     |

| $ d_2 _{\beta_2}$                                     |            |            | 1         | 1         | 1          | —   |

| $ t_3 - d_2 _{\beta_2}$                               |            |            | 0         | 0         | 0          |     |

| $m_3^{-1}(\beta_3)$                                   |            |            |           | 3         | 5          | •   |

| $ t_4 _{\beta_3} =  \frac{t_3 - d_2}{m_3} _{\beta_3}$ |            |            |           | 0         | 0          |     |

| $ d_3 _{\beta_3}$                                     |            |            |           | 0         | 0          | —   |

| $ t_4 - d_3 _{\beta_3}$                               |            |            |           | 0         | 0          |     |

| $m_4^{-1}(\beta_4)$                                   |            |            |           |           | 7          | •   |

| $ t_5 _{\beta_4} =  \frac{t_4 - d_3}{m_4} _{\beta_4}$ |            |            |           |           | 0          |     |

Table 3.1: Example transformation (RNS to MR)  $\,$

an insufficient range is very small. The mechanism for computation finishing is described in [24].

# 3.2 Implementation

## 3.2.1 Transformation into integer number space $\mathcal{Z}$

Implementation of the transformation of input data set into an integer number range is just a simple coding of process described in 3.1.2. No notable problems in this field exist.

## **3.2.2** Transformation into $\mathcal{Z}_n$

To gain the remainder after division the **fmod** function from standard C library is used.

During our development and testing we have used the GNU C compiler and the GNU C library as well.

When using the GNU C library implementation this function should be errorfree for the following architectures, according to the GNU C library manual [21]:

- Alpha

- intel x86 architecture including x86\_64 architecture.

- IA64 (Itanium)

- Sparc in both 32 bit and 64 bit variants

- PowerPC

- S/390

But in the GNU C compiler, this function is also built-in and thus the compiler is free to use its own implementation under certain conditions. In case of problems the built-in function implementation can be suppressed.

Finally, this function will be translated into the **fprem** instruction [19] for x86 architecture processors.

#### 3.2.3 Set of linear congruencies

To solve one set of linear congruencies with modulus m a common Gaussian elimination in residual arithmetic is used. This means that we have to take care of the magnitude of every result of every operation and perform modular reduction if necessary.

#### 3.2.4 The calculation of Final results

Final results are gained from the vector of values calculated according to the algorithm expressed in section 3.1.5 using formula 3.9. There is a need to use a multiple precision floating point library. The implementation strictly follows formula 3.9. At the beginning of computation we predict some degree of precision which is used for this computation. Whenever the results are in the range where some precision could be lost, the range used for this computation is extended accordingly. We can state that for every modulus used there is a need to represent all the possible values with full precision (without any loss). Thus when using, for example, ten modules of 31-bit size, it is necessary to use the range with 310 bits of mantissa, because the product of ten 31-bit numbers can be the number with a 310-bit representation.

This form of processing guarantees that full precision of the result is preserved.

Certainly the final result is not expressed with such a precision. There is a default value for mantissa size of the output vector. This default value can be overridden with a concrete desired precision.

#### 3.2.5 Final result verification

Due to the fact that the completion of the computation is done basically on probability principles, it is necessary to verify the accuracy of the results. Thus, we perform the test whether the left-hand side (LHS), applying the results, is equal to the RHS in every linear equation. The verification process can be described as formulae 3.20.

$$\delta \mathbf{x} = \frac{A\mathbf{x} - \mathbf{y}}{\mathbf{y}}$$

$$\forall i, 0 \le i < dim \quad \delta \mathbf{x}_i < t$$

(3.20)

The tolerance t in formulae 3.20 is implicitly set to  $10^{-6}$  and it can be easily changed.

#### 3.2.6 System Architecture

The application which processes the SLE solution is the core of the whole system. Since its early implementation it has been designed as a parallel application because of its time complexity. The complexity is high because there is a lot of SLCs for every task to solve. This application is designed for parallel clusters using MPI (Message Passing Interface) communication protocol. For more information on MPI see MPI homepage<sup>1</sup>.

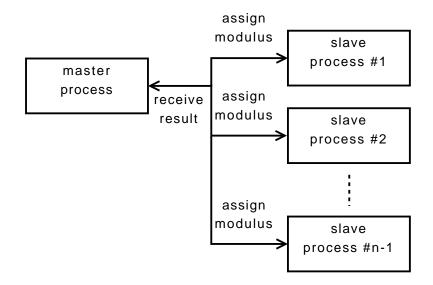

The application itself is divided into two parts. The first can be described as a **master** process and the other one as a **slave** process. The relationship between these two kinds of processes is demonstrated in figure 3.1.

The computation can be described as a sequence of three phases. The next paragraph describes each phase solely in view of **master/slave** process partitioning.

- 1. This phase should be called **Initialization**. The **master** process allocates the memory needed. Then it reads the input data from the disk and performs the basic conversion of the problem to integer numbers according to section 3.1.2. The **slave** process just allocates memory locations needed.

- 2. The next phase is the most time consuming part of the computation. Master process assigna moduli to slave processes (*assign modulus* in figure 3.1) and processes results received from slave processes. The way of processing the result is theoretically discussed in section 3.1.5, which also includes sufficient precision resolving. Slave processes are responsible for receiving moduli, processing the Gaussian elimination in residual arithmetic with all the received moduli (3.1.4), and providing SLC solutions back to the master process.

- 3. In the last phase, only administrative tasks are performed. **Master** process sends a *stop* message to **slave** processes and stores the final results. All processes clean up their environment.

# 3.3 Complexity

This section concentrates on the complexity of the whole system from different points of view. It is divided into three subsections according to the complexity type. The first section

<sup>&</sup>lt;sup>1</sup>http://www-unix.mcs.anl.gov/mpi/

Figure 3.1: Linsolve architecture

3.3.1 deals with the asymptotic time complexity of every single part of the algorithm. The second subsection 3.3.2 is focused on memory consumption and its effects. The last 3.3.3 expresses the communication complexities.

The parameters of the relations vary. Some of them are clearly understood and stated like the number of cluster nodes p and the dimension of the SLE n. However, the parameter number of moduli used for computation is not so clear and its value is not known. The only way to find its value is to perform the computation.

The count of moduli used should theoretically correspond to the range required to solve the problem, but in practice it is not easy to determine this value.

#### 3.3.1 Time complexity

This section is divided according to the division of the algorithm in section 3.1. It should be remembered that sections 3.3.1.1 and 3.3.1.3, corresponding to sections 3.1.2 and 3.1.5, are performed by the master process (on the main node). Section 3.3.1.2 states the complexity of SLC solution which is handled in slave processes. The difficulty of the whole algorithm is summarized in section 3.3.1.4.

The formulae presented through sections 3.3.1.1 to 3.3.1.3 were taken from [10]. The final complexity of the whole computation stated in 3.3.1.4 can be derived from those relations

and the knowledge of the systems behaviour.

#### 3.3.1.1 Transformation to integer numbers

Transformation to the integer number range is completely determined by the dimension of the problem. The transformation of one value in agreement with the formula 3.2 takes constant amount of time. The time complexity of such a transformation is as follows.

$$t_{toint} = \mathcal{O}(n^2) \tag{3.21}$$

#### 3.3.1.2 SLC

Asymptotic complexity of computation of one set of linear congruencies is given by the complexity of the Gaussian elimination. This algorithm is well known and its complexity is  $t_{SLC} = \mathcal{O}(n^3)$ .

Furthermore, the Gaussian elimination algorithm is performed for every modulus. The asymptotic complexity for the process of all the eliminations is expressed by formula 3.22.

$$\mathcal{O}(m \cdot n^3) \tag{3.22}$$

In addition, the time needed for the transformation from integer numbers into residue arithmetic should be taken into account. But this conversion has the same asymptotic complexity as the transformation into integer numbers expressed in form 3.21, so it does not affect the relation 3.22.

#### 3.3.1.3 Transformation to real numbers

Time complexity of the transformation from RNS into rational numbers depends on the number of moduli used for the computation. This complexity should be expressed by relation 3.23.

$$\mathcal{O}(m^2 n) \tag{3.23}$$

Relation 3.23 arose from a detailed analysis of the algorithm described in section 3.1.5. When studying table 3.1, we can say that for the transformation of one number it is necessary to perform  $m^2$  computational steps. It is obvious that for the conversion of the whole result vector of dimension n the complexity corresponds to formula 3.23.

In fact, 2n+2 conversions are performed because of an independent transformation of positive and negative representations and the determinant. Asymptotically, the final relation is truly formula 3.23.

#### 3.3.1.4 Overall complexity

When combining the complexity of the whole computation, all the parameters have to be taken into account. The final complexity of the whole system is not just a trivial combination of the relations expressed in sections 3.3.1.1 to 3.3.1.3. Actually, the final complexity should be written in form 3.24.

$$\mathcal{O}(n^2 + max(m^2n, m \cdot n^3 \cdot (p-1)^{-1}))$$

(3.24)

The first element  $(n^2)$  of 3.24 represents conversion into integer numbers. The second element of the addition in 3.24 represents the maximum of the time needed for the transformation from the RNS into rational numbers and the SLCs solution itself. The time for SLCs processing is divided by the number of available processors.

We suppose the same hardware configuration for all the nodes used for the computation. If this condition is not fulfilled, then it is impossible to estimate the complexity of the whole computation and the validity of formula 3.24 would be doubtful.

The second part of relation 3.24 shall be described in more details. The meaning of this term is straightforward. When the transformation from the RNS into rational numbers becomes more complicated than the SLCs solution itself, the master process will turn into a bottleneck of the computation. This is due to the fact that the master process will be overloaded and the assignment of the moduli for the slave processes will fail. So, the computational capacity of the slave nodes will not be fully utilized. In this case, the slave nodes will be idle and will wait for the modulus to start the elimination.

This problem would arise in two ways. In the first instance the problem requires too many moduli and in the other where there are too many nodes available. To preserve this situation, condition 3.25 must be fulfilled.

$$t_{SLC} > (p-1) \cdot t_{bt} \tag{3.25}$$

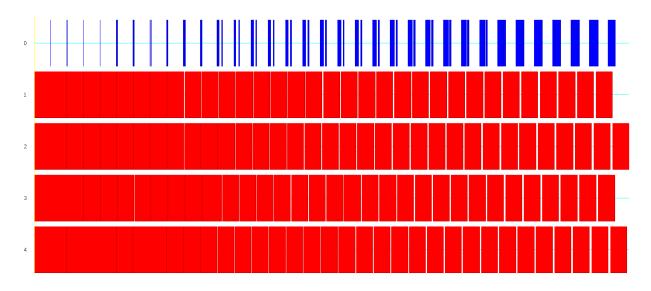

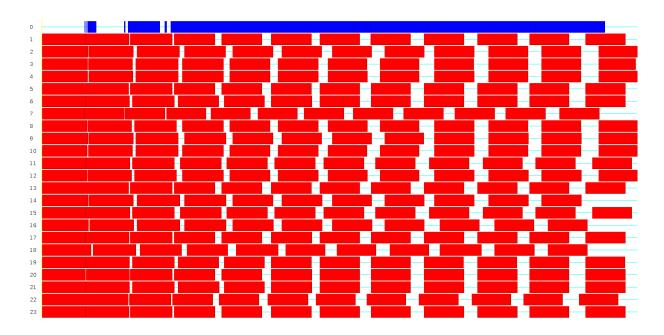

Figure 3.2 shows the work-flow of the computation for fulfilled relation 3.25. Figure 3.3 brings up an other situation, when relation 3.25 does not hold. Figure 3.2 shows that the slave processes (red colour) are fully utilized when the workload of the master process (blue colour) is low and it is free to assign moduli to them. In figure 3.3 we can observe gaps in slave processes utilization at the end of the computation, when, on the other hand, the master process has a igh workload due to MRC computation.

Figure 3.2: An example of the Node workload (n = 500, p = 5) - The graph of different processes utilization. The blue colour represents the master process and the red colour represents slave processes. The master process is idle almost all the time, while the slave processes are busy.

When adjusting relation 3.25 we get a relation for the number of processors, the dimension of the problem and the number of moduli used. This relation is expressed in equation 3.26.

$$p < \frac{t_{SLC}}{t_{bt}} + 1 = \frac{\mathcal{O}(n^3)}{\mathcal{O}(m \cdot n)} = \mathcal{O}\left(\frac{n^2}{m}\right)$$

(3.26)

Formula 3.26 says that the number of processors can grow as fast as dimension square but, on the other hand, with the growing number of used moduli the count of effectively spent

Figure 3.3: An example of the Node workload (n = 500, p = 24) where starvation is obvious - The meaning of colours remains the same as in 3.2. Master process is busy at later stage of computation and the slave processes starve (the gaps in red bars).

processors decreases.

## 3.3.2 Memory consumption

This section deals with memory consumption of the system. The relations do not cover the entire memory which the system uses. It is just the memory complexity of the algorithm. Furthermore, the system uses some temporary variables and buffers for different purposes. These memory areas are neglected due to their relatively small sizes.

A very simple description of the memory complexity is given in [10]. This section provides a more detailed analysis of memory consumption.

The section is divided in the same way as section 3.3.1. Sections 3.3.2.1 and 3.3.2.3 correspond to the computations performed by the master process and section 3.3.2.2 focuses on the memory consumption of the part processed by slave processes.

Although it is not highly important to state the overall memory consumption because we assume that every process is executed on a single node of the cluster, it is presented in section 3.3.2.4.

#### 3.3.2.1 Transformation to integer numbers

Memory consumption of the part of the algorithm performing the conversion of input data into integer numbers is determined by the size of the input data. So, the memory consumption should be expressed by relation  $\mathcal{O}(n^2)$ . The statements in section 3.1.2 imply usage of a 80-bit floating point data type because it is necessary to extend the range in comparison with the range of input data. We suppose input data in the range of double precision floating point values defined by literature [18], which means 64 bits in size. The use of the 80-bit floating point data type finally occupies 96 or 128 bits of memory space. It depends on the compiler and hardware architecture. We are working on x86 architecture and using mostly the GNU C compiler where the long double data type has the size of 128 bits.

The final size of memory space needed is expressed by formula 3.27 in bytes. The memory consumed by the input data has to be taken into account too.

$$m_{toint} = \frac{128 + 64}{8} \cdot n^2 = 24 \cdot n^2 \tag{3.27}$$

#### 3.3.2.2 SLC

Memory claims of the Gaussian elimination are also well known as  $\mathcal{O}(n^2)$ . Unfortunately, it is necessary to guarantee that the needed data will be placed in the physical memory. If this demand is not fulfilled, then the whole will slow down because some parts of the data have to be swapped out of the memory.

Thus, memory consumption has to be expressed more exactly. For the Gaussian elimination itself, 32-bits integer numbers are used. Nevertheless, we need to remember the input data in the form of integer numbers. Those are stored in the variables of the floating point type with 80 bits range. Then the size of memory the SLC solution needs is given by relation 3.28.

$$m_{slc} = \frac{128 + 32}{8} \cdot n \cdot (n+1) = 20 \cdot n \cdot (n+1)$$

(3.28)

When formula 3.28 is adjusted to the form of formula 3.29 it is possible to give an approximate limit to the dimension of the input problem, that can be processed without any complications. This limit is just a guess because of the system memory requirements,