# A NEW STRUCTURAL RECONFIGURATION FOR MULTILEVEL INVERTERS WITH FAULT TOLERANCE CAPABILITY

Meftah Lakhdari<sup>a,\*</sup>, Boualaga Rabhi<sup>a,b</sup>, Amar Benaissa<sup>c</sup>

ABSTRACT. Keeping electrical systems running is critical in industries especially in those that rely on static converters, for example in the case of inverters, continuous and safe of operation must be ensured even if one of the inverter's static switch modules fails. This paper presents a method for fault detection in static converters. The study presents a 3-phase 3-level NPC (Neutral Point Clamped) inverter with IGBTs as static switches where open-circuit or closed-circuit faults are considered. In addition, leg failure and structural reconfiguration are also considered in this fault-tolerant inverter by adding a fourth 3-level leg.

KEYWORDS: Multilevel NPC inverters, IGBT, fault detection, fault isolation, structural reconfiguration, fault tolerant.

### 1. Introduction

Multi-level power converters that efficiently convert electrical energy from one form to another play a very important role in various applications [1–5]. They have been used for several years in high voltage, high power applications [6] and have been successfully applied in medium-voltage, high power electric drives, such as fans, pumps, mines, and electric tractions [7, 8]. Amongst these multilevel converters are those with neutral point clamps (NPC), flying capacitors (FC), and cascaded H-bridges (CHB) [9].

The main advantages of multilevel inverters are a limited voltage transients, low harmonic distortion at the output voltage and current, and high efficiency over the power operating range [10–12]. However, since this type of converters have a large number of switching devices that increases the probability of failure which decreases their reliability, any device failure can cause electrical drives to function abnormally, requiring shutdown of the inverter and the entire production-line system to prevent further serious damages [13–15]. However, when inverters are used in safety-critical or high-reliability applications, they must operate permanently, even in the event of failure [16]. According to a recent industry research on power converters, semiconductor devices are the most sensitive components [17, 18]. Together, these failures account for 21 % of system failures during conversion [19], there are various types of faults that can occur in inverter system, such as DC-link short circuit to ground, DC-link capacitor-bank short circuit, short-circuit damage of the switch, and open-circuit damage of switch [16].

To ensure a continuous safe and fault-tolerant operation of electrical systems after the failure of the inverter, fault-tolerant characteristics must be taken into account during the design phase [20, 21], that is to say, an overall fault tolerance of the power converter must take into account the technological aspects when it comes to the electrical isolation of the power supply switch faulty and reconfiguration of the system after the failure [22]. Moreover, fault tolerance has become of great importance in several applications. For example, wind turbines should not stop in case of failure because their maintenance can be difficult and expensive, however stopping a large-scale energy production can cause serious problems of grid stability and lead to a risk of black-out [11, 22].

This paper focuses on a three-phase three-level NPC inverter provided with a fourth spare fault-tolerant leg. In can detect a power switch fault, either an open circuit or short circuit, using sensors of voltage and an algorithm for the detection of faults. The proposed scheme uses a pair of fuses, additional semiconductor components and 2 auxiliary contacts to isolate the faulty leg and reconfigure the inverter to recover into a safe post-fault operation. To investigate the system performance, simulations are performed for switch failures without and with fault tolerance possibilities.

# 2. Fault detection at three-level NPC inverters

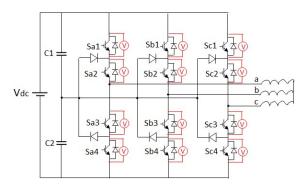

A diagnosing method for switch failures will be develop based on the analysis of electrical quantities with voltage characteristics. This method requires 12 voltage sensors to have measured the 12 voltages of the 12 switches  $(S_{xi}, \text{ with } x = \{a, b, c\}, i = \{1, 2, 3, 4\})$ , denoted  $V_{sxi}$  (Figure 1). The latter allows us to detect the fault of a switch regardless of it being an open circuit or short circuit (OC, or SC), knowing that  $V_{dc}$

$<sup>^</sup>a$  University of Biskra, Electrical Engineering Department, BP 145 RP, 07000 Biskra, Algeria

<sup>&</sup>lt;sup>b</sup> University of Biskra, LMSE Laboratory, BP 145 RP, 07000 Biskra, Algeria

<sup>&</sup>lt;sup>c</sup> University of Djelfa, LAADI Laboratory, PB 3117, 17000 Djelfa, Algeria

<sup>\*</sup> corresponding author: fatthi1@hotmail.fr

FIGURE 1. Three-phase 3-level NPC inverter with 12 voltage sensors for fault detection.

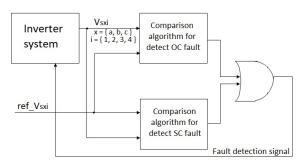

FIGURE 2. Fault detection.

is a voltage source of a direct current ( $V_{dc} = 400 \,\mathrm{V}$ ), C1, C2 are DC capacitors.

To perform this fault detection, it is necessary to implement an algorithm that can compare the measured voltages of the switches to their reference voltages, established from the control orders of the three-level NPC inverter (Figure 2).

### 2.1. ALGORITHM FOR DETECTING A SWITCH OC FAULT

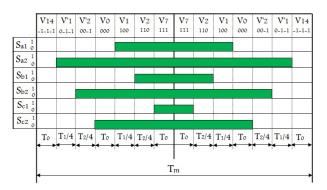

The conduction times of the switches in Sector 1 are shown in Figure 3.

We take, for example, the switch  $S_{a1}$ :

```

if 	ext{ time } >= 2*T_0+T_1/4+T_2/4 \\ and 	ext{ time } < 2*T_0+T_1/4+T_2/4+T_{a1}: \\ if 	ext{ $V_{sa1} > 0$:} \\ K_1 = 1; 	ext{ faulty switch.} \\ else: \\ K_1 = 0; 	ext{ healthy switch.} \\ end; \\ end; \\ end; \\ where

```

$T_0, T_1, T_2$  application time of adjacent vectors,

$T_m$  modulation period,

$T_{a1}$  conduction time of switch  $S_{a1}$  in Sector 1,

$V_{sa1}$  voltage at the  $S_{a1}$  switch terminals,

$K_1$  CO fault detection signal of switch  $S_{a1}$ .

Knowing that,  $V_0, V_1, \dots, V_{14}$  are output voltage vectors

We do the same for the other sectors, and the other switches.

FIGURE 3. Conduction times of switches in Sector 1.

### 2.2. ALGORITHM FOR DETECTING A SWITCH SC FAULT

We take, for example, the switch  $S_{a1}$  in Sector 1 (Figure 3):

```

if 	ext{ time } >= 0 	ext{ } and 	ext{ time } < 2*T_0+T_1/4+T_2/4:

if 	ext{ } V_{sa1} > 0:

K_1 = 0; 	ext{ healthy switch}

else:

K_1 = 1; 	ext{ faulty switch}.

end;

end;

```

We do the same for the other sectors, and the other switches.

# 3. FAULT ISOLATION AND POST-FAULT RECONFIGURATION TECHNIQUE FOR A FAULT-TOLERANT 3-LEVEL 4-LEG NPC INVERTER

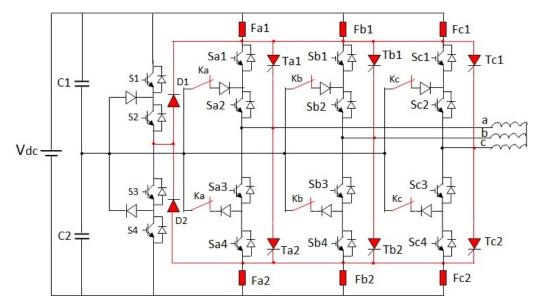

The investigated fault-tolerant topology is a 3-phase 3-level NPC inverter consisting of 3 main legs corresponding to 3 phases and a 4<sup>th</sup> spare leg. Since the four legs are identical, this fourth leg will replace one of the main legs if the one main leg fails due to a short circuit or open circuit in one of its four IGBT (Insulated Gate Bipolar Transistor) switches.

After detecting an IGBT switch fault at the inverter level (done in past section), the corresponding leg is instantaneously isolated. Then, the corresponding phase is connected to the 4<sup>th</sup> spare leg as shown in Figure 4. This reconfiguration can be done by controllers and additional components. An efficient technique that combines both the isolation and the post-failure reconstruction is proposed below.

The isolation of the leg with the faulty IGBT is based on the fusion of a pair of fuses placed on the two ends of the leg ( $F_{x1}$ ,  $F_{x2}$  with  $x = \{a, b, c\}$ ). Indeed, when an IGBT presents a fault, the two fuses must be tripped simultaneously through the triggering of the two thyristors  $T_{x1}$  and  $T_{x2}$  ( $x = \{a, b, c\}$ ) as shown in Figure 4 which are corresponding to the faulty leg. These thyristors ensure the connection of the corresponding phase to the fourth spare leg. And two auxiliary contacts  $K_x$  ( $x = \{a, b, c\}$ ) must be added next to the two clamped diodes to isolate the phase

FIGURE 4. Structure of the proposed three-phase 3-level fault-tolerant NPC inverter.

corresponding to the active neutral point in the event that one of the two internal IGBTs fails in a short circuit.

To ensure the post-fault rescue connection of the isolated phase with the fourth leg so that the latter takes over from the faulty leg, it must insert additional power components. For each leg, there is a pair of diodes, and a pair of thyristors which are previously used for isolation. In normal operation, they are blocked. They enter into conduction after the detection of the fault and connection of a spare leg into switching. The spare leg is, therefore, spontaneously and instantaneously connected to the corresponding phase after the fault and ensures the continuity of the operation at 100 % of voltage and power.

This new technique has two advantages. On the one hand, it is applicable regardless of the nature of the defect. On the other hand, it is inexpensive since the same components, in this case the two thyristors, provide, at the same time, the isolation and the connection of the phase corresponding to the fourth spare leg.

### 4. Simulation results

A simulation was carried out for the inverter in the healthy state case, in the faulty state case without fault tolerance, and in the faulty state case with fault tolerance.

### 4.1. HEALTHY INVERTER

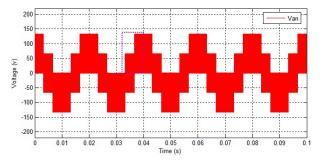

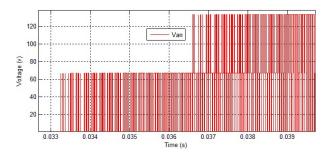

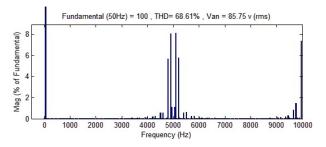

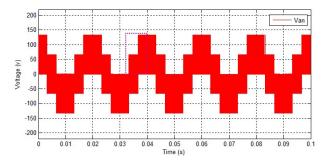

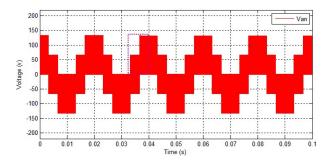

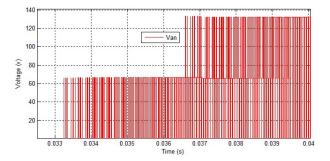

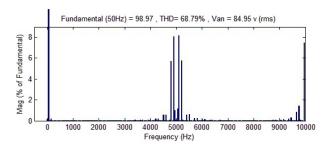

It is obvious that the healthy state case, will give us the theoretically expected results as shown below in (Figure 5, Figure 6, Figure 7).

Figure 5 shows the phase voltage  $(V_{an})$ , which switches between the three voltage levels  $(0, V_{dc}/6 \text{ and } V_{dc}/3)$  with the effective value being 85.75 V as shown in Figure 7.

FIGURE 5. Phase voltage waveform ( $V_{an}$ ) for healthy state case.

FIGURE 6.  $V_{an}$  zoom for healthy state case.

FIGURE 7. Harmonic content of  $V_{an}$  for healthy state case.

Figure 8. Phase voltage waveform (  $V_{an}$  ) for short-circuit fault case.

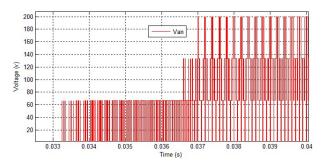

FIGURE 9.  $V_{an}$  zoom for short-circuit fault case.

### **4.2.** Inverter failure without fault tolerance

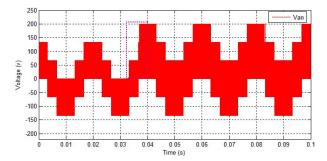

Two cases are done, short-circuit fault case and opencircuit fault case.

### 4.2.1. Short-circuit fault case

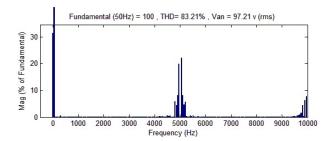

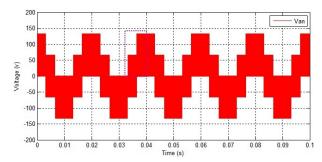

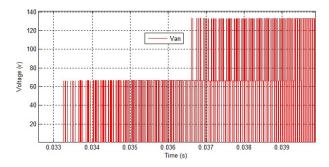

A short-circuit fault is applied to switch  $S_{a1}$  in the first leg, which corresponds to phase a at time t = 0.037 s (Figure 8, Figure 9, Figure 10).

### 4.2.2. OPEN-CIRCUIT FAULT CASE

An open-circuit fault is applied to switch  $S_{a1}$  in the first leg, which corresponds to phase a at time t = 0.037 s (Figure 11, Figure 12, Figure 13).

### **4.3.** Inverter failure with fault tolerance

Two cases are done, short-circuit fault tolerance case and open-circuit fault tolerance case.

#### 4.3.1. Short-circuit fault tolerance case

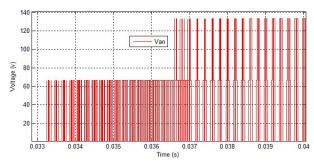

A short-circuit fault is applied to switch  $S_{a1}$  in the first leg, which corresponds to phase a at time  $t=0.037 \,\mathrm{s}$  (Figure 14, Figure 15, Figure 16).

### 4.3.2. OPEN-CIRCUIT FAULT TOLERANCE CASE

An open-circuit fault is applied to switch  $S_{a1}$  in the first leg, which corresponds to phase a at time t = 0.037 s (Figure 17, Figure 18, Figure 19).

Table 1 summarises the simulation result values. From the simulation results, it can be seen that:

• When a short-circuit fault occurs, the phase voltage waveform  $(V_{an})$  is distorted (see Figure 8), the value of voltage  $(V_{an})$  increases to 97.21 V and the THD

FIGURE 10. Harmonic content of  $V_{an}$  for short-circuit fault case.

FIGURE 11. Phase voltage waveform (  $V_{an}$  ) for open-circuit fault case.

FIGURE 12.  $V_{an}$  zoom for open-circuit fault case.

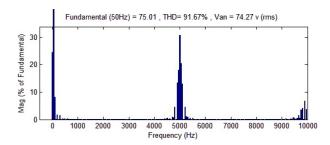

FIGURE 13. Harmonic content of  $V_{an}$  for open-circuit fault case.

Figure 14. Phase voltage waveform (  $V_{an}$  ) for short-circuit fault tolerance case.

FIGURE 15.  $V_{an}$  zoom for short-circuit fault tolerance case.

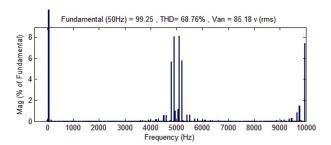

FIGURE 16. Harmonic content of  $V_{an}$  for short-circuit fault tolerance case.

FIGURE 17. Phase voltage waveform (  $V_{an}$  ) for open-circuit fault tolerance case.

(Total Harmonic Distorsion) increases to 83.21%, as shown in Table 1.

- For an open circuit fault, the phase voltage waveform  $(V_{an})$  is unaffected (see Figure 11), the value of voltage  $(V_{an})$  decreases to 74.27 V and the THD increases more than in the short-circuit fault case, to 91.67 %, as shown in Table 1.

- When a proposed fault tolerance is applied, the value of voltage and the harmonics are almost unaffected (see Table 1).

#### 5. Conclusion

The reliability and survivability of electrical drives based on power electronics converters are very important in terms of safety and economic costs.

This article presents a new reconfiguration for a fault-tolerant four-leg NPC inverter. In this topology, the fourth leg, which is added to the standard three-leg NPC topology can replace any of the other legs in the event of a power switch failure, whether

FIGURE 18.  $V_{an}$  zoom for open-circuit fault tolerance case.

FIGURE 19. Harmonic content of  $V_{an}$  for open-circuit fault tolerance case.

| Inverter states                    | $V$ oltage $V_{an}$ [V] | THD<br>[%] |

|------------------------------------|-------------------------|------------|

| Healthy inverter                   | 85.75                   | 68.61      |

| Short-circuit fault case           | 97.21                   | 83.21      |

| Open-circuit fault case            | 74.27                   | 91.67      |

| Short-circuit fault tolerance case | 85.18                   | 68.76      |

| Open-circuit fault tolerance case  | 84.95                   | 68.79      |

Table 1. Simulation result values of  $V_{an}$ .

open or short to using the voltage sensors at the terminals of these switches and a simple algorithm, thus increasing the reliability of the system.

The feasibility and efficiency of open-circuit, short-circuit fault detection, and fault tolerance of our proposed inverter design were verified by a simulation.

#### References

- [1] E. Can. Mathematical algorithm of fuzzy logic controller for multilevel inverter creating vertical divided voltage. *Acta Polytechnica* **59**(1):1–11, 2019. https://doi.org/10.14311/AP.2019.59.0001

- [2] U.-M. Choi, J.-S. Lee, F. Blaabjerg, K.-B. Lee. Open-circuit fault diagnosis and fault-tolerant control for a grid-connected NPC inverter. *IEEE Transactions on Power Electronics* **31**(10):7234–7247, 2016. https://doi.org/10.1109/TPEL.2015.2510224

- [3] T. Qanbari, B. Tousi. Single-source three-phase multilevel inverter assembled by three-phase two-level inverter and two single-phase cascaded H-bridge inverters. *IEEE Transactions on Power Electronics* **36**(5):5204–5212, 2021.

https://doi.org/10.1109/TPEL.2020.3029870

[4] Q. A. Le, D.-C. Lee. Elimination of common-mode voltages based on modified SVPWM in five-level ANPC

- inverters. *IEEE Transactions on Power Electronics* **34**(1):173–183, 2019.

- https://doi.org/10.1109/TPEL.2018.2825230

- [5] M. Dong, H. Dong, L. Wang, et al. A simple open-circuit detection strategy for a single-phase gridconnected PV inverter fed from power optimizers. *IEEE Transactions on Power Electronics* 33(4):2798–2802, 2018. https://doi.org/10.1109/TPEL.2017.2751508

- [6] K. Wang, L. Xu, Z. Zheng, Y. Li. Capacitor voltage balancing of a five-level ANPC converter using phase-shifted PWM. *IEEE Transactions on Power Electronics* **30**(3):1147–1156, 2015. https://doi.org/10.1109/TPEL.2014.2320985

- [7] O. Sivkov. Practical results of a five-level flying capacitor inverter. *Acta Polytechnica* **50**(6):74–80, 2010. https://doi.org/10.14311/1299

- [8] M. Hagiwara, H. Akagi. Control and experiment of pulsewidth-modulated modular multilevel converters. *IEEE Transactions on Power Electronics* **24**(7):1737–1746, 2009. https://doi.org/10.1109/TPEL.2009.2014236

- [9] C. Zhang, X. Li, X. Xing, et al. Modeling and mitigation of resonance current for modified LCL-type parallel inverters with inverter-side current control. *IEEE Transactions on Industrial Informatics* 18(2):932–942, 2022. https://doi.org/10.1109/TII.2021.3076090

- [10] D. Djendaoui, A. Benaissa, B. Rabhi, L. Zellouma. Self tunning filter for three levels four legs shunt active power filter with fuzzy logic controller. *Acta Polytechnica* **61**(3):415–427, 2021. https://doi.org/10.14311/AP.2021.61.0415

- [11] S. Ceballos, J. Pou, J. Zaragoza, et al. Efficient modulation technique for a four-leg fault-tolerant neutral-point-clamped inverter. *IEEE Transactions on Industrial Electronics* **55**(3):1067–1074, 2008. https://doi.org/10.1109/TIE.2008.917098

- [12] K. V. Vasuda, L. K. Johny, J. Mathew. Effective DC link utilization of multilevel dual inverter with single source in the maximal distention mode. *IEEE Access* 12:26212-26221, 2024. https://doi.org/10.1109/ACCESS.2024.3362923

- [13] J. Li, A. Q. Huang, Z. Liang, S. Bhattacharya. Analysis and design of active NPC (ANPC) inverters for fault-tolerant operation of high-power electrical drives. *IEEE Transactions on Power Electronics* **27**(2):519–533, 2012. https://doi.org/10.1109/TPEL.2011.2143430

- [14] Y. Yu, X. Li, L. Wei. Fault tolerant control of five-level inverter based on redundancy space vector optimization and topology reconfiguration. *IEEE Access* 8:194342-194350, 2020. https://doi.org/10.1109/ACCESS.2020.3033805

- [15] D.-T. Do, M.-K. Nguyen, T.-H. Quach, et al. A PWM scheme for a fault-tolerant three-level quasi-switched boost T-type inverter. *IEEE Journal of Emerging and Selected Topics in Power Electronics* 8(3):3029–3040, 2020.

- https://doi.org/10.1109/JESTPE.2019.2922687

- [16] T.-J. Kim, W.-C. Lee, D.-S. Hyun. Detection method for open-circuit fault in neutral-point-clamped inverter systems. *IEEE Transactions on Industrial Electronics* 56(7):2754–2763, 2009.

- https://doi.org/10.1109/TIE.2009.2019775

- [17] S. Yang, A. Bryant, P. Mawby, et al. An industry-based survey of reliability in power electronic converters. *IEEE Transactions on Industry Applications* 47(3):1441–1451, 2011. https://doi.org/10.1109/TIA.2011.2124436

- [18] S. P. Gautam, L. Kumar, S. Gupta, N. Agrawal. A single-phase five-level inverter topology with switch fault-tolerance capabilities. *IEEE Transactions on Industrial Electronics* **64**(3):2004–2014, 2017. https://doi.org/10.1109/TIE.2016.2626368

- [19] S. Yang, D. Xiang, A. Bryant, et al. Condition monitoring for device reliability in power electronic converters: A review. *IEEE Transactions on Power Electronics* 25(11):2734-2752, 2010. https://doi.org/10.1109/TPEL.2010.2049377

- [20] S. Yin, H. Luo, S. X. Ding. Real-time implementation of fault-tolerant control systems with performance optimization. *IEEE Transactions on Industrial Electronics* **61**(5):2402–2411, 2014. https://doi.org/10.1109/TIE.2013.2273477

- [21] B. Mirafzal. Survey of fault-tolerance techniques for three-phase voltage source inverters. *IEEE Transactions* on *Industrial Electronics* 61(10):5192-5202, 2014. https://doi.org/10.1109/TIE.2014.2301712

- [22] A. Bennani-Ben Abdelghani, H. Ben Abdelghani, F. Richardeau, et al. Versatile three-level FC-NPC converter with high fault-tolerance capabilities: Switch fault detection and isolation and safe postfault operation. *IEEE Transactions on Industrial Electronics* 64(8):6453-6464, 2017.

- https://doi.org/10.1109/TIE.2017.2682009