### Assignment of master's thesis

Title: Automatic verification methods in the SystemVerilog register

access layer

Student: Bc. Timur Ganeev

Supervisor: Ing. Martin Kohlík, Ph.D.

Study program: Informatics

**Branch / specialization:** Design and Programming of Embedded Systems

**Department:** Department of Digital Design

Validity: until the end of summer semester 2024/2025

### Instructions

- Study the constructs and components of the register access layer (RAL) of the SystemVerilog UVM library.

- Focus on RAL methods and constructs designed for automatic coverage calculations and built-in checking sequences.

- Create examples for individual RAL components with detailed comments focus on the configuration of the RAL elements and methods from the previous point.

- Create a readme text containing a brief instructions for each example.

Master's thesis

AUTOMATIC

VERIFICATION

METHODS IN THE

SYSTEMVERILOG

REGISTER ACCESS

LAYER

Bc. Timur Ganeev

Faculty of Information Technology Department of Digital Design Supervisor: Ing. Martin Kohlík, Ph.D. May 9, 2024

Czech Technical University in Prague Faculty of Information Technology © 2024 Bc. Timur Ganeev. All rights reserved.

This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

Citation of this thesis: Ganeev Timur. Automatic verification methods in the SystemVerilog register access layer. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2024.

## Contents

| A            | cknowledgments                                                                                                                                                                                                                                                                                                                                                            | viii                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| D            | eclaration                                                                                                                                                                                                                                                                                                                                                                | ix                                                                   |

| $\mathbf{A}$ | bstract                                                                                                                                                                                                                                                                                                                                                                   | x                                                                    |

| Li           | ist of abbreviations                                                                                                                                                                                                                                                                                                                                                      | xi                                                                   |

| In           | atroduction                                                                                                                                                                                                                                                                                                                                                               | 1                                                                    |

| 1            | Specification of the assignment                                                                                                                                                                                                                                                                                                                                           | 3                                                                    |

| 2            | Research 2.1 ChipVerify                                                                                                                                                                                                                                                                                                                                                   | 5<br>5<br>6<br>6                                                     |

| 3            | Analysis 3.1 Universal Verification Methodology 3.1.1 UVM Testbench Components 3.1.2 UVM Phases 3.2 UVM - Register Abstraction Layer 3.2.1 Frontdoor and Backdoor 3.2.2 UVM RAL - Register Model Structure 3.2.3 Prediction modes 3.2.4 Coverage collection 3.2.5 Built-in RAL sequences                                                                                  | 7<br>9<br>10<br>13<br>13<br>14<br>24<br>27<br>31                     |

| 4            | Implementation 4.1 Used Software and Tools 4.2 Initial Testbench 4.2.1 Design Under Test 4.2.2 Interface 4.2.3 Bus Transaction Sequence Item 4.2.4 Register Model 4.2.5 UVM Sequencer 4.2.6 UVM Driver 4.2.7 UVM Agent 4.2.8 UVM Environment 4.2.9 UVM Sequences 4.2.10 UVM Tests 4.2.11 UVM RAL Top Module (Testbench) 4.2.12 Results of Simulation of Initial Testbench | 37<br>37<br>37<br>39<br>40<br>41<br>46<br>46<br>47<br>47<br>50<br>51 |

iv Contents

|    | 4.3   | Final Testbench                                 | 51        |

|----|-------|-------------------------------------------------|-----------|

|    |       | 4.3.1 Design Under Test                         | 53        |

|    |       | 4.3.2 Interface                                 | 54        |

|    |       | 4.3.3 Bus Transaction Sequence Item             | 54        |

|    |       | 4.3.4 Register Model                            | 54        |

|    |       | 4.3.5 UVM Sequencer                             | 61        |

|    |       | 4.3.6 UVM Driver                                | 61        |

|    |       | 4.3.7 UVM Monitor                               | 61        |

|    |       | 4.3.8 UVM Agent and Second Agent                | 62        |

|    |       | 4.3.9 UVM Environment                           | 62        |

|    |       | 4.3.10 Reason for utilization of TWO_MAPS macro | 62        |

|    |       | 4.3.11 UVM Sequences                            | 63        |

|    |       | 4.3.12 UVM Tests                                | 66        |

|    |       | 4.3.13 UVM RAL Top Module (Testbench)           | 67        |

|    |       |                                                 |           |

| 5  | Test  |                                                 | <b>69</b> |

|    | 5.1   | Inserted Bugs                                   | 69        |

|    | 5.2   | Execution of my_custom_sequences_test           | 69        |

|    |       | 5.2.1 Identifying Bugs                          | 69        |

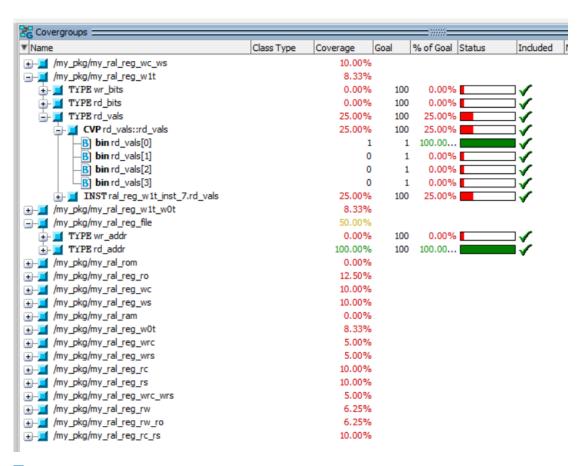

|    |       | 5.2.2 Coverage Collection                       | 72        |

|    | 5.3   | Execution of my_built_in_sequences_test         | 72        |

|    |       | 5.3.1 Identifying Bugs                          | 72        |

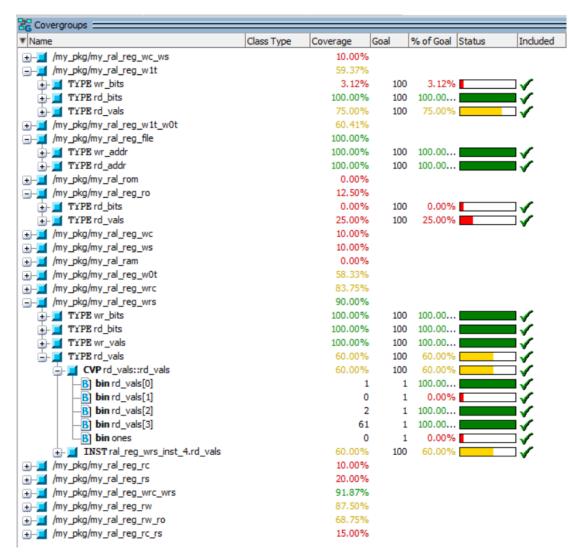

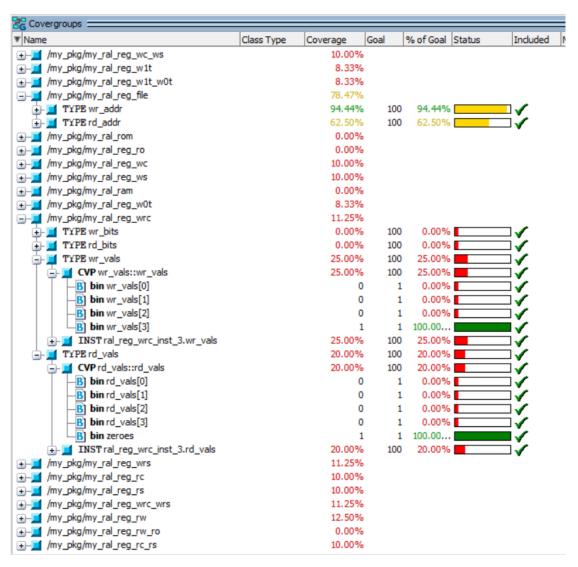

|    |       | 5.3.2 Coverage Collection                       | 75        |

|    | 5.4   | Execution of my_full_test                       | 80        |

|    | 5.5   | Execution of uvm_reg_mem_built_in_seq sequence  | 80        |

|    | 5.6   | Potential memory sampling bug                   | 81        |

|    | 5.7   | Simulation Results                              | 83        |

|    |       |                                                 |           |

| Co | onclu | asion                                           | 85        |

| Co | onten | nts of the attachment                           | 91        |

# List of Figures

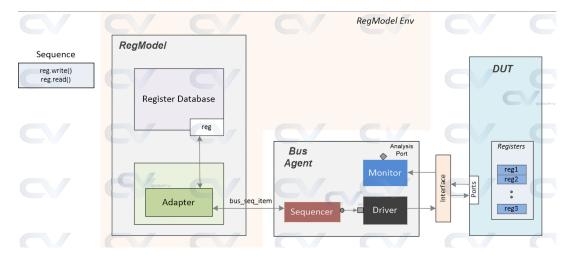

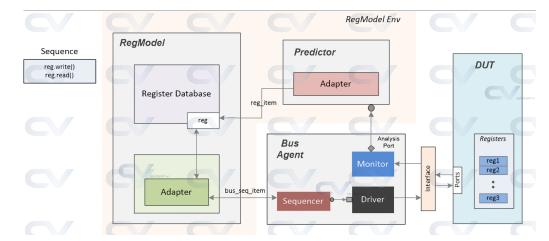

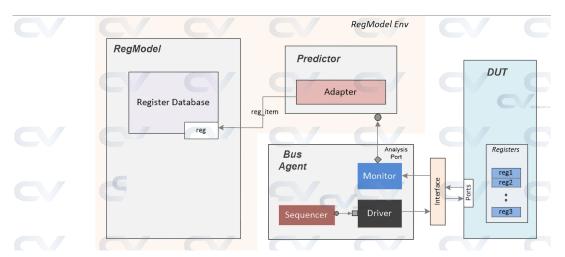

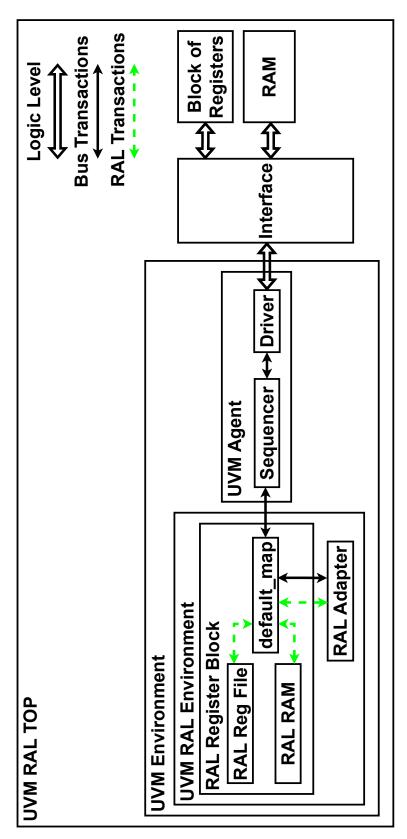

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Universal Verification Methodology Phases Universal Verification Methodology Run Phases UVM Register Abstraction Layer – Register Model Structure Testbench Structure of a Register Model with Implicit Prediction Testbench Structure of a Register Model with Explicit Prediction Testbench Structure of a Register Model with Passive Prediction | 11<br>12<br>14<br>25<br>26<br>26 |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

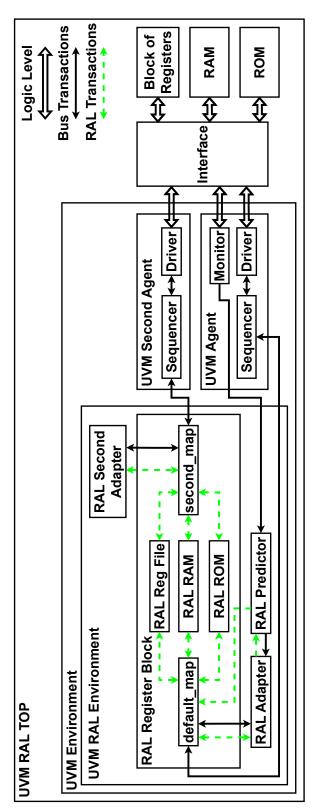

| 4.1<br>4.2                                    | Structure of Initial Testbench                                                                                                                                                                                                                                                                                                                      | 38<br>52                         |

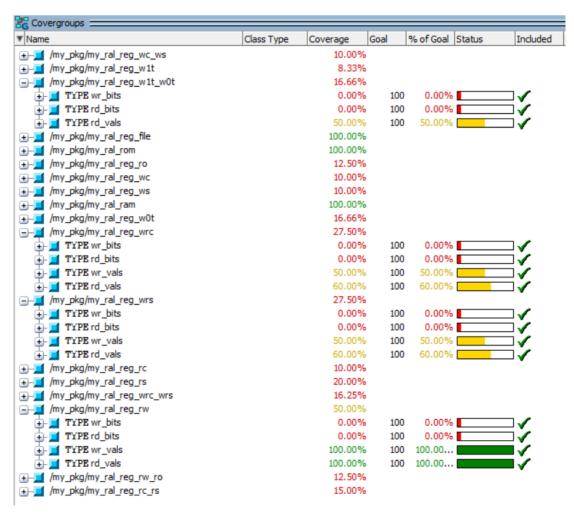

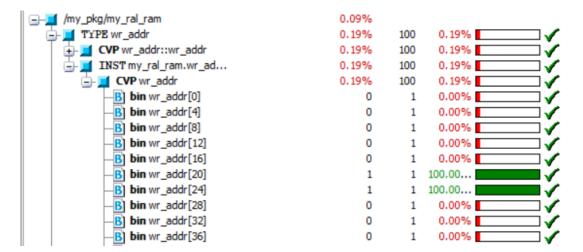

| 5.1<br>5.2                                    | Custom sequences test – collected coverage for individual register and memory addresses models only                                                                                                                                                                                                                                                 | 72<br>73                         |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8        | Custom sequences test – collected coverage with all coverage models built and sampled                                                                                                                                                                                                                                                               | 73<br>76<br>77<br>78<br>79<br>81 |

|                                               | List of Tabl                                                                                                                                                                                                                                                                                                                                        | les                              |

| 3.1<br>3.2<br>3.3<br>3.4                      | Register field access policies supported by UVM RAL  Built-in RAL register sequences                                                                                                                                                                                                                                                                | 18<br>32<br>33<br>35             |

| 4.1<br>4.2                                    | Structure of block of registers in final testbench                                                                                                                                                                                                                                                                                                  | 51<br>57                         |

| 5.1<br>5.2<br>5.3                             | Inserted bugs in the DUT blocks                                                                                                                                                                                                                                                                                                                     | 70<br>83<br>84                   |

vi List of code listings

# List of code listings

| 3.2 uvm_reg::configure() 3.3 uvm_reg::needs_update() 3.4 uvm_reg::write() 3.5 uvm_reg::read() 3.6 uvm_reg::poke() 3.7 uvm_reg::peek() 3.8 uvm_reg::update() 3.9 uvm_reg::mirror() 3.10 uvm_reg::predict() 3.11 uvm_reg_field::new() 3.12 uvm_reg_field::new() 3.13 uvm_reg_file::configure() 3.14 uvm_reg_file::configure() 3.15 uvm_mem::new() 3.16 uvm_mem::configure() 3.17 uvm_mem::burst_write() |      |   |                 | <br>15<br>15<br>16<br>16<br>16<br>16<br>17<br>17 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|-----------------|--------------------------------------------------|

| 3.4 uvm_reg::write() 3.5 uvm_reg::read() 3.6 uvm_reg::poke() 3.7 uvm_reg::peek() 3.8 uvm_reg::update() 3.9 uvm_reg::mirror() 3.10 uvm_reg::predict() 3.11 uvm_reg_field::new() 3.12 uvm_reg_field::configure() 3.13 uvm_reg_file::new() 3.14 uvm_reg_file::configure() 3.15 uvm_mem::new() 3.16 uvm_mem::configure()                                                                                  |      |   |                 | <br>15<br>16<br>16<br>16<br>16<br>17<br>17       |

| 3.5                                                                                                                                                                                                                                                                                                                                                                                                   | <br> |   |                 | <br>16<br>16<br>16<br>16<br>17<br>17             |

| 3.6                                                                                                                                                                                                                                                                                                                                                                                                   | <br> |   |                 | <br>16<br>16<br>16<br>17<br>17                   |

| 3.7 uvm_reg::peek()                                                                                                                                                                                                                                                                                                                                                                                   | <br> |   | <br>            | <br>16<br>16<br>17<br>17                         |

| 3.8 uvm_reg::update() 3.9 uvm_reg::mirror() 3.10 uvm_reg::predict() 3.11 uvm_reg_field::new() 3.12 uvm_reg_field::configure() 3.13 uvm_reg_file::new() 3.14 uvm_reg_file::configure() 3.15 uvm_mem::new() 3.16 uvm_mem::configure()                                                                                                                                                                   | <br> |   | <br><br><br>    | 16<br>17<br>17<br>17                             |

| 3.9                                                                                                                                                                                                                                                                                                                                                                                                   | <br> |   | <br>· · · · · · | 17<br>17<br>17                                   |

| 3.10 uvm_reg::predict()                                                                                                                                                                                                                                                                                                                                                                               | <br> |   | <br><br>        | 17<br>17                                         |

| 3.11 uvm_reg_field::new()                                                                                                                                                                                                                                                                                                                                                                             | <br> |   | <br>            | 17                                               |

| 3.12 uvm_reg_field::configure()          3.13 uvm_reg_file::new()          3.14 uvm_reg_file::configure()          3.15 uvm_mem::new()          3.16 uvm_mem::configure()                                                                                                                                                                                                                             | <br> |   | <br>            |                                                  |

| 3.13 uvm_reg_file::new()                                                                                                                                                                                                                                                                                                                                                                              | <br> |   |                 | 17                                               |

| 3.14 uvm_reg_file::configure()                                                                                                                                                                                                                                                                                                                                                                        | <br> |   |                 | •                                                |

| 3.15 uvm_mem::new()                                                                                                                                                                                                                                                                                                                                                                                   |      |   |                 | 19                                               |

| 3.16 uvm_mem::configure()                                                                                                                                                                                                                                                                                                                                                                             |      | • | <br>            | 19                                               |

| 3.16 uvm_mem::configure()                                                                                                                                                                                                                                                                                                                                                                             |      |   | <br>            | 19                                               |

| 3.17 uvm mem::burst write()                                                                                                                                                                                                                                                                                                                                                                           |      |   |                 |                                                  |

| 511, d/11121110111110 disc_111100()                                                                                                                                                                                                                                                                                                                                                                   |      |   |                 |                                                  |

| 3.18 uvm_mem::burst_read() $\dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                    | <br> |   | <br>            | 20                                               |

| 3.19 uvm_reg_map::new()                                                                                                                                                                                                                                                                                                                                                                               | <br> |   | <br>            | 21                                               |

| 3.20 uvm_reg_map::configure()                                                                                                                                                                                                                                                                                                                                                                         | <br> |   | <br>            | 21                                               |

| 3.21 uvm_reg_map::add_reg()                                                                                                                                                                                                                                                                                                                                                                           | <br> |   | <br>            | 21                                               |

| 3.22 uvm_reg_map::add_mem()                                                                                                                                                                                                                                                                                                                                                                           | <br> |   | <br>            | 21                                               |

| 3.23 uvm_reg_map::add_submap()                                                                                                                                                                                                                                                                                                                                                                        | <br> |   | <br>            | 21                                               |

| 3.24 uvm_reg_map::set_sequencer()                                                                                                                                                                                                                                                                                                                                                                     | <br> |   | <br>            | 22                                               |

| $3.25 \text{ uvm\_reg\_map::set\_base\_addr}() \dots \dots \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                             | <br> |   | <br>            | 22                                               |

| 3.26 uvm_reg_map::set_auto_predict()                                                                                                                                                                                                                                                                                                                                                                  | <br> |   | <br>            | 22                                               |

| 3.27 uvm_reg_map::get_auto_predict()                                                                                                                                                                                                                                                                                                                                                                  | <br> |   | <br>            | 22                                               |

| 3.28 Structure uvm_reg_bus_op                                                                                                                                                                                                                                                                                                                                                                         | <br> |   | <br>            | 22                                               |

| 3.29 uvm_reg_adapter::reg2bus()                                                                                                                                                                                                                                                                                                                                                                       |      |   |                 |                                                  |

| 3.30 uvm_reg_adapter::bus2reg()                                                                                                                                                                                                                                                                                                                                                                       |      |   |                 |                                                  |

| 3.31 uvm_reg_block::new()                                                                                                                                                                                                                                                                                                                                                                             |      |   |                 |                                                  |

| 3.32 uvm_reg_block::configure()                                                                                                                                                                                                                                                                                                                                                                       | <br> |   | <br>            | 24                                               |

| 3.33 uvm_reg_block::create_map()                                                                                                                                                                                                                                                                                                                                                                      | <br> |   | <br>            | 24                                               |

| 3.34 uvm_reg_block::lock_model()                                                                                                                                                                                                                                                                                                                                                                      | <br> |   | <br>            | 24                                               |

| 3.35 uvm_reg_block::is_locked()                                                                                                                                                                                                                                                                                                                                                                       | <br> |   | <br>            | 24                                               |

| 3.36 uvm_reg::include_coverage()                                                                                                                                                                                                                                                                                                                                                                      | <br> |   | <br>            | 27                                               |

| 3.37 uvm_reg_cvr_t                                                                                                                                                                                                                                                                                                                                                                                    |      |   |                 |                                                  |

| 3.38 Enumeration uvm_coverage_model_e                                                                                                                                                                                                                                                                                                                                                                 | <br> |   | <br>            | 27                                               |

| 3.39 uvm_reg::build_coverage()                                                                                                                                                                                                                                                                                                                                                                        |      |   |                 |                                                  |

| 3.40 uvm_reg::add_coverage()                                                                                                                                                                                                                                                                                                                                                                          |      |   |                 |                                                  |

| 3.41 uvm_reg::has_coverage()                                                                                                                                                                                                                                                                                                                                                                          |      |   |                 |                                                  |

| 3.42 uvm_reg::set_coverage()                                                                                                                                                                                                                                                                                                                                                                          |      |   |                 |                                                  |

| 3.43 uvm_reg::get_coverage()                                                                                                                                                                                                                                                                                                                                                                          |      |   |                 |                                                  |

| 3.44 uvm_reg::sample()                                                                                                                                                                                                                                                                                                                                                                                |      |   |                 | 30                                               |

List of code listings vii

| 3.45 | uvm_reg_block::sample()         | 30          |

|------|---------------------------------|-------------|

| 3.46 | uvm_mem::sample()               | 30          |

| 3.47 | Enumeration uvm_reg_mem_tests_e | 34          |

| 4.1  | Initial block of registers      | 39          |

| 4.2  | Initial RAM                     | 39          |

| 43   | Initial interface               | <u> 1</u> 0 |

I would like to give my thanks to my supervisor – Ing. Martin Kohlík, Ph.D. for his willingness and readiness to help me along the way of writing this thesis. Without his assistance this thesis and its practical part would not be finished.

### Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular the fact that the Czech Technical University in Prague has the right to conclude a license agreement on the utilization of this thesis as a school work pursuant of Section 60 (1) of the Act.

In Prague on May 9, 2024

### **Abstract**

The purpose of this thesis is to study the Universal Verification Methodology (UVM) for digital circuit verification and its Register Abstraction Layer (RAL) in particular. This thesis describes the process of testbench implementation for registers and memories using UVM RAL. Next, it is explained how the user can set up automatic coverage collection and how the user can execute built-in UVM RAL sequences for checking functionality of registers and memories.

**Keywords** SystemVerilog, Verilog, Universal Verification Methodology, UVM, Register Abstraction Layer, RAL, Verification, Simulation, Register model, Register, Memory, RAM, ROM, Coverage, Coverage collection, Built-in sequences

### **Abstrakt**

Tato práce se zabývá metodologií pro verifikaci digitálních integrovaných obvodů (Universal Verification Methodology – UVM), zejména její registrovou vrstvou (Register Abstraction Layer – RAL). V dané práci je popsán proces implementace prostředí pro testování registrů a pamětí s využitím komponent a metod UVM RAL. Dále je zde detailně popsáno, jak uživatel může nastavit automatickou kontrolu pokrytí a jak se dá spustit vestavěné UVM RAL sekvence pro verifikaci funkcionality testovaných registrů a pamětí.

**Klíčová slova** SystemVerilog, Verilog, Universal Verification Methodology, UVM, Register Abstraction Layer, RAL, Registrová vrstva, Verifikace, Simulace, Registrový model, Registr, Paměť, RAM, ROM, Pokrytí, Kontrola pokrytí, Vestavěné sekvence

### List of abbreviations

- UVM Universal Verification Methodology

- RAL Register Abstraction Layer

- DUT Design/Device Under Test

- RAM Random-access Memory

- ROM Read-only Memory

- TLM Transaction Level Modeling

- AMBA Advanced Microcontroller Bus Architecture

- XML Extensible Markup Language

- LSB Least Significant Bit

- MSB Most Significant Bit

- HDL Hardware Description Language

- IDE Integrated Development Environment

- NI-SIM Digital Circuit Simulation and Verification

- CTU Czech technical university in Prague

- FIT Faculty of Information Technology

- MIPS Microprocessor without Interlocked Pipelined Stages

xii List of abbreviations

# Introduction

In this day and age embedded systems have become a part of our normal lives and are present all around us – from computers, mobile phones and tablets to TVs, dishwashers and credit cards. Such systems are very robust and complex and can contains billions of transistors. Because of that, it is not impossible to have a bug in such system. If a bug is not discovered in time, it can cost a lot of money to deal with the consequences, since the earlier the bug is discovered – the less it will cost. Textbook example of such a thing is an Intel Pentium FDIV bug in 1994. It affected the division of certain pairs of high-precision numbers and, as a result, processor would return incorrect binary floating-point numbers. In total in costed Intel \$475 million pre-tax to recover replacement and write-off these microprocessors.

Verification of such digital designs is one of the crucial tasks during design process and it cant take up to 70% of the total time spent working on a chip. The end goal of verification is a confirmation, that produced design meets all requirements and specifications. Just for that reason Universal Verification Methodology (UVM) was created with initial version releasing in 2011. It is a standardized methodology, which purpose is to verify integrated circuits. It utilizes SystemVerilog language and follows the principles of object-oriented programming. UVM was derived from the Open Verification Methodology (OVM), which is an open-source verification methodology for digital designs and systems-on-chip and was released in 2008. UVM is more flexible and reusable methodology that can be easily applied to different digital designs.

One of the crucial parts of such designs are registers and memories. Registers can be used for setting desired configurations while memories contain instructions and data. For design to behave without errors they also need to be verified. For that reason UVM contains base class library for registers and memory structures, which is called Register Abstraction Layer (RAL). It is not necessary to use UVM RAL to verify them, but without it, programmer has to take care of each register individually, which can prove to be a tedious task, since typical design can contain hundreds of them. This thesis describes how to create and configure UVM RAL register model to verify registers and memories in design under test (DUT).

Structure of this thesis is as follows: chapter 1 further describes the goals of this work. Chapter 2 contains the research regarding current existing solutions, i.e. websites, articles or theses that present the process of DUT integration into the UVM RAL register model. Chapter 3 talks about UVM in general and shows the usage of individual UVM and RAL components. Chapter 4 describes the process of DUT verification using UVM register abstraction layer. Finally, chapter 5 validates, that DUT was integrated correctly and register model is capable of catching artificially inserted bugs in the design.

2 Introduction

### Chapter 1

# Specification of the assignment

This chapter further describes goals of the assignment of this thesis.

The purpose of this thesis is to showcase the process of integration of registers, RAM and ROM memories into UVM register model and their subsequent verification using UVM RAL. This includes coverage collection and built-in UVM RAL sequences for testing registers and memories.

Before that, this thesis also describes UVM and RAL themselves, so that anyone who is not familiar with it can still understand the essence of this work.

Another purpose of this work is to describe the configuration of individual UVM and RAL components to successfully integrate DUT into the register model.

Implemented testbench will be located in a GitLab repository [1].

### Chapter 2

## Research

This chapter describes existing solutions, i.e. websites, theses and articles, which describe the process of verification of DUT using UVM RAL.

. . . . . . . .

### 2.1 ChipVerify

. . . . . . . . . . . . .

Website [2] is an extensive guide to UVM. It describes every basic component of this methodology and shows how a programmer can use it for verification of DUT of their choice. This website goes into great detail about a lot of aspects of UVM and is a great starting point for everyone, who wants to learn about it from scratch.

It also contains a section about register abstraction layer, where the author describes individual components of this layer and provides complete example of integrated registers in RAL environment.

What this website does not describe, however, is how the user can integrate memories (RAM/ROM) into the RAL. Therefore, it does not provide any information about memory operations that can be used to verify their behavior.

There is also no information about the differences between implicit and explicit prediction in register model (prediction modes are explained in detail later in this work). In the complete example author actually has implemented predictor, but does not provide any explanation as to why and when we should actually use it in our testbenches.

Another thing that this website is lacking is the process of automatic coverage collection during verification using UVM RAL. The only thing, that is related to coverage, is a general description of it using standard SystemVerilog language.

Finally, there is no information at all about built-in UVM RAL sequences.

### 2.2 Verification Guide

Website [3] is also another place, where one can learn more about UVM and RAL in general. In comparison with ChipVerify [2] this website contains even less information and can be a little difficult to understand.

The author briefly explains functionality of implicit and explicit predictions, but does not use any predictors in the complete example, i.e. there is no practical example as to how the user can implement implicit/explicit predictions in their testbenches.

Similarly to [2], there is no information about integrating memories in register model, automatic coverage collection and built-in UVM RAL sequences.

6 Research

### 2.3 VLSI Verify

VLSI Verify website [4] is another place containing useful information about UVM itself and about register abstraction layer.

There are plenty of pictures and schemes describing different aspects of UVM. In comparison with previous websites, this website has a section about implicit, explicit and passive predictions. Author presents advantages and disadvantages of each prediction mode and even provides an example as to how one can turn on desired prediction in their own testbench. But author does so without going into too much detail.

What website does not describe, however, are how the user can integrate memories into register abstraction layer, how to enable automatic coverage collection and how to execute built-in RAL sequences.

### 2.4 Vojtěch Jílek's Master Thesis

The goal of Vojtěch Jílek's master's thesis [5] was to showcase the usage of UVM and RAL in general and to verify the functionality of a simple single cycle and pipelined processor. Another goal of that thesis was to describe common mistakes and problems that a novice developer may encounter while using register abstraction layer.

Vojtěch Jílek was able to accomplish initial goal with his thesis. It contains useful information about UVM and register layer and can be used to quickly get to know all its general components and functions.

The code of the thesis [6] contains testbenches for single cycle and pipelined processors and utilizes a wide variety of constructions, that are supported by UVM to make the verification process as simple as possible. The only problem is that the code barely contains any comments and it can be quite difficult to comprehend what each individual component or function is supposed to do.

Another thing that this thesis is lacking in is the usage of RAL automatic coverage collection and built-in register abstraction layer sequences. The author also does not describe the differences between implicit and explicit predictions.

### Chapter 3

# Analysis

The purpose of this chapter is to describe basic concepts of UVM and its register abstraction layer.

### 3.1 Universal Verification Methodology

As it was already stated in the introduction, UVM is used to verify digital designs. It was created with a purpose of standardizing the structures of verification programs and testing methodologies. With UVM the user can create verification environment for complex designs with the help of built-in classes and methods.

Main features of UVM are:

**Testbench Components** UVM contains a set of classes, that can be used in verification process. They can be extended and modified as the user sees fit.

**Transactions** Communication between the DUT and testbench happens with a help of the so-called transactions. The user can extend the existing transaction class, which is used to transfer information between DUT and testbench.

Communication between individual components inside a testbench happens on a Transaction Level Modeling (TLM) level.

Messaging and Reporting With a help of UVM the user can printout relevant information about the simulation runs, such as warnings and errors, which can be used to further improve verification environment and for debugging.

**Configuration** With a help of configuration database the user can store and retrieve appropriate information for testbench components.

**Functional Coverage** Functional coverage is a process, that evaluates how thoroughly were the functionalities of the design tested. It is a user-defined metric, and, with a help of UVM, the user can ensure, that the DUT was exhaustively verified.

**Register Abstraction Layer** RAL simplifies the process of verification of DUT registers and memories. For more in-depth information about RAL refer to section 3.2.

Basic information about UVM is taken from [7].

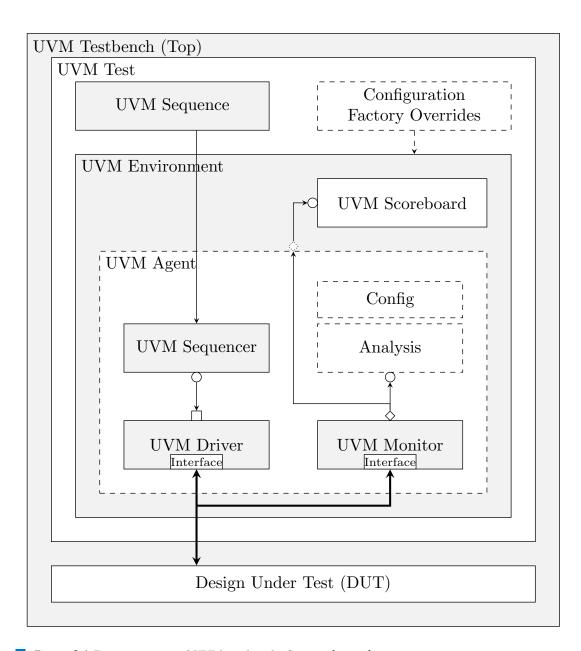

**Figure 3.1** Basic structure of UVM testbench. Source: [8, s. 4]

### 3.1.1 UVM Testbench Components

Here we will describe every major component of UVM. Basic structure of a typical testbench, that utilizes UVM, is shown in figure 3.1.

### UVM Testbench (Top)

Testbench top is used to statically store the instance of DUT and corresponding interfaces. Interfaces are used for DUT and UVM test to communicate with each other. Testbench top is also responsible for generating clock and reset signals, and for choosing a test that will be executed on a DUT block [9].

#### **UVM** Test

Before the simulation starts, UVM test dynamically generates and configures verification environment (UVM Environment). UVM test is also responsible for connecting this environment to DUT using interfaces and it is achieved with a help of configuration database. UVM test can start the simulation itself by executing UVM sequence on UVM sequencers [8, s. 5].

### **UVM** Environment

UVM environment is a container for multiple, reusable verification components, such as agents, drivers, monitors, scoreboards and other environments. These components communicate with each other using TLM ports [8, s. 5].

### **UVM Sequence Item**

UVM sequence item is a data packet, that encapsulates all relevant signals that should be sent to DUT in order to verify its desired functionality. For example, sequence item that would be used to send some data to some register can contain write enable bit, register address and data.

Having these signals in a structure allows user to perform useful operation on them, such as randomizing, modifying, printing out, copying etc.

### **UVM** Sequence

UVM sequence contains data items (uvm\_sequence\_item), which are later sent to the DUT with a help of a driver via sequencer. Sequence can randomize and send these sequence items in a specified order, therefore we can create interesting scenarios for DUT to process. Sequence is not a part of the UVM environment and can be connected to only one UVM Sequencer [8, s. 6].

### **UVM** Sequencer

UVM sequencer is a mediator between sequence and driver. It chooses what data items coming from a sequence should be passed to a driver so that they can be later sent to a DUT. Sequencer is also able to receive response data items from a DUT via driver. Single sequencer can have multiple sequences connected to it [8, s. 6].

### **UVM Driver**

UVM driver communicates with a DUT. It retrieves randomized uvm\_sequence\_item from a sequencer and converts it to a logical level signals for interface. Corresponding interface handle can be acquired from configuration database. Driver class contains REQ (request) and RSP (response) parameterized types, which are of type uvm\_sequence\_item by default. Request is a

sequence item, that will be sent to DUT via interface, whereas response is a sequence item, that contains data sent from the DUT to the testbench [10].

### **UVM Monitor**

UVM Monitor is used to observe signal activity from the interface (logic level) and converts it into transaction level objects (uvm\_sequence\_item) that can be sent to other verification components via TLM analysis port. Monitor can be configured for basic protocol checking and coverage collection [11].

### **UVM** Agent

UVM agent encapsulates sequencer, driver and monitor into a single block. Agent is responsible for their instantiation and for establishing connection between them. Agent can be configured for basic protocol checking and for coverage collection. Agent can be active or passive [12]:

**Active agent** instantiates all three components (sequencer, driver and monitor). Data can be driven to DUT.

Passive agent only instantiates a monitor. Data can not be driven to DUT. This way agent can only observe signals from the interface and send them to other components. Useful when we do not need to send data to DUT.

#### **UVM Scoreboard**

UVM scoreboard is a verification component that checks functionality of the DUT. It receives data items from monitor through TLM port and compares it with a reference (golden) DUT model [13].

### 3.1.2 UVM Phases

In UVM based SystemVerilog testbench class object can be created at any time during simulation. That means that we need to somehow check if object we are about to call is already created, i.e. we need some kind of synchronization mechanism. For that reason UVM introduces the concept of so-called phases.

Each verification component is derived from uvm\_component class and hence supports the usage of phases. Phases are implemented as virtual callback functions/methods and can be defined by the user. Each individual component can not proceed to the next phase, unless all other components finish their operations in the current phase. That way proper synchronization between all components is guaranteed.

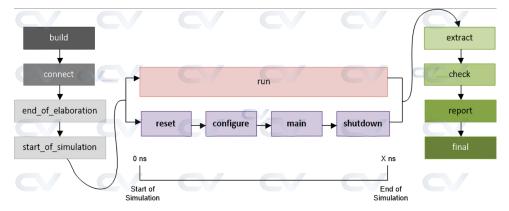

Order of execution of these phases is depicted in figure 3.2. Each individual phase is described in detail in the following sections.

All information regarding UVM phases is taken from [15], [14], [16] and [17].

### 3.1.2.1 build\_phase

Build phase is responsible for creating and configuring testbench structure. It calls build\_phase() of every uvm\_component that is currently present in a testbench in a top-down order. This phase does not consume any simulation time and therefore is implemented as a function.

Typical uses of build\_phase() include instantiation of sub-components, instantiation of register model, getting configuration values for the components being built and setting configuration values for sub-components.

Phase ends when all uvm\_component components have been instantiated.

Figure 3.2 Universal Verification Methodology Phases. Source: [14]

### 3.1.2.2 connect\_phase

Connect phase is used to connect all verification components with each other. connect\_phase() of every uvm\_component that is currently present in a testbench is called in a bottom-up order. This phase does not consume any simulation time and therefore is implemented as a function.

Typical uses of connect\_phase include connecting TLM ports and connecting register model to adapter components.

Phase ends when the connection between all uvm\_components has been established.

### 3.1.2.3 end\_of\_elaboration\_phase

End of elaboration phase is responsible for potential parametrization of verification components. It calls end\_of\_elaboration\_phase() of every uvm\_component that is currently present in a testbench in a bottom-up order. This phase does not consume any simulation time and therefore is implemented as a function.

Typical uses of end\_of\_elaboration\_phase include displaying environment topology, opening files and defining additional configuration settings for components.

Phase ends when all defined operations in it have been executed.

### 3.1.2.4 start\_of\_simulation\_phase

Start of simulation phase is used to print out additional information about verification topology. It calls start\_of\_simulation\_phase() of every uvm\_component that is currently present in a testbench in a bottom-up order. This phase does not consume any simulation time and therefore is implemented as a function.

Typical uses of start\_of\_simulation\_phase include displaying environment topology, setting debugger breakpoints and setting initial run-time configuration values.

Phase ends when all defined operations in it have been executed.

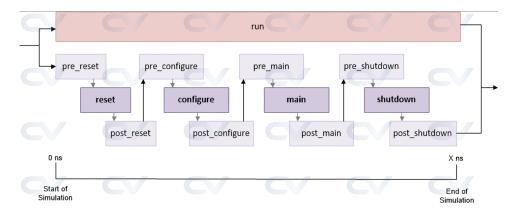

### 3.1.2.5 run\_phase

Run phase starts the simulation of DUT. It calls run\_phase() of every uvm\_component that is currently present in a testbench. Run phase runs in parallel to the other runtime phases, as shown in figure 3.3. All components are synchronized with the respect to the current run phase. This phase (i.e. the simulation itself) consumes actual simulation time and therefore is implemented as a task.

Other runtime phases (apart from run\_phase) are:

Figure 3.3 Universal Verification Methodology Run Phases. Source: [14]

**reset\_phase** This phase is responsible for generating reset and clock signals for verification components that are connected to an interface.

**configure\_phase** This phase is used to configure DUT and its memories to be compatible with the verification environment.

main\_phase This phase is used for primary test stimulus, i.e. its purpose is to properly start stimulus sequences.

**shutdown\_phase** This phase waits for all data to be drained out of the DUT after simulation ends. Buffered data from the DUT is extracted with a help of read/write operations or sequences.

Phases with a name pre\_\* or post\_\*, where \* is a name of a runtime phase, are used to further fine-tune corresponding runtime phase.

Phase run\_phase ends when two conditions are satisfied:

- 1. There is no need for DUT to be simulated further.

- 2. post\_shutdown\_phase is ready to end.

In that case run\_phase terminates in one of two ways:

- 1. Every verification component can raise and drop so-called "objections" on the specified phase. Raised objection indicates, that this component is not ready to end and is still executing some operations. If all objections on run\_phase are dropped phase ends.

- 2. Even if there are raised objections on run\_phase, it can still end if the timeout expires. By default, the timeout is set to 9200 seconds, but can be overridden with set\_timeout() method.

### 3.1.2.6 extract\_phase

This phase is used to extract data from different points of the verification environment. It calls extract\_phase() of every uvm\_component that is currently present in a testbench in a bottom-up order. This phase does not consume any simulation time and therefore is implemented as a function.

Typical uses of extract\_phase include extracting remaining data and final state information from verification components, computing and displaying statistics and closing files.

Phase ends when all desired information has been collected and summarized.

### 3.1.2.7 check\_phase

Check phase is used for checking for any unexpected events in the verification environment. It calls check\_phase() of every uvm\_component that is currently present in a testbench in a bottom-up order. This phase does not consume any simulation time and therefore is implemented as a function.

Main purpose of this phase is to check if there is no unaccounted-for data remains in the testbench.

Phase ends when current test is known to have passed or failed.

### 3.1.2.8 report\_phase

Report phase is responsible for reporting results of the test. It calls report\_phase() of every uvm\_component that is currently present in a testbench in a bottom-up order. This phase does not consume any simulation time and therefore is implemented as a function.

Phase ends when the current test ends.

### 3.1.2.9 final\_phase

Final phase is used for clearing up various things that are related to current simulation run. It calls final\_phase() of every uvm\_component that is currently present in a testbench in a top-down order. This phase does not consume any simulation time and therefore is implemented as a function.

Phase ends when the simulator tool is ready to exit.

### 3.2 UVM – Register Abstraction Layer

Registers are indispensable parts of every hardware design. They can be used to store configuration data and can be written to with a help of software. Such software can use some kind of bus protocol, for example AMBA (Advanced Microcontroller Bus Architecture), to set registers to certain values.

Verifying registers can be tedious, as the user would need to manually create sequence items with desired data, create uvm\_sequence and execute this sequence on an appropriate sequencer. For that reason UVM contains so-called Register Abstraction Layer (RAL).

This register abstraction layer not only makes the process of register verification easier, but is also capable of verifying various memory blocks.

UVM RAL is not necessary in order to verify functionality of the registers and memories, but it contains useful abstract classes and methods, which make verification engineer's job much easier.

All information about RAL is taken from [2] and [18].

### 3.2.1 Frontdoor and Backdoor

Reading and writing registers and memory words through RAL can be done via so-called front-door or backdoor.

Communication between register model and DUT via frontdoor means converting register model transaction to a protocol specific bus transaction and driving this transaction into the DUT through a physical interface. In other words, it is the same as when some component in the actual digital design is communicating with registers or memories in the same design. It means that all logic surrounding such communication is active and clock cycles (i.e. simulation time) are consumed.

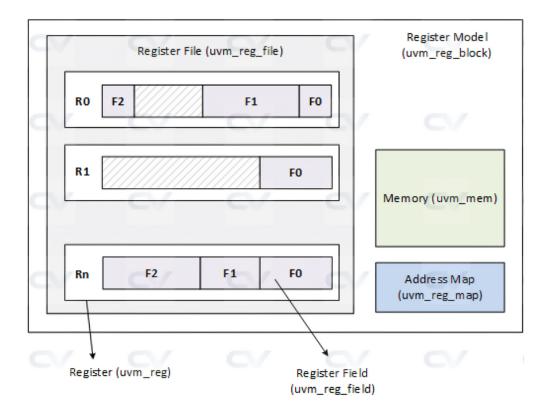

Figure 3.4 UVM Register Abstraction Layer – Register Model Structure. Source: [18]

Communication via backdoor is done via simulator database. The value of signal is written or read based on its name in the design. Transactions that use backdoor to access registers and memories are executed instantaneously and do not consume any clock cycles (i.e. simulation time). The drawback of backdoor access is the absence of a control logic, that is typically active during "normal" operations involving bus communication.

In order to utilize backdoor access the user must specify the hardware description language (HDL) path for a desired register or memory.

Information about frontdoor and backdoor is taken from [19].

### 3.2.2 UVM RAL – Register Model Structure

"Register Model" is the main block of the register abstraction layer. It contains everything that is needed to successfully create testbench that would be capable of verifying registers and memories within a digital design.

Since typical digital design can consist of hundreds of registers and memories, the task of manually creating a register model can be time-consuming. That is why it is a common practice to use some kind of script or software, that takes the register specification as an input, for example in IP-XACT XML format, and generates corresponding register model in SystemVerilog language using RAL base classes [18].

Typical structure of a UVM RAL register model is depicted in figure 3.4. In the following sections each component of the register model will be described in detail.

### 3.2.2.1 uvm\_reg

This base class mimics the actual register in the design. User can extend uvm\_reg class to create and configure their own register, so that it would correspond (functionality wise) to the register in the design. The user can read() from or write() the specified value in the register.

Each UVM RAL register contains so-called desired and mirrored values:

Desired value is the value, that we want register to have. We can set and get this value using set() and get() methods. We can also update() the corresponding register in the DUT to have this desired value.

Mirrored value is the value, that should be in the actual register in the DUT. If implicit (auto) prediction is turned on, each time a read() or write() transaction occurs, corresponding register is updated with a value from the DUT. Mirrored values can be modified manually with predict() method. Method called mirror() updates, and optionally compares, the current mirrored value in the register model with the actual register value from the DUT. Current mirrored value can be read using get\_mirrored\_value() method.

More about register model prediction modes is described in section 3.2.3.

Registers can have multiple "fields", i.e. blocks of continuous bits. Each field represents a certain feature in the design and every field can have different access policies. For example one 32 bits register can have first 16 bits ([31:16]) with read-write access, while the remaining 16 bits ([15:0]) can be read-only. In the RAL fields are represented by uvm\_reg\_field base class. Relevant uvm\_reg\_methods are described in detail below.

### ■ Code listing 3.1 uvm\_reg::new()

Creates a new instance of RAL register with a specified name, total number of bits and functional coverage models.

#### ■ Code listing 3.2 uvm\_reg::configure()

Configures the existing RAL register. Specify the parent register block of this register, parent register file (optional) and register's HDL path.

### Code listing 3.3 uvm\_reg::needs\_update()

```

virtual function bit needs_update()

```

Returns '1' if desired and mirrored values of the fields in this registers are not equal.

### Code listing 3.4 uvm\_reg::write()

Writes the specified value in this register using specified path. Path can have values UVM\_FRONTDOOR or UVM\_BACKDOOR. Both of these paths respect access policies of the registers, i.e. writing to a read-only register will not change the register value.

#### Code listing 3.5 uvm\_reg::read()

Reads the current register and stores its value in value variable using specified path. Path can have values UVM\_FRONTDOOR or UVM\_BACKDOOR. Both of these paths respect access policies of the registers, i.e. reading read-clear register will set this register value to zeroes.

#### **■ Code listing 3.6** uvm\_reg::poke()

Deposits the specified value into this register using its HDL path (backdoor access). Poke method does not respect access policies of the registers, i.e. read-only registers can be written to.

### Code listing 3.7 uvm\_reg::peek()

Reads current register and stores its value in value variable using its HDL path (backdoor access). Peek method does not respect access policies of the registers, i.e. read-clear register will not change its value after peek() method is executed.

### Code listing 3.8 uvm\_reg::update()

Updates the DUT register value with its desired RAL value. It can be done using frontdoor (write()) or backdoor (poke()) access.

#### **Code listing 3.9** uvm\_reg::mirror()

Updates and optionally compares register's mirrored value with an actual value from the DUT. Using arguments UVM\_NO\_CHECK and UVM\_CHECK current mirrored value can be compared with an actual DUT register value and an error message can be displayed in case of these values not being equal. This method can be executed with frontdoor (write()) or backdoor (poke()) accesses.

#### **Code listing 3.10** uvm\_reg::predict()

Manually changes the mirrored value of this register. Returns TRUE if the prediction was successful for every field in the register.

All information about uvm\_reg class is taken from [18] and [20].

### 3.2.2.2 uvm\_reg\_field

This class represents individual bits in a register. They can be configured to have specified size, least significant bit (LSB), reset value and access policy using configure() method. RAL supports wide variety of access policies as shown in the table 3.1 (information about them is taken from [21]).

Relevant uvm\_reg\_field methods are described in detail below.

#### Code listing 3.11 uvm\_reg\_field::new()

```

function new ( string name = "uvm_reg_field" )

```

Creates a new field instance. This method should not be called directly, instead, uvm\_reg\_field::type\_id::create() factory method should be invoked.

### Code listing 3.12 uvm\_reg\_field::configure()

$\blacksquare$  Table 3.1 Register field access policies supported by UVM RAL

| Access policy                     | Description                                                                                                                               |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RO (Read-only)                    | Writing has no effect, reading returns current register value                                                                             |

| RW (Read-write)                   | Writing updates current register value, reading returns current register value                                                            |

| RC (Read-clear)                   | Writing has no effect, reading clears all register bits                                                                                   |

| RS (Read-set)                     | Writing has no effect, reading sets all register bits                                                                                     |

| WRC (Write-read-clear)            | Writing updates current register value, reading clears all register bits                                                                  |

| WRS (Write-read-set)              | Writing updates current register value, reading sets all register bits                                                                    |

| WC (Write-clear)                  | Writing clears all register bits, reading returns current register value                                                                  |

| WS (Write-set)                    | Writing sets all register bits, reading returns current register value                                                                    |

| WSRC                              | Writing sets all register bits, reading clears all register                                                                               |

| (Write-set-read-clear)            | bits                                                                                                                                      |

| WCRS                              | Writing clears all register bits, reading sets all register                                                                               |

| (Write-clear-read-set)            | bits                                                                                                                                      |

| W1C (Write-1-clear)               | Writing '1' clears matching bit, reading returns current register value                                                                   |

| W1S (Write-1-set)                 | Writing '1' sets matching bit, reading returns current register value                                                                     |

| W1T (Write-1-toggle)              | Writing '1' toggles matching bit, reading returns<br>current register value                                                               |

| W0C (Write-0-clear)               | Writing '0' clears matching bit, reading returns current register value                                                                   |

| W0S (Write-0-set)                 | Writing '0' sets matching bit, reading returns current register value                                                                     |

| W0T (Write-0-toggle)              | Writing '0' toggles matching bit, reading returns<br>current register value                                                               |

| W1SRC<br>(Write-1-set-read-clear) | Writing '1' sets matching bit, reading clears all register bits                                                                           |

| W1CRS                             | Writing '1' clears matching bit, reading sets all register                                                                                |

| (Write-1-clear-read-set)          | bits                                                                                                                                      |

| W0SRC                             | Writing '0' sets matching bit, reading clears all register                                                                                |

| (Write-0-set-read-clear)          | bits                                                                                                                                      |

| WOCRS                             | Writing '0' clears matching bit, reading sets all register                                                                                |

| (Write-0-clear-read-set)          | bits                                                                                                                                      |

| WO (Write-only)                   | Writing updates current register value, reading results in error                                                                          |

| WOC (Write-only-clear)            | Writing clears all register bits, reading results in error                                                                                |

| WOS (Write-only-set)              | Writing sets all register bits, reading results in error                                                                                  |

| W1 (Write-once)                   | First write operation updates current register value,<br>other write operations have no effect, reading returns<br>current register value |

| WO1 (Write-only-once)             | First write operation updates current register value, other write operations have no effect, reading results in error                     |

Configures the instance of current register field. Specify the parent register of this field, field size in bits, its position of the LSB relative to the LSB of the register, field's access policy, its reset value, whether the field is actually reset, whether the field may be randomized and whether the field is the only one to occupy a byte lane.

Other relevant methods have the same structure as the uvm\_reg ones.

### 3.2.2.3 uvm\_reg\_file

This class encapsulates a collection of registers and other register files. Relevant methods include:

Code listing 3.13 uvm\_reg\_file::new()

```

function new ( string name = "" )

```

Creates a new instance of a register file with a specified name.

Code listing 3.14 uvm\_reg\_file::configure()

Configures this register file. Specify the parent register block and parent register file. If current register file is instantiated in a register block, regfile\_parent should be set to NULL. If current register file is instantiated in another register file, blk\_parent should be set to that register file's parent block and regfile\_parent should be set to that register file. We can also specify the register file's HDL path [22].

### 3.2.2.4 uvm\_mem

This class represents memory block in the actual design. It can be extended and configured to have specified memory depth, width and access policy. Supported access policies are read-write for RAM and read-only for ROM memories.

Just like with registers, RAL memories can be read and written with read()/peek() and write()/poke() methods. These methods are structurally the same as in the uvm\_reg base class with the exception of offset parameter, which can be used to read/write data from/to specified offset in the memory.

Unlike registers, however, memories do not have desired and mirrored values, since memories are usually much larger than any register file and duplicating all memory words will be counterproductive.

In case of memories, we are able to use burst\_read() and burst\_write() methods. With these methods we can read and write multiple memory words at once, without the need to execute read() and write() on every individual word.

All relevant methods are described below.

#### Code listing 3.15 uvm\_mem::new()

Creates new RAL memory with a specified name. Parameter size specifies the number of memory locations (memory depth), while n\_bits is a number of bits in every memory location (memory width). Access policy and functional coverage models can also be specified.

### ■ Code listing 3.16 uvm\_mem::configure()

Configures current instance of RAL memory with specified parent register block and HDL path.

#### Code listing 3.17 uvm\_mem::burst\_write()

Writes the values from the value dynamic array into the memory starting at the specified offset. Frontdoor (UVM\_FRONTDOOR) or backdoor (UVM\_BACKDOOR) accesses can be used. This method respects the access policy of a memory, i.e. values inside of a ROM memory will not be overwritten.

### Code listing 3.18 uvm\_mem::burst\_read()

Reads and stores data from the memory starting at the specified offset into the value[] dynamic array. The number of read memory locations is defined by the size of value[] array.

Frontdoor  $(UVM\_FRONTDOOR)$  or backdoor  $(UVM\_BACKDOOR)$  accesses can be used. This method respects the access policy of a memory.

All information about uvm\_mem base class is taken from [23].

### 3.2.2.5 uvm\_reg\_map

Every register and memory block is mapped to specific addresses in the register block. This uvm\_reg\_map base class represents an address map, i.e. a collection of registers and memories that are accessible via specific physical interface. Register block can have multiple address maps, each corresponding to a physical interface that is connected to a DUT.

Registers and memories can be added to an address map with add\_reg() and add\_mem() methods respectively. By using these methods we can specify register/memory access policy and offset in current address map. Valid policies are read-write, read-only and write-only. These policies refer to the registers' or memories' accessibility via this address map, not the accessibility of registers and memories themselves.

For example, register can have read-write policy, while not begin accessible for writing via this specific register map. That same register can be mapped to another address map with read-write accessibility and in that case it can be successfully written to.

Address map of another register sub-block can be added to current register block at a specified offset with a add\_submap() method.

Before executing any read and write transaction on registers and memories a sequencer and an adapter must be specified for current address map. It can be achieved using set\_sequencer() method.

All relevant uvmr\_reg\_map methods are described below.

#### Code listing 3.19 uvm\_reg\_map::new()

```

function new ( string name = "uvm_reg_map" )

```

Creates a new instance of register address map with a specified name.

#### Code listing 3.20 uvm\_reg\_map::configure()

Configures the current address map of parent register block. Every register, memory or subblock will be offset relative to the base address (base\_addr) of this address map. Byte width of the bus, on which this map is used, can be specified with n\_bytes parameter. Parameter byte\_addressing specifies whether or not consecutive memory addresses refer to the data that is one byte apart.

### **Code listing 3.21** $uvm_reg_map::add_reg()$