# Assignment of bachelor's thesis

Design of multi-channel DMA controller with interrupt and flexible descriptor configuration Student: Olha Harielina Supervisor: Ing. Ondrej Ille Study program: Informatics Branch / specialization: **Computer engineering** Department: Department of Digital Design until the end of summer semester 2024/2025

# Instructions

Validity:

Research open source implementations of DMA controllers and compare the typical feature sets of generic DMA controllers as well as the capabilities of DMA engines in common microcontrollers.

Propose DMA controller block diagram for modular implementation and configuration of the IP e.g., number of channels, presence of hardware interfaces or interrupts per channel, descriptor storage size etc.

Define structure of DMA descriptor configuration data. Define DMA descriptors mapping to particular system interfaces of choice e.g. AHB, AXI or RISC-V LSU.

Implement the DMA controller in SystemVerilog RTL code supporting both ASIC and FPGA target technology.

Demonstrate DMA controller functionality on a FPGA board or in RTL simulations.

Bachelor's thesis

# DESIGN OF MULTI-CHANNEL DMA CONTROLLER WITH INTERRUPT AND FLEXIBLE DESCRIPTOR CONFIGURATION

Olha Harielina

Faculty of Information Technology Department of Digital Design Supervisor: Ing. Ondrej Ille January 11, 2024

Czech Technical University in Prague Faculty of Information Technology © 2024 Olba Harialina All rights reserved

© 2024 Olha Harielina. All rights reserved.

This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

Citation of this thesis: Harielina Olha. *Design of multi-channel DMA controller with interrupt and flexible descriptor configuration*. Bachelor's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2024.

# Contents

| Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | vi                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | vii                                                                        |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | viii                                                                       |

| Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ix                                                                         |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                          |

| 1       State of the art         1.1       System Bus         1.2       Basics of DMAC         1.3       Address modification         1.3.1       Increasing and Decreasing mode         1.3.2       Wrap mode         1.3.3       Fixed mode         1.3.3       Fixed mode         1.4       Scatter-Gather         1.5       Transfer modes         1.5.1       Cycle stealing mode         1.5.2       Burst mode         1.5.3       Interleaving/Transparent mode         1.6       Data Transfer         1.6.1       Beat transfer         1.6.2       Burst transfer         1.6.3       Block transfer and Repeat mode         1.6.4       Transaction transfer         1.7       Channels         1.8       Interrupts and triggers         1.9       Arbitration         1.10       Control logic         1.10.1       FSM         1.10.2       Microprogrammed controller | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                       |

| 2 Analysis         2.1 FPGA vs ASIC         2.2 Set of features         2.3 Controller         2.4 Datapath         2.4.1 Channel Descriptor         2.4.2 Buffer         2.4.3 Trigger Register         2.4.4 Arbiter         2.4.5 Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19          19          19          20          20          20          20 |

# Contents

| 3  | Des   | lign                                | <b>21</b>       |

|----|-------|-------------------------------------|-----------------|

|    | 3.1   | HDL                                 | 21              |

|    | 3.2   | Design tools                        | 22              |

|    | 3.3   | Datapath                            | 22              |

|    |       | 3.3.1 Register map                  | 22              |

|    |       | 3.3.2 Channels descriptor           | 23              |

|    |       | 3.3.3 Arbiter                       | 24              |

|    |       | 3.3.4 Trigger register              | 25              |

|    |       | 3.3.5 Descriptor buffer and address | 25              |

|    | 3.4   | Controller                          | 25              |

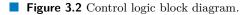

|    | 3.5   | TSDMA                               | 26              |

| 4  | Imp   | Dementation                         | 27              |

| -  | 4.1   | Register map                        | 27              |

|    | 1.1   | 4.1.1 Arbiter                       | $\frac{2}{28}$  |

|    | 4.2   | Trigger register                    | $\frac{-0}{29}$ |

|    | 4.3   | Descriptor                          | $29^{-5}$       |

|    |       |                                     |                 |

| 5  | Test  |                                     | <b>31</b>       |

|    | 5.1   | Basic functionality tests           | 31              |

|    | 5.2   | UVM tests                           | 32              |

|    |       | 5.2.1 Structure of tests and TB     | 32              |

|    |       | 5.2.2 Observed bugs                 | 33              |

| C  | nclu  | ision                               | 35              |

| CC |       | Future work                         | 35              |

|    | 0.0   |                                     | 00              |

| Α  | Reg   | rister map                          | 36              |

| в  | Des   | criptor map                         | <b>42</b>       |

| С  | Inte  | erface                              | 44              |

|    |       |                                     |                 |

| Co | oncer | nts of the attachment               | <b>46</b>       |

# List of Figures

| 1.1           | System bus connecting elements of computer                                          | 3 |

|---------------|-------------------------------------------------------------------------------------|---|

| 1.2           | Block diagram of simple DMAC                                                        | 1 |

| 1.3           | Memory organization                                                                 | 3 |

| 1.4           | Address values for wrap16 addressing mode example                                   | 3 |

| 1.5           | Addressing modes examples [2]                                                       | 7 |

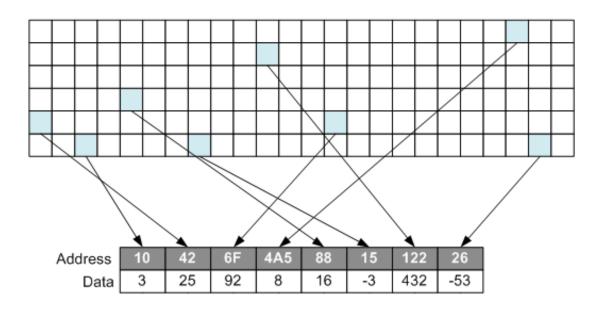

| 1.6           | Scatter-Gather principle [3].                                                       | 3 |

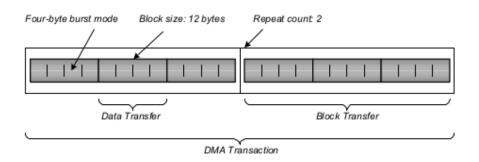

| 1.7           | Beat, block and transaction DMA transfers [2]                                       | ) |

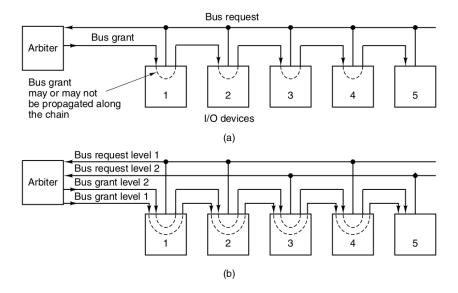

| 1.8           | (a) A centralized one-level bus arbiter using daisy chaining. (b) The same arbiter, |   |

|               | but with two levels $[5, p. 197]$                                                   | 2 |

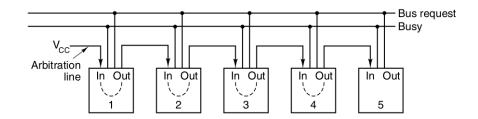

| 1.9           | Distributed bus arbitration [5, p. 198]                                             | 2 |

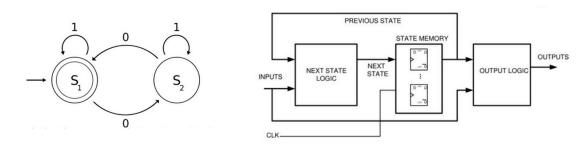

| 1.10          | FSM with two states, where valid input are binary strings with even number of       |   |

|               | zeros                                                                               | 3 |

|               | Block design of Mealy FSM 13                                                        |   |

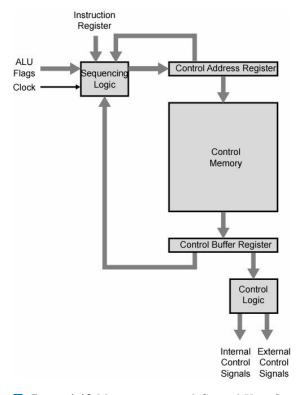

| 1.12          | Microprogrammed Control Unit Organization [7]                                       | 1 |

| 2.4           |                                                                                     |   |

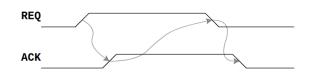

| 2.1           | Four-phase handshake                                                                | ) |

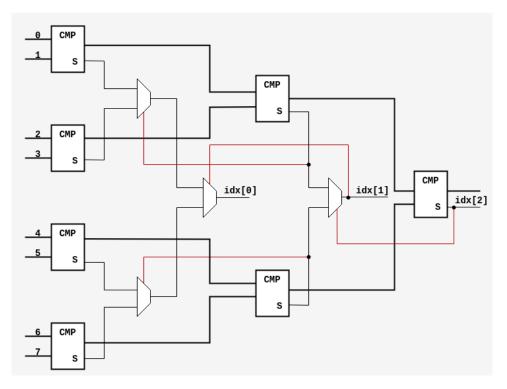

| 3.1           | Block scheme of priority comparators for 8 channels                                 | 1 |

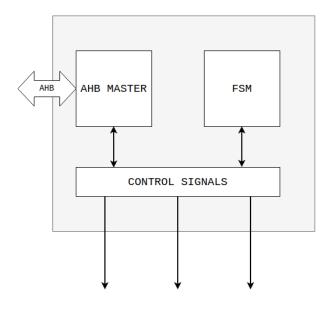

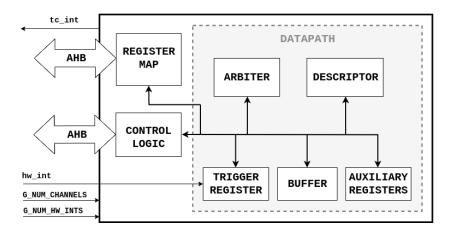

| 3.2           | Control logic block diagram                                                         |   |

| 3.3           | TSDMA block diagram                                                                 |   |

|               |                                                                                     |   |

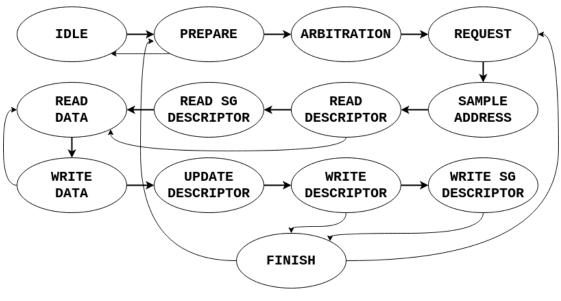

| 4.1           | TSDMA controller's states    28                                                     | 3 |

| 5.1           | TB block diagram                                                                    | 2 |

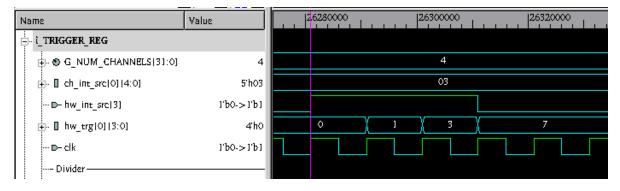

| 5.2           | $hw\_trg$ capturing multiple interrupts on one impulse                              | 3 |

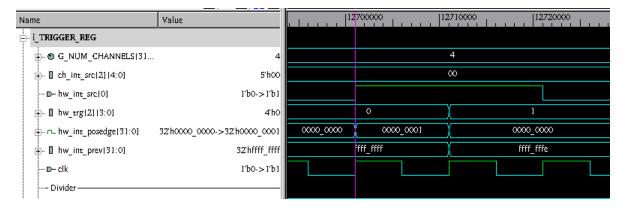

| 5.3           | $hw\_trg$ capturing only positive edge of interrupt                                 | 3 |

| 5.4           | $sw\_trg\_clr$ sets at 1 lower 4 bits and sticks to value                           | 1 |

| 5.5           | $sw\_trg$ has correct values                                                        | 1 |

| C.1           | Ports                                                                               | 1 |

| 0.1           | Generics                                                                            |   |

| $\bigcirc$ .4 | Quinting                                                                            | r |

# List of Tables

2.1 Features of DMAC in STM32Fxx, Atmel AVR 8-bit and PIC24/PIC33 IC's . . . 17

List of code listings

List of code listings

This thesis is based on designing a part of a new product being developed by Tropic Square s. r. o, who I would like to thank first of all for providing me with the topic with future practical application. I would like to thank the entire team for their support and guidance during my work, especially Ing. Ondrej Ille for supervising this thesis and giving me countless advice during consultations. I would also like to thank Dr.-Ing. Martin Novotný for guidelines and recommendations regarding this work. Not least of all I would like to thank my father for immense help during my studies and my mother for support and providing an opportunity to study abroad.

# Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis. I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. In accordance with Section 2373(2) of Act No. 89/2012 Coll., the Civil Code, as amended, I hereby grant a non-exclusive authorization (licence) to utilize this thesis, including all computer programs that are part of it or attached to it and all documentation thereof (hereinafter collectively referred to as the "Work"), to any and all persons who wish to use the Work. Such persons are entitled to use the Work in any manner that does not diminish the value of the Work and for any purpose (including use for profit). This authorisation is unlimited in time, territory and quantity.

In Prague on January 11, 2024

# Abstract

This thesis proposes a versatile multichannel DMA controller with flexible channel and block configuration. It describes the basic and modern functionality of these controllers. It also compares several DMA engines to pick the optimal combination of frequently used features to make sure the design stays simple yet offers a wide enough range of configurations. The DMA controller was written in SystemVerilog targeting ASIC technology and supporting FPGA application as well. The module was tested in RTL simulations using mostly UVM test benches. It is capable of handling up to 32 concurrent data transfers and each transfer size can be configured for up to  $2^{32}$ words at once. The proposed design finds an application in an IP core by Tropic Square s.r.o., and thanks to generic variables and its flexibility the controller is not limited to one application. Due to complete hardware implementation, it offers data transferring at high speed without the use of additional cycles for any instructions to be processed.

**Keywords** multichannel DMA, scatter-gather, generic design, digital design, AHB-Lite, channel arbitration

# Abstrakt

Tato práce navrhuje univerzální vícekanálový řadič DMA s flexibilní konfigurací kanálů a modulu. Popisuje základní a moderní funkce těchto řadičů. Porovnává také několik DMA enginů s cílem vybrat optimální kombinaci s často používanými funkcemi, aby návrh zůstal jednoduchý a přitom nabízel dostatečně širokou škálu konfigurací. Řadič DMA byl napsán v jazyce SystemVerilog se zaměřením na technologii ASIC a podporuje i použití v FPGA. Modul byl testován v simulacích RTL převážně pomocí testů UVM. Je schopen zpracovat až 32 souběžných přenosů dat a každou velikost přenosu lze nakonfigurovat až pro 2<sup>32</sup> slov najednou. Navržený design našel uplatnění v IP jádře od Tropic Square s.r.o. a díky generickým proměnným a své flexibilitě není řadič omezen na jedno konkrétní použití. Díky své kompletně hardwarové implementaci nabízí přenos dat vysokou rychlostí bez použití dalších cyklů pro zpracování případných instrukcí.

Klíčová slova vícekanálové DMA, scatter-gather, obecný návrh, digitální návrh, AHB-Lite, arbitráž kanálů

# Abbreviations

| AGEG                 |                                         |  |

|----------------------|-----------------------------------------|--|

| ASIC                 | Application Specific Integrated Circuit |  |

| AHB                  | Advanced High-performance Bus           |  |

| APB                  | Advanced Peripheral Bus                 |  |

| AXI                  | Advanced Extensible Interface           |  |

| CPU                  | Central Processing                      |  |

| DMA                  | Direct Memory Access                    |  |

| DMAC                 | Direct Memory Access Controller         |  |

| FPGA                 | Field Programmable Gate Array           |  |

| $\mathbf{FSM}$       | Finite State Machine                    |  |

| HDL                  | Hardware Description Language           |  |

| HW                   | Hardware                                |  |

| I/O                  | Input/Output                            |  |

| IC                   | Integrated Circuit                      |  |

| IP                   | Intellectual Property                   |  |

| M2M                  | Memory-to-Memory                        |  |

| M2P                  | Memory-to-Peripheral                    |  |

| P2M                  | Peripheral-to-Memory                    |  |

| P2P                  | Peripheral-to-Peripheral                |  |

| $\mathbf{PC}$        | Personal Computer                       |  |

| $\operatorname{RTL}$ | Register Transfer Level                 |  |

| SV                   | SystemVerilog                           |  |

| SW                   | Software                                |  |

| TB                   | Test-Bench                              |  |

| TSDMA                | Tropic Square DMA                       |  |

| UVM                  |                                         |  |

| VHDL                 | VHSIC Hardware Description Language     |  |

| VHSIC                | Very High Speed Integrated Circuit      |  |

# Introduction

The modern world heavily relies on computers, yet most users are unaware of the sophisticated data exchanges that occur within these systems. When we think of computers, the Personal Computer (PC) typically comes to mind, so the next example is using it. Even before users begin actively using the PC, it is already engaged in various data transfers, such as tracking mouse movements, registering keyboard inputs, and displaying static images. These transfers are continuously taking place in the computer's memory, often without the user's knowledge. In systems other than PCs, the process is similar – various components within the system constantly communicate with each other, exchanging vital data. What many fail to recognize is the significant demand on the Central Processing Unit (CPU) to handle these transfers while simultaneously juggling other tasks. Moreover, crucial data transfers can interrupt ongoing activities, potentially hindering task completion or rendering the computer unresponsive, despite the user's attempts to interact through clicks and commands.

Data transfer is a process of relocating data from one place in memory to another. There are various modes for it and they can be categorized into two groups: those controlled by the CPU and those that operate independently. A brief overview of their main difference is the following.

The first group – managed by the CPU – already gives a hint that the main processor's active participation in data transfer is required. Two similar modes only differ in the way of triggering a transfer. Either the processor keeps checking on the Input/Output (I/O) device for availability and then proceeds to complete the transfer or I/O device sends a request to CPU when it is ready. In the latter case, the peripheral has to wait until the CPU saves the context of its current task and switches to data transfer. In both modes processing unit postpones any activity and fully commits itself to transferring the data.

The second group consists of Direct Memory Access (DMA) mode that does not need the CPU to intervene in data transfers at all. A separate controller – DMA controller (DMAC) – is connected directly to memories through the system interface. All data necessary for a transfer is stored in DMAC's configuration registers. Since the CPU neither initiates nor performs the transfer – it can complete more important and complicated tasks.

When it comes to chip design – choosing a better option between these modes should not seem complicated. DMA undoubtedly overcomes modes where transfers are controlled and run by the CPU. To sum up, DMAC is a control unit that speeds up data transfers in computer systems and enhances the performance of the entire system by enabling DMA mode. Nowadays they play an inevitable role in microchips by handling most of the data transfers without loading the CPU.

The particular DMA controller, that is being created according to the assignment and from now on referred to as TSDMA (Tropic Square DMA), is intended to be placed in a microcontroller. The chip will be designed by Tropic Square s.r.o. – company developing in the niche of chip design. Their goal is to produce products that are open-source and can be utilized in

#### Introduction

crypto wallets, with a focus on security and resilience against vulnerabilities such as Meltdown and Spectre, as well as other micro-architectural attacks. The decision to create a new DMAC specifically for the company, rather than purchasing from a third party, was made after careful consideration of various factors. The most significant factor is the avoidance of signing a nondisclosure agreement with the IP core provider, which would prohibit the ability to expose the code to the public.

By designing the DMAC in-house, the company will have greater control over its verification process, allowing any potential issues to be identified and addressed before they become major problems. Other reasons are additional expenses and lack or excess of functions and flexibility of controller, which most likely could be integrated into chips with equivalent configuration only.

Over the years numerous examples of DMA controllers were introduced and there is a difference in the purpose they serve and, hence, the set of features and configurability. Despite many of them being quite general-purpose and suitable for use by different systems, having your own DMAC designed specifically for the case yet with a flexible interface is a good solution when it comes to open-sourceness and narrow use. Currently, TSDMA is meant to fulfill the requirements of one exact product only, however, in the future, it has the potential to be adapted and utilized by others according to their specific needs.

In this thesis, we will commit to the analysis and review of a DMAC architecture, a brief overview of existing DMACs, and the design of such a controller. Following synthesis, tests, and verification of the circuit will not be fully covered in the text since it reaches out of the main goals of the thesis, test-benches will be provided by the company's verification engineers.

# Goals of the thesis

The main goal of the thesis is to design and implement a generic, configurable DMAC for a new product by Tropic Square s.r.o. company. Next, to investigate the topic and select the most useful aspects among open-source implementations of DMA controllers to resolve in the circuit. As the given microchip aims to be as open-source, small, and efficient as possible, one of the solutions is to devise TSDMA with the most appropriate set of features and configurations to fulfill the goals of the chip.

TSDMA shall support all kinds of data transactions, e.g. Memory-to-Memory (M2M), Peripheral-to-Memory (P2M), Memory-to-Peripheral (M2P), and Peripheral-to-Peripheral (P2P) through a particular type of system interface. It also should be configurable in terms of a number of channels and hardware interrupts by having generic variables. The implementation shall contain all key features of DMA controllers and at the same time not be congested by excessive traits. Lastly, design should respect future implementation not only in Field Programmable Gate Array (FPGA) but also in Application Specific Integrated Circuit (ASIC), hence, it should minimize the use of area on the chip.

This thesis will be organized in the following chapters:

- **Chapter State of the art** covers the fundamental definition and theoretical background of computer structure and architecture related to the topic. Within this chapter, DMA controllers are introduced, and both their basic and advanced features are thoroughly described.

- **Chapter Analysis** This section of the thesis is devoted to evaluating and analyzing publicly available open-source DMACs for microcontrollers with configurations similar to the aimed chip for DMAC integration.

- Chapter Design guides the reader through every step of the design of TSDMA block.

- Chapter Testing explains the main points of TSDMA testing using basic and UVM tests.

- **Chapter Conclusion** contains results of the work done in this thesis and a description of possible future improvements.

# Chapter 1 State of the art

This chapter provides theoretical background for DMA controllers, their basic features and operation principles are described in Section 1.2. Advanced functionality and configurations are described in following sections. Related definitions and terms that are used in context of DMAC will also be introduced below. Following text should help with better understanding of context of the thesis and briefly explain all necessary terms used for following analysis and design of DMAC.

# 1.1 System Bus

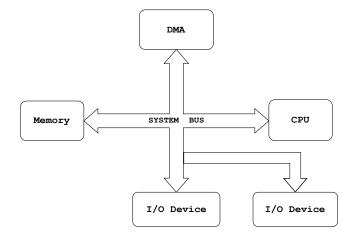

For better understanding of integrating inside the system and communication between the components we need to introduce system bus shown at Figure 1.1.

▶ Definition 1.1 (System bus). A bus is a set of wires that acts as a shared but common datapath to connect multiple subsystems within the system. A system bus provides a communication path for the data and control signals moving between the major components of the computer system.

**Figure 1.1** System bus connecting elements of computer.

#### Basics of DMAC

The system bus works by combining the functions of the three main buses: namely, the data, address and control buses. Each of the three buses has its separate characteristics and responsibilities. The system bus combines the functions of the three main buses, which are as follows:

- The control bus carries the control, timing and coordination signals to manage the various functions across the system.

- The address bus is used to specify memory locations for the data being transferred.

- The data bus, which is a bidirectional path, carries the actual data between the processor, the memory, the DMA controller and the peripherals.

A bus can be point-to-point or a common pathway, however only one device at a time may use the bus. Often devices are categorized as *masters*, the ones who initiate transfers, and *slaves* – responding to these transfers. Operation of multiple devices on a bus is solved with bus protocols [1, p. 179-182].

# **1.2** Basics of DMAC

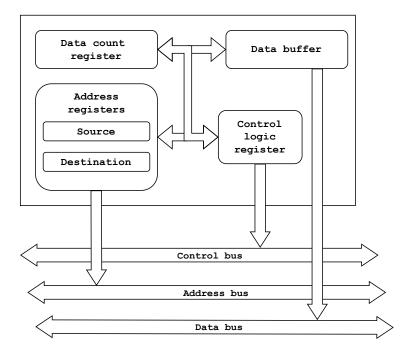

#### **Figure 1.2** Block diagram of simple DMAC

To understand structure of DMA controller and how this memory access mode operates we will look at the most simple controller demonstrated at Figure 1.2. *Data count* register is responsible for amount of transferred data. It is initially loaded with total amount of data to transfer and serve as watchdog. With each transfer it decreases number of them left to the end of transaction. When the value reaches zero, *control logic* generates interrupt to notify other

#### Address modification

components in system about finished transaction. *Address* registers store source and destination addresses of data to be transferred. When no configuration is available, their value is being increased inversely to *data count*. Last register is *control logic*. It plays the role of a DMAC's brain, coordinating internal events and operations. Besides controlling inner state of DMAC this register generates output signals for communication on system bus and processes input signals. DMA data transfer is executed in following way:

- Software(SW) configures necessary registers as source and destination addresses, number of data blocks to transfer.

- DMAC gets triggered, reads data from source address into local buffer, then writes buffered data to destination address.

- DMAC repeats previous step until size of transferred data equals number of data blocks set by SW.

- DMAC sends interrupt after transfer was completed.

Entire transfer then happens without CPU intervention and significantly increases performance of entire system by doing so.

Such module needs to be configured before every separate data transfer and it sends DMA request as far as it's data count register does not equal zero. That can work with minor systems and not so loaded transfer traffic where both source and destination are memory locations.

From these simple controllers to modern DMACs there is a huge step up in their configurability and capability. Multiple channels and transfer trigger sources, different kinds of memory to transfer from and to, bigger choice of address modification and much more.

# **1.3** Address modification

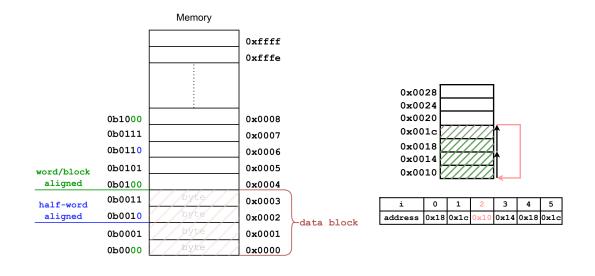

Addresses in memory point to separate blocks of data which could be of different size. For convenience, we will consider 32-bit memory organization. Each data block contains one word – 32 bits – of information stored. To avoid various problems including creating disorder in memory – addresses should be word-aligned as shown at Figure 1.3. One address holds 1 byte (or 8 bits) and to be 32 bits aligned it should be divisible by 4.

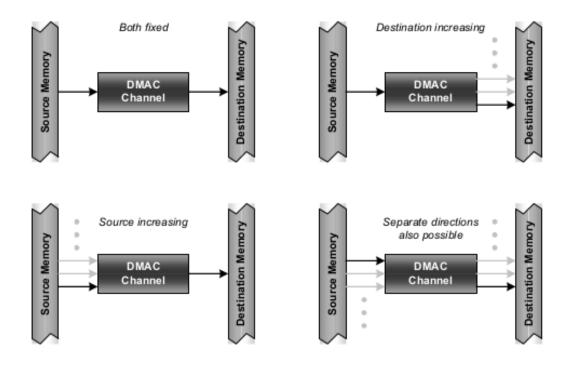

Additional detailed information and clarification regarding memory organization and addressing can be found in [1, p. 186-189]. Some of the possible configurations regarding address modification within data transfer can be seen at the end of this section on Figure 1.5.

# **1.3.1** Increasing and Decreasing mode

At minimalistic DMA controllers source and destination addresses are being changed inversely to data count. At the time it was the only possible mode and is called increasing mode. When a chunk of data is stored in the main memory, it is saved sequentially, block by block from lower to higher address. Thus to read or write such data in memory the knowledge of the starting address, width of block, and number of blocks is sufficient. The source or destination address shall be increased after each read or written block by its size divided by 8 - in this case, it is 32 : 8 = 4. In other words, we add the number of bytes in the data block after each operation on a given address.

In various systems, data is stored starting from the end address. Provided that information increasing mode should be reversed. Operation of address increment turns into decrement and, hence, increasing mode becomes decreasing. In decreasing mode size of one block in bytes is subtracted from the address.

**Figure 1.3** Memory organization

**Figure 1.4** Address values for wrap16 addressing mode example.

# 1.3.2 Wrap mode

In a world full of PCs and other computers using I/O devices – it became unavoidable to perform data transfers with peripherals on either side. The main difference between data in main memory and data in peripherals is the speed of data changing and limited space in the latter. Usually, storage space in peripherals is restricted to one block size or buffer with a small amount of data blocks that could be stored there.

From a peripheral point of view, it is possible to implement buffers in different ways. The main distinction is whether it is a circular buffer or a (multi-byte) shift register. In a circular buffer, it iterates through addresses and wraps back to the starting address after reaching the end of the buffer. Shift register shifts its content and writes to and reads from one point at memory – one address.

Using the wrap mode for a circular buffer is a practical choice. It functions similarly to the increasing mode, with one variation. Instead of simply increasing the address, the last address will have the same value as the starting address, effectively wrapping back to the beginning when it reaches the end of the memory block (Figure 1.4). This mode is usually used with a number of bytes in its name, according to the size of a memory block.

For example, wrap32 wraps on addresses divisible by 32. A buffer with such size contains 8 words – 8 data blocks. Iterating through memory addresses for a 16-bit sector of data would look like shown in Figure 1.4.

You can observe the way addresses in the DMAC's configuration registers will circulate in closed memory space and not overflow out of buffer bounds. In a scenario where the size of the buffer is one data block, there is a more elegant solution in the following part.

### 1.3.3 Fixed mode

Specific case of peripheral buffers can lead to another addressing mode in data transfers. When buffer size is one data block there is no need to change the address since every time read or write will be executed at the same place in peripheral memory. Thus address in fixed mode remains unchanged during the entire data transaction. This mode can be used for different cases such as copying data from one data block to multiple locations in memory or expanding the value.

**Figure 1.5** Addressing modes examples [2].

# **1.4** Scatter-Gather

Scatter-Gather represents an advanced method of data handling within computer systems. Rather than using a linear data transfer approach from a single source to a single destination, scattergather operates by efficiently gathering data from multiple distributed locations in memory or scattering it across various destinations.

This technique is highly beneficial in cases where data exists non-contiguously across separate memory segments or when the processing of multiple data streams is required without disrupting CPU operations. By allowing the DMA controller to access and combine scattered data blocks into a single, uninterrupted stream, this approach reduces overhead and greatly improves data transfer efficiency. This functionality is especially valuable in systems with disparate memory layouts or fragmented data, as it allows for one channel to gather data in a continuous block and other channels to utilize it for various operations at a later time.

The utilization of Scatter-Gather is crucial in storage systems, particularly in the management of file systems or databases. This technique handles the distribution of data among different segments in memory. In multimedia processing, Scatter-Gather plays a key role in the efficient handling and transmission of multimedia data streams, such as audio, video, or graphics, which may be located in various memory locations. Ultimately, its implementation leads to improved data transfer operations and provides an essential approach for managing complex computing environments with non-linear data.

# **1.5** Transfer modes

DMA does not require CPU intervention in data transfer, but this does not necessarily mean that the CPU can operate completely independently. Whenever data needs to be transferred, the system bus (see Definition 1.1) is actively used, which restricts the main processor's ability

**Figure 1.6** Scatter-Gather principle [3].

to execute tasks that rely on bus communication. This means that the CPU may be blocked by DMA if it needs to use the bus. Additionally, DMA offers different transfer modes with varying transfer and bus loading rates. Essentially, these modes determine how long the CPU will be blocked and when it will regain control of the bus. It is difficult to determine which mode is better or worse, as they each have distinct characteristics and are suited for different purposes.

# 1.5.1 Cycle stealing mode

Peripheral devices take some time to prepare or process data in a buffer, hence, it would not be nice for DMAC to block the bus while waiting for data to be ready. DMAC gets control of the bus for one transfer cycle each time data are ready to be transferred. After that CPU takes back ownership of the system and uses it for other tasks until the next chunk of data is prepared. Then this loop continues as far as DMAC's data counter is positive [4].

This method is not the most optimal from DMA's nor CPU's point of view yet it combines reasonable data transfer rate, while still allowing the bus not to be clogged with DMA and let CPU use the bus consistently. Most suitable use for P2M or M2P type of transfers.

## 1.5.2 Burst mode

In *burst mode* entire block, whose size is defined by a number of bytes in the data count register, is being transferred continuously. CPU is being blocked by DMA from having access to the bus during the entire burst of data. Burst mode is advantageous for transferring significant amounts of data as it minimizes the overhead associated with frequent resource acquisition and release. It gives DMA a very high transfer rate since it transfers multiple data at once maximizing utilization of sources without overhead caused by the constant obtaining and releasing of bus and sources. Hence, there is no need to wait for CPU to assign the ownership of the bus for every single data block.

Data transfer's throughput is at its highest in burst mode, however, CPU remains blocked from bus operation for longer periods of time.

### **1.5.3** Interleaving/Transparent mode

*Interleaving*, in some sources *Transparent*, the mode of data transfer is based on using a data bus for transfers only when the CPU completes tasks without the need to access the bus. In other words, DMAC will wait for as long as it can take for the CPU to finish a current task and free the bus. Once the bus is requested by CPU - DMAC stops the transfer and relieves bus ownership until it is free again.

This mode has slowest transfer rate, but is arguably the most efficient from system's point of view, since CPU is not getting blocked by DMA yet transfers are still being completed. It can be used for M2M transfers as they usually do not require high speed or immediate completion.

# **1.6** Data Transfer

Nowadays, as the range of options for transfers and their purposes increase – it is natural that it can be useful to control how much of the total data is needed to be transferred at one trigger impulse. A trigger is a specific signal or event that initiates or activates the start of a data transfer process. It is used as a directive prompting a device or system to start either sending or receiving data. This signal's generation can occur through different methods, including manual input, a preset timing system, or triggered by specific conditions, tailored to the unique demands of the data transfer operation.

# 1.6.1 Beat transfer

Computers can vary in the size of the data block they have, the size of data transfer at once can be as big as the width of the data bus. *Beat* in this text represents the smallest unit of data transferred between components within a system and varies based on the system's data bus width. For instance, in an 8-bit microcontroller, a beat typically corresponds to a byte transfer, while in a 32-bit system, a beat refers to a transfer of 4 bytes due to the wider data bus, reflecting the amount of data moved in a single transfer.

Thus, not to confuse things talking about the smallest unit of transfer regardless of it's size, it is called beat. It takes one transfer cycle and cannot be divided into smaller items.

#### 1.6.2 Burst transfer

*Burst transfer* refers to a method of consecutive transferring blocks of data between components in a system without interruption. It provides moving a sequence of beats in rapid series within a single operation. Burst transfer is often supported directly by bus interfaces. This type of transfer is introduced in multiple bus architectures, e.g. IBM CoreConnect, ARM AHB/APB/AXI architectures, and others, which enable uninterrupted continuous sequence of data transfer cycles.

#### **1.6.3** Block transfer and Repeat mode

*Block transfer* specifies the entire data transfer of a certain amount of data defined by the data count register. Can be divided into burst or beat transfers and be completed in several data transfers triggered by multiple interrupts. It is also possible to configure DMAC to perform an entire block transfer at once.

Size of the block here is restricted by the configuration register, in order to perform bigger transactions a *Repeat mode* was introduced. It allows to perform the same block transaction continuously without reconfiguring DMAC to the same setting several times. A number of repetitions is either given by a number in the corresponding register or is infinite which allows for a continuous and constant stream of data. It is good for constantly renewing data as in video or sound stream.

Channels

### 1.6.4 Transaction transfer

Repetition of the block transfer can come in handy in cases of renewable data in the same memory area. To ease the process of such transfer and its configuration next register that appears in controllers is the repeat counter. It is used to perform the same block transfer several times.

Transaction transfer stands for all operations with data, i.e. performing block transfer number of times defined by repeat counter.

**Figure 1.7** Beat, block and transaction DMA transfers [2].

# **1.7** Channels

Data channels are essential components within a DMA controller, functioning as specialized lanes that streamline data movement without requiring constant intervention from the main processor. These channels operate as dedicated pathways, each assigned with specific tasks for independent data transfer. By utilizing these pathways, the DMA controller can efficiently handle multiple data transfers concurrently. This means it can simultaneously oversee data being transferred from various devices and peripherals, resulting in a faster and more effective process overall.

The number of channels available varies depending on the design of the DMA controller. Some systems may have a small number of channels, while others may offer more, allowing for a higher capacity of simultaneous data transfer tasks. These channels are crucial in enhancing the efficiency of data movement. By enabling multiple data transfers to take place concurrently without taxing the main processor, they significantly contribute to the overall system performance, particularly in tasks involving large amounts of data.

# **1.8** Interrupts and triggers

An interrupt is a crucial signal that is sent from one component of a system or program to the CPU to signify an occurrence of an event. It serves as a way to notify the main processor about a particular event that has taken place and requires immediate attention. One common way interrupts are implemented in HW is by setting the interrupt signal active when both the interrupt flag and interrupt enable are active.

When an interrupt is received, the current program in operation temporarily pauses to allow for the execution of an interrupt procedure. This procedure, usually a smaller subprogram, is responsible for executing the necessary steps to handle the data or event that triggered the interrupt. Additionally, it is common for the interrupt flag to be cleared during this procedure to let the other side acknowledge that the interrupt has been successfully processed. A single system component may generate multiple interrupt events, each with its own signal specifically assigned to one event. Alternatively, there may be just one signal with multiple flags indicating different events. In either case, the CPU's interrupt procedure must retrieve the source of the interrupts and determine which event has occurred.

Similarly, not only the CPU but other components within computer systems as well can respond to incoming signals, similar to interrupts, and perform specific tasks. These signals are called triggers. In terms of DMAC, they are often responsible for initiating data transfer. Triggers and interrupts may arise from both software and hardware sources. In other words, they can be activated through manual signal inputs or be automatically triggered by events occurring in various hardware components.

In addition to the CPU, other components within a computer system can respond to incoming signals, similar to interrupts, and perform specific tasks. These signals, known as triggers, are often responsible for initiating data transfer within the Direct Memory Access Controller (DMAC). Whether generated by manual signals or events within various hardware components, triggers, and interrupts can be triggered by both software and hardware sources.

# **1.9** Arbitration

Arbitration is a process of choosing one of the sources requesting for grant to have access to shared resources, rejecting all other sources at the moment. When faced with multiple data channels, the dilemma arises of how to choose and prioritize among them, especially when more than one transfer is ready to be completed simultaneously. This is similar to bus arbitration, where multiple bus masters request for bus access, but within a single component: which channel will be given priority at the current moment.

Many solutions and variations exist for bus arbitration algorithms, but they can generally be classified into four types [1, p. 385]:

- Round robin: the first type is round-robin, where all sources are granted access in a circular rotation and are given a limited time balanced with respect to other requesting devices.

- Daisy chain: Another solution is fixed priority, or daisy chaining, which grants access to the first encountered requesting device, usually starting with the lowest index. See example in Figure 1.8.

- Centralized parallel arbitration: The third type involves using a custom priority system in which the algorithm for determining the first master to be granted access is determined by the settings of the specific system. Each device is equipped with a request control line and a centralized arbiter responsible for determining which one gains access to the bus. However, this arbitration process usually involves more complicated logic in the arbiter compared to the first two mentioned methods and may lead to bottlenecks.

- Distributed arbitration : This scheme is similar to centralized arbitration, but instead of a central authority selecting who gets the bus, the devices either determine who has the highest priority and who should get the bus or request the bus only when it is not busy. See example in Figure 1.9.

# 1.10 Control logic

The control logic unit is a vital component responsible for directing and coordinating the flow of data in a system. It is responsible for interpreting input signals and executing operations based on specific conditions or instructions. This unit coordinates the timing and functioning of other key components, including arithmetic units, memory, and input/output devices, to ensure that

**Figure 1.8** (a) A centralized one-level bus arbiter using daisy chaining. (b) The same arbiter, but with two levels [5, p. 197].

**Figure 1.9** Distributed bus arbitration [5, p. 198].

#### Control logic

data processing occurs accurately and efficiently. In short, the control logic unit is responsible for directing and controlling the overall behavior of a circuit, making sure that all operations occur in line with the defined instructions or program.

There are two ways we can guarantee the correct setup of control lines. The first is hardwired control, which physically links the control lines to the specific machine instructions. These instructions are then divided into fields, with individual bits being connected to input lines that control different digital logic components. Alternatively, we can use microprogrammed control, which utilizes software made up of microinstructions that execute the microoperations of each instruction [1].

#### 1.10.1 **FSM**

A Finite-State Machine is a mathematical representation of computation. Essentially an abstract machine, that represents sequential circuit. It consists out of states and transitional function from pair of state and input to next state. The FSM is able to transit from one state to another in reaction to outside influences or when certain criteria are met. To define an FSM, one must specify its states, initial state, and the requirements for each transition [6].

The FSM provides output and their timing is based on the type of the machine – Mealy or Moore. Mealy FSM forms its output based on the current state and input, meanwhile, the second option, Moore FSM, generates output depending solely on the current state. For capturing all the information about FSM it is often being represented as a state transition diagram in Figure 1.10. In design then it is represented with one register for the current state and combinational logic taking the current state and input to FSM as an input and providing the next state as an output, see Figure 1.11.

**Figure 1.10** FSM with two states, where valid input are binary strings with even number of zeros

**Figure 1.11** Block design of Mealy FSM

#### 1.10.2 Microprogrammed controller

A microprogrammed controller is a control unit that stores binary control values in memory as words. It arranges a series of signals with each clock cycle, which gives the ability to generate the necessary instructions for execution. These output signals trigger a specific micro-operation, such as a register transfer. Ultimately, this process creates distinct micro-operations that can be saved in memory through a set of control signals.

An advantage of this technique lies in its flexibility, as it allows for a customizable definition of the system's operations. Furthermore, it streamlines the execution of complex tasks by breaking them down into smaller, more manageable instructions stored as microcode. These microinstructions are conveniently accessed from a control memory, functioning as the conductor of operations and ensuring the smooth and efficient functioning of the system.

# Control logic

**Figure 1.12** Microprogrammed Control Unit Organization [7].

# Chapter 2 Analysis

In Chapter 1, we have provided a theoretical overview of DMA controllers and data transfers. We explored the widely utilized functionality of DMACs and gained an understanding of where these separate features are most useful and applicable. In this chapter, we will delve into potential approaches for designing and reasoning behind the inclusion or exclusion of functions in the chosen set of features for TSDMA.

To complete a given task we need to decide a strategy that will be used for design. To refresh our memory: we need to make a design suitable for FPGA and ASIC applications, fast and versatile, generic and with flexible descriptor configuration.

# 2.1 FPGA vs ASIC

When it was mentioned that the design shall target both technologies it is good to understand what are the differences and how to change design depending on technology and whether it is needed at all. Both ASIC and FPGA are microchips that are used for electronics design.

The main difference is that FPGA is an already manufactured chip with programmable logic that can be reprogrammed and is dedicated for general purpose utilization. Such board is usually equipped with a large amount of flip-flops – registers for keeping the data – so they can be easily overused. This allows us to make design easier by not implementing hard combinational logic into it and just keeping things easy and mostly sequential.

Meanwhile, ASIC is a microchip designed for one specific application and cannot be reprogrammed or somehow modified once it is manufactured. The cost of flip-flops on ASIC is bigger than other logic gates, so it is more common to focus more on combinational logic instead of sequential and using registers to save values.

The choice of design style is heavily influenced by the intended technology, and their respective approaches can vary significantly. In the case of TSDMA design, the use of FPGA is not a primary objective and is solely utilized for the final verification of the overall IC. Because of the smaller size of TSDMA, there is no need for a separate FPGA-specific version, as the design created for ASIC will not exceed the limitations of the FPGA board.

The decision not to adjust the design for FPGA was made during one of the consultations with the team. For verification and validation purposes of TSDMA itself, RTL simulations based on UVM testbenches are sufficient.

# **2.2** Set of features

There is no exact microcontroller yet for TSDMA to be placed in, but there are certain requirements for a system that we will follow and consult with the team of designers to get to better decisions when there are several equally functional options according to given requirements.

Information given about the chip is its 32-bit memory organization and system bus width, AHB-Lite protocol used for communication within the microcontroller, and targeting ASIC technology. Even though the number and names of components of the systems are not known yet, it is expected that the IP core has a similar range of components and basic functions as STM32 ICs, a list of them can be found in [8].

To know which features to choose it is necessary to understand where the versatility starts and ends and which aspects can be solved as generic variables. The TSDMA operates solely through hardware, without the involvement of firmware, which limits its inherent versatility. Nevertheless, the TSDMA can still offer a considerable degree of adaptability through its extensive range of configurable features in both channel descriptors and DMA configuration.

We will compare the features of DMAC in several microcontrollers and determine if they would be a valuable addition to our design. After consideration and studying several opensource DMA controllers it has been determined that the functionality of the following ICs is closest to the expected functionality of TSDMAC:

#### 1. STM32Fxx

2. Atmel AVR 8-bit (XMEGA DMA Controller)

#### 3. PIC33/PIC24

Their features are compared side by side in Table 2.1. revealing subtle distinctions between them. However, overall, all three groups of microcontrollers offer similar DMAC functionality that we will take into consideration for our controller.

In determining which features should be included in the final implementation, we must prioritize maintaining an uncomplicated design. This means considering if certain functionalities can be achieved through alternative configurations. We should prioritize implementing the simplest and most commonly used features, while more complex ones that encompass multiple functions may not need to be directly incorporated, as they can be accessed through the basic ones.

#### • Address modification

Fixed and incrementing address modes play a crucial role in data transfers, hence, we confidently select them as our primary options. Decrementation of addresses is determined not to be necessary for TSDMAC due to their low usability in a system. However, by utilizing Scatter-Gather mode and having each address in the descriptor be one block lower than the previous one, we can achieve the same effect with certain limitations. If a decrementing mode becomes necessary in the future, we are fully prepared to expand our addressing modes without any difficulties.

The inclusion of address reload after block transfers seems implicit, making it a non-configurable value for now. Conversely, enforcing address reload at any point other than the end of a block may only serve to complicate matters unnecessarily. Thus, another solution would be to implement a wrap mode of fixed size that enables the system to remain within a fixed memory section, regardless of the amount of transferred data.

#### • Transfer modes

While it's true that two out of three controllers offer single and burst transfers, these are not necessarily essential features. Initially, the mentioned transfer modes were considered to be a part of the configuration, but after numerous discussions and reviews, we ended up

### Set of features

|                                   | STM32F                                              | Atmel AVR                                                                         | PIC33/PIC24                                       |  |  |  |

|-----------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|

| Address modes                     |                                                     |                                                                                   |                                                   |  |  |  |

| Fixed address                     | yes                                                 | yes                                                                               | yes                                               |  |  |  |

| Address incrementation            | yes                                                 | yes                                                                               | yes                                               |  |  |  |

| Address decrementa-<br>tion       | -                                                   | yes                                                                               | yes                                               |  |  |  |

| Address reload                    | yes                                                 | yes                                                                               | yes                                               |  |  |  |

| Peripheral indirect<br>addressing | -                                                   | -                                                                                 | yes                                               |  |  |  |

|                                   | Transfer m                                          | odes                                                                              |                                                   |  |  |  |

| Single transfer                   | -                                                   | yes                                                                               | yes                                               |  |  |  |

| Burst transfer                    | _                                                   | 2/4/8 byte                                                                        | yes                                               |  |  |  |

| Block transfer                    | yes                                                 | yes                                                                               | yes                                               |  |  |  |

| Repeated transfer                 | _                                                   | yes                                                                               | yes                                               |  |  |  |

| Stream transfer                   | yes                                                 | yes                                                                               | yes                                               |  |  |  |

|                                   | Channel arbitrat                                    | tion modes                                                                        |                                                   |  |  |  |

| Round Robin                       | _                                                   | yes                                                                               | yes                                               |  |  |  |

| Fixed priority                    | lowest index first                                  | yes                                                                               | lowest index first                                |  |  |  |

| Custom priority                   | up to 4 levels of pri-<br>ority                     | channel 0 or both 0<br>and 1 – highest pri-<br>ority, round robin<br>for the rest | -                                                 |  |  |  |

|                                   | Triggers and in                                     | nterrupts                                                                         |                                                   |  |  |  |

| Disable/Enable<br>interrupt       | yes                                                 | yes                                                                               | yes                                               |  |  |  |

| Completion<br>interrupt           | yes                                                 | yes                                                                               | yes                                               |  |  |  |

| Half-done interrupt               | yes                                                 | -                                                                                 | yes                                               |  |  |  |

| Error interrupt                   | yes                                                 | yes                                                                               | yes                                               |  |  |  |

| Additional<br>interrupts          | -                                                   | -                                                                                 | yes                                               |  |  |  |

| HW triggers                       | fixed set per<br>channel                            | configurable per<br>channel                                                       | configurable per<br>channel, up to 128<br>sources |  |  |  |

| SW trigger                        | yes                                                 | yes                                                                               | yes                                               |  |  |  |

|                                   | Other                                               |                                                                                   |                                                   |  |  |  |

| Channels                          | 12                                                  | 4                                                                                 | n                                                 |  |  |  |

| Size of transfer                  | 8/16/32-bit,<br>source/destination<br>independently | 8-bit                                                                             | 8/16-bit                                          |  |  |  |

|                                   |                                                     | _                                                                                 | _                                                 |  |  |  |

| Scatter-Gather                    |                                                     |                                                                                   |                                                   |  |  |  |

**Table 2.1** Features of DMAC in STM32Fxx, Atmel AVR 8-bit and PIC24/PIC33 IC's

#### Set of features

eliminating these modes from the feature set of TSDMA. This is because the same result can be achieved by using block transfers of corresponding sizes. It is not worth it for us to include these as separate features yet. However, it is more important for our design to have repeated and stream transfers as they have a high potential for practical use in peripherals.

#### • Channel arbitration

Fixed priority is a fundamental basic feature that may be a reliable method for resolving conflicts, yet it alone cannot fully meet the objectives of the TSDMA strategy. After assessing the strengths and characteristics of different arbitration modes, we have concluded that a mix of Round Robin and Fixed priority, along with a Custom priority mode, is the relevant approach. Offered by us Custom mode guarantees that each channel is assigned a unique priority value, allowing users to have complete control over channel priorities. Furthermore, in situations where multiple channels hold the same priority value, the channel with the lowest index is given precedence and will be served first.

#### • Interrupts

Undoubtedly beneficial interrupts are completion and error interrupts. These two signals provide essential information about a transfer, indicating whether it was successful or not, or if it even finished at all. On the other hand, the Half-done interrupt only informs the system that the transfer has reached the halfway point, which may be useful in advanced systems, but for our specific scenario, it appears unnecessary and will not be incorporated. However, despite the profit of Error interrupt it will not be included in TSDMA for now.

As an additional interrupt in the PIC family, there is an interrupt signal that indicates when data written to the internal buffer has not yet been successfully transferred to the destination memory. This feature is particularly beneficial for systems with larger buffers and the ability to put the DMAC in sleep mode. This allows for uninterrupted re-enabling and resuming of the same transfer process.

#### • Triggers

Reviewing triggers, based on several other subsystems in a mentioned early Tropic's IP core shown in Figure ??, we decided to include up to 31 distinct hardware sources for event triggers in TSDMA. Since the exact number of external trigger sources will be known at the time of integration of DMAC in the system, this will be one of the generic variables. Hence, it can be altered accordingly to accommodate the appropriate number of hardware trigger sources lately. The significance of software triggers in M2M data transfers has been taken into account and was included in our design without bigger consideration. TSDMA will have a maximum of 32 diverse trigger sources, with each channel having the capability to independently assign any of them, thus giving users complete control over their priorities.

#### • Other features.

As required by the assignment, to ensure versatility the number of channels can be a generic variable. Taking into account the size of the microcontroller, it has been determined that the maximum value will be set at 32.

The size of the transfer will be fixed, 32 bits, with very simple reasoning – targeted microcontroller has a 32-bit architecture, and all transfers within the system are planned to be of the same size.

The block size will range from 1 to 65535 as in reviewed ICs, and when combined with repeat mode, it will enable the transfer of up to  $2^{32}$  words, providing ample flexibility for data management.

One feature that is not included in any of the compared controllers but can be seen in Table 2.1 is Scatter-Gather. It was mentioned during one of the consultations and after a discussion

#### Controller

with Ondrej Ille, we decided to include this feature in TSDMA controller. Scatter-Gather is beneficial for DMA in numerous ways, which are described in Section 1.4.

# 2.3 Controller

There are various approaches to implementing control logic, with two key contenders being the *Micro-programmed controller* and *Finite State Machine* (FSM). These two solutions each have their unique strengths and weaknesses. We'll analyze these traits to understand where they excel and where they might have limitations.

Using FSMs allows for a simpler and faster design and implementation process compared to micro-programmed controllers. This is due to their direct hardware-based approach, making them well-suited for smaller ICs. Micro-programmed controllers, on the other hand, tend to be more complex and demand additional hardware resources due to the need for microcode storage and control logic. As a result, their execution may be slower because of cycles for micro-instruction sequencing and interpretation. Additionally, the larger chip area and resource utilization required for microcode storage can limit their feasibility for smaller ICs with limited resources. FSMs have minimal hardware overhead, making them a viable option for applications where chip area and resource utilization are critical. They also exhibit predictable behavior, making them suitable for applications requiring straightforward sequential logic control.

Through the use of microcode sequences, micro-programmed controllers offer great flexibility, allowing for easy adaptation to changes. Their ability to handle complex logic makes them suitable for different applications, without the need for hardware modifications. With the simple modification of the microcode, adjustments can be made to the logic and instructions without direct hardware changes. In contrast, FSMs rely on hardwired sequential circuits, which can make it challenging to adjust control logic and implement modifications. As the control logic increases in complexity, FSMs may prove difficult to design and may encounter limitations. To alter their behavior or functionality, a significant redesign is often required.

# 2.4 Datapath

In order to effectively manage data movement and processing, it is necessary to include supplementary modules that are controlled by the central processor. Despite the fact that standard DMACs feature four additional registers in addition to the control logic, this may not be sufficient given the potential for multiple channels of varying numbers. Consequently, it is not feasible to allocate address, buffer, and counter registers for each channel within a single block. As the development of TSDMA continues, it becomes clear that the datapath will require more than just these four registers to successfully accomplish its objectives.

## 2.4.1 Channel Descriptor

Each channel will be assigned a descriptor that contains all or most of the features relevant to that specific channel and its transfer. This includes the source and destination addresses, as well as a data counter register. Additional features pertaining to these registers or specific modes of the channel/transfer may also be present in this descriptor. These descriptors will be saved in memory and their starting address will be included in the DMA configuration. Since all descriptors are equal in size, we can effortlessly retrieve any channel descriptor by knowing the starting point.

When a channel is operating in normal mode with sequential memory addresses it is enough to store all related information in one descriptor. However, it is not sufficient for Scatter-Gather mode where different locations in memory are involved in one transfer. One of the possible solutions is to describe a list of descriptors in memory through the channel's descriptor. Datapath

### 2.4.2 Buffer

From the very start, the use of a buffer has been essential in storing data when transferring from the source address to the destination address. Naturally, TSDMA will require one as well. However, since there is more to be temporarily stored in our block, we will introduce a descriptor buffer. This will allow us to effectively work with the data transfer within the TSDMA module. As each descriptor is loaded from memory, it will be updated locally throughout the transfer process. Finally, at the end of the triggered activity, the updated descriptor will be written back to memory.

# 2.4.3 Trigger Register

#### **Figure 2.1** Four-phase handshake.

The next thing to consider is how the transfers will be set off. The external triggers represented as interrupts from other components of a computer system may arise at any moment and it is not guaranteed that the DMA controller can process them right away. Hence, it is necessary to capture them in a register. The first idea was to acknowledge a signal with a four-phase handshake (Figure 2.1), but it could be too complicated taking into account that it should be implemented on both sides and involve modifying existing interfaces. The second and for now last idea was to capture the rising edges of incoming interrupts into an inner buffer for triggers.

# 2.4.4 Arbiter

Once triggers are captured channel is ready for data transfer, with a greater number of channels available at the same time comes the need to choose which channel to serve first. Arbiter will be the module responsible for this. As discussed in Section 2.2 it will support three different algorithms to choose a highest priority channel. Meanwhile, it seems easy to understand the design of *Round Robin* and *Fixed* priority algorithms, *Custom* priority mode has a few uncertainties in it. It has to pick the highest priority channel amongst all active and triggered ones. It is a linear problem if sequential logic is involved, but it could then take up to 32 clock cycles, so we will try to design a combinational solution in the following chapters.

## 2.4.5 Register Map

In order to communicate with DMA and effectively configure the block's inner registers, it is crucial to arrange them in a clear and logical manner and map them to the system memory. The register map must then be assigned an address in memory space before the controller is integrated into the chip. Additionally, the register map will feature a slave bus interface, allowing it to be accessed by other components. This interface will enable all necessary read and write operations for configuration registers not included in channel descriptors. It could manage such registers as flag or DMA status registers, customizable priority values, or the external trigger source for the channels. A major part of the register map including signals for bus communication will be generated by the DMAC's description using scripts.

# Chapter 3 Design

The previous chapter provided the necessary information on which features should the TSDMA consist of and how these components function. After analyzing the system, it is necessary to design how to implement it in practice. First, the technologies to be used for the implementation shall be chosen. Then we will go through all the components and how they will be designed. The chapter serves as an overview of the design decisions that arose during the process.

# 3.1 HDL