#### Assignment of master's thesis

| Title:                   | Design of System On Chip with RISC-V processor for USI |  |

|--------------------------|--------------------------------------------------------|--|

|                          | graphical pen controller                               |  |

| Student:                 | Bc. Martin Stahl                                       |  |

| Supervisor:              | Ing. Tomáš Novák                                       |  |

| Study program:           | Informatics                                            |  |

| Branch / specialization: | Design and Programming of Embedded Systems             |  |

| Department:              | Department of Digital Design                           |  |

| Validity:                | until the end of summer semester 2023/2024             |  |

#### Instructions

1. Familiarize yourself with USI Pen Controller SoC requirements, with the existing platform based on CoolRISC and with available IP blocks.

2. Analyze differences between RISC-V and CoolRISC CPU platform and prepare system level design for System On Chip controller based on RISC V.

3. Implement the design at the RTL level and demonstrate its correct operation.

4. Validate the designed system on the FPGA circuit.

5. Estimate the power consumption and compare it with the CoolRISC processor implementation.

Master's thesis

# Design of System On Chip with RISC-V processor for USI graphical pen controller

Bc. Martin Stahl

Department of Digital Design Supervisor: Ing. Tomáš Novák

May 3, 2023

## Acknowledgements

I would like to thank my supervisor Ing. Tomáš Novák for his guidance and project leadership during my work on this Master's thesis. Furthermore, I would like to thank my colleagues Ing. Tomáš Tuček, Ing. Michal Skiba, Ing. Radek Hájek, and Ing. Petr Jašek, for their great help and expertise. Lastly, I would like to thank my partner Domen Stropnik for his great mental support during my entire Master's Degree studies.

### Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. I further declare that I have concluded an agreement with the Czech Technical University in Prague, on the basis of which the Czech Technical University in Prague has waived its right to conclude a license agreement on the utilization of this thesis as a school work under the provisions of Article 60 (1) of the Act. This fact shall not affect the provisions of Article 47b of the Act No. 111/1998 Coll., the Higher Education Act, as amended.

In Prague on May 3, 2023

. . . . . . . . . . . . . . . . . . .

Czech Technical University in Prague Faculty of Information Technology © 2023 Martin Stahl. All rights reserved. This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the

#### Copyright Act).

#### Citation of this thesis

Stahl, Martin. Design of System On Chip with RISC-V processor for USI graphical pen controller. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2023.

### Abstrakt

Tato diplomová práce se zabývá RTL návrhem a implementací systému systému na čipu na procesorové platformě RISC-V pro USI ovladač grafického pera. Současný SoC ovladače pera založeného na CoolRISC je analyzován a na základě této analýzy je vytvořen systémový návrh pro nové SoC ovladače pera založeného na RISC-V. RTL návrh nového SoC je implementován do 180 nm technologie a jeho systémová spotřeba energie je měřena v simulaci a poté porovnána se stávajícím systémem na bázi CoolRISC. Práce se také zabývá technickým srovnáním procesorových platforem CoolRISC a RISC-V.

**Klíčová slova** Systém na čipu, RISC-V, CoolRISC, systémový návrh, RTL implementace, FPGA validace, analýza spotřeby

### Abstract

This diploma thesis covers the RTL design and implementation of System On Chip based on the RISC-V processor platform for USI graphical pen controller. The current CoolRISC-based pen controller SoC is analysed and based on this analysis new system design for the RISC-V-based pen controller SoC is created. The RTL design of the new SoC is implemented into 180 nm technology, and its system power consumption is measured in simulation and then compared to the existing CoolRISC-based system. The thesis also covers the technical comparison between CoolRISC and RISC-V processor platforms.

**Keywords** System On Chip, RISC-V, CoolRISC, system design, RTL implementation, FPGA validation, power analysis

# Contents

| In       | Introduction 1 |        |                                | 1        |

|----------|----------------|--------|--------------------------------|----------|

| 1        | Goa            | 1      |                                | 3        |

| <b>2</b> | USI            | Pen (  | Controller SoC requirements    | <b>5</b> |

|          | 2.1            | Existi | ng CoolRISC pen controller SoC | 5        |

|          |                | 2.1.1  | Block description              | 6        |

|          |                | 2.1.2  | Power modes                    | 8        |

|          |                | 2.1.3  | Reset structure                | 8        |

|          |                | 2.1.4  | Power domains                  | 9        |

|          |                | 2.1.5  | Clock structure                | 9        |

|          |                | 2.1.6  | Peripherals                    | 10       |

|          |                | 2.1.7  | Software                       | 11       |

|          | 2.2            | CoolR  | ISC CR816L overview            | 12       |

|          |                | 2.2.1  | Harvard RISC-like architecture | 12       |

|          |                | 2.2.2  | Register-memory architecture   | 12       |

|          |                | 2.2.3  | Memory sizes                   | 12       |

|          |                | 2.2.4  | Three-stage pipeline           | 12       |

|          |                | 2.2.5  | 8bx8b multiplier               | 12       |

|          |                | 2.2.6  | Stand-by mode                  | 12       |

|          |                | 2.2.7  | Data and peripheral bus        | 12       |

|          |                | 2.2.8  | Instruction set                | 13       |

|          |                | 2.2.9  | Double-latch design            | 13       |

|          | 2.3            | RISC-  | V overview                     | 14       |

|          |                | 2.3.1  | Simplicity and modularity      | 14       |

|          |                | 2.3.2  | Extendability                  | 14       |

|          |                | 2.3.3  | Open source                    | 14       |

|          |                | 2.3.4  | RISC-V Foundation              | 14       |

|          |                | 2.3.5  | ISA architecture               | 14       |

|          |     | 2.3.6 CV32E40P core                             | 15         |

|----------|-----|-------------------------------------------------|------------|

|          | 2.4 | CR816L and CV32E40P difference analysis         | 17         |

|          |     | 2.4.1 Code and data storage in the same memory  | 17         |

|          |     | 2.4.2 General Purpose Registers                 | 17         |

|          |     | 2.4.3 Instruction set                           | 17         |

|          |     |                                                 | 19         |

|          |     | - ,                                             | 19         |

|          |     | *                                               | 19         |

|          |     |                                                 | 22         |

|          |     |                                                 | 22         |

|          |     |                                                 | 23         |

|          | 2.5 |                                                 | 23         |

| 3        | Sve | tem design of RISC-V pen controller SoC         | 25         |

| U        | 3.1 |                                                 | 26         |

|          | 0.1 |                                                 | $20 \\ 27$ |

|          |     | 1                                               | 30         |

|          |     |                                                 | 30         |

|          | 3.2 |                                                 | 31         |

|          | 0.2 |                                                 | 31         |

|          |     |                                                 | 31         |

|          |     |                                                 | 32         |

|          |     | 5.2.5 FI GA legister asynchronous set and leset | )2         |

| 4        | -   |                                                 | 33         |

|          | 4.1 | 1                                               | 34         |

|          | 4.2 | 0                                               | 34         |

|          |     | 1                                               | 34         |

|          |     | 0                                               | 35         |

|          | 4.3 |                                                 | 39         |

|          |     |                                                 | 39         |

|          |     | 4.3.2 PML                                       | 39         |

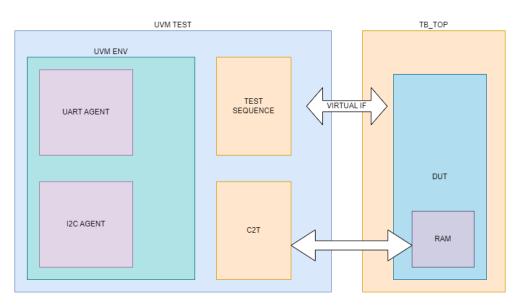

| <b>5</b> | Ver | ification 4                                     | <b>41</b>  |

|          | 5.1 | Test bench structure                            | 41         |

|          | 5.2 | Test bench implementation                       | 42         |

|          | 5.3 | Software compilation                            | 43         |

|          |     | 5.3.1 CoreMark                                  | 44         |

|          | 5.4 |                                                 | 45         |

|          |     |                                                 | 45         |

|          |     | 1                                               | 45         |

|          |     |                                                 | 45         |

|          |     |                                                 | 45         |

|          |     |                                                 | 45         |

|          |     |                                                 | 45         |

|          |     |                                                 |            |

|   |     | 5.4.7     | penriscv_pml_01                                                                         | 45 |

|---|-----|-----------|-----------------------------------------------------------------------------------------|----|

|   |     | 5.4.8     | penriscv_timer_00                                                                       | 45 |

|   |     | 5.4.9     | $penriscv\_uart_00$                                                                     | 46 |

|   |     | 5.4.10    | $penriscv_wdt_00$                                                                       | 46 |

|   |     | 5.4.11    | $penriscv\_wdt\_01  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $    | 46 |

|   |     | 5.4.12    | penriscv_usi_01 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 46 |

|   |     | 5.4.13    | $penriscv\_wut\_00  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $     | 46 |

|   |     | 5.4.14    | penriscv_coremark_01                                                                    | 46 |

| 6 | FP  | GA val    | idation                                                                                 | 47 |

|   | 6.1 | FPGA      | . platform                                                                              | 47 |

|   | 6.2 | FPGA      | design changes                                                                          | 47 |

|   |     | 6.2.1     | GPIO Debouncer                                                                          | 47 |

|   |     | 6.2.2     | Removing clock multiplexors from WDT and WUT                                            | 49 |

|   |     | 6.2.3     | Replacing buffers on clock sources in PML                                               | 49 |

|   |     | 6.2.4     | Replacing system clock multiplexor in PML                                               | 49 |

|   |     | 6.2.5     | Emulating POWER DOWN mode by dig_core reset                                             | 49 |

|   | 6.3 | FPGA      | implementation                                                                          | 50 |

|   |     | 6.3.1     | FPGA top                                                                                | 50 |

|   |     | 6.3.2     | Constraints                                                                             | 51 |

|   |     | 6.3.3     | PCB for high-voltage pentip driver                                                      | 52 |

|   | 6.4 |           | ng ROM contents in bitstream                                                            | 58 |

|   | 6.5 | Valida    | tion scenarios                                                                          | 58 |

|   |     | 6.5.1     | LED control by GPIO                                                                     | 58 |

|   |     | 6.5.2     | UART communication with the PC                                                          | 58 |

|   |     | 6.5.3     | I2C Master communication with an I2C Slave device                                       | 59 |

|   |     | 6.5.4     | Coremark run longer than 10 seconds                                                     | 59 |

|   |     | 6.5.5     | Transmission on pentip $0 \ldots \ldots \ldots \ldots \ldots \ldots$                    | 60 |

|   |     | 6.5.6     | Reception on pentip $0 \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                | 60 |

| 7 | Phy | vsical in | mplementation                                                                           | 63 |

|   | 7.1 | Techno    | ology                                                                                   | 63 |

|   | 7.2 | Synthe    | esis                                                                                    | 63 |

|   |     | 7.2.1     | Design Constraints                                                                      | 64 |

|   |     | 7.2.2     | UPF                                                                                     | 64 |

|   |     | 7.2.3     | RAM and ROM technology cells                                                            | 65 |

|   |     | 7.2.4     | Outputs                                                                                 | 65 |

|   |     | 7.2.5     | Area results                                                                            | 66 |

|   | 7.3 | Place-a   | and-route                                                                               | 66 |

|   | 7.4 |           | Timing Analysis                                                                         | 66 |

|   | 7.5 | Gate-le   | evel simulations                                                                        | 66 |

| 8 | Pov | ver sim   | nulations and comparison                                                                | 67 |

|   | 8.1 | Scenar    | rios                                                                                    | 67 |

|        | 8.1.1   | penriscv_coremark_01                                                  | 67 |

|--------|---------|-----------------------------------------------------------------------|----|

|        | 8.1.2   | penriscv_usi_01 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 68 |

| 8.2    | Switch  | ning activity                                                         | 68 |

| 8.3    | Averag  | ge power consumption calculations                                     | 68 |

| 8.4    | Metho   | odology                                                               | 68 |

|        | 8.4.1   | Power consumption across hierarchy                                    | 69 |

|        | 8.4.2   | Corrections                                                           | 71 |

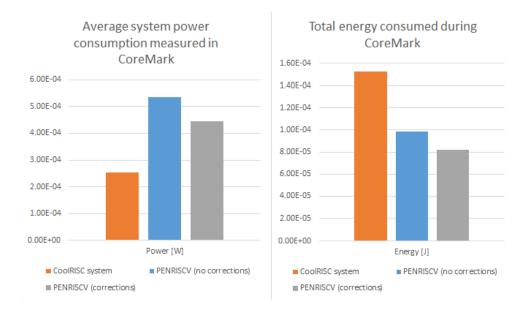

| 8.5    | Result  | ts                                                                    | 72 |

|        | 8.5.1   | penriscv_coremark_01                                                  | 72 |

|        |         | 8.5.1.1 RAM access                                                    | 73 |

|        | 8.5.2   | penriscv_usi_01                                                       | 74 |

|        | 8.5.3   | Power measurement conclusion                                          | 77 |

| Conclu | ision   |                                                                       | 79 |

| Biblio | graphy  |                                                                       | 81 |

| A List | t of ab | breviations used                                                      | 85 |

| В Сог  | ntents  | of the attachments                                                    | 87 |

# **List of Figures**

| 2.1  | CoolRISC SoC block diagram                                             | 6  |

|------|------------------------------------------------------------------------|----|

| 2.2  | CoolRISC SoC power domains                                             | 9  |

| 2.3  | CoolRISC SoC clock structure                                           | 10 |

| 2.4  | CV32E40P block diagram [4]                                             | 15 |

| 2.5  | RISC-V Pseudo Instructions [8]                                         | 18 |

| 2.6  | Non-overlapping clock example waveform                                 | 19 |

| 2.7  | General D-Latch structure in CMOS [9]                                  | 20 |

| 2.8  | More efficient D-Latch structure in CMOS [10]                          | 20 |

| 2.9  | General D-Flip-Flop structure in CMOS [11]                             | 21 |

| 2.10 | More efficient D-Flip-Flop structure in CMOS [12]                      | 21 |

| 2.11 | Latch time borrowing example                                           | 22 |

| 3.1  | Changes in PENRISCV SoC compared to previous SoC. Green                |    |

| 5.1  | outline = new module, Red outline = modified existing module           | 25 |

| 4.1  | New RISC-V pen controller SoC - PENRISCV                               | 33 |

| 4.2  | AHB-lite basic transfers [17]                                          | 37 |

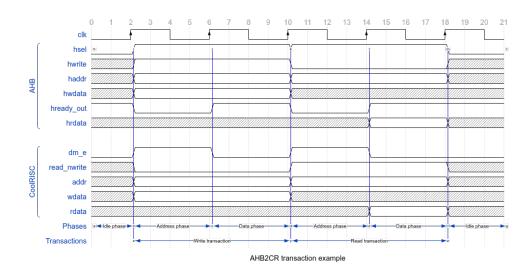

| 4.3  | AHB2CR bridge transaction example                                      | 38 |

| 5.1  | PENRISCV test bench structure                                          | 42 |

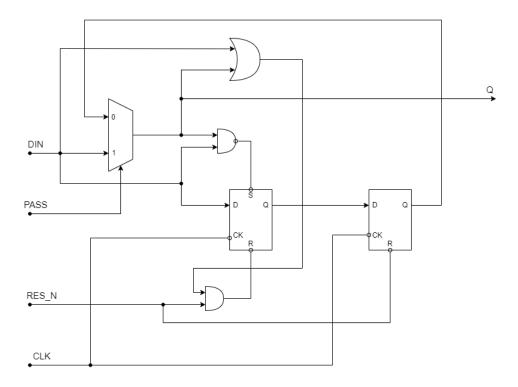

| 6.1  | GPIO debouncer used in the CoolRISC-based system                       | 48 |

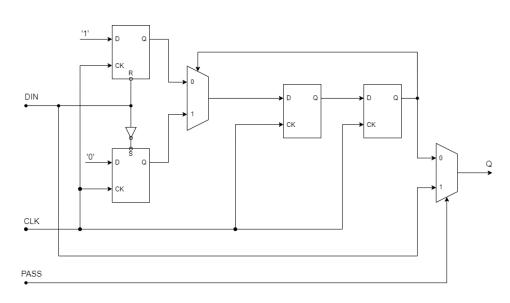

| 6.2  | GPIO debouncer adjusted for FPGA                                       | 49 |

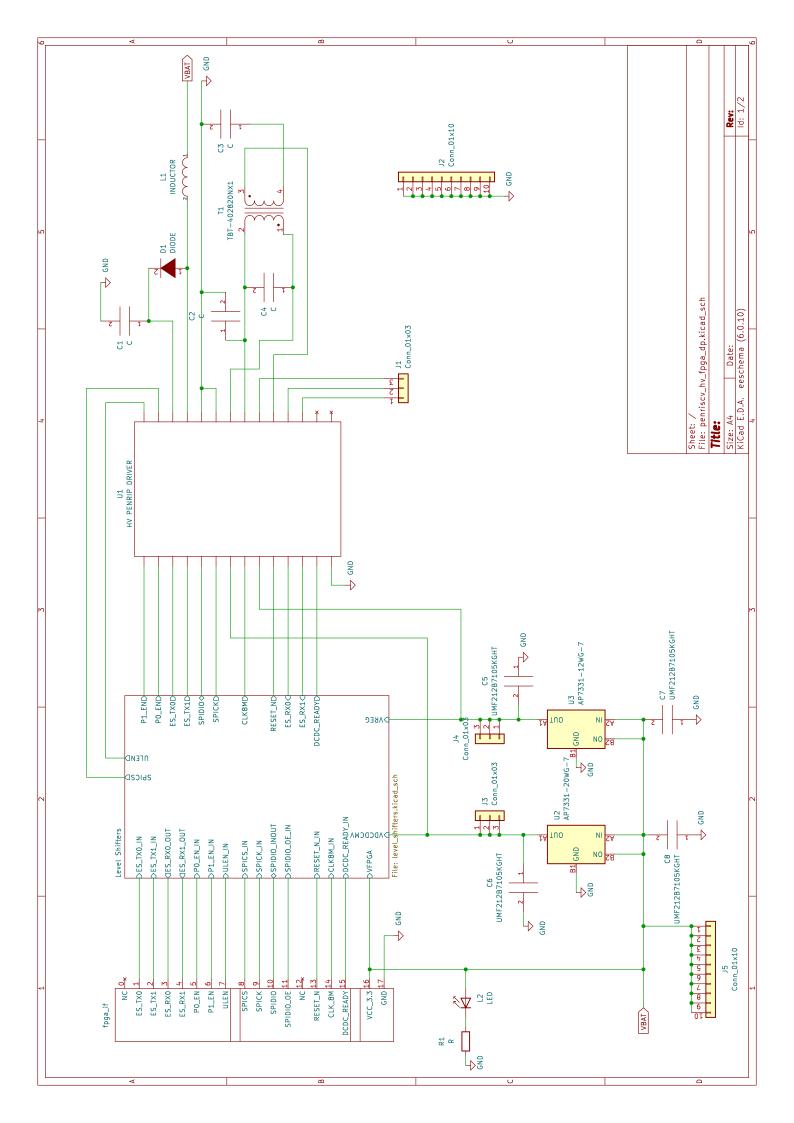

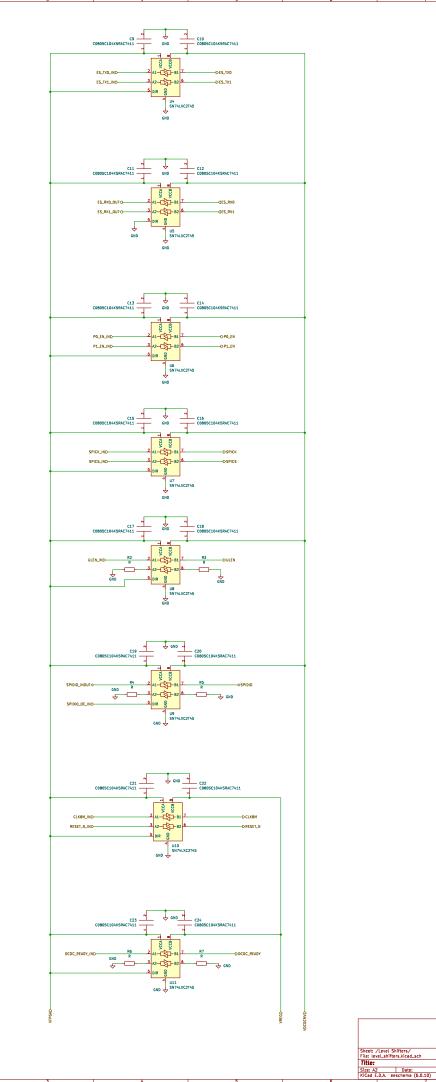

| 6.3  | HV pentip driver PCB                                                   | 55 |

| 6.4  | HV pentip driver PCB FPGA interface                                    | 56 |

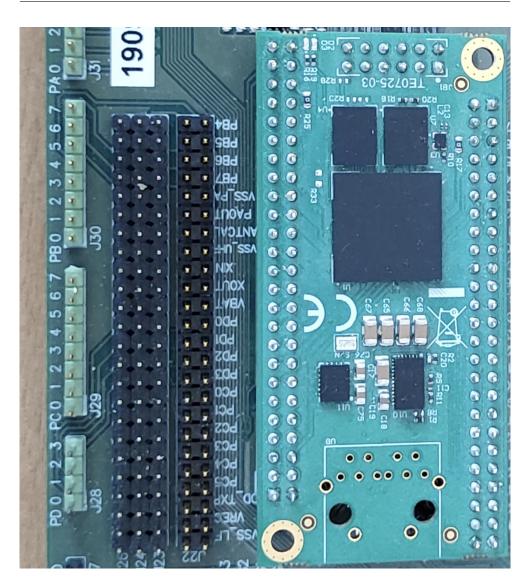

| 6.5  | Connected HV pentip driver PCB to the FPGA board                       | 57 |

| 6.6  | CoreMark result from PENRISCV run on the FPGA                          | 59 |

| 6.7  | Transmission on pentip 0 measured with an oscilloscope $\ldots \ldots$ | 60 |

| 6.8  | Reception on the pentip 0 from DELL laptop touch screen                | 61 |

| 8.1  | Power consumption distribution across the hierarchy in CoreMark        | 70 |

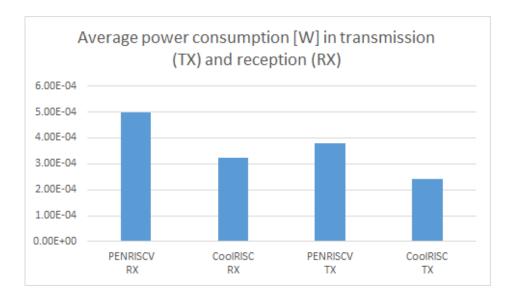

| 8.2 Average power and total energy consumption during Corel   | 1ark 7      | 72 |

|---------------------------------------------------------------|-------------|----|

| 8.3 Power consumption distribution across the hierarchy in tr | ansmis-     |    |

| sion/reception scenario                                       | 7           | 74 |

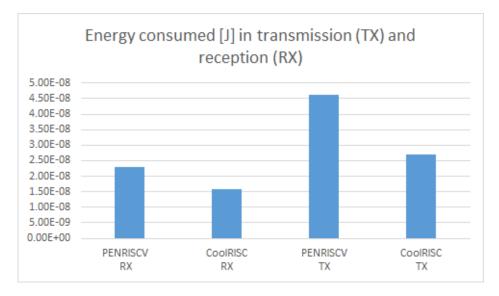

| 8.4 Average system power consumption during transmission an   | l recep-    |    |

| tion                                                          | 7           | 76 |

| 8.5 Total system energy consumption during transmission and   | reception 7 | 76 |

# List of Tables

| PENRISCV top interface - generics                   | 27                                    |

|-----------------------------------------------------|---------------------------------------|

| PENRISCV top interface - Main signals               | 28                                    |

| PENRISCV top interface - USI Control Logic signals  | 29                                    |

| PENRISCV top interface - GPIO signals               | 29                                    |

| Memory address mapping                              | 30                                    |

| Peripheral address mapping                          | 30                                    |

|                                                     |                                       |

| CoolRISC data bus interface                         | 35                                    |

| AHB-lite bus interface                              | 36                                    |

|                                                     |                                       |

| Virtual interfaces                                  | 42                                    |

|                                                     | 71                                    |

|                                                     |                                       |

| Final results relative to the CoolRISC-based system | 77                                    |

|                                                     | PENRISCV top interface - Main signals |

### Introduction

Modern pens for graphic tablets are not just pieces of plastic with a hard tip which makes contact with the tablet to make the contact for drawing in resistive displays. Today most graphic pens are much more complex. They can measure pen pressure, the angle at which the pen is held against the tablet and the precision is far better. They also feature buttons and a battery which requires charging.

Furthermore, these graphic pens shall work according to the Universal Stylus Initiative (USI) which defines the industry standards for graphic pens communication protocols. This is to enable these pens to work with a large variety of touch screens in devices such as phones, tablets, and other platforms.

These functionalities require a digital controller module which also needs to be ultra-low-power to last long on a very small battery. ASICentrum s.r.o has been developing pen controller SoCs for these graphical pens for several years. They have been using the CoolRISC CPU platform as the brain of the controller, however, it is only an 8-bit CPU and it is increasingly becoming a bottleneck in the system's performance.

They want to move to a new CPU platform for better performance but they do not know how much the new CPU is going to affect the overall power consumption of the system. The ultra-low power consumption of the system is a requirement.

They have tasked me with implementing their CoolRISC-based pen controller SoC with a modern RISC-V CPU to simulate and estimate the power consumption of the system with the new CPU and compare it to the existing CoolRISC-based system. Part of this will be the creation of an FPGA environment where the customer can test their software.

The result of this thesis will be the pen controller SoC implemented with the RISC-V CPU platform. It will be simplified in some ways to make the development faster while still keeping the core functionality necessary for valid power comparisons. The basic functionality of the system will be verified and then customer-required functionality will be validated on an FPGA. 180 nm technology will be used for physical implementation which is then going to be used for power consumption simulations.

Part of the analysis will be also the comparison of CoolRISC and RISC-V CPU platforms to highlight the differences, advantages and disadvantages of each platform which go beyond just the power consumption.

### CHAPTER

# Goal

The goal of this thesis is to analyse the existing CoolRISC-based pen controller SoC and implement it with the RISC-V CPU platform in RTL and estimate the power consumption using simulation measurements of its physical implementation.

The RISC-V CPU, which is going to be used for the new implementation, is the CV32E40P developed by the OpenHW group and is fully open source. The newly implemented system will be simplified in some ways to make the implementation faster while keeping the core functionality necessary for valid power comparisons. The basic functionality of the system will be verified in a test bench simulation environment and then customer-required functionality will be validated on an FPGA. After the system is verified and validated, synthesis and placement into 180 nm technology will be performed. This physical implementation will be used for the power consumption simulations and estimations and the results will be compared with the results from the existing CoolRISC-based system.

The goal of the USI Pen Controller SoC requirements chapter is to analyse the existing CoolRISC-based system to identify the key components and features of the system. These findings will be used to create requirements for the new RISC-V-based implementation called "PENRISCV". Those requirements will be used to make a system design for the new implementation. Part of this chapter is also the analysis of both CPU platforms and their comparison.

The goal of the implementation is to use the system design from the previous chapter and based on it implement PENRISCV in RTL.

The goal of the verification and validation is to verify PENRISCV's basic functionality and to check the correct behaviour of the system. Validation on FPGA is intended to check customer-required functionality for software testing.

The goal of physical implementation and power simulations is to implement PENRISCV into 180 nm process technology and then estimate the theoretical power consumption simulated and estimated in selected scenarios. The results 1. Goal

of these estimations will be then compared to the results from the CoolRISC-based system.

# CHAPTER 2

# USI Pen Controller SoC requirements

In this chapter, I analyse the existing system, which utilized the CoolRISC CR816L CPU core, its features and characteristics. I focus on the digital part of the system (dig\_top) because it is the core of the system and the main focus of power comparison. Analogue parts will stay the same in both systems. Then I compare the CoolRISC CPU platform to the RISC-V platform.

Based on the features of the existing system and the differences between both CPU platforms I create requirements for the new system that utilizes a new RISC-V CPU core.

#### 2.1 Existing CoolRISC pen controller SoC

The pen controller is a multi-chip system built into a graphical pen used for drawing on touch screens and graphic tablets. It is the main control unit of the graphical pen.

The main functionality of the pen controller is to transmit and receive signals on its two pentips<sup>1</sup> from the electrostatic field generated by a touch screen or a graphic tablet.

Those signals represent the data communication stream between the tablet and the pen controller. In the real environment, there is a lot of electrostatic noise during communication, therefore, computation algorithms are required for reliable communication. This is managed by the pen controller hardware and software. The pen controller also handles other functionality of the graphical pen such as battery charging.

The pen controller consists of two chips. The first chip is the low-voltage SoC which contains the CPU, memory, power management, peripherals and

$<sup>^1\</sup>mathrm{A}$  pentip is a wire connected to a pen controller IO pad which is designed for high voltages

low-voltage analogue parts. It is the main control unit of the system which runs the software.

The second chip is the high-voltage pentip driver which contains voltage control logic, DCDC and other high-voltage analogue parts for transmitting and receiving high-voltage signals on the pentips.

These two parts of the system communicate together through a specific interface and a custom SPI. The manufactured implementation consists of both chips connected together in a single package.

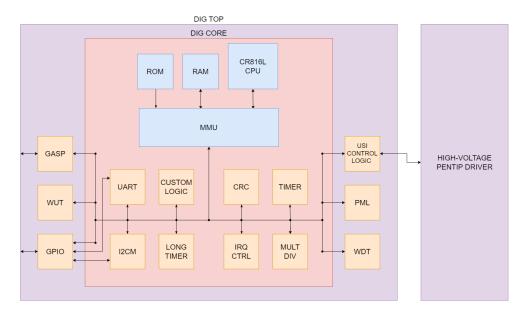

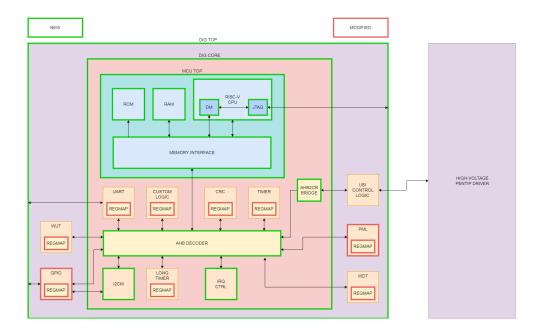

Figure 2.1: CoolRISC SoC block diagram

#### 2.1.1 Block description

Here I briefly described the function of each block in the CoolRISC implementation. Each block is visible in the system block diagram in Figure 2.1.

- 1. Central Processing Unit (CPU): The CR816L CPU core is responsible for running compiled software. It accesses the RAM, ROM and Flash memory through the MMU. Peripherals are accessed through CR816L's data bus. Each peripheral has its own defined address space.

- 2. Random Access Memory (RAM): Memory for runtime data while the software is being executed on the CPU.

- 3. **Read-Only Memory (ROM):** Contains boot software and other minor procedures needed for the system before the CPU starts fetching from the Flash memory.

- 4. Memory Management Unit (MMU): Serves as an arbitrer of the address space. Multiplexed devices are accessed based on the address from the CPU. Address space for RAM, ROM and peripherals is defined during implementation. It also features an NVM controller for Flash memory.

- 5. Power Management Unit (PML): Is mainly responsible for managing system clock switching, reset synchronization and distribution, reset synchronization from WDT, and system power mode transitions. It also features DCDC control, Switch control, LED control and battery charging control.

- 6. WatchDog Timer (WDT): To prevent deadlock situations a watchdog timer is available to monitor embedded firmware activity. Watchdog is controlled by the CPU and generates a system reset upon a time-out.

- 7. Wake-Up Timer (WUT): 8-bit programmable down counter from 512 us to 2 ms. It is used to switch the running system from SLEEP or POWER-DOWN mode to ACTIVE mode.

- 8. General-Purpose Input/Output (GPIO): Configurable 3-bit input and output pads that can be controlled through software. Contains debouncers and edge/level detectors. Two pads are also used for the I2CM interface. Also manages the selection of UART interface on two GASP pads.

- 9. Interrupt Controller: Control unit to enable, mask and give priority to interrupts which are generated by peripherals.

- UART: Standard UART interface with TXD and RXD interface. The frame structure is: start bit / 8 bits data / 1 stop bit. Parity may be even / odd / no (default). Supported baud rates are 9 600 Bd, 14 400 Bd, 19 200 Bd, 28 800 Bd, 38 400 Bd, 57 600 Bd, 115 200 Bd.

- 11. **I2CM:** Standard I2CM interface. Implements the standard mode with a baud rate of up to 100 kHz and the Fast mode with a baud rate of up to 400 kHz. It can operate as a single master-receiver or master-transmitter.

- 12. **Timer:** 16-bit down counter with auto-reload mode or single shoot (stopped when 0x00 value is reached)

- 13. **CRC:** Hardware acceleration for cyclic redundancy check. Allows to define polynomials for CRC calculation.

- 14. Custom Logic: Hardware acceleration for specific bitwise operations.

- 15. Multiplication/Division accelerator (MULTDIV): Multiplication performs 16-bit x 8-bit operation. The duration is a maximum of 9 clocks. The division performs 16-bit / 8-bit operations. The duration is a maximum of 18 clocks.

- 16. **USI<sup>2</sup> Control Logic:** Custom control logic IP which implements the USI pen protocol. It sends and receives data from the HV pentip driver.

- 17. GASP: Custom debugging interface.

#### 2.1.2 Power modes

To help the CoolRISC system to save power, several power modes are implemented.

#### 1. **ACTIVE:**

- All parts of the dig\_top are active.

- CPU is running and executing code.

#### 2. **SLEEP:**

- CPU is in sleep mode and not executing code.

- System clock is switched to a lower frequency oscillator.

- System can be switched back to ACTIVE mode upon interrupt or event or system reset.

#### 3. POWER-DOWN:

- VDD1 power domain is switched off.

- System clock is switched to a lower frequency oscillator.

- System can be switched back to ACTIVE mode upon GPIO or Wake-up Timer event or by a system reset.

#### 2.1.3 Reset structure

The SoC has two external negative reset sources, power-on reset and battery charger reset. Internally there are other reset sources such as WDT, GASP and switching off VDD1 domain reset. The PML is responsible for synchronizing these reset sources and distributing them in the system.

<sup>&</sup>lt;sup>2</sup>Universal Stylus Initiative (USI) defines communication standards for graphic pens

#### 2.1.4 Power domains

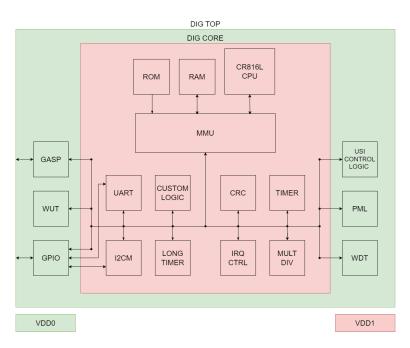

The CoolRISC implementation features two power domains to be able to switch the second one off and save power when all functions of the system are not needed at the moment. These domains are VDD0 and VDD1.

- **VDD0** domain stays switched on and powers PML (Power Management Logic), GPIO, Watchdog, Wake-up timer and the USI Control Logic.

- **VDD1** domain is switched off when the system enters POWER-DOWN mode. It stays on during other power modes. It powers the remaining blocks (for example CPU, peripherals, memory, etc.) of the system.

The voltage supplied to both power domains should be between 0.85-1.4 V.

Figure 2.2: CoolRISC SoC power domains

#### 2.1.5 Clock structure

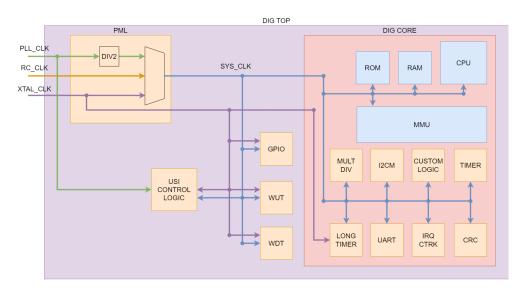

There are three main clock sources in the CoolRISC implementation.

• **RC oscillator:** Main clock source which is always running. It can provide 2 MHz, 4 MHz and 6 MHz frequencies for the system clock which can be selected by software through the PML.

- **PLL**: 8 MHz clock source which is internally divided by two (creating a 4 MHz clock) when PLL is selected as the system clock source. This clock source is generated by an external PLL. The PLL is not active at all times, it may be enabled and disabled as needed.

- **XTAL oscillator:** Secondary slower 32 kHz clock used in SLEEP and POWER-DOWN mode of the system as a system clock as well as a clock source for Watchdog timer, Wakeup timer, Long timer and GPIO.

These clock sources are then distributed through the system and controlled by the PML.

PLL 8 MHz clock source is present in the system to be able to supply 8 MHz to the USI Control Logic.

The reason for the slower XTAL oscillator clock source is to allow larger time-out intervals for timers without using large clock dividers or counters. A slower clock is also used during sleep mode to lower switching activity. Both use cases for the slower clock are to save power.

Figure 2.3: CoolRISC SoC clock structure

#### 2.1.6 Peripherals

The current CoolRISC implementation features various peripherals which will be also re-used in the new RISC-V implementation. These peripherals are accessible by the CPU on the system bus in a specified address range. Those peripherals are PML, GPIO, Wakeup-timer, Watchdog, UART, I2CM, Timer, Custom Logic, CRC, Interrupt controller, Long-timer, MultDiv and USI Control Logic.

#### 2.1.7 Software

Software running on the CPU is the "brain" of the system. It is present in the Flash which is located outside of the system. The Flash is accessed through the NVM controller implemented in the MMU. Boot code and smaller procedures are hard-wired into the ROM.

#### 2.2 CoolRISC CR816L overview

The CR816L core is a member of the CoolRISC [1] family of 8-bit microcontroller CPUs developed by the Swiss Center for Electronics and Microtechnology (CSEM) [2]. In this section, I describe the key features of the CoolRISC platform based on its documentation.

#### 2.2.1 Harvard RISC-like architecture

Instructions are stored in the instruction memory whereas general-purpose data and peripherals are stored in separate data memory. The advantage of this architecture is that it gives the CPU the capability to read instruction operands in the data memory simultaneously with one instruction fetch.

#### 2.2.2 Register-memory architecture

Instructions can operate with operands stored either in registers or in the data memory.

#### 2.2.3 Memory sizes

Maximum data memory size is 64 Kbytes. The maximum program memory size is 64 Kinstructions, where one instruction is 22-bit wide.

#### 2.2.4 Three-stage pipeline

One instruction enters the pipeline every clock cycle and it takes at most three clock cycles to execute. The pipeline does not feature branch prediction therefore it remains relatively simple.

#### 2.2.5 8bx8b multiplier

The CR816 includes an 8-bit multiplier unit which executes one 8-bit multiplication in one clock cycle.

#### 2.2.6 Stand-by mode

The HALT instruction can switch the core to halt mode in which the internal clock is stopped. The processor can be woken up using either events, interrupts or a reset. This minimizes power consumption.

#### 2.2.7 Data and peripheral bus

The CPU features its own custom 8-bit data bus for data memory and peripherals. The bus does not feature any additional decoder. Each peripheral is connected to the data bus directly and decodes the address on the data bus in its own register map.

#### 2.2.8 Instruction set

The ISA offers both RISC and CISC instructions to achieve a very dense program code. Each instruction is 22-bit wide.

#### 2.2.9 Double-latch design

The CPU uses two non-overlapping clock sources with shifted phases and the CPU is made entirely made out of D-Latch registers. This reduces the area, power consumption and STA timing requirements of the CPU.

#### 2.3 RISC-V overview

RISC-V [3] is an open-source, royalty-free ISA designed for computer processors. It was first introduced in 2010 at the University of California, Berkeley, and has since gained significant attention in the technology industry. It is a simplified and streamlined ISA that emphasizes simplicity and modularity, making it ideal for use in embedded systems and low-power devices.

#### 2.3.1 Simplicity and modularity

One of the key features of RISC-V is its simplicity. It has a reduced number of instructions compared to other ISAs, making it easier to understand and implement. Additionally, RISC-V is modular, allowing designers to choose the specific instructions and features they need for a particular application. This modularity also makes it easier to customize and optimize the ISA for specific use cases.

#### 2.3.2 Extendability

RISC-V is also designed to be extensible, meaning that new instructions and features can be added without breaking compatibility with existing software. This makes it easier to incorporate new technologies and innovations into the ISA without requiring significant changes to existing software and hardware.

#### 2.3.3 Open source

Another advantage of RISC-V is that it is open-source and royalty-free. This means that anyone can access and use the ISA without paying licensing fees, making it a cost-effective choice for many applications.

#### 2.3.4 RISC-V Foundation

To make the ISA stable and well defined the RISC-V Foundation was created in 2015 to own, maintain and publish current RISC-V ISA specifications.

"More than 3,100 RISC-V members across 70 countries contribute and collaborate to define RISC-V open specifications as well as convene and govern related technical, industry, domain, and special interest groups." [3]

#### 2.3.5 ISA architecture

The RISC-V ISA is a load-store little-endian architecture supporting 32-bit or 64-bit address space. It features 32 general-purpose registers which are 32-bit wide. It does not require data to be properly aligned for the load and store instructions. In other words, any value may be stored at any address.

However, if data is not word-aligned then the load-store unit takes extra cycles to complete an instruction.

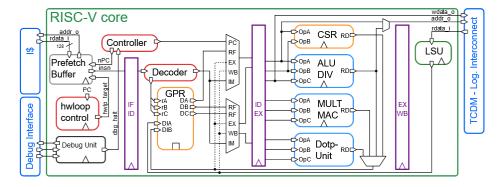

# 2.3.6 CV32E40P core

Figure 2.4: CV32E40P block diagram [4]

The CV32E40P [4] is a high-performance, low-power, 4-stage in-order 32-bit RISC-V processor core designed for embedded and IoT applications. Like CoolRISC, it uses Harvard architecture and has separate memory for instructions and data. The ISA of CV32E40P has been extended to support multiple additional instructions including hardware loops, post-increment load and store instructions and additional ALU instructions that are not part of the standard RISC-V ISA. The core also includes a debug interface and support for trace and profiling, making it easy to debug and optimize system performance.

The core is maintained by the OpenHW group [5] and it is fully verified by them which is one of the reasons why this core was selected for the implementation.

The RISC-V instruction sets supported by this core are RV32IMAC [6].

- **RV32I:** Base integer instruction which includes instructions for arithmetic, logical, and data transfer operations.

- **RV32M:** Extension to RV32I that adds instructions for integer multiplication and division.

- **RV32A**: Extension to RV32I that adds instructions for atomic memory operations.

- **RV32C:** Extension to RV32I that provides compressed 16-bit instructions to reduce code size and improve performance.

The RV32A is not needed and will not be used for the new SoC implementation to save the area and power consumption of the CPU.

The core uses Open Bus Interface (OBI) [7] protocol for instruction and data memory access. OBI is a point-to-point bus interface request-grantbased protocol developed by the OpenHW group. It is compatible with other industry bus protocols such as AMBA AHB and AMBA AXI developed by ARM.

#### 2.4 CR816L and CV32E40P difference analysis

There are many differences between the CR816L core and the CV32E40P core. The first major difference is the data/instruction/address width. The CR816L features 8-bit data operations and 22-bit instructions compared to CV32E40P which has larger width of 32 for both. This gives the CV32E40P an advantage when it comes to larger address space and a performance advantage when it comes to operations with larger data types.

#### 2.4.1 Code and data storage in the same memory

In the CoolRISC-based system, Flash memory is used for storing both code and data which means storing together 8-bit data and 22-bit instructions. This either causes poor memory utilization or requires additional logic to manage data alignment in the memory.

In comparison, the CV32E40P is 32-bit for both data and instructions. This means there are neither of these issues. Furthermore, the CV32E40P supports 16-bit compressed instructions which can be tightly packed in the memory along with 32-bit instructions because the CPU features hardware support for this.

#### 2.4.2 General Purpose Registers

The CR816L features 16 8-bit data registers which are used during code execution. In comparison, the CV32E40P (and the RISC-V ISA in general) features 32 32-bit data registers. This gives the CV32E40P an advantage in being able to store more temporary data in itself instead of storing and fetching data from memory.

#### 2.4.3 Instruction set

Comparing both instruction sets it comes clear that there are several differences between them. Arithmetic and logical operations are similar and present in both, however, the CV32E40P lacks any kind of "carry" flags in arithmetic operations.

CR816L also features a hardware stack which CV32E40P does not implement at all.

More differences are present in the branching instructions and instructions for specific comparison and bit manipulation instructions. CV32E40P does not have a direct counterpart to some of them however those instructions can be emulated by pseudo instructions which are performed by different CV32E40P instructions with specific values in operands. Such pseudo instructions can be seen in Figure 2.5

Additional instructions, which the CV32E40P offers compared to CR816L, are mainly integer division instructions and custom instructions built into the

#### 2. USI PEN CONTROLLER SOC REQUIREMENTS

core on top of the standard RISC-V instruction sets. However, the custom instructions will not be used in the new system to save area and power as their functionality is not needed.

| Mnemonic              | Instruction                       | Base instruction(s)                                  |

|-----------------------|-----------------------------------|------------------------------------------------------|

| LI rd, imm12          | Load immediate (near)             | ADDI rd, zero, imm12                                 |

| LI rd, imm            | Load immediate (far)              | LUI rd, imm[31:12]<br>ADDI rd, rd, imm[11:0]         |

| LA rd, sym            | Load address (far)                | AUIPC rd, sym[31:12]<br>ADDI rd, rd, sym[11:0]       |

| MV rd, rs             | Copy register                     | ADDI rd, rs, 0                                       |

| NOT rd, rs            | One's complement                  | XORI rd, rs, -1                                      |

| NEG rd, rs            | Two's complement                  | SUB rd, zero, rs                                     |

| BGT rs1, rs2, offset  | Branch if rs1 > rs2               | BLT rs2, rs1, offset                                 |

| BLE rs1, rs2, offset  | Branch if rs1 ≤ rs2               | BGE rs2, rs1, offset                                 |

| BGTU rs1, rs2, offset | Branch if rs1 > rs2<br>(unsigned) | BLTU rs2, rs1, offset                                |

| BLEU rs1, rs2, offset | Branch if rs1 ≤ rs2<br>(unsigned) | BGEU rs2, rs1, offset                                |

| BEQZ rs1, offset      | Branch if rs1 = 0                 | BEQ rs1, zero, offset                                |

| BNEZ rs1, offset      | Branch if rs1 ≠ 0                 | BNE rs1, zero, offset                                |

| BGEZ rs1, offset      | Branch if $rs1 \ge 0$             | BGE rs1, zero, offset                                |

| BLEZ rs1, offset      | Branch if rs1 ≤ 0                 | BGE zero, rs1, offset                                |

| BGTZ rs1, offset      | Branch if rs1 > 0                 | BLT zero, rs1, offset                                |

| J offset              | Unconditional jump                | JAL zero, offset                                     |

| CALL offset12         | Call subroutine (near)            | JALR ra, ra, offset12                                |

| CALL offset           | Call subroutine (far)             | AUIPC ra, offset[31:12]<br>JALR ra, ra, offset[11:0] |

| RET                   | Return from subroutine            | JALR zero, 0(ra)                                     |

| NOP                   | No operation                      | ADDI zero, zero, 0                                   |

Figure 2.5: RISC-V Pseudo Instructions [8]

#### 2.4.4 Multiplication/Division accelerator

The CR816L supports multiplication with 8-bit operands and 16-bit result. This multiplication takes one clock cycle to execute. The core does not feature division operation.

In comparison, the CV32E40P supports multiplication with 32-bit operands and gives lower 32-bit result while also supporting multiplication operation for the upper 32-bit result. Together this can provide 64-bit result. The lower half of the result takes one clock cycle to execute while the upper half takes five clock cycles to execute.

The core does support division operation which accepts 32-bit operands and is able to calculate the result in 3-35 clock cycles.

#### 2.4.5 Interrupts

CR816L supports 24 interrupts divided into 3 levels of priority. In comparison, the CV32E40P supports up to 1008 interrupts each with up to 255 levels of priority.

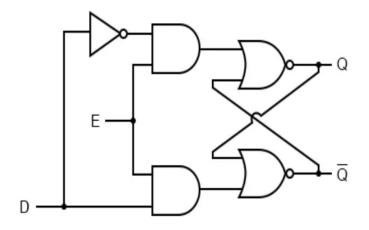

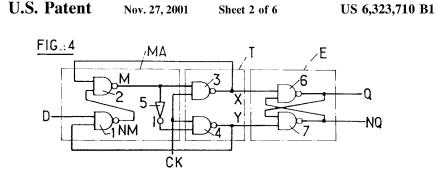

#### 2.4.6 Double latch vs. edge-based design

CV32E40P is a fully synchronous rising edge design. Meaning it is nearly fully made out of D-Flip-Flop registers. In comparison, CR816L is the direct opposite. The core is a latch-based design (or double-latch design) meaning that the core is made out of just D-latch registers.

Such a system works on a principle of two separate non-overlapping clock sources and D-latch registers being clocked by one or the other clock source.

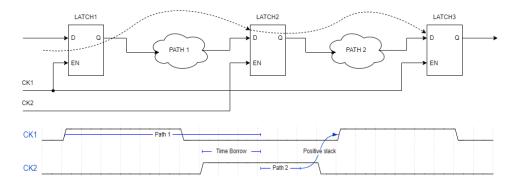

Figure 2.6: Non-overlapping clock example waveform

Data between registers is transferred in two phases. First CK1 clocked latches open for new data when CK1 is at '1', then they close when CK1 is at '0', and then CK2 clocked latches open for new data from CK1 clocked registers which are closed and stable at that moment when CK2 is at '1'.

In the pipeline, the first phase clock covers instruction prefetch and operand prefetch for ALU. The second phase clock covers the instruction decode and ALU execution.

In comparison in the edge design new data is loaded into registers on the rising (or falling) edge of the clock, and there is only one clock source for all registers (assuming the design is fully synchronous). Registers in such design are generally edge-triggered D-Flip-Flop type.

This gives the CR816L advantage in area and power consumption compared to RISC-V because latches are approximately half the size of normal D-Flip-Flop.

A D-Latch register generally consists of one inverter gate (2 transistors), two AND gates (2x6 transistors) and two NOR gates (2x4 transistors). In total, this accounts for 22 transistors. The structure of a D-Latch register is shown in Figure 2.7.

Figure 2.7: General D-Latch structure in CMOS [9]

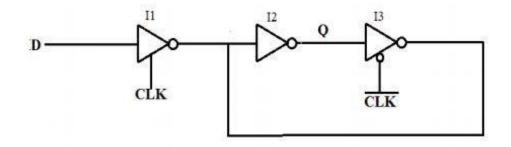

However, in practice, there is a more efficient implementation used for the D-Latch register which is built out of fewer transistors. Such D-Latch is built using Tri-State buffers in structure in Figure 2.8. This is the D-Latch structure which was used in the 180 nm technology for PENRISCV.

Figure 2.8: More efficient D-Latch structure in CMOS [10]

This structure consists only of two inverter gates (2x2 transistors) and two tri-state buffers with inverted outputs (2x4 transistors). In total this accounts for 12 transistors.

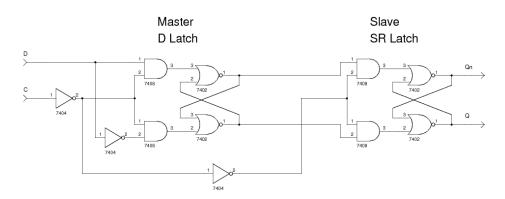

In comparison, an edge-triggered D-Flip-Flop is made out of two D-Latch structures with an additional inverter gate (meaning extra 2 transistors to the total count of 46 transistors). An example of an edge-triggered D-Flip-Flop can be seen in Figure 2.9.

Figure 2.9: General D-Flip-Flop structure in CMOS [11]

The 180 nm process technology, which was used for the CoolRISC-based system and is going to be used for PENRISCV, uses a patented structure of an edge-triggered D-Flip-Flop.

This structure, in Figure 2.10, consists of 6 NAND gates (6x4 transistors) and one inverter gate (2 transistors). This accounts for 26 transistors in total. This is the DFF structure which was used in the 180 nm technology for PENRISCV.

Figure 2.10: More efficient D-Flip-Flop structure in CMOS [12]

If we compare both register types then the D-Latch structure consists of less than half of the number of transistors of the D-Flip-Flop structure.

The other advantage (design-wise) of the double-latch design approach is that thanks to D-Latch registers, the CPU has better timing characteristics. This means that (in theory) the clock tree does not need to be so strictly balanced because it is expected that paths from CK1 to CK2 and backwards are not open at the same time. This reduces the number of required cells for the clock tree.

Better timing characteristics are thanks to **latch time borrowing** because latches are level sensitive. This can be defined as: "Time borrowing is the property of a latch by virtue of which a path ending at a latch can borrow time from the next path in the pipeline such that the overall time of the two paths remains the same. The time borrowed by the latch from the next stage in the pipeline is, then, subtracted from the next path's time." [13]

Figure 2.11: Latch time borrowing example

#### 2.4.7 System clock speed vs MIPS

One disadvantage of the double-latch design is that it makes the system run only at half of the MIPS relative to the system clock frequency. In standard rising-edge design, a CPU executes an instruction in the pipeline every clock cycle. In comparison, the CR816L requires positive pulses on both CK1 and CK3 to execute an instruction in the pipeline. This effectively means that the number of MIPS the CPU can offer equals roughly half the number of MHz of the system clock.

## 2.4.8 Software support

As CR816L was developed in 2001, meaning there is very little continuous software/compiler support for it today. There is only one compiler which is not actively developed. The only modern tool for the CoolRISC CPU platform is Ride7 IDE [14] developed by Raisonance.

In comparison, RISC-V ISA is supported by a variety of modern compilers (such as GNU GCC, CLANG and more), modern IDEs (GNU MCU Eclipse, PlatformIO and more) as well as simulators and other useful tools. These and other new tools are in active development by the RISC-V community. [15]

#### 2.4.9 Area and power consumption

In terms of area, CR816L has an advantage compared to CV32E40P. From internal measurements, CR816L has a size of around 4000 standard gate cells whereas CV32E40P ends up at around 40000. This difference will result in higher theoretical total power consumption on the CV32E40P in exchange for twice the MIPS/MHz, more instructions in the ISA and 32-bit data/instruction width.

To know if CV32E40P is a feasible alternative to CR816L in this system in terms of power and area, the system needs to be re-implemented with the new CPU and the power consumption estimated in post-layout gate level simulation.

If the CV32E40P turns out to not be a feasible alternative, the SoC implementation can still be used for testing other more efficient RISC-V cores. This is the advantage of the RISC-V ecosystem because it is the same ISA with many open-source (or even licensable) cores out there. With the same or similar interface, the CV32E40P is easily swappable for another RISC-V CPU. One that is currently being explored is the IBEX [16] RISC-V core which has a size of only around 15 000 standard gate cells.

## 2.5 Requirements for the new RISC-V pen controller SoC

Based on the analysis of the existing CoolRISC-based system and the differences between CR816L and CV32E40P cores I compiled the following requirements for the new RISC-V-based implementation of the SoC:

- 1. Perform transmission and reception of data on the pentips. Run software like CoreMark on the CPU.

- 2. Utilize the CV32E40P CPU core and minimize its area.

- 3. Use the ROM instead of Flash for software fetching. Memory Interface does not feature an NVM controller and this Flash memory will not be used for future projects anymore.

- 4. Feature the same power modes as the CoolRISC SoC.

- 5. Feature the same power domain structure as the CoolRISC SoC.

- 6. Feature the clock structure without the RC oscillator clock source. The main clock source shall be the 8 MHz PLL with a 4 MHz system clock. This is to simplify the development of the system to do the power consumption simulations because only one clock source is active during the majority of the system's operation.

- 7. Use the AHB-lite as a data bus for peripherals.

- 8. Reuse the following peripherals: PML, GPIO, Wakeup-timer, Watchdog, UART, I2CM, Timer, Custom Logic, CRC, Interrupt controller, Long-timer, and USI Control Logic. If any peripheral is too difficult to reuse for any reason, it shall be replaced with a peripheral with similar functionality.

- 9. Use the existing high-voltage pentip driver chip which was used for the CoolRISC SoC. For FPGA validation, use a manufactured sample.

- 10. DCDC control, Switch control, LED control and battery charging control do not need to be implemented in the system for power consumption results because analogue parts will be the same in both systems and will not affect the power consumption.

# CHAPTER **3**

# System design of RISC-V pen controller SoC

In this chapter, I create a system design with the necessary changes for the new RISC-V-based pen controller SoC utilising the CV32E40P core. I name the new SoC "PENRISCV".

Figure 3.1: Changes in PENRISCV SoC compared to previous SoC. Green outline = new module, Red outline = modified existing module

## 3.1 System design

- The new SoC will implement enough functionality to be able to perform transmission and reception of data on the pentips as well as run software like CoreMark on the CPU.

- The new SoC will share the same power modes and power domains.

- The clock structure will be reduced to PLL and XTAL oscillator clock. The PLL clock will replace the RC oscillator clock as the main clock source for the system. The RC oscillator is not necessary for power estimations of the digital part of the SoC and omitting it is going to make the implementation of the new SoC faster.

- The external reset structure will be reduced to just a power-on reset source as the battery charger functionality will not be implemented in the new SoC for power estimations.

- The CV32E40P core will be configured in its smallest configuration possible. Such configuration disables all custom CV32E40P instruction extensions which are not part of the standard RISC-V ISA, it sets the number of debug performance counters inside the CPU to zero and uses the latch-based version of the CV32E40P register file. This is to save as much area and power as possible as the core is expected to be much bigger than the CR816L core. The core will be placed into a new design block along with the memory interface, RAM, ROM and debug module to better structure the system hierarchy.

- Software will be fetched from the ROM instead of the Flash. The ROM will have a size of 32768 bytes. RAM will have a size of 8192 bytes.

- The memory interface is a new design block which will replace the Memory Management Unit from the previous SoC. Because CR816L and CV32E40P use different data/instruction interface the original MMU cannot be reused.

- The system bus for peripherals in the new SoC will be AMBA AHBlite [17]. AHB-lite was chosen because it is one of the compatible bus protocols the CV32E40P supports and internally in the company AHBlite already has various generating scripts to speed up integration.

- Power Management Logic will be reused and simplified/adjusted to fit in the new SoC design. Elements such as non-overlapping clocks for CoolRISC will be removed as the new SoC will be mainly a rising edgebased design. DCDC control, Switch control, LED control and battery charging control logic inside the PML will not be implemented.

- A new bus interface for peripherals means that each peripheral needs to have its register map replaced by one that is AHB-lite compliant. However, the USI Control Logic cannot be modified, it does not feature a standard register map which would be easily replaceable. It is also an externally made IP. An interface converter from AHB-lite to the CoolRISC data interface will be needed for this block.

- Current I2C Master will be replaced by a new I2C Master which is AHB-lite compliant. The previous I2C Master is not compatible with AHB-lite and new system clock structure therefore it was decided to replace it with a new I2C Master IP.

- AHB-lite requires a dedicated AHB Decoder which will manage access to peripherals based on a given address. The decoder will be created to fit the defined address space and peripherals used in the SoC.

- The previous interrupt controller will be replaced by a new one because CV32E40P and CR816L have different interfaces for interrupts. All interrupts in the system will be considered asynchronous. Interrupt sources are UART, I2CM, GPIO, WDT, WUT, and USI Control logic.

- The GASP interface and custom CoolRISC debug module was used for debugging in the previous SoC. The GASP interface will be replaced by JTAG and the debug module will be replaced by RISC-V specific debug module.

- UART interface will be connected directly to the top and not through GPIO. This is to make the debugging easier.

## 3.1.1 Top interface

Top interface signals are described in tables 3.1, 3.2, 3.3 and 3.4.

| Generic name        | Description                                        |

|---------------------|----------------------------------------------------|

| G_ACTIVE_EDGE_LVL   | Active edge level (rising/falling) of the system   |

| G_ACTIVE_EDGE_LVL_N | Negative edge level (rising/falling) of the system |

| G_IO_ADDR_WIDTH     | Address width of AHB                               |

| G_IO_DATA_WIDTH     | Data width of AHB                                  |

| G_REG_ADDR_OFFSET   | Register offset of AHB peripherals                 |

| G_TARGET_TECH       | Target technology. '0' for ASIC, '1' for FPGA      |

Table 3.1: PENRISCV top interface - generics

## 3. System design of RISC-V pen controller SoC

| Signal name            | Description                                    |

|------------------------|------------------------------------------------|

| clk_i                  | Main 8 MHz clock from PLL                      |

| clk_32khz_i            | 32 kHz clock from XTAL oscillator              |

| rst_ni                 | Power-on negative asynchronous reset           |

| test_en_i              | Test mode enable                               |

| idcode_i               | IDCODE for JTAG TAP                            |

| tck_i                  | JTAG test clock pad                            |

| tms_i                  | JTAG test mode select pad                      |

| trst_ni                | JTAG test reset pad                            |

| td_i                   | JTAG test data input pad                       |

| td_o                   | JTAG test data output pad                      |

| tdo_oe_o               | Data out output enable                         |

| DoC_and_core_acc_dis_i | disable all access except for SBA              |

| uart_rxd               | RXD pad of UART                                |

| uart_txd               | TXD pad of UART                                |

| core_busy_o            | Indicator signal that CPU is not in sleep mode |

| dmi_req_active_o       | DMI Clock Request                              |

| vdd1_sleep_ack_n       | Acknowledge signal for VDD1 switching          |

| pml_xtalosc_en         | XTAL oscillator enable                         |

Table 3.2: PENRISCV top interface - Main signals  $% \left( {{{\rm{A}}_{{\rm{B}}}} \right)$

| Signal name   | Description                                     |

|---------------|-------------------------------------------------|

| pp_data       | Pen pressure data                               |

| pp_rdy        | Pen pressure ready                              |

| usi_pp_cpmd   | Pen pressure compare                            |

| usi_pp_oe     | Pen pressure output enable                      |

| usi_pp_ck_32k | Pen pressure 32 kHz clock                       |

| usi_pll_en    | PLL enable                                      |

| usi_pp_run    | Pen pressure run                                |

| usi_pp_double | Pen pressure double run                         |

| sw_data       | Switch data                                     |

| pll_rdy       | PLL ready                                       |

| pll_err       | PLL error                                       |

| hv_spi_cs     | SPI chip select for HV pentip driver            |

| hv_spi_ck     | SPI clock for HV pentip driver                  |

| hv_spi_do     | SPI data to from dig_top to HV pentip driver    |

| hv_spi_do_oe  | SPI data output enable for HV pentip driver     |

| hv_spi_di     | SPI data input from HV pentip driver to dig_top |

| hv_es_rx0     | Data from pentip 0                              |

| hv_es_rx1     | Data from pentip 1                              |

| hv_p0en       | Pentip 0 enable                                 |

| hv_p1en       | Pentip 1 enable                                 |

| hv_ulen       | Uplink enable                                   |

| hv_es_tx0     | Data to pentip 0                                |

| hv_es_tx1     | Data to pentip 1                                |

| hv_reset_n    | HV pentip driver reset                          |

Table 3.3: PENRISCV top interface - USI Control Logic signals

Table 3.4: PENRISCV top interface - GPIO signals

| Signal name  | Description                |

|--------------|----------------------------|

| pa_in        | GPIO pads input            |

| pa_in_en     | GPIO pads input enable     |

| pa_out       | GPIO pads output           |

| pa_pu        | GPIO pads pull-up enable   |

| pa_oe        | GPIO pads output enable    |

| pa_i2c_pu_en | GPIO I2C pull-up enable    |

| pa_i2c_od    | GPIO I2C open-drain enable |

| pa_i2c_q     | GPIO I2C output signals    |

## 3.1.2 Memorry address mapping

Addresses for each memory can be found in Table 3.5.

| Memory            | Base address (hexadecimal) |

|-------------------|----------------------------|

| ROM               | 0x00008000                 |

| RAM               | 0x00010000                 |

| Debug Module      | 0x00015000                 |

| Peripherals (AHB) | 0x00020000                 |

Table 3.5: Memory address mapping

## 3.1.3 Peripheral address mapping

Addresses for each peripheral can be found in Table 3.6.

| Peripheral        | Base AHB address (hexadecimal) |

|-------------------|--------------------------------|

| IRQ Ctrl          | 0x0000                         |

| UART              | 0x0400                         |

| I2CM              | 0x0800                         |

| Timer             | 0x0C00                         |

| Custom Logic      | 0x1000                         |

| CRC               | 0x1400                         |

| WDT               | 0x1800                         |

| WUT               | 0x1C00                         |

| Long Timer        | 0x2000                         |

| GPIO              | 0x2800                         |

| USI Control Logic | 0x2C00                         |

| PML               | 0x3000                         |

Table 3.6: Peripheral address mapping

## 3.2 FPGA vs ASIC implementation

In this section, I describe the differences and limitations between FPGA and ASIC and how they affect the design implementation.

#### 3.2.1 FPGA's clocking resources

FPGAs are limited in some ways for implementing digital designs. One of the limiting factors is the limited number of clock tree resources. In an ASIC, a clock tree is created and balanced in the place-and-route step of the design. However, FPGA only has a set number of pre-balanced clock trees and corresponding buffers for its registers. This limits the number of separate clocks in the design and other constructs such as clock gating or clock multiplexing. [18]

### 3.2.2 FPGA LookUp Tables

Another limiting factor of FPGAs is the fact that when a design is placed onto the FPGA, it is not made out of standard gates as it would be on an ASIC. The design will be implemented onto the FPGA using its Lookup Tables (LUTs), Flip-Flop registers, Block RAM modules, etc.

"The LUT is the basic building block of an FPGA and is capable of implementing any logic function of N Boolean variables." [19]

For normal synchronous designs without any special constructs, this is not an issue. However, when a design features specific structures made out of basic gates to ensure required behaviour, issues may arise in the design.

For example, a design may feature some specific logic constructs which are made out of specific basic gates to ensure glitch-free output (for example clock gates). Another example may be a debouncer structure.

In an ASIC you can simply hand-build these structures using basic gates and you can be (almost) sure that the structure will be present in the design after synthesis exactly as you designed it.

In an FPGA there are no basic gates. There are only LUTs configured to give desired output based on the boolean function that is defined by the RTL code. Since this is a LUT and not a basic gate, it cannot be guaranteed that the output will have the same glitch-free characteristics as the basic gate on ASIC.

Furthermore, the FPGA synthesis tool may optimize the design and the boolean functions and the final implementation may have different characteristics while giving the same output.

#### 3.2.3 FPGA register asynchronous set and reset

Another limitation of an FPGA is that a design cannot use both asynchronous sets and reset at the same time. Only one may be implemented at the time.

"The flip-flops in Xilinx FPGAs can support both asynchronous and synchronous reset and set controls. However, the underlying flip-flop can natively implement only one set / reset / preset / clear at a time." [20]

This is not an issue when implementing a fully synchronous design on an FPGA, however, it may be an issue when specialized constructs are being implemented, which require this both set and reset. This is for example a register which has its value loaded into it asynchronously. Then this implementation needs to utilise both asynchronous set and reset.

# CHAPTER 4

## Implementation

In this chapter, I describe the RTL implementation of the new pen controller SoC with RISC-V CPU. I also describe the implementation of the test bench for its verification.

Before beginning the RTL implementation, I studied how the CoolRISCbased system was implemented in detail. This helped me when creating the new implementation. The old implementation served as a reference when creating the new implementation.

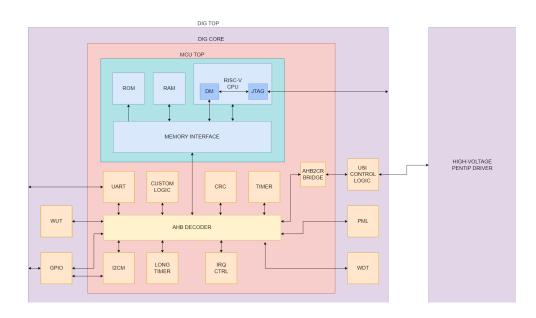

Figure 4.1: New RISC-V pen controller SoC - PENRISCV

## 4.1 mcu\_top

I decided to use a combination of SystemVerilog and VHDL for the implementation. This was not a problem as modern simulators support mixed language simulation.

To start the implementation, I first created the mcu\_top module from the SoC block diagram4.1 which contained the CPU, Debug Module, JTAG, Memory Interface, RAM and ROM. I reused a module which contained the CPU and Debug Module. This module was provided to me by the company.

Next, I modified an XML file for the script that generated the Memory Interface. This script was provided to me by the company. In the XML file, I defined the interface properties for the module, as well as the address ranges for RAM, ROM, Debug Module, and peripheral access. Based on this definition, the script generated a Memory Interface module in SystemVerilog that included interfaces for the CPU and the interfaces defined in the XML file.

RAM and ROM were implemented in the form of a SystemVerilog RTL model. These models were also generated by the company's script using an XML definition. These modules were replaced by actual technology cell models later in the Physical implementation chapter.

## $4.2 \quad \text{dig}_{-}\text{core}$

After creating the mcu\_top module I moved to the dig\_core module which contained the mcu\_top, AHB-lite decoder, UART, I2C Master, Custom Logic, CRC, Timer, Long Timer and IRQ Ctrl.

For the AHB-lite decoder and the IRQ Ctrl, I used another script provided to me by the company to generate them. AHB-lite decoder was defined by an XML similarly to Memory Interface. Each peripheral had a specified base address and range in the XML. Based on this definition the decoder was generated as a SystemVerilog module.

The IRQ Ctrl also had an XML definition with required interrupt sources and the type of each interrupt. All interrupts in this design were considered asynchronous.

#### 4.2.1 Peripherals

The remaining peripherals are going to be reused (I2CM is going to be reused from a different project). However, first, peripherals needed to have their register maps and data interface adjusted to be AHB-lite compliant.

To do this I used the company's scripts for register map generation. The script can receive a PERL register map definition and generate a register map block in VHDL based on given register templates.

For each peripheral, I created its own PERL register map definition. When creating each definition I tried to keep the same register structure as in the CoolRISC SoC implementation. Because of the move from an 8-bit to a 32-bit system, I decided to merge some registers into one where it made sense and would not affect functionality.

After generating new register maps for all peripherals, I integrated them into each peripheral.

I did this process for peripherals located outside of the dig\_core block as well. The only exception is the USI Control Logic which cannot be modified with a new register map.

Some reused peripherals feature CK3 clock input even after the register map adjustments. That is because those peripherals may be using the CK3 clock internally. I connected the standard system clock to this clock source after verifying that it will not affect the functionality of the peripheral.

#### 4.2.2 AHB2CR bridge

To connect the USI Control Logic, which still uses the CoolRISC data bus interface, to the AHB-lite bus, I needed to create an interface converter. After studying both AHB-lite and CoolRISC data bus protocol I came up with a solution.

| Signal name | Description                                                 |

|-------------|-------------------------------------------------------------|

| ck1         | Phase 1 system clock                                        |

| ck3         | Phase 2 system clock                                        |

| dm_e        | Active transaction on the bus                               |

| read_nwrite | '1' for the read transaction, '0' for the write transaction |

| dm_addr     | Address from the CPU to peripheral                          |

| wdata       | Data from the CPU to peripheral                             |

| rdata       | Data from peripheral to CPU                                 |

Table 4.1: CoolRISC data bus interface

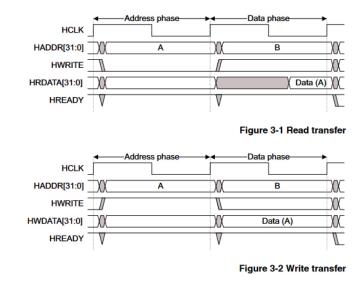

The CoolRISC data bus protocol executes a transaction in two steps. The first step is the start of a transaction by asserting the  $dm_-e$ ,  $read_-nwrite$ ,  $data_-out$  and  $dm_-addr$  signals. Because this is a double latch-based design the  $dm_-e$ ,  $read_-nwrite$ ,  $data_-out$  and  $dm_-addr$  signals are latched when CK1 is high.

The second step is data access. A write access can start on the falling edge of the CK1 signal and for read access, the read data is latched when CK3 is high. In PENRISCV there was only a single clock source for the system clock. This means that the first step described above would happen on the first rising edge of the clock. The write access would happen on the second rising edge of the clock. Read access data would be available on the third rising edge of the clock.

| Signal name | Description                                                                            |

|-------------|----------------------------------------------------------------------------------------|

| hclk        | System (bus) clock                                                                     |

| hsel        | Decoded peripheral bus select                                                          |

| hwrite      | Bus transfer direction indication. '0' for read transaction, '1' for write transaction |

| haddr       | Address from the AHB master to peripheral                                              |

| htrans      | Transfer type                                                                          |

| hsize       | Transfer size per clock                                                                |

| hready_in   | Bus ready (from bus multiplexer, indicates CPU bus is in a wait state)                 |

| hwdata      | Write data bus                                                                         |

| hready_out  | Ready output (used to insert bus wait states based on peripheral response rate)        |

| hrdata      | Read data bus                                                                          |

| hresp       | Bus transfer response $(0 = OK, 1 = ERROR)$                                            |

Table 4.2: AHB-lite bus interface