### Assignment of master's thesis

| Title:                   | Modular Compiler for the TinyC Language    |

|--------------------------|--------------------------------------------|

| Student:                 | Bc. Martin Prokopič                        |

| Supervisor:              | Ing. Petr Máj                              |

| Study program:           | Informatics                                |

| Branch / specialization: | System Programming                         |

| Department:              | Department of Theoretical Computer Science |

| Validity:                | until the end of summer semester 2023/2024 |

#### Instructions

Familiarize yourself with the syntax and semantic of the TinyC language used in the NI-GEN course. Analyze the current C++ specific toolchain and determine how to extend it to support other implementation languages. As a proof of concept, design and implement optimizing compiler for the tinyC language in Scala compatible with the existing toolchain (including the tiny86 VM). Pay close attention to how advanced algorithms from compiler construction can be implemented in the Scala language in an idiomatic and clean way useful for educational purposes. Evaluate your design choices.

Electronically approved by doc. Ing. Jan Janoušek, Ph.D. on 24 November 2022 in Prague.

Master's thesis

## Modular Compiler for the TinyC Language

Bc. Martin Prokopič

Department of Theoretical Computer Science Supervisor: Ing. Petr Máj

May 4, 2023

# Acknowledgements

First and foremost, I would like to thank my supervisor, Ing. Petr Máj, for his guidance and expertise in the field of compiler construction, which made this work possible. I would also like to extend my thanks to doc. Ing. Filip Křikava, Ph.D. for introducing me to the world of Scala and functional programming in general as part of the BIE-OOP and NIE-APR courses. Finally, I would like to thank my loving family, whose support has been instrumental in my academic and personal success.

## Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. In accordance with Article 46 (6) of the Act, I hereby grant a nonexclusive authorization (license) to utilize this thesis, including any and all computer programs incorporated therein or attached thereto and all corresponding documentation (hereinafter collectively referred to as the "Work"), to any and all persons that wish to utilize the Work. Such persons are entitled to use the Work in any way (including for-profit purposes) that does not detract from its value. This authorization is not limited in terms of time, location and quantity. However, all persons that makes use of the above license shall be obliged to grant a license at least in the same scope as defined above with respect to each and every work that is created (wholly or in part) based on the Work, by modifying the Work, by combining the Work with another work, by including the Work in a collection of works or by adapting the Work (including translation), and at the same time make available the source code of such work at least in a way and scope that are comparable to the way and scope in which the source code of the Work is made available.

In Prague on May 4, 2023

. . .. . . . . . . . . . . . . . . .

Czech Technical University in Prague Faculty of Information Technology © 2023 Martin Prokopič. All rights reserved. This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its

usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

#### Citation of this thesis

Prokopič, Martin. *Modular Compiler for the TinyC Language*. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2023.

## Abstrakt

Tato práce popisuje překladač jazyka tinyC do assemberu virtuálního stroje tiny86 (oboje používané v předmětu NIE-GEN). Překladač je implementován v jazyce Scala, je napojen na existující nástroje používané v předmětu, podporuje všechny konstrukty jazyka tinyC a pro generování kódu používá pokročilé algoritmy. Hlavní části překladače (frontend, middleend, backend) jsou jasně odděleny a lze je využívat buď ze Scaly nebo externě pomocí vlastního textového mezikódu ve stylu LLVM. Díky své jednoduchosti a modularitě je překladač vhodný pro výukové účely.

**Klíčová slova** překladač, pokrývání stromu, barvení grafu, tinyC, tiny86, Scala

## Abstract

This thesis introduces an ahead-of-time compiler for the tinyC language targeting the tiny86 VM (both used in the NIE-GEN course) implemented in Scala. The compiler seamlessly integrates with the existing toolchain, supports all tinyC features and uses tree covering instruction selection and graphcoloring register allocation. The main modules (frontend, middleend, backend) are cleanly separated and can be extended either from Scala, or externally through a custom text-serializable LLVM-like SSA intermediate representation, which encourages use of the compiler for educational purposes.

Keywords compiler, tree covering, graph coloring, tinyC, tiny86, Scala

# Contents

| 1        | Intr | roduction 1                                     |

|----------|------|-------------------------------------------------|

|          | 1.1  | A Modular Compiler                              |

|          | 1.2  | TinyC                                           |

|          | 1.3  | Tiny x86                                        |

|          | 1.4  | Scala                                           |

|          | 1.5  | Previous Work                                   |

|          | 1.6  | Thesis Outline                                  |

| <b>2</b> | Inte | ermediate-Code Generation and Optimization 7    |

|          | 2.1  | String Parsing Theory                           |

|          | 2.2  | Lexical and Syntax Analysis                     |

|          | 2.3  | Semantic and Type Analysis                      |

|          | 2.4  | Intermediate Representation                     |

|          | 2.5  | Compiling Source Code to IR                     |

|          | 2.6  | Converting IR into SSA Form                     |

|          | 2.7  | Optimizations                                   |

| 3        | Inst | cruction Selection 29                           |

|          | 3.1  | Overview of Instruction Selection Techniques 30 |

|          | 3.2  | Tree Covering                                   |

|          | 3.3  | Phi Node Elimination                            |

|          | 3.4  | Macro Expansion                                 |

| <b>4</b> | Reg  | sister Allocation and Assignment 43             |

|          | 4.1  | A Simple Local Register Allocator               |

|          | 4.2  | Liveness Analysis                               |

|          | 4.3  | Register Allocation by Graph Coloring           |

|          | 4.4  | Linear Scan Register Allocation                 |

|          | 4.5  | Post Processing                                 |

| <b>5</b>     | Design and Implementation                                                                          | 57  |

|--------------|----------------------------------------------------------------------------------------------------|-----|

|              | 6.1 Design Goals                                                                                   | 57  |

|              | 5.2 Extending the NIE-GEN Toolchain                                                                | 58  |

|              | 5.3 Parsing and Typechecking TinyC                                                                 | 60  |

|              | 5.4 Semantic and Type Analysis                                                                     | 62  |

|              | 5.5 Intermediate Representation                                                                    | 63  |

|              | 5.6 Compiling TinyC to IR                                                                          | 68  |

|              | 5.7 The Optimizer $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 70  |

|              |                                                                                                    | 71  |

|              | 5.9 Instruction Selection                                                                          | 72  |

|              | 5.10 Register Allocation                                                                           | 74  |

|              | 5.11 Post Processing                                                                               | 76  |

|              | 5.12 Implementation                                                                                | 77  |

|              | 5.13 Documentation                                                                                 | 81  |

| 6            | Evaluation                                                                                         | 83  |

|              | 0.1 Unit Tests                                                                                     | 83  |

|              | 5.2 Integration and End to End Tests                                                               | 83  |

|              | B.3 Benchmarks                                                                                     | 84  |

| Co           | clusion                                                                                            | 89  |

|              | Future Work                                                                                        | 89  |

| Bi           | liography                                                                                          | 91  |

| $\mathbf{A}$ | Acronyms                                                                                           | 97  |

| в            | User Guide                                                                                         | 99  |

|              | 3.1 Building                                                                                       | 99  |

|              | B.2 Usage                                                                                          | 100 |

|              | 3.3 Supported TinyC Features                                                                       | 102 |

| С            | R Grammar                                                                                          | 103 |

| D            | Contents of the Electronic Attachment                                                              | 107 |

# **List of Figures**

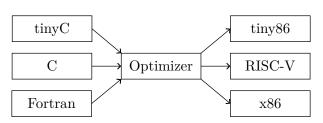

| 1.1  | A modular compiler supporting 3 different languages and targets                                       | 2  |

|------|-------------------------------------------------------------------------------------------------------|----|

| 2.1  | $\delta_1$ for grammar $G_1 = (\{E, T, F\}, \{+, *, (, ), a\}, \delta_1, E)$                          | 8  |

| 2.2  | $\delta_2$ for grammar $G_2 = (\{E\}, \{+, *, (, ), a\}, \delta_2, E)$                                | 8  |

| 2.3  | A parse tree and two different derivations of $a + a$ in $G_2$                                        | 9  |

| 2.4  | Two possible parse trees for the sentence $a + a * a$ in $G_2$                                        | 9  |

| 2.5  | A modified grammar $G'_2$ with removed left recursion and new start                                   |    |

|      | symbol $S$                                                                                            | 10 |

| 2.6  | Productions of $G_3$ demonstrating the dangling-else problem                                          | 12 |

| 2.7  | A PEG $P_1 = (\{S, E, T, F, A\}, \{+, *, (, ), a\}, R, S)$ , where R is writ-                         |    |

|      | ten above                                                                                             | 14 |

| 2.8  | An example of (a) parse tree (as parsed by grammar from fig. 2.1)                                     |    |

|      | and (b) equivalent AST for expression $(a) + a * a$                                                   | 16 |

| 2.9  | A simple C program demonstrating the limitations of tree-address                                      |    |

|      | code. (a) shows the original code and (b) the equivalent three-                                       | 10 |

| 0.10 | address code, where each statement does only a single operation.                                      | 19 |

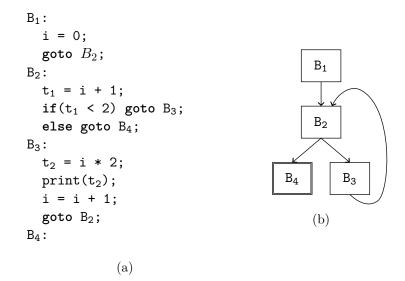

| 2.10 | (a) the program from fig. 2.9b lowered into a set of basic blocks                                     |    |

|      | and (b) its basic block control-flow graph. $B_1$ is the entry point, $B_4$ is the only ovit point    | 20 |

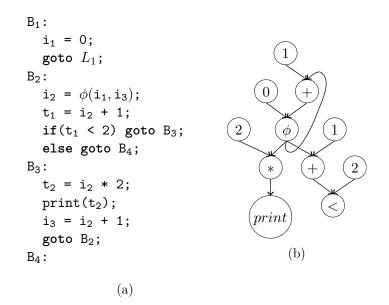

| 0.11 | is the only exit point. $\dots$ A SSA form of the program from fig. 2.10a. We use the $\phi$ -node to | 20 |

| 2.11 | join values of <i>i</i> coming from $B_1$ and $B_3$ . (b) then shows a DFG of                         |    |

|      | the program, where the $\phi$ -node completes a cycle                                                 | 21 |

| 2.12 | An example of a LLVM IR of a simple C program (a) before and (b)                                      |    |

| 2.12 | after optimizations (clang-16 -O1). Function inlining together with                                   |    |

|      | constant propagation have determined that $\mathbf{x}$ is always truthy, so                           |    |

|      | the compiler could replace the if statement with its body. Strength                                   |    |

|      | reduction also replaced multiplication by two with a left shift. (c)                                  |    |

|      | shows the original C source code                                                                      | 27 |

|      |                                                                                                       |    |

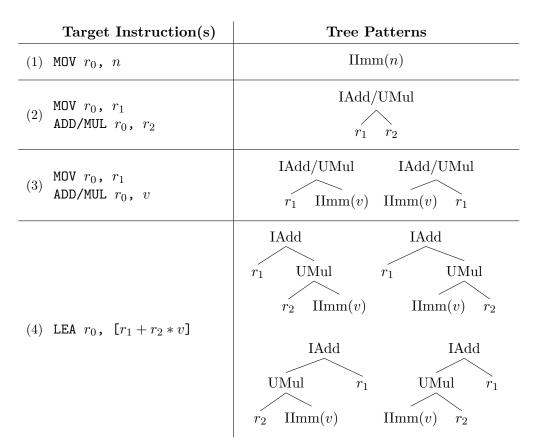

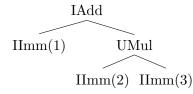

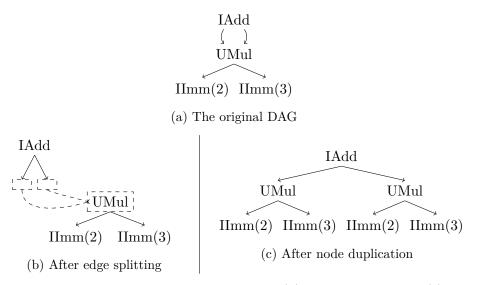

3.1 An intermediate representation of the expression 1 + 2 \* 3. ... 31

| 3.2 | An example showing the effect of (b) edge splitting and (c) node<br>duplication on a common subexpression. After edge splitting the |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

|     | UMul is evaluated only once and its result is stored in a register.                                                                 | 36 |

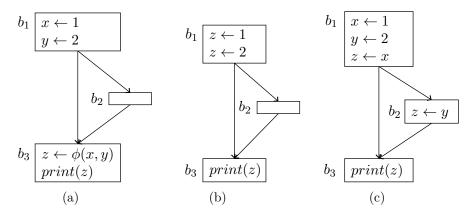

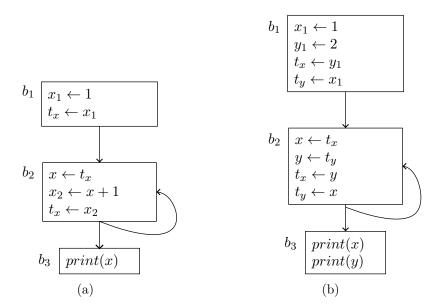

| 3.3 | An example of a shortcoming of naive $\phi$ -node elimination. (a)                                                                  | 00 |

| 0.0 | shows the original CFG, (b) shows the incorrect result of merging                                                                   |    |

|     | the $x, y$ and $z$ variables, which was corrected in (c) by inserting                                                               |    |

|     | copy statements.                                                                                                                    | 38 |

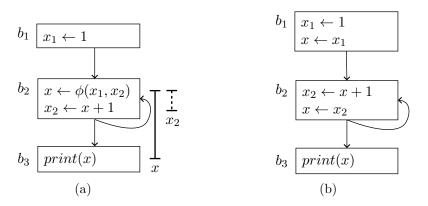

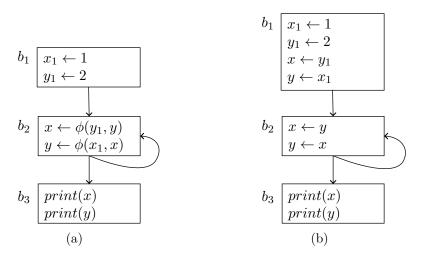

| 3.4 | An example demonstrating the lost-copy problem when we hoist a                                                                      | 00 |

| 0.1 | copy across a critical edge. The program in (b) incorrectly prints                                                                  |    |

|     | the value of $x$ from the last instead of the penultimate iteration.                                                                | 39 |

| 3.5 | An example of the swap problem, the program in (b) is incorrect.                                                                    | 40 |

| 3.6 | A corrected version of (a) the lost copy and (b) swap problem                                                                       |    |

|     | examples by introducing temporary variables $t_x$ and $t_y$                                                                         | 40 |

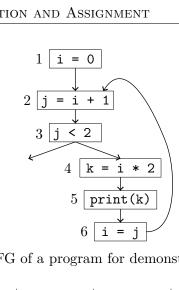

| 4.1 | Example CFG of a program for demonstrating liveness analysis.                                                                       | 46 |

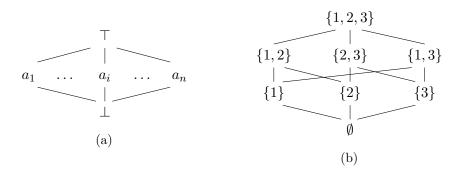

| 4.2 | Hasse diagram of (a) a flat lattice and (b) a powerset lattice                                                                      | 47 |

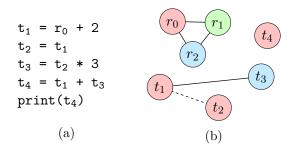

| 4.3 | A sample source code and a corresponding colored interference                                                                       |    |

|     | graph with three precolored physical registers $r_1$ , $r_2$ and $r_3$ . $t_1$                                                      |    |

|     | and $t_2$ do not interfere, because they are related only by a move.                                                                | 49 |

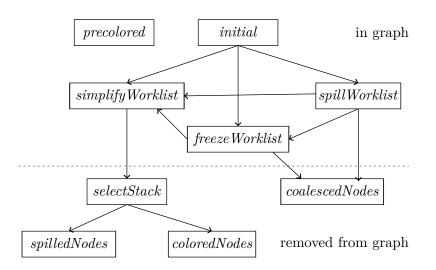

| 4.4 | Diagram of phases of the graph coloring register allocation algorithm                                                               | 49 |

| 4.5 | Lifecycle diagram of a node during register allocation                                                                              | 53 |

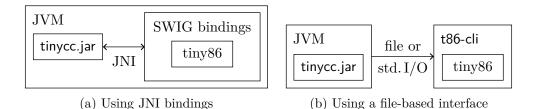

| 5.1 | Two variants of integrating our compiler (tinycc.jar) with tiny86, in                                                               |    |

|     | (a) tiny86 runs inside the JVM together with the compiler and in                                                                    |    |

|     | (b) the applications are separated on the OS level and communicate                                                                  |    |

|     | using files                                                                                                                         | 58 |

| 5.2 | Compilation of a tinyC function which accepts and returns a struct.                                                                 |    |

| 5 0 | The structures are passed by reference and copied by the callee                                                                     | 69 |

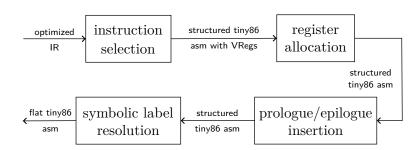

| 5.3 | Diagram of the backend architecture                                                                                                 | 71 |

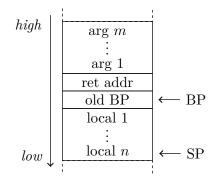

| 5.4 | Stack layout after entering a function. The first argument is at [BP                                                                |    |

|     | + 2], the first local variable is at $[BP + -1]$                                                                                    | 74 |

| 5.5 | Spilling VF7 requires a new integer temporary VR9, which the inte-                                                                  | 74 |

| 56  | ger register allocator later assigns to R0                                                                                          | 74 |

| 5.6 | register-specific information and additional spilling-related code.                                                                 | 80 |

|     | register-specific information and additional spinnig-related code.                                                                  | 00 |

# List of Tables

| 2.1          | FIRST and FOLLOW sets for $G'_2$                                                                                                                                                                                                                                                      | 11 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $2.2 \\ 2.3$ | A parsing table for grammar $G_2$                                                                                                                                                                                                                                                     | 11 |

|              | for typechecking listing 2.2. $I$ stands for an integer literal, $E$ for<br>an expression and $X$ for a program variable (functions are treated<br>as values) [1]                                                                                                                     | 18 |

| 3.1          | A simple pattern set for a tree-based IR and tiny86-like target language. The LEA instruction can be used to perform combined multiply-add operation in a single instruction                                                                                                          | 31 |

| 4.1          | Steps of the iterative solver for the CFG from fig. 4.1                                                                                                                                                                                                                               | 46 |

| 5.1          | Mapping between PEG expressions and our combinator library                                                                                                                                                                                                                            | 61 |

| 6.1          | Comparison of size and performance of generated code with and<br>without enabled SSA construction. With enabled optimizations,<br>the code is in both cases smaller and the program finishes execution<br>faster.                                                                     | 87 |

| 6.2          | Comparison of size and performance of generated code by our com-<br>piler (tinycc) with a different, older compiler (tinyc) with only rudi-<br>mentary instruction selection and a simple local register allocator.<br>tinycc produces smaller and faster code for both programs. The |    |

|              | numbers in the second column are different from table 6.1 because<br>here they include the required <b>printnum</b> implementation                                                                                                                                                    | 87 |

# List of Listings

| 4  | .1 An example of printing a string to standard output in tinyC using the builtin print.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.1          |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 5  | .2 An example of Scala 2 code with an immutable list and pattern matching.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.2          |

| 17 | .1 An example of variable shadowing in tinyC and C since the C99 revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.1          |

| 18 | .2 A simple $\mu$ C program which demonstrates type inference. The type of x and y is not known until after the call expression                                                                                                                                                                                                                                                                                                                                                                                                               | 2.2          |

| 32 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.1          |

| 33 | The first pattern matches a $+=$ operator if the result should be<br>stored in the A register, the first operand is an integer argument<br>stored in A register and the second operand is a NAME node. If<br>the match succeeds, the compiler emits the assembly code (after<br>expanding the AL and AR macros) and replaces the matched IR<br>subtree with the left subtree (RLEFT). The second pattern is<br>used for matching +, -,  , & and ^ arithmetic operators and<br>uses the OI macro and   operator for more concise notation. [2] | 3.2          |

| 59 | .1 The VM crashed as a result of loading from invalid memory address -1 after it fetched the MOV instruction on address 5 even though it was never going to be executed.                                                                                                                                                                                                                                                                                                                                                                      | 5.1          |

| 61 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.2          |

| 61 | v a a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.3          |

| 68 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.4          |

| 00 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $5.4 \\ 5.5$ |

| 73 | instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | J.J          |

| 76 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.6          |

| 10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.0          |

| 5.7 | Example of how the single-purpose classes can be combined to compile a tinyC source code into IR. We also provide a conve- |    |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

|     | nience function to do these steps at once.                                                                                 | 78 |

| 5.8 | Using Scala class composition to construct and run a tiny86                                                                |    |

|     | maximal munch instruction selector with the default rules<br>et                                                            | 80 |

| 6.1 | factorize.c: A program for computing prime factors of a positive                                                           |    |

|     | integer.                                                                                                                   | 84 |

| 6.2 | collatz.c: A program that prints the number of reduction steps                                                             |    |

|     | required to reach 1 from a positive starting integer $n$                                                                   | 85 |

| 6.3 | A complete listing of void collatz(int) from collatz.c com-                                                                |    |

|     | piled by tinycc with optimizations. The tiny86 assembly does                                                               |    |

|     | not support symbolic labels, so they are represented as comments.                                                          | 88 |

|     |                                                                                                                            |    |

CHAPTER **]**

## Introduction

The Compiler Construction (NIE-GEN) course teaches tens of FIT CTU students every year how to design and implement a compiler from start to finish, focusing mostly on the optimizer and target code generation (backend) parts. Each student is provided with a copy of the NIE-GEN Toolchain, which contains a parser for tinyC, a low-level C-like programming language [3], and the tiny86 virtual machine to be used as the target.

Although the tinyC parser is complete and the tiny86 VM has features that make it excellent for teaching purposes, the only way to interact with them is through a C++ API [4]. It means that without creating bindings for another language (which is a lot of additional work for an already extensive project) the student has to implement the entire compiler in C++.

The goal of this thesis is to design a modular compiler for tinyC in Scala (a modern high-level language [5]) that integrates well with the existing toolchain and which can be stripped down to be used as a foundation for NIE-GEN students to build their compiler projects on. We evaluate suitability of Scala by selecting and implementing some advanced techniques from compiler construction, chosen with the goal of exploiting most of the features provided by the tiny86 VM.

#### 1.1 A Modular Compiler

Designing a compiler is a substantial project, which requires knowledge from multiple fields of computer science. To make the development process more tractable, we usually split the compiler into three parts – the frontend, the middleend (optimizer), and the backend. They work together to translate a source code in one language into another accepted by the target.

Programming in the (usually higher-level) source language is more pleasant and a good optimizing compiler can make better decisions than a programmer ever could if they have chosen to code in the target language directly.

#### 1. INTRODUCTION

Figure 1.1: A modular compiler supporting 3 different languages and targets.

#### 1.1.1 Frontend

The frontend is responsible for analyzing the source code and translating it into an intermediate representation that is then processed by the rest of the compiler. The frontend is the only part dependent on the source language.

Lexical Analysis First, a lexical analyzer scans the source code into a sequence of tokens (e.g. an identifier, an operator, or an integer or string literal) while also removing whitespace and comments.

**Syntax Analysis** A parser then uses a grammar to build an abstract syntax tree, which captures the structure of the program. This is a well-researched part of computer science and in section 2.1 we describe two techniques – LL(1) parsing and parser expression grammars.

**Semantic Analysis** The grammar used by the parser cannot capture all of the intricacies of the source language. The semantic analyzer links identifiers to their declarations, determines the type of each expression according to the rules of the language and optionally performs some additional checks.

**Intermediate Code Generation** The remainder of the frontend then takes the AST annotated with type and other semantic information and translates it into an unified intermediate representation (more in section 2.4). The compiler uses the IR as an abstraction over all supported source and target languages, which is the main tool enabling its modularity. Instead of developing  $N \cdot M$ specialized compilers for each combination of N source and M target languages, we implement only N frontends and M backends that use a shared optimizer (see fig. 1.1).

#### 1.1.2 Middleend (Optimizer)

The middleend takes IR produced by the frontend and optimizes it using language-independent passes. Thanks to the shared optimizer, both frontends and backends can be much simpler and easier to maintain. We mention optimizations such as SSA construction and constant propagation in sections 2.6 and 2.7, both of which can significantly improve efficiency of the generated code.

#### 1.1.3 Backend

The last part of a compiler is the backend, which is responsible for generating the target code from the optimized intermediate representation produced by the previous stages.

**Instruction Selection** First, the instruction selector implements the IR program using the best combination of machine instructions in respect to execution speed, code size or some other criterion. We describe two popular techniques, macro expansion and tree covering, in chapter 3.

**Register Allocation and Assignment** The code generated by the instruction selector uses an unlimited amount of temporaries, but the target provides only a fixed amount of physical registers. The register allocator determines whether a temporary should be stored in a register or spilled to the (slower) memory. This is a NP-complete problem [6], but we show two heuristic methods producing good results in chapter 4.

**Target-Dependent Optimizations** After register allocation, the compiler has the last opportunity to perform target-specific optimizations. This is often a peepholer pass, which can make up for a simpler instruction selector by replacing common patterns in the target code with their optimal alternatives.

#### 1.2 TinyC

The first part of the NIE-GEN toolchain is the tinyC parser. TinyC is a simplified subset of the C programming language, designed for teaching compilers and code generation. Just like C, it is a general-purpose programming language suitable for writing portable code, which can then be executed on different targets. It is a relatively "low level" language, which means that it does not deal with objects or more complex data structures and it leaves memory management up to the programmer.

To make it better suitable for teaching, it has been stripped as much as possible while keeping some parts interesting for compiler construction. It supports functions, the usual control flow statements (if, for, while, switch), local and global variables, pointers<sup>1</sup>, structures and 1D arrays. However, the syntax has been simplified and only 3 basic data types have been included (char, int and double). We show an example program in listing 1.1. [3]

<sup>&</sup>lt;sup>1</sup>including pointers to functions

#### 1. INTRODUCTION

The tinyC language reference specifies only the syntax, which allows students to express some creativity during the implementation. We design our compiler to adhere as much as possible to semantics of the regular C language as specified by the C99 standard [7], which makes our variant of tinyC more predictable to unfamiliar readers and enables easy translation between regular C and tinyC code.

```

int main() {

char *str = "Hello, world!\n";

while(*str) {

print(*(str++));

}

return 0;

}

```

Listing 1.1: An example of printing a string to standard output in tinyC using the builtin print.

#### 1.3 Tiny x86

Our tinyC compiler targets the tiny86 VM, designed by Ivo Strejc [4] for purposes of NIE-GEN. It simulates a CPU with a custom register-based ISA. There are two sets of registers, 64-bit-wide integer and double precision floating point registers, whose amount is configurable by the user. This configurability allows testing a compiler even before we implement a working register allocator. Tiny86 instructions can also access a data memory addressed in 64-bit words (Harvard architecture) and communicate with the user through standard input and output.

Targeting tiny86's simplified ISA allows the student to focus more on the compiler itself instead of studying the intricacies of a fully-fledged architectures like x86 or RISC-V. Still, many tiny86 instructions support multiple complex addressing modes, which puts it into the CISC territory.

Tiny86 is distributed as a shared C++ library, which exposes a simple builder interface to directly construct a program using instruction objects. It contains no built-in text- or binary-based assembly format, which makes integrating with non-C++ applications harder.

Luckily, Filip Gregor extended [8] the tiny86 interpreter with a proof-ofconcept parser for a text-based program representation as part of his work on an interactive debugger. In chapter 5 we describe how we have used this parser to interface tiny86 with our tinyC compiler.

During execution, the VM collects information about lifecycle of each instruction as it goes through the CPU pipeline. Such statistics include the number of memory accesses or the count of pipeline  $stalls^2$ , which allow us to measure quality of the code emitted by our compiler.

#### 1.4 Scala

Scala is a modern high-level language, which combines object-oriented and functional programming concepts together in a statically typed language. The name Scala stands for scalable language and it was chosen because it grows with demands of the programmer. Novice users can quickly start developing programs and senior developers can fully utilize the advanced syntax constructs and extensibility offered by Scala. [5]

From functional language perspective, it offers a powerful type system, large immutable collection library and constructs designed to allow building code from smaller blocks. The object-oriented aspect helps with structuring large projects and defining clear abstractions and interfaces between components. Scala mainly targets the JVM and can seamlessly interoperate with other projects within the Java ecosystem<sup>3</sup>. [5]

Currently there are two simultaneously supported versions of Scala, numbered 2 and 3, where Scala 3 is fairly new (released in 2021) and a major overhaul of the previous version. Scala 2 is already taught on FIT CTU in the Object-Oriented Programming (BIE-OOP) and Static Program Analysis (NIE-APR) courses, so it is the natural choice given the educational aspect of this thesis. Listing 1.2 contains a small snippet of Scala 2 code demonstrating its functional and object-oriented nature.

```

sealed trait Animal

case object Cat extends Animal

case class Dog(name: String) extends Animal

List(Cat, Dog("Spot"), Dog("Buck")).foreach({

case Cat => println("a_Lcat:_Meow!")

case Dog(name) => println(s"$name:_Woof!")

})

```

Listing 1.2: An example of Scala 2 code with an immutable list and pattern matching.

$<sup>^2{\</sup>rm A}$  pipelined CPU stalls when the next instruction depends on completion of another in a previous stage that has not yet finished.

<sup>&</sup>lt;sup>3</sup>There is also Scala.js, which allows Scala to run in the web browser and Scala Native, which is an ahead of time compiler to native executables.

#### 1.5 Previous Work

The most popular compilers used today are GNU Compiler Collection (GCC) and Low Level Virtual Machine (LLVM), both supporting many languages and targets. They are comparable in terms of quality of the generated code, but GCC is built as a monolithic program with a fixed set of built-in supported languages and extending it means directly modifying its source code, which can be difficult to understand.

On the other hand, Lattner et. al designed LLVM [9] from the ground up with a common low-level intermediate representation and a framework for lifelong analysis and transformation of programs, which can be used by other software. If we wanted to implement a tinyC compiler using LLVM, we could just translate the source into a textual representation of the LLVM IR and let the optimizer and backend turn it into the target code.

The ahead-of-time microC ( $\mu$ C) compiler [10] designed by Král is comparable in scope to our thesis. The  $\mu$ C language is similar in design and purpose to tinyC, but Král's thesis focuses on the optimizer part of a compiler, while in our thesis we explore interesting ideas in all parts of a modular compiler with emphasis on code generation in the backend.

#### 1.6 Thesis Outline

In the following three chapters we describe techniques currently used in compiler construction (chapter 2 – frontend & optimizer, chapter 3 – instruction selection, and chapter 4 – register allocation).

In chapter 5 we then choose a subset of the described methods and explain how we have used them to design and implement our own modular tinyC compiler targeting the tiny86 VM.

In chapter 6 we evaluate correctness and performance of our implementation and in the last chapter we conclude our thesis and suggest possible future improvements.

# CHAPTER 2

# Intermediate-Code Generation and Optimization

In this chapter we will describe the first two parts of a typical modular compiler, which were introduced in section 1.1 – the frontend and optimizer.

Before the compiler can translate the source program into the target language, it must first understand its structure (syntax) and meaning (semantics). To make the syntax analysis easier to implement and reason about, we do not use characters of the source code directly. Instead, we first processes them into a stream of tokens using lexical analysis. Before we can design a simple lexical and syntax analyzer, we first have to define some basic principles of the string and parsing theory. A good resource with more complete definitions and explanations is the book by Aho et al. [6], known as "the Dragon Book", which we have also used while writing this chapter.

#### 2.1 String Parsing Theory

**Definition 1.** A string is a finite sequence of symbols from a finite set called the *alphabet* (usually denoted  $\Sigma$ ). The symbol  $\varepsilon$  means an empty string.

#### 2.1.1 Context-Free Grammar

**Definition 2.** A context-free grammar is a 4-tuple  $(N, \Sigma, \delta, S)$ , where

- N is a finite set of nonterminals (syntactic variables),

- $\Sigma, \Sigma \cap N = \emptyset$  is a finite set of terminals called the alphabet,

- $\delta \subseteq N \times (N \cup \Sigma)^*$  is a finite set of rewrite rules (*productions*), where each has a single nonterminal on the left side and a (possibly empty) string of nonterminals and terminals on the right, and

#### • $S \in N$ is the start symbol.

A grammar is a precise specification of syntax of a given language. It is structured, yet easy-to-understand and there exist tools to automatically construct a syntax analyzer from some classes of grammars. That can be advantageous when we want to extend the grammar later in development of the compiler. In fig. 2.1 we show a set of productions for a grammar  $G_1 = (\{E, T, F\}, \{+, *, (,), a\}, \delta_1, E)$ , which describes a simple language for arithmetic expressions.

For ease of understanding, we will use uppercase characters for nonterminals and we may use | to join alternative productions for a single nonterminal.

$$\begin{split} E &\rightarrow E + T \mid T \\ T &\rightarrow T * F \mid F \\ F &\rightarrow (E) \mid a \end{split}$$

Figure 2.1:  $\delta_1$  for grammar  $G_1 = (\{E, T, F\}, \{+, *, (, ), a\}, \delta_1, E).$

By applying a sequence of productions of a grammar as rewrite rules beginning with the start symbol, we construct a derivation. In each step, we replace a single nonterminal using one of the productions of the grammar. We will now use a simplified version (fig. 2.2) of the previous grammar. By applying the rule  $E \to (E)$  we get  $E \Rightarrow (E)$  and say that E derives (E). We say that (E) is a sentential form, because it contains the nonterminal E, which can be derived further. We can for example continue with the rule  $E \to a$  to get  $E \Rightarrow (E) \Rightarrow (a)$ . There are now no more nonterminals left and the derivation has proven that (a) is one of the strings in the language produced by the grammar  $G_2$ .

#### 2.1.2 Parse Tree

A *parse tree* is another way to prove that a sentence (a string of terminals) can be derived by a grammar, it however does not show the exact order of derivations. The root and interior nodes of the parse tree are labeled with nonterminals representing a left side of a production and their children are nodes labeled left-to-right with symbols of the corresponding right side. The

$$E \to E + E \mid E * E \mid (E) \mid a$$

Figure 2.2:  $\delta_2$  for grammar  $G_2 = (\{E\}, \{+, *, (, ), a\}, \delta_2, E).$

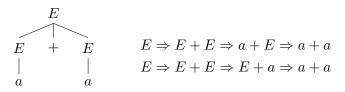

Figure 2.3: A parse tree and two different derivations of a + a in  $G_2$ .

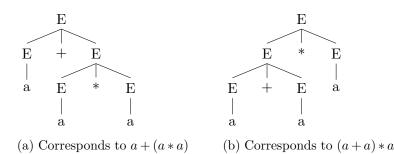

Figure 2.4: Two possible parse trees for the sentence a + a \* a in  $G_2$ .

leaves of the tree contain terminals and nonterminals, which when read leftto-right denote a sentential form or a sentence.

For a given sequence of derivations, we can construct an unique parse tree and from a parse tree we can construct (possibly multiple) sequences of derivations [6]. We can choose to produce leftmost or rightmost derivations to make this relationship one-to-one – we always expand either the leftmost or rightmost nonterminal in a sentential form. In fig. 2.3 we show an example parse tree and two possible sequences of derivations for the same sentence.

#### 2.1.3 Ambiguity of a Grammar

The last term we need to define before we can proceed with description of parsing techniques is ambiguity of a grammar. The grammars  $G_1$  (fig. 2.1) and  $G_2$  (fig. 2.2) describe the same language, but the second one is ambiguous. A grammar is *ambiguous* if it produces more than one parse tree for some sentence s. In another words, there are multiple possible leftmost and rightmost derivations of s. We use the nonterminals E, F and T in  $G_1$  to capture the priority of + and \*, whereas in  $G_2$  there is only a single nonterminal E. In fig. 2.4 we show two different parse trees of the sentence a + a \* a in  $G_2$ .

Compilers usually use grammars that are either unambiguous, or the parsers contain additional disambiguating rules that always select one of the possible parse trees for further processing.

#### 2.1.4 Top-Down Parsing

Top-down parsing is one of the two most common approaches to constructing a parse tree for a given sentence, the other one being bottom-up parsing. A top-down parser tries to find a *left parse* (a sequence of leftmost derivations) by building the parse tree from the root and continuing in preorder (depth-first) fashion. This is often implemented as a *recursive-descent* parser.

At each step the parser needs to select a production to use for the current (leftmost) nonterminal. In the most general way it can use backtracking to try all possibilities, but that is not used in practice because of exponential time complexity.

LL(k) parsers make this decision by looking ahead at the next k symbols in the unconsumed input, for that reason they are called *predictive parsers*. Whenever a LL(k) parser makes a decision, it never backtracks. That greatly limits the class of grammars it can be constructed for (and therefore languages it can accept), but it is still usually generic enough for programming languages.

A left-recursive grammar like the one in fig. 2.1 cannot be used to construct a recursive-descent parser (even one with backtracking), because it would get stuck in an infinite loop while expanding the nonterminal E or T. Luckily, left recursion can be removed by introducing new nonterminals [6] like in fig. 2.5. We have also added a new start symbol S, which matches the original Eterminated by an end-of-input marker . This will be required later during parsing table construction.

$$S \rightarrow E \ \ E \rightarrow T \ E'$$

$$E' \rightarrow + T \ E' \mid \varepsilon$$

$$T \rightarrow F \ T'$$

$$T' \rightarrow * F \ T' \mid \varepsilon$$

$$F \rightarrow (E) \mid a$$

Figure 2.5: A modified grammar  $G'_2$  with removed left recursion and new start symbol S.

To construct a predictive parser from a grammar, we need to define two functions,  $FIRST(\alpha)$  and FOLLOW(A).

**Definition 3.** FIRST :  $(N \cup \Sigma)^* \to \Sigma \cup \{\varepsilon\}$  returns the set of all possible terminals that may appear at the beginning of sentences derived from the sentential form  $\alpha$ . If an empty string can be derived from  $\alpha$  in some number of steps,  $\varepsilon$  is also included.

**Definition 4.** FOLLOW :  $N \to \Sigma \cup \{\varepsilon\}$  returns the set of terminals that may appear immediately after the nonterminal A in some sentential form.

We can easily compute both FIRST and FOLLOW from the grammar definition [6] and use them to build a predictive parser. We have included a sample of values for  $G'_2$  in table 2.1.

| Rule $(A \to \alpha)$ | $\mathrm{FIRST}(\alpha)$ | $\operatorname{FIRST}(A)$ | $\operatorname{FOLLOW}(A)$              |

|-----------------------|--------------------------|---------------------------|-----------------------------------------|

| $S \to E $            | $\{(,a\}$                | $\{(,a\}$                 | $\{\varepsilon\}$                       |

| $E \to T E'$          | $\{(,a\}$                | $\{(,a\}$                 | {),\$}                                  |

| $E' \to + T E'$       | {+}                      | $\{+,\varepsilon\}$       | {),\$}                                  |

| $E' \to \varepsilon$  | $\{\varepsilon\}$        | \_,c}                     | $\chi$ , $\Psi$                         |

| $T \to F T'$          | $\{(,a\}$                | $\{(,a\}$                 | $\{+,),\$\}$                            |

| $T' \to * F T'$       | {*}                      | $\{*, \varepsilon\}$      | {+,),\$}                                |

| $T' \to \varepsilon$  | $\{\varepsilon\}$        | \*,°∫                     | $\{\top, j, \psi\}$                     |

| $F \rightarrow (E)$   | {(}                      | ∫( a]                     | {*,+,),\$}                              |

| $F \rightarrow a$     | $\{a\}$                  | $\Big  \ \{(,a\}$         | $\{\uparrow, \uparrow, \top, J, \Psi\}$ |

Table 2.1: FIRST and FOLLOW sets for  $G'_2$ .

The grammar  $G'_2$  is LL(1) – only a single symbol look-ahead is required to choose the correct production. Given the grammar and the values of FIRST and FOLLOW functions, we can now compute the *parsing table* using the algorithm from [6]. The result for  $G_2$  is shown in table 2.2. Rows of the table correspond to nonterminals, the columns contain the next symbol in the input and the cells hold the production rule that the parser should select. The parsing table can then be easily translated to implementation code (a procedure for each nonterminal containing a **switch** statement for look-ahead).

|    | a                 | +                    | *               | (            | )                    | \$                   |

|----|-------------------|----------------------|-----------------|--------------|----------------------|----------------------|

| S  | $S \to E $        |                      |                 | $S \to E $   |                      |                      |

| E  | $E \to T E'$      |                      |                 | $E \to T E'$ |                      |                      |

| E' |                   | $E' \to + T E'$      |                 |              | $E' \to \varepsilon$ | $E' \to \varepsilon$ |

| T  | $T \to F \ T'$    |                      |                 | $T \to F T'$ |                      |                      |

| T' |                   | $T' \to \varepsilon$ | $T' \to * F T'$ |              | $T'\to\varepsilon$   | $T' \to \varepsilon$ |

| F  | $F \rightarrow a$ |                      |                 | $F \to (E)$  |                      |                      |

Table 2.2: A parsing table for grammar  $G_2$ .

If the parsing table contains an unique rule in each cell, the grammar is LL(1). Otherwise, we would either have to perform some more reductions of the grammar [6] or use a different parser family altogether.

An ambiguous grammar can never be LL(k), but sometimes the best solution is to manually pick one option in the parsing table. Many programming languages with the **if** statement deal with a so-called *dangling else* problem. See an example grammar  $G_3 = (\{S', S, E\}, \{\text{if}, \text{then}, \text{else}, expr, stmt, \$\}, \delta_3, S')$  with  $\delta_3$  in fig. 2.6.

$\begin{array}{l} S' \rightarrow S\$ \\ S \rightarrow \mathbf{if} \ expr \ \mathbf{then} \ S \ E \\ S \rightarrow stmt \\ E \rightarrow \mathbf{else} \ S \mid \varepsilon \end{array}$

Figure 2.6: Productions of  $G_3$  demonstrating the dangling-else problem.

If we tried to construct a parsing table for  $G_3$ , it would contain duplicate entries for E and **else**. The grammar does not specify if the **else** statement should belong to the closest **if** (usually the desired behavior) or not, see for example the sentence **if** expr **then if** expr **then** stmt **else** stmt. We can fix this without changing the grammar by manually modifying the parsing table to prefer  $E \to$  **else** S.

#### 2.1.5 Parser Expression Grammar

A context-free grammar describes how sentences of the language can be produced. But when developing a parser, we need to recognize how an already existing sentence was derived. This clash of directions led Ford [11] to design a formalism for parser expression grammars (PEGs), which are used to more directly describe a top-down parser.

**Definition 5.** A PEG is a 4-tuple  $(N, \Sigma, R, e_S)$  where

- N is a finite set of nonterminals,

- $\Sigma, \Sigma \cap N = \emptyset$  is a finite set of terminals,

- *R* is a total function from nonterminals to *parsing expressions*, and

- $e_S$  is the initial parsing expression.

We write the rules given by R as  $A \leftarrow e$ .

R being a total function means that for each nonterminal  $A \in N$  there is exactly one parsing expression R(A). A parsing expression receives an input string of terminals and either fails, or succeeds and consumes a prefix of the input, leaving a remaining suffix. We define parsing expressions inductively, the syntax is as follows:

$$e = \varepsilon \mid a \mid A \mid e_1 e_2 \mid e_1 / e_2 \mid e^* \mid ! e$$

- $\varepsilon$  matches the empty string (and does not consume any input),

- $a, a \in \Sigma$  matches and consumes the terminal a,

- $A, A \in N$  tries to match R(A),

- $e_1e_2$  (a sequence) matches  $e_1$  and tries to match  $e_2$  on the remaining input,

- $e_1/e_2$  (prioritized choice) tries to match  $e_2$  and only if it fails tries to match  $e_2$ ,

- $e^*$  greedily<sup>4</sup> matches zero or more repetitions of e,

- !e (a not-predicate) fails if e succeeds, otherwise if e fails !e succeeds without consuming any input.

In comparison with LL(k) languages, PEGs have more expressive power. A PEG can express all LL(k) and deterministic LR(k) languages and even some non-context-free languages, thanks to the limited backtracking ability and the not-predicate [11]. Despite this, they can be parsed in linear time with the help of memoization [12].

We have rewritten the simple expression grammar from section 2.1.4 as a PEG in fig. 2.7. Like with LL(1) parsing, we need to explicitly model end of input, because parsing expressions match on a prefix of the input. Instead of appending a terminator the input string, we use the expression !A, where A matches any terminal. Parsing expressions also cannot contain left-recursion, but we can perform the same transformation as with LL(1) grammars, or use the repetition expression  $(e^*)$ .

A natural way to implement recursive descent parsers in functional languages (including Scala [5]) is using higher-order functions called parser combinators<sup>5</sup>. A combinator parser as designed by Hutton [13] is a function from an input string of symbols to a list of result values and remaining suffixes. That is, it performs full backtracking and returns a list of all possible matches. If we modify the parser to return a Maybe (Option in Scala) instead of a list, we get the same semantics as a PEG [14]. The Scala standard parser combinator library does exactly that and includes some additional combinators to limit backtracking to improve performance [5].

<sup>&</sup>lt;sup>4</sup>as many times as possible

<sup>&</sup>lt;sup>5</sup>A parser *combinator* is a higher-order function, which takes one or more parsers as arguments and combines them into a new parser.

$S \leftarrow E ! A$   $E \leftarrow T (+ T)^*$   $T \leftarrow F (* F)^*$   $F \leftarrow (E) / a$  $A \leftarrow any \ terminal$

Figure 2.7: A PEG  $P_1 = (\{S, E, T, F, A\}, \{+, *, (, ), a\}, R, S)$ , where R is written above.

We build a combinator parser from smaller parsers using combinators, which perform the same basic operations as the operators in a parser expression (a sequence, prioritized choice, repetition and not-predicate). [13]

#### 2.1.6 Error Reporting

When a parser is unable to recognize some input, we would usually want it to report the probable location of the syntax error. In some cases it could be beneficial if it tried to recover and continue parsing anyway, so we can display all found errors to the user at once.

In this section we will focus on error reporting, because error recovery is more complicated and can result in cascading errors [14].

Error reporting for LL parser (and LR for that matter) is simple, because it processes the input from start to end without backtracking. If the parsing table does not specify any transition for the next terminal, the parser aborts with an error at the current location in the input [6]. However, when a PEG or combinator parser reports a failure, the original source and location of the error is usually lost, because the parser could have backtracked and tried other alternatives [15].

Ford [15] implemented a simple heuristic, which simulates the error reporting of predictive parsers by passing information about all errors that occurred at the furthest point of the input string up the chain of parser expressions. The final error message contains information about the location, next symbols in the input and all expected symbols, but it is missing any additional context.

Maidl [14] proposed an extension of the PEG grammar with *labeled failures*, which work similarly to exceptions in programming languages. He added a new expression  $\uparrow^l$ , which always fails with the label l and extended the ordered choice operator  $e_1/Se_2$  to backtrack only if  $e_1$  fails with a label  $l \in S$ . The primitives emit the fail label on failure by default, but every parsing expression can be annotated to convert those fail labels to a custom label using the new try..catch-like operators. Together, this gives the author of the grammar more control over backtracking and the ability to supply custom context-rich error messages.

Scheidecker [16] mentioned in his blog post a simple improvement of Ford's technique. Instead of keeping the expected symbols in a flat structure, he uses an expectation tree that is extended with friendly description l using new describeParser(e, l) combinator. When the inner parser e fails without matching any input<sup>6</sup>, it overwrites its expectation with l. If e failed after matching some input, it wraps the expectation of e with a new node labeled with l.

Once the failure is propagated to the root and becomes fatal, the parser has the expectation tree for the furthest visited point of the input. Scheidecker uses the description of each leaf to list the expected symbols/tokens and the description of the innermost ancestor of all leaves as the context to build the error message.

#### 2.1.7 Other Parsing Methods

In addition to LL(k) and PEG parsing, we will use this section to briefly mention a few other methods.

Bottom-up parsing constructs a parse tree starting from the leaves and continuing up until the root. The LR(k) class of grammars can be parsed by a shift-reduce parser, which is the most commonly used bottom-up parser style. They are table-driven like LL parsers and can be implemented efficiently while recognizing most context-free grammars for programming languages (the LR(k) class of grammars is a proper superset of LL(k)). One disadvantage of LR parsers is that they are too complex to be built by hand without help of automatic tools. [6]

Algorithms exist for testing whether a string can be generated by a generic context-free grammar, but they have high time complexity, which makes them unsuitable for use in compiler construction [6].

#### 2.2 Lexical and Syntax Analysis

The first thing a compiler frontend does is scanning and grouping of the input characters into *lexemes* and production of stream of meaningful tokens. A token has a name and an optional attribute and it is used as a terminal symbol during syntax analysis. A lexer of a typical C-like language recognizes the following classes of tokens [6]:

- tokens for every program keyword (such as if, while...),

- tokens for operators and other special symbols (+, ==, ->, [, )...),

<sup>&</sup>lt;sup>6</sup>Remember that we work with the furthest visited location.

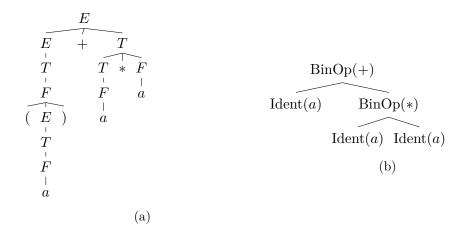

Figure 2.8: An example of (a) parse tree (as parsed by grammar from fig. 2.1) and (b) equivalent AST for expression (a) + a \* a.

- a token representing an identifier the name is stored in the attribute,

- a token representing a constant (an integer, a real number...),

- a token for string literal ("foo", '\n'...).

We implement a lexer greedily, so it always matches the longest possible tokens, because otherwise it could incorrectly recognize identifiers such as **iface** as keywords (**if**). For that reason, CFGs are not suitable for describing the patterns of tokens. Instead, we can use ad-hoc algorithms, PEG parsers or their subset called regular expressions in a loop to parse a prefix of the input into a single token.

The syntax analyzer is then a top-down or bottom-up parser based on the theory described in section 2.1. During parsing, we call actions to construct an abstract syntax tree (AST). An AST is a data structure similar to a parse tree, but it hides the nuances of the grammar and keep only the syntax information useful for further processing.

The interior nodes of a parse tree represent nonterminals, whereas in an AST, they represent programming constructs. For the expression grammar from fig. 2.5, we would use only two node types instead of 6 nonterminals – a binary operator (+, \*) and an identifier (a). We compare a typical parse and syntax trees for (a) + a \* a in fig. 2.8.

An alternative to separate lexical and syntax analysis is to build an unified PEG parser and grammar. This is possible thanks to the greedy nature of PEG [11], but leads to a more complex grammar and a slower parser. The advantage of this approach is that we can easily express more complex lexing rules (for example the  $\gg$  at the end of a nested C++ template<sup>7</sup> [11]) and we

<sup>&</sup>lt;sup>7</sup>Older versions of C++ mandated the space in vector<vector<int> >, so it is not confused with the >> bitwise shift operator.

can even embed one PEG parser into another (for example to parse JavaScript embedded in a HTML document [14]).

#### 2.3 Semantic and Type Analysis

The parser hands off the AST to the semantic analyzer, which links identifiers to their declarations and checks type of each expression. It then augments the AST with the collected information and passes it to the intermediate code generator.

The semantic analyzer recursively visits every AST node in order and tracks the identifiers accessible from the current scope in *symbol tables (environments)*. Whenever an identifier enters the current scope through a declaration, we add the symbol and a reference to the declaration (*a binding*) into the active environment. We then discard the binding when the declaration leaves the current scope. Whenever we visit an identifier, we look up its declaration in the active environment or return an error if there was no match.

Some languages, such as tinyC [3] or C since the C99 revision [7] have lexical scoping, which allows *shadowing* of multiple declarations of the same identifier (see listing 2.1). In case of lexical scoping, we store the environments in a stack, otherwise one or two shared symbols tables (one for global and one for local scope) suffice.

```

int x = 1;

do {

int x = 2; // shadows the previous declaration

print(x); // prints 2

} while(0);

print(x); // prints 1

```

Listing 2.1: An example of variable shadowing in tinyC and C since the C99 revision.

#### 2.3.1 Type Analysis

During type analysis, the compiler assigns a type to each program expression (represented by an AST node) and checks that the types conform to a set of logical rules (*type system*) dependent on the source language. We use type checking to reduce (or completely eliminate) the need for dynamic checking for type errors and to aid intermediate code generation. [6]

In most statically typed languages (including C [7] and tinyC), we define a type of an expression in terms of types of its subexpressions (*type synthesis*). We can check the rules in this case by recursively visiting the abstract syntax tree. Whenever we cannot determine a type of an expression, we raise a type error. A typical rule can look like this: "if the current node is +, the left child

has type int and the right child has type double, then the result has type double."

Other languages, such as ML or  $\mu C^8$  [17] are strongly typed, however the types are automatically *inferred* by the compiler without relying on the user. The types also cannot be computed using a single bottom-up pass over the AST, see for example a small  $\mu C$  program in listing 2.2. The typechecker does not know the type of the arguments of the sum function until it is called. For this reason, we build a list of *type constraints* for the whole program and then solve them using *unification* [1].

```

select(c, x, y) { var r; if(c) r = x; else r = y;

return r; }

main() {

var a, b, r;

a = 2; b = 3;

return select(1, a, b);

}

```

Listing 2.2: A simple  $\mu$ C program which demonstrates type inference. The type of x and y is not known until after the call expression.

We define constraints for each expression in terms of type variables ( $\llbracket E \rrbracket$  holds the type of E). We list a few rules in table 2.3. Description of the constraint solver itself is outside of the scope of this thesis and can be found in [1] or [6].

$$I: [\![I]\!] = \operatorname{int} X = E: [\![X]\!] = [\![E]\!]$$

if (E) S<sub>1</sub> else S<sub>2</sub>: [[E]] = int

$X(X_1, \dots, X_n) \{ \dots \operatorname{return} E; \}: [\![X]\!] = ([\![X_1]\!], \dots, [\![X_n]\!]) \to [\![E]\!]$

Table 2.3: A subset of TIP (equivalent to  $\mu$ C) type inference rules required for typechecking listing 2.2. *I* stands for an integer literal, *E* for an expression and *X* for a program variable (functions are treated as values) [1].

#### 2.4 Intermediate Representation

In a modular compiler, the translation between the source code and compilation target is not direct. Instead, the compiler uses one or more intermediate representations (IRs), which are easier to analyze and optimize and act as a middleman between the frontend and the backend. A typical intermediate representation emitted by the frontend resembles instructions of a low-level

$<sup>^8{\</sup>rm a}$  programming language designed for the static program analysis (NI-APR) course based on the TIP language from Møller's book [1]

Figure 2.9: A simple C program demonstrating the limitations of tree-address code. (a) shows the original code and (b) the equivalent three-address code, where each statement does only a single operation.

abstract machine. We design the IR to be easily producible from all of the supported source languages (can express all of their features in some way) and so it can be easily translated into all supported target languages. [6]

We can classify the form of an IR as either flat or hierarchical (usually a tree or a graph).

### 2.4.1 Flat IR

The flat variant has the form of a list of instructions, which are executed sequentially and the control flow is specified by labels and branch instructions. Each instruction performs only one operation (three-address code) and stores the result to a specified temporary variable, of which there is usually unlimited amount available. Figure 2.9 shows a simple program and its three-address code representation, which we will use as a running example. [18]

We group sequences of instructions, which always get executed together without any branches into *basic blocks*. A basic block ends with a terminator (usually an (un)conditional branch, return or a halt instruction), which specifies the next basic block to be executed.

To be able to reason better about the control flow of instructions or basic blocks in analyses and optimizations, we define the control-flow graph.

**Definition 6.** A control-flow graph (CFG) is a directed graph, where nodes correspond to instructions (or basic blocks) of a program. An edge (u, v) exists iff instruction (basic block) v can be executed directly after instruction (basic block) u. We mark one node as the *entry point* (entry(*cfg*)) of the program and a set of nodes as *exit points* (exit(*cfg*)). A node n has a set of predecessors (pred(n)) and successors (succ(n)) determined by its incoming and outgoing edges.

We would like to build a similar graph representation for the flow of values, but for that we need a form of IR where every variable has only one unique

Figure 2.10: (a) the program from fig. 2.9b lowered into a set of basic blocks and (b) its basic block control-flow graph.  $B_1$  is the entry point,  $B_4$  is the only exit point.

definition. We call this extension of three-address code the single static assignment (SSA) form. A distinctive aspect of SSA form is the presence of  $\phi$ -nodes to combine two definitions of a variable coming from different predecessor blocks. This is a notational convention rather than a real instruction, which we later again eliminate during instruction selection or register allocation. See fig. 2.11 for an example of three-address code and its SSA form.

We can construct SSA form for every program by giving variables unique names and inserting  $\phi$ -nodes in appropriate places. We will describe algorithms for that in section 2.6.

The single unique definition property of SSA allows us to visualize the data dependencies of instructions using a data-flow graph.

**Definition 7.** A data-flow graph (DFG) is a directed graph, where nodes correspond to instructions in a program and edges to their data dependencies. An edge (u, v) means that the instruction v uses (depends on) the result of instruction u.

In a valid DFG, every cycle must go through some  $\phi$ -node. Otherwise none of the instructions in the cycle can have their requirements satisfied and begin executing. The data-flow graph is used by various dataflow analyzes, which we will mention in section 2.7.

Figure 2.11: A SSA form of the program from fig. 2.10a. We use the  $\phi$ -node to join values of *i* coming from  $B_1$  and  $B_3$ . (b) then shows a DFG of the program, where the  $\phi$ -node completes a cycle.

#### 2.4.2 Tree-Based IR

Another common way to represent IR instructions is as tree nodes. A treebased intermediate representation looks similarly to an abstract syntax tree, but the operations are much simpler (like in the flat three-address code from section 2.4.1). The hierarchy of a tree is closer to the typical programming language, but the tree representation of control flow is impractical for analyses and optimizations.

Appel [19] describes implementation of a simple optimizing compiler and uses trees as an intermediate representation. Instead of the high level control flow nodes like **if** and **while**, he defines a system of labels and jumps similar to a flat IR. In a later stage of the compilation, he splits the tree into smaller trees (one for each program statement) and groups sequences of the resulting trees into basic blocks.

#### 2.4.3 Intermediate Representation in Existing Compilers

**LLVM** The core of the LLVM framework is built around a flat RISC-like IR. The instructions operate on SSA virtual registers and their control flow is given explicitly by listing them in basic blocks. The frontends do not have to emit SSA directly, instead they can use the available memory instructions (e.g. alloca, load and store), most of which the compiler then eliminates in a SSA construction pass (mem2reg). Figure 2.12 contains example of LLVM

IR code before and after optimization. [9]

**GCC** The main intermediate representation used in GCC are GENERIC and GIMPLE. The frontends target the GENERIC IR, which a tree representation with a structure similar to C source code. The middleend then lowers this IR into the GIMPLE representation, which is a standard three-address code. [20]

**JVM** The Java Virtual Machine uses a stack-based IR, which is a form somewhere between flat and hierarchical. Control flow is modeled using labels and jumps like in flat intermediate representation, but the operations do not use variables. Instead, they pop their operands from the implicit operand stack and push back their result. [18]

## 2.5 Compiling Source Code to IR