# Assignment of master's thesis

| TinyC Optimizing Compiler                  |

|--------------------------------------------|

| Bc. Martin Slávik                          |

| Ing. Petr Máj                              |

| Informatics                                |

| System Programming                         |

| Department of Theoretical Computer Science |

| until the end of summer semester 2022/2023 |

|                                            |

# Instructions

Design and implement an intermediate representation and an optimizing compiler for the tinyC language and tiny86 target VM using the methods from the NI-GEN course. The compiler must correctly translate the entirety of the tinyC language and generate a correct and non-trivial t86 assembly. Implement intra-procedural optimizations and inlining in the optimizer and instruction selection and register allocation using selected techniques from NI-GEN course in the backend part. The code must be written in idiomatic C++ consistent with the rest of the tinyverse platform, be clearly structured and well documented so that it can be used as a reference implementation in the NI-GEN course.

Master's thesis

# **TinyC Optimizing Compiler**

Bc. Martin Slávik

Department of Theoretical Computer Science Supervisor: Ing. Petr Máj

May 3, 2023

# Acknowledgements

I would like to thank my supervisor Ing. Petr Máj for his patience and valuable advice during the creation of this thesis.

# Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. In accordance with Article 46 (6) of the Act, I hereby grant a nonexclusive authorization (license) to utilize this thesis, including any and all computer programs incorporated therein or attached thereto and all corresponding documentation (hereinafter collectively referred to as the "Work"), to any and all persons that wish to utilize the Work. Such persons are entitled to use the Work in any way (including for-profit purposes) that does not detract from its value. This authorization is not limited in terms of time, location and quantity. However, all persons that makes use of the above license shall be obliged to grant a license at least in the same scope as defined above with respect to each and every work that is created (wholly or in part) based on the Work, by modifying the Work, by combining the Work with another work, by including the Work in a collection of works or by adapting the Work (including translation), and at the same time make available the source code of such work at least in a way and scope that are comparable to the way and scope in which the source code of the Work is made available.

In Prague on May 3, 2023

. . .. . . . . . . . . . . . . . . .

Czech Technical University in Prague Faculty of Information Technology © 2023 Martin Slávik. All rights reserved. This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

## Citation of this thesis

Slávik, Martin. *TinyC Optimizing Compiler*. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2023.

# Abstrakt

Práce pojednává o tvorbě kompilátoru, a jeho vnitřních částí pro výukové účely.

Práce má za úkol vytvořit kompilátor, který přeloží programy zapsané v jazyce TinyC do instrukční sady definované virtuální architekturou tiny86. TinyC je podobný jazyku C s menší sadou typů a redukovanou funkcionalitou. Tiny86 virtuální stroj je inspirovaný x86 architekturou s jednodušší instrukční sadou, za účelem lepší srozumitelnosti. Instrukční sada tiny86 zachovává zajímavé a důležité vlastnosti, které architektura x86 nabízí. Během překladu kompilátor využívá optimalizační techniky pro dosažení lepšího výkonu kompilovaného kódu. Práce porovnává výsledky naivní kompilace a kompilace se zapnutými optimalizacemi.

**Klíčová slova** kompilátor, optimalizační kompilátor, TinyC, překladač, alokace registrů, výběr instrukcí

# Abstract

This thesis is about compiler creation and its internal parts for educational purposes.

It should compile programs described with the TinyC language to the instruction set specified by the virtual architecture tiny86. TinyC is a C-like language with a smaller subset of types and a limited set of features. The tiny86 Virtual Machine is inspired by x86 architecture but has a simpler instruction set, so it is more understandable for students. The tiny86 instruction set preserves interesting and important features that the x86 architecture offers. Throughout the compilation, optimization techniques are used to achieve better performance of the compiled code. The thesis compares the naïve compilation and compilation with optimization techniques turned on.

**Keywords** compiler, optimizing compiler, TinyC, translator, register allocation, instruction selection

# Contents

| In                              | trod | uction                |                               | 1        |

|---------------------------------|------|-----------------------|-------------------------------|----------|

|                                 | Tiny | Verse .               |                               | 3        |

|                                 | •    |                       | view                          | 4        |

| 1 Overview of a Modern Compiler |      |                       | of a Modern Compiler          | <b>5</b> |

|                                 | 1.1  | Front-e               | end                           | 8        |

|                                 |      | 1.1.1                 | Lexical Analysis              | 8        |

|                                 |      | 1.1.2                 | Syntax Analysis               | 9        |

|                                 |      | 1.1.3                 | Semantic Analysis             | 9        |

|                                 | 1.2  | Interm                | ediate Representation         | 9        |

|                                 |      | 1.2.1                 | Types of IR                   | 9        |

|                                 |      | 1.2.2                 | Single Static Assignment      | 11       |

|                                 | 1.3  | Optim                 | izer                          | 13       |

|                                 |      | 1.3.1                 | Analyses                      | 14       |

|                                 |      | 1.3.2                 | Optimizations                 | 15       |

|                                 | 1.4  | Back-e                | nd                            | 16       |

|                                 |      | 1.4.1                 | Instruction Selection         | 16       |

|                                 |      | 1.4.2                 | Target specific optimizations | 18       |

|                                 |      | 1.4.3                 | Register Allocation           | 18       |

|                                 |      | 1.4.4                 | Instruction Reordering        | 20       |

|                                 | 1.5  | Case S                | tudies                        | 21       |

|                                 |      | 1.5.1                 | GCC                           | 21       |

|                                 |      | 1.5.2                 | LLVM                          | 26       |

| <b>2</b>                        | Des  | ign and               | d Implementation              | 33       |

| <b>S</b>                        |      | ediate Representation | 34                            |          |

|                                 | 2.2  |                       | o IR Translation              | 36       |

|                                 | 2.3  | Optim                 | izer                          | 46       |

|                                 |      | 2.3.1                 | Analyses                      | 46       |

|                   |              | 2.3.2 Optimizations                     | 47 |

|-------------------|--------------|-----------------------------------------|----|

|                   | 2.4          | Back-end                                | 49 |

|                   |              | 2.4.1 Instruction Selection             | 50 |

|                   |              | 2.4.2 Register Allocation               | 54 |

|                   |              | 2.4.3 Calling Conventions               | 56 |

|                   |              | 2.4.4 Assembly Finalization             | 57 |

| 3                 | Eva          | luation                                 | 59 |

|                   | 3.1          | Goals and Setup                         | 59 |

|                   | 3.2          | Verification and Validation             | 59 |

| Conclusion 63     |              |                                         |    |

|                   | Futu         | re Work                                 | 63 |

| Bi                | bliog        | graphy                                  | 65 |

| $\mathbf{A}$      | A Acronyms 6 |                                         |    |

| в                 | Tin          | yC Language Specification               | 69 |

|                   | B.1          | TinyC Language Reference                | 69 |

|                   |              | B.1.1 Functions                         | 69 |

|                   |              | B.1.2 Statements                        | 69 |

|                   |              | B.1.3 Types                             | 70 |

|                   |              | B.1.4 Type Declarations                 | 70 |

|                   |              | B.1.5 Expressions                       | 71 |

| C IR Instructions |              |                                         | 73 |

|                   | C.1          | Control Flow Instructions               | 73 |

|                   | C.2          | Function Call Instructions              | 74 |

|                   | C.3          | Memory Access & Allocation Instructions | 75 |

|                   | C.4          | I/O Instructions                        | 78 |

|                   | C.5          |                                         | 78 |

|                   | C.6          |                                         | 79 |

|                   | C.7          | Other Instructions                      | 80 |

| D                 | Con          | tents of enclosed SD card               | 81 |

# Listings

| 0.1 | The difference between high-level (on the left) and low-level(on | 0  |

|-----|------------------------------------------------------------------|----|

|     | the right) languages of the same program                         | 2  |

| 1.1 | Example of three-address code where are used constants, vari-    |    |

|     | ables, and temporary values                                      | 11 |

| 1.2 | Example showing how entangled can optimization passes be.        |    |

|     | In code number 1) the 'then' branch cannot be easily removed     |    |

|     | due to the variable b. But after CP showing and replacing b      |    |

|     | with its constant, dead code elimination can see the guard is    |    |

|     | false and therefore the 'then' branch never executes, thus the   |    |

|     | code is dead and can be removed                                  | 13 |

| 1.3 | Example C code                                                   | 21 |

| 1.4 | Example GIMPLE for C code from example 1.3                       | 22 |

| 1.5 | Low GIMPLE representation for C code from Example 1.3 $$ .       | 22 |

| 1.6 | Exmaple RTL for C code from Example 1.3                          | 24 |

| 1.8 | Example of LLVM IR                                               | 28 |

| 1.7 | Example C code                                                   | 28 |

| 2.1 | Example of translation of plus operator from TinyC language      |    |

|     | to IR                                                            | 37 |

| 2.2 | Example of translation of an if statement from TinyC language    |    |

|     | to IR                                                            | 38 |

| 2.3 | Example of translation of a while statement from TinyC lan-      |    |

|     | guage to IR.                                                     | 38 |

| 2.4 | Example of translation of a switch statement from TinyC lan-     |    |

|     | guage to IR.                                                     | 40 |

| 2.5 | Example of translation of '&&' Operator from TinyC language      |    |

|     | to IR                                                            | 41 |

| 2.6 | Example of translation of variables from TinyC language to IR.   | 43 |

| 2.7 | Example of translation of an array from TinyC language to IR.    | 44 |

| 2.8 | Example of translation of a structure from TinyC language to     |    |

|     | IR                                                               | 45 |

| 2.9  | Example of translation of an AllocG instruction from IR to     |    |  |

|------|----------------------------------------------------------------|----|--|

|      | Tinyx86                                                        | 51 |  |

| 2.10 | Example of translation from IR to Tinyx86, where an AllocL     |    |  |

|      | instruction is in a loop.                                      | 53 |  |

| 2.11 | Example of translation of IR with Call expressions to Tinyx86. | 55 |  |

| 3.1  | Code samples used for testing, sample A (on the left) was used |    |  |

|      | for constant propagation, and sample B (on the right) was used |    |  |

|      | for function inlining                                          | 61 |  |

|      |                                                                |    |  |

# **List of Figures**

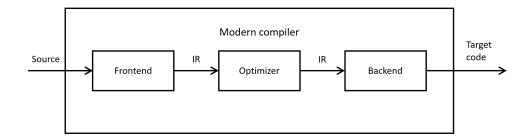

| 1.1        | High-level overview of a Modern compiler                                                                   | 6  |

|------------|------------------------------------------------------------------------------------------------------------|----|

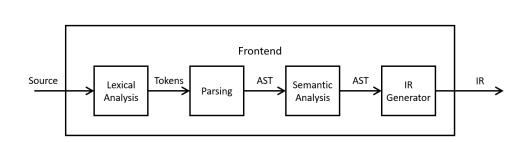

| 1.2        | Design of front-end internals of a modern compiler                                                         | 7  |

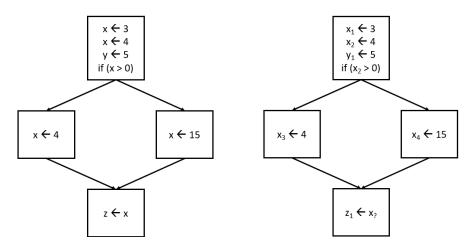

| 1.3        | Example of conversion to SSA Form with the use of indexes                                                  | 11 |

| 1.4        | Problem occurring in conversion to SSA Form                                                                | 12 |

| 1.5        | Usage of Phi instruction to resolve problems with the conversion                                           | 12 |

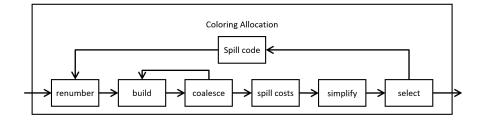

| 1.6        | Chaitin et al.'s iterative graph coloring based register allocator                                         | 20 |

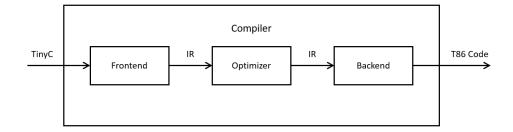

| 2.1<br>2.2 | Compiler                                                                                                   |    |

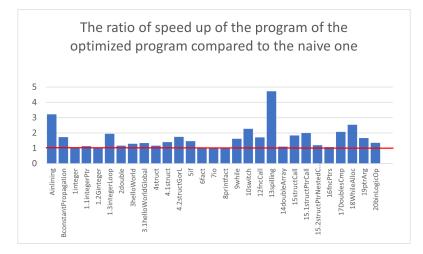

| 3.1<br>3.2 | Graph showing the ratio of speed up of the program of the opti-<br>mized program compared to the naive one | 62 |

| J.Z        | mized program compared to the naive one                                                                    | 62 |

# List of Tables

| 3.1 | Benchmark comparison of code sample A, where there are results    |    |  |

|-----|-------------------------------------------------------------------|----|--|

|     | of the optimized compilation on the left, and on the right, there |    |  |

|     | are results from the most Naïve run the compiler can perform. All |    |  |

|     | units are ticks unless specified otherwise                        | 60 |  |

| 3.2 | Benchmark comparison of code sample B, where there are results    |    |  |

|     | of the optimized compilation on the left, and on the right, there |    |  |

|     | are results from the most Naïve run the compiler can perform. All |    |  |

|     | units are ticks unless specified otherwise.                       | 61 |  |

# Introduction

In the beginning, computers were programmed by directly specifying the operations that the computer was capable of. These operations were encoded as numbers in a representation called the machine code. The construction of such programs was straightforward. The programmer had precise control over the target system's behavior, and the target machine's full potential could be accessed. On the other hand, precise control means that the programmer has to control everything and specify it in the machine code. Unfortunately, such a description of an algorithm, while perfect for the machine, is almost useless for humans because the target operations are far too primitive to describe the complex idea being developed. The first step towards expressing more readable programs for humans was to replace the numbers that encode the operations with short mnemonics, which led to the Assembly language, which was better because the instruction did. But still, the idea of the program was hidden behind the Assembly instructions.

The next evolution came with an abstraction of the operations used in programming, such as loading and storing a variable. This abstraction led to high-level languages. High-level languages use constructs that help programmers avoid repeating code and separate themselves from low-level details that machine code carries with it. The Example 0.1 on the left shows a program written in a high-level language, whereas, on the right, there is an Assembly representation of the same program. There are many instructions, and some parts are repeated. That shows why a high-level representation is more convenient for programmers because they do not need to repeat themselves.

To grasp the program's structure, the programmer can use constructs like functions for specifying reusable code that can vary in inputs, but the core idea stays the same. For these constructs to work, they need to be translated into a correct underlying machine code. Conversion back to low-level details can be done automatically by a program. This program is called a compiler.

```

1; Assembly code

// C code code

2

main:

# @main

int main(){

3

push

rbp

mov

rbp, rsp

4

5

sub

rsp, 16

dword ptr [rbp - 4], 2023

int year = 2023;

mov

6

dword ptr [rbp - 8], 0

int userYear = 0;

7

mov

rdi, [rip + .L.str]

printf("What year were

lea

8

mov

al, 0

you born?");

9

printf@PLT

call

10

11

lea

rdi, [rip + .L.str.1]

scanf("%d", &userYear);

rsi, [rbp - 8]

12

lea

13

mov

al, 0

__isoc99_scanf@PLT

14

call

eax, dword ptr [rbp - 4]

int userAge = year - userYear;

15

mov

eax, dword ptr [rbp - 8]

sub

16

dword ptr [rbp - 12], eax

mov

17

esi, dword ptr [rbp - 12]

printf("You are %d years old."

mov

18

lea

rdi, [rip + .L.str.2]

, userAge);

19

al, 0

mov

20

printf@PLT

21

call

eax, eax

}

22

xor

add

rsp, 16

23

24

рор

rbp

25

ret

26

.L.str:

.asciz "What year...born?"

27

28

.L.str.1:

.asciz "%d"

29

.L.str.2:

30

.asciz You are %d years old."

31

```

Listing 0.1: The difference between high-level (on the left) and low-level(on the right) languages of the same program.

Initially, a brand new compiler had to be created for every language. A simple program that found a statement and converted it to specific target instructions. However, as these compilers evolved and many features were added because programmers realized that compilers could do much more than replace the constructs back. Decisions about the target's resource usage must be made during the compilation. For example, the target machine can have *registers*. Registers serve as storage where the program values are held, and the target machine uses them for addressing. Instructions can copy, load from, and store to the registers.; for example, an ADD instruction loads from two registers, and the result of the addition is stored in a register. Values can also be stored in memory, but the operations working with memory are expensive, therefore, it is better to use them as little as possible.

It is difficult and labor-intensive for programmers to specify which registers should hold which values (and when during the program) while, in the target, there is a limited amount of these registers. Therefore, a machine will solve these problems. Unfortunately, it is very hard or sometimes impossible for all programs. Designing these algorithms to be fast and effective and resolving similar problems arising from optimizing parts inside the compiler is the hard part of creating a compiler. Furthermore, optimization is the next part of why the program compilation is considered challenging because the compiler should not only give a working program but a faster equivalent that does not waste the target resources. The compiler which gives better (faster and more efficient) programs is called the optimizing compiler.

Although constructing a compiler is hard, it is beneficial for programmers because the compiler reduces the amount of work that they need to put into creating a program. Moreover, it prevents programmers from making mistakes in parts that the compiler manages nowadays since it is the responsibility of the compiler, and usually the compiler gives better results than deciding this manually for larger programs. It is also very beneficial because the programmer can focus more on the algorithmic part of the programming; therefore, the development of programs can be faster than before.

# TinyVerse

The task of this Master's thesis is to build an optimizing compiler, which can be used in a course NI-GEN, where students are required to build a naïve compiler. This thesis presents a compiler with more features so the students can see what is the difference between using various optimization techniques and none — compiling entirely naïvely.

The TinyVerse project helps with compiler teaching. It is a whole package that can compile and run compiled code. All languages and targets share the compiler functionality. The languages and targets then provide the languageand target-specific functionality, such as front-ends, Optimizers – middle-ends, and back-ends. The whole system is designed so that its parts can be swapped at compile time to suit different languages, targets, optimizers, etc.

Two parts of TinyVerse are essential for this thesis.

The first is the TinyC language, which we will compile. TinyC is a C-like language with a smaller subset of types (int, char, double, arrays and structs, function pointers, and pointers) and a limited set of features. TinyC's semantics and grammar are simpler, which makes TinyC not a strict subset of C. The language specification can be found in chapter B located in the appendix of this thesis.

The second is the package t86 which contains tiny86 virtual machine — the target to which the compiler from this thesis compiles. Tiny86 was inspired by the x86 Architecture, but with a reduced instruction set so it is easier for students to understand the compilation process. The simplification kept both interesting and important parts of the x86 architecture which are valuable for teaching.

# Thesis Overview

This thesis comprises four chapters: Overview, Design and Implementation, Evaluation, and Conclusion.

- The chapter Overview describes how modern compilers are designed. Modern compilers define an internal representation (IR) that serves to represent the source program in a form that is more suitable for the compiler; section 1.2 describes the internal representations — their design, advantages, and disadvantages of various designs. It also describes the composition of regular modern compiler suites, and the most popular compiler suites nowadays.

- The second chapter, Design and Implementation, describes and justifies the ideas behind the algorithms picked for the implementation including the design of the internal representation, description, and examples of the translation performed in the front-end and the ideas behind the algorithms used in the Optimizer and the compiler's back-end.

- The third chapter, Evaluation, contains the evaluation of the optimization changes in terms of effectiveness and the number of instructions that need to be executed.

CHAPTER **1**

# **Overview of a Modern Compiler**

Compilers used to be straightforward programs that only replaced parts of the input code for sequences depending on which target machine the compilation was performed. Making keywords instead of low-level sequences has two significant benefits, the independence from the target machine — the programming no longer requires specific coding instruction and the readability for a programmer. With this evolution came slight problems in the form of question: Values are stored in registers, and who defines which value comes to which register? First languages used hint keywords by which the programmer could specify in which register the value should be, and the compiler's task was to respect the constraints that the programmer gave for a value where it should be. However, as compilers evolved, less and less emphasis was put on that functionality. The task of which value should reside in which register soon became the task of compilers. Like this, more tasks make the outputted programs faster or memory efficient. Generally, compilers are valuable tools for programmers and became more complicated.

Throughout the evolution of compilers, rules were established that define what every compiler should do:

- 1. The compiler has to generate an appropriate valid output for every valid input. So, the outputted program has to keep its behavior described in the input program.

- 2. It should warn and terminate the compilation if the input is not valid.

- 3. Also, the output program should be as effective as possible. Concerning the size or speed of execution of such a program. (This is why compilation is considered challenging.)

The core of every modern compiler of some programming language is often very similar. This similarity comes from the fact that it has the same task of translating and optimizing. It reads the input, performs some optimization, and translates it into or machine code. As the compiler has several tasks to help the programmer with, it is helpful to divide modern optimizing compilers into parts. This separation also has advantages considering reusability when another source language or target machine needs to be supported.

When the compiler parts can be swapped, an interface must be designed. This interface in the program representation is called intermediate representation. The modern compiler parts are the front-end, middle-end, and back-end as shown in Figure 1.1.

Figure 1.1: High-level overview of a Modern compiler

- *Front-end:* The front-end task is translating the source language to the intermediate representation specific to the compiler.

- *Middle-end:* The middle-end is the core of the compiler. It performs all operations specific to the Optimizations, making the outputted program more efficient.

- *Back-end:* The back-end's task is a translation to the specific target; when a different target has to be used, the target has to be changed. It contains all parts of the compiler dedicated to the specific target.

When compilers need to translate source code described in a different source language or compile to a different target, they differ only at the beginning of the process; thus, a front-end has to be changed to support the language, or the second difference is at the back-end, where a different target and its instruction set is available that means a change in code generator and target optimizations.

The next part describes the most significant parts of a compilation with more details.[1]

- *Front-end* with the task to understand and transform the source program, find errors in it, and translate it into IR can be separated into parts:

- *Lexical Analysis* The task of lexical analysis is to read and separate its input into tokens defined by the input language. For example,

Figure 1.2: Design of front-end internals of a modern compiler

if,  $\{$ , 5. This part aims to have less work while implementing syntax analysis.

- Syntax Analysis The task is constructing an abstract syntax tree (AST) structure from the tokens produced before. This step also checks the validity of the input code and that the AST nodes can be created from the input.

- Semantic Analysis checks the correctness of the AST. The main part is the Typechecker, which checks if the program is type sound – if the used operations support the types supplied to them. Semantic analysis can check the validity of working with variables if it is declared before use. These first three steps also generate errors for the error handler that informs the programmer where a mistake happened or warnings about some part of the code will work but maybe not as intended.

- *IR generation* After the correct AST is constructed and passed to the IR generation, the IR is generated. The form of IR is specified by the compiler and is useful for various analyses. The form is usually of an SSA or a three-address code type.

- Target independent Optimizations perform the majority of optimization generally in separated passes. This part belongs to *middle-end*. The advantage is that these optimizations are neither source- nor target-dependent.

- The *back-end*'s task is to translate the IR into the target code. It consists of two parts:

- *Code Generator* The next step is to translate the independent IR into a code mainly designated for the target in the form of a machine code. For this translation, instructions and registers need to be selected. Both processes play a crucial role in the efficiency of the target code.

• Target-dependent Optimizations The last part eliminates the suboptimality generated in the previous step and the target-dependent optimization.<sup>1</sup>

If there is a need for a compilation of a large program, it is possible to multiply all three parts of the compiler so that they can run in parallel, but then an additional step called linking is required to build the final program. For this purpose, objective files are constructed by the back-end instead of a full-fledged executable. The linker takes object files and patches dependencies between them.

## 1.1 Front-end

The front-end translates the input programming language to the Internal Representation. Translation can be done naïvely in case each keyword or construct in language has its specific form in Internal Representation. If the IR instruction is not present, a transformation into a combination of IR instructions that achieves the same result is necessary.

### 1.1.1 Lexical Analysis

Lexical analysis is the first phase of a compiler. The lexical analyzer breaks the input into a series of tokens by removing any whitespace or comments in the source code. If the lexical analyzer finds a token invalid, it generates an error. The lexical analyzer works closely with the syntax analyzer. It reads character streams from the source code, checks for legal tokens, and passes the data to the syntax analyzer.

Tokens are of several types:

- Keywords are words reserved by the source language with special meanings such as int, break, or while.

- *Identifiers* are words that meet requirements defined by the language, usually used for naming constructs supported by the source language.

- Operators The special non-alphabetical characters define operators.

- Numbers are integral or decimal, created by digits.

- *Strings* and *Characters* are sequences of characters usually surrounded by language-defined characters.

<sup>&</sup>lt;sup>1</sup>In some literature, the last two steps are swapped or merged together. But the work that needs to be done persists.

### 1.1.2 Syntax Analysis

Syntax analysis, also known as parsing, is the phase where the compiler analyzes the structure of the source code and checks for syntax errors. The primary goal of syntax analysis is to ensure that the code conforms to the rules of the source language's grammar and does not include any (grammar) errors.

During the syntax analysis phase, the parser analyzes the source code broken down into tokens obtained from the lexical analysis. The parser checks that the sequence of tokens is valid according to the source language grammar. The parser generates an abstract syntax tree (AST), which represents the code structure without the details of the tokens. Syntax analysis can detect syntax errors, such as missing semicolons, mismatched parentheses, or invalid expressions. When syntax errors are detected, the parser generates error messages that help the programmer correct the errors.

### 1.1.3 Semantic Analysis

Semantic analysis is the phase where the compiler analyzes the meaning of the source code and checks for semantic errors. Errors in this part that can appear are grammatically correct but do not make sense. For example, the program is not type coherent. The primary goal of semantic analysis is to ensure that the code is semantically correct and can be executed without any issues.

# **1.2** Intermediate Representation

Intermediate representation, mostly called IR, represents the input program and other compiler-generated information that the compiler needs to work with and understand. IR is a representation independent of the source code and target machine. It resolves tasks such as how to represent the control flow, machine operations, types, etc.

The advantages of using this representation should be:

- Easy to process, such as create, read, write, traverse, or transfer.

- Easy to optimize, for example, allowing target-independent low-level optimizations.

## 1.2.1 Types of IR

Types of IR can be conceptually divided by the form of the representation — main classes are graphical and linearized. Abstract syntax trees or control flow graph belong to the graphical class. Stack based and Three-address code belong to the linear-based class. The linear based are closer to a machine

code, therefore, are considered a lower-level. The last is *Hybrid class*, which combines the properties of both mentioned.

## Tree Based

Tree-based IR is used to represent the structure and semantics of a program in a hierarchical tree data structure. In this representation, each tree node represents a statement, expression, or other constructs in the source program. It is often pictured with edges representing the relationship between the nodes. In tree-based IR, can be found AST or parse trees.

The advantage is that these types of IR are closer to the source language and can usually express all the source semantics. Source language type systems and variables can be reused. The tree IR is a trivially constructed prom parser. And they are easy to translate, for example, by syntax-driven code generation. Tree IR is great for local optimizations like constant propagation or common sub-expression elimination.

The disadvantage comes from tree representations being far from the target language. Memory efficiency is unsatisfactory because of its poor locality in the naïve form. This representation is unsuitable for global optimizations when they do not provide information about the program's control flow.

### Linear Based

The second structurally different type of IR is the linearized one. This representation's structure is a sequence closer to the machine code. Therefore this IR can be considered a lower-level than tree based.

#### Stack Based

The stack-based IR uses stack structure to address values; therefore, most instructions do not need explicit specification of arguments. They get them from the stack. They represent operations such as pushing to or popping from the stack. When performing an arithmetic operation, binary, for example, the input operands are taken from the top of the stack. The result of an operation is pushed back to the stack.

The most significant benefit of stack IR is simplicity and straightforwardness. The small instruction set belongs to the advantages of this IR because stack IR always works with the top of the stack; there is no need for complex addressing features that require more memory to encode the instruction.

On the other hand, other simple operations, such as code movement, are difficult to perform. Just moving the instructions is not enough; preparing and reorganizing the stack for movement is also necessary.

#### Three-address Code

In three-address code (3AC), each statement is represented as a sequence of up to three operands and an operator. The operands can be either constants, variables, or temporary values. The difference between temporary value and variable is that temporary value originally does not have a place in memory where it can be stored. So when there is a requirement to store it, extra work is required to prepare the memory. In Example 1.1, you can see how expression d = (a + b) \* 15 + (a + b) can be translated into the 3AC.

Listing 1.1: Example of three-address code where are used constants, variables, and temporary values

The advantage of the three-address code is its similarity to target instructions because many ISA instructions do not have more than two operands and one output. The next advantage is how easy it is to reorder instructions in a program represented in a three-address code. Instructions can be stored in a list where insertion is easy, and when a few rules are followed when reordering, there is no problem like in stack-based, where instructions need to be added to emulate the stack behavior. Rules such as do not swap instructions after the position of its first use.

### 1.2.2 Single Static Assignment

In compiler design, static single assignment form (often abbreviated as SSA) is a property of an IR, which requires that each variable is assigned exactly once, and every variable is defined before it is used. Existing variables in the original IR are split into versions, new variables typically indicated by the original name with a subscript so that every definition gets its own version.

When converting to SSA, the tool to preserve the rule is the following: Variable names are appended with indexes that are incremented at each new assignment. Figure 1.3 demonstrates the conversion.

Figure 1.3: Example of conversion to SSA Form with the use of indexes.

#### 1. Overview of a Modern Compiler

However, when using this technique, a problem occurs when translating expressions with arguments dependent on the program's control flow. It is shown in Figure 1.4. The solution is to introduce a 'Phi' Instruction<sup>2</sup>. The

Figure 1.4: Problem occurring in conversion to SSA Form.

'Phi' instruction helps us to use a result from two or more different source instructions in case they are in different Basic Blocks. It manages that each source instruction will eventually share the same register as Figure 1.5 shows.

Figure 1.5: Usage of Phi instruction to resolve problems with the conversion.

The reason to use the SSA form is that it brings benefits for analysis. Look at the situation in Figure 1.3; humans can see that the first line is

$<sup>^{2}</sup>$  can be found under *Phi Node* term.

useless because it is overwritten right after the assignment, but a reaching definition analysis must be done for a computer if the code is not in SSA. Other compiler optimization algorithms, such as dead code elimination, common sub-expression elimination, constant propagation, register allocation, etc. are faster and easier to perform when SSA is used.

# 1.3 Optimizer

The Optimizer has two parts, analysis and optimization. Its task is to analyze the program and find parts that can be rewritten so the program runs faster or to find dead code, which can be omitted, and therefore the program size will be smaller.

This part of a compiler is in the middle-end. Some optimizations require only a pattern to be found, and others require analysis results. These optimizations and analyses run in a loop because the code optimization usually unlocks another optimization. For example, code with tricky dependencies prevents dead code elimination (DCE) from optimizing. However, constant propagation (CP) optimizes a chunk of the tricky part, making it decidable for DCE afterward. The idea is demonstrated in Example 1.2.

| 1 | //1) original code | //2) after CP | //3) after DCE |

|---|--------------------|---------------|----------------|

| 2 | a = 5;             | a = 5;        | a = 5;         |

| 3 | b = 0;             | b = 0;        | b = 0;         |

| 4 | if (b > 4){        | if(0 > 4){    |                |

| 5 | a = 7;             | a = 7;        |                |

| 6 | b++;               | b++;          |                |

| 7 | }                  | }             |                |

| 8 | b +=10;            | b +=10;       | b +=10;        |

Listing 1.2: Example showing how entangled can optimization passes be. In code number 1) the 'then' branch cannot be easily removed due to the variable b. But after CP showing and replacing b with its constant, dead code elimination can see the guard is false and therefore the 'then' branch never executes, thus the code is dead and can be removed.

Pass Scheduler decides how long and what attempts for optimizations are made. The Pass Scheduler is a maintainer of all passes and decides when to start which pass (optimization) will be started, after which one, how many times, and when to end with the optimization. All these decisions are based on the outputs from the analysis that is run between passes or, in better implementations, results of the analysis are updated by the passes because running whole types of analysis could be potentially costly and sometimes even not possible when various types of profile information are stored.

#### 1.3.1 Analyses

The analyses are often divided into two sections, static and dynamic. Dynamic analysis techniques can be used to evaluate the performance and behavior of compiled code, but they are not typically used directly within the compiler itself. The dynamic analysis emulates the execution and collects results. Static analysis involves examining the source code or intermediate representation of a program without the need for emulation or execution.

Every (perfect) analysis goal is to satisfy three properties:

Soudness: Analyses should not miss any errors,

Completeness: Analyses should not raise false alarms,

Termination: Analyses should terminate with a given answer.

Unfortunately, thanks to Rice's theorem, this cannot happen. That is why analyses only approximate and cannot give an exact answer (we wish to have) to every question about the program.[2] The approximation is made so that the answer might be decidable and the results are safe, meaning they must be conservative. For example, we are trying to eliminate an expression from the program. The analysis is asked if the code can be eliminated — its result is not used. The safe answer is that the result is used; we can only eliminate the expression if we are sure it is not used. Otherwise, the optimization would cause errors in the program. Specifying tight criteria can give useless results since the algorithm cannot be sure; on the other hand, too loose criteria can give correct but useless for the Optimizer. So the challenging part about static analysis is to get results that are not useless and do it in a reasonable time and space.

Analyses can also be divided by the range, where the analysis is performed.

An *intra-procedural* analysis is a mechanism for performing optimization for each function, using only the information available for that particular function. Its results are useful for local optimization.

An *inter-procedural* analysis performs analysis on the whole program. Its results are used in global optimizations, which need to consider greater parts of the program. For example, function inlining needs to have information about the whole program. Inlining recursive functions is not beneficial.

The next separation of analysis algorithms is in the direction they perform the analysis, the so-called *forward* and *backward* analysis. This considers how the information is enhanced throughout the analysis.

For example, *liveness analysis*, which gives information about the live ranges of the variables, belongs to the backward analyses. On the other hand, the reaching definition analysis is of the forward type. *Reaching definitions* analysis is useful for dead code elimination. It generally thinks that every variable is not alive at the end. When the first use of the variable is seen (in the backward run – so the last use in the program), the variable is added to

the alive set. Then when the definition is seen, it is again removed from the alive set. The result of the liveness analysis is the contents of the alive set at each time.

#### 1.3.2 Optimizations

The optimizations in a compiler are classified into two types: machine dependent and machine independent optimization. The machine-dependent belongs to the back-end part of the compiler and is driven by constraints like what instructions the machine supports or a set of hazards that can occur in the machine. Independent optimizations are located in the middle-end.

The part that makes machine-independent optimization, called Optimizer, has to take results from the analysis described before and performs code rewriting to make the execution of the code faster or to make it more compact in terms of code size.

Generally, optimizations can be divided into global and local ones. Local optimization involves finding the optimal solution for a specific search space region. The global optimization for problems with greater and more complex search space. Therefore, local optimizations are easier to perform because the analysis can give a more specific result due to the reduced context on which the desired change depends. On the other hand, local optimization cannot solve all optimization problems, such as function inlining, there needs to be performed a change across the whole program.

#### **1.3.2.1** Local optimizations

Local optimization is a technique of making a code inside a region more effective for some given criteria. It takes results from the intra-procedural analysis. Generally, the region is a Basic Block since there are no troubles with control flow. To local optimization belongs:

- *Constant folding* involves evaluating constant expressions at compile time instead of at runtime. This optimization can improve the performance of a program by reducing the number of instructions executed.

- Algebraic simplifications simplify algebraic expressions in a way that does not change the value of a result but is the most efficient or compact to represent.

- Dead code elimination (DCE) is an optimization that identifies and removes sections of code that are no longer needed nor executed during the program's runtime. It improves performance while 'Jump' instructions are removed, reducing the code size overall.

#### **1.3.2.2** Global optimizations

Global optimization can consider the whole functions, where more constraints affect the result, and thus the optimization is more complicated to accomplish.

For example, it makes sense to make constant propagation in a Basic Block and extend it to the whole function while considering the local variables in the whole program. The same applies to function inlining; without the ability to change multiple functions in the program, achieving the desired result would not be possible. To representatives belongs:

- *Function inlining* involves replacing a function call with the body of the called function. This optimization can improve the performance of a program by reducing the overhead of function calls.

- *Common-subexpression elimination* (CSE) involves identifying repeated computations in a program and replacing them with a single computation. This optimization can improve the performance of a program by reducing the number of redundant computations and the number of instructions executed.

- Constant propagation (CP) involves replacing variables or expressions with their known constant values at compile time. This optimization can improve the performance of a program by reducing the number of instructions executed.

# 1.4 Back-end

The back-end's task is to translate the result from the Optimizer into a target-specific language, generally into the target-specified instruction set architecture (ISA). So the instructions represented in IR should be rewritten into a sequence of the target instructions.

After producing the target code, there can also be the last part that does the target-dependent optimization because translation often leaves bits that can be further optimized. Such Optimizer can be, for example, *Peepholer*. Peepholer looks at a few instructions in the 'peephole' and tries to find a pattern to be optimized within the peephole. The peephole is shifted throughout the program.

#### 1.4.1 Instruction Selection

Instruction selection maps IR instruction to target instruction so that the result is efficient in execution but requires the minimum amount of instructions and target resources possible to achieve the correct result. Generally, it is responsible for converting the constructs in IR into machine code. How much

this process is demanding depends on the desired quality of the generated code, the level of IR, and the target instruction set architecture.

The process involves analyzing the intermediate representation of the program and selecting the most efficient sequence of machine instructions to implement each operation. The process can be described in several steps:

- Generating a candidate set of instructions: The compiler must generate a set of possible machine instructions for each high-level construct to implement the operation.

- Evaluating the candidate set: The compiler must evaluate each candidate instruction's correctness, efficiency, and adherence to the target architecture's instruction set. This evaluation involves analyzing the instruction's latency, throughput, register usage, and other factors impacting the program's performance.

- Selecting the optimal instruction: Based on the evaluation, the compiler selects the most efficient instruction from the candidate set to implement the operation. This selection process may involve heuristics, such as choosing the instruction with the shortest latency or the lowest register usage.

Various techniques can be used for the generation of the candidate set and selection of the optimal instruction:

- *Table-based code generation:* This technique uses tables or matrices to map high-level language constructs or IR code to corresponding or machine instructions. These tables can be hand-coded or automatically generated by a tool.

- *Pattern matching:* This technique involves matching patterns in the high-level language construct or IR code with pre-defined patterns of code or machine instructions. These patterns can be hand-coded or automatically generated by a tool as well.

- *Tree-based code generation:* This technique involves representing the high-level language construct or IR code as a tree and using tree traversal algorithms to generate the corresponding or machine instructions.

- *Dynamic programming:* The problem is formulated as an optimization problem, and an optimal solution is found by dynamic programming algorithms.

- *Constraint solving:* The problem is formulated as a constraint satisfaction problem, using constraint-solving algorithms to find a solution that satisfies the given constraints.

More straightforward techniques considering only instruction at a time generate inefficient code; therefore, a peephole optimization often runs after the IS. The next section 1.4.2 describes the peephole optimization. Chosen techniques overall depend on various factors such as the complexity, form of the IR, the performance requirements, and the available resources.

## 1.4.2 Target specific optimizations

Target-specific optimizations are compiler optimizations that are designed to take advantage of the specific features and capabilities of a particular hardware architecture or target platform. Peephole optimization is a type of local targetspecific optimization technique, which improves the performance of generated code. It involves analyzing a small window of instructions in the code, known as a 'peephole,' and replacing the instructions with a more efficient sequence of instructions that achieves the same result.

The peephole optimization technique is based on the idea that small code sequences often contain inefficiencies that can be removed by analyzing the instructions in a small window. The window typically contains three to five instructions, and the optimization is applied to all possible windows in the code.

#### 1.4.3 Register Allocation

Register allocation (RA) is a technique that involves mapping the values of a program to the limited number of registers available in the target, in order to minimize the number of memory accesses required during program execution. By keeping frequently used variables in registers, this technique can improve program performance.

The problem of register allocation is complex and falls under the category of NP-hard problems. Therefore, finding the optimal solution to register allocation is not feasible in practice. However, there are several simple solutions to this problem that can be used in compilers:

- *Naive approach:* This approach simply allocates a register for each variable used in the program. When no registers are full, pick the oldest for release. However, this approach may lead to many register spills (i.e., storing the register value back to memory), and hence performance may not improve.

- *Graph coloring approach:* This approach views the register allocation problem as a graph coloring problem, where the nodes represent the variable's live ranges and the edges represent conflicts between them. This approach can be applied to both local and global register allocation problems.

- *Linear scan approach:* This approach uses a linear scan of the program to allocate registers to variables. This simple and efficient approach may not always generate an optimal result.

- *Heuristic-based approach:* This approach involves using heuristics to guide the register allocation process. Examples of heuristics include the use of spill costs and register pressure.

- *Hybrid approach:* This approach combines multiple register allocation techniques, such as graph coloring and linear scan, to achieve better performance.

The peephole optimization should be performed again to obtain even better results because RA adds the spill code, which can also be optimized.

The register allocator's tasks are:

- To maintain all registers for values that reside in registers.

- To maintain a spill table mapping all values in memory and their addresses.

- To decide which values in registers will be spilled to free up space for new values.

- To resolve at which point of execution a restoration of spilled value is required. That means where to load value back to register to keep the values in registers consistent with the computation that requires these values.

#### **Coloring Allocation**

The Coloring Allocation's task is to select which target registers will carry which values and which values to spill to minimize the number of spills over the execution. It was first introduced by Chaitin et al.[3]

The idea is to represent this problem as a graph in which nodes represent live ranges (temporary values, variables) that need to have assigned a target register and edges connect interfering live ranges, i.e., live ranges alive at the same time, which might be conflicting for a target register. Register allocation this way is reduced to a graph coloring problem: which colors (registers) will be assigned to the nodes such that two nodes connected by an edge do not share the same color. The graph can be built using a liveness analysis.

The allocator consists of the phases shown in Figure 1.6 are following:

- *Renumber:* Detect live ranges and number them in the IR.

- Build: Compose the interference graph of the live ranges.

- *Coalesce:* Merge the live ranges of variables with the same value i.e., those created with copy instructions and rebuild the graph.

- Spill cost: Determine the cost of spills for each variable.

- Simplify: Color the graph nodes and continue with selection.

- Spill Code: Insert spill code, including load, stores, or move instructions.

- *Select:* Select a register for each position (instruction) that requires the register; if not possible, add a spill code.

Figure 1.6: Chaitin et al.'s iterative graph coloring based register allocator

#### 1.4.4 Instruction Reordering

Instruction reordering is useful for superscalar processors when more instructions without specific dependencies can be executed together. Superscalar processors use instruction parallelism to achieve faster execution. Each instruction is divided into some execution parts, such as instruction fetch, operand fetch, ALU, and others. However, problems called hazards appear when the processor wants to start the execution of an instruction that does not have a result ready while it is still in the process of computation. That way, the processor needs to insert *NOP instruction* and therefore stall in computation. So the task is to prepare the code for the processor in a way that the instructions do not need to wait on each other and utilize all parts of the processor as much as possible therefore if it might be helpful to reorder instructions to reduce the time necessary for a program to finish.

Nowadays this problem is solved by the target itself. The target has buffers and computes instructions that are eligible for computation in a different order. The eligible instructions are those that will not produce a different result when executed now (out of order). This way compiler reordering task is not as significant as it was before.

# 1.5 Case Studies

It is reasonable to talk only about two compiler suites at this time. Nowadays, two main compiler suites exist: The GNU C Compiler (GCC) and the LLVM. There also exist other compilers like javac, D compiler, etc. However, these are language or target specific; therefore, the inner structure differs from the modular, in which this thesis is interested.

#### 1.5.1 GCC

GCC (GNU Compiler Collection) is a compiler suite developed as a GNU project. Richard Stallman founded the project to create a completely free operating Unix-like system. However, no free compilers were available for C language he could use by then. So he decided to develop his own.

The first version of GCC was released in 1987 under the name GNU C Compiler. This release significantly impacted the development of openly licensed software because even nowadays, C language is widely used.

In 1997 a fork called EGCS was founded. This project was better at optimization and had better support for C++ and Fortran. This project was an answer to a too-strict policy for upgrades. After two years, the Free software foundation acknowledged project EGCS as an official compiler of the GNU project. After that, these projects were united again.[4]

GCC supported many different target architectures, from micro-controllers to the most performant ones. Also, it can translate many languages, including C, C++, Fortran, Java, or Go, and is used as the default translator in modern Unix systems — in many different variants, GNU/Linux or BSD.[4]

#### Intermediate representations

GCC uses all together three forms of internal representation GENERIC, GIM-PLE, and RTL. GENERIC serves as an independent representation of the higher-level input language. This form is used in the front-end. It has a form of a typed AST. Types are common for all GCC front-ends. It is also possible to define own types of AST nodes if the source language requires so.

```

1 int g = 4;

2 int main(){

3 int l = 16;

4 return g < l;

5 }

```

Listing 1.3: Example C code

After the input is unified, the GENERIC is translated into GIMPLE using so-called *gimplifier*. If own types were defined, functions translating own types to GENERIC or straight to GIMPLE are required. All platform-independent optimizations are then made on GIMPLE, which is a subset of the generic

```

main ()

2

{

3

int l;

int D.2318;

4

5

l = 16;

6

g.0_1 = g;

7

_2 = l > g.0_1;

8

D.2318 = (int) _2;

9

goto <D.2319>;

10

11

D.2318 = 0;

goto <D.2319>;

12

<D.2319>:

13

14

return D.2318;

15

}

```

Listing 1.4: Example GIMPLE for C code from example 1.3

language. Complicated structures that are possible to represent in GENERIC are forbidden in GIMPLE and therefore disassembled into less complicated constructs with only three operands. This way, a three-address code is obtained. Gimple is also transformed into an SSA form. In the documentation, they call it 'Tree SSA.' The last transformation step is to convert 'HIGH GIM-PLE' to 'LOW GIMPLE.' The difference is a description of control flow. The 'HIGH GIMPLE' contains control-flow structures, but the 'LOW GIMPLE' contains only conditional jumps.

```

1 main ()

2

{

int l;

3

int D.2318;

4

5

int g.0_1;

_Bool _2;

6

int _5;

7

8

9

<bb 2> :

l_3 = 16;

10

g.0_1 = g;

11

_2 = l_3 > g.0_1;

12

13

_{5} = (int) _{2};

14

<bb 3> :

15

<L0>:

16

return _5;

17

18

19 }

```

Listing 1.5: Low GIMPLE representation for C code from Example 1.3

The final form is named Register Transfer Language, known as RTL, which in the back-end serves as an independent interface for performing back-enddependent optimizations. RTL is inspired by Lisp lists and is composed of 'RTL Classes,' which can be combined into more complex ones called 'RTL expressions.' These expressions are used to precisely describe what a target instruction does, how it behaves, which types it uses, and other properties. Example 1.6 shows commented the RTL representation.

#### Optimizations

Optimization in GCC is performed throughout the compilation in several parts. Some are target-independent, others target-dependent. The Target dependent optimizations are performed in the back-end on the RTL form. The first optimization is performed while conversion into GIMPLE is made; the part is described as Analysis and Optimization of GIMPLE tuples. This part converts The Generic into SSA, and alias analysis is also performed.[5] The second important construct for optimization and analysis is Control Flow Graph (CFG). It is built on top of the intermediate representation. The demanding part of CFG is maintaining it throughout the compilation and optimization, as reconstruction is too expensive, and some information may not be obtainable again. CFG keeps the information about Basic Blocks and profile information like frequency and counts, specifying how often the part is executed. These statistics are necessary to decide which optimization should be used because it might trade between code size and execution time.

There is also a component in GCC called Link Time Optimization (LTO) which works by dumping GIMPLE or RTL into a file and then traversing the file looking for parts that can be optimized. This approach is beneficial because it has all the module's information accessible at link time.

The inter-procedural optimizations (IPA) are performed and organized in IPA passes in the Link Time Optimization (LTO) section. The IPA passes are organized into three categories — small, regular, and late passes. Each pass has several stages, and depending on the category, they are run in a different part of the compilation — operating at different times of the compilation. Stages are LGEN, WPA, and LTRANS. These stages describe the general needs for general optimization:

- Analysis which is made in *LGEN time* generates and writes down a summary.

- Propagation or execution that transforms a copy of CFG is described as WPA time. This way, the original functions, and variables stay untouched because there would be inconsistency between starting analysis and operations that each pass wants to make. This process may create conflicts. At this time a decision on how to resolve these conflicts that may some passes create is made as well. For this operation are useful profile options as well.

```

(note 1 0 3 NOTE_INSN_DELETED)

(note 3 1 2 2 [bb 2] NOTE_INSN_BASIC_BLOCK)

(note 2 3 5 2 NOTE_INSN_FUNCTION_BEG)

(insn 5 2 6 2 // l_3 = 16;

E

(set

(mem/c:SI

6

(plus:DI

7

(reg/f:DI 77 virtual-stack-vars)

8

(const_int -4 )))

9

(const_int 16 )) -1

10

11

(nil))

(insn 6 5 7 2 // g.0_1 = g;

12

13

(set

14

(reg:SI 82 [ g.0_1 ])

(mem/c:SI (symbol_ref:DI ("g") [flags 0x2]

15

<var_decl 0x7f9876c8ee10 g>) [1 g+0 S4 A32])) -1

(nil))

17

(insn 7 6 8 2 // _2 = l_3 > g.0_1;

18

19

(set

(reg:CCGC 17 flags)

20

21

(compare:CCGC

22

(mem/c:SI

23

(plus:DI

(reg/f:DI 77 virtual-stack-vars)

24

(const_int 4 -1 )) )

25

26

(reg:SI 82 [ g.0_1 ]))) -1

27

(nil)

(insn 8 7 9 2 // (int) _2

28

29

(set

30

(reg:QI 83 [ _2 ])

31

(gt:QI

(reg:CCGC 17 flags)

32

33

(const_int 0 ))) -1

34

(nil))

(insn 9 8 12 2

// _5 = _2;

35

(set

36

(reg:SI 84 [ _5 ])

37

(zero_extend:SI (reg:QI 83 [ _2 ]))) -1

38

39

(nil))

40

(insn 12 9 16 2 // return _5;

41

(set

42

(reg:SI 85 [ <retval> ])

(reg:SI 84 [ _5 ])) -1

43

44

(nil))

(insn 16 12 17 2

45

(set

46

(reg/i:SI 0 ax)

47

(reg:SI 85 [ <retval> ])) -1

48

49

(nil))

(insn 17 16 0 2

50

51

(use (reg/i:SI 0 ax)) -1

52

(nil))

```

Listing 1.6: Exmaple RTL for C code from Example 1.3

• Transformation which sees the result of WPA time and changes the original structures underneath by the result obtained in WPA time. This stage is referred as to LTRANS time.

The small IPA is compact because it cannot be separated into stages. Examples of small IPA are 'IPA remove symbols,' which performs reachability analysis and removes unused symbols, or 'IPA increase alignment,' which is helpful for vectorization.

Regular uses all stages like 'IPA constant propagation,' 'IPA inline,' or 'IPA identical code folding.'

Lastly, the late IPA is described as performing all at once as small but later after regular passes are performed. To late IPA's belong, for example, 'IPA points-to analysis.'

GCC has a WHOPR option that performs optimizations in parallel, that is the reason why the passes are designed like this, especially in *WPA time* where it operates on the copy.

#### **Back-end**

The GCC back-end uses RTL and definition files of the target instruction set. The task is to transform the RTL to a shape that is similar to symbolic address language. So the translation to a symbolic address language can be trivially performed. The work of the back-end can be separated into several steps

- *RTL generation* also called 'expand'. This first part converts GIMPLE to RTL with the help of instruction patterns. Some mandatory definitions exist in the back-end, but also optional can be implemented. If there are none, the compilation ends with an internal error.

- *optimization* After RTL is generated, some optimization steps are run, including condition conversion, tail call elimination, or common sub-expression elimination (CSE).

- *instruction combining* Similar to peephole optimization tries to combine several RTL instructions into one. Together with previous steps, this belongs to instruction selection and has the greatest impact on which target instructions will be in the final product.

- register allocation This part contains several passes over the RTL, continuously replacing virtual registers called 'pseudo registers' with fixed ones and replacing instruction patterns. Hence, the arguments are acceptable by the target definitions. Register spilling and restoring and function prologs and epilogues — etc. calling conventions — all these steps are made in this part too.

*final* the last pass that writes in the output file. For every RTL instruction, an adequate representation in symbolic address language is selected with the help of the target description.

Target description is done with RTL and C macros. The description of the general properties and characteristics of the target architecture is a composite of three files one C-like pair *target.h*, which defines the target properties, and *target.c*, which defines an extra functionality which overrides the defaults, and one *target.md* which serves as an input to the compiler in compile time.

#### 1.5.1.1 Conclusion

In summary, GCC is a mature and reliable compiler suite that has been used for decades to build high-performance software. Its flexibility, performance, and open-source nature make it a popular choice for developers around the world.

#### 1.5.2 LLVM

The LLVM Project is a collection of compilers and toolchain technologies — programs and libraries written in C++.[6]

The project was founded in 2000 by a research group of developers at the University of Illinois in Urbana Champaign. The original goal of this group was to examine dynamic translation techniques. Therefore the name was Low-Level Virtual Machine, but nowadays, the original was extended further. It is used in many projects, so it changed the name to LLVM as the last name's abbreviation since the original idea drifted slightly in a different direction.[7]

Essential parts of LLVM are platform independent optimizer, code generator of LLVM Core, and compiler of C, C++, and C-Objective language called Clang. However, this project supports more languages like Fortran, Ada, Rust, Swift, etc. Some of them belong to the 'DragonEgg' project, which combines the GCC front-end with the LLVM optimizer and back-end. The following useful thing is that LLVM contains other tools like a debugger, assembler, or even a standard C++ library. That is why LLVM began to be used with branches of UNIX systems as an alternative to GCC and GNU Binutils. It is composed of modules and libraries useful for both programmers and end-users.

The LLVM Core is the core part of LLVM. Most of the time, by referring to LLVM, it is referred to this part. It consists of libraries and programs working with intermediate representations called LLVM IR. LLVM developers use these to interact with the IR; end-users should not need to use them themselves. A description of such programs follows:

*llvm-as* Is a program that converts assembler LLVM IR from a text file to the program's binary representation. The instructions in bytecode format are still from the LLVM IR, not the native bytecode ones.

- *llvm-dis* The program is used to convert bytecode byte form into LLVM IR text form.

- *llvm-link* Servers as Linker for LLVM bytecode. Combines more binary files containing bytecode into one output file.

- *lli* The program for interpreting the LLVM bytecode. Runnable on x86 architecture, Sparc, and PowerPC and supports just-in-time (JIT) translation as well.

- *llc* This program serves as the back-end of LLVM. Its task is to translate LLVM bytecode (IR) into instructions the target supports. The output can also be in the language of symbolic addresses or an object file. This program is a cross-translator as it can translate into different targets without the need for the recompilation of the whole project.

- *opt* Is the middle-end of LLVM. It contains optimization techniques that LLVM does. From input reads in LLVM bytecode or text LLVM IR form. Optimizes it and optimized code saves into output in LLVM IR.

#### Bitcode

LLVM IR is a universal SSA form represented by a three-address code that creates the interface between the front-end where it is created, the middle-end where optimization passes use it, and the back-end where it is transformed into target code. The best property of LLVM IR is its independency on all inputs and its 'storability.' Hence, it is possible to store it anytime, load it afterward, and continue without any information loss. At the end of the translation ending with the same result as no memory dump was performed. This property is very useful for scaling for parallel runs. Programs written in the form of LLVM IR are composed of modules where each module refers to each input file. Each module specifies a symbol table, global variables, and functions of the input program.

Instructions are divided into several categories

- *terminating instructions* are those that do not produce any computation result; therefore, its return type is typically *void*. They are used to alter the control flow of a program. Instructions like *indirectbr*, *br*, or *ret* belongs here.

- *binary operations* represent the arithmetic operations, take two input arguments of the same type, and produce one value of the same type as input ones. For example *div*, *mull*, *add*.

- *memory instructions* represents work with memory. The most used are *load* and *store*, but instructions like *alloca*, which allocates memory on

```

@g = global i32 4, align 4

2

3

define i32 @main() #0 {

%1 = alloca i32, align 4

4

\%2 = alloca i32, align 4

5

store i32 0, i32* %1, align 4

6

store i32 16, i32* %2, align 4

7

%3 = load i32, i32* @g, align 4

8

%4 = load i32, i32* %2, align 4

9

%5 = icmp slt i32 %3, %4

11

%6 = zext i1 %5 to i32

ret i32 %6

12

13 }

```

Listing 1.8: Example of LLVM IR

the stack, belong here too, as well as *cmpxchg* or *atomicrmw* representing atomic operations with memory.

• And others like unary, conversion, vector, aggregate, or unclassified operations such as *call*, '*trunc* ... *to*' instructions.

The LLVM type-system contains types for

- plain data types like integer numbers and floating point numbers,

- functions, which define types of arguments and type of the return value

- special complex types for representing structures and arrays.

```

1 int g = 4;

2 int main(){

3 int l = 16;

4 return g < l;

5 }

```

Listing 1.7: Example C code

The naming convention for variables takes the original variable's name from the source program. If the variable is compiler-defined, it is named by a number. Moreover, all variables have a prefix defining if it is a local variable prefixed with the '%' symbol or a global variable prefixed with the '@' symbol. If the LLVM IR instruction produces a result, it is stored in a variable.

#### Pass Scheduler

The Pass Scheduler is at the heart of the LLVM Optimizing section. Its task is to schedule, organize and manage passes over the LLVM IR that performs optimization. Moreover, the goal is to be as effective as possible while minimizing the compilation time. The Pass Scheduler is divided into components:

- Pass Manager which is responsible for organizing the passes and scheduling their execution. The LLVM supports multiple types of Pass Managers like FunctionPassManager or CGSCCPassManager (abbreviation for Call Graph strongly connected component).

- Pass Groups is a collection of passes that are meant to be executed together. This way, it is possible to define the order in which the passes inside the same group will be executed. Optionally, criteria can be specified to enable or disable the execution of the passes.

- Pass Ordering defines a process determining the order in which passes and groups will be performed. Various techniques are used to determine the optimal pass order. These techniques decide with the help of profiling data, user hints, and heuristics.

- Pass Dependencies helps to specify the relations and relationship between passes, mainly to determine the correct ordering.

- Pass Manager APIs specify the interface for managing pass groups and passes. Management concerns adding, removing, configuring, and getting information about dependencies and ordering.

#### Back-end