#### **Bachelor Thesis**

Czech Technical University in Prague

Faculty of Electrical Engineering Department of Radioelectronics

Implementation of the JESD204B Standard on an FPGA Enabling the Interfacing of High-speed A/D Converters with a Sampling Rate Higher than 250 MSPS

František Boháček

Supervisor: Ing. Radek Sedláček, Ph.D. Study program: Open Electronic Systems May 2023

# BACHELOR'S THESIS ASSIGNMENT

#### I. Personal and study details

Student's name: Bohá ek František

Personal ID number: 498966

Faculty / Institute: Faculty of Electrical Engineering

Department / Institute: Department of Radioelectronics

Study program: **Open Electronic Systems**

#### II. Bachelor's thesis details

Bachelor's thesis title in English:

Implementation of the JESD204B Standard on an FPGA Enabling the Interfacing of High-speed A/D Converters with a Sampling Rate Higher than 250 MSPS

Bachelor's thesis title in Czech:

Implementace standardu JESD204B na FPGA umož ující p ipojení vysokorychlostních A/D p evodník se vzorkovací frekvencí vyšší než 250 MSPS

Guidelines:

1. Study the principle of the receiving part of the JESD204B standard, intended for connecting A/D converters to FPGA circuits. 2. In VHDL, implement the receiving part of the JESD204B standard for connecting A/D converters with this interface. 3. Verify the draft of the standard using a suitable simulation tool (e.g. in the ModelSim environment). 4. Choose an affordable A/D converter with JESD204B interface, design a simple development board for it to connect to the Intel Cyclone 10 GX development kit. 5. Verify the correct operation of the implementation of the JESD204B standard on real data obtained from the chosen A/D converter.

Bibliography / sources:

[1] JESD204B Survival Guide: Practical JESD204B Technical Information, Tips, and Advice from the World's Data Converter Market Share Leader. In: Analog Devices [online]. [cit. 2023-01-30]. Available from: https://www.analog.com/media/en/technical-documentation/technical-articles/JESD204B-Survival-Guide.pdf

[2] Intel® Cyclone® 10 GX FPGA Development Kit. In: Terasic [online]. [cit. 2023-01-30]. Available from:

https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=253&No=1147

[3] PEDRONI, Volnei A. Digital electronics and design with VHDL. Amsterdam ; Boston, c2008. ISBN 978-0123742704.

Name and workplace of bachelor's thesis supervisor:

Ing. Radek Sedlá ek, Ph.D. Department of Measurement FEE

Name and workplace of second bachelor's thesis supervisor or consultant:

Date of bachelor's thesis assignment: **30.01.2023**

Deadline for bachelor thesis submission: 26.05.2023

Assignment valid until: 22.09.2024

Ing. Radek Sedlá ek, Ph.D. Supervisor's signature doc. Ing. Stanislav Vítek, Ph.D. Head of department's signature prof. Mgr. Petr Páta, Ph.D. Dean's signature

#### III. Assignment receipt

The student acknowledges that the bachelor's thesis is an individual work. The student must produce his thesis without the assistance of others, with the exception of provided consultations. Within the bachelor's thesis, the author must state the names of consultants and include a list of references.

Date of assignment receipt

# Acknowledgements

I would like to thank my supervisor, Ing. Radek Sedláček, Ph. D., for helping me to choose a topic I would be happy with and for pointing me in the right directions during the work on the thesis.

I would also like to thank LVR (laboratoře pro vývoj a realizaci) for mounting the BGA connector (10 rows, 40 pins each) on my board and Ing. Stanislav Drozd for mounting most of the other components on the board.

Last but not least, I would like to thank my family for supporting me during my studies.

# Declaration

I declare that the presented work was developed independently and that I have listed all sources of information used within it in accordance with the methodical instructions for observing the ethical principles in the preparation of university theses.

František Boháček, Prague, May 26, 2023

Prohlašuji, že jsem předloženou práci vypracoval samostatně a že jsem uvedl veškeré použité informační zdroje v souladu s Metodickým pokynem o dodržování etických principů při přípravě vysokoškolských závěrečných prací.

František Boháček, V Praze, 26. května 2023

# Abstract

The aim of this thesis is to implement a receiver of the JESD204B protocol that is used for high-speed ADCs (250 MSPS and more). The receiver has been implemented in the language VHDL. Testing components, called testbenches, were made and simulated using ghdl and Modelsim. These testbenches verified that the components behave as expected. A testing board with two ADCs has been designed. This board is compatible with the Intel Cyclone 10 GX FPGA development kit. It was attempted to test the board connecting it to the development kit using the custom design. The attempt was not successful and it was discussed where the problem could be and how to find out for sure.

**Keywords:** JESD204B, ADC, ADC receiver, VHDL, FPGA

Supervisor: Ing. Radek Sedláček, Ph.D.

# Abstrakt

Cílem této práce je vytvoření přijímače protokolu JESD204B, který se používá pro vysokorychlostní AČ převodníky (250 milionů vzorků za vteřinu nebo více). Přijímač byl implementován v jazyce VHDL. Byly vytvořeny komponenty pro testování, tzv. testbenche, které byly odsimulovány prostřednictvím programu ghdl a Modelsim. Tyto testy verifikovaly, že komponenty dělají to, co je očekáváno. Dále byla navržena testovací deska se dvěma AČ převodníky. Tato deska je kompatibilní s vývojovou sadou pro FPGA Intel Cyclone 10 GX. Proběhl pokus o otestování vlastní implementace přijímače připojením k této vývojové sadě. Tento pokus nebyl úspěšný a bylo diskutováno, kde by mohla být chyba, případně, jak ji v budoucnu nalézt.

Klíčová slova: JESD204B, AČP, AČP přijímač, VHDL, FPGA

**Překlad názvu:** Implementace standardu JESD204B na FPGA umožňující připojení vysokorychlostních A/D převodníků se vzorkovací frekvencí vyšší než 250 MSPS

# Contents

| Acronyms                           | 1        |

|------------------------------------|----------|

| 1 Introduction                     | 3        |

| 2 Comparison of interfacing method |          |

| for A/D converters                 | 5        |

| 3 Description of JESD204B protoco  |          |

| specification                      | <b>9</b> |

| 3.1 Clocks                         | 12<br>19 |

| 3.2 Physical layer                 | 12       |

| 3.3 Data link layer                | 13       |

| 3.3.1 8b/10b encoding              | 13       |

| 3.3.2 Synchronization              | 14       |

| 3.3.3 Code group synchronization   | 14       |

| (CGS)                              | 14       |

| 3.4 Scrambling                     | 18       |

| 3.5 Transport layer                | 18       |

| 3.6 Deterministic latency          | 19       |

| 3.6.1 Subclass 1                   | 21       |

| 3.6.2 Subclass 2                   | 21       |

| 3.7 Test modes                     | 23       |

| 4 Implementation of the receiver   | 25       |

| 4.1 VHDL introduction              | 26       |

| 4.2 Design                         | 26       |

| 4.2.1 Defined record types         | 26       |

| 4.2.2 Top level entities $\ldots$  | 27       |

| 4.2.3 Helpers                      | 30       |

| 4.2.4 Data link layer              | 33       |

| 4.2.5 Transport layer              | 43       |

| 4.3 Testbenches                    | 44       |

| 5 Design of the testing (mezzanine | )        |

| board                              | <br>47   |

| 5.1 Clock generation               | 50       |

| 5.2 Analog front-end               | 51       |

| 5.3 Supply, voltage levels         | 52       |

| 5.4 High-speed CML lanes           | 52       |

| 5.5 Length matching                | 54       |

| 5.6 Controlled impedance           | 55       |

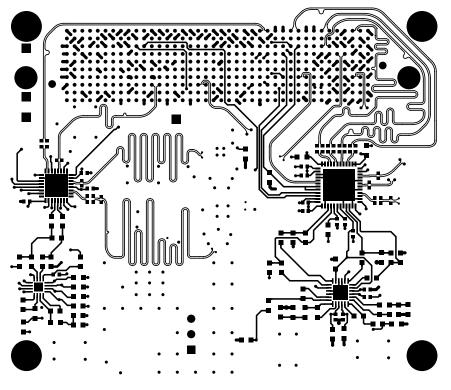

| 5.7 Final board                    | 55       |

| 6 Setup and testing on FPGA        |          |

| development kit                    | 57       |

| 6.1 FPGA setup using Quartus       | 57       |

| 6.2 Board configuration            | 59       |

| 6.3 Results                        | 59<br>61 |

|                                    |          |

| 7 Conclusion                       | 63       |

| 7.1 What's next                    | 64       |

| Bi | bliography                   | 65 |

|----|------------------------------|----|

| Α  | Contents of the attachment   | 69 |

| В  | Exported Gerber files of the |    |

| cu | stom printed circuit board   | 71 |

|    |                              |    |

# Figures

| 1 15 41 65                                              |

|---------------------------------------------------------|

| 2.1 Comparison of CMOS, LVDS and                        |

| CML drivers power consumption. [1] 6                    |

| CML drivers power consumption. [1] 0                    |

|                                                         |

| 3.1 JESD204B link and multipoint link                   |

| demonstrations 10                                       |

| 3.2 Illustration of JESD204B layers                     |

|                                                         |

| flow 11                                                 |

| 3.3 The 8b/10b coding scheme. [6] . 14                  |

| 3.4 Link synchronization sequence                       |

|                                                         |

| (data link layer function chart), valid                 |

| for subclass 0. $[3] \ldots 15$                         |

| 3.5 Initial lane alignment within                       |

| a single link with elastic buffer                       |

| -                                                       |

| demonstration. $[5]$ 16                                 |

| 3.6 Serial scrambling bit order. [3] . 18               |

| 3.7 Transport layer samples to lane                     |

|                                                         |

| octets decomposition. $[4]$ 19                          |

| 3.8 Deterministic latency definition. 20                |

| 3.9 Timing diagram illustration for                     |

| 0 0                                                     |

| deterministic latency equal to                          |

| multiple of multiframe period. [3] . 21                 |

| 3.10 Data release timing using                          |

| SYSREF in a subclass 1. $[5]$ 22                        |

| $515\text{KEF} \text{ III a subclass 1. } [5] \dots 22$ |

|                                                         |

| 4.1 Diagram of JESD204B multipoint                      |

| link receive VHDL entity                                |

| 4.2 Diagram of JESD204B link receive                    |

| -                                                       |

| VHDL entity 29                                          |

| 4.3 Diagram of synced combination                       |

| VHDL entity 30                                          |

| 4.4 Diagram of LMFC generation                          |

|                                                         |

| VHDL entity 31                                          |

| 4.5 Diagram of LMFC counter VHDL                        |

| entity                                                  |

|                                                         |

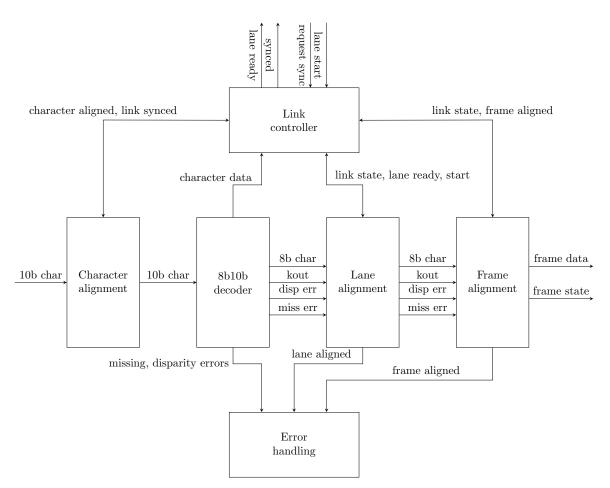

| 4.6 Block diagram of the data link                      |

| layer VHDL entity                                       |

| 4.7 Diagram of data link layer VHDL                     |

|                                                         |

| J.                                                      |

| 4.8 Diagram of ILAS parser VHDL                         |

| entity                                                  |

| 4.9 Link controller states                              |

|                                                         |

| 4.10 Diagram of link controller VHDL                    |

| entity                                                  |

| 4.11 Diagram of character alignment                     |

|                                                         |

| VHDL entity                                             |

| 4.12 Diagram of 8b10b decoder VHDL                      |

| entity                                                  |

| -                                                       |

|                                                         |

| 4.13 Diagram of lane alignment VHDI                                                                                                   | _        |

|---------------------------------------------------------------------------------------------------------------------------------------|----------|

| entity                                                                                                                                | 40       |

| 4.14 Diagram of frame alignment                                                                                                       |          |

| VHDL entity                                                                                                                           | 41       |

| 4.15 Frame alignment states                                                                                                           | 42       |

| 4.16 Diagram of error handler VHDL                                                                                                    |          |

| entity                                                                                                                                | 43       |

| 4.17 Diagram of transport layer VHDI                                                                                                  |          |

| entity                                                                                                                                | 44       |

| 4.18 Signal timing diagram of                                                                                                         |          |

| JESD204B link rx test bench                                                                                                           | 46       |

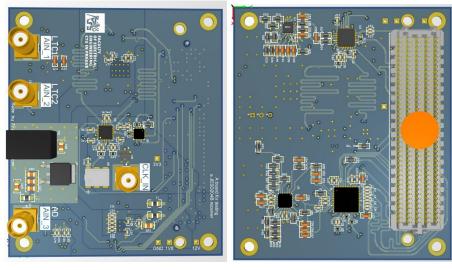

| 5.1 Top side of Intel Cyclone 10 GX                                                                                                   |          |

| development kit with highlighted                                                                                                      |          |

| FMC connector.                                                                                                                        | 48       |

| 5.2 Testing board high-level                                                                                                          | 40       |

| conception.                                                                                                                           | 49       |

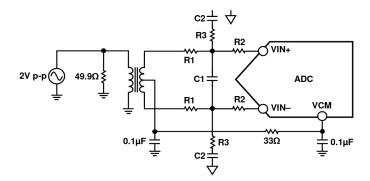

| 5.3 Differential transformer-coupled                                                                                                  | -10      |

| configuration. [12]                                                                                                                   | 51       |

| 5.4 Differential input configuration                                                                                                  | 01       |

| using the ADA4930. [12]                                                                                                               | 51       |

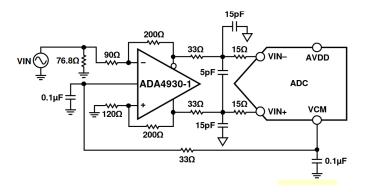

| 5.5 Some of the guidelines for                                                                                                        | 01       |

| high-speed signal routing. [20]                                                                                                       | 54       |

| 5.6 Configuration of differential pair                                                                                                | <u> </u> |

| controlled impedance from Saturn                                                                                                      |          |

| PCB Toolkit                                                                                                                           | 55       |

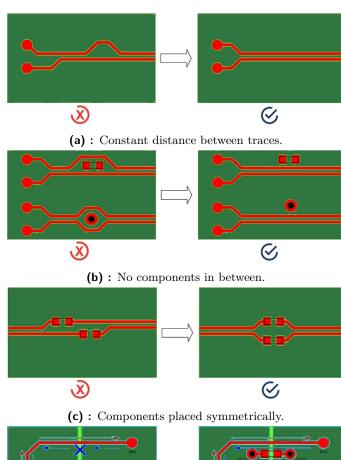

| 5.7 Comparison of the final printed                                                                                                   | 00       |

| board and Altium Designer 3D view.                                                                                                    | 56       |

| _                                                                                                                                     |          |

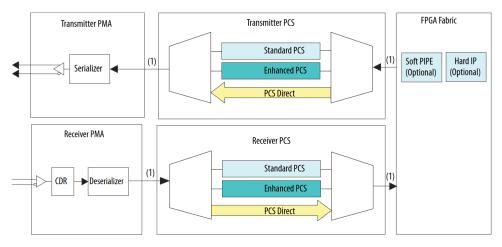

| 6.1 Transceiver channel in full duplex                                                                                                |          |

| mode. $[21]$                                                                                                                          | 57       |

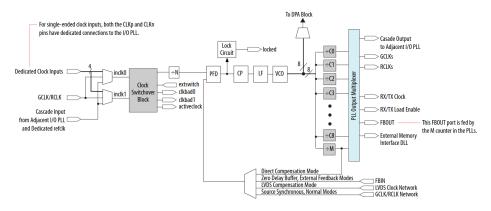

| 6.2 Typical I/O PLL architecture.                                                                                                     |          |

| $[22] \ldots $ | 58       |

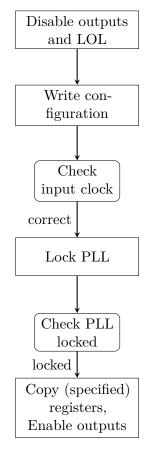

| 6.3 Simplified flowchart of Si5338                                                                                                    |          |

| configuration. Full flowchart available                                                                                               | Э        |

| in $[14]$ on page 23. $\ldots$                                                                                                        | 60       |

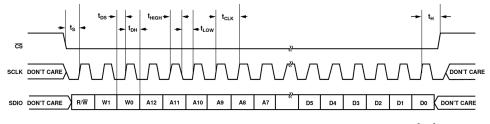

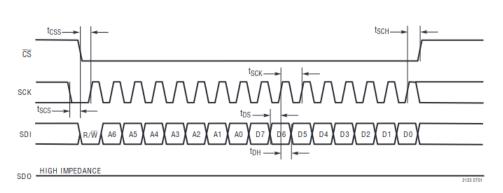

| 6.4 AD9683, SPI Timing, writing data                                                                                                  | ì        |

| to a register. $[12]$                                                                                                                 | 60       |

| 6.5 LTC2123, SPI Timing, writing                                                                                                      |          |

| a byte to a register. $[13]$                                                                                                          | 61       |

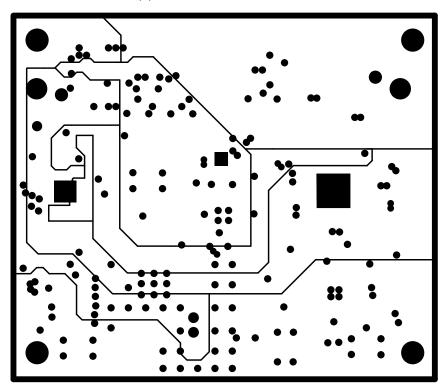

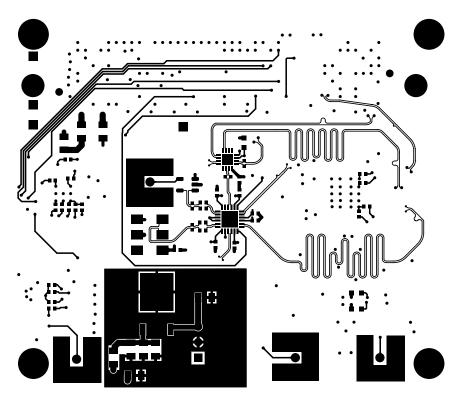

| B.1 Exported Gerber files of each of                                                                                                  |          |

the 4 layers of the custom PCB. ... 73

# **Tables**

| 3.1 Control characters from 8b/10b       |    |

|------------------------------------------|----|

| encoding with their aliases used in      |    |

| the text                                 | 13 |

| 3.2 Mapping of configuration fields to   |    |

| octets in ILAS. $[3]$                    | 16 |

| 3.3 Fields of the link configuration for | •  |

| individual lanes. $[3]$                  | 17 |

|                                          |    |

| 4.1 Fields of defined link_character     | ~  |

| record type                              | 27 |

| 4.2 Fields of defined frame_state        | ~  |

| record type                              | 27 |

| 4.3 Input and output ports of            | _  |

| jesd204b_multipoint_link_rx VHDI         |    |

| entity                                   | 28 |

| 4.4 Generic parameters of                |    |

| jesd204b_multipoint_link_rx VHDI         |    |

| entity.                                  | 28 |

| 4.5 Input and output ports of            |    |

| $jesd204b\_link\_rx$ VHDL entity         | 29 |

| 4.6 Generic parameters of                |    |

| $jesd204b\_link\_rx$ VHDL entity         | 30 |

| 4.7 Input and output ports of            |    |

| synced_combination VHDL entity.          | 31 |

| 4.8 Generic parameters of                |    |

| synced_combination VHDL entity.          | 31 |

| 4.9 Input and output ports of            |    |

| $lmfc\_generation VHDL entity$           | 31 |

| 4.10 Generic parameters of               |    |

| $lmfc\_generation VHDL entity$           | 32 |

| 4.11 Input and output ports of           |    |

| lmfc_counter VHDL entity                 | 32 |

| 4.12 Generic parameters of               |    |

| lmfc_counter VHDL entity                 | 32 |

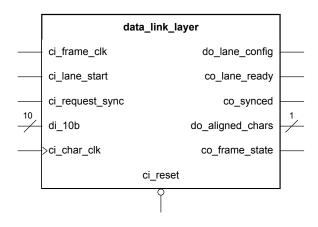

| 4.13 Input and output ports of           |    |

| data_link_layer VHDL entity              | 33 |

| 4.14 Generic parameters of               |    |

| data_link_layer VHDL entity              | 35 |

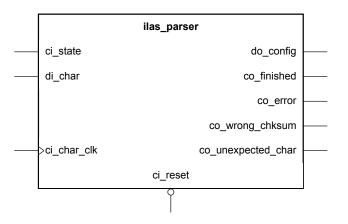

| 4.15 Input and output ports of           |    |

| ilas_parser VHDL entity                  | 35 |

| 4.16 Generic parameters of ilas_parse    | r  |

| VHDL entity                              | 36 |

| 4.17 Input and output ports of           |    |

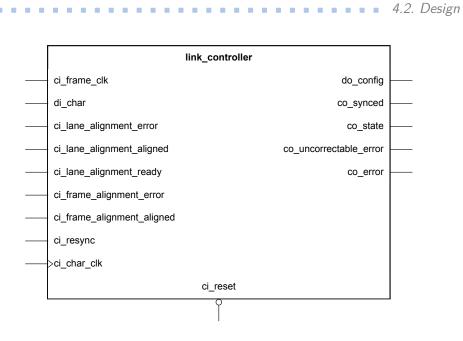

| link_controller VHDL entity              | 37 |

| 4.18 Generic parameters of               |    |

| link_controller VHDL entity              | 38 |

|                                          |    |

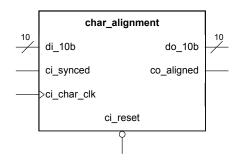

| 4.19 Input and output ports of        |    |

|---------------------------------------|----|

| char_alignment VHDL entity            | 38 |

| 4.20 Generic parameters of            |    |

| char_alignment VHDL entity            | 38 |

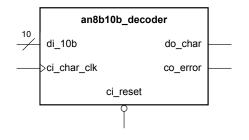

| 4.21 Input and output ports of        |    |

| an<br>8b10b_decoder VHDL entity       | 39 |

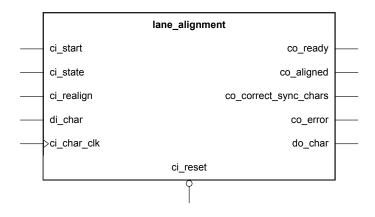

| 4.22 Input and output ports of        |    |

| lane_alignment VHDL entity            | 40 |

| 4.23 Generic parameters of            |    |

| lane_alignment VHDL entity            | 40 |

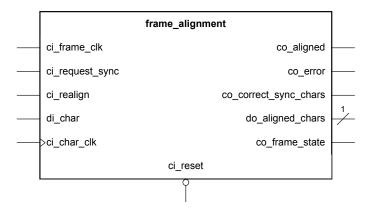

| 4.24 Input and output ports of        |    |

| frame_alignment VHDL entity           | 41 |

| 4.25 Generic parameters of            |    |

| $frame\_alignment VHDL entity$        | 42 |

| 4.26 Input and output ports of        |    |

| error_handler VHDL entity             | 43 |

| 4.27 Generic parameters of            |    |

| error_handler VHDL entity             | 44 |

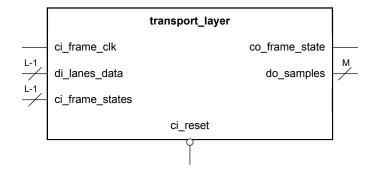

| 4.28 Input and output ports of        |    |

| transport_layer VHDL entity           | 44 |

| 5.1 Listing of the most important     |    |

| parameters of LTC2123 and AD9683      |    |

| [12][13]                              | 48 |

| 5.2 Individual signals of AD_CTRL     | 10 |

| and LTC_CTRL signal groups in         |    |

| Figure 5.2.                           | 50 |

| 5.3 Maximum supply currents needed    | 00 |

| from datasheets of the components.    |    |

| The total row contains the sum for    |    |

| the given voltage level and the row   |    |

| with the maximum shows the allowed    | l  |

| limit for the given voltage level,    |    |

| according to the development kit user | r  |

| guide. For 5 V, specifications of the |    |

| chosen step-down and LDO are          |    |

| shown.                                | 53 |

|                                       |    |

## Acronyms

- **ADC** Analog to digital converter. vi, 3, 5, 6, 9, 10, 15, 20, 22, 23, 47–53, 60, 61, 63, 69

- ASIC Application specific integrated circuit. 3, 5, 9

- BGA Ball grid array. v

- CDR Clock/Data Recovery. 7, 12

- CGS Code group synchronization. 14

- CML Current mode logic. viii, 5–7, 12, 47, 48, 52–56

- CMOS Complementary metal oxide semiconductor. viii, 5–7, 50

- CSV Comma-separated values. 59

- DAC Digital to analog converter. 9, 10, 17, 22, 23

- **DDR** Double data rate. 6

- **FIFO** First in, first out. 11, 15, 33, 39

- FMC FPGA mezzanine card. viii, 47–49, 52, 53, 58, 63

- **FPGA** Field programmable gate array. i, vi, 3–5, 9, 25, 26, 47, 49, 50, 52, 57–59, 62, 63

- **ILAS** Initial lane alignment sequence. 14, 15, 20, 22, 23, 39, 45, 61

- IP core Intellectual property core. 57, 58, 61

- I<sup>2</sup>C Inter-Integrated Circuit. 5, 6, 47, 49, 50, 59, 63

- LMFC Local multiframe clock. viii, 12, 17, 20–23, 28, 30–32

- LOL Loss of lock. 60

- LVDS Low voltage differential signaling. viii, 5–7, 47, 50, 55

**PCB** Printed circuit board. 71

PCS Physical coding sublayer. 57, 58

PMA Physical media attachment. 57, 58

**RBD** Rx buffer delay. 15, 20

${\bf RMS}\,$  Root mean square. 50

**SDR** Single data rate. 6

**SNR** Signal to noise ratio. 48, 51, 52

**SPI** Serial Peripheral Interface. 5, 6, 47, 48, 50, 52, 59, 63

- VCO Voltage controlled oscillator. 58

- VHDL VHSIC Hardware Description Language. vi, viii, 3, 4, 25, 26, 29–32, 34, 35, 37–41, 43, 44, 59, 62

# Chapter 1 Introduction

There is still an upward trend in the needs for performance in data processing systems, including an upward trend in ADC sampling frequencies. Some of the applications that require higher sampling frequencies are traffic control systems or wireless communications.

Attempts have been made to make new standards for transmitting data from Analog to digital converter (ADC) to FPGAs/ASICs while having fast sampling rates (more than 250 MSPS) and while keeping the number of connections low. Having a small number of connections allows for easier PCB designs and keeps the costs lower. JESD204 is a standard from JEDEC that is made for interfacing high-speed ADCs. There are multiple revisions of JESD204, it started with JESD204 in 2006, in 2008, revision A was published (JESD204A). In 2011, JESD204B came out. This thesis is mainly about this revision. The last revision<sup>1</sup> is JESD204C, from 2017. The original standard supported only one signal to transfer data through, of frequency up to 3.125 Gbps. In rev. A, support for sending data over multiple lanes has been added. Revision B added the possibility of speeds of up to 12.5 Gbps over one lane. This revision also introduced a mechanism for ensuring determined latency. Determined latency may be used for synchronizing data from multiple ADCs. [1] JESD204C introduced usage of 64b/66b encoding instead of 8b/10b encoding that had been used in the previous revisions, as well as some other changes. [2]

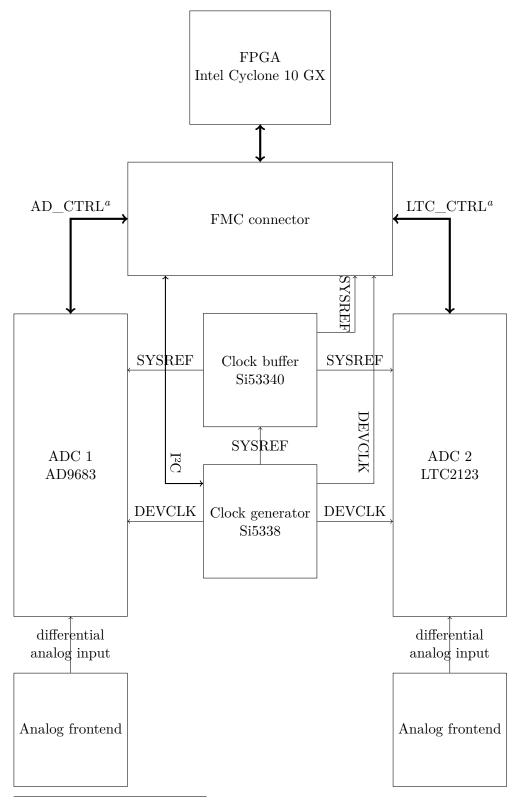

The main goal of this thesis is to implement JESD204B receiver in VHDL. This receiver will be tested in a simulation as well as on an FPGA. To test the receiver on FPGA, a testing board with an ADC will be developed. Attempt to synchronize data from two ADC will be made by using subclass 1 with the support of deterministic latency.

In chapter 2, various digital output standards as well as standards used for interfacing ADCs will be presented. It will be discussed where the JESD204B standard comes in.

In chapter 3, the JESD204B standard will be described. It will be shown what it is used for, its terminology, and how the data being transmitted looks. This will be presented mainly from the viewpoint of a receiver as a receiver

<sup>&</sup>lt;sup>1</sup>as of May 2023, revision D is expected to be published late Q3 2023, see https: //www.comcores.com/chip-to-chip-solutions/jesd204d/

1. Introduction

will be implemented as part of this thesis.

In chapter 4, an implementation of custom JESD204B receiver in VHDL will be described. This receiver should contain most of the features of the standard for subclass 0 and 1. Testbenches for testing the final design will be discussed here as well.

In chapter 5, the design of the PCB for testing of the receiver, will be presented. It will be discussed what components were chosen for the PCB and why, how the board was designed and some challenges that came with routing the high-speed signals.

And finally, in chapter 6, testing using Intel FPGA will be described and the results of the testing will be presented.

The appendices contain the main folder structure of the attachment, in Appendix A, and exported Gerber files, in Appendix B.

# Chapter 2

# Comparison of interfacing methods for A/D converters

There are several ways to interface data from ADCs to FPGAs/ASICs. What the right way for a specific application is, may depend on multiple parameters. Some of the most important parameters may be the sampling frequency or the number of I/O pins.

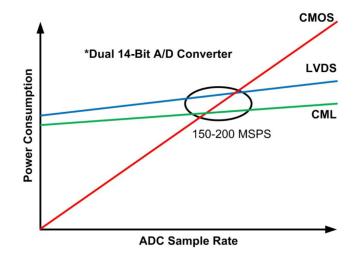

When it comes to the format of the data being transmitted, there are various standards for that. Some of these standards include: parallel CMOS, parallel LVDS, serial LVDS, I<sup>2</sup>C, SPI, and JESD204. [1] Some of these are named after a digital output standard, specifically Complementary metal oxide semiconductor (CMOS), Low voltage differential signaling (LVDS), and Current mode logic (CML). Digital output standards prescribe how the output is driven and thus also tell how to correctly receive the data from the signal. Power consumption of these digital output standards for dual channel ADC with 14 bits of resolution is illustrated in Figure 2.1. [1] CMOS is common among lower-speed (sub 200 MSPS) ADCs as it consumes less power. One of the motivations to use JESD204 (using CML) for high-speed ADCs is that it draws less current than both CMOS or LVDS for higher sampling rates.

CMOS digital output standard draws little current when the output is not changing. That is because there are transistors that draw little current when in static state. However, when the signal is changing, the transistors draw more current. For faster transition higher currents are needed. Another drawback of parallel CMOS is that N outputs are needed to transfer data from N-bit converter. That would lead to very complex board layouts as the number of converters grows. [1] If the data were transmitted serially, that would mean higher frequencies and consequently more current drawn.

LVDS is a differential standard and thus needs double the number of wires compared to CMOS for the same number of signals making the routing more difficult. There are a couple of advantages to LVDS compared to CMOS though. LVDS is differential and that offers the benefit mutual noise cancellation. Noise is usually common to both signal paths and is thus canceled out. LVDS uses lower voltage swings compared to CMOS and the driver draws a constant current. This offers benefits compared to CMOS. There could be a situation where all of the CMOS drivers are being

**Figure 2.1:** Comparison of CMOS, LVDS and CML drivers power consumption. [1]

simultaneously changed and the power supply voltage may get pulled down due to that.

Power consumption of LVDS is not that much higher than for CML, but all of the LVDS lanes must be aligned to a data clock. Because of that, there is an upper bound for LVDS, whereas CML may go to much higher speeds. [1] LVDS is limited to 1.9 Gbps for an ideal transmission medium, however for the real world that limit is usually about 1.0 Gbps. [1]

Serial LVDS usually uses data and frame clocks aligned with the data on the LVDS pairs. Serial LVDS may be employed instead of parallel LVDS where the number of pins is more important than interface speed. Parallel LVDS can be though of as being made from multiple serial LVDS lines. [1]

Both LVDS and CMOS may utilize Double data rate (DDR). In Single data rate (SDR), data are sent from the transmitter on one clock edge and sampled at the receiver on the next edge. For DDR the data are sent and sampled on both edges. [1]

Another possibility to interface ADCs, is to use Inter-Integrated Circuit (I<sup>2</sup>C), it uses only two wires - clock an data. A large number of devices may be present on one I<sup>2</sup>C bus without any more additional pins. Each of the devices has an address that is sent at the beginning of the communication. It is relatively slow, allowing for only up to 1 MHz. If size is an important parameter, I<sup>2</sup>C may come in handy. It may also be used as a control interface. [1].

Serial Peripheral Interface (SPI) is an interface that uses 3 or 4 wires: clock, data in and data out (or bidirectional data) and a chip select. Multiple devices may be present on one bus, however, each slave device needs to have a separate "chip select" signal for selecting which device the master is talking to. SPI allows for up to 100 MHz speeds. It's commonly used as a control interface as well as a data interface. [1]

Converters with higher resolutions and higher speeds may utilize CML.

CML allows up to 12.5 Gbps speeds. That means it's possible to use fewer signals compared to both LVDS and CMOS that do not support such high speeds. This makes the board design simpler and less expensive. [1]

CML requires very few connections as the speeds may go higher than for the other standards, and the data are transferred serially. That also means a need for the introduction of a serialized data interface. One of these interfaces is JESD204. To correctly recover the clock from the data stream it's also needed to make as many changes in the data as possible. This may be done using encoding schemes such as 8b/10b (see subsection 3.3.1) or 64b/66b, leading to larger throughput for same frequency. The downside of using these encoding schemes is that they reduce the effective bandwidth. For 8b/10b encoding, which is used by JESD204B, the bandwidth is reduced to 80 % of the theoretical value. [1]

There are also greater requirements for LVDS compared to CML as it must be ensured that all of the lanes and data clock skews are not too large. JESD204B has means of aligning multiple lanes and does not require routing data clock synchronized to the data on CML lanes. The bit clocks are recovered on the receiver using Clock/Data Recovery (CDR). [1]

JESD204B includes more advanced features such as multidevice synchronization, deterministic latency, and harmonic clocking. Applications requiring these won't be able to use LVDS or CMOS standards. [1]

Both LVDS and CML need a controlled differential impedance of  $100 \Omega$  and a termination resistor of  $100 \Omega$  to remove any reflections. [1]

It's important to note that CMOS and LVDS are still being used. CML offers advantages for higher frequencies, but for lower sampling rates, CMOS and LVDS may still be employed.

# Chapter 3

# Description of JESD204B protocol specification

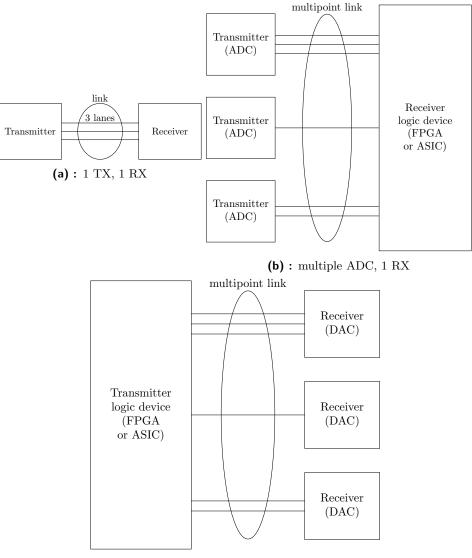

JESD204B is a protocol used for either transferring data from high-speed ADCs to FPGA/ASIC (logic device) or from FPGA/ASIC (logic device) to DACs. Its aim is to use as few connections as possible and allow for high sampling frequencies. Synchronizing multiple ADCs is possible using determined latency.

There is always only one logic device in the design. It may either be the transmitter, then it sends data to DACs. In the other case where the logic device is the receiver, ADCs are sending data to it. This is illustrated on Figure 3.1. The terminology for links, lanes, and multipoint links is demonstrated in these figures as well. ADCs or DACs may have different numbers of lanes. The channels of ADC devices are not displayed for simplicity, but it should be noted that each transmitter may contain multiple channels.

In case there are multiple ADCs, the structure is called a multipoint link. Between each ADC and FPGA, there is a link. One link may contain multiple lanes consisting of differential pairs. On these lanes, bits are transmitted using 8b/10b encoded characters.

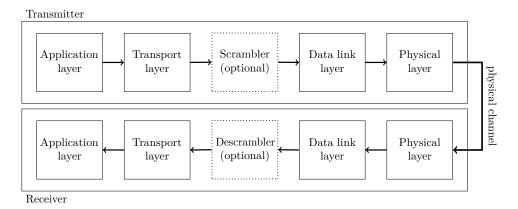

Similar to protocols such as TCP/IP, JESD204B consists of multiple layers. The layer names and the data flow is illustrated on Figure 3.2. JESD204B has 3 subclasses that define how the data link layer behaves.

- Subclass 0 is for backward compatibility with an older version of JESD204, JESD204A. It does not support deterministic latency. [3]

- Subclass 1 supports deterministic latency by adding one more signal called SYSREF. [3]

- Subclass 2 may encode signal used for ensuring deterministic latency using SYNC~ signal that is already present in subclass 0 devices. Subclass 2 uses the same number of signals as subclass 0. [3]

Data are sent serially over one or more lanes. The number of lanes is denoted as L. Data characters are 8b/10b encoded to ensure DC balance. 8b/10b encoding ensures the same number of zeros and ones in longer periods. Data may be additionally scrambled as well to reduce EMI noise caused by

(c) : 1 TX, multiple DAC

Figure 3.1: JESD204B link and multipoint link demonstrations.

repeating patterns. Scrambling may be disabled for applications where it does not introduce any benefit. [1]

A short introduction to what each layer on the receiver does, follows. A more thorough explanation is below.

**Physical layer** consists of transceivers that deserialize serial data from the transmitter. Bits are coming from differential lanes of up to 12.5 Gbps, as noted before. There is a separate transceiver for every physical lane. The output is one or more 10-bit characters going to the data link layer. [3]

JESD204B receiver has to first synchronize with data from transmitters, that is what the **Data link layer** is used for. The characters are enclosed inside frames and frames are enclosed inside multiframes. These are then used for ensuring and monitoring alignment. The data link layer also processes

Figure 3.2: Illustration of JESD204B layers flow.

lane configuration (used to check whether the configuration of the receiver and transmitter is the same) that is transmitted during synchronization. For every lane, there is one data link, the data links need a connection between themselves to ensure alignment between the lanes. In case of multiple transmitters, another connection between links is needed for subclass 1 and 2. [4]

Lane alignment is done by waiting for a character at a given position on all the links. Until that character is received on every lane, oncoming data are stored in a FIFO starting from the same character on every lane. After every lane receives the given character, the data link is ready to start sending data. This is done to account for skews between the lanes. Subclass 0 starts sending data right after all lanes are aligned, subclass 1 and 2 work slightly differently, waiting for the right moment until releasing the data. The output of the data link layer is a frame of characters. The data goes to the transport layer. [5]

Between the data link and transport layer, there may be a (de)scrambler if the characters are scrambled. This descrambler takes and outputs a whole frame. Data during synchronization are never scrambled. [4]

**Transport layer** is used for converting received frames into samples from the converters. Samples consist of the sampled voltage itself, and may consist of one or more control bits. Control bits are application specific. Some common usages may be to use them for indicating overflow or underflow. The exact layout of the frame depends on the configuration of the link. [4]

**Application layer** is application specific. It should have control over lower layers, such as allowing to realign to the lost frame boundary or to request a synchronization if something goes wrong. The application layer on the transmitter should support generating test sequences. The receiver should be able to detect test sequences. [4]

## 3.1 Clocks

It's recommended that there is one source for the device clock going to each device on the multipoint link. Each device will need to generate its clocks from the main device clock. These generated clocks will be called local clocks as they are local for the given device and may have different phases in each of the devices. There are means of synchronization of some local clocks as described below. [3]

Data are transmitted over differential lanes on data/bit rate. As characters are sent as 10 bits, the character rate is the bit rate divided by 10. [3]

Each device needs to generate a frame clock, that is a clock with the frequency of a frame. In terms of character rate, it's character rate divided by F, the number of characters in a frame. [3]

Each device will need an LMFC as well, its frequency is frame clock divided by K, the number of frames in a multiframe. [3]

Devices that use subclass 1 and 2 have to have multiframe clocks aligned to each other. For subclass 1, that happens using a separate signal called SYSREF. It's recommended that SYSREF is generated from the same device that generates the device clock. For subclass 2, SYSREF is not needed and the data needed for synchronization are encoded inside of SYNC~ signal. [3]

SYSREF may be either periodic or gapped periodic. Its frequency should be an integer multiple of multiframe clock period. It's preferred to generate SYSREF using one device, but it's not required. Generating separate SYSREF for each device is possible. But it must be ensured that there is a deterministic relationship between each of these to allow for deterministic latency. [3]

## 3.2 Physical layer

The physical layer uses CML to transmit the data from the transmitter to the receiver across a transmission line. The physical layer on the transmitter consists of a parallel to serial converter and differential CML driver. [3]

On the receiver it is made of:

- Differential CML Receiver

- Optional Equalizer

- Clock/Data Recovery (CDR)

- Character alignment and Serial to Parallel Converter 1:10

The CDR block finds the bit boundary and aligns a bit clock to the bit boundary (recovers the clock). This bit clock may be used to generate a character clock that is utilized inside the data link layer. The character alignment should align to /K/ character boundary only upon link synchronization. The equalizer is not required but may be implemented to support sending the data across larger distances. [3]

# **3.3** Data link layer

In the following text, symbol aliases will be used for 8b/10b control characters. Below is a table explaining what characters these aliases map to.

**Table 3.1 :** Control characters from 8b/10b encoding with their aliases used in the text.

| Character bits | Symbol  | Alias          |

|----------------|---------|----------------|

| 101 11100      | /K28.5/ | /K/            |

| 011 11100      | /K28.3/ | /A/            |

| 111 11100      | /K28.7/ | $/\mathrm{F}/$ |

| 000 11100      | /K28.0/ | /R/            |

| $100 \ 11100$  | /K28.4/ | $/\mathrm{Q}/$ |

The data link may receive one or more 10-bit characters at a time. Its responsibility is to decode 8b/10b characters, align all lanes, align with the frame, and output the frame. [3]

#### **3.3.1** 8b/10b encoding

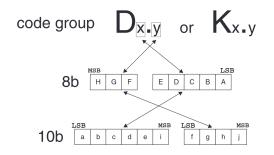

As the name suggests, 8b/10b encoding encodes 8-bit data into 10-bit symbols. It's used mainly for high-speed systems that need to have the same number of 0's and 1's in the channels. That is to prevent a charge from being built up in the media and allows for easier clock data recovery as well. It's used in protocols such as PCI Express or HDMI as well. [6]

Every character is encoded either with five 1's and five 0's, or four 1's and six 0's or six 1's and four 0's. The encoder must keep track of the last symbol difference in 1's and 0's to make sure that in a long time, the data will be balanced. The difference between the number of 1's and 0's is called running disparity. It may be either +1 or -1. Every character that has an unbalanced number of 1's and 0's, has a counterpart representing the same character, but with swapped number of 1's and 0's. The transmitter will swap between the counterparts according to the current running disparity. It must keep the disparity either +1 or -1 at all times. The receiver may check whether the current character has the expected running disparity. That may be useful for detecting errors. [6]

The 8-bit data words are split into two smaller words, 3-bit and 5-bit words. 3-bit words are then encoded into 4 bits, and 5-bit words are encoded into 6 bits. This effectively means that 8b/10b encoding is decomposed into two simpler encodings, 5b/6b encoding, and 3b/4b encoding. Coded words are then joined. 5b/6b code at the top half and 3b/4b at the bottom half. [6] The decomposition of 8-bit characters and composition of 10-bit characters can be seen in Figure 3.3. The symbols are usually denoted as /D.x.y/, where x stands for a 5-bit number (0 - 31) whereas y stands for a 3-bit number (0 -7).

Figure 3.3: The 8b/10b coding scheme. [6]

Apart from standard data symbols, 8b/10b encoding contains control symbols. These may be used to notify the receiver about a special event. JESD204B uses control characters when synchronizing and later for alignment monitoring. Control symbols are denoted using K instead of D, ie. /K.28.y/. [6]

There are three special control symbols called comma symbols. These symbols contain a unique sequence that may allow recognizing the boundary of a character. Alignment with character boundary may take place when synchronizing the link. [6]

For JESD204B, this is done in the code group synchronization stage. The character boundary should not be changed after synchronization is established. That's to ensure that the link is not desynchronized because the data may contain an error that would be confused for a comma symbol. [3]

#### **3.3.2** Synchronization

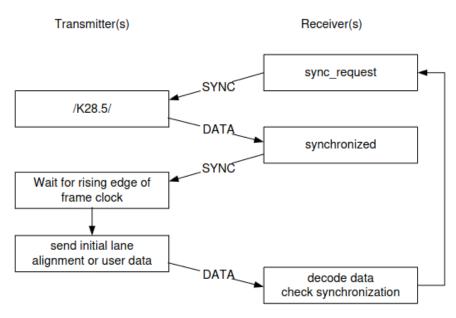

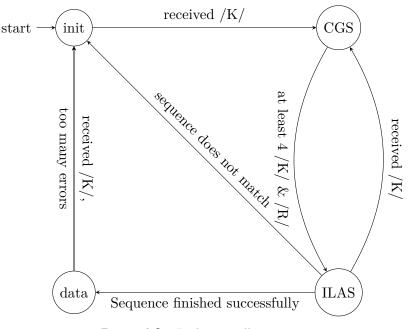

Synchronization of the link has two stages, code group synchronization and initial lane alignment synchronization. CGS and ILAS are never scrambled. [3] The whole process is illustrated on Figure 3.4.

#### 3.3.3 Code group synchronization (CGS)

After losing synchronization, SYNC~ going to the transmitter should be set to notify the transmitter about lost synchronization. The synchronization may be requested from the transmitter as well, by sending /K/ symbols. The SYNC~ may be used for reporting errors after synchronization, too. That may be done by deasserting it for shorter periods of time. The transmitter will acknowledge code group synchronization on all lanes by sending /K/ characters. [3]

The receiver may get aligned with the start of a character when in CGS. That's done by special properties of /K/ comma character. After 4 consequent /K/ characters are successfully received, the receiver should deassign SYNC $\sim$ . Full synchronization is assumed after receiving 4 more correct 8b/10b symbols (the character is in the encoding table and with correct disparity). Until then, any symbol error will result in the need for resynchronization. [3]

3.3. Data link layer

**Figure 3.4:** Link synchronization sequence (data link layer function chart), valid for subclass 0. [3]

#### Initial lane synchronization (ILS)

Initial lane synchronization will begin after the first non-/K/ character is received. That character will be at a start of a multiframe. [3]

ILAS consists of 4 multiframes. Each of the multiframes starts with /R/ and ends with /A/. The second multiframe contains link configuration data. See Table 3.3 for configuration options. The mapping of link configuration may be seen in Table 3.2. The configuration should be the same for the whole link, except for lane identification. It should match the configuration of the receiver. The configuration will follow right after /Q/ character which should be at the second position of the second multiframe. [3] From the mapping, it's obvious that there are 14 bytes needed for the configuration. Adding 1 for /Q/, 1 for /R/ (beginning of multiframe), and /A/ (end of multiframe), that makes 17 bytes the minimum number of bytes needed in one multiframe. That effectively means that  $F \cdot K$  must be  $\geq 17$ .

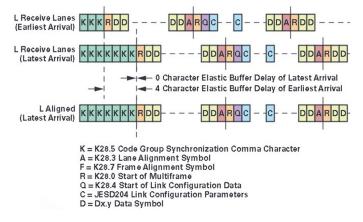

During ILAS the lanes in one link should get aligned to each other. That allows for the correct function of the transport layer. Right after the ILAS starts with /R/ character, data should get saved to an elastic FIFO buffer. The buffer may be released only after all lanes received the first /R/. It's possible that due to differences in the delay of the links, every lane will receive /R/ at a different time. [3] Lane alignment with FIFO buffers is demonstrated on Figure 3.5.

In subclass 0, the data will start going out of the buffers right after all lanes receive /R/. In subclass 1 or 2, data should be released 1 to K frames after multiframe clock pulse, this delay is called Rx buffer delay (RBD) (see section 3.6). [3]

Right after ILAS, the data from ADCs will follow. [3]

| Configuration | Bits                     |          |        |          |         |   |   |     |

|---------------|--------------------------|----------|--------|----------|---------|---|---|-----|

| octet no.     | MSB                      | 6        | 5      | 4        | 3       | 2 | 1 | LSB |

| 0             | DID<7:02                 | DID<7:0> |        |          |         |   |   |     |

| 1             | ADJCNT                   | <3:0>    |        |          | BID<3:0 | > |   |     |

| 2             | х                        | ADJDIR   | PHADJ  | LID<4:02 |         |   |   |     |

|               | Λ                        | <0>      | <0>    | LID<4:0> |         |   |   |     |

| 3             | SCR < 0 >                | Х        | Х      | L<4:0>   |         |   |   |     |

| 4             | F < 7:0>                 | F<7:0>   |        |          |         |   |   |     |

| 5             | Х                        | Х        | Х      | K<4:0>   |         |   |   |     |

| 6             | M < 7:0>                 | M<7:0>   |        |          |         |   |   |     |

| 7             | CS<1:0> X                |          | N<4:0> | 4:0>     |         |   |   |     |

| 8             | SUBCLASSV<2:0>           |          |        | N'<4:0>  |         |   |   |     |

| 9             | JESDV<2:0>               |          |        | S<4:0>   |         |   |   |     |

| 10            | HD < 0 >                 | Х        | Х      | CF<4:0>  | ,       |   |   |     |

| 11            | RES1<7:0> - Set to all X |          |        |          |         |   |   |     |

| 12            | RES2<7:0> - Set to all X |          |        |          |         |   |   |     |

| 13            | FCHK<7:0>                |          |        |          |         |   |   |     |

**Table 3.2**: Mapping of configuration fields to octets in ILAS. [3]

**Figure 3.5:** Initial lane alignment within a single link with elastic buffer demonstration. [5]

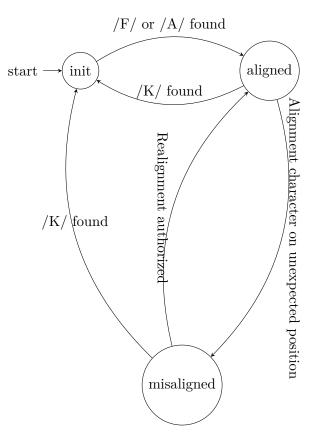

#### Alignment monitoring, realignment

During data transmission, there will be alignment characters inserted in special scenarios to verify the link is still aligned. If the alignment is lost, it may sometimes be restored. In cases where that's not possible, resynchronization must be requested. [3]

For non-scrambled data, if two consequent frames end with the same character, /F/ will be sent instead. The receiver has to replace that /F/ with the character from the last frame. /F/ may be only on the last position in a frame. Thus its position may be compared with the previous frame alignment character. [3]

In case two consequent multiframes end with the same character, it's similar to the case above. /A/ will be sent instead. That may be used to check lane alignment. [3]

For scrambled data, if /D28.7/ is at an end of a frame, it will get replaced by /F/ = /K28.7/. At the end of a multiframe the same is true for /D28.4/.

It will get replaced by /A/ = /K28.4/. The receiver should replace /F/ with /D28.7/ and /A/ with /D28.4/. [3]

If alignment characters (/A/, /F/) are at the wrong location, the receiver may realign. At least two alignment characters should be at the same position before realignment. If one alignment character right after realignment is detected at the previous location, the receiver should realign back to the previous position. Since data are stored in a buffer for ensuring lane alignment, the position in the buffer may be changed to restore alignment over the lanes. [3]

| Parameter | Description                                              |

|-----------|----------------------------------------------------------|

| ADJCNT    | Number of adjustment resolution steps to adjust DAC      |

|           | LMFC. Applies to subclass 2 operation only.              |

| ADJDIR    | Direction to adjust DAC LMFC, 0 - Advance, 1 - Delay.    |

|           | Applies to subclass 2 operation only.                    |

| BID       | Bank ID - Extension to DID.                              |

| CF        | Number of control words per frame clock period per link. |

| CS        | Number of control bits per sample.                       |

| DID       | Device $(= link)$ identification number.                 |

| F         | Number of octets per frame.                              |

| HD        | High Density format.                                     |

| JESDV     | JESD204 version, 000 - JESD204A, 001 - JESD204B.         |

| К         | Number of frames per multiframe.                         |

| L         | Number of lanes per converter device (link).             |

| LID       | Lane identification number (within link).                |

| М         | Number of converters per device.                         |

| Ν         | Converter resolution.                                    |

| N'        | Total number of bits per sample.                         |

| PHADJ     | phase adjustment request to DAC, subclass 2 only.        |

| S         | Number of samples per converter per frame cycle.         |

| SCR       | Scrambling enabled.                                      |

| SUBCLASSV | Device subclass version.                                 |

| RES1      | Reserved field 1.                                        |

| RES2      | Reserved field 2.                                        |

| CHKSUM    | Checksum $\Sigma$ (all above fields) mod 256.            |

Table 3.3 : Fields of the link configuration for individual lanes. [3]

# 3.4 Scrambling

Scrambling may prevent spectral peaks caused by repeating the same data. Every device should support scrambling. Scrambling must be enabled for the whole device, it may not be used only for some of the lanes. [3]

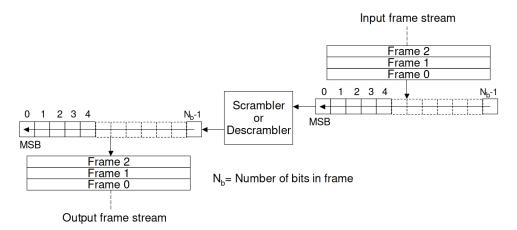

There is one scrambler per lane. The scrambler word size is equal to F. The bit order to a serial scrambler is illustrated in Figure 3.6. The polynomial of the self-synchronous scrambler is  $1 + x^{14} + x^{15}$ . The scrambler or descrambler should be situated between the data link layer and the transport layer. It's possible to implement the scrambler as either serial or parallel. [3]

Some of the scrambled data will be lost when the descrambler initially doesn't have state registers synchronized. This loss may be prevented by allowing unscrambled octets to flow through the state register as well. [3]

Initial lane alignment sequence as well as code group synchronization sequence are never scrambled. [3]

Figure 3.6: Serial scrambling bit order. [3]

## 3.5 Transport layer

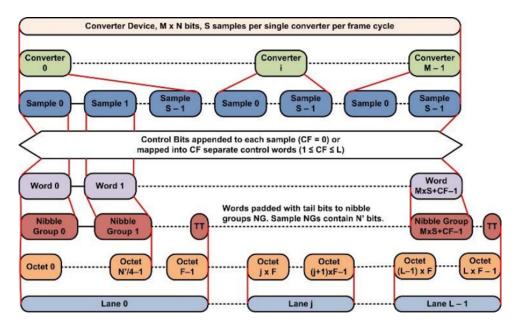

The transport layer operates on frame clock frequency. Its responsibility is to map octets from all of the lanes to raw samples. Each sample may have associated control bits. [3]

Every frame contains samples from all of the converters. One frame may contain more than one sample for every converter, that is called oversampling. [3]

For one lane, samples are mapped to a linear axis starting with the first converter. If oversampling is enabled, all of the samples from the first converter are added as first. Then samples from the rest of the converters follow. Sample words are padded to multiples of 4 bits. 4 bits create a nibble group. There is a possibility to enable a high-density mode that will work without inserting tail bits. Samples may be directly followed by control bits. Another possibility is to send control bits at the end of a frame as control words. The control bits in a control word are mapped the same way as samples. [3]

For multiple lanes, the process is the same. At the end, the data is split into multiple lanes. Every lane will contain F characters per frame. There will be a total of  $L \cdot F$  characters in one frame. See Figure 3.7 for visualization of the mapping. [3]

To prevent the tail bits from reducing the generation of frame synchronization symbols, they should meet one of the requirements:

- The sequence is the same for all frames. [3]

- The sequence is generated pseudo-randomly based on a polynomial that has a degree of at least 9. [3]

Figure 3.7: Transport layer samples to lane octets decomposition. [4]

## 3.6 Deterministic latency

There are means defined in the JESD204B standard to allow for synchronization of some of the local clocks between the devices and also to allow for ensuring a deterministic latency between sampling and receiving the data. Ultimately leading to synchronization between multiple transmitter device samples. [3]

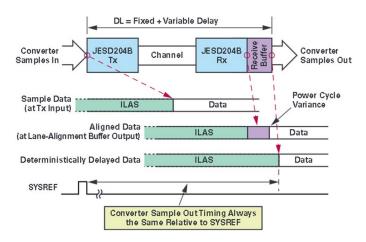

According to JEDEC standard description, the definition of the deterministic latency is: "The deterministic latency across the link is defined from the parallel frame-based data input on the TX device to the parallel frame-based data output on the RX device, all measured within the frame clock domain." [3] This definition is illustrated on Figure 3.8

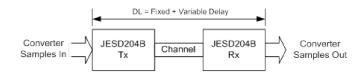

Figure 3.8: Deterministic latency definition.

The deterministic latency is a sum of fixed and variable delays. Fixed delays are a result of circuit design and are constant from one power cycle to another. Variable delays may be caused by various factors and are dependent on the power cycle. [5]

To achieve deterministic latency, there are two requirements:

- The transmitters should begin sending ILAS at a well-defined moment in time. [3]

- The receiver should buffer the incoming data to allow data from all lanes to be received. As each lane may have different skew, the data won't arrive simultaneously. The buffers should be released at a well-defined time. [3]

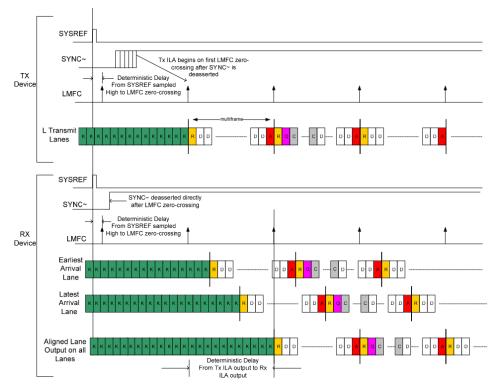

A well-defined moment in time at which transmitters should begin initial lane alignment, is the first LMFC tick after SYNC~ is deassigned. A well-defined moment in time at which the receiver should release the buffers is a whole number of frame cycles after an LMFC tick. The number of frame cycles should be programmable and is called Rx buffer delay (RBD). [3] The timing diagram for achieving deterministic latency is illustrated on Figure 3.9.

For proper performance of the deterministic latency, some requirements must be followed:

- The period of a multiframe must be larger than the maximum delay between transmit and receive devices. [3]

- The value of RBD multiplied by the frame period must be larger than the maximum delay. [3]

- The RBD must fit into a multiframe. [3]

Subclass 0 does not support deterministic latency. The variable delays cannot be accounted for as there are no means for that present. [3] It still may be possible to synchronize multiple ADCs in the application layer though. JESD204B allows for control bits to be added to the sample bits. If there is a SYSREF-like signal distributed to all of the devices and the ADCs are sending a control bit along the samples that indicates the SYSREF edge has been encountered, it's possible to align multiple ADCs by aligning samples with the indication. [5]

**Figure 3.9:** Timing diagram illustration for deterministic latency equal to multiple of multiframe period. [3]

#### 3.6.1 Subclass 1

Subclass 1 allows for deterministic latency by utilizing the SYSREF signal. LMFC and frame clock realignment are necessary only when the link is being synchronized. [3]

All devices should be able to issue a request for SYSREF generation. That may be usable if the SYSREF is a gapped periodic or one-shot signal. The request should be issued upon link synchronization. The devices should adjust LMFC and frame clock boundary on some of the SYSREF rising edges. The exact alignment moment is left to the implementer. For example, the device may be instructed to use the next detected SYSREF pulse to force the alignments through a configuration interface. This idea is illustrated on Figure 3.10 [3]

The delay between SYSREF being sampled and LMFC rising edge should be specified for each device. [3]

#### 3.6.2 Subclass 2

In subclass 1 the deterministic latency is achieved by aligning LMFC between the devices. It is achieved the same way in subclass 2, but the alignment part is different. Whereas in subclass 1 another external signal, SYSREF, is needed, in subclass 2 the data needed for LMFC alignment are inside of the

Figure 3.10: Data release timing using SYSREF in a subclass 1. [5]

#### SYNC~ signal. [5]

The SYNC~ signal generated by the receiver must be generated based on the receiver's LMFC. That will mean it will carry LMFC information to the transmitter. This information may then be used for aligning LMFC on all of the devices. [5]

This means that the master reference is generated from a different source, in subclass 1 the master is the clock source, whereas in subclass 2, it's the master logic device. The implementation is different for both ADCs and DACs. [5]

#### ADC subclass 2 deterministic latency

The SYNC~ is de-asserted by the logic device (receiver in this case) and sampled by the ADC. When the ADC detects the deassignment of SYNC~, it resets its LMFC. The transmitter will begin sending /K/ characters until the clock is settled. After the clocks have settled, the ADC will begin sending ILAS. It's possible to utilize a periodic SYNC~ to monitor the phase alignment of the ADC's LMFC. [5]

#### DAC subclass 2 deterministic latency

For DACs, the logic device is the transmitter. It's not possible to align the transmitter to all of the DACs, as the clock phase may be different for each of them. This presents a challenge as there is not a separate indication signal going from the transmitter to the DACs. The DACs will deassign the SYNC~ on their LMFC edge. The logic device may detect the phase difference between its LMFC and the DAC LMFC. It may issue a command to the DAC to adjust the phase during ILAS. The relevant parts of the link configuration are PHADJ (phase adjust), ADJCNT (adjustment count), and ADJDIR (adjustment direction). [5]

• PHADJ indicates whether an adjustment is needed.

- ADJCNT indicates the number of adjustment steps needed.

- ADJDIR indicates what direction to adjust the LMFC to.

It's possible that the adjustment will have to be repeated multiple times. After each adjustment, the DAC issues an error report by deasserting the SYNC $\sim$ . (again aligned with LMFC) If misalignment is detected, the ILAS will be issued with PHADJ request again and the process will be repeated. In other case, ILAS will be issued without PHADJ. Data may be sent after the ILAS. [5]

The deterministic latency is achieved the same way as in subclass 1 after the LMFCs are aligned.

## 3.7 Test modes

To test the link, the JESD204B specification includes a predetermined sequences of characters that every transmitter should be able to send. Some ADCs allow for specifying a user test pattern. The sequences that every transmitter should be able to send are:

- Continuous sequence of /D21.5/ characters (1010101010). [3]

- Continuous sequence of /K/ characters. [3]

- Repeated transmission of lane alignment sequence. The transmitter should be able to initiate code group synchronization upon receiving a synchronization request. [3]

- Continuous sequence of a modified random pattern or scrambled jitter pattern. [3]

All receivers should be able to verify some of these sequences. Namely a continuous /K/ sequence and a repeated lane alignment sequence. [3]

# Chapter 4

# Implementation of the receiver

The implementation was done in VHDL. The code has been tested using testbenches for each component itself and for the whole receiver connecting all of the components. It's possible to start these testbenches using ghdl and view the result inside gtkwave using make, Makefile is located in the root folder. Another possibility is to use the Quartus project that is also in the root folder and all testbenches are present there, it's possible to run these in Modelsim.

A short introduction to each of the programs or tools mentioned, follows.

GHDL is an open-source compiler that may simulate VHDL code. It directly translates/compiles VHDL code to machine code, so an executable program is created. [7]

Gtkwave is an open-source wave viewer for Unix and Win32. GHDL program may produce a standard Verilog VCD file that may be explored using Gtkwave. [8]

Modelsim is a simulation tool from Siemens, it can simulate some of the hardware description languages. Among other languages, it supports VHDL or Verilog.

Quartus Prime is a software bundle developed by Intel. It supports everything for designing on Intel FPGAs, such as synthesizing. It is able to simulate VHDL code as well. [9]

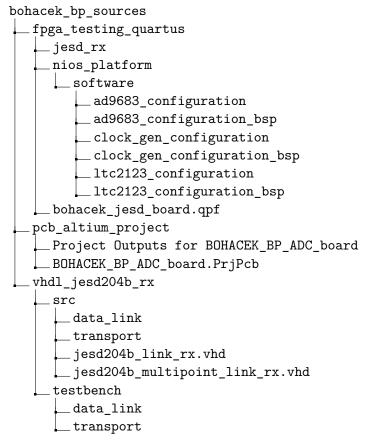

The root folder of the custom implementation contains src/ folder containing all the sources. The sources are grouped into folders by layer. Testbench folder testbench/ has the same structure. Testbenches are named the same way as sources with added \_tb at the end. When there is need to test multiple configurations of one entity, the file names may be different. The files are located on attachment for this thesis and the file tree structure of the attachment is located in Appendix A.

Care was taken to make all of the entities modular using generics. Every entity may be used with different configurations to accommodate for any possible usage of the JESD204B protocol. The design is split into smaller entities to make it possible to use only smaller parts of the design, if there was need to replace some of the entities.

# 4.1 VHDL introduction

VHDL is a hardware description language. VHDL code specifies a structure of a digital circuit. The code may be synthesized to a digital circuit and put on an Field programmable gate array (FPGA). The resulting circuits may as well be simulated using specialized software. There are some spin-offs of VHDL language by different vendors. [10] VHDL derives syntax from a language called Ada.

VHDL is similar to programming languages. Any algorithm may be written using VHDL, but its main purpose is to describe hardware. VHDL may be executed, similar to other programs. But it's common to call the process of execution simulation for VHDL. That is because VHDL is mainly for modeling designs. [7]

To use VHDL on real hardware, it must be synthesized. Synthesis tool transforms a program into a gate-level description. [7]

## 4.2 Design

The following section should act as a sort of a documentation of the VHDL implementation. It mainly shows the conception of the code and describes the inner workings of some of the more complex components. The design contains top level entities that may be used as a standalone entity representing the whole JESD204B receiver, even for a multipoint link consisting of multiple transmitters. The structure of these components is discussed to show how to compose an entity like that from the individual components.

#### 4.2.1 Defined record types

VHDL allows to make user defined record types that store multiple fields of specified types. There are some records in the implementation to ease transferring data between entities.

One of these is a link config, fields of the link config are specified in the table below. Link config contains JESD204B configuration fields of a link that can be seen in Table 3.3.

Another custom record type is a link character containing 8-bit character information, the 8-bit character itself, whether it's a control character and whether there was a disparity or not in table error.

For the transport layer, there is a record called frame state, it contains information about errors in a frame, whether the frame contains user data (data from the converters), whether there were some errors for the 8-bit decoder or later. It also tells whether the last frame was repeated, the frame gets repeated in case there is an error.

Every testbench contains a custom record type as well, containing inputs to the unit under test and usually expected output as well.

| Name             | Type        | Description                                  |

|------------------|-------------|----------------------------------------------|

| kout             | $std_logic$ | Whether the character is a control character |

| disparity_error  | $std_logic$ | Disparity does not match                     |

| $missing\_error$ | $std_logic$ | Not in 8b10b encoding table                  |

| d8b              | $std_logic$ | 8-bit character                              |

| user_data        | $std_logic$ | Whether the character is from data state or  |

|                  |             | is from synchronization                      |

Table 4.1 : Fields of defined link\_character record type.

Table 4.2 : Fields of defined frame\_state record type.

| Name                    | Type        | Description                             |

|-------------------------|-------------|-----------------------------------------|

| user_data               | $std_logic$ | Whether the frame consists only of      |

|                         |             | samples                                 |

| $invalid\_characters$   | $std_logic$ | Whether there are any characters that   |

|                         |             | shouldn't be in the frame               |

| $not\_enough\_data$     | $std_logic$ | An error stating there isn't enough     |

|                         |             | data to output a whole frame            |

| ring_buffer_overflow    | $std_logic$ | An error stating that there isn't       |

|                         |             | enough data to output a whole frame     |

| $disparity\_error$      | $std_logic$ | An error stating that there was a dis-  |

|                         |             | parity mismatch in the frame            |

| $not\_in\_table\_error$ | $std_logic$ | An error stating that some of the char- |

|                         |             | acters weren't present in $8b/10b$ en-  |

|                         |             | coding table                            |

| $wrong\_alignment$      | $std_logic$ | An error stating alignment characters   |

|                         |             | were found on unexpected position       |

| $last\_frame\_repeated$ | $std_logic$ | Whether a frame has been repeated,      |

|                         |             | due to errors                           |

#### 4.2.2 Top level entities

Top level entities are just wrappers of other entities without a lot of logic added. They allow for easier implementation of JESD204B standard to new design as well as show how to link the lower level components correctly.

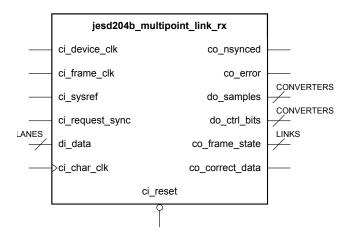

#### JESD204B multipoint receive link

Multipoint receive link is a component that connects multiple JESD204B link receive components (see subsubsection 4.2.2). It may generate multiframe clock and align it with the SYSREF signal. Subclasses 0 and 1 are supported. It should be possible to use this component as a top level entity for data link and transport layers in any design with one or more JESD204B links. It expects 10-bit characters from the lanes directly on its input, as di\_data input, shown on Figure 4.1. Samples from the converters are on the output of this component.

The inside of this component is quite simple, as it just connects jesd204b\_link\_rx, synced\_combination and lmfc\_generation.

| Name                | Description                                          |

|---------------------|------------------------------------------------------|

| ci_device_clk       | Device clock                                         |

| $ci\_char\_clk$     | Character clock                                      |

| $ci_frame_clk$      | Frame clock                                          |

| ci_sysref           | Sysref signal                                        |

| ci_reset            | Asynchronous reset (active low)                      |

| ci_request_sync     | Externally request synchronization                   |

| co_nsynced          | Indicates correct synchronization (active low)       |

| co_error            | Indicates any kind of error                          |

| di_data             | Input data from transceivers, 10-bits for every lane |

| $do\_samples$       | Output samples, valid if frame_state is okay         |

| $do\_ctrl\_bits$    | Output control bits, valid if frame_state is okay    |

| $co_frame_state$    | Combined state of all of the links and lanes         |

| $co\_correct\_data$ | Indication coming from co_frame_state, indicating    |

|                     | whether the data are okay                            |

Table 4.3 : Input and output ports of jesd204b\_multipoint\_link\_rx VHDL entity.

.

Table 4.4 : Generic parameters of jesd204b\_multipoint\_link\_rx VHDL entity.

| Name              | Description                                    |

|-------------------|------------------------------------------------|

| K_CHAR            | The 8-bit /K/ character                        |

| R_CHAR            | The 8-bit $/R/$ character                      |

| A_CHAR            | The 8-bit $/A/$ character                      |

| $Q\_CHAR$         | The 8-bit $/Q/$ character                      |

| DATA_RATE         | Multiple of device clock to get data rate      |

| MULTIFRAME_RATE   | $F \cdot K$                                    |

| ALIGN_BUFFER_SIZE | Size of the buffer for aligning lanes          |

| RX_BUFFER_DELAY   | Number of frames to wait before releasing buf- |

|                   | fer (for subclass 1)                           |

| LINKS             | Number of links on the multipoint link         |

| LANES             | Total number of lanes                          |

| CONVERTERS        | Total number of converters                     |

| CONFIG            | The configuration for each link                |

| ERROR_CONFIG      | The configuration for error_handler            |

#### JESD204B link receive

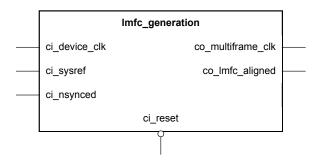

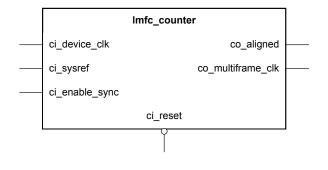

This entity encapsulates multiple data\_link\_layer entities, a descrambler and a transport\_layer for one JESD204B link. It receives a local multiframe clock as an input, seen on Figure 4.2, and thus may not generate multiframe clock by itself. For generating LMFC, lmfc\_generation should be used. Or alternatively, the multipoint top level entity may be used instead.

÷.

Figure 4.1: Diagram of JESD204B multipoint link receive VHDL entity.

Figure 4.2: Diagram of JESD204B link receive VHDL entity.

Table 4.5 : Input and output ports of jesd204b\_link\_rx VHDL entity.

| Name              | Description                                   |

|-------------------|-----------------------------------------------|

| ci_char_clk       | Character clock                               |

| $ci_frame_clk$    | Frame clock                                   |

| ci_multiframe_clk | Multiframe clock                              |

| ci_reset          | Asynchronous reset (active low)               |

| ci_request_sync   | Externally request synchronization            |

| co_nsynced        | Whether the link is synchronized (active low) |

| co_error          | Whether the output data are errorful          |

| di_data           | 10 bit characters for each lane               |

| do_samples        | Samples in a frame                            |

| $do\_ctrl\_bits$  | Samples control bits in a frame               |

| $co_frame_state$  | State of the frame                            |

| co_correct_data   | Whether samples are without an error          |

| Name              | Description                                    |

|-------------------|------------------------------------------------|

| K_CHAR            | The 8-bit /K/ character                        |

| R_CHAR            | The 8-bit $/R/$ character                      |

| A_CHAR            | The 8-bit $/A/$ character                      |

| Q_CHAR            | The 8-bit $/Q/$ character                      |

| Link config       | See Table 3.2                                  |

| ALIGN_BUFFER_SIZE | lane alignment FIFO buffer size                |

| RX_BUFFER_DELAY   | Number of frames to wait until releasing lanes |

|                   | (used for subclass 1)                          |

| ERROR_CONFIG      | Configuration for error handler                |

| SCRAMBLING        | Whether data are scrambled                     |

Table 4.6 : Generic parameters of jesd204b\_link\_rx VHDL entity.

### 4.2.3 Helpers

There are some entities used inside of top level entities to split logic that does not go into any of the layers directly.

#### Sync combination

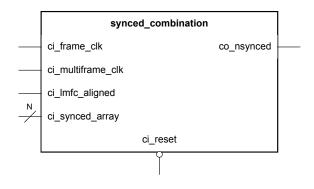

Sync combination component is used in top level entities for the link and multipoint link. Its function is to take multiple sync signals, as may be observed on Figure 4.3, and combine them into one sync output signal.

It respects JESD204B specification timing requirements for different subclasses. For subclass 0, sync combination will set sync signal only on frame clock, for subclass 1, sync combination will set sync signal only on multiframe clock and only in case the LMFC is aligned.