Czech

Technical

University

in Prague

F3

Faculty of Electrical Engineering Department of Cybernetics

# Implementation of Image Processing in the UVDAR System on FPGA

Bc. Vojtěch Vrba

Supervisor: Ing. Viktor Walter

Field of study: Cybernetics and Robotics Subfield: Cybernetics and Robotics

January 2023

# MASTER'S THESIS ASSIGNMENT

# I. Personal and study details

Student's name: Vrba Vojt ch Personal ID number: 474409

Faculty / Institute: Faculty of Electrical Engineering

Department / Institute: Department of Cybernetics

Study program: Cybernetics and Robotics

Branch of study: Cybernetics and Robotics

### II. Master's thesis details

Master's thesis title in English:

Implementation of Image Processing in the UVDAR System on FPGA

Master's thesis title in Czech:

### Implementace zpracování obrazu v systému UVDAR na FPGA

### Guidelines:

The MRS group uses on its robotic platforms designed for communication-free cooperation the visual relative localization system UVDAR. Since the current implementation of the system is divided into numerous discrete components and its software elements use the processing power of onboard computers. Therefore, there is currently a need to at least in part integrate the system into a single device. Research the operational principles of the UVDAR system. Based on this research evaluate which elements of the system can be consolidated into a single device or efficiently implement on FPGA. Design and implement the selected system elements on a FPGA development board and subsequently perform analysis of parity with the current implementation and of the computational performance improvement brought by the new implementation.

### Bibliography / sources:

- [1] Walter, Viktor a Staub, Nicolas a Saska, Martin a Franchi, Antonio "Mutual Localization of UAVs based on Blinking Ultraviolet Markers and 3D Time-Position Hough Transform" Munich, 2018.

- [2] C ı z ek, Petr a Faigl, Jan "Real-Time FPGA-Based Detection of Speeded-Up Robust Features Using Separable Convolution" USA, 2018.

- [3] Scaramuzza, Davide, et. al. "A Flexible Technique for Accurate Omnidirectional Camera Calibration and Structure from Motion" New York, 2006.

Name and workplace of master's thesis supervisor:

### Ing. Viktor Walter Multi-robot Systems FEE

Name and workplace of second master's thesis supervisor or consultant:

Date of master's thesis assignment: 21.01.2022 Deadline for master's thesis submission: 10.01.2023

Assignment valid until: 30.09.2023

Ing. Viktor Walterprof. Ing. Tomáš Svoboda, Ph.D.prof. Mgr. Petr Páta, Ph.D.Supervisor's signatureHead of department's signatureDean's signature

### III. Assignment receipt

The student acknowledges that the master's thesis is an individual work. The student must produce his thesis without the assistance of others, with the exception of provided consultations. Within the master's thesis, the author must state the names of consultants and include a list of references.

Date of assignment receipt Student's signature

# Acknowledgements

I would like to thank my thesis supervisor Ing. Viktor Walter for all his guidance throughout this work and for his invaluable feedback. I am also thankful to doc. Ing. Jan Fischer, CSc., for providing the imaging sensors necessary for conduction of the experimental part of this work. Finally, I must express my very profound gratitude to my parents for their unfailing support and continuous encouragement during my years of study.

# **Declaration**

I declare that the presented work was developed independently and that I have listed all sources of information used within it in accordance with the methodical instructions for observing the ethical principles in the preparation of university theses.

| Prague, 10 January 2023. |

|--------------------------|

| Signature:               |

# **Abstract**

The thesis focuses on the design of a Field Programmable Gate Array (FPGA) implementation of image processing algorithms used in the UltraViolet Direction And Ranging (UVDAR) system, developed for mutual relative localisation of Unmanned Aerial Vehicles (UAVs). In general terms, the UVDAR system consists of ultraviolet LED markers producing narrow-band signals, a UV-sensitive camera and image processing algorithms implemented in the C++ language. At first, the original software implementations of the algorithms were analysed in order to assess their computational complexity and memory allocation requirements. The main focus was on the specialised variation of the Features from Accelerated Segment Test (FAST) algorithm used for detection of active LED markers in camera images and on the 4D Hough Transform used for retrieval of linearly approximated image trajectories of the detected markers. Based on the analysis results, a FPGA architecture implementing the FAST-like algorithm was designed, producing identical outputs as the original C++ implementation. A selection of a suitable FPGA development board followed, together with a hardware design of a compatible circuit board with integrated CMOS sensor. The development platform Terasic DE10-Nano containing Cyclone V System-on-Chip (SoC) was selected for conducting real FPGA experiments. The VHSIC Hardware Description Language (VHDL) was used for implementation of the proposed FPGA architecture. Additional circuitry for visualisation of output data was designed using VHDL as well, allowing an output through HDMI interface in the form of an annotated video stream. Lastly, the current results, as well as an optional implementation of the UVDAR system into

an embedded device are discussed, with further proposals for future development on the SoC.

**Keywords:** UVDAR, UAVs, mutual relative localization, imaging sensor, bright spot detection, Hough Transform, 3D line fitting, FPGA

**Supervisor:** Ing. Viktor Walter

# **Abstrakt**

Tato diplomová práce se zabývá návrhem implementace obrazových algoritmů, které využívá systém UVDAR (UltraViolet Direction And Ranging) vyvinutý pro vzájemnou relativní lokalizaci dron v rojích, na programovatelných hradlových polích (FPGA). Systém UVDAR je ve svém základu složen z ultrafialových (UV) LED diod produkujících signály v úzkém pásmu spektra, kamerového senzoru citlivého v UV spektru a obrazových algoritmů implementovaných v jazyce C++. Nejprve byly analyzovány původní softwarové implementace těchto algoritmů a byla vyhodnocena jejich výpočetní a paměť ová náročnost, konkrétně u speciální variace algoritmu FAST (Features from Accelerated Segment Test) používané pro detekci aktivních jasových značek ve snímcích z kamery a u 4D Houghovy transformace používané pro nalezení lineární aproximace trajektorií detekovaných značek v obraze. Na základě výsledků analýzy byla navržena FPGA architektura pro implementaci variace FAST algoritmu, která produkovala shodné výstupy jako původní softwarová implementace. Následoval výběr vhodné vývojové desky s FPGA společně s návrhem hardwaru pro kompatibilní desku plošných spojů s CMOS kamerovým senzorem. Pro experimentální část práce byla vybrána vývojová deska Terasic DE10-Nano obsahující čip Cyclone V SoC (System-on-Chip). Poté byla implementována předložená FPGA architektura v jazyce VHDL (VH-SIC Hardware Description Language). Ve VHDL byla implementována i dodatečná logika pro vizualizaci výstupních dat v reálném čase ve formě anotovaného videa skrze rozhraní HDMI. V závěru práce jsou diskutovány dosažené výsledky, možnosti implementace systému UVDAR do samostatného zařízení a autorovy náměty pro další vývoj.

Klíčová slova: UVDAR, drony, vzájemná relativní lokalizace, obrazový senzor, detekce jasových značek, Houghova transformace, prokládání 3D přímkami, programovatelná hradlová pole

**Překlad názvu:** Implementace zpracování obrazu v systému UVDAR na FPGA

# **Contents**

| Introduction                                             | 1            |

|----------------------------------------------------------|--------------|

| 1 The UVDAR System                                       | 3            |

| 1.1 System Design Overview                               | 4            |

| 1.2 Theoretical Background                               | 6            |

| 1.2.1 Features from Accelerated                          |              |

| Segment Test (FAST)                                      | 6            |

| 1.2.2 Hough Transform (HT)                               | 10           |

| 1.3 Current Implementation Details                       | 18           |

| 1.3.1 Hardware Overview                                  | 18           |

| 2 FPGA Use Case                                          | 21           |

| 2.1 Initial Pipeline Stage                               | 21           |

| 2.2 The FAST-like Algorithm                              | 22           |

| 2.2.1 Related FPGA                                       |              |

| Implementations                                          | 23           |

| 2.2.2 Proposed FPGA Architecture                         | 24           |

| 2.3 The 4D Hough Transform                               | 26           |

| 2.3.1 Related FPGA Implementations                       | 31           |

|                                                          | 22           |

| 3 Hardware Selection & Design 3.1 FPGA Boards            | <b>33</b> 33 |

| 3.1.1 Microchip Hello FPGA Board                         | 33           |

| 3.1.2 Terasic DE10-Nano Board                            | 34           |

|                                                          | 35           |

| 3.1.3 Boards Comparison                                  | 36           |

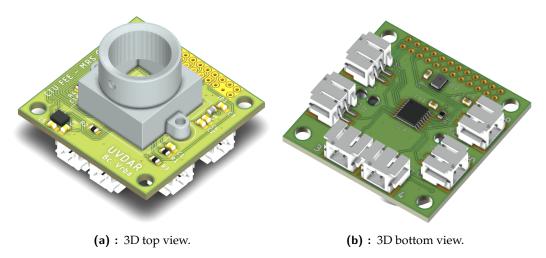

| 3.3 The Camera Board                                     | 37           |

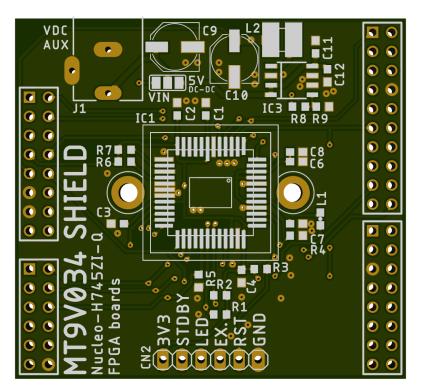

| 3.3.1 Hardware Design                                    | 38           |

| 3.3.2 Board Validation                                   | 40           |

|                                                          |              |

| 4 FPGA Experiments                                       | 43           |

| 4.1 Clock Configuration                                  | 44           |

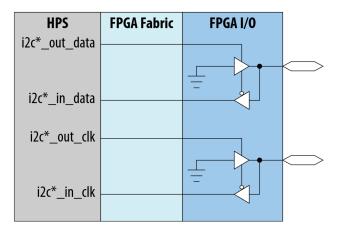

| 4.2 I2C Master Interface                                 | 44           |

| 4.3 DCMI Interface                                       | 48           |

| 4.4 VGA-to-HDMI Interface                                | 51           |

| 4.5 FAST-like Algorithm                                  | 57           |

| 4.6 Hard Processor System (HPS)                          | 62           |

| 4.6.1 Initial Setup                                      | 63           |

| 4.6.2 FPGA-HPS Communication using AXI/Avalon Interfaces | 64           |

| A Complete Camera Board Design                         | 83        |

|--------------------------------------------------------|-----------|

| References                                             | 77        |

| 6 Conclusion                                           | <b>75</b> |

| 5.4 Embedded Application of the UVDAR System           | 72        |

| 5.3 Running ROS Distribution for Comparison of Results | 72        |

| 5.2 Feasible HT4D FPGA Implementation                  | 71        |

| 5.1 Shortcomings of the FPGA Implementation            | 71        |

| 5 Discussion & Future Work                             | 71        |

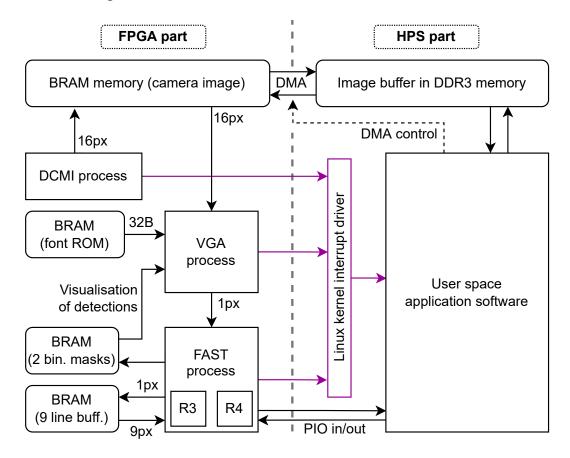

| 4.8 Complete Project Structure                         | 69        |

| 4.7 Total Resources Utilisation                        | 68        |

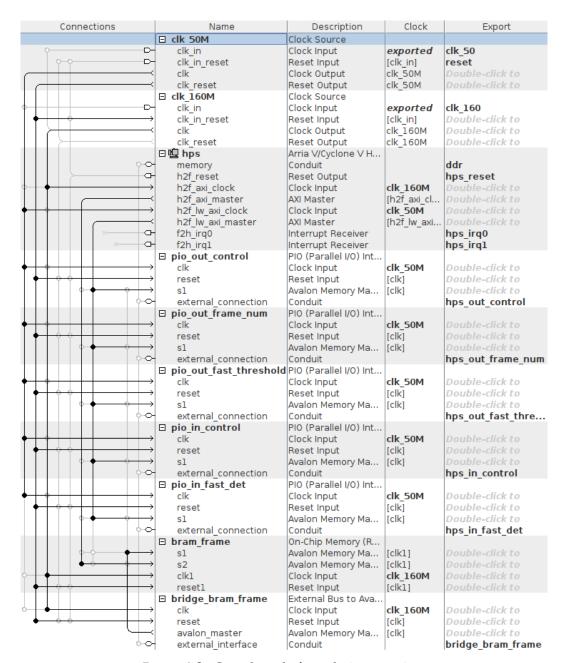

| 4.6.7 Complete Platform Designer Project               | 67        |

| 4.6.6 Software Description                             | 66        |

| 4.6.5 Sharing Memory Resources with the FPGA           | 65        |

| 4.6.4 Handling FPGA-to-HPS Interrupts                  | 65        |

| 4.6.3 Input/Output IP blocks                           | 65        |

# **Figures**

| 1.1 Block diagram of the UVDAR pipeline                                   |  |

|---------------------------------------------------------------------------|--|

| pipeline                                                                  |  |

| feature detector. [10]                                                    |  |

| 1.3 Comparison of the used and                                            |  |

| Bresenham's circle approximations. 8                                      |  |

| 1.4 Application of the Hough Transform for the straight line search. [14] |  |

| 1.5 Explanation of parameters needed                                      |  |

| for arbitrary shape detection using                                       |  |

| the GHT                                                                   |  |

| 1.6 Explanation of the t-points (the moving markers w.r.t. time). [7] 13  |  |

| 1.7 Generated masks for the pitch $\phi$                                  |  |

| parameter (8 pitch and 10 time steps) - with a cut for a more informative |  |

| visualisation                                                             |  |

| 1.8 Generated masks for the yaw $\psi$                                    |  |

| parameter (8 yaw and 10 time                                              |  |

| steps)                                                                    |  |

| 1.9 Projection of sample hybrid masks to the x-y plane                    |  |

| 1.10 Cylinder shell defined around the                                    |  |

| retrieved t-line. [7] 17                                                  |  |

| 1.11 Photos of the camera module and the lens used by the UVDAR           |  |

| system                                                                    |  |

| 0.1 D 1 EDCA 1'' (                                                        |  |

| 2.1 Proposed FPGA architecture for the FAST-like algorithm 24             |  |

| 2.2 Sizes of the hybrid masks for equal                                   |  |

| numbers of pitch and yaw steps 28                                         |  |

| 2.3 Hybrid mask sizes for the default                                     |  |

| parameter values                                                          |  |

| 2.4 Sums of hybrid mask sizes for $t \in [2, 14]$ - 3D surface            |  |

| approximation                                                             |  |

|                                                                           |  |

| 3.1 Microchip Hello FPGA Board                                            |  |

| Overview                                                          | 34             |

|-------------------------------------------------------------------|----------------|

| 3.3 ST Nucleo-H745ZI-Q Board                                      | J <del>1</del> |

| Overview                                                          | 36             |

| 3.4 DCMI frame structure in hardware                              | <u>,</u>       |

| synchronisation mode. [48]                                        | 37             |

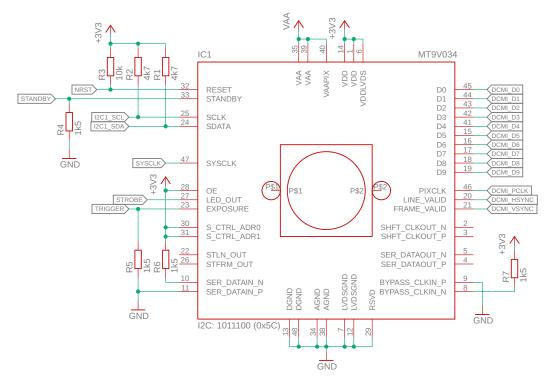

| 3.5 Schematic of the MT9V034 CMOS                                 |                |

| imaging sensor pin connections                                    | 38             |

| 3.6 Top layout of the custom camera board                         | 39             |

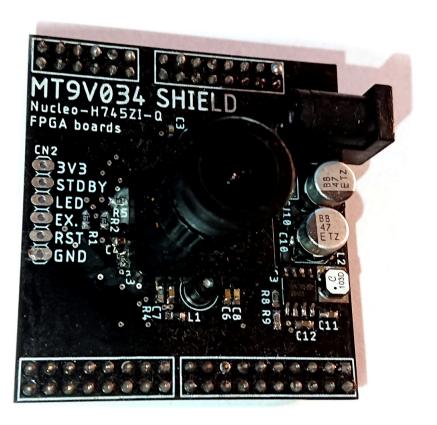

| 3.7 Photo of the assembled custom                                 |                |

| camera board with mounted lens                                    | 40             |

| 4.1 I2C wiring to the FPGA pins. [49]                             | 45             |

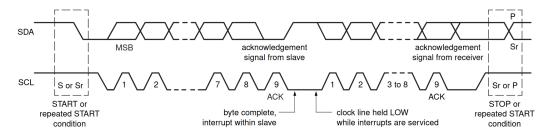

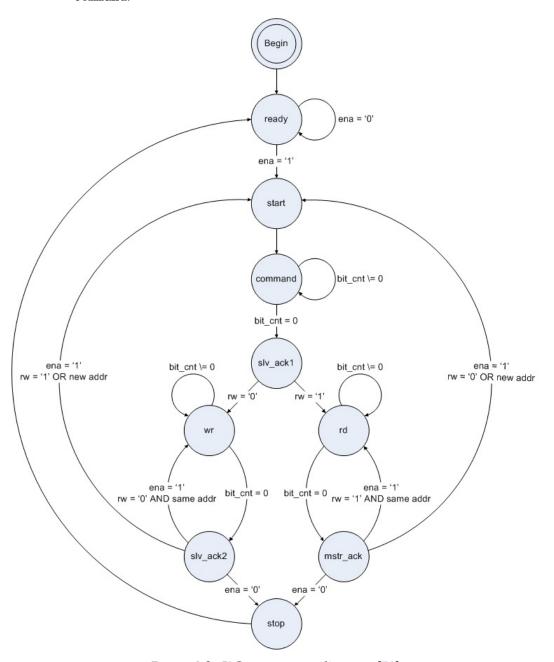

| 4.2 I2C data transfer diagram. [51] .                             | 45             |

| 4.3 I2C master state diagram. [50]                                | 46             |

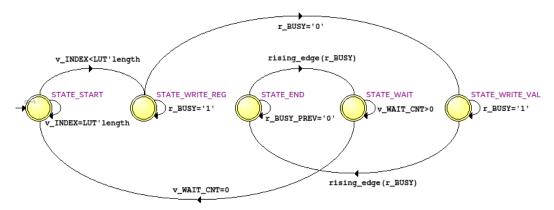

| 4.4 State diagram of the FSM serving                              | 457            |

| the I2C interface.                                                | 47             |

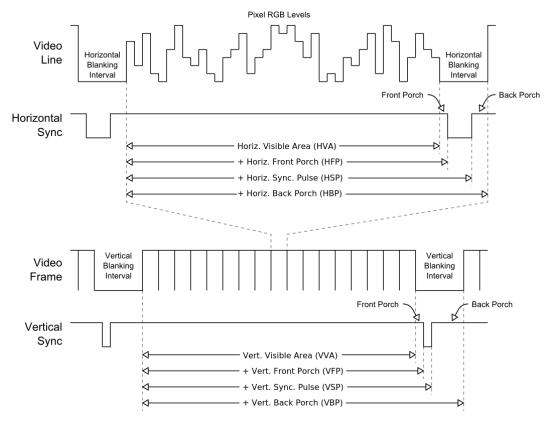

| 4.5 General VGA timing diagram                                    | 51             |

| 4.6 A sample frame captured from the HDMI video output            | 57             |

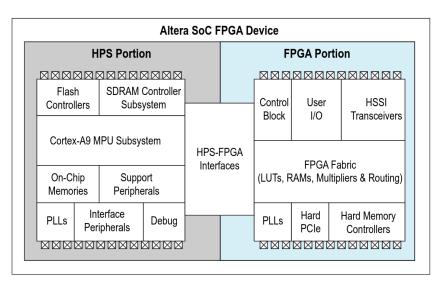

| 4.7 Altera SoC FPGA Device Block                                  |                |

| Diagram. [54]                                                     | 62             |

| 4.8 Complete platform designer                                    |                |

| project                                                           | 68             |

| 4.9 Complete project structure block                              | 69             |

| diagram                                                           | 09             |

| 5.1 Proposed design for a camera                                  |                |

| board of the embedded UVDAR                                       |                |

| system.                                                           | 72             |

| 5.2 Proposed design for a MCU board of the embedded UVDAR system. | 73             |

| A.1 Complete camera board layout.                                 | 83             |

| A.2 Complete camera board                                         |                |

| schematic                                                         | 84             |

|                                                                   |                |

|                                                                   |                |

# **Tables**

| 1.1 UVDAR ROS nodes/nodelets and                                                           |         |

|--------------------------------------------------------------------------------------------|---------|

| their description                                                                          | 18      |

| 2.1 Definition of the parameters of the camera                                             | e<br>21 |

| 2.2 The pipeline input stage requirements                                                  | 21      |

| 2.3 Parameters of the FAST-like algorithm                                                  | 22      |

| 2.4 Requirements of the FAST-like algorithm                                                | 23      |

| 2.5 Parameters of the 4D Hough transform algorithm                                         | 27      |

| 2.6 Optimal parameters of the formula approximating the computed sizes of the hybrid masks |         |

| 2.7 Computational requirements of the HT4D algorithm                                       |         |

| 2.8 Memory requirements of the HT4D algorithm                                              |         |

| 3.1 Comparison of the considered FPGA boards                                               | 35      |

| 3.2 Custom board signals connection to Nucleo and FPGA boards                              | 39      |

| 4.1 Prefix notation of the VHDL statements                                                 | 43      |

| 4.2 Summary of the FPGA clock signals                                                      | 44      |

| 4.3 Selectable VGA timings for the HDMI transmitter                                        | 52      |

| 4.4 Total FPGA resources utilisation.                                                      | 69      |

# Introduction

Localisation algorithms are used extensively in modern robotics, particularly for multi-robot systems. The localisation task can be approached via multiple different ways, traditionally using absolute localisation systems that cooperate with an external source of localisation signals (e.g., a navigation satellite), requiring appropriate receivers to be mounted on the robots. However, these systems are limited to outdoor or well defined indoor environments because of their working principle (e.g., due to a signal perception requirement) and with growing numbers of robots in the multi-robot system, they usually introduce new challenging problems that need to be solved for a proper functionality. In order to overcome the practical limitations of the absolute localisation approaches, relative localisation systems are being researched as they require only computational and sensory resources carried by the robots themselves.

The UVDAR (UltraViolet Direction And Ranging) system [1] developed by the Multi-Robot Systems Group at the Department of Cybernetics at the CTU is one of relative localisation systems and is described in detail in the chapter 1. Camera images are used as the only source of localisation information used by the UVDAR system as it relies completely on two image processing algorithms, particularly on FAST-like image feature detection and on a four-dimensional Hough Transform. Thus, the chapter 1 covers theoretical background of these algorithms and also describes the current software and hardware implementation of the UVDAR system.

The image processing algorithms are computationally demanding, which is the primary motivation for finding a way to separate the UVDAR system from computational resources which are used by the robots for many other important tasks, such as odometry calculation, mapping, mutual communication, etc. A FPGA (Field Programmable Gate Array) is considered for this task as is can be programmed to efficiently process large amounts of data in parallel. In order to evaluate feasibility of a FPGA implementation of the image processing algorithms, their computational and memory requirements are analysed in the chapter 2. State-of-the-art implementations of the FAST algorithm and of the Hough Transform are found in literature and their aspects are considered for the proposed FPGA architecture.

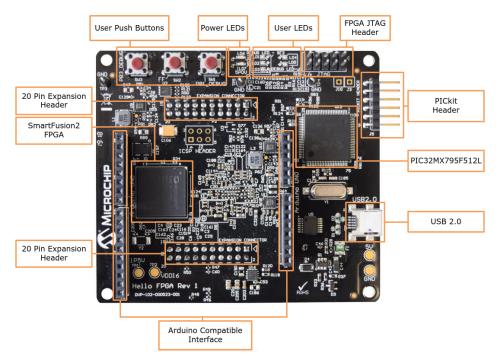

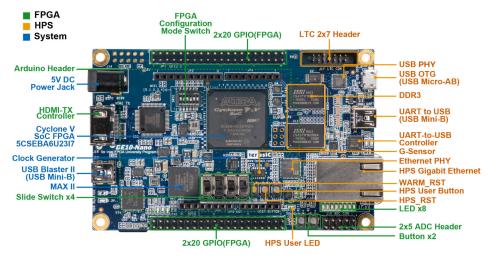

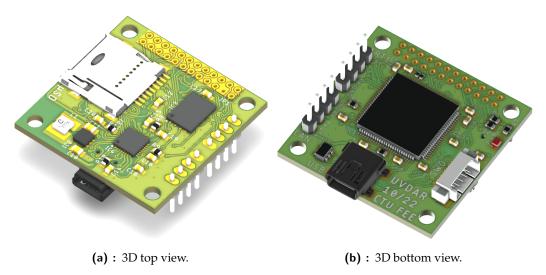

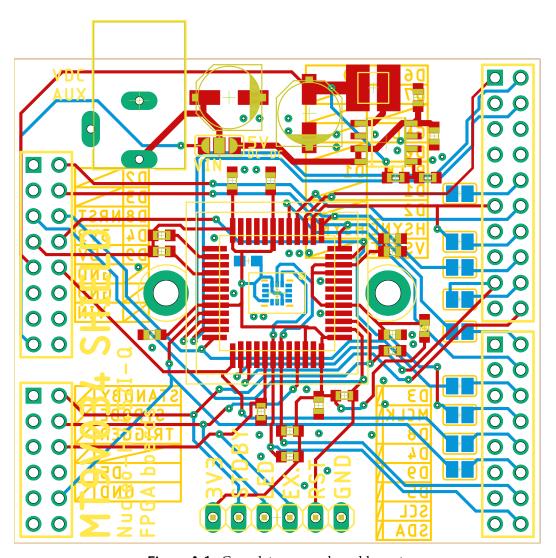

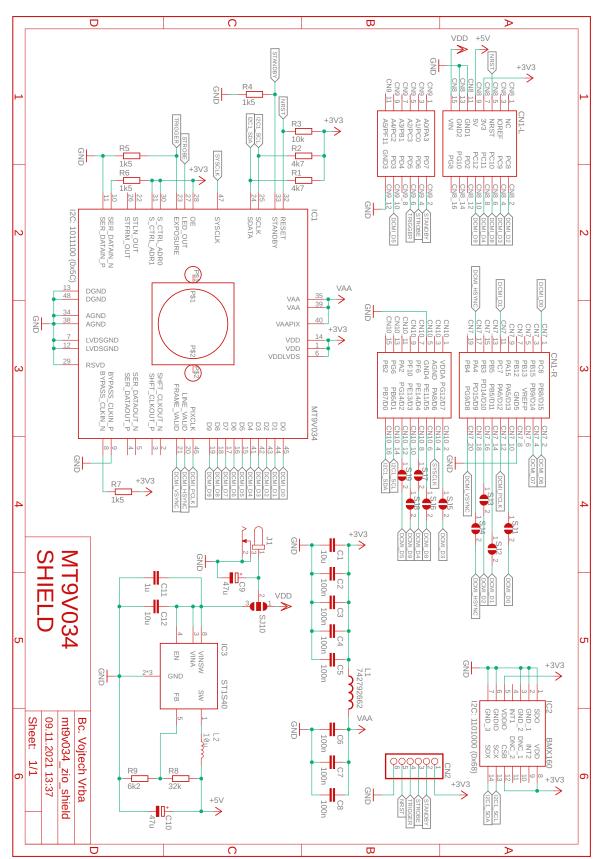

The chapter 3 is concerned with a selection of a suitable FPGA development board. Two different SoC (System-on-Chip) boards are compared based on parameters of

their FPGA and the CPU parts, as well as on their current price and availability on the market. Also, a custom camera board hardware design with a CMOS imaging sensor, which is originally utilised by the UVDAR system, is presented and a MCU board for its initial testing is described.

The actual FPGA experiments are discussed in the chapter 4. Used interfaces and their VHDL implementations are presented together with the VHDL implementation of the FAST-like algorithm. A setup of a HPS (Hard Processor System) of the SoC is described in detail, including a development of a Linux kernel module and a user space software application. At the end of the chapter, the total FPGA resources utilised by the proposed architecture are shown.

A discussion of shortcomings of the proposed architecture follows in the chapter 5. Ideas concerning a FPGA implementation of the Hough Transform and future improvements of the application software are discussed. The chapter 6 concludes the thesis.

# Chapter 1

# The UVDAR System

This chapter focuses on explanation of the main aspects of the UVDAR system. The system is overall complex and many different objectives must be fulfilled in order to achieve a robust system and to deploy it to real-world UAV swarms (i.e., multi-UAV systems).

The mutual localisation of the robots in cooperative swarms is an important tool for the performance of their cooperative tasks. All necessary information describing the swarm nodes (e.g., the current position, orientation and dynamics) must be always provided to each of them, otherwise no cooperation can be performed. Usually, the tools used to address the problem are dependent on the surrounding environment and also on the network architecture, which may be centralised or distributed.

The centralised architecture uses one central node with a processor which fuses all available information simultaneously to retrieve the state of all nodes. The information is then transmitted to the nodes using some conventional communication infrastructure, such as Wi-Fi, Bluetooth or another radio-based transmission method. The downsides of this approach are primarily:

- All nodes need to communicate with the central node. Whenever a node disconnects from the network, the state estimation of the swarm is incomplete.

- The processing power requirements of the central node grow rapidly with every node added to the swarm.

- The central node also presents a single point of failure, so a back-up central node should always be available in the swarm.

On the other hand, in **the distributed architecture** all the nodes process the available data about the swarm locally. The processing power grows slowly with the increasing swarm size, which results in better scalability of the whole system. But not all the important information is always available for each node which often means worse accuracy of the state estimation.

There are many methods of acquiring the current position and the orientation of the nodes. The most frequently used methods for **absolute localisation** (i.e., providing exact localisation data in global and/or local reference frames) among others are:

- GNSS (Global Navigation Satellite System) This method relies on the perception of the satellite navigation signal where each node carries its own GNSS receiver. Nowadays the precision of the GNSS-RTK (Real Time Kinematics) localisation method is in a range of millimetres. However this method may only be used outdoors in the open-sky conditions with a direct satellite link and it may also suffer from jamming and/or spoofing. [2]

- Motion capture (MoCap) systems These external localisation solutions are suitable for well defined indoor environments. A ground station (the central node) equipped with a set of cameras (usually infrared) calculates positions of all nodes inside the covered area and then provides the results for their coordination. [3]

**Relative localisation** frameworks are intended to be more flexible when used in GNSS-denied or unknown environments. They can be separated into two main categories:

- Distance-based frameworks The relative distances between the nodes are acquired by e.g., wireless communication devices such as ultra-wideband radio (UWB) [4], Wi-Fi [5] or Bluetooth modules [6]. Their obvious advantage is the omnidirectionality of the working principle, although a signal jamming and/or wireless traffic overload may occur with increasing swarm size.

- Vision-based frameworks The on-board camera sensors are used to detect neighbour nodes carrying specific patterns (passive markers) or light-source (active) markers to be easily detected by basic computer vision algorithms. These methods overcome wireless network limitations but introduce new ones, such as the FoV (Field-of-View) limits, dependence on the visibility and lighting conditions and also higher computational complexity.

The UVDAR system is an example of the distributed, relative localisation, vision-based framework which uses UV-light sources as node markers together with UV band-pass filters mounted on the lens of the cameras to avoid the sunlight saturation in the visible spectrum. [1] It is comprised of a complete software pipeline as well as a commercially available and a custom designed hardware underlay.

The following parts of this chapter present the overview of the system design as a whole, introduce the theory of the incorporated algorithms and also review the current implementation of the system.

# 1.1 System Design Overview

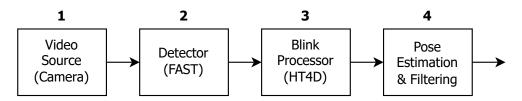

The UVDAR system can be understood as a 4-step pipeline as shown in fig. 1.1. Each step can be treated independently of the others as long as it produces data in a format expected by the next step.

**Figure 1.1:** Block diagram of the UVDAR pipeline

- 1. **Video Source** In a real-world application, the pipeline input is represented by a suitable camera device. The output of this block provides the raw images (video frames) at a reasonably high frame rate. The UVDAR system requires only monochromatic (grey scale) images at the input stage for the next steps.

- 2. **Detector** This block implements a bright-spot detection algorithm. In particular, the FAST-like algorithm (Features from Accelerated Segment Test) is used. This block outputs a set of (x, y) pixel coordinates of the detected bright points as well as a set of pixels belonging to the projection of the sun used for additional filtration, while both sets are obtained once per each video frame.

- 3. **Blink Processor** The sets of the bright spots (or markers) gathered from individual frames are first buffered as (x, y, t) triplets (referred to as t-points) in t-sets, with the latest frame corresponding to t = 0. The t-points lie along curves in (x, y, t) space (when the physical swarm node dynamics are limited) that can be approximated by straight lines, defined by their origin points and the pitch and yaw angles  $(\phi, \psi)$ . The lines are produced by the computation of the 4D Hough Transform (HT4D). The transform is also used to separate the sets of blinking markers belonging to individual swarm nodes as the markers belonging to the same rigid body (node) tend to lie on parallel lines. The swarm nodes can then be identified by their unique blinking patterns and when multiple blinking patterns are used by the same swarm node, its orientation can be also estimated. [7]

- 4. Pose Estimation & Filtering Each set of the blinking markers should fit a real model of a swarm node carrying the blinking LEDs. With the prior knowledge of the mutual distances and positions of the LEDs on the UAV model, multiple methods can be used to obtain a relative pose of the actual swarm node carrying the camera w.r.t. an another swarm node observed as a set of its blinking markers, such as a method based on the Unscented Transform (UT) [8] [9], a solution to the Perspective-Three-Point (P3P) problem or the Iterative Closest Points (ICP) algorithm, which is currently implemented in the UVDAR system. These methods also translate the known precision of markers' detection into the covariance of the pose estimation for the next use in a linear Kalman filter for correction of the measured poses and for additional improvement of the robustness of the system.

# 1.2 Theoretical Background

# 1.2.1 Features from Accelerated Segment Test (FAST)

The FAST algorithm is a feature detection algorithm used in computer vision primarily for detection of corners or other visually distinctive features from an image based on characteristics of the neighbourhood pixels. Other popular feature detection algorithms include Harris corner detection, SIFT (Scale Invariant Feature Transform), SURF (Speed-Up Robust Features) or BRIEF (Binary Robust Independent Elementary Features).

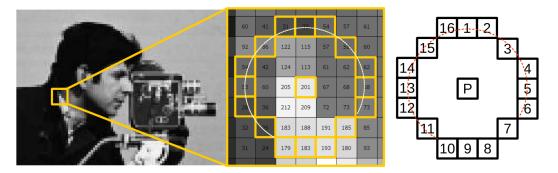

**Figure 1.2:** Illustration of the FAST image feature detector. [10]

An illustration of a principle of the FAST algorithm is shown in fig. 1.2. As explained in the original proposal of this algorithm in [11], the segment test is based on pixel intensities of the circular neighbourhood of the candidate pixel at the centre of the circle. The test is passed if all contiguous pixels of the selected neighbourhood differ in their intensity from the intensity of the candidate pixel at least by a static threshold value.

### The FAST-like algorithm

A simplified pseudocode of the algorithm used by the UVDAR system is summarised below. Intensity of every image pixel is tested for representing a marker point (the candidate pixel is brighter than the circular neighbourhood) or a sun point (the candidate pixel and the neighbourhood pixels are all very bright). When the image point retains its potential to be a marker point after the iterations over the neighbourhood pixels are finished, the pixel with highest intensity inside the interior (i.e., between the candidate pixel and the neighbourhood pixels) is stored as the detected marker.

In addition to the algorithm steps above, the UVDAR implementation also stores a binary mask of interiors related to the stored markers, which enables the algorithm to skip already processed marker areas so the markers are not processed and stored more than once. The sun points are used to filter out the detected markers too close to the projection of the sun as they might be just a result of a glare effect.

#### Algorithm 1 The FAST-like algorithm pseudocode ⊳ image width **Require:** W > 0**Require:** H > 0> image height **Require:** T > 0*⊳* static threshold value Require: N[(i,j)] $\triangleright$ array with opposing pixel coordinates (i, j) in sequence 1: **for** $0 \le x < W$ , $0 \le y < H$ **do** $\triangleright$ iterate over image coordinates (x, y)2: if $I_{x,y} > T$ then $\triangleright$ if the point's intensity $I_{x,y}$ is large enough $S \leftarrow False$ *▷* initially it does not have a potential to be a sun point 3: if $I_{x,y} > 2T$ then *⊳ if the point is very bright* 4: $S \leftarrow True$ by then has a potential to be a sun point 5: end if 6: $M \leftarrow True$ *⊳ initially it has a potential to be a marker* 7: $s \leftarrow 0$ ▶ keep a count of very bright neighbourhood pixels 8: for $(i, j) \in N$ do *⊳ iterate over the neighbourhood* 9: **if** $(I_{x,y} - I_{x+i,y+j}) < T/2$ **then** $\triangleright$ if the difference is too small 10: $M \leftarrow False$ > then it cannot be a marker point 11: **if** *S* is *True* **then** *⊳ if the point could be a part of the sun* 12: *▶* then the counter is incremented 13: $s \leftarrow s + 1$ else 14: break > otherwise the point is not relevant anymore 15: end if 16: else *⊳ if the difference is too large* 17: $S \leftarrow False$ *▶* then it cannot be a sun point 18: end if 19: end for 20: **if** *M* is *True* **then** *▶ if the marker potential is preserved* 21: Store argmax of the neighbourhood's interior as a marker. 22: **else if** S is True and s = length(N) then 23: ▷ if the sun potential is preserved and all neighbours are very bright Store (x, y) as a sun point. 24: 25: end if end if 26: 27: end for

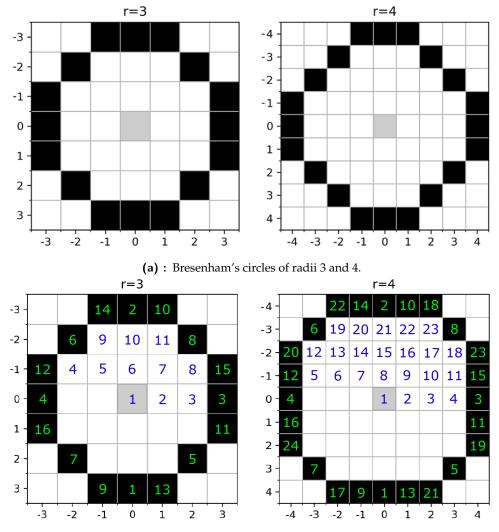

## Circle approximations

A Bresenham's circle [12] is usually used as an approximation of the circular neighbourhood but arbitrary approximations are possible. The circle approximations used by the UVDAR system are compared to the Bresenham's approximations in fig. 1.3. Only the circles with the radius of 4 pixels differ in their shapes.

**(b)**: Used circles of radii 3 and 4 with a denoted order of pixels for the algorithm.

Figure 1.3: Comparison of the used and Bresenham's circle approximations.

The speed of the segment test can be increased by a smarter choice of the order of the neighbourhood pixels. With the prior assumption of the size of the bright spots to be detected by this algorithm and the respective pixel intensity gradients present in the image, the UVDAR implementation minimises the number of required test steps by a selection of the mutually furthermost pixels in the circular neighbourhood. The order of the pixels used for the segment test (green) and the order of the interior pixels used for the search of the maximum value (blue) are shown in fig. 1.3b.

## An equivalent conditional approach

The FAST-like algorithm can be also described using the following equations:

1. The candidate point (x, y) cannot be a marker point if the following condition is met:

$$\exists (i,j) \in N : \left(I_{x,y} - I_{x+i,y+j}\right) < \frac{T}{2}$$

$$\Leftrightarrow \min_{(i,j)} \left(I_{x,y} - I_{x+i,y+j}\right) < \frac{T}{2}$$

$$\Leftrightarrow I_{x,y} - \max_{(i,j)} \left(I_{x+i,y+j}\right) < \frac{T}{2}$$

$$(1.1)$$

2. The candidate point (x,y) retains its potential to be a marker point if the following condition is met:

$$\forall (i,j) \in N : (I_{x,y} - I_{x+i,y+j}) \ge \frac{T}{2}$$

$$\Leftrightarrow \min_{(i,j)} (I_{x,y} - I_{x+i,y+j}) \ge \frac{T}{2}$$

$$\Leftrightarrow I_{x,y} - \max_{(i,j)} (I_{x+i,y+j}) \ge \frac{T}{2}$$

$$(1.2)$$

3. The candidate point (x, y) cannot be a sun point if the following condition is met:

$$\exists (i,j) \in N : (I_{x,y} - I_{x+i,y+j}) \ge \frac{T}{2}$$

$$\Leftrightarrow \max_{(i,j)} (I_{x,y} - I_{x+i,y+j}) \ge \frac{T}{2}$$

$$\Leftrightarrow I_{x,y} - \min_{(i,j)} (I_{x+i,y+j}) \ge \frac{T}{2}$$

$$(1.3)$$

4. The candidate point (x, y) retains its potential to be a sun point if the following condition is met:

$$\forall (i,j) \in N : \left(I_{x,y} - I_{x+i,y+j}\right) < \frac{T}{2}$$

$$\Leftrightarrow \max_{(i,j)} \left(I_{x,y} - I_{x+i,y+j}\right) < \frac{T}{2}$$

$$\Leftrightarrow I_{x,y} - \min_{(i,j)} \left(I_{x+i,y+j}\right) < \frac{T}{2}$$

$$(1.4)$$

It is obvious that the condition (1.1) is the negation of the condition (1.2), the same holds for conditions (1.3) and (1.4). Also, the condition (1.2) directly implies the condition (1.3) and (1.4) implies (1.1). When subtracting unsigned integer types it is also desirable to check their values for possible underflow.

Using the conditional expressions, the FAST feature detection can be separated into two steps performed for each image patch (i.e., overlapping patches of size 7x7 pixels for the radius of 3 or 9x9 pixels for the radius of 4) containing the whole circular neighbourhood:

- 1. For each image patch, find and store:

- a. the maximum and minimum values of the neighbourhood pixels (i.e., max and min of  $I_{x+i,y+j}$ ).

- b. the pixel intensity of the central candidate point (i.e.,  $I_{x,y}$ ).

- c. the maximum value of the pixels in the interior together with its coordinates (i.e., max and argmax).

- 2. If  $I_{x,y} > T$ , then evaluate the candidate point's potential to be:

- a. a marker point using the condition (1.2).

- b. a sun point using a condition  $I_{x,y} > 2T$  together with (1.4).

This separation of the computation steps inherently leads to a minimal FPGA implementation which is described later.

# 1.2.2 Hough Transform (HT)

The Hough Transform is a computer vision method of detecting complex patterns of points in binary images. The patterns are characterised using their specific parameters so that spatially extended patterns can be transformed into compact features in the resulting parameter space (referred to as *Hough space*). This way, a pattern detection problem in the image space is translated into a local peak detection problem in the Hough space. [13]

### A 2D lines search example

The simplest application of the Hough Transform is the search for straight lines made up of the points of interest. Every line in (x, y) plane can be expressed as y - mx - c = 0 using the slope parameter m and the intercept parameter c, however the parameter  $m \to \infty$  for lines approaching the vertical y axis.

More suitable line parameterisation in the form  $\rho = x\cos(\theta) + y\sin(\theta)$  is usually used, where  $\rho$  and  $\theta$  are the length and orientation of the normal vector to the line from the image origin. This way the parameter  $\theta$  can be limited to a range < 0,  $\pi$ ) and the parameter  $\rho$ 's magnitude is bounded approximately by the  $L^1$ -norm of the point vector.

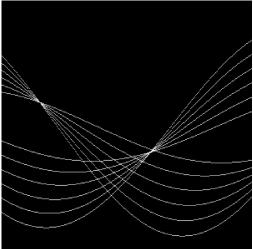

Then each image point maps to a sinusoidal curve representing all lines the point is incident on in the resulting parameter plane  $(\rho, \theta)$  (i.e., the Hough space), so the lines joining multiple points are found as the intersections of the matching sinusoidal curves (i.e., as the local maxima after summation of the curves' graphs).

Visual explanation is shown in fig. 1.4.

**(b)** : Sinusoidal curves in the Hough space:  $\rho = x_i \cos(\theta) + y_i \sin(\theta)$  The two rifest intersections correspond to the two expected straight lines in the image plane.

**Figure 1.4:** Application of the Hough Transform for the straight line search. [14]

An important note is the points in the discrete image plane (i.e., the pixel raster) do not exactly lie on the incident lines in most cases which causes that the resulting curve intersections in the discrete Hough space also may not be exact, which is also determined by the resolution of discretisation of the parameters. The local maxima obtained by the summation of the discretised curves therefore lead to an approximation of the incident lines.

Similarly, more complicated analytic patterns such as circles [14] or ellipses [15] can be detected using the Hough Transform, but for the price of increasing number of dimensions of the Hough space resulting in higher computational and memory requirements.

# Generalised Hough Transform (GHT)

Generalised Hough Transform (GHT) must be used when a detection of non-analytic patterns (i.e., without a general shape formula) is needed. [16]

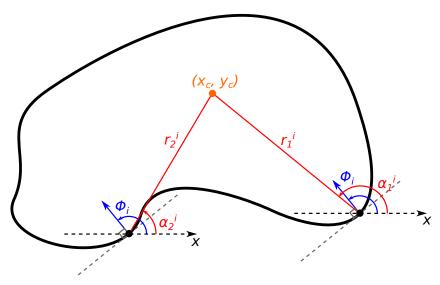

To perform the detection of arbitrary shapes using the GHT, the shape at first has to be described using its edge points together with the angles between the edge normal vectors originating in that points and the x-axis, as explained in fig. 1.5 where two different edge points with the same normal vector direction  $\Phi_i$  are shown. Also a fixed reference point  $(x_c, y_c)$  of that shape must be selected, allowing to compute the relative distances  $r_j^i$  and the angles  $\alpha_j^i$  related to a j-th edge point. The parameters of the shape are usually referred to as a so-called *object template* (or a R-table).

**Figure 1.5:** Explanation of parameters needed for arbitrary shape detection using the GHT.

The search for the object in an image is simplified by carrying out a *voting procedure* in the Hough space. The voting process refers to the maxima (peak) search in the Hough space (an example of the voting procedure is also the search for sinusoidal curve intersections in the aforementioned detection of 2D lines).

The GHT also allows adding more 2D shape parameters like its rotation  $\theta$  or a scale factor s, leading to a dense 4D parameter space. The resulting computational complexity is defined by four nested loops, in particular by iterating over all image points (points of interest) and by applying the object template (i.e., iterating over all 2D edge point coordinates defined for the desired shape, all possible rotations and all possible scale factors), generating every possible parameter combination that is used to increment the corresponding positions in the Hough space. [17]

The main principles behind the GHT (template generating and application on the points of interest, the voting procedure) are the same as for a 3D line search used by the UVDAR system.

# A 3D line pattern detection (HT4D)

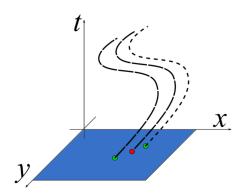

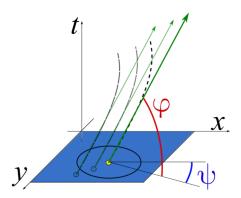

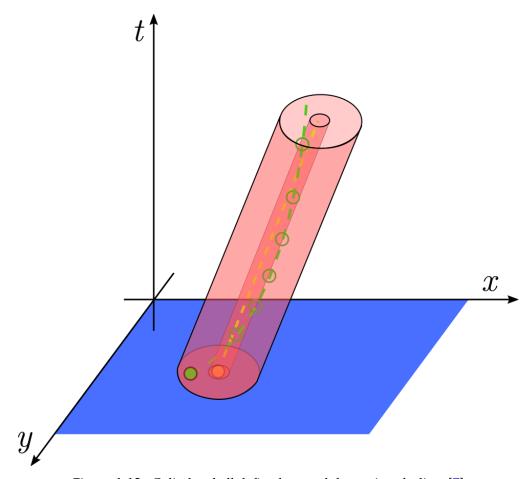

The UVDAR system utilises the Hough Transform to retrieve separate t-lines for each t-set of the t-points, more specifically to retrieve the corresponding origin points and the parameters of the t-lines, thus allowing retrieval of the blinking sequences along them. Visual explanation of the t-points and the t-lines is in fig. 1.6.

**(a)**: Moving along smooth curves (the green points are visible - ON, the red one is temporarily invisible - OFF)

**(b)**: Straight line approximation (the yellow point is the origin point in the current frame - the blue plane)

**Figure 1.6:** Explanation of the t-points (the moving markers w.r.t. time). [7]

In order to detect a straight line pattern in a 3D space (i.e., the t-lines in the (x, y, t) space), at least 4 parameters are required [18] which leads to a dense discretisation of a 4D Hough space. The memory and/or computational resources on most embedded UAV solutions usually do not suffice for a local maxima search in such space, hence the novel UVDAR approach [7] performs several simplifications to reduce the computational complexity:

■ Relaxation of the t-lines reconstruction by discretising the t-line parameters with a conveniently large steps  $\Delta \phi$  and  $\Delta \psi$ :

$$\phi_{i} = i \frac{0.5\pi}{\Delta \phi}, \ i \in \left\langle \frac{\phi_{\min}}{\Delta \phi}, \frac{\phi_{\max}}{\Delta \phi} \right\rangle \subset \mathbb{N}$$

$$\psi_{j} = j \frac{2\pi}{\Delta \psi}, \ j \in \left\langle \frac{\psi_{\min}}{\Delta \psi}, \frac{\psi_{\max}}{\Delta \psi} \right\rangle \subset \mathbb{N}$$

$$(1.5)$$

That also ensures lower susceptibility to small errors emerging from the preceding pipeline stages. Realistic t-lines are also constrained by the physics of the swarm system, permitting additional reduction of the Hough space size.

■ To avoid direct application of the 4D Hough Transform to the t-sets, the algorithm uses a simpler 4D space of indices for permuted  $(\phi, \psi)$  parameters. The Hough Transform transforms the t-points into the Hough space in a form of voxelated surfaces of pre-computed masks.

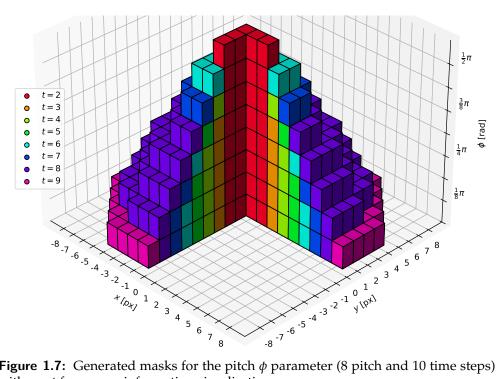

**Figure 1.7:** Generated masks for the pitch  $\phi$  parameter (8 pitch and 10 time steps) with a cut for a more informative visualisation.

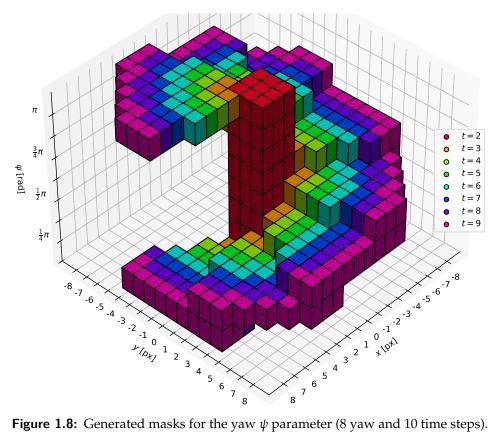

**Figure 1.8:** Generated masks for the yaw  $\psi$  parameter (8 yaw and 10 time steps).

Visualisations of generated voxel masks with sample parameter steps and time steps are shown in figures 1.7 and 1.8. The voxel surfaces belonging to consecutive time steps are overlapping to prevent discontinuities in the masks, which is not visible in the visualisations (new colours belong to the new voxels added at subsequent time steps).

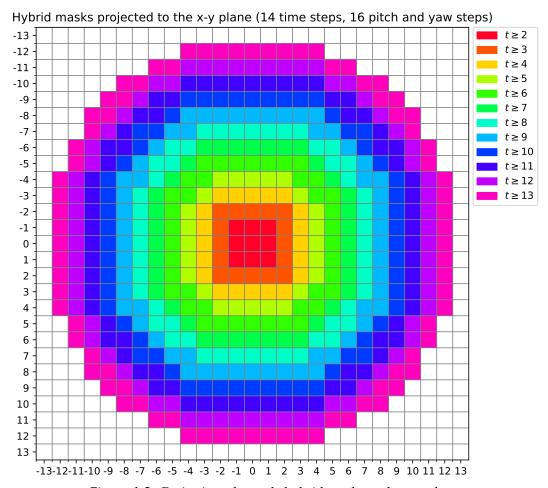

The permutation of the t pairs of the generated 3D masks for the pitch (i.e.,  $(x, y, \phi)$ ) and the yaw (i.e.,  $(x, y, \psi)$ ) parameters into t 3D arrays for the 4D hybrid masks is done by representing the third dimension by the parameters' indices combined in a yaw-pitch order (i.e.,  $(x, y, N_{\phi \text{ steps}} \cdot j + i)$ ). Projection of the permuted hybrid masks to the x-y plane is shown in fig. 1.9.

**Figure 1.9:** Projection of sample hybrid masks to the x-y plane.

If multiple t-points belong to the same marker, their images in the Hough space intersect (i.e., the voxel values are summed up) at voxels corresponding to the parameters of the t-line which they are incident to. [7]

The search for local maxima is conducted in a 2D space (referred to as maxima array). The maxima array is obtained by flattening the aforementioned 3D Hough space in the sense of selecting maxima in the t-axis direction. The

indices of permuted  $(\phi, \psi)$  parameters matching the maxima values are stored in another 2D array (referred to as *angle array*) of the same shape.

Then the maxima found in the maxima array correspond to the expected origin points of the t-lines (valid for both ON and OFF states of the markers) and the matching t-line parameters are found using the angle array.

## A summary of the t-lines retrieval algorithm

The process of retrieving t-lines is summarised in the following steps:

### 1. Initialisation:

- a. Allocate memory resources to store the 3D Hough space, the maxima array, the angle array and an accumulator array for t-sets of t-points (with a length equal to the number of time steps).

- b. Generate the steps for pitch and yaw parameters and store them in two separate arrays.

- c. For each time step, generate the voxel masks for pitch and yaw, permute them to 3D arrays for the 4D hybrid masks with combinations of the parameter array indices.

- 2. Insert a new t-set into the accumulator's first position (t = 0), drop the eldest t-set if the accumulator is full. The length of the most recent t-set is the number of visible markers. The number of expected markers (i.e., the markers currently in the OFF state) is a difference between the maximum of lengths of all accumulated t-sets and the number of the visible markers.

- 3. Apply the Hough Transform on the updated accumulator:

- a. Reset the Hough space and the maxima array.

- b. Apply the hybrid masks to the accumulated t-sets (i.e., increment the voxels of the Hough space belonging to the masks centred at the coordinates of the t-points).

- c. Flatten the Hough space to obtain the maxima array (i.e., store maxima values from the third axis direction) and the angle array.

### 4. Obtain the results:

- a. Nullify the maxima array around the visible markers to limit the search for the peaks only to the expected markers.

- b. Find the local maxima points in the maxima array and the corresponding permuted indices in the angle array. The search can stop when the number of found peaks is equal to the number of expected markers.

- c. Retrieve the blinking patterns, average yaw angles and average pitch angles for the origin points that are stored in an array made of the visible markers and the found peaks.

- 5. Repeat from the step 2.

### Blinking pattern retrieval

The blinking frequencies (or the blinking patterns) are retrieved by clustering all t-points close to the identified t-lines. This is done by considering small relative distances of origin points of the relevant t-lines from the centre of a *t-cylinder* which is generated around a *t*-axis of the retrieved t-lines (shown as yellow dashed line) passing through the origin points (yellow) as visualised in fig. 1.10. The green dashed line presents the real non-linear trajectory of the t-points.

**Figure 1.10:** Cylinder shell defined around the retrieved t-line. [7]

The expected radius range of the t-cylinder shell at a certain time step is calculated using the pitch parameter already obtained from the angle matrix for the estimated origin point. All visible t-points in the corresponding t-set in the accumulator are then filtered by their distance from the estimated origin point compared with the expected radius range, the pitch values of the valid visible matches are used in a next iteration for an average pitch calculation. The visible matches are filtered again using a t-cylinder generated using the estimated average pitch. If no visible matches remain present in the filtered array at a certain time step, the state of the blinking marker is considered to be OFF, otherwise ON. This way the blinking pattern is reconstructed.

# 1.3 Current Implementation Details

The current implementation [19] is written in the C++ language as a Robot Operating System (ROS) package containing nodes and nodelets for the individual pipeline stages.

The main nodes and nodelets with their description are shown in table 1.1.

| Node / Nodelet  | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Detector        | Detects bright points from the UV camera image.                                                                                             |

| BlinkProcessor  | Extracts blinking signals and image positions of the markers detected previously.                                                           |

| PoseCalculator  | Calculates approximate pose and error covariance of the MAVs carrying the UV LED markers.                                                   |

| Kalman          | Filters out sets of detected poses with covariance based on positions or the included identities.                                           |

| BluefoxEmulator | Generates an image stream similar to the output of the Bluefox cameras with UV band-pass filters.                                           |

| LedManager      | Sends commands to the controller boards that set<br>the signals of the blinking UV LEDs on the current<br>MAV using the Baca Protocol [20]. |

**Table 1.1:** UVDAR ROS nodes/nodelets and their description.

The software requirements (except the ROS distribution) include several ROS packages maintained by the MRS group, containing utility libraries, message type definitions and serial communication interface, a ROS package for accessing mvBlue-FOX cameras and several libraries used for testing of the implementation in simulation.

### 1.3.1 Hardware Overview

The cameras used by the UVDAR system are Matrix Vision mvBlueFOX-MLC200wG [21]. The photo of the camera is in fig. 1.11a. This camera model has a 0.4MP resolution (752x480 pixels) and a frame rate of 60 FPS is used. It uses a monochrome global-shutter 1/3" CMOS imaging sensor MT9V034 from ON Semiconductor (formerly Aptina) with a quantum efficiency of about 38% at the wavelength of 395 nm [22]. This wavelength is produced by the active LED markers placed on the UAVs. [1]

The lens mounted on the camera modules are Sunex DSL215 fisheye lens with approximately 180° of the horizontal FOV, depicted in fig. 1.11b. Also near-UV band-pass filters MidOpt BP365-R6 are placed between the CMOS sensors and the lens.

**(a)** : Matrix Vision mvBlueFOX-MLC200wG camera module.

(b): Sunex DSL215 fisheye lens.

**Figure 1.11:** Photos of the camera module and the lens used by the UVDAR system.

The custom hardware developed specifically for the UVDAR system is a LED controller board controlled by a STM32 microcontroller. [23] The LEDs driven by the controller board are ProLight Opto PM2B-1LLE with an emission angle of 130° and a maximum optical power of 315mW.

A custom camera board that was developed for this thesis uses the same CMOS imaging sensor as the mvBlueFOX camera modules. This way the input stage of the pipeline remains unchanged and the results can be easily validated against the current implementation. The custom board design is presented in the following chapter.

# Chapter 2

# **FPGA** Use Case

This chapter determines the memory and computational requirements of the two image processing algorithms considered for an implementation in the FPGA, i.e., of the FAST-like algorithm and of the 4D Hough Transform. Related approaches to FPGA implementations of the FAST algorithm and of the Hough Transform are also reviewed.

# 2.1 Initial Pipeline Stage

At first, the camera's parameters are defined in table 2.1 with their default values used by the current UVDAR implementation. The requirements of the input state of the pipeline are in table 2.2.

| Name               | Description                                               | Value                  |

|--------------------|-----------------------------------------------------------|------------------------|

| CAM <sub>IW</sub>  | Image width                                               | 752 px                 |

| CAM <sub>IH</sub>  | Image height                                              | 480 px                 |

| CAM <sub>IA</sub>  | Image area (i.e., CAM <sub>IW</sub> · CAM <sub>IH</sub> ) | 360960 px <sup>2</sup> |

| CAM <sub>FR</sub>  | Frame rate                                                | 60 FPS                 |

| CAM <sub>CLK</sub> | Pixel clock frequency                                     | 26.67 MHz              |

**Table 2.1:** Definition of the parameters of the camera.

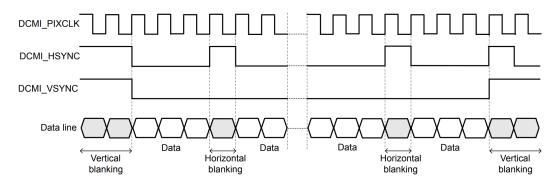

The camera's CMOS imaging sensor MT9V034 provides the image data through a DCMI (Digital Camera Interface) running at the  $CAM_{CLK}$  frequency and the interface is described in detail in the next chapters of this work.

| Requirement description   | Value                 |

|---------------------------|-----------------------|

| Memory requirements       |                       |

| Image (frame) (uint8_t[]) | $CAM_{IA} = 360960 B$ |

**Table 2.2:** The pipeline input stage requirements.

2. FPGA Use Case

It is shown in the following section that it is not necessary to store complete camera frame for the following image processing algorithms, thus reducing the memory requirements of the initial stage of the pipeline of the UVDAR system.

# 2.2 The FAST-like Algorithm

The FAST-like algorithm implementation uses parameters shown in table 2.3 for both radii of 3 and 4 pixels.

| Name                 | Description                                  | Value |

|----------------------|----------------------------------------------|-------|

| FAST <sub>T</sub>    | Static threshold (8-bit unsigned)            | 105   |

| FAST <sub>DP</sub>   | Maximum number of detected points            | 30    |

| FAST <sub>SD</sub>   | Minimum distance of the markers from the sun | 25 px |

| Radius of 3          | pixels                                       |       |

| FAST <sub>R3PS</sub> | Image patch (square) size                    | 7 px  |

| FAST <sub>R3B</sub>  | Size of the circular boundary                | 16 px |

| FAST <sub>R3UI</sub> | Size of the used neighbourhood's interior    | 11 px |

| FAST <sub>R3TI</sub> | Total size of the neighbourhood's interior   | 21 px |

| Radius of 4 pixels   |                                              |       |

| FAST <sub>R4PS</sub> | Image patch (square) size                    | 9 px  |

| FAST <sub>R4B</sub>  | Size of the circular boundary                | 24 px |

| FAST <sub>R4UI</sub> | Size of the used neighbourhood's interior    | 23 px |

| FAST <sub>R4TI</sub> | Total size of the neighbourhood's interior   | 45 px |

**Table 2.3:** Parameters of the FAST-like algorithm.

The pseudocode of the algorithm described in the previous chapter implies the requirements shown in table 2.4.

The worst-case time complexities are theoretical upper bounds of usual time complexities of the algorithm. The validation of a potential of a point to be a marker or a part of the sun ends in a majority of cases after only a few of iterations over boundary pixels of the neighbourhood, as there is usually a low number of the visible markers in the image (usually up to  $FAST_{DP}$ ) and the sun's projection is also limited in its size. The usual time complexity of the sun-to-marker distance check depends on the number of the detected sun points.

From the memory requirements perspective, it is disadvantageous to store the sun points as an array of their coordinates because of their usual abundance in the images. It is favourable to store the sun points in a binary mask array (i.e., a binary image with bit values set to 1 when the binary coordinates correspond to the detected sun points). Then the sun-to-marker distance checks can be performed e.g., using a repeated dilation of the sun mask followed by a bit value checking at the corresponding marker coordinates.

| Requirement description                                                | Value                                                |  |

|------------------------------------------------------------------------|------------------------------------------------------|--|

| Computational requirements                                             |                                                      |  |

| Worst-case complexity of potentials' validation                        | $\mathcal{O}\left(CAM_{IA}\cdotFAST_{RxB}\right)$    |  |

| Usual complexity of the interior search                                | $\mathcal{O}\left(CAM_{IA}\cdotFAST_{RxUI}\right)$   |  |

| Worst-case complexity of the sun distance check                        | $\mathcal{O}\left(CAM_{IA}\cdotFAST_{DP}\right)$     |  |

| Memory requirements                                                    |                                                      |  |

| Markers (coordinates) (uint16_t[]) $4 \cdot FAST_{DP} = 120 \text{ H}$ |                                                      |  |

| Sun points (coordinates) (uint16_t[])                                  | $4 \cdot \text{CAM}_{\text{IA}} = 1443840 \text{ B}$ |  |

| Sun points (binary mask) (uint8_t[])                                   | $CAM_{IA}/8 = 45120 B$                               |  |

| Memory requirements - radius of 3 pixels                               |                                                      |  |

| Boundary points (coordinates) (int8_t[]) $2 \cdot FAST_{R3B} = 32 B$   |                                                      |  |

| Interior points (coordinates) (int8_t[]) $2 \cdot FAST_{R3UI} = 22$    |                                                      |  |

| Memory requirements - radius of 4 pixels                               |                                                      |  |

| Boundary points (coordinates) (int8_t[])                               | $2 \cdot \text{FAST}_{\text{R4B}} = 48 \text{ B}$    |  |

| Interior points (coordinates) (int8_t[]) $2 \cdot FAST_{R4UI} = 46 E$  |                                                      |  |

**Table 2.4:** Requirements of the FAST-like algorithm.

### 2.2.1 Related FPGA Implementations

Many image co-processor (or accelerator) FPGA architectures can be found in the literature [24] [25] [26] [27] [28] [29] for many different feature detection algorithms. All of them possess an ability to process the image data stream with a minimal processing latency (i.e., they are *streaming architectures*).

As the results of the FAST algorithm can be evaluated based on the neighbour-hood of the pixels, which is completely contained in the corresponding image patches, it is suitable to provide a way to access the image patches without unnecessary delays and also to minimise the requirements for storing intermediate results. Usually, the sources of the image frames (e.g., cameras) provide the pixel data in a row-first order, meaning all the data in the first row must be read and handled before the second row's data is available.

This fact enforces such co-processors to implement so-called *line buffers* to store whole rows of the images. The buffers are filled sequentially with the incoming pixels from the video source. When all the line buffers required for the main image processing part are filled up, then the data then can be read from them in parallel, i.e., whole columns of the image patches are provided to the main processing part at once. [10]

The line buffers introduce an initial delay before the main image processing can take place. There is also an additional delay caused by the processing part itself before the first result is available at the output. After the two delays pass, the processing results are synchronised with the new incoming pixel data (i.e., with the pixel clock frequency). [30]

2. FPGA Use Case

This streaming approach reduces the needed amount of memory resources of the FPGA chip as the image does not have to be stored in its memory completely.

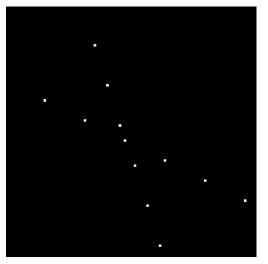

# 2.2.2 Proposed FPGA Architecture

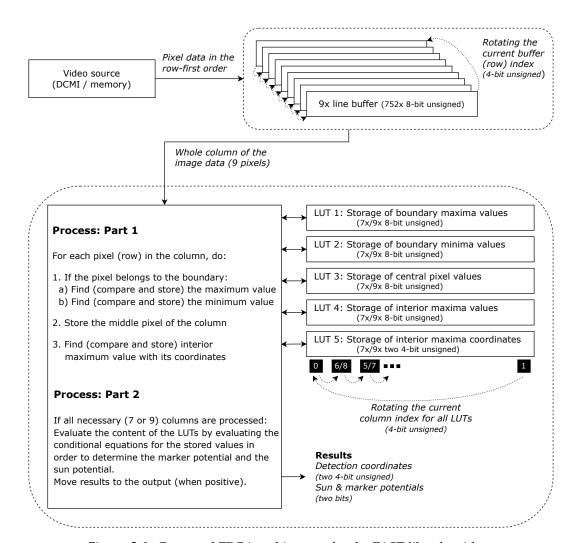

Figure 2.1: Proposed FPGA architecture for the FAST-like algorithm.

The proposed FPGA architecture for the implementation of the FAST-like algorithm is shown in a form of a block diagram in fig. 2.1.

■ It utilises 9 line buffers (or FIFOs) to store the consecutive image rows (i.e., with sizes equal to CAM<sub>IW</sub> bytes).

The resulting initial delay is thus equal to the height of the largest image patch times the image width, i.e.,  $CAM_{IW} \cdot FAST_{R4PS}$ , in terms of the  $CAM_{CLK}$  clock cycles. The process which handles memory access to the line buffers uses a row\_shift signal to keep track of the currently filled line buffer. When the 9th

row (i.e., the row\_shift is equal to 8) is about to be written to the last buffer (i.e., the initial delay passes), the new value is also read from the buffer (i.e., the memory is used in a write-first mode) together with the other 8 pixel values in the preceding buffers and the whole column is provided to the main FAST process (including the row\_shift signal). After the end of every 9th row, the row\_shift resets to 0 and the first line buffer gets overwritten as its old content is not needed anymore.

■ The main process is split into 2 parts and uses the conditional approach as described in the previous chapter. Five LUTs (Look Up Tables) are utilised to store the local information about boundary minima and maxima values, central pixel values and the interior maxima with their coordinates. Each of the LUTs contain 7 (or 9) elements used by both of the steps (depending on the selected circular radius).

The row\_shift signal is used for a calculation of a row\_index variable that is used as an index of the r-th pixel in the column array, so the pixel with r = 0 always lies in the topmost row of the image patch. The equation for its calculation is shown in equation (2.1).

$$row_index = (row_shift + r) \mod FAST_{R4PS}$$

;  $r = 0, ..., FAST_{R4PS} - 1$  (2.1)

■ The first part of the sequential process implements the comparisons of the maxima and minima values stored in the 5 LUTs with the pixel values in the current column. Hence each column is processed 7 (or 9) times on the same rising clock edge for the 7 (or 9) overlapping image patches and the results are stored into the LUT at the position corresponding to a column\_index variable. When the first 7 (or 9) columns for each row are processed (i.e., the additional delay passes and all columns and rows of the first image patch are evaluated), the second part of the process takes place.

The column\_index variable rotates in such a way that the different pixel comparisons for the current column c are saved to the correct LUT positions for the overlapping patches. An auxiliary column\_shift variable is initially set to 0 and gets incremented by 1 up to 6 (or 8) after each completion of the first part, then rewinds to value 0. The column\_index for the currently processed column c of the image patch is computed as shown in equation (2.2), hence the pixels with c = 0 always lie in the leftmost column of the image patch.

$$col\_index = (col\_shift - c) \mod FAST_{RxPS}$$

;  $c = 0, ..., FAST_{RxPS} - 1$  (2.2)

■ The second part of the process is a straightforward implementation of the conditional equations. The data is read from the 5 LUTs (using an incremented column\_shift variable as an index matching the currently finished image patch) and the final comparisons with the static threshold value are performed. Eventually the local coordinates of the detected marker or sun point inside the

2. FPGA Use Case

image patch are moved to the output signals, including two bits indicating the designation of the point.

• At the moment when the detection results are read from the output, the final detection coordinates inside the original image frame are computed as the detection coordinates in the image patch plus the image coordinates of the current pixel being written to the line buffer and with each coordinate decremented by the processing delay (equal to the size of the image patch, FAST<sub>RXPS</sub>).

The comparisons in the first part of the process can be implemented with several different approaches, depending on how the boundary and interior coordinates are accessed or derived:

- 1. The relative coordinates of the circular neighbourhood can be stored in another two LUTs (for the boundary and the interior coordinates respectively), in similar fashion as they are stored in arrays used within the current implementation. This approach requires additional iterating over the LUTs and comparing the stored coordinates with the current row and column indices used in the process.

- 2. The affiliation of a pixel inside the image patch to the circular boundary (or to the interior) can be evaluated using its relative centred coordinates (x, y) with equations (2.3).

$$(10r - 3)^{2} < 100(x^{2} + y^{2}) < (10r + 5)^{2}$$

$$100(x^{2} + y^{2}) < (10r - 3)^{2}$$

(2.3)

The first equation produces the same circular boundary in a discrete pixel raster as the one used by the current implementation for both radii r = 3 and r = 4, the second equation refers to the interior.

3. The comparisons for the particular pixels in the columns can be hard-wired inside the VHDL process. No additional memory resources or loops are needed. Arbitrary shapes of the neighbourhood can be used, but at the cost of worse modifiability of the VHDL code.

For the proposed architecture, I opted for the third approach above as the VHDL code can be easily generated using a simple and parameterisable Python script.

The data types used by the architecture are 8-bit unsigned integers for all pixel-related values and 4-bit unsigned integers for all values related to coordinates, shifts and indices (limited by the image patch size).

# 2.3 The 4D Hough Transform

The parameters relevant to the implementation of the 4D Hough Transform with their default values are listed in table 2.5.

| Name                | Description                                                  | Value |

|---------------------|--------------------------------------------------------------|-------|

| HT4D <sub>MS</sub>  | Number of memory (time) steps                                | 14    |

| HT4D <sub>PS</sub>  | Number of pitch steps for the masks generation               | 16    |

| HT4D <sub>YS</sub>  | Number of yaw steps for the masks generation                 | 16    |

| HT4D <sub>NR</sub>  | Nullify radius for resetting the maxima array                | 5     |

| HT4D <sub>RR</sub>  | Reasonable radius for the blinking pattern retrieval         | 6     |

| HT4D <sub>MPS</sub> | Max. pixel shift for the mask width calculation              | 1     |

| HT4D <sub>FS</sub>  | Frame scale for the masks width calc. $(0.3 \cdot CAM_{FR})$ | 18    |

| HT4D <sub>MW</sub>  | Mask width $(1 + 2 \cdot HT4D_{MPS} \cdot (HT4D_{FS} - 1))$  | 35    |

**Table 2.5:** Parameters of the 4D Hough transform algorithm.

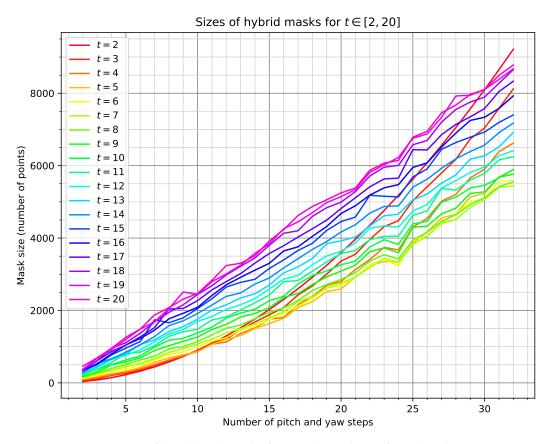

The Hough Transform implementation requires the pre-generated hybrid masks (i.e., the arrays of 3D coordinates) stored in the memory so that they are readily accessible by the algorithm to be applied onto the accumulated t-points. For simplicity of the visualisation of their sizes in fig. 2.2, an equal number of the pitch steps and of the yaw steps ranging from 2 up to 32 is assumed (i.e.,  $HT4D_{PS} = HT4D_{YS}$ ), for time step t ranging from 2 to 20.

The x and y point coordinates stored in the mask array for a time step t are in practise limited to a range [-(t-1),(t-1)] and it is obvious from the visualisation in fig. 1.9 in the previous chapter, the permuted yaw-pitch index (the z coordinate) is limited to range  $[0, \text{HT4D}_{PS} \cdot \text{HT4D}_{YS} - 1]$ . It should be noted that the x, y range limits arise from a maximum pixel shift parameter (i.e., the largest allowed pixel distance between two t-points belonging to the same t-line in subsequent time steps) which is equal to 1 for all assumptions stated in this thesis. In turn, the minimal pitch angle of a t-line equals to  $45^{\circ}$ .

With the assumption of the range limits, a 6-bit signed integer (range -32 to 31) can be used to store both the x and y coordinates and 10-bit unsigned integer (range 0 to 1023) to store the z coordinate (for all the masks assumed in the aforementioned visualisation).

For the default values listed in the table 2.5 (HT4D<sub>MS</sub> = 14, HT4D<sub>PS</sub> = 16, HT4D<sub>YS</sub> = 16), sufficient data types are 5-bit signed integers for x and y, and 8-bit unsigned integer for z (i.e., each 3D point takes 18 bits of the memory).

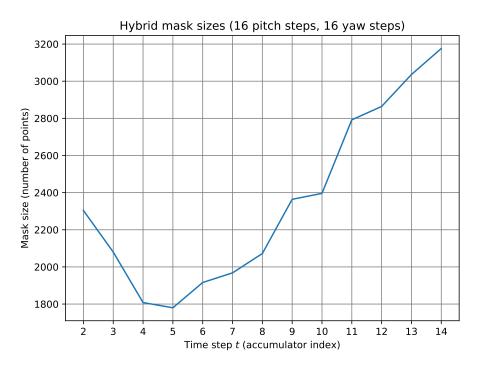

The sizes of the masks for the default parameter values are depicted in detail in fig. 2.3. All the mask arrays together contain 30556 points, occupying 550008 bits of the memory (or equally 68751 bytes, when the suggested data types are used).

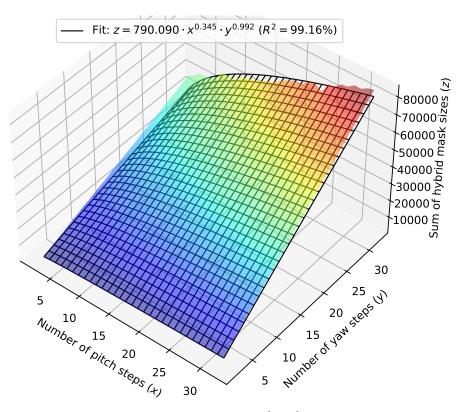

As a side note, the mask sizes (and also their cumulative sums) form a surface in a 3D space with dimensions (HT4D<sub>PS</sub>, HT4D<sub>YS</sub>, mask\_size) that can be approximated by a function (2.4) with score  $R^2 > 0.99$  (the coefficient of determination) for all numbers of steps in range 2 to 32 and  $t \le 20$ , as can be seen in fig. 2.4.

$$mask\_size = a \cdot (HT4D_{PS})^b \cdot (HT4D_{YS})^c; \ a, b, c \in \mathbb{R}$$

(2.4)

2. FPGA Use Case

**Figure 2.2:** Sizes of the hybrid masks for equal numbers of pitch and yaw steps.

**Figure 2.3:** Hybrid mask sizes for the default parameter values.

**Figure 2.4:** Sums of hybrid mask sizes for  $t \in [2, 14]$  - 3D surface approximation.

Furthermore, the parameters a, b, c can be approximated as well, as functions of the time step t, leading to a formula (2.5) for computing the mask size (its number of points) for a particular time step t.

$$mask\_size = \left(\alpha_a + \frac{\beta_a}{1 + \gamma_a^{-t + \delta_a}}\right) \cdot \left(HT4D_{PS}\right)^{\left(\alpha_b + \beta_b^{-t + \gamma_b}\right)} \cdot \left(HT4D_{YS}\right)^c \tag{2.5}$$

| Parameter     | Optimal value |

|---------------|---------------|

| $\alpha_a$    | -14.4478      |

| $\beta_a$     | 283.172       |

| $\gamma_a$    | 1.27306       |

| $\delta_a$    | 12.0956       |

| $\  \alpha_b$ | 0.03493       |

| $\beta_b$     | 1.25669       |

| $\gamma_b$    | 1.98181       |

| С             | 0.99576       |

**Table 2.6:** Optimal parameters of the formula approximating the computed sizes of the hybrid masks.

2. FPGA Use Case

The formula (2.5) can be used to determine the upper bound of the necessary memory utilisation when the hybrid masks are generated for new parameters. The formula's 8 real parameters have optimal values listed in table 2.6, with  $R^2 \approx 0.996$  for all numbers of steps in range 2 to 32 and time steps  $t \le 20$ .

The computational and memory requirements of the current implementation of the 4D Hough Transform are summarised in tables 2.7 and 2.8.

Apart from the main memory requirements listed in the table 2.8, there are also several auxiliary arrays needed, e.g., for storing the detected blinking patterns and the averaged pitch and yaw angles.

| Comp. complexity description   | Value                                                                                                       |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|

| A t-set insertion              | $\mathcal{O}\left(FAST_{DP}\right)$                                                                         |

| The Hough space reset          | $\mathcal{O}\left(CAM_{IA}\cdotHT4D_{PS}\cdotHT4D_{YS}\right)$                                              |

| The maxima array reset         | $\mathcal{O}\left(CAM_{IA} ight)$                                                                           |

| The hybrid mask application    | $\mathcal{O}\left(\text{max. mask size} \cdot \text{FAST}_{\text{DP}} \cdot \text{HT4D}_{\text{MS}}\right)$ |

| The Hough space flattening     | $\mathcal{O}\left(CAM_{IA}\cdotHT4D_{PS}\cdotHT4D_{YS}\right)$                                              |

| The maxima array nullification | $\mathcal{O}\left( FAST_{DP} \right)$                                                                       |

| The maxima search              | $\mathcal{O}\left(CAM_{IA} ight)$                                                                           |

| A blinking pattern retrieval   | $\mathcal{O}\left(\text{FAST}_{\text{DP}}\cdot\text{HT4D}_{\text{MS}}\right)$                               |

**Table 2.7:** Computational requirements of the HT4D algorithm.

| Memory requirement description      | Value                                                                            |

|-------------------------------------|----------------------------------------------------------------------------------|

| Pitch steps (float32_t[])           | $4 \cdot \text{HT4D}_{PS} = 64 \text{ B}$                                        |

| Yaw steps (float32_t[])             | $4 \cdot \text{HT4D}_{\text{YS}} = 64 \text{ B}$                                 |

| Cotangent maxima (float32_t[])      | $4 \cdot \text{HT4D}_{PS} = 64 \text{ B}$                                        |

| Cotangent minima (float32_t[])      | $4 \cdot \text{HT4D}_{PS} = 64 \text{ B}$                                        |

| Accumulator for t-sets (uint16_t[]) | $6 \cdot \text{FAST}_{\text{DP}} \cdot \text{HT4D}_{\text{MS}} = 2520 \text{ B}$ |

| Hough space (uint8_t[])             | $CAM_{IA} \cdot HT4D_{PS} \cdot HT4D_{YS} \approx 92 \text{ MB}$                 |

| Maxima array (uint8_t[])            | $CAM_{IA} = 360960 B$                                                            |

| Angle array (uint8_t[])             | $CAM_{IA} = 360960 B$                                                            |

| Hybrid masks ((u)int8_t[])          | $3 \cdot \text{sum}(\text{mask sizes}) = 91668 \text{ B}$                        |

**Table 2.8:** Memory requirements of the HT4D algorithm.

It is obvious that unlike the memory requirements of the FAST-like algorithm, the memory utilisation of the 4D Hough Transform is too large in comparison with common internal memory resources inside embedded microcontrollers or FPGA chips. For a practical embedded application of this algorithm in its current form, an external memory resource has to be used.

### 2.3.1 Related FPGA Implementations

One of the earliest implementations of the Hough Transform on FPGA for 2D line pattern detection is presented in [31]. More specifically, the Fast Incremental Hough Transform (FIHT2) [32] is used as it does not require any trigonometric operations and only addition operations are needed. Their architecture also consists of constant value multipliers needed for a correction of the values retrieved via incrementation. This incremental approach, however, applies only to 2D line patterns.