Insert here your thesis' task.

Master's thesis

### PUF Based IoT Device Over-the-air Update

Marek Kňazovický

Department of Information Security Supervisor: Ing. Jiří Dostál, Ph.D.

June 23, 2022

# Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular that the Czech Technical University in Prague has the right to conclude a license agreement on the utilization of this thesis as school work under the provisions of Article 60(1) of the Act.

In Prague on June 23, 2022

.....

Czech Technical University in Prague Faculty of Information Technology © 2022 Marek Kňazovický. All rights reserved. This thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

#### Citation of this thesis

Kňazovický, Marek. *PUF Based IoT Device Over-the-air Update*. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2022.

# Abstrakt

Práca sa zaoberá prieskumom a navrhnutím zabezpečeného OTA update procesu s využitím SRAM PUF a nasadením na obecnom IoT zariadení. Je rozdelená na tri časti.

Prvá časť skúma štruktúru a fungovanie bezbežného OTA procesu a je ukončená navrhnutím obecnej varianty vhodnej pre zdrojovo obmedzené zariadenia. Druhá časť skúma možnosti využitia PUF v kryptografických technikách daného OTA procesu. A na záver bola vyvinutá knižnica obecne užívajuca SRAM PUF, integrovaná a následne nasadená do ESP32 proof of concept využitia, kde bol použitý v rámci diskutovaného návrh OTA procesu.

**Kľúčové slová** OTA, SRAM, PUF, IoT, zdrojovo obmedzené zariadenie, kryptografické techniky, ESP32, proof of concept

## Abstract

The work deals with surveying and designing a secure OTA update process using an SRAM-based PUF and a typical IoT device deployment. It consists of three parts.

The first part examines the structure and the functionalities of a common OTA process. It is concluded with a proposal of a simple variant of the process suitable for resourceconstrained devices. The second part studies the possibilities of using a PUF within the cryptographic techniques utilized by the proposed OTA process. And finally, a library for general use of SRAM PUF was designed, integrated and deployed on an ESP32 proof of concept demonstration, where it was used among the simplified OTA proposal.

**Keywords** OTA, SRAM, PUF, IoT, resource-constrained device, cryptographic techniques, ESP32, proof of concept

# Contents

| In       | trod              | uction    |                                                           | 1                        |

|----------|-------------------|-----------|-----------------------------------------------------------|--------------------------|

|          | Thes              | sis goals | 3                                                         | 2                        |

| _        | 0                 |           |                                                           | •                        |

| 1        |                   |           | Air update analysis and model proposal                    | 3                        |

|          | 1.1               |           | update scheme                                             | 4                        |

|          |                   | 1.1.1     | Provisioning                                              | 5                        |

|          |                   | 1.1.2     | Second stage boot loader                                  | 5                        |

|          |                   | 1.1.3     | OTA update transfer, speed and compression                | 8                        |

|          |                   | 1.1.4     | General challenges and requirements                       | 9                        |

|          |                   | 1.1.5     | OTA update security                                       | 11                       |

|          |                   |           | 1.1.5.1 OTA security concerns, threats and risks          | 11                       |

|          |                   |           | 1.1.5.2 Security measure inquiry                          | 13                       |

|          |                   |           | 1.1.5.3 Cryptographic techniques in OTA security measures | 15                       |

|          | 1.2               | Resour    | ce-efficient OTA update model                             | 17                       |

|          |                   | 1.2.1     | OTA architecture                                          | 17                       |

|          |                   | 1.2.2     | Requirements and implementation strategies                | 18                       |

|          |                   | 1.2.3     |                                                           | 19                       |

|          |                   | 1.2.4     |                                                           | 23                       |

|          |                   |           | 1.2.4.1 Brief analysis and attacks on the CTs             | 23                       |

|          |                   |           | 1.2.4.2 Vulnerabilities to attacks                        | 24                       |

|          |                   |           | 1.2.4.3 Viable CT to be replaced                          | 24                       |

|          |                   | 1.2.5     | -                                                         | 25                       |

| <b>2</b> | PIII              | Fs and    | IoT devices                                               | 27                       |

| -        | 2.1               |           |                                                           | 27                       |

|          | $\frac{2.1}{2.2}$ |           |                                                           | 21                       |

|          | $\frac{2.2}{2.3}$ |           |                                                           | $\frac{29}{30}$          |

|          | $\frac{2.3}{2.4}$ |           | -based PUF details                                        |                          |

|          | 2.4               | 2.4.1     |                                                           |                          |

|          |                   | 2.4.1     |                                                           | $\mathcal{O}\mathcal{L}$ |

|              |                                   | 2.4.2          | PUF response error rate improvement tools                   |  |  |  |

|--------------|-----------------------------------|----------------|-------------------------------------------------------------|--|--|--|

| 3            | 3 SRAM PUF processing framework 3 |                |                                                             |  |  |  |

|              | 3.1                               | Enrolr         | nent                                                        |  |  |  |

|              |                                   | 3.1.1          | PUF library provisioning                                    |  |  |  |

|              |                                   | 3.1.2          | PUF mask and SRAM bits                                      |  |  |  |

|              |                                   | 3.1.3          | Von Neumann Corrector debiasing                             |  |  |  |

|              |                                   | 3.1.4          | Construction of a mask of stable bits                       |  |  |  |

|              |                                   | 3.1.5          | Helper data assembly                                        |  |  |  |

|              | 3.2                               | Secret         | extraction                                                  |  |  |  |

|              | 3.3                               | SRAM           | I PUF framework summary43                                   |  |  |  |

| 4            | Pro                               | of of c        | oncept implementation 45                                    |  |  |  |

|              | 4.1                               |                | rdware platform comparison                                  |  |  |  |

|              | 4.2                               |                | y implementation details on the ESP32 platform              |  |  |  |

|              |                                   | 4.2.1          |                                                             |  |  |  |

|              |                                   | 4.2.2          | SRAM PUF library                                            |  |  |  |

|              |                                   |                | 4.2.2.1 Development                                         |  |  |  |

|              |                                   |                | 4.2.2.2 Getting SRAM uninitialized state                    |  |  |  |

|              |                                   |                | 4.2.2.3 SRAM PUF library ESP32 integration                  |  |  |  |

|              |                                   |                | 4.2.2.4 Usage of a DRAM block for PUF                       |  |  |  |

|              |                                   |                | 4.2.2.5 Library PUF metrics module                          |  |  |  |

|              |                                   |                | 4.2.2.6 Library integration and use on ESP32                |  |  |  |

|              |                                   |                | 4.2.2.7 Library integration testing on ESP32                |  |  |  |

|              |                                   | 4.2.3          | PUF-based OTA update process                                |  |  |  |

|              |                                   |                | 4.2.3.1 OTA process on ESP32                                |  |  |  |

|              |                                   |                | 4.2.3.2 SRAM PUF library integration into an OTA project 66 |  |  |  |

|              | 4.3                               | Integra        | ation conclusion                                            |  |  |  |

|              |                                   | 0              |                                                             |  |  |  |

| Co           | onclu                             | ision          | 69                                                          |  |  |  |

| Re           | efere                             | nces           | 71                                                          |  |  |  |

| $\mathbf{A}$ | Acr                               | onyms          | 77                                                          |  |  |  |

| в            | Lib                               | rary us        | age 81                                                      |  |  |  |

| D            |                                   | •              | mtesting project                                            |  |  |  |

|              | D.1                               | B.1.1          | Prerequisites of the pufSym library                         |  |  |  |

|              |                                   | B.1.1<br>B.1.2 | Use of pufSym library                                       |  |  |  |

|              | B.2                               |                | m library testing project                                   |  |  |  |

|              | 10.4                              | B.2.1          | Requirements   82                                           |  |  |  |

|              |                                   | B.2.1<br>B.2.2 | Deployment                                                  |  |  |  |

|              |                                   | B.2.2          | Usage                                                       |  |  |  |

|              |                                   | B.2.4          | Data collection         83                                  |  |  |  |

|              | B.3                               |                | pted Binary OTA update with SRAM PUF usage                  |  |  |  |

| B.3.1                    | Requirements            | 83 |  |  |  |  |  |  |

|--------------------------|-------------------------|----|--|--|--|--|--|--|

| B.3.2                    | Usage                   | 84 |  |  |  |  |  |  |

| B.3.3                    | Monitoring              | 84 |  |  |  |  |  |  |

| B.3.4                    | Glitch/bug notice       | 84 |  |  |  |  |  |  |

| stents of enclosed DVD 8 |                         |    |  |  |  |  |  |  |

| itents d                 | tents of enclosed DVD 8 |    |  |  |  |  |  |  |

#### C Contents of enclosed DVD

# **List of Figures**

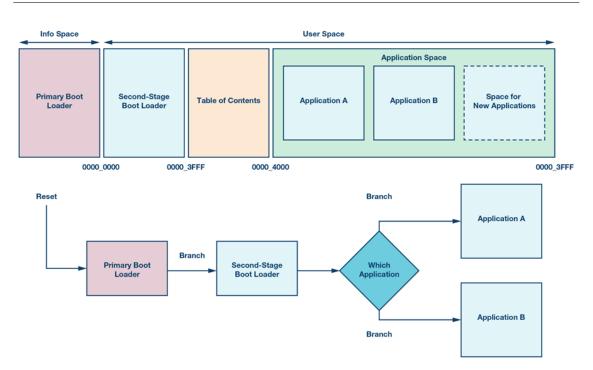

| 1.1  | General bootloader scheme              | 7  |

|------|----------------------------------------|----|

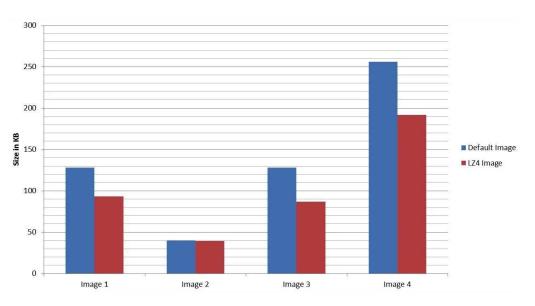

| 1.2  | LZ4 compression examples               | 10 |

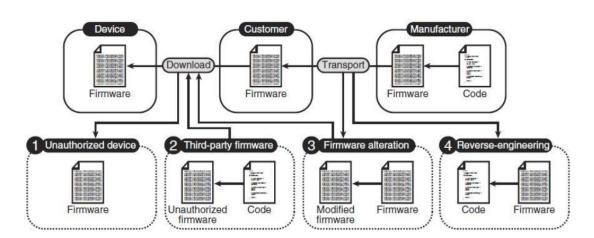

| 1.3  | Common OTA security threats            | 13 |

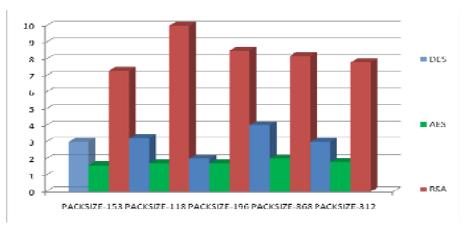

| 1.4  | AES vs RSA encryption speed comparison | 21 |

| 1.5  |                                        | 22 |

| 2.1  | PUF principle                          | 28 |

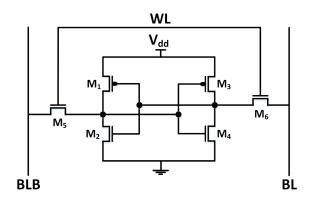

| 2.2  | 6T SRAM cell                           | 32 |

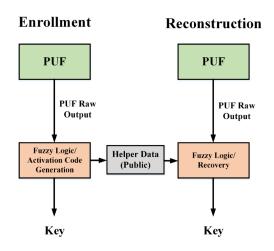

| 2.3  | Enrolment procedure SRAM PUFs          | 34 |

| 3.1  | Dynamic wear levelling                 | 41 |

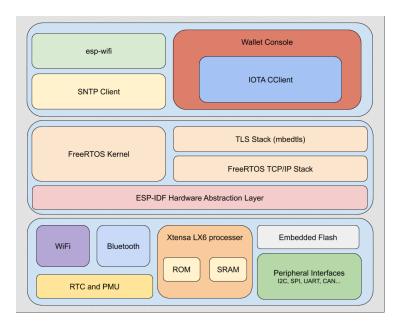

| 4.1  | Illustration of an ESP32 architecture  | 48 |

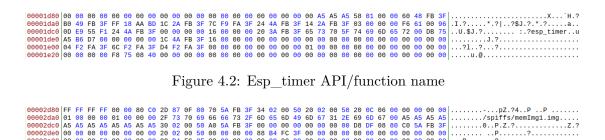

| 4.2  | Esp_timer API/function name            | 54 |

| 4.3  | Snapshot saving pathname               | 54 |

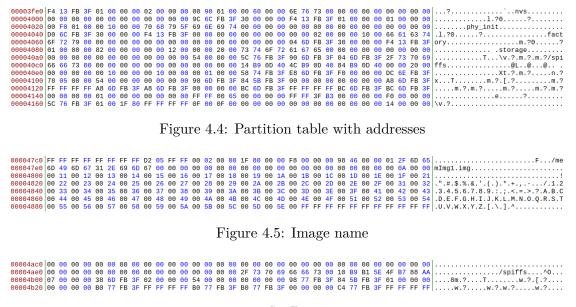

| 4.4  | Partition table with addresses         | 55 |

| 4.5  | Image name                             | 55 |

| 4.6  | Spiffs volume name                     | 55 |

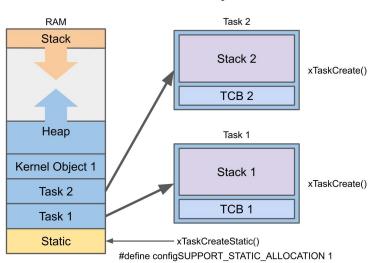

| 4.7  | FreeRTOS memory management             | 56 |

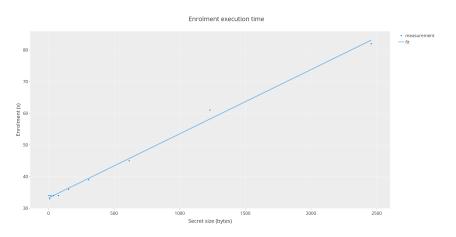

| 4.8  | Enrolment time consumption             | 60 |

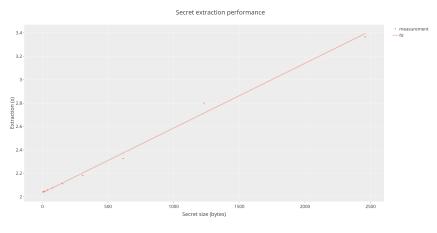

| 4.9  | Extraction time consumption            | 60 |

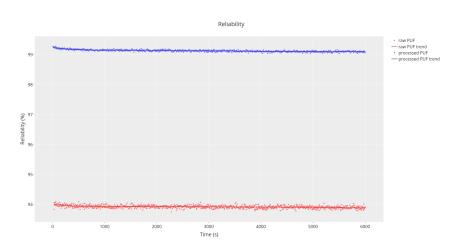

| 4.10 | Reliability comparison                 | 62 |

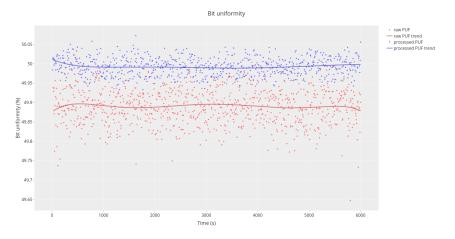

| 4.11 | Bit uniformity comparison              | 62 |

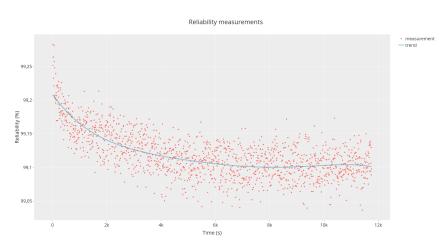

| 4.12 | Long reliability testing               | 63 |

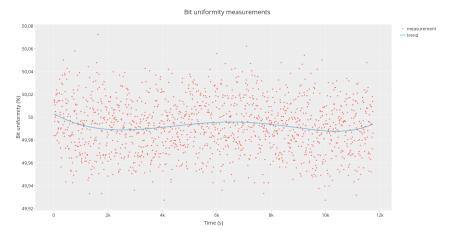

| 4.13 | Long bit uniformity testing            | 63 |

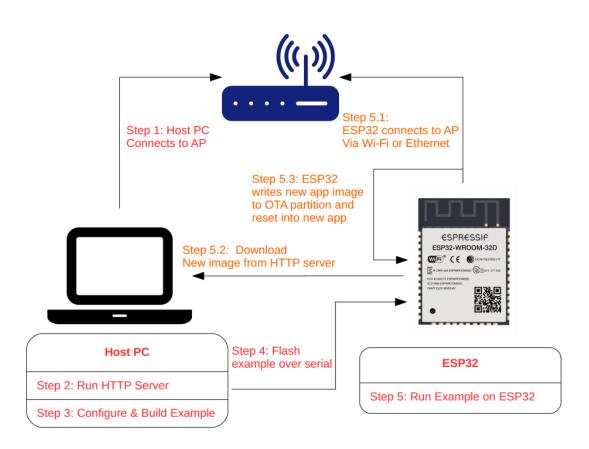

| 4.14 | Basic OTA process                      | 35 |

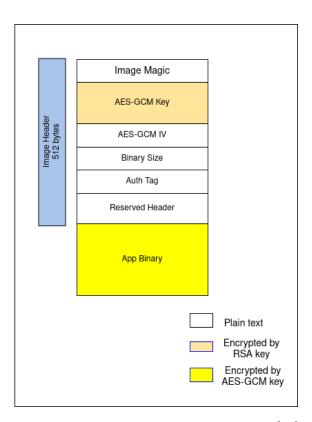

| 4.15 | ESP EIAL firmware format               | 36 |

# List of Tables

| 4.1 | Example of SRAM address layout                   | 51 |

|-----|--------------------------------------------------|----|

| 4.2 | SRAM PUF library performance comparison on ESP32 | 61 |

# Introduction

As per the numerous forecasts predicting the enormous increase in the spending related to IoT solutions, e.g. [1], the everpresent need to keep the IoT devices safe and secure in a consistent, well administered, reliable and scalable manner grows even more, each year. Thus, the Over the Air update comes into play - a process to push updates from a centralised node remotely to possibly a large fleet of IoT devices while also, perhaps, attending to specific device' needs based on its specific state. However, these devices do not always possess the means to perform the required cryptographic techniques, which would make the process much safer. Thus a question arises of whether to somehow compromise on the security while updating such constrained devices or look for more unorthodox OTA process models and alternative means to acquire the required cryptographic assets.

#### Thesis goals

One of the goals of this thesis is to unravel the Over the Air update process and its pitfalls, more precisely which factors come into the play that make it as effective as a standard OTA process is, while also maintaining a good level of security. Afterwards, the threats and the types of attacks that commonly plague various aspects of the OTA process are examined, and typical security countermeasures to such concerns are brought up in contrast. Furthermore, a proposal for an OTA process suited for a resource-constrained IoT device is brought forward to summarise the first part of the work. Also, due to the constrained resources, even some cryptographic assets that play an essential part during the previously described security countermeasures might be missing. Therefore, it is then discussed which ones can be substituted with a PUF that does not impede the used cryptographic techniques.

The second primary goal is to look at the state of the PUF sphere and to explore how they could be implemented on a typical IoT device. The PUF variants that do not require physical intervention are brought up in more detail, and their possible participation during the proposed OTA process is discussed further. Afterwards, the one with the best prospects, SRAM PUF, is further analysed, and a way to implement its use on a resourceconstrained device is outlined.

The last part of the thesis discusses the implementation details of the outlined general library incorporating the SRAM PUF as an asset for performing the desired cryptographic technique. The library's functionality is further tested on an ESP32 device test project, where the PUF properties, such as memory cell stability, reliability and bit uniformity, are examined more closely. Afterwards, a simplified version of the initial OTA update process proposal is applied to an ESP32 device. Finally, it is tested as a proof of concept while replacing a cryptographic asset that some CT would be using.

CHAPTER

# Over the Air update analysis and model proposal

The need for secure, up-to-date software and thus safely operating hardware has been increasingly important in recent years. On most platforms, this goal can be achieved with a process called Over the Air (OTA) update. It can be a relatively straightforward procedure due to entirely unconstrained system resources or preexisting, tried frameworks and systems already in place, such as the ARM platform upon which the Android ecosystem is built [2]. However, currently, the most significant portion of devices connected to the internet is machine to machine, or more commonly, IoT - Internet of Things devices. Moreover, if the circumstances do not change radically, the proportion of IoT devices on the market will increase even more [3].

The massive number of these devices and its further increase also means that quite a few will be parts of critical infrastructures, making them possible attack vectors into large ecosystems or even targets themselves. Thus, keeping them exploit-free and safely operating is a critical concern, so they need to be updated regularly. Until a few decades ago, this was done manually on site almost exclusively. Nowadays, manual updates are still done in specific or very critical cases, where the transfer of the updated software with the help of network and automation is simply not acceptable due to numerous concerns, such as [4]:

- incredibly **small failure threshold** of critical applications as a lot can go wrong during an automated process such as an OTA update

- **update scheduling** with either automated or massively done an update of an IoT product, it might be impossible to find a time slot where it can go offline, requiring it to be done manually

- **potential problems induced by the update** simply updating the IoT device might cause it to be inaccessible from the connected network, making further off-site interaction impossible

• scale - the amount of IoT devices might be an order of magnitude smaller than the amount of effort required to implement OTA (no need to solve OTA security and similar concerns)

However, despite these concerns the OTA brings, it might be a great idea to use it as of the aforementioned increase in the IoT device amounts, during which the use of OTA brings the most benefit [4]. However, the fact that most of these devices are heavily resource-constrained poses a challenge in implementing this process safely and reliably.

#### 1.1 OTA update scheme

Due to the nature of most IoT devices and their resource constraints, there might be a particular OTA scheme in place. However, with the rise of cloud usage [5] the need for at least partial uniformity of this mechanism becomes apparent. With this, there are generally accepted steps that must be adhered to and implemented to have a flexible and scalable IoT solution. To generalise the OTA update process - the IoT device, sometimes referred to as an edge node, will be specified as a client, and the other participant, the one identifying the client, choosing and administering the update, will be called the server (represented mainly by a cloud-like platform).

In general, the OTA update primarily consists of:

- correct **mutual identification** and subsequent authentication between a client and the server providing said update

- ascertain whether the client is **eligible** for the specific update

- **fetching** the updated binary

- the process, generally, should be device *optimised*, caching a few pages at a time or even writing through in the worst-case scenario (in the case of a very small RAM)

- the use of *compression* depends on the device's resources and capabilities

- the downloaded app should be **verified** (correct CA signing, checksum validation/hash comparison, etc.)

- after the update is in accordance with all requirements, the SSBL should branch to the new app on the next reset

- in case of unexpected failure, the old app should be designated as a fallback app, so SSBL can branch to it instead if needed

#### 1.1.1 Provisioning

Not really a part of the OTA process, but it is still needed to have a functional network connection between the client and the server, which is achieved by provisioning. In most cases, it consists of configuring the device to access the local network properly (e.g. setting up WiFi credentials and certificates). For example, on the ESP32 platform, this is achieved by Unified Provisioning [6] (go to /api-reference/provisioning/provisioning.html), which does the following:

- 1. User installs the configuration app, which connects to a target device in provisioning mode, which has some form of beaconing

- 2. The target device either host a WiFi Access Point with a running HTTP server or uses BLE to which the user can connect to

- in the case of an Access Point, there should be security measures, such as WPA2 secured WiFi with a passcode provided with the device, e.g. in the form of a QR code on the device itself

- however, the level of security is flexible and not enforced by the ESP32 framework

- there might be additional configuration installed, or even certificates necessary for the OTA

- 3. After a successful configuration, the device turns off the provisioning interface so it can free resources (e.g. BLE can take up to a fifth of the ESP32's of memory [6](go to /api-reference/provisioning/provisioning.html)) and be more stable (running the ESP32 in SoftAP+STA mode is costly in terms of power consumption and since both use the same radio stack and antenna it makes the communication less reliable)

- 4. The device connects to the local network with the provided configuration

#### 1.1.2 Second stage boot loader

Generally speaking, the booting architecture is mainly based on the two (or more) stage bootloader. This originated on the PC platform, where by default, the first loaded sector was limited to a 512-byte size, thus narrowing down what the bootloader could do, for it must have been limited to this size. Thus naturally, a multi-stage bootloader was implemented, where the only limitation was placed on the first stage bootloader (FSBL), whose only job was to initialise necessary hardware and correctly load the second stage boot loader (SSBL) and execute it correctly. SSBL has no size limitations, so its logic and capabilities can be quite extensive.

On the IoT platforms and specifically the ESP32 platform, it might have been possible only to include a single-stage bootloader. However, it was disadvantageous to do so mainly as a result of FSBL residing in the read-only memory [7]:

- in the case of including the OTA capabilities to FSBL, it would not be possible to update them, thus limiting the lifespan of the device significantly

- if the OTA capabilities were to be granted to the user application, then that would result in

- in the case of Real-Time Operating System, which ESP32 has, it would be problematic to grant the SSBL obligations to the user application, for simply branching to the reset handler of the new, updated application would induce serious issues due to RTOS presence - e.g. other tasks might be running in the background, etc.

- if the branching to the current version of the application were to be done by the FSBL, it would solve the RTOS task issue, as it runs before the RTOS is initiated, but it might become unstable because of the interrupt vector table (IVT) which might be required to be relocated - if a power cycle occurs during this process the device might become inoperable

Having an SSBL solves the abovementioned problems since it resides at a constant address and always contains the current IVT table (an array of pointers to functions, handling faults, system requests, interrupt requests etc.[8]), is not in read-only memory, so that it can be patched later on. Since it is a non-RTOS "program", it can safely branch to whichever application is required [7]. Also, an SSBL that handles most of the OTA functionality can reduce application size by a large margin because neither the new, the fallback, nor any alternative version of the app are required to have the same duplicated OTA and other related code. However, the ESP32 platform has a minimalistic SSBL since the ESP32 OTA process cannot patch the SSBL directly. The reason behind this restriction is that if done and a power failure occurs, it might cause the device to become inoperable [7]. The SSBL patching can, therefore, be only done by uploading the new firmware locally [9].

Concerning the SSBL, the OTA proceeds as follows (with the ESP32 specifics [6](go to /api-reference/system/ota.html)):

- 1. OTA/user portion of the user application detects an available update on the server.

- 2. It gets a new application and places it into the appropriate OTA partition.

- 1. Establishes trust with the server (e.g. PKI usage)

- 2. Downloads the update

- 3. Verifies the update

- 4. Updates the *ota\_data* (similar to the Table of Contents in the figure 1.1)

- 5. Grants control the SSBL by resetting the system.

- 3. After getting control from FSBL, the SSBL detects an updated application from the *ota\_data* and partition table and acts accordingly:

Figure 1.1: General bootloader scheme [7]

- 1. Initializes internal modules, among them, e.g. Flash encryption and Secure Boot, if enabled

- 2. Selects the updated application based on the *ota\_data* partition (in case of the first boot of the new app, otherwise select the fallback app)

- 3. Relinquishes control to either the next stage bootloader or the application/RTOS

To summarise, having a part of OTA logic present during the SSBL initialisation operations can be exceedingly effective since it allows control over the selected application to load and run, thus allowing additional logic to be executed to determine the best course of action. Therefore, if the OTA logic running during the SSBL phase figures out that either the new application either has some internal inconsistency, a wrong version of a component or some other fatal problem, it could even suspend the loading of the said new application and switch to a previous or even the factory version.

Also, suppose it was somehow communicated to the device that the new application has some sort of dangerous behaviour, making it unsafe to use (unsafe operational logic, introduction of a security concern or the developing team becoming aware of an exploit). In that case, it can decide to use a fallback application too.

#### 1.1.3 OTA update transfer, speed and compression

Nowadays, an average application has numerous external dependencies, which are normally not in the developer's control. All these dependencies pose a potential risk that often becomes real and needs to be monitored and acted upon if necessary. Suppose this is taken into account with the fact that a well-operating IoT service should also have regular user code security fixes, feature improvements or even new features frequently. In that case, all of this must be reflected in the frequency and volume of OTA updates. However, if such a system is using the OTA update often and in a large enough volume, then normal operation disruptions due to OTA updates must be taken into account and addressed.

Numerous factors affect the transfer process of an OTA update, some of which is:

- speed of the storage medium, in the case it is a bottleneck

- type of interface that provides the **network connectivity** to the device

- reliability of the network connectivity

- wireless connectivity the strength and quality of the signal

- wired connectivity the amount of noise present in the environment

- limited ability to use the available **network capacity** due to

- device operations e.g. critical action done by the device needing most resources

- limited network bandwidth of the device

- Limited amount of data available to transfer

- the **size** of the updated binary

These factors need to be considered, but most of them are out of scope during software development. However, the size of the update binaries is inherently tied to the development activity. Numerous factors do unnecessarily enlargen the application binary, which does, logically, by the same amount, increase the volume of data the OTA process has to transfer. Among these, the usual offenders are :

- the use of high-level constructs with needless overhead

- using a general solution for a problem instead of a minimal one

- forgetting to remove **unused components** and libraries

- inefficient choice of compiler and its configuration, etc.

However, these are still out of scope for the OTA mechanism to influence in any way. So in the case of the OTA process on the update server getting a binary executable on input, the most direct way for it to reduce the transmitted volume of data would be by compressing it [10]. There are multiple ways of doing so, which involve many quite simple and advanced algorithms. However, in the context of resource-constrained devices, the focus will be on its low hardware footprint and good **lossless** compression ratios.

Numerous compression algorithms offer very favourable compression ratios; however, the main concern in their case would be the system resource requirements and almost gigantic RAM prerequisites for their normal operation [10]. That might not be a problem automatically since lossless data compression is a two-way process, where decompressing is typically quite fast, sometimes even almost **100x** than the compression time [10]. Thus even libraries with unacceptable compression times might be usable on such devices since only decompression would be used, as it would receive already compressed binary data from the OTA update server. Though this is a feedback loop - to decompression library, including the complicated compression methods, included on the device. Thus the library would have to be also included in all binary files that would be received through OTA, potentially negating some of the achieved size reduction.

Nonetheless, plenty of compression libraries are designed for resource-constrained devices that attain good performance during both compression and decompression while having a limited memory footprint. One of such solutions is an open-source specified LZ4 compression algorithm. It is designed for very fast compression and decompression while retaining low resource consumption and favourable compression ratios on binary application data as high as 40% [10]. It might even be possible to store the application binary compressed and only decompress it during SSBL loading the program from flash, thus saving extra device flash memory aside from saving OTA update time. The algorithm's performance is visualised in 1.2.

There are, of course, other ways of reducing binary application size by the OTA process, such as by not transferring the whole firmware at once. Such an example might be by introducing **binary difference data**, that after applying to the old firmware would result in a successful update, in place even, if the device is capable of it [11]. However, that might make using the fallback feature harder to implement and also might involve a lot of additional logic overhead which is never desirable.

So to summarise, depending on the exact hardware specification and the use case, applying a compression function on the sent OTA update might be very interesting. It also might be intriguing to evaluate the decompress costs, mainly time-wise, and potentially save the compressed firmware directly to flash.

#### 1.1.4 General challenges and requirements

For the OTA process not to be just a simple fetch and persist tool that focuses on delivering the update as quickly as possible, it needs to conform to various functional expectations, guidelines and conditions. After fulfilling such requirements, the process should result

#### 1. Over the Air update analysis and model proposal

Figure 1.2: LZ4 compression examples [10]

in more predictable, robust and, most importantly, **secure** and deterministic behaviour. Out of those, the most important ones should be named specifically as[12] [13]:

- A failsafe mechanism after a failed update

- frequent update deployment increases the likelihood of update failure

- actual conditions of the working environment might seriously impact the ability to communicate with the server amidst an update

- A guarantee the device will receive the intended update

- if the same server is serving multiple IoT devices with differing firmware branches of updates, it might result in the incorrect device receiving the incorrect firmware. Even with a failsafe mechanism, this would still result in a waste of device, server and network time. If not implemented, it might even disrupt normal functionalities of the devices since they would be receiving bogus updates not applicable to them

- An assurance that the update truly comes from the expected authority

- if the process is not using methods through which it is cryptographically verifiable that the origin of the update is the intended authority, it could lead to losing control over the whole deployed ecosystem

- A means of update delivery which does not expose its contents to third parties

- if the communication channel is unsecured, there is no guarantee that the concerned data is kept only by the intended parties, which also means that even if an initial connection might have been initiated with the trusted server, the data have no certainty that they have not been tampered with

Most of these are related to cryptographically secure needs of conduct of the OTA process. Therefore, that guarantees a more detailed look at the specific CTs involved while staying aware of the attacks and vulnerabilities that come hand in hand.

#### 1.1.5 OTA update security

For a well-designed OTA process to function properly and also to tackle the already described elementary, functional and QoL requirements, it needs to take security seriously and implement it in a well thought out and systematic manner. Depending on the perspective, an OTA process can be seen as a trust-based process [14] since most security actions have a general purpose of trying to ascertain whether the party and the firmware are both genuine and keeping a **chain of trust** during the whole process in a verifiable manner. However, the OTA process, security-wise, should only be concerned with safeguarding the update process itself and immediately relevant system aspects, not the other facets of operations of either the server or the client[15], since it also needs to be as lightweight as possible.

#### 1.1.5.1 OTA security concerns, threats and risks

There are numerous concerns and risks if one considers the security of an OTA update network, aside from more general security threats of a network-connected device. Therefore, threats related to the process are [16]:

- OTA server-side, where

- the updates are stored and possibly also built, signed, encrypted and otherwise prepared for distribution among the wider population of the IoT device line.

- various security details crucial to the device operations are being stored

- server's private part of the PKI infrastructure used to verify itself and other cryptographic assets used

- IoT device side, the party that

- normally is the one initiating the update process

- is the subject of the update

- the main subject running the OTA routines

Therefore, in order to somehow gain access, to gain classified information or otherwise damage the party operating the parties of whose the OTA process consists, the attacker could target one of those attack surfaces or anything in between them. Thus, the common attacks and threats are:

- MiTM attack generally happens when an attacker either breaches the communication by attacking the protocol itself or using other exploits [17]. In other words, a third party to a normally two-party communication (in the OTA context, the IoT device and the server) inserts itself. The third party generally inserts itself into this communication by either placing a node under their control between the communicating parties or by executing malicious code on one the hardware of one of the parties [17]. The manner of malicious participation of such a third party differs immensely on the objective of the attack, visualised in 1.3. The main ones in the OTA context might be:

- *impersonating* either the server or the device, compromising the whole singular OTA ecosystem

- eavesdropping and stealing the firmware

- *modifying* the firmware

- replacing the firmware with a preprepared binary created by the attacker

- Brute force attacks If preferring the speed, resources or fast development over security and using insufficient security measures, an attacker could try to break such a measure with a brute force attack. E.g. an OTA process using keys that are either too short or of a predictable type that in the end reduces their actual bits of security to a too low amount, guessable by a brute force attack within manageable time.

- Denial of service a classic attack that makes the network resource unavailable to the intended group of users. It is normally achieved by flooding the resource with many requests so the resource cannot properly be used by the legitimate group of users[18]. In the context of an OTA update process, that would mean mimicking the IoT devices and flooding the OTA server with superfluous requests.

- Side-channel attacks harnesses various signal emissions and other possible information leakages that the device might possess. There are multiple attack models, such as SPA, DPA, CPA and EM [19]; they normally require some knowledge of the system and the platform by the attacker

- attacker must have access to the device

- possible to retrieve virtually any resource, maintaining security with which the device works during runtime; requires a high degree of preparedness by the attacker

Figure 1.3: Common OTA security threats [16]

#### 1.1.5.2 Security measure inquiry

For the sake of counteracting the described attack vectors and reducing the possible attack surfaces, there have been proposed and currently are in use numerous approaches, techniques and even philosophies of conduct. Among those, the ones relevant for use on the IoT device-side during the OTA process might be:

- Secure boot In a well-protected IoT device, the user application code should be routinely verified and authenticated whether it has not been modified or hijacked by an attacker while stored in the flash memory. The best moment to do this would be during the booting process. More specifically, the SSBL should have a routine that does at least part of the process. This process is generally called Secure boot [14] and, as such, is a good addition to an OTA process since it might counter some threats and issues that come with using firmware from a remote source. In terms of the attack surface, it protects the IoT device directly in the case the firmware was somehow hijacked and redirects the attacker's attention to the SSBL or some other component doing the checks.

- **Poor security policy** Using industry best practices for key lengths and employing valid cryptographic technique selection is also paramount. Not exactly conforming to the security standards and choosing an inadequate combination of cryptographic assets or just cheapening out on the bits of provided security by the chosen keys just to save some resources might [16] result in numerous vulnerabilities. To be specific, e.g. choosing triple DES might be a poor decision since, according to NIST [20], it is a deprecated standard with potential vulnerabilities to, among them, brute force attacks in the near future, since it has a 112 bits long key with only 80 bits of actual security due to its inadequacies. Therefore, giving up bits of security in favour of some performance increase is inadvisable and should be avoided.

#### 1. Over the Air update analysis and model proposal

- Authentication The way of proving one's own identity is a powerful tool and quite necessary in the situation of deciding whether to trust the firmware provided by another party or not. By authenticating, if done correctly, it is being cryptographically proven that the party declaring itself in a certain role does, in reality, have the necessary verifiable cryptographic identification. Demanding successful server authentification as a prerequisite to subsequent firmware transfer during the OTA update negates some attack vectors, mainly a few MiTM attacks. As per authentication types, there are three main categories:

- Centralised three-way administrator registers the IoT devices with the main authority, assigning them valid certificates. After that, the authority facilitates secure handshakes between the registered parties [21]. As a plus, the devices do not have any certificates on them. Not relevant to most OTA processes.

- Distributed two-way i.e. mutual authentication. The device and the OTA server ought to have each other's public certificate installed, with the update commencing only when both the device and the server can authenticate each other [21]. However, managing that many more certificates and overhead on the device might not be feasible.

- Distributed one way only one party to the communicating pair is being authenticated; thus, in OTA, only the server has to prove to the device that it really is the OTA server authority. Therefore, only the public certificate of the OTA server needs to be distributed amongst the devices eligible for the updates [21]. However, a case could arise that an uneligible device might take hold of the certificate in the case of unprotected firmware might mean a serious leak, therefore requiring further measures.

- Securing of the firmware binary on an otherwise maximally secured ecosystem, where all parties are authenticated and communicate securely, the need for extra security just for the binary would not be extra useful outside of redundancy purposes. However, it is a powerful tool on, e.g. *Distributed one-way* authentication models, where the device receiving the update would not be authenticated. In this case, in order to not leak the firmware, it needs to be cryptographically ensured that only the right party can use the firmware. Also, just signing the firmware instead of doing full authentication of the server would not suffice since an attacker could hijack or otherwise mimick the OTA server role and perform a retransmission attack. Alternatively, even worse, send an older version of the firmware with a potentially unfixed exploit for it to harness later on.

- Securing communication channel after authenticating the parties securely, the goal should be to agree on a session key in a similarly secure manner with whose help will the device and the server push their update-related communication through. A safely established, encrypted channel is paramount in keeping the updated firmware safe from the eavesdropping of other malicious parties. In this case, the TLS protocol is the main representation, which serves as a transparent layer

for other communication protocols [22]. DTLS can sometimes be found on really constrained devices, trying to provide a similar level of security as TLS but with a significantly lowered overhead.

- Side-channel attack Another serious issue is the ability of an attacker to use a side channel to gain normally secure information or even compromise the device. This attack vector is a tough one to protect against since an IoT device is fundamentally a relatively cheap platform, making the application of any more advanced measures financially inadvisable for the solution to make sense still. However, there are still actions that can be undertaken[19]:

- software side

- \* device operation, ideally, should be independent of data number of clock cycles randomised or uniform to not leak operation timings

- $\ast\,$  avoid reusing the keys

- \* power consumption not dependent on instructions executed

- hardware side

- \* use of Physical Unclonable Functions as CTs

- $\ast\,$  correct shielding to mitigate leaking data through electromagnetic radiation

- Flash encryption another way to counter various side-channel attacks is by safely encrypting the persistent flash storage. In the context of an IoT device, the only efficient way to do so is to use a symmetric key, and doing just that creates a problem of where the key would be stored. One such way might be having a hardware solution securely generating the said key and storing it in the form of an HSM, e.g. inside a chip on eFuses that is inaccessible to the CPU. Only the hardwarebased encryption/decryption engine has the access, thus making the attacker have to use a more drastic invasive type of side-channel attack to access the eFuses and recover the key [23].

#### 1.1.5.3 Cryptographic techniques in OTA security measures

When mentioning cryptography, nowadays, is commonly understood as a science centred around studying various techniques and methods with whose help it is possible to secure disparate types of data and communication. It is also closely related to cryptanalysis, whose study of methods of obtaining the protected information without the proper means of access, i.e. it is challenging the methods of cryptography. As for these cryptographic techniques, they are well-defined, deterministic algorithms whose operations should take adversarial behaviour into account, or their execution should be meant to counter it [24]. Ultimately, these CTs should have the pursuit of the following principles as their goal[24]:

• **Confidentiality** - only the authorised subjects should be able to view the protected information

- **Integrity** the protected information should be either non-modifiable or easily detectable, e.g. during transit, storage etc.

- **Non-repudiation** that no communicating party should be able to deny that they have sent or received the information in question

- Authentication the identity of a communicating party can be confirmed

Therefore, these CTs use, in general, cryptographic methods/algorithms that in some way or form use cyphers, which is an algorithm used for encrypting and decrypting data. These techniques can be grouped into several categories:

- Symmetric cryptography an encryption system whose purpose is to encrypt and decrypt data. The system uses only one key, which is relatively fast, but both parties need to have the knowledge of the said key in order for the system to work. A typical representative nowadays in the IoT sphere is the AES, with key sizes of 128, 192 and 256 bits [24].

- commonly used as a session key of a TLS session while solving the key exchange problem inherent to symmetric cryptography - more standardised way of establishing a safe OTA update communication channel

- used as the main means of encryption in hybrid cryptography systems therefore, OTA firmware encryption

- also utilised by most flash encryption approaches to further secure the OTA update firmware

- Asymmetric cryptography also an encryption system for data encryption purposes. However, it is based on key pairs, typically of which one is **private**, and one is **public**. Both can be used for encryption and decryption. It is quite slow but has solved the key exchange problem [24].

- commonly used for safe establishing of a TLS session solves the authentication of the server or both communicating parties

- used as a basis of PKI cryptography, certificates and authentication techniques

the chain of trust building

- use in hybrid cryptography, e.g. OTA firmware encryption

- used for firmware signing

- **Cryptographic hash functions** in contrast to normal encryption algorithms, proper hash functions should be a one-way function, where the original data should not be recoverable.

- also utilises encryption, with the difference in not persisting the cypher texts of each block but just using it as an IV during the next round, with the hash output being the last cypher block

- firmware signing, device verification and identification

#### 1.2 Resource-efficient OTA update model

The chapter will describe the common feasible architectural approaches the OTA process can take while opting for one of them, will list the relevant functional obligations which a practical, robust, and secure OTA mechanism should strive to fulfil and also the strategies describing how to get these obligations fulfilled and finally, a description of the proposed OTA model in detail.

#### 1.2.1 OTA architecture

There is no one size fits all type of OTA architecture, evermore due to the very different capabilities and granularities distinct IoT architectures have in the field. For example, in a use case where the amount of IoT devices per location is in the realm of tens or even hundreds with possibly very low computing power and resources, maybe even combined with a requirement for spending much time during deep sleep to conserve power, would have to approach the OTA update problem in a very contrasting manner than a use case with one deployed device per customer which is more autonomous resource-wise. Thus these dissimilar dilemmas could be categorised into three main architectural update classes [12] [25]:

- 1. Edge to cloud OTA a single network-connected device with internet access that is solely responsible for itself. Its capabilities include the ability to receive and apply an update from a remote server by itself.

- 2. Gateway to cloud OTA an internet-coupled gateway that manages a fleet of local edge devices. Capable of receiving the update from a remote server, same as the first architecture case. The update might be only intended for itself or the hosting environment.

- Single point of failure in the gateway since the devices rely on the gateway being up to date.

- 3. Edge to gateway to cloud OTA an internet-coupled gateway that manages a fleet of locally connected edge devices. Capable of receiving the update from a remote server, same as the previous architecture cases. However, the update might be either intended for itself, the hosting environment, the devices that are being managed or some kind of a subset of these devices, basically capable of attending to a heterogeneous group of devices and also acting as an update dispatcher for the said fleet.

- Since the devices being managed are able to receive updates, having the gateway fail might not mean update failure overall.

- Useful where the internet access is easier to set up for a single device, which would manage it for the other minor ones. It might be very useful in conditions where connecting the whole fleet directly to the internet would lead to a risk of deteriorating the connection or security concerns.

While each of these mentioned OTA update architectures has its uses, the proposed model will be based on an **Edge to Cloud** OTA architecture since it allows more time spent on the challenges of a specific device acquiring the update directly and its interactions with the remote server, having to solve all the security-related tasks too.

#### 1.2.2 Requirements and implementation strategies

As per the past section describing requirements, there are numerous qualitative features to an OTA update that need to be included in order to design a robust process.

Some sort of a **Failsafe mechanism** is practically a fundamental property since, over the course of operation, the OTA process is bound to enter a state where the update either cannot process or has been corrupted. Thus there needs to be a well-defined procedure describing how to approach such situations. Interestingly, OTA possessing a single attribute changes that - **transactionality**.

If the OTA process is transactional in nature and thus supports something of a commit and rollback operations, it:

- *improves* the update process reliability; the update is either "committed" as the currently active version or rolled back to the last good known one in case of any kind of an error

- *rollback feature* can also be used in other circumstances, i.e. in case of a new known exploit introduced in a new update in this case, the central node administering the updates can mark the vulnerable version as faulty, and the devices will revert to a safe older version if possible as a quick fix

- however, this might be a contested feature safety-wise if an attacker finds a way to exploit it, e.g. the old version contains unfixed security exploit, it might lead to the device willingly setting up itself for a future attack

Henceforth, having the OTA process with these properties could be characterised as having ACID attributes. As a result, it can be considered robust and capable of enduring errors during multiple points of use while retaining the functioning state of the application.

**Versioning** is a helpful, inexpensive tool that helps with achieving numerous aims. Among them is:

- to be able to tell whether the device is up to date or runs an unsafe version there needs to be some way to keep track of versions

- also, the versions should be able to track other aspects as well, such as whether or not the current version was successfully run, has a known exploit present, uses outdated or unavailable resources or is outright obsolete and should not be used at all

By itself, it might not exactly fulfil any requirements, but it might come into effect, e.g. during rollback operations while choosing the application with a version preference.

Due to OTA update being a resource and time-critical process, the inherent requirement is to use as little processing time as possible. Therefore, having the need to download and process a full update might be, in some cases, detrimental. So **differential update** approach might:

- *save* significant amounts of memory and reduce the time, power and bandwidth to fetch the update desirable in deployments with low-powered devices with bad downlink connections.

- will require more *system resources* to maintain transactionality and keep versions up to date

- if the updates are sufficiently different, it mostly degrades to a normal approach while also retaining the differential overhead

Though using the differential approach implicitly might not be the way to go since it heavily depends on the specific use case and update data nature, therefore having it as a selectable feature would be preferred.

## 1.2.3 Proposed OTA process

After outlining the qualities a reliable and secure OTA update process should have in the preceding sections, the moment has come to choose and narrow down which properties and features should such a procedure, mainly focused on serving resource-constrained devices, possess. Due to this constrained nature, the proposal will move incrementally, only adding the essentials that will guarantee secure operations.

Therefore, the main execution steps, and the exact client obligations, of an Edge to cloud-type OTA are

- connecting to an AP

- establishing communication with an OTA server

- downloading the new firmware

- applying the received OTA update

This very basic OTA process, however, does not contain any security features. Thus firstly, both the two communicating parties and the firmware that is being transferred are not guaranteed to really be the requested parties/resource. This process is vulnerable to, amongst others, a MiTM attack due to a lack of server identity authentification and unsecured channel communication due to unsafe HTTP usage.

Furthermore, secondly, in the case of a malicious device of a third party, which is not the intended recipient of the update, it would be possible for an attacker to obtain the updated firmware itself, potentially undermining the whole subject deploying it. Thus by neglecting the IoT device authentication, the OTA process becomes a potential victim of a spoofing attack.

In order to have a secure OTA process, it is vital to counter these risks. They can be countered by

- introducing public key cryptography through certificates, so it is possible to authenticate the server

- private certificate is known only to the server. With its help, the server authenticates itself after a request

- public certificate is known to everyone and used by the device requesting the download to prove the safety of using the offer by the said server

- establishing a secured connection with the authenticated server, e.g. through a transparent TLS layer

- done only after the server had been authenticated

- encrypting the firmware sent by the server, if the OTA logic on the device is capable of decryption, of course

The authentication that would be done according to the preceding points would be only one way, that of the server to the device. Of course, the authentication of the IoT device could be useful too and could be achieved through another pair of public and private certificates, but that would introduce several problems such as

- having to store the private certificate on the device itself, either alongside or instead of the firmware decryption key

- safely generating and deploying a considerable amount of private certificates while storing the public certificates all on the server, which in a system where the amount of IoT devices is an order of magnitude larger than the OTA server participating hardware, could easily become unmanagable

- not necessarily replacing the guarantees provided by the firmware encryption

Therefore transferring the problem of authentication of the device out of the PKI cryptography realm to a simple requirement of knowledge of a secret necessary for the use of the firmware. This might probably be more resource-friendly as well, since the firmware would have to, in the case of failure of other components, be somehow cryptographically secured, either way, thus creating a kind of redundancy. Therefore writing off the PKI authentication of the IoT device to the server would have a twofold effect:

• *reduce* the workload of the OTA server, which would not be obliged to review each client's authenticity against the specific public certificate of the said device

Figure 1.4: AES vs RSA encryption speed comparison [26]

• *increasing* the overall OTA process speed, for not depending on an extra exchange between the server and the device means that the update can be applied sooner

As for the mentioned **encryption of the firmware**, which is the subject of the whole OTA process, it is crucial to have an efficient scheme in place. By default, the simplest scheme would be to, once again, use public-private key pair, encrypting the firmware on the server by the public key and decrypting it by the private key on the device. However, asymmetric cryptography is terribly inefficient if working with any data larger than session information or of similar small data volume, as presented in the figure 1.4, with demonstrated key length of 56 bits for AES and 1024+ for RSA [26].

Since the application binary is in the realm of hundreds of thousands of bytes, this would practically make the whole OTA process unusable. Hence there are potentially two solutions to this problem [27]:

- distribution and storage of a single symmetric key per device

- distribution is a nontrivial problem

- needs to be securely stored on both ends

- therefore, inherent problems with device scaling

- hybrid cryptography both the symmetric and asymmetric keys used

- only the asymmetric key needs to be distributed directly, for which asymmetric cryptography is designed

- only the private asymmetric key needs to be stored

Even though in terms of performance, the solution with the symmetric key would have a slight edge since the hybrid solution ought to decrypt a small amount of data by an asymmetric key first, other than that, the symmetric key solution would provide no

| Security<br>Strength | Symmetric<br>Key<br>Algorithms | FFC<br>(DSA, DH,<br>MQV) | IFC*<br>(RSA)    | ECC*<br>(ECDSA,<br>EdDSA, DH,<br>MQV) |

|----------------------|--------------------------------|--------------------------|------------------|---------------------------------------|

| 128                  | AES-128                        | L = 3072 $N = 256$       | <i>k</i> = 3072  | f=256-383                             |

| 192                  | AES-192                        | L = 7680 $N = 384$       | <i>k</i> = 7680  | <i>f</i> = 384-511                    |

| 256                  | AES-256                        | L = 15360<br>N = 512     | <i>k</i> = 15360 | <i>f</i> =512+                        |

#### 1. Over the Air update analysis and model proposal

Figure 1.5: AES vs RSA security strength[28]

real advantage, even to the contrary. Unless the device was using the same symmetric key during its whole lifetime, it would need to perform a symmetric key distribution, which by itself cannot be done and needs the help of asymmetrically based cryptography. Also, the need to store a key on the server's end might also prove fatal since the server would have to keep large records of deployed devices with corresponding symmetric keys safely stored in an HSM. Hybrid cryptography solution has none of those drawbacks.

**Hybrid cryptography** [27], where the practicality of an asymmetric key and the speed of a symmetric key are both retained, is critical for resource-constrained platforms. More specifically, the schema follows the model of public key cryptography, where the encryption can be done by anyone possessing the public key, i.e. the authenticated OTA server in this case, but the decryption can be only done by the party with the private asymmetric key, which is only the trusted device with the said key. However, the main difference if compared to a pure regular cryptographic model using public/private key pairs is that the only asymmetrically encrypted information is the symmetric key. After decrypting the symmetric key, the device is automatically authenticated and implicitly authorised to use the decrypted symmetric key in order to obtain the plaintext [27], in this case, the updated firmware.

However, to maintain security, the server needs to randomise the *initialisation vector* of the symmetric key so that no two binaries will be of the same encrypted value, even if they are equivalent in plaintext [27].

Finally, the question of secure storage of the private keys/secrets - in the current form, the proposed OTA update model uses only one private key on the side of the IoT device, and that is the asymmetric key used for retrieval of the symmetric key of the transferred binary. Therefore, the IoT device has to have some kind of HSM capable of safely storing the said asymmetric key. Also, according to NIST [28], the recommended RSA equivalent in terms of current perceived security strength to a commonly used AES-128 is an RSA of the length 3072 [28]. This is visualised in the table 1.5.

Storing such a key might be problematic for some IoT devices, so exploring alternative options of safely retaining and extracting such a key, such as **PUFs** using from some

unique device property, might be very convenient and useful. More specifically, the main secrets that have to be securely stored on the device during the proposed OTA process are the asymmetric key for firmware decryption and, in the case of mutual authentication, also the device's private certificate. If the device does not possess an HSM that could also operate safely in tandem with the normal device operations (an external HSM module might be unsafe for side-channel attacks), the SRAM PUF really might be the answer since it is already integrated into the typical device and it also provides good statistical properties to go ahead with either storing such a key or even deriving it. However, it all depends on the specific device, the SRAM quality, the manner of use and such, thus needing to be further investigated in such regard.

## 1.2.4 Usage of a PUF and CTs in OTA

As was already stated, there are numerous types of attacks against the cryptographic techniques employed by an IoT device during the process of updating its firmware. So therefore, in reference to the proposed OTA model, the following will be a listing of such CTs that are paramount to the process:

- PKI certificates, or more specifically, asymmetric cryptography

- Firmware encryption, therefore, hybrid cryptography

The listed CTs are the two main pillars of the proposed OTA process security. The first point guarantees the authentication of the OTA server and the subsequent creation of a secure communication channel. The second one guarantees the confidentiality of the subject of the communication, the OTA firmware. It also implicitly authenticates the device if it is able to decrypt it and consecutively authorises it for its storage and use.

#### 1.2.4.1 Brief analysis and attacks on the CTs

As hybrid cryptography has been already looked upon in the previous chapter, let us examine the PKI certificate.

Firstly, **Public Key Infrastructure** is a framework, a two-key asymmetric cryptographic system, that does one main thing - it enables its users the use of secure information exchange through its certificates [29]. The reasoning behind the choice of the keyword of *Infrastructure* is mainly due to the fact that it encompasses all the numerous various factors that make this exchange possible. Among them, the following certainly belong to [29]:

- hardware solutions designed to support cryptographic operations

- software solutions harnessing the said hardware securely

- policies that are in place that, e.g. dictate how the specific operations should unfold

- methods and entities needed to make the whole system work. Their responsibilities might involve certificate

- distribution

- verification

- revoking

The certificate is an asymmetric key bundled with other information related to the subject so that the authentication process can take place. Also, the mentioned entities certainly include[29]:

- Certification Authority a trusted member of the PKI. It is the root of trust of the specific certificate chain since it possesses the root certificate only for its use. The main service it provides is authentication.

- **Registration Authority** permitted by the main CA to perform some of its duties to distribute the workload. Mainly issues specific certificates for specific groups.

- Certificate store and database first used as a means to store certificates on an end-user, e.g. an IoT device; the other is used to track details about the issued certificates, also used for later certificate revoking.

#### 1.2.4.2 Vulnerabilities to attacks

The main issues with the **PKI** are not related to the asymmetric cryptography directly (though it might come into question in the future, with the emergence of systems trivialising the underlying cryptographic algorithm) but more to the concept of the chain of trust. Therefore, an attacker would certainly find more success targetting the weakest link in this chain. After compromising the CA, every certificate issued by this CA becomes unsafe and exploitable by the attacker, thus dooming the whole specific PKI-based system [29]. So in the context of an OTA process, there is not much it can be done other than choose the CA issuing the certificates used for authentication during the update carefully. Moreover, again, in the IoT and the OTA context, using self-signed certificates might be actually a completely fine idea.

As for the issues with the *hybrid cryptography*- in the case of correct usage, they all depend on whether the asymmetric key used to encrypt the symmetric key has been kept safe by the device. Therefore, this degrades to the already described issues with safely storing a secret on a device, which might be a real problem if the device lacks an HSM or any other tools to keep the stored private key securely stored.

#### 1.2.4.3 Viable CT to be replaced

As per the already discussed threats, only the securing of the private asymmetric key could be somewhat considered for replacement or implementation on devices without the needed cryptographic infrastructure.

More broadly, constrained devices often have low overall capabilities and hardware tools eligible for implementing such security measures, e.g. hardware support for AES encryption, no HSM present and etc. Nevertheless, what they almost always do have is an SRAM - thus, one might be able to implement sufficient measures and CT with the help of the SRAM-based unclonable function. More specifically, since a device often needs to store an asymmetric private key, whether for authentication, data signing or firmware encryption purposes, placing such a crucial secret in unprotected flash is unacceptable. Thus having an SRAM-based PUF to either derive the key itself or enrol it after being provided by the admin and store an auxiliary noncritical structure in flash memory that only with it and the help of the PUF the key can be recovered. Therefore an SRAM might be the way to go in the case of storing private keys critical to the OTA update process.

## 1.2.5 Conclusion

So to finalise - a draft of a lightweight OTA update process was proposed. It highlights the necessary security features that such a process should harness, mechanisms like server authentication, firmware encryption and etc. Due to its focus on constrained devices, the process does not implement additional features discussed before, like compression, or it does not mention the use of transactionality and other reliability features. However, this is of little consequence since they could always be implemented afterwards, but to approach security in this manner would be a whole another issue. Also, as of the constraints such devices often have, usage of a PUF in some capacity as a CT might be very beneficial and allow the device to be more secure with more resources to spare.

Chapter 2

# **PUFs and IoT devices**

Even if an average IoT device wants to operate as securely as possible during all times, it also has to maintain its operational requirements, thus, in most cases, sacrificing something security-wise. Therefore, in the case of devices that already are very resource strained or lack the assets to perform the needed cryptographic techniques, it might be very lucrative and potentially groundbreaking to look at the options a PUF can provide.

# 2.1 PUF principles, properties and definitions

Every valid PUF needs to possess some quality that is unique and is a source of entropy - no other device, even if being of the same manufacturing line or type, should have the same manner of such quality - it should behave like a fingerprint [30]. At least during normal circumstances, this quality should not be reproducible by any physical means, such as deliberately constructing a device imitating such quality or by modelling the behaviour artificially.

In order to somehow harness this quality, there ought to be some logic layer that, based on input, produces some output based on the specific quality.

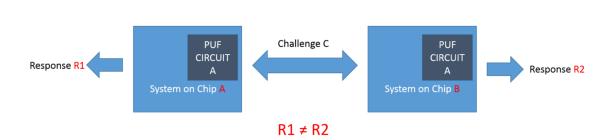

In other words, let challenge C be a sequence of bits that the PUF circuit accepts as an input. The response R will be the output generated due to the underlying quality and that of the challenge. Such a pair is thusly defined as CRP - **Challenge Response Pair**. Also, even if two chips have similar PUF-like qualities and respond to the same challenge, their PUF responses cannot be the same. Therefore, there should not exist a pair of such devices where the response is equal, as it is visualised in the 2.1 figure [30] [31].

Thus, there are several properties a proper PUF has to possess, such as [31]:

- a CRP should be **random**, with no two differing challenges providing the same response

- modelling from a set of CRPs should not be easily achievable

- low attack multiplicity actually extracting a CRP by an attacker should be impossible to repeat at more than one-time instance

## 2. PUFS AND IOT DEVICES

Figure 2.1: PUF principle [30]

- has to satisfy SAC - Strict Avalanche Condition - the probability of the output bit being flipped should be 50% if the input bit has been flipped

If considering the amount and the manner of CRPs a PUF can actually provide, the PUFs can be divided into three categories[30] [31]:

- **weak PUF** linear increase in PUF circuit size results in a linear gain in the volume of CRPs

- **strong PUF** linear increase in PUF circuit size results in an exponential growth of the CRP amount

- **controlled PUF** is based on a strong PUF in the background, with a front end consisting of control logic.

Due to the described nature of the PUFs, they are often used as authentication devices and in other related roles during secure communications [30].

Having a PUF primitive might be especially advantageous on resource-constrained devices, which might lead to an added ability to authenticate or securely communicate while not having any other cryptographic assets capable of doing so. So to satisfy such devices, there needs to be a specific authentication protocol based on the CRP phenomenon. Such a universal protocol is composed of [30]:

- Enrolment phase

- 1. The server with a database is connected to the device with PUF through an interface directly might be before device deployment in a controlled environment; therefore possible to focus on speed

- 2. The server floods the device with all the possible challenge requests and records the relevant responses

- 3. Finally, the database is populated by, ideally, all the CRPs the PUF potentially can produce.

- Authentication phase

- 1. The enrolment is a prerequisite the server has a table or a database populated with all the CRPs.

- 2. To authenticate the device, the server sends a challenge for the device PUF.

- 3. If the response matches the specific one from the CRP pair in the DB, the device can be deemed authenticated.

The described authentication protocol favours the *strong PUFs* very heavily since, with their larger volume of CRPs, it does not matter whether a few are published publically or not. *Weak PUFs* on the other hand, are a lot less suitable for this since they often have only a few unique CRPs, sometimes even only one. They, however, might be a lot more suited for replacing other cryptographic techniques, such as deriving keys [31].

# 2.2 PUF threats and attack vectors

Since an essential feature of an IoT device is being able to operate in various conditions, it also means they have to be exposed to numerous threats too. Aside from direct physical attacks to communication disruptions and other malicious manipulations of the device's operating conditions, the device can face direct threats to the security provided by the PUF. Of course, a weak PUF faces quite different security threats than a strong PUF since they are mostly implemented to provide for or even implement different cryptographic techniques or assets. Thus in the context of strong PUFs, with CRPs being published between the two communicants [30]:

- MiTM attack no physical access

- malicious actor can hijack or otherwise get the knowledge of certain exchanged CRPs. Afterwards, the attacker can either perform replay attacks if the implementation is vulnerable or try to, piece by piece, reconstruct a model of the PUF with, e.g. ML

- Side Channel attack requires physical access

- Categorisation by the invasiveness

- \* **invasive** damaging the device in order to access crucial components requires precision and complex equipment - should result in PUF becoming inoperable

- $\ast\,$  **non-invasive** extract information by exploiting operational data of the device

- Categorisation by type of activity

- \* **passive** purely observatory in nature

- \* **active** tampering with the device operations, e.g. supply voltage control by the attacker