CZECH TECHNICAL UNIVERSITY IN PRAGUE Faculty of Electrical Engineering Department of Measurement

Master's Thesis

# Design of electronic fuse emulator with advanced functions

Bc. Josef Burda Cybernetics and Robotics

Supervisor doc. Ing. Jan FISCHER, CSc.

Prague 2022

## MASTER'S THESIS ASSIGNMENT

### I. Personal and study details

| Burda Josef                       | Personal ID number:                                                 | 466347                                                                                          |

|-----------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Faculty of Electrical Engineering |                                                                     |                                                                                                 |

| ute: Department of Measurement    |                                                                     |                                                                                                 |

| Cybernetics and Robotics          |                                                                     |                                                                                                 |

| Cybernetics and Robotics          |                                                                     |                                                                                                 |

|                                   | Faculty of Electrical Engineering<br>ute: Department of Measurement | Faculty of Electrical Engineering<br>ute: Department of Measurement<br>Cybernetics and Robotics |

#### II. Master's thesis details

Master's thesis title in English:

Design of electronic fuse emulator with advanced functions

Master's thesis title in Czech:

#### Návrh emulátoru elektronické pojistky s pokro ilými funkcemi

#### Guidelines:

Design and realise a device that will emulate new functions of a power electronic fuse with integrated protection functions for automotive use. To emulate these new functions, use an automotive grade MCU from the SPC58xx family. Design the hardware and the software of the device. When designing the emulator pay attention to the possibility of integrating the emulator into a car's power distribution system. Reaction time requirements to certain signals (e.g., emergency stop) should also be considered. During testing focus on carmaker requirements and functional safety.

#### Bibliography / sources:

1. STMicroelectronics: RM0403 Reference manual SPC58 2B Line, Rev 7, 2021

2. RIBBENS, William B.: Understanding automotive electronics. 7th ed. ELSEVIER, ©2012, ISBN 978-0-08-097097-4 3. VOLKSWAGEN, VW 80000 Electric and Electronic Components in Motor Vehicles up to 3.5 t General, Requirements, Test Conditions, and Tests, 2017

4. Vít Záhlava: Návrh a konstrukce DPS, Ben 2010

Name and workplace of master's thesis supervisor:

#### doc. Ing. Jan Fischer, CSc. Department of Measurement FEE

Name and workplace of second master's thesis supervisor or consultant:

Date of master's thesis assignment: **31.01.2022**

Deadline for master's thesis submission: 20.05.2022

Assignment valid until: by the end of summer semester 2022/2023

doc. Ing. Jan Fischer, CSc. Supervisor's signature

Head of department's signature

prof. Mgr. Petr Páta, Ph.D. Dean's signature

#### III. Assignment receipt

The student acknowledges that the master's thesis is an individual work. The student must produce his thesis without the assistance of others, with the exception of provided consultations. Within the master's thesis, the author must state the names of consultants and include a list of references.

Date of assignment receipt

Student's signature

## **Declaration**

I declare, that I have written this thesis independently, with help from the thesis supervisor doc. Ing. Jan Fischer, CSc. and that I have used only the literature quoted in the thesis. I further declare, that I have no objections to reproduction or presentation of this thesis or it's parts with consent of the faculty.

In Prague 20.5.2022

Bc. Josef Burda

## Acknowledgement

I would like to thank everyone that offered me support when writing this thesis. I would especially like to thank my supervisor, doc. Ing. Jan Fischer, CSC., for his patient support and guidance throughout the project. Thanks also go to all of my colleagues, who were willing to discuss ideas and solutions to problems. Last but not least, I would like to thank all of my family members who supported me throughout my life.

## Abstract

The goal of this thesis is to design and realise an emulator of advanced functions of an electronic fuse currently in development. The emulator is built around an already existing electronic fuse device. The additional features are emulated by a microcontroller. Most important of these feature is the ability to control and diagnose the electronic fuse via SPI bus. An analysis of the parameters of the future device was performed and based on that the hardware and software was designed and implemented. In Application Validation measurements were performed on the finished device to validate that the requirements were met and determine it's parameters.

Key words: electronic fuse, automotive, emulator, microcontroller

## Abstrakt

Tato práce se zabývá návrhem a realizací emulátoru pokročilých funkcí elektronické pojistky, která je ve vývoji. Emulátor je založen na již existující elektronické pojistce, která těmito funkcemi nedisponuje. Pokročilé funkce budou emulovány pomocí mikrokontroléru.

Mezi nejdůležitější z těchto funkcí patří možnost ovládat a diagnostikovat elektronickou pojistku prostřednictvím rozhraní SPI. Byl proveden rozbor parametrů budoucího zařízení, na jehož základu byl navržen a relizován hardware a software emulátoru. Na dokončeném zařízený byla provedena validační měření, jejichž cílem bylo ověřit zda byly splněny všechny požadavky.

Klíčová slova: elektronická pojistka, automotive, emulátor, mikrokontrolér Překlad názvu: Návrh emulátoru pokročilých funkcí elektronické pojistky

# Contents

| 1        | Intr | oducti                          | on                                                     | 1        |  |  |

|----------|------|---------------------------------|--------------------------------------------------------|----------|--|--|

| <b>2</b> | Ass  | ignmei                          | nt analysis                                            | <b>2</b> |  |  |

|          | 2.1  |                                 | tor design requirements                                | 2        |  |  |

|          | 2.2  | Emula                           | tor hardware design                                    | 2        |  |  |

|          | 2.3  | Emula                           | tor software design and implementation                 | 3        |  |  |

|          | 2.4  | Testin                          | g and validation                                       | 3        |  |  |

| 3        | Intr | oducti                          | ion to fuses                                           | <b>5</b> |  |  |

|          | 3.1  | Fuses                           | in automotive applications                             | 5        |  |  |

|          |      | 3.1.1                           | Types of faults in power distribution systems          | 6        |  |  |

|          |      | 3.1.2                           | Fuse parameters                                        | 6        |  |  |

|          |      | 3.1.3                           | Fuse selection process                                 | 8        |  |  |

|          | 3.2  | Introd                          | uction to electronic fuses                             | 10       |  |  |

|          |      | 3.2.1                           | Electronic fuse principle                              | 10       |  |  |

|          |      | 3.2.2                           | Current sensing in electronic fuses                    | 11       |  |  |

|          |      | 3.2.3                           | Protection mechanisms integrated into electronic fuses | 14       |  |  |

|          |      | 3.2.4                           | Additional e-fuse features                             | 18       |  |  |

|          |      | 3.2.5                           | E-fuse vs Melting fuse comparison                      | 20       |  |  |

| 4        | Em   | Emulator design requirements 23 |                                                        |          |  |  |

|          | 4.1  | Emula                           | tor hardware requirements                              | 23       |  |  |

|          |      | 4.1.1                           | Required electrical characteristics                    | 24       |  |  |

|          |      | 4.1.2                           | Communication and control interface                    | 25       |  |  |

|          |      | 4.1.3                           | Analog to digital conversion of voltages and currents  | 25       |  |  |

|          |      | 4.1.4                           | Setting the e-fuse parameters via SPI                  | 25       |  |  |

|          | 4.2  | Emula                           | tor software requirements                              | 26       |  |  |

|          |      | 4.2.1                           | VNF9D1M5 state machine                                 | 26       |  |  |

|          |      | 4.2.2                           | Communication and control interface                    | 26       |  |  |

|          |      | 4.2.3                           | Reaction times to control signals                      | 27       |  |  |

| <b>5</b> | Des  | ign of                          | Emulator Hardware                                      | 28       |  |  |

|          | 5.1  | Selecte                         | ed components                                          | 28       |  |  |

|          |      | 5.1.1                           | Basic e-fuse device                                    | 28       |  |  |

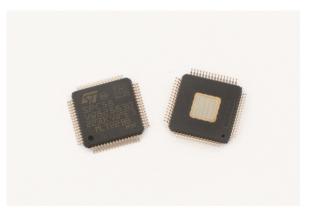

|          |      | 5.1.2                           | Microcontroller used for emulation                     | 30       |  |  |

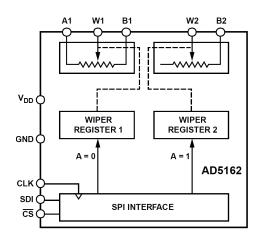

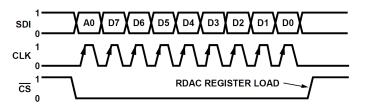

|          |      | 5.1.3                           | Digital potentiometers for e-fuse parameter setting    | 31       |  |  |

|          |      | 5.1.4                           | Power and signal connectors                            | 32       |  |  |

|          | 5.2  | Emula                           | tor PCB design and realisation                         | 33       |  |  |

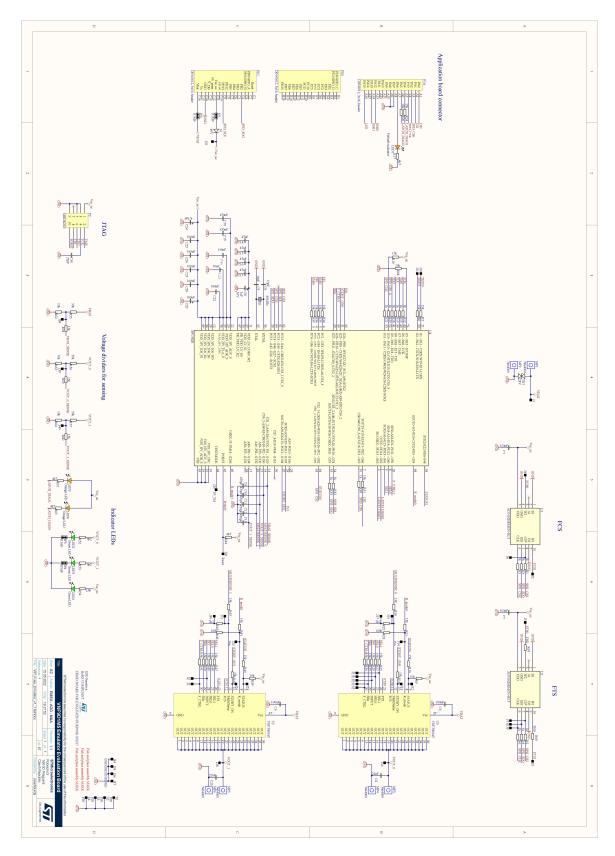

|          |      | 5.2.1                           | Design of the emulator's electrical schematic          | 34       |  |  |

|              |      | 5.2.2   | Definition of physical properties of the PCB                                                                            | 36        |

|--------------|------|---------|-------------------------------------------------------------------------------------------------------------------------|-----------|

|              |      | 5.2.3   | Layout of the emulator's PCB                                                                                            | 36        |

|              | 5.3  | Final   | emulator board assembly                                                                                                 | 41        |

|              | 5.4  | Board   | and signal description                                                                                                  | 41        |

| 6            | Des  | ign an  | d Implementation of emulator software                                                                                   | 43        |

|              | 6.1  | Micro   | controller configuration                                                                                                | 43        |

|              |      | 6.1.1   | Core and clock configuration                                                                                            | 43        |

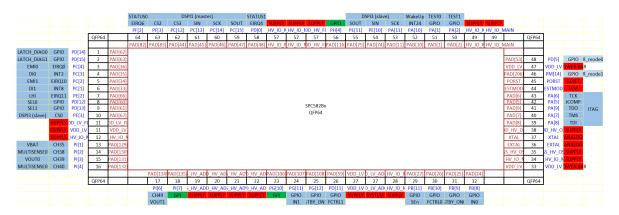

|              |      | 6.1.2   | SIUL2 configuration                                                                                                     | 45        |

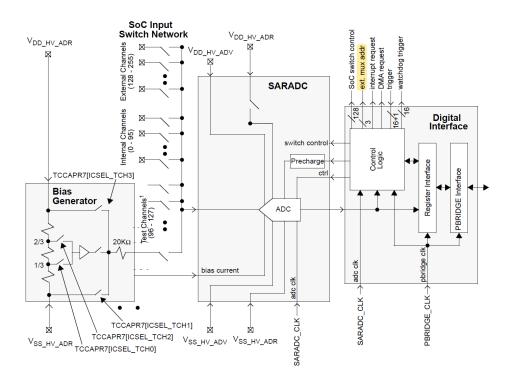

|              |      | 6.1.3   | Analog to Digital Converter configuration                                                                               | 46        |

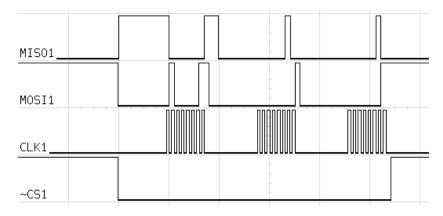

|              |      | 6.1.4   | Deserial Serial Peripheral Interface                                                                                    | 47        |

|              |      | 6.1.5   | PWM generation module configuration                                                                                     | 49        |

|              |      | 6.1.6   | PIT configuration                                                                                                       | 50        |

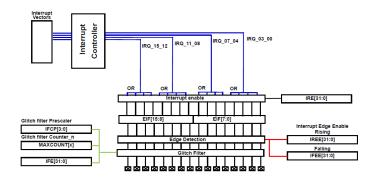

|              |      | 6.1.7   | Interrupt controller configuration                                                                                      | 52        |

|              | 6.2  | Memo    | ry map implementation                                                                                                   | 52        |

|              | 6.3  | SPI co  | ommunication implementation                                                                                             | 53        |

|              | 6.4  | Finite  | state machine implementation                                                                                            | 54        |

|              |      | 6.4.1   | Mode transition                                                                                                         | 54        |

|              |      | 6.4.2   | Standby mode                                                                                                            | 55        |

|              |      | 6.4.3   | Failsafe Mode                                                                                                           | 55        |

|              |      | 6.4.4   | Normal Mode                                                                                                             | 57        |

|              |      | 6.4.5   | Capacitive charging mode                                                                                                | 58        |

| 7            | Vali | idation | n of the emulator                                                                                                       | <b>59</b> |

|              | 7.1  | Evalua  | ation platform and test setup                                                                                           | 59        |

|              | 7.2  | Contre  | ol of the emulator through SPI and pins                                                                                 | 62        |

|              | 7.3  |         | nt consumption of the emulator                                                                                          | 62        |

|              | 7.4  | Valida  | tion of the $I^2t$ curve settings $\ldots \ldots \ldots$ | 63        |

|              | 7.5  |         | tion of state machine implementation                                                                                    | 68        |

|              | 7.6  | Digita  | l current sense and voltage monitoring performance                                                                      | 72        |

|              | 7.7  | SPI fr  | ame processing time                                                                                                     | 75        |

| 8            | Cor  | nclusio | n                                                                                                                       | 76        |

| $\mathbf{A}$ | Sigi | nal De  | scription                                                                                                               | 79        |

| в            |      |         | s electrical schematic and PCB layout                                                                                   | 80        |

|              |      |         | ·                                                                                                                       |           |

| $\mathbf{C}$ | Cor  | ntents  | of the attached CD                                                                                                      | 86        |

# **List of Figures**

| 3.1  | Example of fuse temperature relating curve [1]                                              | 7  |  |

|------|---------------------------------------------------------------------------------------------|----|--|

| 3.2  | Average time-current characteristic of differently rated fuses [1]                          | 8  |  |

| 3.3  | Comparison of time-current characteristics of fuses with different con-                     |    |  |

|      | struction [1]                                                                               | 9  |  |

| 3.4  | Example of maximum and minimum opening time of a fuse $[2]$                                 | 9  |  |

| 3.5  | Basic schematic of an electronic fuse                                                       | 10 |  |

| 3.6  | Current sensing mirror                                                                      | 13 |  |

| 3.7  | Improved current sensing mirror                                                             | 14 |  |

| 3.8  | Voltage drop caused by short circuit at $t = 1 \text{ ms}$ (e-fuse vs. melting fuse)        | 15 |  |

| 3.9  | Overload protection illustration                                                            | 16 |  |

| 3.10 | Open load detection mechanism                                                               | 19 |  |

| 4.1  | The basic structure of the emulator $\ldots$                                                | 24 |  |

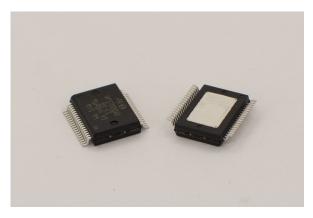

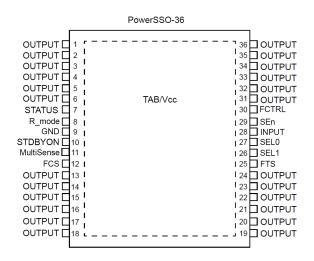

| 5.1  | PowerSSO-36 package                                                                         | 29 |  |

| 5.2  | VNF7000AY pinout $[3]$                                                                      | 29 |  |

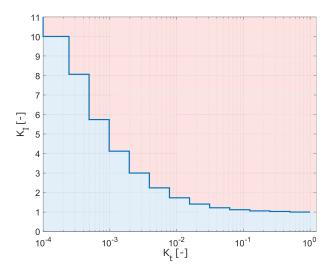

| 5.3  | Nominal $I^2t$ curve of the VIP-Fuse protection $\ldots \ldots \ldots \ldots \ldots \ldots$ | 30 |  |

| 5.4  | Emulation microcontroller - SPC582B60E1                                                     | 31 |  |

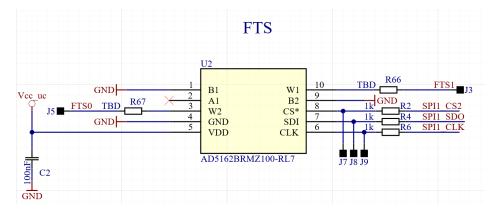

| 5.5  | Block schematic and pinout of the AD5162 digital potentiometer $\left[8\right]$             | 32 |  |

| 5.6  | REDCUBE Plug connectors and plugs                                                           | 33 |  |

| 5.7  | Universal 48-pin board to board connector                                                   | 34 |  |

| 5.8  | Signal assignment to the pins of the emulator MCU                                           | 34 |  |

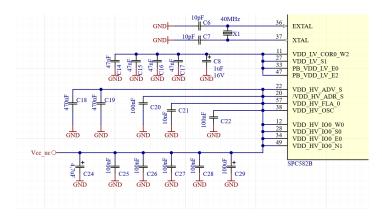

| 5.9  | Microcontroller ballast schematic                                                           | 35 |  |

| 5.10 | Schematic of the FTS potentiometer with offset resistors                                    | 35 |  |

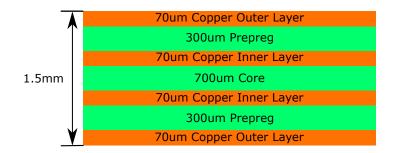

|      | Stackup of the emulator PCB                                                                 | 37 |  |

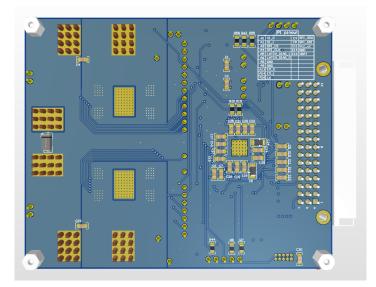

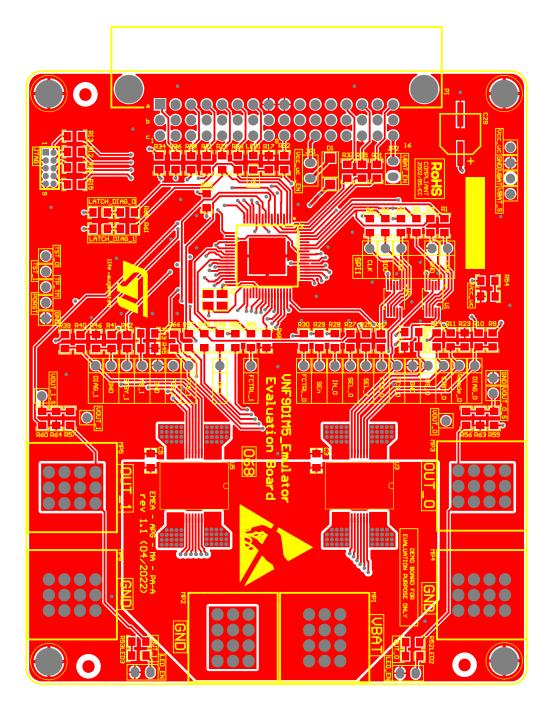

|      | Top view of the PCB rendered in the design software                                         | 37 |  |

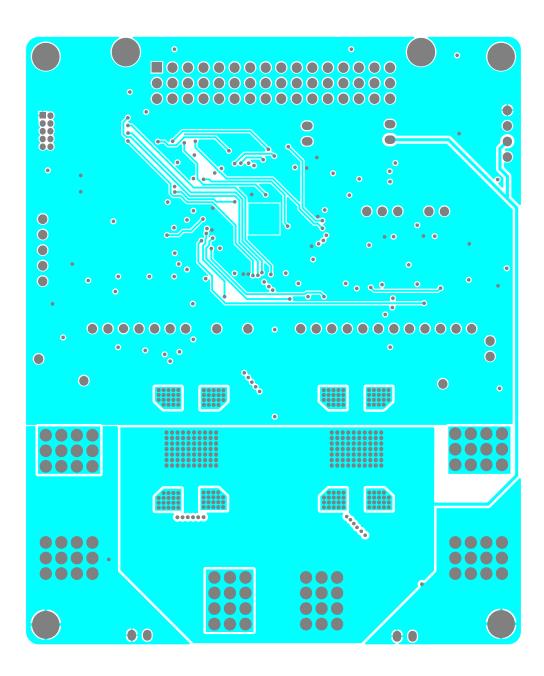

|      | Bottom view of the PCB rendered in the design software                                      | 38 |  |

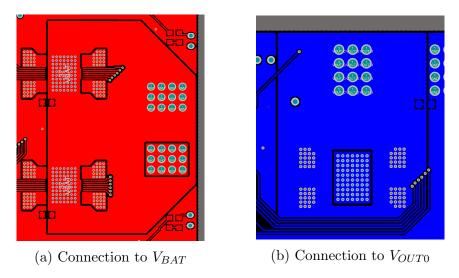

|      | VNF7000AY connection to the PCB                                                             | 39 |  |

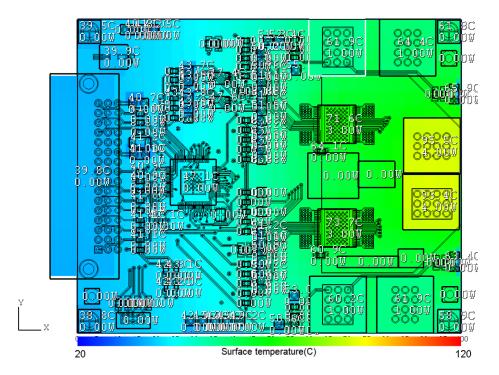

|      | PICLS simulation of heat distribution across the emulator PCB                               | 40 |  |

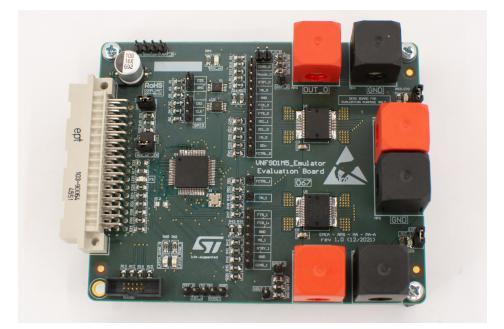

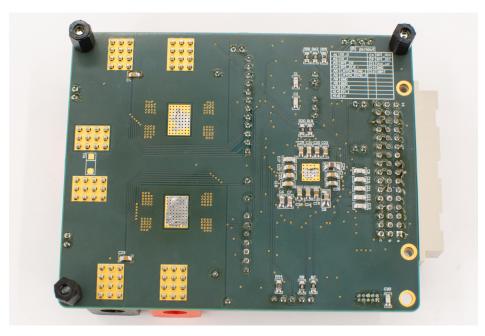

|      | The top of the populated emulator PCB                                                       | 41 |  |

| 5.17 | The bottom of the populated emulator PCB                                                    | 42 |  |

| 5.18 | Description of the emulator's PCB                                                           | 42 |  |

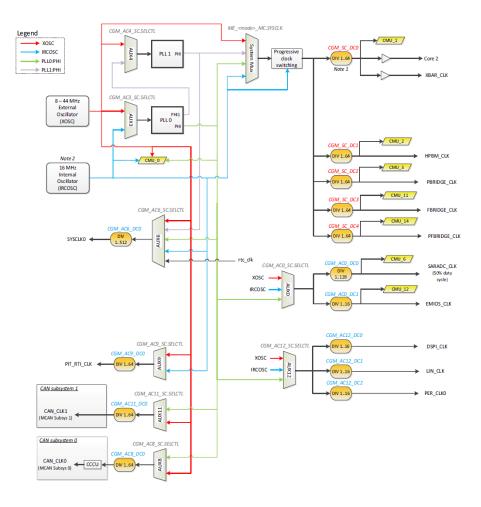

| 6.1  | Clock distribution diagram for SP582B MCU [13]                                              | 44 |  |

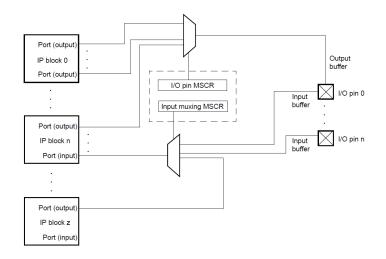

| 6.2  | I/O pin multiplexing in the SIUL2 module $[13]$                                             | 46 |  |

| 6.3  | Pad to interrupt controller connection diagram $[13]$                                       | 46 |  |

| 6.4  | Structure of the SAR ADC in the SPC582B MCU [13]                                            | 48 |  |

| 6.5  | SPI frame format required by the emulator                                                   | 49 |  |

| 6.6  | SPI communication format used by the digital potentiometers [8]                             | 49 |  |

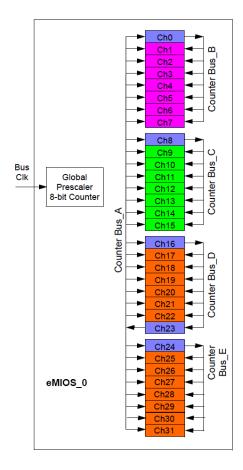

| 6.7  | Structure of the eMIOS module in SPC582B [13]                                                          | 51<br>52 |

|------|--------------------------------------------------------------------------------------------------------|----------|

| 6.8  | Definition of the union representing Global Status Byte                                                | 53       |

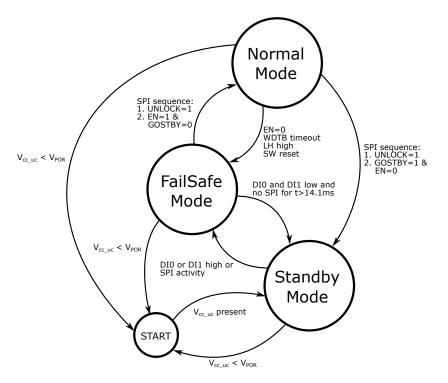

| 6.9  | State diagram of the emulator state machine                                                            | 54       |

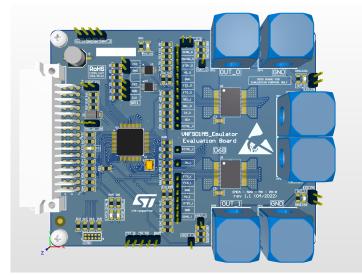

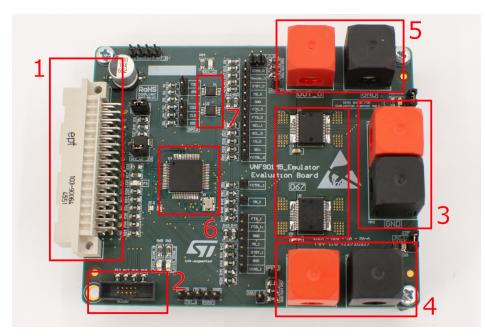

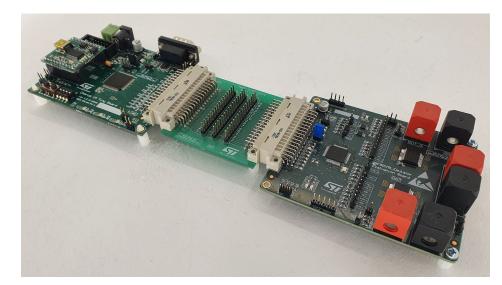

| 7.1  | Chorus 1M Tiny Board v1.0 universal motherboard                                                        | 60       |

| 7.2  | Main screen of the PC application for controlling the evaluation platform                              | 60       |

| 7.3  | Complete evaluation platform with the emulator (right) and mother-                                     |          |

|      | board (left) $\ldots$ | 61       |

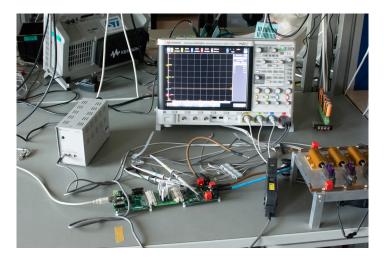

| 7.4  | Measurement setup                                                                                      | 62       |

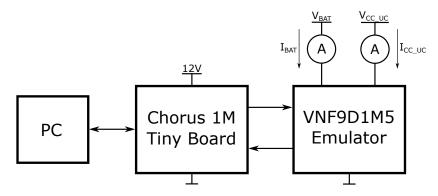

| 7.5  | Current consumption measurement setup schematic                                                        | 63       |

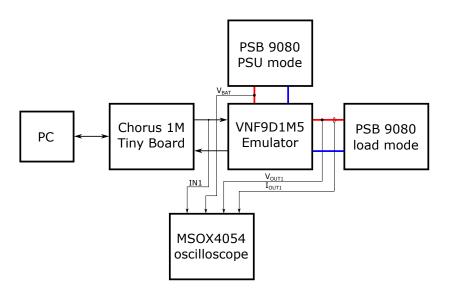

| 7.6  | Testing setup for emulator's $I^2t$ curve settings evaluation                                          | 64       |

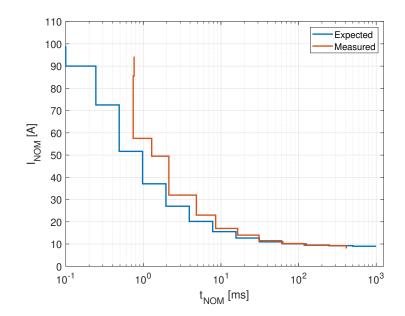

| 7.7  | Comparison of the expected and measured $I^2t$ curves $\ldots \ldots \ldots$                           | 66       |

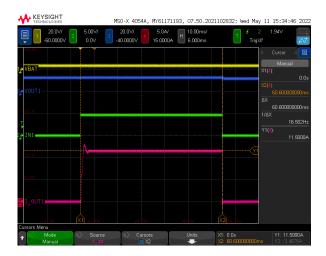

| 7.8  | A captured image of one of the $I^2t$ curve validation measurement $\ldots$                            | 67       |

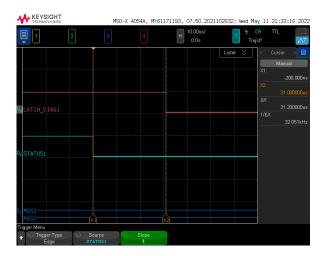

| 7.9  | Reaction time to output activation via direct input                                                    | 68       |

| 7.10 | Reaction time to Limp Home pin activation                                                              | 69       |

|      | Reaction time to emergency stop pin activation                                                         | 69       |

|      | Emulator startup time measurement                                                                      | 70       |

| 7.13 | Fault propagation time measurement                                                                     | 71       |

| 7.14 | Delay between an output activation SPI command and output activation                                   | 71       |

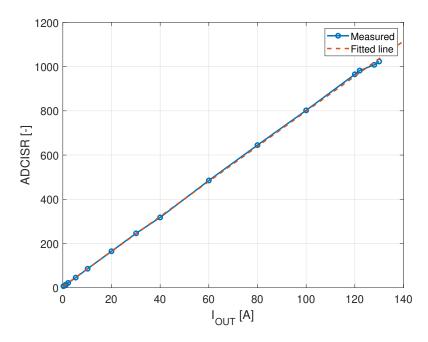

|      | Output current vs. ADCISR value                                                                        | 73       |

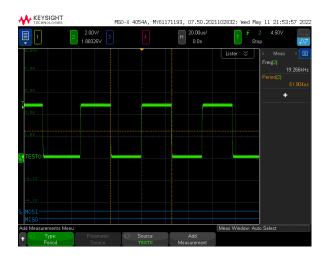

|      | Measurement of emulator's ADC sampling rate                                                            | 74       |

| 7.17 | Processing time of the first byte of an SPI frame                                                      | 75       |

| B.1  | Complete schmematic of the emulator                                                                    | 81       |

| B.2  | Layout and silkscreen of the top layer of the PCB                                                      | 82       |

| B.3  | Layout of the first inner layer of the PCB                                                             | 83       |

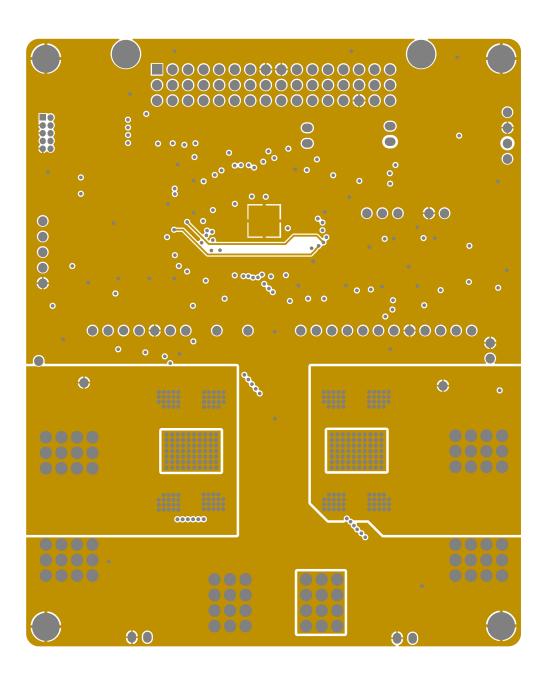

| B.4  | Layout of the second inner layer of the PCB                                                            | 84       |

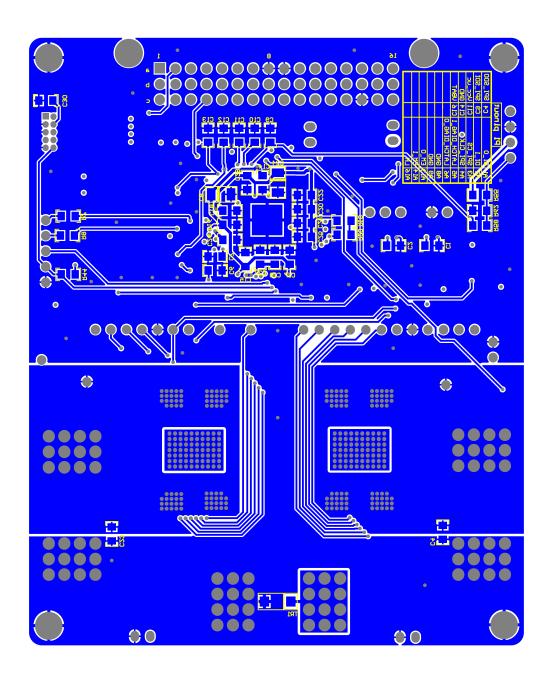

| B.5  | Layout and silkscreen of the bottom layer of the PCB                                                   | 85       |

# **List of Tables**

| 4.1                 | SPI frame used in VNF9D1M5. OCx - opcode, Ax - address, Dx - data [5]   | 27             |

|---------------------|-------------------------------------------------------------------------|----------------|

| $5.1 \\ 5.2 \\ 5.3$ | Coefficients defining the shape of the nominal $I^2t$ curve $\ldots$    | 30<br>32<br>42 |

| 6.1                 | SAR ADC channel assignment                                              | 47             |

| 6.2                 | PIT LDVAL register values for different periods                         | 52             |

| 7.1                 | Emulator's current consumption in different operating modes             | 63             |

| 7.2                 | Latch off times $t_{LOFF}$ for a fixed FCS and varying FTS settings     | 64             |

| 7.3                 | Latch off times $t_{LOFF}$ for a fixed FTS and varying FCS settings     | 65             |

| 7.4                 | $I^{2}t$ stairstep curve measurements for fixed FTS=0 and FCS=1 config- |                |

|                     | uration                                                                 | 66             |

| 7.5                 | Results of the digital current sense evaluation measurement             | 73             |

| 7.6                 | Measured voltages vs. values given by the emulator                      | 74             |

| A.1                 | Description of signals available on the emulator                        | 79             |

## **List of Abbreviations**

- ADC Analog to Digital Converter

- e-fuse Electronic Fuse

- EMC Electromagnetic Compatibility

- FCS Fuse Current Setting

- FTS Fuse Time Setting

- FW Firmware

- GPIO General Purpose Input Output

- GSB Global Status Byte

- GUI Graphical User Interface

- HAL Hardware Abstraction Layer

- HW Hardware

- IAV In Application Validation

- I/O Input/Output

- $I^2C$  Inter Integrated Circuit

- JTAG Joint Test Action Group

- LDO Low Drop-Out Voltage Regulator

- MCU Microcontroller Unit

- MOSFET Metal-Oxide Silicon Field Effect Transistor

- OLD Open Load Detection

- OTP One Time Programmable (memory)

- PCB Printed Circuit Board

- PIT Periodic Interrupt Timer

- PLL Phase-Locked Loop

- PWM Pulse Width Modulation

- RAM Random Access Memory

- RMS Root Mean Square

- ROM Read Only Memory

- RUL Remaining Useful Life

- SAR Successive Approximation Register

- SPI Serial Peripheral Interface

- SW Software

- UART Universal Asynchronous Receiver-Transmitter

# Chapter 1 Introduction

As modern cars get more complex, their power distribution systems are getting more complex as well. This increase in complexity requires a more sophisticated solution for power distribution. The standard melting car fuses have not changed for several decades, and they have several shortcomings, which are no longer acceptable in modern cars. Among these shortcomings is the fact, that melting fuses are not reusable. One way of addressing the growing requirements for reliability and safety is the use of electronic fuses. An electronic fuse is a device which replaces the traditional melting fuse as a circuit protection device while offering more features and improved performance. The adoption of electronic fuses in the automotive industry is relatively recent, and the developers of car power distribution systems need to get familiar with them before applying them to a car's systems.

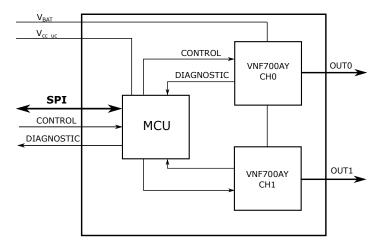

This thesis aims to design and develop an emulator of an electronic fuse that is currently in development (VNF9D1M5), which will be used to provide the automotive developers with a way to familiarise themselves with the e-fuse before it is manufactured. The emulator will emulate advanced functions of the future device and will be built around an already existing e-fuse device (VNF7000AY) that does not provide these features. The most notable of these functions is the control and diagnostics of the e-fuse via SPI.

The emulator's development will involve the analysis of the future device's parameters, from which the requirements for the emulator's design will be derived. Based on these requirements, the emulator hardware and software will be designed and implemented. The HW design will include the selection of components and the design of a PCB. The SW design and implementation will involve implementing then features not available on the VNF7000AY. When the emulator's design is complete and the device is realised, validation measurements will be performed to confirm that the design requirements have been met.

# Chapter 2 Assignment analysis

As mentioned in the introduction, the goal of this thesis is to design and implement an emulator of an electronic fuse with advanced functions. This emulator will be using an already existing electronic fuse. The purpose of the emulator will be to emulate advanced functions, which will be added to a new iteration of the e-fuse. These new functions include communication via SPI and basic diagnostic of the device as well as better configurability of the device and several other functions.

## 2.1 Emulator design requirements

Before the emulator is designed, the requirements of the new device need to be analysed in order to determine which functions can be emulated and what will be its limitations. This analysis will produce a list of achievable parameters of the emulator. Based on this, the emulator specification will be drawn up.

## 2.2 Emulator hardware design

The design of the emulator's hardware will be focused on meeting the requirements for the future e-fuse device. Some of these requirements will be fulfilled only partially or not at all. This is because it would be too complicated to implement them, and they are not key to the function of the device. HW design will be based on the block schematic, which was created as part of the requirement analysis.

The emulator will be designed as an evaluation platform at first. This means that the design will put emphasis on the accessibility of signals and generally making it easier to work with the device in a laboratory. Another more compact and simplified version might be designed when this version is properly evaluated, but that will not be a part of this thesis. The emulator will be designed to be able to integrate into a vehicle's power distribution system.

The first step of the design will be selecting the components from which the emulator will be assembled. This includes microcontroller selection, integrated circuits and connectors. E-fuse devices are already provided, which means I will not be selecting them. This process also includes checking the compatibility of the devices and their availability. Since the device is going to have automotive applications, it is also important to select automotive grade components where possible.

After the component selection comes the schematic design. The schematic will be derived from the block schematic. For the integrated circuits, the microcontroller and the e-fuses, the reference designs will be followed. The schematic design also involves determining the pinout of the MCU. This will be partly done in component selection because the MCU will need to have enough pins to accommodate our needs. Before proceeding with the PCB design, the schematic will be reviewed.

Once the schematic has been finished and reviewed, I will be able to proceed with the printed circuit board design (PCB). During the design, basic design rules and device requirements shall be taken into account. The emulator is required to work with high currents (up to 64 A). This means that power losses on components, connectors and the board itself will need to be taken into account. Before manufacturing the board, a thermal simulation will be performed to determine whether the board and the components on it have sufficient cooling. A review of the PCB design will be performed as well.

When all this is done, the board design files will be sent to the chosen manufacturer. After receiving the board, the hardware part of the device will be completed by soldering the components onto the PCB. This will also include some testing to uncover design or soldering errors and prepare the board for software development.

## 2.3 Emulator software design and implementation

Software development for this project will involve the design and implementation of firmware (FW) for the MCU, which emulates the behaviour of the new e-fuse. Part of the development can be done before the hardware is ready. While waiting for the PCB to be manufactured, I shall familiarise myself with the MCU and its peripherals (SPI, ADC,...). Peripheral and core configurations will be examined, and the most appropriate ones will be selected.

Once the hardware is available, it will be possible to develop the code on it. The peripheral and I/O configurations shall be verified to work on the new hardware. The future e-fuse device behaviour is described using a finite state machine. A modified version of this state machine will be defined for the emulator. This modified state machine will be implemented. The FW needs to be designed to be indistinguishable from the real device by the user.

Since there are strict safety requirements concerning reaction times and speed in general, no Hardware Abstraction Layer (HAL) libraries shall be used. The MCU will be programmed using direct register access. This approach will result in more difficult development but also better FW performance. Important signals shall be handled by interrupts in order to minimise the reaction time as much as possible.

Alongside the FW for the microcontroller, software for an application platform will be developed. This software will be provided by STMicrocelectronics and its development is not part of this thesis. This application software will be used for the evaluation of the emulator.

## 2.4 Testing and validation

Once the emulator is finished, it needs to be tested and validated. This means it will be necessary to verify that the design requirements were met. It will also provide a more accurate view of the emulator's parameters. The testing and validation will be carried out according to a test specification which will have to be drawn up. This must be done as a part of the emulator's specification. The test specification will be based on the requirement list and automotive industry standards. Because the emulator is built on an already existing e-fuse device, it will not be necessary to perform every test on the power part of the device.

# Chapter 3 Introduction to fuses

In this chapter, I will give a brief overview of automotive fuses and their application. The reasons why fuses are needed and their parameters will be discussed. Then the concept of electronic fuses will be introduced and compared to the standard melting fuse. Applications and benefits (and disadvantages) of electronic fuses will be discussed as well.

## **3.1** Fuses in automotive applications

The purpose of fuses in power distribution systems is to protect individual components and the entire system. In standard melting fuses, this protection is achieved by the fuse melting under overcurrent conditions. When the fuse melts, the current flow in the circuit is interrupted, and the overcurrent condition is eliminated.

Wiring in cars is made from copper. Even though copper has excellent electrical conductivity, the wire resistance is not negligible. The wire resistance can be determined using the following formula:

$$R = \frac{\rho \cdot l}{A},\tag{3.1}$$

where  $\rho$  is the electrical resistivity of the material (copper  $\rho_{Cu} = 17 \times 10^{-9} \,\Omega \,\mathrm{m}$ ), l is the length of the wire, and A is the wire cross-section area.

When the passing current through a non-ideal conductor, Joule's law applies, meaning that a part of the power flowing through the conductor is turned into heat. The power turned into heat is proportional to the conductor resistance and square of the current as expressed in this formula:

$$P = I^2 R. aga{3.2}$$

The conductor needs to dissipate the heat generated by the passing current. When the current is within the rating, the conductor manages to dissipate the heat into its surroundings. When the current exceeds the rating, the wire begins to overheat. This issue is exacerbated by the fact the wires in cars are bound into a wiring, where there are more wires generating heat and the heat dissipation is diminished. Wire overheating can lead to isolation melting which can lead to a short circuit between the wires in a wiring harness. It can even lead to the melting of the conductor itself. These are serious safety risks, and fuses are essential in reducing them.

In this section, an overview of fuse parameters and behaviour will be given, and the fault states against which fuses protect the circuits will be presented.

#### **3.1.1** Types of faults in power distribution systems

Fuses generally protect against overcurrent faults. This means that the current flowing through the circuit exceeded the maximum rated current. This condition can be caused by both overloads and short circuits. When any of these faults occur, the fuse must open the circuit and interrupt the current flow. The fuse reaction must be fast enough in order to prevent any permanent damage to the circuit.

An overload in the circuit occurs when the current exceeds the rating of the wiring and the devices connected to it. In this condition, current is flowing only through the defined pathways (i.e. the wires). This usually happens when too many active devices are connected to the circuit at the same time or when a device experiences a malfunction. This can lead to wiring and/or device damage due to overheating.

Short circuit occurs when an unintended connection is made between the power source (battery, alternator) and the ground. This could happen as a result of wiring insulation damage or device malfunction. In this case, the current is flowing through an undefined path. Short circuits have very low resistance, which means that the supply voltage forces huge currents through them. Such large currents can damage the wiring, connected devices and even the power supply itself. Because the current passing through the wires during short circuit is so high, the chance of wiring insulation melting and catching fire is greatly increased.

#### **3.1.2** Fuse parameters

When selecting an appropriate fuse for a circuit, it needs to have defined parameters. These parameters describe the fuse's maximum ratings and its behaviour during overcurrent. Fuse parameters can also be applied to e-fuses. Following is a brief overview of these parameters.

#### Voltage rating

As with most electric and electronic components, fuses also have maximum voltage ratings. This is the maximum voltage that can occur in the circuits. Fuses are designed so that they operate safely under this voltage. When voltage rating is exceeded, the fuse might not work as expected due to arcing. The circuit voltage must never exceed the fuse maximum voltage rating. Voltage rating is usually specified in volts DC. Sometimes AC value is given as well.

#### Breaking capacity

Breaking capacity or Interrupting rating determines the maximum current the fuse is able to handle safely. During an overcurrent event, the current through the fuse can be several times the nominal current. If this current is higher than the breaking capacity, it can result in fuse package damage. The damaged fuse might damage surrounding components (e.g. other fuses), or it may not break the circuit properly. Fuse breaking capacity is specified as maximum current at rated voltage.

#### Current rating

The current rating specifies the maximum current that the fuse can carry continuously. This rating can change depending on external conditions, especially temperature. Under normal conditions (25 °C), the maximum current is usually derated to a lower value. This is done to avoid the fuse blowing prematurely due to manufacturing tolerances. Under normal conditions, the derating factor is typically 25%. For example a fuse rated for 20 A would be derated to just 15 A at 25 °C.

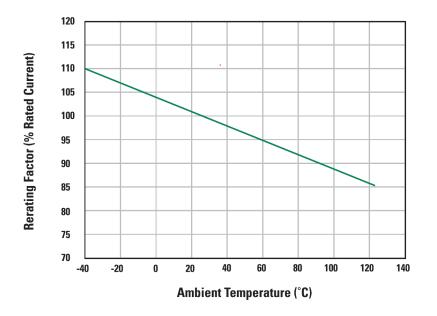

When ambient temperature increases, the fuse's ability to dissipate heat decreases. This means that the fuse will blow at a lower current than at 25 °C. In order to determine which fuse to use, rerating for increased ambient temperature needs to be performed. The rating for the defined temperature can be determined using the following formula:

$$I_{RAT} = \frac{I_{NOM}}{0.75 \cdot r_T},$$

(3.3)

where  $I_{NOM}$  is the nominal circuit current,  $r_T$  is the temperature relating factor and  $I_{RAT}$  is the required rating of the fuse. The relating factor can be obtained from Temperature Relating Curve from the fuses datasheet. An example of this curve can be seen in figure 3.1. For example if the circuit current is  $I_{NOM} = 10$  A and the ambient temperature is t = 80 °C, the relating factor from the curve is  $r_T = 0.92$ . The related current is then

$$I_{RAT} = \frac{10}{0.75 \cdot 0.92} = 14.5 \,\mathrm{A}. \tag{3.4}$$

This means that at least a 15 A fuse should be used for the circuit under these conditions.

Figure 3.1: Example of fuse temperature relating curve [1]

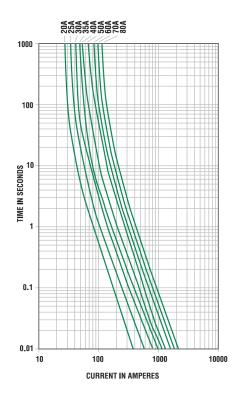

#### Time-current characteristic

All of the parameters mentioned so far described static parameters, but when selecting a fuse, reaction times are as important as the current rating. Time-current characteristic describes the response times to different overcurrent values. These characteristics are always declining, meaning that when the current gets higher, the time needed for the fuse to break the circuit is shorter. Knowing the time-current characteristic helps to select the right fuse when the fault needs to be cleared in a specified

Figure 3.2: Average time-current characteristic of differently rated fuses [1]

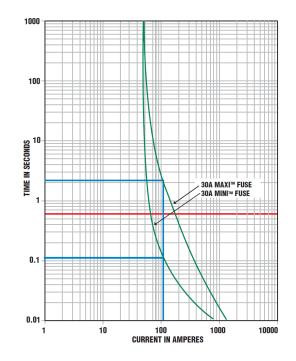

time. It can also be used to choose a fuse that will allow a temporary overload. In figure 3.2 you can see a comparison of average, characteristics of fuses with different current ratings. In figure 3.3 characteristics of two fuses with identical current ratings and different constructions are compared.

#### $I^2t$ rating

$I^{2}t$  expresses the amount of thermal energy available from the current. The unit is A<sup>2</sup>s. It is also used for rating electric motors or wiring. There are three kinds of  $I^{2}t$  rating. Melting  $I^{2}t$  rating expresses the amount of energy needed to melt the fuse. Arcing  $I^{2}t$  expresses the amount of heat dissipated during arcing. Total Clearing  $I^{2}t$  expresses the total amount of heat dissipated in the fuse from the start of the overcurrent event to its end when the fuse clears the fault by interrupting the current.

$I^{2}t$  rating is important when selecting fuses. The total clearing  $I^{2}t$  of a fuse needs to be higher than the  $I^{2}t$  rating of the wiring of the circuit it protects.

#### 3.1.3 **Fuse selection process**

All of the parameters mentioned above need to be considered when selecting a fuse. Another complication in the selection process comes from the conditions in which the fuse operates, such as ambient temperature. In order to compensate for these, the fuses need to be rerated according to specified characteristics.

When using melting fuses, another issue is introduced into the selection process, and that is the variance of the parameters. As with essentially every electrical and electronic component, no two identically rated fuses are the same. The parameters in the fuses datasheet are only the average values. As you can see in figure 3.4, taken

Figure 3.3: Comparison of time-current characteristics of fuses with different construction [1]

from a LittelFuse catalogue [2], the maximum and minimum opening times of a fuse can differ by several orders of magnitude. This means that in the event of an overload, it is difficult to determine for how long will the overcurrent flow. When rating the wiring and devices in the circuit, the longest time the fuse takes to open needs to be considered. This usually leads to overrating of the wiring in order for it to handle the longer overcurrent event. The overrating of the wiring leads to increased mass and cost of the wiring. The increased mass also leads to increased fuel consumption of the car. The electronic fuse aims to resolve this problem by being much more accurate than the melting fuse.

| Time-Current Characteristics |                            |  |

|------------------------------|----------------------------|--|

| % of Rating                  | Opening Time Min / Max (s) |  |

| 110                          | 360,000 / ∞                |  |

| 135                          | 0.75 / 120                 |  |

| 200                          | 0.15 / 5                   |  |

| 350                          | 0.08 / 0.25                |  |

| 600                          | 0.03 / 0.1                 |  |

Figure 3.4: Example of maximum and minimum opening time of a fuse [2]

## **3.2 Introduction to electronic fuses**

As modern car systems get more and more complex, the power delivery systems need to keep up with the requirements. Many of these requirements focus on safety and reliability. Fuses are key safety components of a car's power distribution system safety. To make the system safer and more reliable, the fuses need to get more sophisticated. The advancements in areas of power transistors and integrated circuits in general lead to the concept of the electronic fuse (e-fuse), which is an ideal replacement for the traditional fuse.

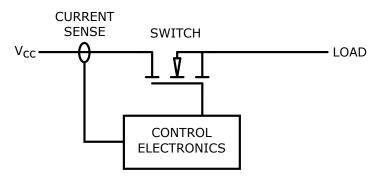

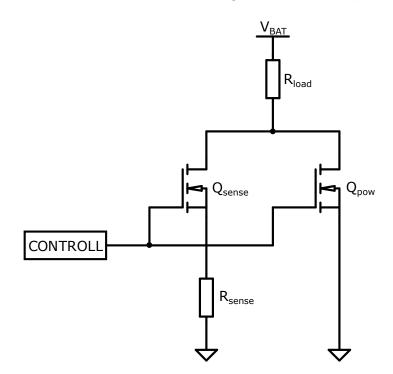

In its most basic form, the electronic fuse uses a power switch, which is usually a MOSFET, some form of current sensing and control logic which controls the switch and evaluates the current sense data. This structure is illustrated in figure 3.5. When the current in the circuit is below the set threshold, the transistor remains switched on. Once the current exceeds the threshold (overcurrent event), the transistor switches off, interrupting the current through the circuit.

This is the simplest version of the electronic fuse possible. Thanks to the modern processes that allow integrating complex circuits onto the same chip as the power transistor, e-fuses can have many more functions. Different and more sophisticated protection mechanisms and even diagnostics of the fuse can be implemented in one device.

In this section, the principle of e-fuse will be introduced and the main protection mechanisms and other features of electronic fuses will be presented. After that, a comparison between the traditional melting fuse and the electronic fuse will be made. This will show the reasons for adopting electronic fuses into modern car power systems.

Figure 3.5: Basic schematic of an electronic fuse

### **3.2.1 Electronic fuse principle**

An electronic fuse is an electronic device that can be used to protect a circuit in case of an overcurrent. The electronic fuse can also protect against other kinds of faults in the power grid. Its primary purpose in a system is the same as that of a standard melting fuse: interrupt current passing through it when it reaches a predefined level. However, the mechanisms used to interrupt the current are different. When the melting fuse experiences an overcurrent, the conductive element of the fuse heats up to the point of melting, which interrupts the current. E-fuses use electronic switches, transistors, and current sensing. When the e-fuse detects an overcurrent, it opens the switch, interrupting the current flow.

E-fuse can be realised either as a single integrated circuit or assembled from discrete

components (transistors, diodes, transils,...). The discrete solution allows the designer to select exactly which protections to implement. Unfortunately, this approach results in a much larger and less efficient device than the integrated solution. Modern manufacturing processes allow the integration of control logic onto the same silicon as the power switch. This tight integration allows for much more control over the transistor. For example, it is much easier to measure the transistor's temperature in the IC than to measure it on a discrete component.

Since the switching off of the transistor is controlled by the control logic of the efuse, the fuse parameters can be configured to required values instead of having preset parameters from the factory. This is very useful because the fuse can be configured precisely to the requirements of the circuit it protects. E-fuses are also more precise when it comes to current measurement and interrupt times. The VNF7000AY's current sense has accuracy of  $\pm 7\%$  for currents from 10 A to 30 A [3], which is much lower than tolerances of melting fuses. The current sense accuracy is worse for current that are much lower than nominal, which is why, it is important to select the appropriate e-fuse device. Thanks to this, the wiring in the circuit does not need to be overrated, resulting in weight and cost reduction.

Since the fuse control logic can be realised as an integrated circuit, it is much easier and cheaper to implement more functions than standard overcurrent protection. These functions can include more protection mechanisms, diagnostics and configuration of the fuse's behaviour.

### 3.2.2 Current sensing in electronic fuses

For the electronic fuse to be able to perform its function, it needs to be able to monitor the amount of current passing through the circuit. In this section, the various methods of current sensing will be presented. Since there are many ways to measure current, we first need to determine the requirements for an automotive e-fuse.

The current measurement methods vary in complexity and accuracy and their principle of operation. One of the basic classifications is to direct and indirect methods. Direct methods need to interrupt the circuit in order to insert a measurement device (ammeter) through which the current will pass. Indirect methods do not need to interrupt the circuit because they measure the magnetic fields generated by the passing current. Since the e-fuse is already inserted into the circuit, the direct methods are the obvious choice.

#### **Current Shunt**

The most used direct current measurement method is using a current shunt. A current shunt is a resistor of a known resistance inserted into the circuit. When current passes through the shunt, a voltage drop appears on it.. By measuring the voltage across the shunt, the current can be determined using Ohm's law:

$$U = R \cdot I. \tag{3.5}$$

This method can be very accurate, but it is dependent on the accuracy of the voltage measurement and the accuracy of the resistor. Current shunts also have very good resistance against interference, depending on the measured current (frequency, amplitude). Unfortunately, the principle upon which current shunts operate is also their greatest weakness. When current passes through the shunt, heat is generated (Joule's law):

$$P = U \cdot I = R \cdot I^2. \tag{3.6}$$

This causes the shunt to heat up, which can lead to its damage or destruction. The power loss on a shunt resistor also decreases the efficiency of the entire system. One shunt would probably not be a problem, but there can potentially be dozens of these in a single car. This can be mitigated by using lower resistance shunts. Using a lower resistance shunt also means lowering the voltage across the shunt. This can complicate the measurement and potentially make it less accurate. A lower resistance current shunts are also more expensive, as they require tighter manufacturing tolerances. A current shunt's price is comparable to the price of an entire electronic fuse.

#### **Ratio Metric Sense MOSFET**

When using MOSFETs, another current measurement method is available. Modern power MOSFETs are composed of many parallel cells with their sources, drains and gates connected. This is done to achieve a large current carrying capacity with low onresistance. This is a very simplified explanation; for more detail, see a power electronics book. Some of these cells can have their sources electrically disconnected from the others and connected to a separate pin. This pin is usually called Current Sense or Mirror. If this pin is connected to the same potential as the source of the power transistor, the sense transistor acts as a current mirror. It consists of a large power transistor  $Q_{pow}$  and a small sense transistor  $Q_{sense}$  as illustrated in figure 3.6. In this case, an N-type MOSFET is used as a low side switch. For now, the  $R_{sense}$  resistor will be considered to be  $0 \Omega$ .

The Shichman-Hodges model of the MOSFET provides an equation that can be used to calculate the current flowing through the transistor based on its parameters and voltages:

$$I_D = \frac{1}{2} K_p \frac{W}{L} (V_{GS} - V th)^2 (1 + \lambda V_{DS})$$

(3.7)

- $I_D$  is the drain current

- $K_p$  is the technological constant of the transistor

- W and L are the width and length of the transistor

- $V_{GS}$  is the gate-source voltage

- $V_{th}$  is the transistor threshold voltage

- $V_{DS}$  is the drain-source voltage

- $\lambda$  is the channel length modulation constant

Since both the transistors have their gates, drains, and sources connected and are made using the same technology, we can substitute into this equation and determine the ratio between  $I_{D\_sense}$  and  $I_{D\_pow}$ .

$$\frac{I_{D\_pow}}{I_{D\_sense}} = \frac{\frac{1}{2}K_p \left(\frac{W}{L}\right)_{pow} (V_{GS} - Vth)^2 (1 + \lambda V_{DS})}{\frac{1}{2}K_p \left(\frac{W}{L}\right)_{sense} (V_{GS} - Vth)^2 (1 + \lambda V_{DS})} = \frac{\left(\frac{W}{L}\right)_{pow}}{\left(\frac{W}{L}\right)_{sense}}$$

(3.8)

This means that the ratio between the drain currents is the same as the ratio between the sizes of the transistors. This ratio is given by the number of MOSFET cells used in the power part and the number of cells used in the sense part.

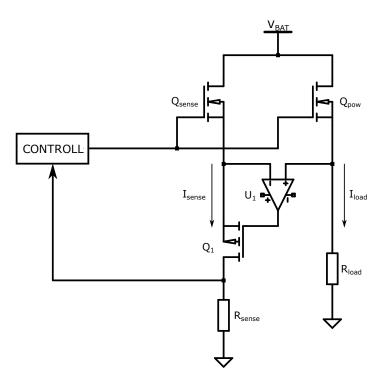

However, to measure the current passing through the sense transistor, a resistor  $R_{sense}$  needs to be connected to the source. This, unfortunately, causes the drain-source voltage of the sense transistor  $V_{DS\_sense}$  to change and no longer equal to  $V_{DS\_pow}$ . This causes the above equation to no longer apply. The higher the  $R_{sense}$  resistance, the worse the accuracy of the mirror. This makes the selection of the  $R_{sense}$  resistor a little complicated. In integrated circuits, the solutions are more complex, and an example of such a solution can be seen in figure 3.7. The transistor  $Q_1$  and the operational amplifier  $U_1$  are used to match the source voltages of transistors  $Q_{sense}$  and  $Q_{pow}$  [4].

Figure 3.6: Current sensing mirror

Figure 3.7: Improved current sensing mirror

### 3.2.3 Protection mechanisms integrated into electronic fuses

As mentioned in previous sections, thanks to the control logic being integrated into the e-fuse, it is possible to implement more protection mechanisms than just overcurrent protection. Some of these protections are also necessary to protect the e-fuse itself. This section will introduce the basic and the advanced protection mechanisms.

#### Short-circuit protection

During a short circuit, the current flows through a low resistance path from one terminal of the power supply to the other. The current is limited only by the resistance of the wiring and the voltage and output resistance of the power supply. That is why short circuit currents are usually very high.

One of the main functions of any fuse is to protect the circuit from short circuits by interrupting the current. This applies to electronic fuses too. Melting fuses, as the name suggests, interrupt the current by melting due to heating up by the passing current. E-fuses monitor the current passing through them, and when the current exceeds the preset limit, the control logic turns off the transistor, interrupting the current.

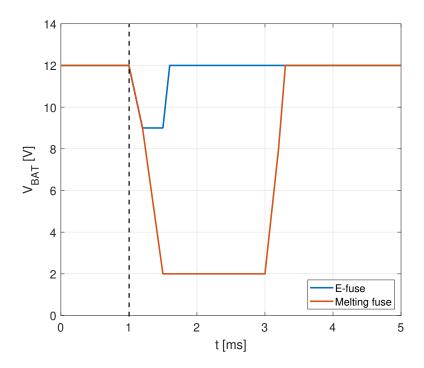

When a short circuit occurs, the current is so high that it can cause the power supply voltage to drop. If this voltage drop is significant and long enough, it can cause problems for systems connected to the same power supply. This is considered a safety risk. It is therefore important to interrupt the current as soon as possible. For reasons explained in the previous section, the melting fuse cannot react very fast. However, a well-designed e-fuse can respond much more quickly, as illustrated in figure 3.8.

Figure 3.8: Voltage drop caused by short circuit at t = 1 ms (e-fuse vs. melting fuse)

#### **Overload** protection

During an overload, a current higher than expected is running through the circuit, usually due to a device fault. These currents are lower than during a short-circuit but can still cause damage. They are especially dangerous to wiring, as it can heat up to the point of melting the insulation. This can, in turn, lead to a short circuit. It is sometimes necessary to allow an overload for some time, for example, when turning a device on and charging its input capacitors. The  $I^2t$  rating of the wiring is the deciding factor here. It must not be exceeded.

Melting fuses have their own  $I^2t$  rating. A fuse with an  $I^2t$  rating lower than that of the wiring will protect it. However, the tolerances in fuse parameters mean that the wiring needs to be overrated in order to handle the worst-case scenario of the fuse's performance.

E-fuses can use logic and mathematics. One option is to have a set of predefined threshold currents and corresponding turn-off times. When the current exceeds a certain threshold, the fuse will wait for the defined amount of time, and if the current does not drop, it interrupts the circuit. This approach is very simple and, for many reasons, impractical. For instance, it does not really take repeating overloads into account.

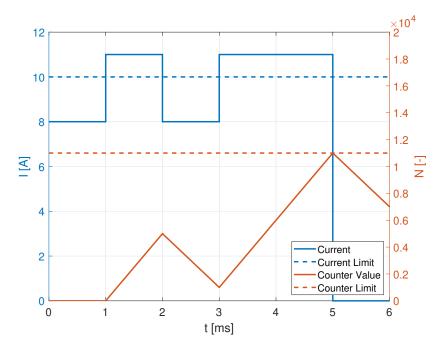

Another option is to compute the  $I^2t$  of the current running through the fuse. By its principle, this approach requires some form of integrating the current over time. One option is to sample the current periodically and compute the  $I^2t$  using a microcontroller. Unfortunately, using an MCU would make the e-fuse too expensive. A simpler approach is to use a counter. When the current through the e-fuse exceeds the preset threshold, the counter starts counting up. The counter increment is proportional to the size of the overcurrent. When the current drops below the threshold, the counter starts to decrement. If the counter reaches a certain predefined value, which corresponds to an  $I^2t$  rating, the fuse interrupts the current. This process is illustrated in figure 3.9. The second overload is long enough for the fuse to latch off at t = 5 ms.

The  $I^2t$  computation allows the fuse to be closely matched to the wiring and devices protected by the e-fuse. E-fuses also offer greater precision than melting fuses, which reduces the need for overrating the wiring. This approach is used for fault detection in many other systems, as it helps to reduce false alarms. The way this system is implemented is key to the accuracy of the  $I^2t$  computation, but the exact implementation is kept secret by the manufacturers.

Figure 3.9: Overload protection illustration

#### Overvoltage and Undervoltage protection

So far, all of the mentioned protections are present in melting fuses as well as in efuses. Since the e-fuse already contains some form of an ADC, it is possible to monitor the supply voltage. The power supply voltage  $(V_{BAT})$  is not constant. It can be higher or lower than the nominal voltage.

Undervoltage occurs when the  $V_{BAT}$  voltage drops a certain amount below the nominal level. It can be caused by a fault in the circuitry or in a device in the system. An undervoltage can cause the systems in the power grid to behave incorrectly or stop working altogether. The e-fuse can detect the undervoltage event and can send a warning to other parts of the system. This warning can be used to turn off devices safely before they are affected by the undervoltage.

During an overvoltage,  $V_{BAT}$  voltage exceeds the nominal level. This can cause unexpected behaviour and even damage to some systems. A melting fuse has no way of detecting an overvoltage; therefore, the protection needs to be built in into the devices. An e-fuse can monitor the  $V_{BAT}$  voltage, and when it detects an overvoltage, it can generate a warning and eventually interrupt the circuit. This means that the devices in the circuit protected by the e-fuse do not need to implement their own overvoltage protection.

Overvoltage protection becomes more important as new power distribution systems in cars start to include 48 V supply. A short between the 12 V and 48 V power rails could

cause the 48 V voltage to appear on the 12 V power rail. This would probably destroy most devices connected to that power rail. An e-fuse with overvoltage protection will reliably protect the devices.

#### Overtemperature protection

While the above-mentioned protection mechanisms focus on protecting the circuit wiring and devices connected to it, overtemperature protection primarily aims to protect the e-fuse itself. Like every electronic device, the e-fuse has a maximum operating temperature. When this temperature is exceeded, the e-fuse may not behave according to specification or be damaged. The e-fuse can overheat due to the high current passing through it (power loss in the switch) or due to high ambient temperatures. Usually, overheating is caused by the combination of these two factors.

In order for the power distribution to operate safely, the e-fuse needs to operate safely as well. This is the reason why e-fuses implement overtemperature protection. It is fairly easy to implement temperature monitoring in integrated circuits. A diode or a pair of diodes is used. The temperature dependence of these structures is well known  $(-2 \text{ mV K}^{-1} \text{ for an Si diode})$ . The voltage of this structure is monitored, and once the voltage corresponding to the maximum junction temperature is reached, the overtemperature protection engages.

The e-fuse can also generate a warning that its temperature is approaching the maximum possible level. This can help the system to prevent the e-fuse from overheating by lowering the current passing through it or engaging active cooling (a fan).

#### **Power limitation**

Another way the e-fuse can protect itself is through power limitation. Sufficiently high currents can damage the e-fuse even before the overtemperature or short-circuit protections step in. The high currents can potentially melt the bonding wires between the silicon chip itself and the package pins. This would make the e-fuse completely unusable, and it would need to be replaced. This current limit  $(I_{LIM})$  can be in excess of 150 A.

There is no need to interrupt the current passing through the e-fuse; it is enough to limit it. This can be done by changing the operating point of the power transistor. It is possible to change the gate voltage so that the transistor  $R_{DS(on)}$  resistance increases. This is another advantage of the integrated circuit e-fuse. The increase in on-resistance limits the current that can pass through the e-fuse at the supply voltage (see Ohm's law).

The increased  $R_{DS(on)}$  also means larger power loss and, therefore, heating of the e-fuse. If the current is limited for long enough, the e-fuse reaches its maximum temperature, and the overtemperature protection interrupts the current. The increased on-resistance also means a large voltage drop across the e-fuse, meaning the circuit voltage (power for devices protected by the e-fuse) will be lower.

There are various ways to implement this kind of protection. One way is to monitor the current and when it exceeds the  $I_{LIM}$  current, change the transistor gate voltage to increase the  $R_{DS(ON)}$ . This approach has the disadvantage of being fairly slow as the current measurements take time. Another option is to place two diodes into the IC. One close to the power transistor, the other on the edge of the die. When a large current passes through the transistor, it heats up, and so does one of the diodes. By comparing the forward voltages of these diodes, a temperature gradient can be detected. If it is large enough, the power limitation is triggered.

### 3.2.4 Additional e-fuse features

Thanks to the e-fuse being an integrated circuit, it is possible to include additional features that extend the use of the device beyond just a fuse. These features can improve the safety and reliability of the power distribution system as well as provide greater control over it.

Modern integrated logic technology allows manufacturers to include complex, computationally demanding features into their devices. The result of this are so-called smart electronic fuses. The inclusion of some communication interface (SPI,  $I^2C$ ) into the e-fuse gives the user more control and much more information.

#### Fault diagnostic

At their most basic, e-fuses do not differ much from ordinary melting fuses. They interrupt the current when it exceeds a certain level or when the  $I^2t$  rating is exceeded. It is impossible to distinguish the reason for the melting fuse to blow. However, the e-fuse can be equipped with dedicated diagnostic pins or diagnostic registers, which can be accessed through a communication interface.

This can be very useful in case of overloads, which are usually caused by malfunctioning devices. By latching off and then unlatching again, the e-fuse resets the device, which might clear the overload fault. Knowing that there is an overloaded device in the circuit, the controller may disable it, thereby removing the source of the overload. On the other hand, if the cause of the e-fuse latching off is a short-circuit, it is usually caused by wiring damage. The retry strategy can be defined by the car manufacturer to suit the application.

#### Open load detection

By monitoring the various currents and voltages available, the e-fuse becomes a source of valuable data. This data can be used to diagnose the state of the circuit. Open load detection (OLD) can detect if the load has been disconnected from the e-fuse. This mechanism is often implemented in high side switches and drivers. There are two kinds of open load detection. Off-state (offline) when the switch is open and On-state (online) when the switch is closed.

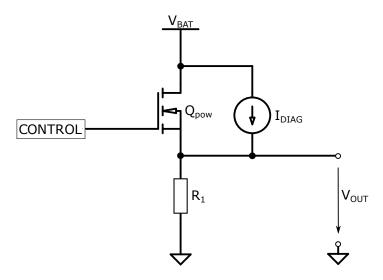

On-state open load detection monitors the current passing through the device. When it falls below the open load current threshold  $I_{OLD}$ , it is evaluated as an open load state. Off-state open load detection works as indicated in the schematic in figure 3.10. When the power transistor is off, a source of small diagnostic current ( $I_{DIAG}$ ) is connected to the output. The control logic senses the power supply voltage  $V_{BAT}$  and the output voltage  $V_{OUT}$ . If the load is connected ( $R_{LOAD}$  is small), the diagnostic current is not high enough to cause a large enough voltage drop across the load. However, if the load is disconnected ( $R_{LOAD}$  is high), the output of the device is pulled high to the supply voltage  $V_{BAT}$ . This voltage can be measured by the control circuitry. The current source could be replaced by a resistor, but in an IC, it is simpler to use a current source.

Figure 3.10: Open load detection mechanism

#### E-fuse parameter programmability

E-fuse properties are defined by the control logic. The logic of the e-fuse can be programmed to fit the application. The e-fuse's breaking current and time characteristics can be defined by setting one or more parameters. These settings can be based on the required  $I^2t$  of the e-fuse.

There are various ways of programming the e-fuse. For simpler e-fuses, it can be done by external resistors. If the e-fuse is equipped with a communication interface, SPI for example, it can be programmed by simply setting the values in appropriate registers. The programming can also be done by writing the one time programmable (OTP) memory in the e-fuse. The OTP is programmed when the e-fuse is installed into the system in the factory. Using OTP can reduce the risk of fault due to accidental rewrite of the e-fuse parameters.

The fact that e-fuses can be programmed to a specific application also relieves supply chain issues. Instead of several different types of melting fuses with different parameters, one type of integrated circuit (i.e. an e-fuse) is used and programmed as needed.

#### Automatic fuse reset

When a melting fuse clears a fault in the circuit, it is destroyed and needs to be replaced. That means that the systems protected by the fuse are inoperable until the fuse is replaced. This is problematic for systems responsible for the safety of the vehicle. To solve this problem in modern cars, there are two independent power supplies for such systems.

When an e-fuse clears a fault, it simply switches off a transistor. This transistor can be switched on again. When an overload in the system is caused by a device malfunction, it is possible that the device malfunction was only temporary, and the reset (because of the power supply loss) fixed the problem. That is the reason why e-fuses come with auto-reset functionality. When the e-fuse latches off, it way for a period of time and then unlatches. This process can be repeated. Most e-fuses have a maximum number of retries before requiring action by a master system.

#### Health monitoring of the wiring

Health monitoring of the wiring harness is a very advanced functionality proposed for the next generation of electronic fuses. These e-fuses operate with a model of the power distribution grid. Using the model of the wiring and the measurements of the current passing through it, they are able to estimate the temperature of the wiring. From this, it is possible to estimate the state of health of the wiring. This can be used to determine the remaining useful life (RUL) of the wiring.

Normally, the wiring is replaced only when it is damaged. This is unsatisfactory from the point of safety as the wiring could fail at a critical moment (i.e. emergency braking). When a reliable estimate of the remaining useful life is known, predictive maintenance can be applied. When the wiring is nearing the end of its RUL, it is replaced during regular service.

#### Capacitive charging mode

Modern cars are equipped with a large number of electronic devices which need to be powered. These electronic devices draw current in short pulses, which can be so large that the power supply can not deliver them, or they can be limited by the impedance of the power lines. This is why electronic devices require decoupling (or bypass) capacitors that are capable of delivering short high current pulses. Through the combination of many devices in the circuit or one device with very large capacitance, the capacity that needs to be charged when the circuit is turned on can become very large, in the range of millifarads. A car's battery is an excellent voltage source, and when a capacitor is connected to it, the capacitor will start to charge to the battery's voltage. The charging current is defined by the circuit resistance, battery voltage and capacitor voltage. The circuit resistance is a combination of factors: battery internal resistance, wiring resistance and the equivalent series resistance (ESR) of the capacitor. The blocking capacitors tend to have low ESR values, as that makes them more efficient and reliable. That means that the capacitor charging currents can become very large (in excess of 100 A), which could be damaging to the circuit. Capacitive charging tries to solve this problem by limiting the RMS value of the current to a manageable level. Meaning the capacitor will take longer to charge (milliseconds instead of microseconds), but the current will not damage the e-fuse or the circuit. One way of limiting the current is to use a pulse width modulation (PWM) during turning on of the e-fuse, which will charge the capacitor a little bit every time the e-fuse turns on, limiting the time the current is flowing, thus limiting the RMS value.

#### 3.2.5 E-fuse vs Melting fuse comparison

Now that the electronic fuse has been introduced and the application of fuses in automotive has been discussed, a comparison between the electronic fuse and the melting fuse can be made. In this section, the advantages and disadvantages of using e-fuses instead of melting fuses will be discussed.

For these reasons and many more, the automotive industry has started to adopt electronic fuses instead of melting fuses. The introduction of e-fuses brings a reduction of costs during manufacturing. They also help to reduce the weight of the car (slightly), which in turn helps to reduce fuel consumption and  $CO_2$  emissions. E-fuses also help manufacturers to keep up with the increasing demands on reliability and safety.

#### Reusability of electronic fuses

The obvious advantage of e-fuse over melting fuses is the reusability of the e-fuses. When a melting fuse clears an overcurrent event, it needs to be replaced. The e-fuse just needs to be switched back on. Since e-fuses are not user-replaceable, there is no need to place them somewhere accessible, like a fuse box. An e-fuse can be integrated directly into the system it is meant to protect, or it can be a part of a large power distribution module. The absence of a fuse box means more space for other systems and a lower overall weight of the car. The reusability of e-fuses also improves the safety and reliability of the car.

#### Improved accuracy of fault detection

As was already mentioned, the e-fuse relies on measuring the current, rather than on the effect of the current on the fuse, to protect the circuit from overcurrent. This helps to improve the accuracy of the fuse. Melting fuses have quite large manufacturing tolerance, which has a negative influence on the variance of their parameters. Integrated circuits are manufactured with much smaller tolerances. If the current measurement is done correctly, the e-fuse can react more accurately, which can lead to reduction of diameter of wiring connected to the e-fuse. This can, in turn, reduce weight, cost and emissions. The same applies to reaction times. The e-fuse has built-in logic that will react to overcurrent as fast as specified.

#### Variability e-fuse parameters

The fact that e-fuses are programmable also increases their variability. The designers of the power distribution system are no longer limited by the range of available fuses. They are able to define the e-fuse behaviour exactly as is required for the protected circuit.

Furthermore, some e-fuses can be reprogrammed during operation (those with a communication interface), which allows the system to change the e-fuse properties during an emergency (limp-home mode). One scenario when this can be used is when a vital system malfunctions and requires more power to continue working. The power distribution system may allow temporary overload of the circuit by changing the nominal current rating in order to keep the system working.

#### Control and monitoring

By controlling the logic of the e-fuse, it is possible to control the power MOSFET. With this, the e-fuse can be used as a high side switch. This allows the power grid controller to connect and disconnect the loads protected by the fuse. The monitoring of various voltages and currents provides a lot of information about the circuit. By combining these features, the e-fuse improves the management of the power distribution system.

#### Price and life-time

One of the disadvantages of electronic fuses is price. E-fuses are more expensive than melting fuses, due to the fact that they are complex electronic devices. The price difference is however offset by savings in other areas, such as the reduced diameter of wiring.

Both melting and electronic fuses are designed for a specific life-time. Melting fuses have shorter life-times, due to the fact that the mechanical stresses caused by thermal cycling, weaken their structure. Electronic fuses are designed for the same life-time as most automotive electronics (around 80000 hours), which is much longer than a life-time of a melting fuse.

#### Failure conditions

When discussing functional safety of a device, its failure states need to be considered. This is a problematic topic when it comes to electronic fuses. When an electronic fuse fails (burns out), there are two failure modes of its power switch: fail open and fail closed. In the event the e-fuse fails open, the circuit remains protected, but nonfunctional. In case the e-fuse fails closed, the current can pass through it uncontrollably and the circuit is not protected. Currently, there is no way to guarantee that the switch fails open. This safety problem can be solved by using one central melting fuse to prevent catastrophic overcurrents. Another option is to use two e-fuses in parallel; therefore, if one fails open, the other can still interrupt the current.

# Chapter 4 Emulator design requirements